## POLITECNICO DI TORINO Repository ISTITUZIONALE

### A Rail-to-Rail Ultra-Low Power OTA Based on a Hybrid Nauta-DIGOTA Topology

Original

A Rail-to-Rail Ultra-Low Power OTA Based on a Hybrid Nauta-DIGOTA Topology / Faustini, Paolo; Richelli, Anna; Colalongo, Luigi; Crovetti, Paolo. - STAMPA. - (2024), pp. 1-4. (Intervento presentato al convegno 19th Conference on Ph.D Research in Microelectronics and Electronics (PRIME) tenutosi a Larnaca (Cyprus) nel 9-12 June 2024) [10.1109/PRIME61930.2024.10559718].

Availability: This version is available at: 11583/2990103 since: 2024-07-01T14:50:34Z

Publisher: IEEE

Published DOI:10.1109/PRIME61930.2024.10559718

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2024 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A rail-to-rail ultra-low power OTA based on a hybrid Nauta-DIGOTA topology

Paolo Faustini<sup>1</sup>, Anna Richelli<sup>1</sup>, Luigi Colalongo<sup>1</sup>, Paolo Crovetti<sup>2</sup>

<sup>1</sup>Department of Information Engineering, University of Brescia, Brescia, Italy <sup>2</sup>Dept. of Electronics and Telecommunications (DET), Politecnico di Torino, Torino, Italy e-mail: paolo.faustini@unibs.it

*Abstract*—A novel ultra-low power amplifier is presented, composed of a Nauta amplifier ( $1^{st}$  stage) and a digital OTA ( $2^{nd}$  stage). This configuration significantly improves the performance in terms of signal distortion, by allowing the DIGOTA to work in a better operating window. The proposed amplifier has been a validated through simulations in TSMC 0.18 µm and compared to the DIGOTA: when used as a voltage-follower it features a much lower output distortion, especially for low amplitude signals.

Index Terms-ultra-low power, digital-based amplifier, Nauta amplifier

#### I. INTRODUCTION

In recent years, CMOS technological processes have undergone significant improvements, both in terms of feature size and minimum supply voltage. Although digital circuits have benefited greatly, their analog counterparts still lag behind: deteriorating intrinsic gain, reduced voltage swing [1, 2], short channel effects and increased process variability [3] have had a limiting effect on such improvements in analog blocks.

Furthermore, analog circuit design still requires a significant design effort in simulation, transistor level optimization, layout design and prototyping [1, 2].

Recently, the literature features a strong research interest towards the implementation of analog functionalities through purely digital circuits. Analog blocks such as ADCs [4, 5], DACs [6] and voltage comparators [7] have been reported in the literature. Several variations of digital-based analog amplifiers (DIGOTAs) have also been investigated [3, 8, 9, 10]. Thanks to their digital mode of operation, DIGOTAs can achieve nanoWatt scale power consumption at ultra-low power supplies down to 250 mV [9]. Unfortunately DIGOTAs have some limitations, especially with low amplitude signals. This can be an issue in biomedical applications, where signals are typically weak [11].

In this paper, a novel amplifier stage is presented: it is based on a fully-differential Nauta amplifier followed by a DIGOTA. It exhibits better performance, while still retaining a very low power consumption.

#### II. DIGOTA

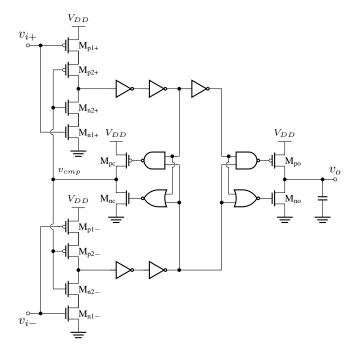

Fig. 1 shows the schematic of the DIGOTA. It should be noted that thanks to its digital operation, the DIGOTA doesn't operate around a DC operating point like traditional amplifiers, but realizes its amplification through the digital domain.

The main building blocks of the DIGOTA are a pair of Muller C-elements as an input stage and a network of logic

Fig. 1. Schematic of the DIGOTA.

gates that implements an internal feedback loop, as well as a path towards the output stage.

The pair of Muller C-elements are part of a pair of coupled ring oscillators, thanks to the internal feedback loop and the signal  $v_{cmp}$ , which forces a synchronized oscillation. The Muller C-elements act as inverters whose delay is voltagecontrolled by the inputs  $v_{i\pm}$ , through the current-starving action of the transistors  $M_{n1\pm}$  and  $M_{p1\pm}$ . This configuration allows the circuit to perform a voltage-to-time conversion: in the presence of a differential input  $v_{iD}$ , the input with the lower value will feature a slower falling edge and a faster rising edge in the output signal of its Muller C-element. This translates into a difference in the propagation delays: the two Muller C-element outputs are detected as different logic levels by the following logic network for a time interval  $\Delta t_C$ .  $\Delta t_C$  is proportional to the differential input voltage and is translated by the output stage into a current pulse whose duration is itself proportional to  $v_{iD}$ , thus enacting a transconductance amplification.

Thanks to its mostly digital operation, the DIGOTA can achieve a very low power consumption, due to the absence of the static biasing current that is required in the operation of traditional analog stages. Furthermore, digital circuits can operate with lower supply voltages compared to their analog counterparts. This makes the DIGOTA a prime candidate in those applications where very little power is available, for example where the power supply is obtained through energy harvesting. Unfortunately, the DIGOTA features some significant limitations:

- because of its digital operation, the transcharacteristic curve features a flat spot (deadzone) around  $v_{iD} = 0$ . Small values of  $|v_{iD}|$  produce very short intervals  $\Delta t_C$ , which are not long enough to activate the output stage, due to the non-negligible switching delays of  $M_{no,po}$ ;

- the input common-mode range is limited by the Muller C-element input stage: when the inputs  $v_{i\pm}$  approach GND ( $V_{DD}$ ), the strong current-starving action of  $M_{n1\pm}$  ( $M_{p1\pm}$ ) greatly decreases the self-oscillation frequency, thus deteriorating the performance of the DIGOTA.

The first issue is particularly damaging for low amplitude signals, since the relative impact of the deadzone becomes bigger.

#### III. NAUTA-DIGOTA

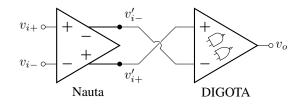

Fig. 2. Schematic of the Nauta-DIGOTA.

A novel transconductance amplifier stage has been devised, composed of a fully differential analog stage, implemented as a Nauta amplifier and a DIGOTA, as shown in fig. 2. The overall amplifier exhibits an increased differential gain and improved behaviour of the Muller C-elements.

#### A. Nauta amplifier

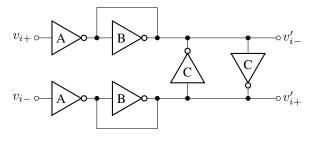

The schematic of the Nauta amplifier is shown in fig. 3. The input stage is based on the pair of inverters A, whose active load is a pair of self-coupled (B) and cross-coupled (C) inverters.

The Nauta amplifier achieves common-mode rejection with the contrasting actions of inverters B and C, maximized if they have the same aspect ratio and size. By also using the same size for inverters A, the gain simplifies to  $A_{vD} = A_v/3$ ,  $A_{vCM} \approx -1/2$ , where  $A_v = G_m r_o$  is the intrinsic gain of the single inverter.

Although the common-mode rejection is quite limited, it's still adequate for the use in the Nauta-DIGOTA, since most of the common-mode attenuation is enacted by the DIG-OTA. Furthermore, the differential gain introduced by this

Fig. 3. Schematic of the Nauta amplifier.

stage, although limited, helps to increase the overall amplifier transconductance.

#### IV. SIMULATION RESULTS

The DIGOTA shown in fig. 1 and the Nauta-DIGOTA shown in fig. 2 were designed using the TSMC  $0.18 \,\mu\text{m}$  technology. In order to enable a fair comparison between the two amplifiers, the same exact dimensioning was used for both DIGOTAs, adapted from the one in [9]. Both amplifiers are designed to operate with a 300 mV power supply, as well as to drive a large 150 pF output load.

Due to the digital operation of the DIGOTA, all simulations are carried out as transient analyses and the frequency response is calculated using a DFT function.

A. Transconductance deadzone

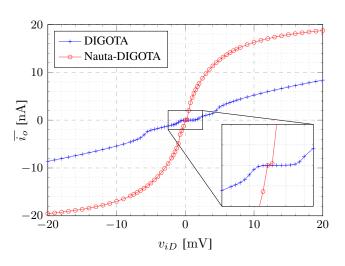

Fig. 4. Transcharacteristic plot of the two amplifiers for  $v_{iCM} = 150 \text{ mV}$ .

The transcharacteristic of both amplifiers is shown in fig. 4. As highlighted by the inset, the DIGOTA features a deadzone around  $v_{iD}$ : the output stage transistors cannot drive the very short current pulses required in this condition. The introduction of the Nauta stage helps in this regard: the differential gain between the input  $v_{i\pm}$  and the input for the DIGOTA  $v'_{i\pm}$  greatly reduces the amplitude of the deadzone, thus reducing its effect on the amplifier performance. Furthermore, fig. 4 also shows the much greater transconductance that is achieved in the Nauta-DIGOTA, thanks to the differential gain of the Nauta stage.

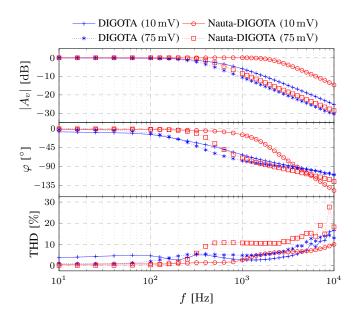

Fig. 5. Frequency characterization of the two amplifiers in a voltage-follower configuration, including the total harmonic distortion.

The frequency characterization is carried out using a unitygain voltage-follower configuration. Fig. 5 shows the results for both amplifiers for two different values of the input amplitude: a small signal (10 mV) and a much larger one (75 mV). In both cases, the DC offset of the input is the midway point of the power supply  $V_{DD}/2 = 150 \text{ mV}$ .

Predictably, both amplifiers feature a wider bandwidth for the smaller signal input: this can be explained by a combination of two phenomena:

- larger input signals reach the slew-rate limit at much lower frequencies compared to smaller signals;

- the self-oscillation frequency of the DIGOTA depends on the common-mode input: due to the stronger currentstarving action when the inputs are near GND or  $V_{DD}$ , the average self-oscillation frequency is smaller for larger input signals. Since the self-oscillation frequency acts as a sampling frequency (the input is only evaluated when the output of the Muller C-elements cross the logic threshold), a lower sampling frequency worsens the performance of the amplifier.

Conversely, the total harmonic distortion of the output for both amplifiers is better for the large signal input: this is explained by the greater relative effect of the width of deadzone on smaller signals.

Tab. I shows the comparison between the two amplifiers: the introduction of the Nauta stage increases the bandwidth of the amplifier and its differential gain  $A_d$ . The THD of the output at low frequencies is also much lower, due to the increased gain and the reduced deadzone amplitude. It should be noted that the sharp increase of the THD for the 75 mV input signal for the Nauta-DIGOTA around 400 Hz is caused by the slew-rate limit.

TABLE I

FREQUENCY CHARACTERIZATION OF THE AMPLIFIERS

|                  | $A_i$ | GBW     | A <sub>d</sub> @ 10 Hz |

|------------------|-------|---------|------------------------|

| DIGOTA           | 10 mV | 572 Hz  | 7.71 dB                |

|                  | 75 mV | 367 Hz  | 33.4 dB                |

| Nauta-<br>DIGOTA | 10 mV | 2823 Hz | 34.4 dB                |

|                  | 75 mV | 523 Hz  | 49.6 dB                |

#### C. Amplitude characterization

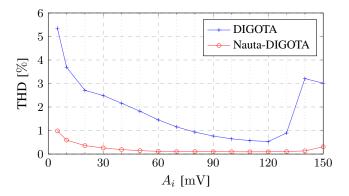

Fig. 6. THD of the output of the two amplifiers, in a voltage-follower configuration, for a 10 Hz sinusoidal input of varying amplitude.

In order to fully appreciate the improvements caused by the Nauta stage, the amplifiers are characterized in a voltagefollower configuration and a fixed frequency sinusoidal input (10 Hz) is applied, whose amplitude  $A_i$  is varied across the whole power supply range.

Fig. 6 shows the results of this characterization. For both amplifiers, the THD gets significantly worse when the amplitude matches one of two conditions:

- for a smaller input amplitude, the THD increases, due to the stronger effect of the deadzone on the output;

- for inputs that span nearly the entire supply range, the distortion is much greater due to the worse performance of the DIGOTA near the power supplies, caused by the reduced self-oscillation frequency.

Those trends are still visible in the Nauta-DIGOTA, but the presence of the Nauta stage greatly improves the THD below 1 % for all signals with an amplitude of at least 5 mV, due to the increased differential gain, the reduction in the deadzone width and the better operational range of the Muller C-elements.

#### D. Transient waveforms

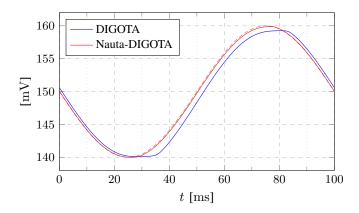

In order to better show the shape of the output waveforms, a single period of the output of a 10 Hz, 10 mV sinusoidal input is shown in fig. 7. The distortion is much more noticeable in the DIGOTA case:

• when  $v_{iD} > 0$ , the presence of the deadzone introduces a voltage offset, which prevents the output from getting close to the input.

Fig. 7. Transient waveform for a 10 Hz, 10 mV sinusoidal input.

• when  $v_{iD} < 0$ , the voltage offset has the opposite sign, thus the output is bigger than the input.

This translates in an apparent phase delay between the input and the output. Furthermore, asymmetries in the DIGOTA mean that the deadzone is not symmetric itself: in this case it's much bigger in the  $v_{iD} > 0$  case.

In fig. 7, the output waveforms feature a "flat-spot" near the peaks of the sine wave: this is once again caused by the deadzone, which prevents the activation of the output stage when the differential input is too close to 0.

E. Slew-rate

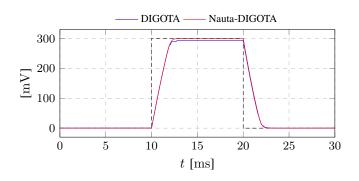

Fig. 8. Transient waveforms used to measure the slew-rate.

Fig. 8 shows the waveforms of the step response of the two amplifiers in a voltage-follower configuration used to measure the slew rate. The waveforms clearly show how the presence of the Nauta stage does not affect the slew-rate, since it only depends on the output stage of the DIGOTA and the load capacitance. The average slew rate is 143.8 V/s for the DIGOTA and 145.2 V/s for the Nauta-DIGOTA.

#### F. Power consumption

The addition of the analog Nauta stage leads to a higher power consumption for the Nauta-DIGOTA. Furthermore, the Nauta stage forces the inputs of the DIGOTA to operate much closer to  $V_{DD}/2$ , thus increasing the self-oscillation frequency and further increasing power consumption. Nevertheless, the power consumption of the Nauta-DIGOTA is still in the nanoWatt range, as shown in tab. II.

TABLE IIPOWER CONSUMPTION IN A VOLTAGE-FOLLOWER CONFIGURATION( $P_{10 \ Hz}$  REFERS TO A 10 Hz SINUSOIDAL INPUT,  $P_{max}$  REFERS TO THEHIGHEST POWER CONSUMPTION AMONG THE POINTS IN FIG. 5)

|              | $A_i = 10 \mathrm{mV}$ |           | $A_i = 75 \mathrm{mV}$ |           |

|--------------|------------------------|-----------|------------------------|-----------|

|              | $P_{10  \text{Hz}}$    | $P_{max}$ | $P_{10\mathrm{Hz}}$    | $P_{max}$ |

| DIGOTA       | 1.592nW                | 2.070nW   | 1.001nW                | 2.995nW   |

| Nauta-DIGOTA | 2.147nW                | 3.667nW   | 2.282nW                | 5.131nW   |

#### G. Corner analysis

In order to verify the robustness of the Nauta-DIGOTA against process variations, the worst-case corner analysis was carried out. In a voltage-follower configuration, with a 10 Hz, 10 mV input, the Nauta-DIGOTA guaranteed an output distortion lower than 0.9%. On the contrary, the worst case for the DIGOTA (the SF corner) featured a 7.9% THD.

#### REFERENCES

- P. Toledo et al. "Re-Thinking Analog Integrated Circuits in Digital Terms: A New Design Concept for the IoT Era". In: *IEEE Transactions* on Circuits and Systems II: Express Briefs 68.3 (2021), pp. 816–822. DOI: 10.1109/TCSII.2021.3049680.

- [2] B. Xu et al. "A scaling compatible, synthesis friendly VCO-based delta-sigma ADC design and synthesis methodology". In: 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC). 2017, pp. 1– 6. DOI: 10.1145/3061639.3062192.

- [3] P. S. Crovetti. "A Digital-Based Analog Differential Circuit". In: *IEEE Transactions on Circuits and Systems I: Regular Papers* 60.12 (2013), pp. 3107–3116. DOI: 10.1109/TCSI.2013.2255671.

- [4] O. Aiello, P. Crovetti, and M. Alioto. "Fully Synthesizable Low-Area Analogue-to-Digital Converters With Minimal Design Effort Based on the Dyadic Digital Pulse Modulation". In: *IEEE Access* 8 (2020), pp. 70890–70899. DOI: 10.1109/ACCESS.2020.2986949.

- [5] S. Weaver, B. Hershberg, and U.-K. Moon. "Digitally Synthesized Stochastic Flash ADC Using Only Standard Digital Cells". In: *IEEE Transactions on Circuits and Systems I: Regular Papers* 61.1 (2014), pp. 84–91. DOI: 10.1109/TCSI.2013.2268571.

- [6] R. Rubino et al. "A 880 nW, 100 kS/s, 13 bit Differential Relaxation-DAC in 180 nm". In: 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME). 2023, pp. 269–272. DOI: 10.1109/PRIME58259.2023.10161768.

- [7] X. Zou and S. Nakatake. "A Fully Synthesizable, 0.3V, 10nW Railto-rail Dynamic Voltage Comparator". In: 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS). 2020, pp. 199–202. DOI: 10.1109/MWSCAS48704.2020.9184498.

- [8] A. Richelli et al. "An Investigation of the Operating Principles and Power Consumption of Digital-Based Analog Amplifiers". In: *Journal* of Low Power Electronics and Applications 13.3 (2023). ISSN: 2079-9268. DOI: 10.3390/jlpea13030051.

- [9] P. Toledo et al. "Design of Digital OTAs With Operation Down to 0.3 V and nW Power for Direct Harvesting". In: *IEEE Transactions on Circuits and Systems I: Regular Papers* 68.9 (2021), pp. 3693–3706. DOI: 10.1109/TCSI.2021.3089339.

- [10] R. Rubino, S. Carrara, and P. Crovetti. "Direct Digital Sensing Potentiostat targeting Body-Dust". In: 2022 IEEE Biomedical Circuits and Systems Conference (BioCAS). 2022, pp. 280–283. DOI: 10.1109/ BioCAS54905.2022.9948649.

- [11] L. Zhu et al. "A High CMRR Differential Difference Amplifier Employing Combined Input Pairs for Neural Signal Recordings". In: *IEEE Transactions on Biomedical Circuits and Systems* 18.1 (2024), pp. 100–110. DOI: 10.1109/TBCAS.2023.3311465.