# POLITECNICO DI TORINO Repository ISTITUZIONALE

# Hardware Model Checking Algorithms and Techniques

Original

Hardware Model Checking Algorithms and Techniques / Cabodi, Gianpiero; Camurati, Paolo Enrico; Palena, Marco; Pasini, Paolo. - In: ALGORITHMS. - ISSN 1999-4893. - ELETTRONICO. - 17:6(2024). [10.3390/a17060253]

Availability: This version is available at: 11583/2989815 since: 2024-06-24T16:43:30Z

Publisher: MDPI

Published DOI:10.3390/a17060253

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

# **Hardware Model Checking Algorithms and Techniques**

Gianpiero Cabodi <sup>1,\*</sup>, Paolo Enrico Camurati <sup>1</sup>, Marco Palena <sup>2</sup>, and Paolo Pasini <sup>3,\*</sup>

- <sup>1</sup> DAUIN, Department of Control and Computer Engineering, Politecnico di Torino, 10129 Turin, Italy; paolo.camurati@polito.it

- <sup>2</sup> CNIT, National Inter-University Consortium for Telecommunications, 10129 Turin, Italy; marco.palena@cnit.it

- <sup>3</sup> DET, Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Turin, Italy

- \* Correspondence: gianpiero.cabodi@polito.it (G.C.); paolo.pasini@polito.it (P.P.); Tel.: +39-011-090-7082 (G.C.)

**Abstract:** Digital systems are nowadays ubiquitous and often comprise an extremely high level of complexity. Guaranteeing the correct behavior of such systems has become an ever more pressing need for manufacturers. The correctness of digital systems can be addressed resorting to formal verification techniques, such as model checking. Currently, it is usually impossible to determine a priori the best algorithm to use given a verification task and, thus, portfolio approaches have become the de facto standard in model checking verification suites. This paper describes the most relevant algorithms and techniques, at the foundations of bit-level SAT-based model checking itself.

Keywords: formal verification; model checking; SAT; Boolean functions

# 1. Introduction

Ranging from commodity devices to business or safety critical environments, digital systems have proliferated into most aspects of our daily lives. Moreover, thanks to Moore's law and the advent of high-level synthesis, contemporary hardware designs often comprise an extremely high level of complexity. As a direct consequence, design verification has become one of the most relevant aspects of the design and production flow. In such a scenario, guaranteeing the correct behavior of digital systems, with respect to their specification, is becoming an ever more pressing need for manufacturers [1]. The increasing complexity of hardware designs, together with the demand for short development cycles imposed by ever evolving markets, makes the delivery of defect-free systems an extremely challenging task. This is particularly true when considering sequential designs, in which the behavior of the system depends not only on the inputs applied at a given time but also on the state the system finds itself in. Modern systems are characterized by the presence of several million elements, those being transistors, logic gates, memory elements or other things. In such a scenario, design verification can represent one of the most time consuming, yet necessary, activities to be performed, with reports purporting it in the range between 40% and 70% of the entire cycle's endeavor [2]. Oftentimes, the usual testing techniques are not enough to prove the correctness of a whole system in a timely fashion, and further problems arise when taking into account the issue of transferring theoretical results to industrial practice [3].

Traditionally, hardware designs are verified through *simulation*. In simulation, a model of the system is solicited by a set of stimuli while the resulting behavior is checked against the expected behavior. Simulation is scalable, being applicable to designs of virtually any size, but is also costly and incomplete. In fact, it is often unfeasible to completely cover the behaviors of a realistic design through simulation. The incompleteness of simulation is often aggravated by the increasing complexity of hardware designs, which not only increases the number of behaviors to check but may also introduce corner cases difficult to cover. Starting from the late 1980s, *formal hardware verification* has become an attractive approach to overcome the coverage limitations of simulation. Formal verification is the use

Citation: Cabodi, G.; Camurati, P.E.; Palena, M.; Pasini, P. Hardware Model Checking Algorithms and Techniques. *Algorithms* **2024**, *17*, 253. https:// doi.org/10.3390/a17060253

Academic Editor: Jesper Jansson

Received: 8 May 2024 Revised: 5 June 2024 Accepted: 7 June 2024 Published: 9 June 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). of the formal methods of mathematics and logic to prove (or disprove) the correctness of a design with respect to a given formal specification of its expected behavior. During the last two decades, research in the field of formal verification has led to the development of many techniques. Such techniques can be subdivided into three main approaches to formal verification: *theorem proving* [4,5], *equivalence checking* [6] and *model checking* [7,8].

Model checking is the most widely used formal verification approach for sequential hardware designs. In model checking, a *model* of the design and a formalized representation of its specification are formulated using some mathematically precise and unambiguous language. Then, an algorithmic procedure automatically checks whether or not the model meets the formal specification. Such a procedure exhaustively traverses the modeled behaviors of the system and either confirms that the system behaves correctly or produces a trace that demonstrates a violating behavior (called a *counterexample*). The main advantages of model checking are its fully automated nature and its ability to produce counterexamples. Usually, the design to be verified is modeled as a *transition system*, comprising states and transitions between states, and the specification is formalized by writing *temporal logic properties*. Invariant verification is a particular model checking task in which the system specification is described as an invariant property that must hold true in every reachable state of the model.

From an algorithmic standpoint, in the beginning, model checking was based on explicit state enumeration; thus, its practical application was severely hindered by mere state space representation problems. The introduction of BDD-based representation [9] was the turning point for model checking applicability to industrial-level scenarios. Despite the huge impact of such an approach to model checking, BDD-based representations still suffered from unpredictable memory requirements and, thus, additional paths of research opened up in order to overcome such limits, such as the introduction of SAT-based approaches.

Today, model checking can exploit explicit state enumeration or symbolic state enumeration, via BDD- or SAT-based representations. Furthermore, solutions based on automatic test pattern generations are admissible. Each of these, in turn, has led to a number of distinct model checking algorithms and techniques.

Up until today, there is not a concrete winner among all the available techniques. The most reliable approach is obtained from running in parallel several of these algorithms, exploiting multi-core environments, and halting verification as soon as one of the engines has found a solution to the verification problem at hand [10,11].

Complementary to the verification phase itself, there is then the additional problem of certifying checkers' results, in order to better support their acquisition in complete design cycles scenarios [12,13].

A recent trend in hardware model checking is to exploit the ability of SMT solvers to perform word-level reasoning based on bit-vectors. This trend is demonstrated by the introduction of word-level tracks in recent editions of the Hardware Model Checking Competition [14]. However, word-level model checking shines for problems with memory modeled with arrays; bit-level solvers are currently the de facto standard in the industry and prove to be still superior on many word-level designs after bit-blasting [15].

This paper (part of the contents of this paper are a redacted version of the introductory chapters of the PhD thesis of two of its authors, Marco Palena [16] and Paolo Pasini [17], which have not been published before besides diffusion within the Politecnico di Torino and the respective thesis defense committees) describes the most relevant algorithms and techniques targeting explicitly bit-level SAT-based hardware model checking, in a formal and theoretically sound fashion. A description of complementary topics and a broader overview of the vast field of model checking and satisfiability is provided in [18,19]. A description of topics concerning model checking, with additional examples and applications, is provided in [8]. Complementary to previous works, a specific focus on the design and verification of cyber-physical systems is provided in [20].

# Outline

The rest of the paper is organized as follows:

- In Section 2, we provide some preliminary notions with the purpose of presenting the adopted notation and terminology and make this work self-contained. In particular, we first provide some general concepts from the field of logic and computer science and then we discuss in more depth the necessary concept to contextualize model checking in detail.

- In Sections 3–7, we present a complete description of the most relevant bit-level SAT-based hardware model checking algorithms.

- In Section 8, we present a practical evaluation of model checking algorithms over industrial-level benchmarks.

- In Section 9, we summarize the current work and provide some insights concerning future developments in the field.

#### 2. Background and Notation

In this section, we introduce some notions needed to understand the rest of the paper. In particular, we provide some basic concepts and definitions from the fields of logic and computer science relevant to the topics at hand.

#### 2.1. Mathematical Logic

Model checking aims at verifying whether a finite-state model of a system meets a given specification. In order to solve such a problem algorithmically, both the model of the system and its specification need to be expressed in some precise mathematical language. The fields of mathematical logic and formal language theory provide us the tools we need to reason about the system states in a symbolical and rigorous manner. Mathematical logic is the systematic study of reasoning. By reasoning, we intend the abstract capability to provide *arguments* supporting the fact that a given statement, called the *conclusion*, follows from some other statements, called the *premises*. The steps through which conclusions are reached from premises are termed *inferences*. Mathematical logic relies on *formal languages* in order to provide a symbolic representation of abstract concepts, like statements about the model of the system we are interested to reason about, that can then be manipulated through formal, mathematical processes. We will rely on common concepts stemming from logic, and we will specifically introduce and define just the ones that are more relevant to this work. We refer the interested reader to [21,22] for a comprehensive exposition of those subjects.

#### 2.2. Formal Languages

A formal language is a mathematical object that describes the syntax of a set of finite *strings* of *symbols*. A formal language is a purely syntactic tool and can be completely defined without making any reference to an interpretation for its symbols. In the following, we provide some basic notions from the field of *formal language theory* (we refer the interested reader to [23] for an more in depth discussion on the subject).

**Definition 1** (Alphabet and Words). An alphabet  $\Sigma$  is any non-empty finite set of symbols. A word over  $\Sigma$  is any finite or infinite string of symbols in  $\Sigma$ . The set of all finite words over  $\Sigma$  is denoted by  $\Sigma^*$  (called the Kleene closure of  $\Sigma$ ).

**Definition 2** (Formal Languages). *Given an alphabet*  $\Sigma$ *, a formal language*  $\mathcal{L}$  *over*  $\Sigma$  *is any set of finite words over*  $\Sigma$ *, i.e.,*  $\mathcal{L} \subseteq \Sigma^*$ .

A formal language  $\mathcal{L}$  is often described by a set of rules that determine how its words are formed (*rules of formation*). Many formalisms can be used to describe the rules of formation of a formal language, such as formal grammars, regular expressions and automata [23].

**Definition 3** (Well-formed Formulas). *Given a formal language*  $\mathcal{L}$  *over*  $\Sigma$ *, a word*  $w \in \Sigma^*$  *is said to be a well-formed formula of*  $\mathcal{L}$ *, often abbreviated with* wff*, iff*  $w \in \mathcal{L}$ *.*

Note that a formal language can be identified with the set of its well-formed formulas. Throughout the rest of this paper, we simply use the term *formula* to refer to a well-formed formula of a given formal language.

Formal languages are entirely syntactic in nature but may be given interpretations that provide meaning to their symbols and sentences. Given a formal language  $\mathcal{L}$ , from the semantic standpoint, the symbols of  $\mathcal{L}$  may be subdivided into logical symbols and non-logical symbols.

**Definition 4** (Logical Symbols). *A symbol of a formal language is said to be a logical symbol if it always has the same meaning, independently from the language interpretation.*

Examples of logical symbols in the context of propositional and first-order logic are logical connectives ( $\neg$ ,  $\land$ ,  $\lor$ , etc.), quantifiers ( $\forall$ ,  $\exists$ , etc.) and the equality predicate (=).

**Definition 5** (Non-logical Symbols and Signature). A symbol of a formal language is said to be a non-logical symbol if it has a meaning only when one is assigned to it by means of a language interpretation. Given a formal language  $\mathcal{L}$ , its signature  $\sigma$  is defined as the set of its non-logical symbols.

Note that non-logical symbols may have different meanings under different language interpretations. Examples of non-logical symbols in the context of propositional and first-order logic are variables and symbols for constants, function and relation.

A fundamental problem in formal language theory is that of determining the membership of a given word in a formal language.

**Definition 6** (Membership Problem). *Given a formal language*  $\mathcal{L}$  *and a word*  $w \in \Sigma^*$ *, the membership problem is the problem to determine whether*  $w \in \mathcal{L}$ *, i.e., whether* w *is a wff of*  $\mathcal{L}$ *.*

As we show later in Section 2.6, each problem in the important computational class of *decision problems* can be represented as a membership problem for a formal language. SAT-based model checking algorithms encode state reachability problems, defined on a model of the system, as instances of a particular decision problem known as Boolean Satisfiability (SAT).

#### 2.3. Logical Systems

A fundamental concept in mathematical logic is that of *logical consequence*, describing the relationship between statements that hold true when one statement, called the *conclusion*, logically follows from one or more other statements, called the *premises*. Historically, the concept of logical consequence has been studied from two different but interrelated perspectives: syntactic and semantic.

Proof theory is the branch of logic that studies logical consequence from the syntactic standpoint. The formalism of *formal systems* is used to model deductions (a *deduction* is a kind of inference that is always valid, i.e., its conclusion is always a logical consequence of its premises) as syntactical transformations (*inference rules*) applied to strings of symbols (*formulas*). In this context, the concept of logical consequence is related to the ability to derive a *proof*, that is, a sequence of syntactic transformations that allow us to derive the conclusion from the premises.

Model theory is the branch of logic that studies logical consequence from the semantic standpoint. Semantics is about associating a meaning with the well-formed formulas of some formal language. Formulas are given a meaning by relating their constituents to elements of the *domain of discourse* by means of an *interpretation*. Given an interpretation of the symbols of a formal language, each formula can be related to the concept of *truth* based on whether or not its meaning holds true in the domain of discourse, i.e., the world we

are interested to reason about. The set of all possible interpretations of a formal language define a *formal semantic* for that language. In this context, the concept of logical consequence is related to whether or not a conclusion would be evaluated as true under all the possible interpretations that evaluate the premises as true.

Even if the syntactic and semantic notions of logical consequence have different definitions, the concepts from the two branches of logic are systematically related. We give the following definitions.

**Definition 7** (Logical System). *Given a formal language*  $\mathcal{L}$ *, a logical system (or logic) for*  $\mathcal{L}$  *is defined as a pair*  $\mathscr{L} \stackrel{def}{=} \langle \mathcal{S}, \mathcal{V} \rangle$ *, consisting of a formal system*  $\mathcal{S}$  *and a formal semantics*  $\mathcal{V}$  *for*  $\mathcal{L}$ *.*

**Definition 8** (Soundness and Completeness). *Given a formal language*  $\mathcal{L}$ , *a logical system*  $\mathscr{L} = \langle \mathcal{S}, \mathcal{V} \rangle$  for  $\mathcal{L}$  is sound iff every formula that can be derived from  $\mathcal{S}$  is valid according to  $\mathcal{V}$ . A logical system  $\mathscr{L}$  is complete iff every formula that is valid according to  $\mathcal{V}$  can be derived from  $\mathcal{S}$ .

Therefore, in a sound and complete logical system the concepts of semantic and syntactic logical consequence coincide. The same is true for the semantic and syntactic versions of validity, consistency, necessity and impossibility.

# 2.4. Propositional Logic

*Propositional logic* (or *Boolean logic*) is a sound and complete logical system concerned with the study of propositions. A *proposition* is an abstract entity bearing a truth value that is expressed as a statement on a domain of discourse. Boolean logic considers (complex) propositions to be composed of *atomic propositions* connected by means of *logical operators*. Atomic propositions are propositions whose structure cannot be further decomposed in terms of logical operators. Later, in Section 2.7, we will use Boolean logic to provide a symbolical representation of hardware-derived state transition systems at the bit level.

# 2.4.1. Syntax of Propositional Logic

From the syntactic standpoint, the language of propositional logic consists of a set of non-logical symbols called *propositional variables* and a set of logical symbols, comprising *logical connectives* ( $\neg$ ,  $\land$  and  $\lor$ ) and *logical constants* ( $\top$  and  $\perp$ ).

**Definition 9** (Syntax of Propositional Formulas). *Given a set of propositional variables AP, the syntax of propositional formulas is defined inductively as follows:*

- $\top$  and  $\perp$  are propositional formulas.

- Each  $a \in AP$  is a propositional formula.

- *Given F, a propositional formula,*  $\neg F$  *is a propositional formula.*

- *Given*  $F_1$  and  $F_2$ , propositional formula  $F_1 \wedge F_2$  is a propositional formula.

- *Given*  $F_1$  and  $F_2$ , propositional formula  $F_1 \lor F_2$  is a propositional formula.

Note that  $\perp$  and  $\vee$  can be omitted from Definition 9 without losing expressiveness as they can be easily derived from  $\top$ ,  $\neg$  and  $\wedge$ . Parentheses "(" and ")" can be used to improve the readability of formulas. We also provide the following definitions about propositional formulas.

**Definition 10** (Atomic Formulas). *An atomic formula is a propositional formula consisting of a propositional variable only.*

**Definition 11** (Support). *Given a propositional formula* F*, we call support of* F*, denoted by* Vars(F), the set of propositional variables occurring in F*. Accordingly, given a set of propositional formulas*  $\Phi$ *, we call support of*  $\Phi$ *, denoted by* Vars( $\Phi$ ), the set of propositional variables occurring in at least one formula of  $\Phi$ :

$$\operatorname{Vars}(\Phi) = \bigcup_{F_i \in \Phi} \operatorname{Vars}(F_i) \tag{1}$$

2.4.2. Semantics of Propositional Logic

Intuitively, from the semantic point of view, propositional variables represent atomic propositions, logical constants represent special propositions that are either always true  $(\top)$  or always false  $(\bot)$  and logical connectives represent standard Boolean functions such as logical negation  $(\neg)$ , logical conjunction  $(\land)$  and logical disjunction  $(\lor)$ .

Each propositional variable is interpreted as an atomic proposition about the domain of discourse which can either be true or false. Such an interpretation is described by means of a *truth assignment* defined as follows.

**Definition 12** (Truth Assignments). *Given a set of propositional variables*  $A \subseteq AP$ , *a truth assignment*  $\mu : A \to \mathbb{B}$  *is a function mapping each propositional variable*  $a \in A$  *to a truth value in*  $\mathbb{B}$ .

Note that, from the model-theoretic perspective, truth assignments can be seen as equivalent representations of structures along with a definition of truth. Since the only non-logical symbols of propositional logic are propositional variables, a structure for the propositional language is an interpretation of those variables as atomic propositions on the domain of discourse. A definition of truth then maps each atomic proposition to a truth value. The composition of the two is equivalent to a truth assignment.

**Definition 13** (Complete or Partial Truth Assignments). *Given a propositional formula* F, *a complete truth assignment for* F *is a function*  $\mu$  :  $Vars(F) \rightarrow \mathbb{B}$  *assigning a truth value to each variable of* F. *A partial truth assignment for* F *is a function*  $\mu : A \subset Vars(F) \rightarrow \mathbb{B}$  *assigning a truth value to each variable of* F.

Each logical connective is given a *truth-functional interpretation*, mapping it to a specific *Boolean function*. Logical connectives are therefore thought as having a certain *arity*, according to the Boolean function they represent: logical conjunction and disjunction are binary connectives whereas negation is a unary connective. Under its truth-functional interpretation, each logical connective of arity *n* corresponds to a Boolean function  $f : \mathbb{B}^n \to \mathbb{B}$  mapping the truth value of its operands to the truth value of its result. The truth-functional interpretation of logical connectives is usually described by means of truth tables. Additional logical connectives, representing other standard Boolean functions such as implication ( $\leftrightarrow$ ), bi-implication ( $\leftrightarrow$ ) and exclusive disjunction ( $\oplus$ ), may be included in the language of propositional logic according to their usual semantics and and syntactic definition, following.

$$F_1 \to F_2 \stackrel{\text{def}}{=} \neg F_1 \lor \neg F_2 \tag{2}$$

$$F_1 \leftrightarrow F_2 \stackrel{\text{def}}{=} (\neg F_1 \land \neg F_2) \lor (F_1 \land F_2) \tag{3}$$

$$F_1 \oplus F_2 \stackrel{\text{def}}{=} (\neg F_1 \land F_2) \lor (F_1 \land \neg F_2) \tag{4}$$

As a way of reducing the number of necessary parentheses, the following precedence order between logical operators is usually applied (from highest precedence to lowest precedence):  $\neg$ ,  $\land$ ,  $\lor$ ,  $\rightarrow$ ,  $\leftrightarrow$  and  $\oplus$ .

Each propositional formula, therefore, unambiguously represents a given Boolean function, which can be determined combining the function associated with its logical connectives according to the precedence order.

**Definition 14** (Semantics of Propositional Logic). *Given a set of propositional variables AP, a propositional formula F over* Vars(F) *and a truth assignment*  $\mu$  *over*  $A \subseteq AP$  *with*  $Vars(F) \subseteq A$ *,*

*we give the following inductive definition of when*  $\mu$  satisfies *F* (*or equivalently, F evaluates to*  $\top$  *under*  $\mu$ )*, denoted as*  $\mu \models F$ :

- $\mu \models \top$  and  $\mu \not\models \bot$ .

- For each  $a \in Vars(F)$ ,  $\mu \models a$  iff  $\mu(a) = \top$ .

- $\mu \models \neg F \text{ iff } \mu \not\models F.$

- $\mu \models F_1 \land F_2$  iff  $\mu \models F_1$  and  $\mu \models F_2$ .

- $\mu \models F_1 \lor F_2$  iff  $\mu \models F_1$  or  $\mu \models F_2$ .

The semantics of other logical connectives can easily be inferred from their truth tables. We provide the following useful definitions:

**Definition 15** ((Propositional) Models). *Given a propositional formula* F, a truth assignment  $\mu$ : Vars $(F) \rightarrow \mathbb{B}$  is a model (or satisfying assignment) of F iff  $\mu \models F$ .

**Definition 16** ((Propositional or Boolean) Satisfiability). A propositional formula *F* is said to be satisfiable iff it has at least one model, i.e., there exists  $\mu$  such that  $\mu \models F$ . Otherwise, *F* is said to be unsatisfiable.

**Definition 17** ((Propositional) Consequence). *Given a set of propositional formulas*  $\Phi$  *and a propositional formula F such that*  $Vars(F) \subseteq Vars(\Phi)$ , *F is said to be a consequence of*  $\Phi$  *iff every model of*  $\Phi$  *can be restricted to a model for F, denoted as*  $\Phi \models F$ .

**Definition 18** ((Propositional) Equivalence). *Given two propositional formulas F and G such* that Vars(F) = Vars(G), *F is said to be equivalent to G iff every model of F is also a model of G* and vice versa, denoted as  $F \equiv G$ .

**Definition 19** ((Propositional) Validity). An argument from a set of propositional formulas  $\Phi$  to a conclusion *F* is valid iff  $\Phi \models F$ .

**Definition 20** ((Propositional) Consistency). *A set of propositional formulas*  $\Phi$  *is consistent iff there is a complete truth assignment*  $\mu$  *that is a model for every formula of*  $\Phi$ .

**Definition 21** (Valid Propositional Formulas). *A propositional formula F is said to be a valid* (or a tautology), denoted as  $\models$  *F*, iff every truth assignment over its variables is a model for it.

**Definition 22** (Strength of Propositional Formulas). *Given two propositional formulas F and G, if*  $F \models G$  *then F is said to be stronger than G and, conversely, G is said to be weaker than F. From the semantics of implication* ( $\rightarrow$ )*, it is clear that, if*  $\models F \rightarrow G$ *, then*  $F \models G$  *and, thus, F is stronger than G.*

We also provide the following remarks about notation for models and truth assignment.

**Notation 1** (Formulas as Set of Models). *Given a propositional formula* F, we denote with Mods(F) the set of all models of F. Any propositional formula F can be seen as a representation of its set of models Mods(F).

Any truth assignment can be represented as a formula satisfied by it or the set of propositional variables it assigns to  $\top$ .

**Notation 2** (Restriction of Models). *Given a propositional formula* F, a truth assignment  $\mu$  :  $A \to \mathbb{B}$ , with  $\operatorname{Vars}(F) \subset A$  can be restricted to a model of F iff its restriction  $\mu|_{\operatorname{Vars}(F)} \models F$ .

**Notation 3** (Truth Assignments as Formulas). *A truth assignment*  $\mu$  *over a set of propositional variables A*  $\in$  *AP can be represented as the following propositional formula:*

$$F_{\mu} \stackrel{\text{def}}{=} \bigwedge_{a_i \in A} l_i \quad \text{where} \quad \begin{cases} l_i = a_i, & \text{iff } \mu(a_i) = \top \\ l_i = \neg a_i, & \text{iff } \mu(a_i) = \bot \end{cases}$$

(5)

**Notation 4** (Truth Assignments as Sets of Propositional Variables). A truth assignment  $\mu$  over a set of propositional variables  $A \in AP$  can be represented by the following set of propositional variables:

$$A_{\mu} \stackrel{\text{def}}{=} \{ a \in A \mid \mu(a) = \top \}$$

$$\tag{6}$$

*Vice versa, a set of propositional variables*  $A \in AP$  *induces a truth assignment*  $\mu_A$  *equal to the characteristic function of* A*, i.e.:*

$$\mu_A(a) = \begin{cases} \top & \text{if } a \in A \\ \bot, & \text{otherwise} \end{cases}$$

(7)

Following Notation 4, the satisfaction relation for propositional logic ( $\models$ ) can be extended to sets of propositional variables:  $A \models \varphi$  if and only if  $\mu_A \models \varphi$ .

2.4.3. Conjunctive Normal Form

We provide the following definitions about propositional formulas.

**Definition 23** (Literals, Clauses and Cubes). *A* literal *is either an atomic formula or the negation of an atomic formula. A clause is a disjunction of literals, whereas a cube is a conjunction of literals.*

**Definition 24** (Conjunctive Normal Form). *A formula F is said to be in Conjunctive Normal Form* (CNF) *if is is a conjunction of clauses.*

For instance, *a*, *b*, *c* and *d* being propositional variables, *a* is an atomic formula, both  $\neg a$  and *b* are literals,  $(\neg a \lor b \lor \neg c)$  is a clause,  $(\neg a \land b \land \neg c)$  is a cube and  $(\neg a \lor b \lor \neg c) \land (\neg b \lor \neg c \lor d)$  is a CNF formula. Given a truth assignment  $\mu$  is easy to see the following:

- A literal *a* is satisfied by  $\mu$  iff  $\mu(a) = \top$ .

- A literal  $\neg a$  is satisfied by  $\mu$  iff  $\mu(a) = \bot$ .

- A clause  $C = l_0 \lor \cdots \lor l_n$  is satisfied by  $\mu$  iff  $\mu \models l_i$  for some  $0 \le i \le n$ .

- A cube  $Q = l_0 \land \cdots \land l_n$  is satisfied by  $\mu$  iff  $\mu \models l_i$  for each  $0 \le i \le n$ .

- A CNF formula  $F = C_0 \land \cdots \land C_n$  is satisfied by  $\mu$  iff  $\mu \models C_i$  for each  $0 \le i \le n$ .

# 2.5. Boolean Functions

In this paper we are interested in verifying the properties of hardware digital systems. Such systems can be thought to be made from large assemblies of logic gates which, in turn, are simple electronic implementations of Boolean functions. As described in Section 2.4, formulas of Propositional Logic can be used to represent Boolean functions and reason about them. In this section, we introduce some basic notions about Boolean functions.

**Definition 25** (Boolean Function). A Boolean function is a function  $f : \mathbb{B}^n \to \mathbb{B}$ , where  $\mathbb{B} = \{\top, \bot\}$  is the Boolean domain and  $n \in \mathbb{N}$  identifies the arity of the function.

**Definition 26** (Functions Monotone in a Variable). Given an *n*-ary Boolean function  $f : \mathbb{B}^n \to \mathbb{B}$  and a value  $k \in \mathbb{N}$ , with  $1 \le k \le n$ , we say that f is monotone in the variable  $x_k$  if  $f|_{x_k=\perp} \to f|_{x_k=\top}$ . Thus, when f is monotone in  $x_k$ , changing the value of  $x_k$  from  $\perp$  to  $\top$  cannot change the value of f from  $\top$  to  $\perp$ . The definition here provided of monotonicity in a given variable is also known as unateness or positive monotonicity in that variable.

**Definition 27** (Monotone Functions). *A Boolean function* f *is monotone if it is monotone in each of its variables. Thus, changing the value of any of its variables from*  $\bot$  *to*  $\top$  *cannot change the value of f from*  $\top$  *to*  $\bot$ .

#### 2.6. Decision Problems

In Section 2.1, we have presented logic as a tool to formalize and reason about a world of interest, whereas in Section 2.5 we have provided some background knowledge about commonly used models for representing combinational and sequential hardware circuits. Our aim is to use the tool of logic, and in particular Propositional Logic, to provide a formal representation of hardware sequential systems and reason about some of their properties. In particular, we are interested in asking certain questions about the formalized systems and having those questions answered by algorithmic procedures. We are, thus, interested in solving some computational problems arising from those questions, which typically belong to the class of *decision problems*.

In this section we provide an overview of decision problems and their properties and we present Boolean Satisfiability (SAT), a fundamental decision problem in computer science of particular interest in the context of this paper.

**Definition 28** (Decision Problems and Instances). A decision problem  $\mathcal{P}$  is any arbitrary question admitting a YES or NO answer over an infinite set of inputs. An instance of a decision problem  $\mathcal{P}$  is a particular input for  $\mathcal{P}$ . We distinguish between YES-instances, instances for which  $\mathcal{P}$  gives a YES answer, and NO-instances, instances for which  $\mathcal{P}$  gives a NO answer.

Traditionally, a decision problem is identified by its set of YES-instances. Instances of a decision problem are usually encoded as strings over an alphabet  $\Sigma$ . As a consequence, a decision problem  $\mathcal{P}$  is often defined as a *formal language*  $\mathcal{L}(\mathcal{P})$  over that alphabet and can be formulated as an instance of the *membership problem* for  $\mathcal{L}(\mathcal{P})$ .

**Theorem 1** (Decision Problems as Membership Problems). *Given a decision problem*  $\mathcal{P}$ , *determining whether the answer to a given instance is* YES *is equivalent to determining whether an encoding*  $w \in \Sigma^*$  *of that instance over an alphabet*  $\Sigma$  *is in the corresponding language*  $\mathcal{L}(\mathcal{P})$ .

In order to solve a decision problem  $\mathcal{P}$ , we are interested in algorithms that terminate with a correct answer for every input of  $\mathcal{P}$ , as formalized by the following definitions.

**Definition 29** (Soundness and Completeness of an Algorithm). An algorithm for a given decision problem  $\mathcal{P}$  is sound iff when it returns a YES answer the input is a YES-instance of  $\mathcal{P}$ . An algorithm for a given decision problem  $\mathcal{P}$  is complete iff it always terminates and it returns a YES answer when the input is a YES-instance of  $\mathcal{P}$ .

Unsound algorithms are rarely of practical interest. Incomplete algorithms may be effective in solving only YES- or NO-instances of a decision problem. Ideally, however, we would like to have an algorithm for a decision problem  $\mathcal{P}$  that is both sound and complete.

**Definition 30** (Decision Procedure). *A decision procedure is an algorithmic procedure that, given an instance of a decision problem* P*, always terminates with a correct* YES or NO *answer.*

**Definition 31** (Decidability of a Decision Problem). *A decision problem for which there exists a decision procedure is said to be decidable.*

Decidability is an important property to determine whether a given problem may be tackled algorithmically. Many important problems are undecidable, such as the so-called *Entscheidungsproblem* asking for the validity of a first-order formula in the general case (proved undecidable by Church and Turing).

Sometimes, decision procedures are also asked to produce certificates as a way to prove that the results of their computation are correct.

**Definition 32** (Certificates). A certificate is a string of symbols that can be used to prove the answer of a decision procedure on a given instance. We distinguish YES-certificates, produced by the algorithm to certify a YES answer, and NO-certificates, produced by the algorithm to certify a NO answer.

The typical decision problems we are interested in concern the satisfiability or validity of formulas in some logical system  $\mathscr{L}$ . Those two problems are interchangeable, as deciding the satisfiability of a formula  $\varphi$  can be seen as the negation of the decision problem to determine whether the formula  $\neg \varphi$  is valid. Focusing on the validity problem, we can formulate such a problem as the membership problem of a formula  $\varphi$  to the language of logically valid formulas of  $\mathscr{L}$  (or the language theorems, supposing  $\mathscr{L}$  to be sound and complete).

In what follows, we assume  $\mathscr{L}$  to be both sound and complete. This is because we are mainly interested in decision problems over propositional logics, which are both sound and complete under the usual semantics and proof systems. Considering logical systems that are both sound and complete, we equate the problem of validity (checking whether a formula is a tautology in  $\mathscr{L}$ ) to the problem of derivability (checking whether the formula is a theorem in  $\mathscr{L}$ ).

*Propositional (or Boolean) Satisfiability* (SAT) is the problem to decide whether a given propositional formula is satisfiable, as defined in Definition 16.

**Definition 33** (Boolean Satisfiability Problem). *Given a propositional formula*  $\varphi$  *over the propositional variables* V, *SAT is the problem to determine whether*  $\exists \mu(V) : \mu \models \varphi$ . *If that is the case, the formula*  $\varphi$  *is a* YES-*instance of the problem and is said to be satisfiable* (SAT). *The model*  $\mu$  *is a* YES-*certificate for the problem on*  $\varphi$ . *Otherwise, the formula*  $\varphi$  *is a* NO-*instance of the problem and is said to be unsatisfiable* (UNSAT).

SAT is a fundamental decision problem in computer science, important from both the theoretical and the practical perspective. From the theoretical standpoint, SAT plays a central role in computational complexity theory. From the practical standpoint, SAT can be used as a modeling framework to encode many computationally hard problems.

SAT is known to be a computationally hard problem: it is, in fact, a member of the NP-complete class of complexity [24]. This briefly means that no algorithm is currently known that is able to solve all instances of SAT in a polynomial amount of time. Despite this theoretical limitation, the SAT problem is considered in many cases to be tractable, thanks to the fact that its instances often present some kind of structure arising from the application domain they originate from. Currently, state-of-the-art SAT solvers are able to handle SAT instances up to millions of variables and constraints.

**Definition 34** (SAT-Solving Algorithm). *A SAT-solving algorithm is a decision procedure to answer the SAT problem.*

A *SAT solver* is software that runs a SAT-solving algorithm, taking a propositional formula (usually in CNF) as input and determining whether or not such a formula can be satisfied by a truth assignment of its variables. SAT-solving algorithms are usually designed as search procedures over the space of truth assignments, following the highly influential DPLL [25] algorithm. To give a better understanding of the subject at hand, Algorithm 1 highlights the top-level procedure of DPLL; a brief description follows as well as a partial example of the assignment's space exploration.

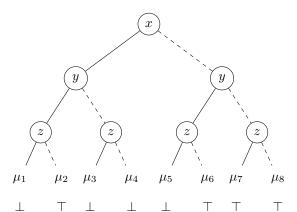

Figure 1 depicts a search tree enumerating all the truth assignments, one for each leaf node, over three variables, taking into account  $CNF = \{\{\neg x, y\}, \{\neg y, \neg z\}\}$  as a target formula. Given the visual representation, it is easy to see how looking for a satisfying

assignment is equal to looking for a path, and hence a leaf node, that satisfies a given CNF. Furthermore, taking into account the tree topology and the leaf values, it is possible to identify simplifying steps that reduce the search space, e.g., neither  $\mu_3$  nor  $\mu_4$  can lead to satisfying assignments; thus, it is irrelevant to evaluate the role of variable *z* given a partial assignment that reaches such a branch.

**Figure 1.** Search tree enumerating all possible assignments for three variables *x*, *y* and *z* with respect to  $CNF = \{\{\neg x, y\}, \{\neg y, \neg z\}\}$ . Solid (dashed) edges correspond to *true* (*false*) assignments.

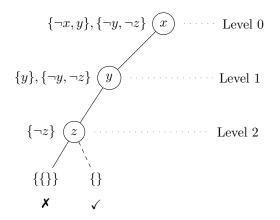

In order to evaluate the amount of work that the DPLL algorithm has to perform, a common notion used is that of the *termination tree*, which evaluates the actual search tree considered during exploration. Figure 2 depicts a partial termination tree taking into account the same example introduced in Figure 1. Within a termination tree, one can find conflicts (X) and valid ( $\checkmark$ ) assignments, as well as a trace for the conditioned CNF at each level of the search space.

**Figure 2.** Partial termination tree associated with the example of Figure 1 where each node is labeled with the corresponding CNF. Crosses denote contradiction within a given path whereas check marks denote admissible assignments.

Most modern state-of-the-art SAT solvers employs a SAT-solving algorithm called *Conflict-Driven Clause Learning* (CDCL) [26]. CDCL is based on *clause learning* and *non-chronological backtracking* in order to avoid repeated exploration of regions of the search space that do not lead to a satisfying assignment. During search, CDCL algorithms maintain a *trail* of literals representing the current partial assignment. Under a given partial assignment, each clause loaded in the solver can be either *satisfied, conflicts, units* or *unresolved*. Clauses are satisfied if at least one of their literals is satisfied. If each literal in a clause is falsified, then the whole clause is a conflict. If all but one literals of the clause are falsified, then the clause is a unit. Otherwise the clause is unresolved. If a clause is a unit, its only non-falsified

literal is implied by the current partial assignment; thus, its variable can be assigned so that the literal is satisfied.

| Algorithm 1 Top-level procedure of the DPLL algorithm.                              |                                                             |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| <b>Input:</b> <i>C</i> a set of clauses.<br><b>Output:</b> $res \in {SAT, UNSAT}$ . |                                                             |  |

|                                                                                     |                                                             |  |

| 2:                                                                                  | while $\exists$ unit clause $l \in C$ do                    |  |

| 3:                                                                                  | $C \leftarrow \text{UNITPROPAGATE}(C, l)$                   |  |

| 4:                                                                                  | while $\exists$ pure literal $l \in C$ do                   |  |

| 5:                                                                                  | $C \leftarrow PureLiteralAssign(C, l)$                      |  |

| 6:                                                                                  | if $C = \emptyset$ then                                     |  |

| 7:                                                                                  | return SAT                                                  |  |

| 8:                                                                                  | if empty clause $\in C$ then                                |  |

| 9:                                                                                  | return UNSAT                                                |  |

| 10:                                                                                 | $l \leftarrow \text{CHOOSELITERAL}(C)$                      |  |

| 11:                                                                                 | <b>return</b> DPLL( $C \cup l$ ) or DPLL( $C \cup \neg l$ ) |  |

The search starts by selecting a variable, using some suitable heuristic, and assigning it a truth value. This process is called *decision*. After a decision has been made, some of the clauses loaded in the solver may have become conflicts or unit clauses. The solver looks up for unit clauses using efficient data structures, called *watch lists*, in order to perform *Boolean* Constraint Propagation (BCP). During BCP, the solver finds and assigns every clause that is a unit under the current partial assignment. Such a procedure iterates until either no more unit clauses can be found or the solver has found a conflict. In the first case, the solver proceeds with the next decision. In the second case, the solver analyzes the sequence of assignments that have led to the conflict, a process called *conflict analysis* [26]. The result of such an analysis is a *learned clause* catching the causes of the conflict. Such a clause is added to the current formula in order to avoid future iterations to enter the region of the search space that led to the conflict (learning). The algorithm, thus, performs non-chronological backtracking canceling enough of its latest decisions (even all of them) to leave such a region of space and then resume search on another region. Eventually, either a conflict is found when no decisions have been made, meaning that the problem at hand is UNSAT, or every variable has been assigned without incurring a conflict, meaning that the problem at hand is SAT.

State-of-the-art SAT solvers are sophisticated artifacts of engineering that often include various techniques and heuristics to enhance their performance. Among such techniques, there are those to periodically *restart search* in order to better explore the space [27], simplifying the problem at hand either before starting searching for a solution or during search [28] and periodically trimming the database of learned clauses.

In many applications, SAT solvers are required to answer a sequence of related calls. In order to preserve useful information about the problem at hand, maintained in the state of the solver, many SAT solvers expose an *incremental interface*. Incremental interfaces enable the user to load a formula in the solver, solve the corresponding SAT problem, then modify the formula and solve the related SAT problem without losing inferences or other useful information about the problem stored in the state. Between incremental calls, the formula can usually be modified by either specifying *variable assumptions* or *adding or removing clauses*.

Many modern SAT solvers can be instructed to provide a *refutation proof* in the case a problem is declared to be UNSAT. Such a proof can be thought of as a NO-certificate that can be used by an independent checker to assess the correctness of the SAT solver's answer. Refutation proofs are usually produced as either *resolution proofs* [29] or *clausal proofs* [30]. A resolution proof is a series of applications of the *resolution rule* that derives the empty clause from the clauses of an unsatisfiable propositional formula.

**Definition 35** (Binary Resolution Rule). *Given two clauses*  $C_1$  *and*  $C_2$ , *the (binary) resolution rule is the inference rule:*

$$\frac{(C_1 \lor a) \land (\neg a \lor C_2)}{(C_1 \lor C_2)} \tag{8}$$

Modern SAT solvers are capable, without incurring too large an additional cost, to generate a resolution proof from unsatisfiable runs [31]. Clausal proofs can be seen as logs of the sequence of clauses learned by the solver in the order in which they were learned. A resolution proof can be constructed starting from a clausal proof using BCP [32]. Another common feature of modern SAT solvers is the extraction of *unsatisfiability cores*. Given an UNSAT problem, an unsatisfiability core is a subset of the clauses of the original problem that is still unsatisfiable. The set of clauses in a resolution proof can be seen as an unsatisfiability core.

# 2.7. Model Checking

Model checking is an automated formal verification technique for determining whether a design meets a given specification. The behavior of the design is usually modeled using a *transition system*. The specification usually consists of a *property* (or a set of properties) expressed in a temporal logic.

Transition systems and temporal logics are discussed in detail in Sections 2.8 and 2.9, respectively. Section 2.10 formalizes the model checking problem as well as a particular subclass of that problem, called invariant verification. In Section 2.11, a way to symbolically represent transition systems is presented, whereas in Section 2.12 the invariant verification problem is reduced to a reachability problem on such a symbolic representation. These concepts form the foundation for the discussion in the remaining sections of this paper, which will each focus on specific model checking algorithms and techniques.

#### 2.8. Transition Systems

Transition systems are often used in computer science as models to describe the behavior of real-world systems. They can be seen as directed graphs, with nodes representing *states* and edges representing *transitions*. A state describes some unique configuration of information about a given system at a certain moment of its behavior. Transitions specify how the system can evolve from one state to another.

**Definition 36** (Transition System). A transition system (also known in the literature as a Kripke structure [33]) is a tuple  $\mathcal{TS} \stackrel{\text{def}}{=} \langle S, S_0, R, AP, L \rangle$ , where S is the set of states,  $S_0 \subseteq S$  is the set of initial states,  $R \subseteq S \times S$  is the transition relation, AP is a set of propositional variables representing atomic propositions and  $L: S \to 2^{AP}$  is a labeling function.

For each state  $s \in S$ , the labeling function L(s) denotes the set of atomic propositions that hold in s. A transition system can be either *finite* or *infinite*, depending on whether or not it admits an infinite set of states (and consequently transitions). In this paper, we are interested in the model checking of bit-level hardware sequential circuits. Since the behavior of such systems can be modeled using finite transition systems, we restrict the discussion to those models. For this reason, we hereinafter use the term *transition system* as a shorthand for *finite transition systems* without risk of ambiguity.

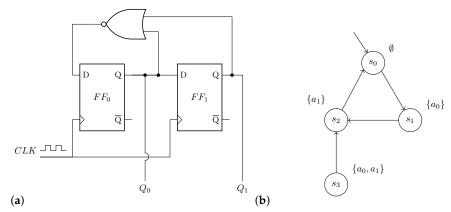

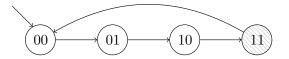

**Example 1.** The sequential hardware system described in Figure 3a, representing a 2-bit synchronous counter that counts up to 2, can be modeled as the following transition system:

$$\mathcal{TS} = \langle S, S_0, R, AP, L \rangle \tag{9}$$

$$S = \{s_0, s_1, s_2, s_3\}$$

(10)

$$S_0 = \{s_0\}\tag{11}$$

$$R = \{(s_0, s_1), (s_1, s_2), (s_1, s_0), (s_3, s_2)\}$$

(12)

$$AP = \{a_0, a_1\}$$

(13)

$$L = \{(s_0, \emptyset), (s_1, \{a_0\}), (s_2, \{a_1\}), (s_3, \{a_0, a_1\})\}$$

(14)

States  $S = \{s_0, s_1, s_2, s_3\}$  represent the four possible states of the counter, corresponding to the combined digital values of the two flip flops;  $s_0$  represent the reset state of the system, in which the output of both flip flops is low, R indicates how the system will transition between states at each clock cycle and the labeling function L maps each state to a set of atomic propositions in  $AP = \{a_0, a_1\}$  each indicating that either  $Q_0$  or  $Q_1$  is high, respectively. The transition system is visualized in Figure 3b. We will use this system and its model as a running example in the rest of the section.

**Figure 3.** (**a**) A simple sequential hardware design implementing a 2-bit counter from 0 to 2 using D-type flip flops. (**b**) The model of the counter as a transition system.

Let  $TS = \langle S, S_0, R, AP, L \rangle$  be a transition system; we provide the following useful definitions.

**Definition 37** (Transition). A transition in TS is a pair of states  $(s_1, s_2)$  such that  $(s_1, s_2) \in R$ .

**Definition 38** (Successor and Predecessor States). *Given a pair of states* (p, s), p *is said to be a predecessor of s iff* (p, s) *is a transition in* TS. *Vice versa, s is said to be a successor of p.*

**Definition 39** (Paths). A path in TS is any sequence of states  $\pi = (s_0, s_1, ...)$  of arbitrary (even infinite) length  $|\pi|$  such that  $(s_i, s_{i+1})$  is a transition in TS for each  $0 \le i < |\pi|$ . A path  $\pi$  is said to be finite if  $|\pi| \in \mathbb{N}$ ; otherwise, it is said to be infinite. We denote by  $\pi_i = (s_i, s_{i+1}, ...)$  the suffix of  $\pi$  starting with the (i + 1)-th state of  $\pi$ . We also denote by  $\pi_i$  the (i + 1)-th state in  $\pi$ .

**Definition 40** (Initial Paths). An initial path in TS is any path  $\pi = (s_0, s_1, ...)$  such that  $s_0 \in S_0$ .

**Definition 41** (Exact and Bounded Reachability). A state  $s \in S$  is reachable in exactly k steps in TS iff a finite initial path  $\pi = (s_0, \ldots, s_{k+1})$  of length k + 1 such that  $s_{k+1} = s$  exists. A state  $s \in S$  is reachable within k steps (or reachable bounded by k) in TS iff there is  $i \leq k$  such that s is reachable in exactly i steps in TS.

**Definition 42** (Reachability). A state  $s \in S$  is reachable in TS if it is reachable within an arbitrary (finite) number of steps in TS.

**Definition 43** (Sets of Exactly Reachable and Sets of Bounded Reachable States). We denote with  $\mathcal{R}_i^E(\mathcal{TS})$  the set of states reachable in exactly *i* steps in  $\mathcal{TS}$ . We denote with  $\mathcal{R}_i(\mathcal{TS})$  the set of states reachable within *i* steps in  $\mathcal{TS}$ , *i.e.*,

$$\mathcal{R}_{i}(\mathcal{TS}) \stackrel{def}{=} \bigcup_{0 \le j < i} \mathcal{R}_{j}^{E}(\mathcal{TS})$$

(15)

**Definition 44** (Reachability Diameter). *We define the reachability diameter of* TS *to be the minimal number*  $d \in \mathbb{N}$  *of steps required for reaching all reachable states in* TS*:*

$$d \stackrel{\text{def}}{=} \arg\min_{i \in \mathbb{N}} \{i \mid \mathcal{R}_i(\mathcal{TS}) = \mathcal{R}_{i+1}(\mathcal{TS})\}$$

(16)

**Definition 45** (Set of Reachable States). We denote with  $\mathcal{R}(\mathcal{TS})$  the set of states reachable in  $\mathcal{TS}$

$$\mathcal{R}(\mathcal{TS}) \stackrel{\text{def}}{=} \bigcup_{0 \le j < d} \mathcal{R}_j(\mathcal{TS})$$

(17)

where *d* is the reachability diameter of TS.

When considering reachability, we use the term *timeframe i*, to denote what happens after *i* transitions from the initial states. It is trivial to prove that, for a finite-state transition system, there always exists a (finite) reachability diameter.

**Example 2.** Given the hardware design and its transition system described in Example 1,  $\pi = (s_0, s_1, s_2)$  is both a path and an initial path, the set of reachable states is  $\mathcal{R}(\mathcal{TS}) = \{s_0, s_1, s_2\}$  and the reachability diameter of the system is d = 2.

# 2.9. Temporal Logics

Temporal logics are extensions of classical logics that are used to represent, and reason about, statements qualified in terms of *time*. Both propositional and predicate logic can be extended to include temporal modalities. In this dissertation, we are only interested in *Propositional Temporal Logics* (PTLs), i.e., temporal logics obtained augmenting propositional logic with *temporal operators*. This is because they are the logics typically used to express the requirements for bit-level sequential circuits. Hereinafter, when referring to those logics, we will omit the prefix "propositional" for conciseness.

Different temporal logics, with different expressiveness, can be defined based on the temporal operators they use. The two temporal logics used the most in practice are *Linear Temporal Logic* (LTL) and *Computation Tree Logic* (CTL). LTL adopts a *linear-time* perspective, in which every moment in time is followed by a single successor moment. A possible behavior in LTL can, therefore, be seen as an infinite, ordered sequence of moments. CTL, instead, adopts a *branching-time* perspective, in which every moment in time representing different courses of execution. A possible behavior in CTL can, therefore, be seen as an infinite, directed tree of moments. Neither of these logics is a subset of the other, as many temporal properties can be expressed only using one of either LTL or CTL.

The model-theoretic semantics usually given to temporal logics is defined in terms of paths and states of transition systems.

#### 2.9.1. Linear Temporal Logic

Linear Temporal Logic (LTL) was introduced by Pnueli [34] for the specification and verification of reactive systems. Formulas of LTL are constructed from a set of *propositional variables AP* using the usual *logical connectives* (negation  $\neg$ , conjunction  $\land$  and disjunction  $\lor$ ) and some *temporal operators* **X** ("next time"), **F** ("eventually"), **G** ("always") and **U** ("until").

LTL formulas are interpreted in terms of paths, i.e., sequences of states of a transition system. Their semantics is also extended to states and whole transition systems.

**Definition 46** (Syntax of LTL Formulas). *Given a set of propositional variables AP, the syntax of LTL formulas is defined inductively as follows.*

- Boolean constants  $\top$  and  $\perp$  are LTL formulas.

- *Each*  $a \in AP$  *is an* LTL *formula.*

- Given  $\psi$ , an LTL formula  $\neg \psi$  is an LTL formula.

- Given  $\psi_1$  and  $\psi_2$ , LTL formula  $\psi_1 \wedge \psi_2$  is an LTL formula.

- Given  $\psi_1$  and  $\psi_2$ , LTL formula  $\psi_1 \lor \psi_2$  is an LTL formula.

- *Given*  $\psi$ *, an LTL formula*  $\mathbf{X}\psi$  *is an LTL formula.*

- Given  $\psi$ , an LTL formula  $\mathbf{F}\psi$  is an LTL formula.

- Given  $\psi$ , an LTL formula  $\mathbf{G}\psi$  is an LTL formula.

- Given  $\psi_1$  and  $\psi_2$ , LTL formula  $\psi_1 \mathbf{U} \psi_2$  is an LTL formula.

Note that  $\perp$  and  $\vee$  can be omitted from Definition 46 without losing expressiveness as they can be easily derived from  $\top$ ,  $\neg$  and  $\wedge$ . Similarly, **F** and **G** can also be omitted, as they can be derived from **X** and **U** as  $\mathbf{F}\psi \stackrel{\text{def}}{=} \top \mathbf{U}\psi$  and  $\mathbf{G}\psi \stackrel{\text{def}}{=} \neg \mathbf{F}\neg\psi$ . Furthermore, the syntax can be extended to other common Boolean operators by means of their usual definitions in Propositional Logic.

**Example 3.** Given the hardware design and its transition system described in Example 1, we can model the specification describing how the system will never reach a state in which the output of both flip flops is high as the following property in LTL logic:

$$\psi = \neg \mathbf{F}(a_0 \wedge a_1) \tag{18}$$

Intuitively, the semantics of the temporal operators of LTL is the following:  $X\psi$  holds at the current moment if  $\psi$  holds at the next moment;  $F\psi$  holds at the current moment if there is a future moment at which  $\psi$  holds;  $G\psi$  holds at the current moment if  $\psi$  holds at the current moment at the current moment if  $\psi$  holds at the current moment at which  $\psi_2$  holds and  $\psi_1$  holds at the current moment until that future moment. Formally, the semantics of LTL formulas is defined with respect to paths, states and transition systems, as follows.

Definition 47 (Semantics of LTL Formulas with Respect to Paths). Given a transition system

$\mathcal{TS} \stackrel{def}{=} \langle S, S_0, R, AP, L \rangle$ , let  $\pi = (s_0, s_1, ...)$  be an infinite path in  $\mathcal{TS}$  and let  $\psi$  be an LTL formula over AP. We give the following inductive definition of when  $\pi$  satisfies  $\psi$ , denoted as  $\pi \models \psi$ :

- $\pi \models \top$  and  $\pi \not\models \bot$ .

- For each  $p \in AP$ ,  $\pi \models p$  iff  $p \in L(\pi[0])$ .

- $\pi \models \neg \psi_1 \text{ iff } \pi \not\models \psi_1.$

- $\pi \models \psi_1 \land \psi_2$  iff  $\pi \models \psi_1$  and  $\pi \models \psi_2$ .

- $\pi \models \psi_1 \lor \psi_2$  iff  $\pi \models \psi_1$  or  $\pi \models \psi_2$ .

- $\pi \models \mathbf{X}\psi_1 \text{ iff } \pi_1 \models \psi_1.$

- $\pi \models \mathbf{F}\psi_1 \text{ iff } \pi_i \models \psi_1 \text{ for some } i \ge 0.$

- $\pi \models \mathbf{G}\psi_1 \text{ iff } \pi_i \models \psi_1 \text{ for every } i \ge 0.$

- $\pi \models \psi_1 \mathbf{U} \psi_2$  iff  $\pi_i \models \psi_2$  for some  $i \ge 0$  and  $\pi_i \models \psi_1$  for every  $0 \le j < i$ .

Other common Boolean operators have semantics that can easily be inferred from the semantics of  $\neg_r \land \text{ or } \lor$ .

**Definition 48** (Semantics of LTL Formulas with Respect to States). *Given a transition system*  $\mathcal{TS} \stackrel{\text{def}}{=} \langle S, S_0, R, AP, L \rangle$ , let  $s \in S$  be a state and let  $\psi$  be an LTL formula over AP. We say that s satisfies  $\psi$ , denoted as  $s \models \psi$ , iff  $\pi \models \psi$  for each infinite path  $\pi = (s_0, s_1, ...)$  with  $s_0 = s$ .

**Definition 49** (Semantics of LTL Formulas with Respect to Transition Systems). *Given a transition system*  $\mathcal{TS} \stackrel{def}{=} \langle S, S_0, R, AP, L \rangle$ , *let*  $\psi$  *be an LTL formula over AP. We say that*  $\mathcal{TS}$  *satisfies*  $\psi$ , *denoted as*  $\mathcal{TS} \models \psi$ , *iff*  $s_0 \models \psi$  *for each*  $s_0 \in S_0$ .

The interpretation of an LTL formula  $\psi$  in terms of a state *s* requires that all the computations starting from *s* satisfy  $\psi$ , in order for *s* to satisfy  $\psi$ . In LTL semantics, therefore, there is an implicit universal quantification over all computations when determining whether a state satisfies a formula. Thus, LTL can be used to express properties holding for every path from a state but it cannot express properties holding only for some of such paths.

#### 2.9.2. Computation Tree Logic

Computation Tree Logic (CTL) was introduced by Clarke et al. [35] to overcome the semantics limitation of LTL. In CTL, two kinds of formulas are distinguished: *state formulas* and *path formulas*. CTL also introduces two new temporal operators, called *path quantifiers* to allow the specification of properties for some or all the paths starting from a state. These quantifiers are **A** ("for all paths") and **E** ("there exists a path"). CTL formulas are interpreted in terms of trees of paths, i.e., possible alternative paths of a transition system. Their semantics is also extended to states and whole transition systems.

**Definition 50** (Syntax of CTL Formulas). *Given a set of propositional variables AP, the syntax of CTL state formulas is defined inductively as follows.*

- Boolean constants  $\top$  and  $\perp$  are CTL state formulas.

- *Each*  $a \in AP$  *is a* CTL *state formula.*

- Given  $\psi$ , a CTL state formula  $\neg \psi$  is a CTL state formula.

- Given  $\psi_1$  and  $\psi_2$ , CTL state formula  $\psi_1 \wedge \psi_2$  is a CTL state formula.

- *Given*  $\psi_1$  *and*  $\psi_2$ *,* CTL *state formula*  $\psi_1 \lor \psi_2$  *is a* CTL *state formula.*

- *Given*  $\varphi$ *, a CTL path formula*  $\mathbf{A}\varphi$  *is a CTL state formula.*

- Given  $\varphi$ , a CTL path formula  $\mathbf{E}\varphi$  is a CTL state formula.

The syntax of CTL path formulas is defined inductively as follows:

- Given  $\psi$ , a CTL state formula  $\mathbf{X}\psi$  is a CTL path formula.

- *Given*  $\psi$ *, a CTL state formula* **F** $\psi$  *is a CTL path formula.*

- Given  $\psi$ , a CTL state formula  $\mathbf{G}\psi$  is a CTL path formula.

- Given  $\psi_1$  and  $\psi_2$ , CTL state formula  $\psi_1 \mathbf{U} \psi_2$  is a CTL path formula.

Note that Definition 50 can be restricted to exclude  $\top$ ,  $\lor$ , **F** and **G**, without losing expressiveness in the same way as Definition 46. Syntax can also be expanded to other common Boolean operators as usual.

**Example 4.** Given the hardware design and its transition system described in Example 1, we can model the specification describing how the system will never reach a state in which the output of both flip flops is high as the following property in CTL logic:

$$\psi = \neg \mathbf{EF}(a_0 \wedge a_1) \tag{19}$$

Intuitively, state formulas describe properties of states, whereas path formulas describe properties of (infinite) paths. Path formulas can be transformed into state formulas by prefixing them with a path quantifier. Note that path quantifiers must immediately precede temporal operators in order for the resulting state formula to be well formed. Intuitively, the semantics of path quantifiers is the following:  $\mathbf{A}\varphi$  holds at the current state if  $\varphi$  holds

for all paths starting at the current state;  $\mathbf{E}\varphi$  holds at the current state if  $\varphi$  holds for some paths starting at the current state. Formally, the semantics of CTL formulas is defined with respect to paths, states and transition systems, by means of two satisfaction relations: one for state formulas and the other for path formulas.

**Definition 51** (Semantics of CTL Path Formulas with Respect to Paths). *Given a transition* system  $\mathcal{TS} \stackrel{def}{=} \langle S, S_0, R, AP, L \rangle$ , let  $\pi = (s_0, s_1, ...)$  be an infinite path in  $\mathcal{TS}$  and let  $\varphi$  be a CTL path formula over AP. We give the following inductive definition of when  $\pi$  satisfies  $\varphi$ , denoted as  $\pi \models \varphi$ :

- $\pi \models \mathbf{X}\psi$  iff  $\pi[1] \models \psi$ .

- $\pi \models \mathbf{F}\psi$  iff  $\pi[i] \models \psi$  for some  $i \ge 0$ .

- $\pi \models \mathbf{G}\psi$  iff  $\pi[i] \models \psi$  for every  $i \ge 0$ .

- $\pi \models \psi_1 \mathbf{U} \psi_2$  *iff*  $\pi[i] \models \psi_2$  *for some*  $i \ge 0$  *and*  $\pi[j] \models \psi_1$  *for every*  $0 \le j < i$ .

**Definition 52** (Semantics of CTL State Formulas with Respect to States). *Given a transition* system  $TS \stackrel{def}{=} \langle S, S_0, R, AP, L \rangle$ , let  $s \in S$  be a state and let  $\psi$  be a CTL state formula over AP. We give the following inductive definition of when s satisfies  $\psi$ , denoted as  $s \models \psi$ :

- $s \models \top$  and  $s \not\models \bot$ .

- For each  $p \in AP$ ,  $s \models p$  iff  $p \in L(s)$ .

- $s \models \neg \psi_1 \text{ iff } s \not\models \psi_1.$

- $s \models \psi_1 \land \psi_2 \text{ iff } s \models \psi_1 \text{ and } s \models \psi_2.$

- $s \models \psi_1 \lor \psi_2$  iff  $s \models \psi_1$  or  $s \models \psi_2$ .

- $s \models \mathbf{E}\varphi_1$  iff  $\pi \models \psi$  for some infinite initial path  $\pi$  starting in s.

- $s \models \mathbf{A}\varphi_1$  iff  $\pi \models \psi$  for each infinite initial path  $\pi$  starting in s.

**Definition 53** (Semantics of CTL State Formulas with Respect to Transition Systems). *Given* a transition system  $\mathcal{TS} \stackrel{def}{=} \langle S, S_0, R, AP, L \rangle$ , let  $s \in S$  be a state and let  $\psi$  be a CTL state formula over AP. We say that  $\mathcal{TS}$  satisfies  $\psi$ , denoted as  $\mathcal{TS} \models \psi$ , iff  $s_0 \models \psi$  for each  $s_0 \in S_0$ .

# 2.9.3. Temporal Properties

**Definition 54** (Temporal Properties). *Given a transition system* TS*, a temporal property is any property*  $\psi$ *, expressed in a temporal logic, that specifies the admissible (or desired) behaviors of* TS*.*

Temporal properties typically fall under one of two main categories: safety properties and liveness properties, defined informally as follows.

**Definition 55** (Safety Properties). *Given a transition system* TS*, a safety property asserts that some (undesired) conditions never happen for* TS ("nothing bad ever happens").

**Definition 56** (Liveness Properties). *Given a transition system* TS*, a liveness property asserts that some (desired) conditions will eventually happen for* TS (*"something good eventually happens"*).

Typical examples of safety properties include deadlock freedom and mutual exclusion, whereas a typical example of a liveness property is starvation freedom. Both safety and liveness properties can be expressed using LTL and CTL. The main difference between the two categories of properties is that safety properties can be violated by finite computations of a system, whereas liveness properties can only be violated by infinite computations of a system. In practical applications, safety properties are prevalent. The temporal properties defined in Examples 3 and 4 are safety properties.

We distinguish a kind of safety properties of particular interest, called *invariant properties*, defined as follows:

**Definition 57** (Invariant Properties). *Given a transition system* TS, an invariant property asserts that the condition described by a given propositional formula  $\varphi$  over AP, called an invariant condition, always happen for TS ("some invariant condition  $\varphi$  always happens").

Invariant properties can be described in LTL as formulas  $\mathbf{G}\varphi$  with the invariant condition  $\varphi$  a formula over *AP*. Similarly, invariant properties in CTL take the form  $\mathbf{AG}\varphi$  with the invariant condition  $\varphi$  a formula over *AP*.

**Example 5.** *The corresponding invariant properties of the safety properties defined in Examples 3 and 4 are as follows:*

$$\psi = \mathbf{G}(\neg a_0 \lor \neg a_1) \tag{20}$$

$$\psi = \mathbf{AG}(\neg a_0 \lor \neg a_1) \tag{21}$$

in LTL and CTL, respectively.

Properties management [36,37] goes beyond the scope of this paper, but it is still a topic as relevant as the proper choice of the actual model checking algorithm to be used given a specific scenario.

#### 2.10. Model Checking Problem

Let  $TS = \langle S, S_0, R, AP, L \rangle$  be a transition system; the model checking problem can be formalized as follows:

**Definition 58** (Model Checking Problem). *Given a transition system* TS *and a temporal property*  $\psi$  *over* AP*, the decision problem to check whether*  $TS \models \psi$  *is called a model checking problem. In the case*  $TS \not\models \psi$ *, the model checking procedure is required to provide a counterexample.*

**Definition 59** (Counterexample). *Given a transition system* TS *and a temporal property*  $\psi$  *over* AP *such that*  $TS \not\models \psi$ *, a counterexample to*  $\psi$  *for* TS *is any initial path*  $\pi$  *of* TS *such that*  $\pi \not\models \psi$ .

Model checking is therefore a decision problem, as defined in Section 2.6, that admits a YES-answer ( $\psi$  holds for TS) or a NO-answer ( $\psi$  does not hold for TS).

**Definition 60** (Model Checking Algorithm). *A model checking algorithm, or model checker, is any decision procedure able to solve a model checking problem.*

When a model checking algorithm terminates with a NO-answer, it must also emit a NO-certificate in the form of a counterexample. Model checking algorithms must systematically traverse all behaviors of the system in order to either confirm that the property holds or provide a counterexample. A model checking algorithm may have either or both of the following qualities.

**Definition 61** (Completeness and Soundness (of a Model Checking Algorithm)). A model checking algorithm is said to be complete iff, given a transition system TS and a property  $\psi$ , it is able to either provide a counterexample of  $\psi$  for TS or detect the absence of counterexamples of any length. A model checking algorithm is said to be sound iff, given a transition system TS and a property  $\psi$ , it provides a counterexample of  $\psi$  for TS only when  $TS \not\models \psi$  and it proves the absence of counterexamples of any length only when  $TS \models \psi$ .

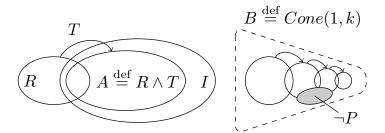

Different classes of model checking problems can be distinguished, depending on the category of temporal properties being checked. In this paper, we are interested only in the model checking of invariant properties, also called *invariant verification problems*, which we show can be solved via reachability analysis on the transition system under verification.

**Definition 62** (Invariant Verification Problem). *Given a transition system* TS *and an invariant property*  $\psi$  *over* AP, *the invariant verification problem of*  $\psi$  *for* TS *is the model checking problem to decide*  $TS \models \psi$  *or to provide a counterexample.*

**Definition 63** (Invariant). *Given a transition system* TS *and an invariant property*  $\psi$  *over* AP, *if*  $TS \models \psi$ , *then the invariant condition*  $\varphi$  *of*  $\psi$  *is a propositional formula over* AP *and is said to be an invariant of* TS.

The invariant verification problem can be reduced to a reachability problem over TS, as follows.

**Theorem 2** (Reduction of Invariant Verification to Reachability). *Given a transition system* TS and an invariant property  $\psi$  over AP, let  $\varphi$  over AP be the invariant condition of  $\psi$ ; then, the invariant verification problem can be reduced to the problem to check whether a state  $s \in S$  such that  $s \not\models \varphi$  is reachable in TS. If that is the case,  $TS \not\models \psi$  and any initial path to s is a counterexample for the invariant verification problem. Otherwise,  $TS \models \psi$ . Such a problem is called the reachability problem of  $\neg \varphi$  in TS.

Therefore, the invariant verification problem can be simply solved by means of a procedure that traverses the reachable state space of TS and checks whether or not  $\varphi$  holds for every traversed state. Since the state space is finite, the procedure eventually terminates either providing a counterexample or confirming  $\varphi$  as an invariant of TS. In practice, such a state space is usually too large to be explicitly traversed. State-of-the-art model checking methods rely on a symbolic representation of the system instead.

#### 2.11. Symbolic Representation of Transition Systems

The model checking formulation provided in the previous subsection relies on an explicit representation of states and transitions. Such an explicit representation is not adequate to handle large state spaces. In *symbolic model checking*, the (explicit) transition system is converted into a more concise, implicit representation based on propositional formulas, called *symbolic representation*. Using a symbolic representation, model checking algorithms can traverse the state space of the system more efficiently, by manipulating sets of states and transitions directly, instead of being forced to operate on one state or transition at a time. In addition, since the symbolic representation relies on propositional formulas, symbolic model checking algorithms can leverage well-developed automatic techniques for manipulating such formulas such as BDDs or SAT solvers.

In this Subsection we show how to *encode* a transition system into its symbolic representation and how to formulate the invariant verification problem on such a representation. Given a transition system  $TS = \langle S, S_0, R, AP, L \rangle$ , to obtain a symbolic representation of TS, we must define how to encode each of its constituents into propositional formulas.

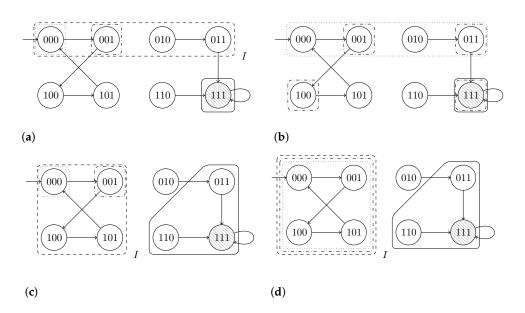

#### 2.11.1. Symbolic Representation of States

In order to symbolically represent the set of states *S* of a transition system  $\mathcal{TS}$ , we introduce a set of propositional variables *V*, called *state variables*, with  $|V| = \lceil log_2|S| \rceil$ . Given a transition system  $\mathcal{TS} = \langle S, S_0, R, AP, L \rangle$  and a set of state variables *V*, we give the following definitions.

**Definition 64** (Encoding Function). An encoding function  $\phi : S \to \mathbb{B}^{|V|}$  over V is an injective function mapping states to complete truth assignments over V.

**Definition 65** (Encoding of States). A state  $s \in S$  is encoded as a complete truth assignment  $\mu_s = \phi(s)$  over *V* according to an encoding function  $\phi$ . The complete truth assignment  $\mu_s$  is called encoding of *s* over *V*.

Note that  $\phi$  is bijective if and only if  $|S| = 2^{|V|}$ . Otherwise, some pseudo-state representations are introduced in the symbolic representation of *S* by encoding. Such pseudo-states can be disregarded and treated as unreachable states of TS.

Propositional formulas over *V* are used to represent sets of states. Any propositional formula  $F_Q$  over *V* represents the set of states  $Q \subseteq S$  such that, for each state  $q \in Q$ , its corresponding encoding  $\mu_q$  over *V* satisfies  $F_Q$ , i.e.,  $\mu_q \models F_Q$ . Given an encoding function  $\phi$  over *V*, and letting  $q \in S$  be a state of  $\mathcal{TS}$ , many logically equivalent propositional formulas over *V* can be used to represent *q*. We define one example of such a formula as follows.

**Definition 66** (Characteristic Formula for States). *The characteristic formula of q is the propositional formula*  $\xi_q$  *over V such that*

$$\xi_q \stackrel{def}{=} \bigwedge_{v_i \in V} l_i \quad where \quad \begin{cases} l_i = v_i, & \text{iff } \mu_q(v_i) = \top \\ l_i = \neg v_i, & \text{iff } \mu_q(v_i) = \bot \end{cases}$$

(22)

where  $\mu_q = \phi(q)$ .

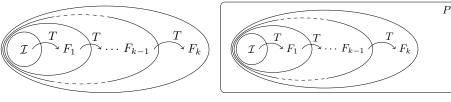

Note that  $\xi_q$  is a cube and it is satisfied only by the complete truth assignment  $\mu_q$  encoding *q*.