## POLITECNICO DI TORINO Repository ISTITUZIONALE

A Deep Study of Resistance Switching Phenomena in TaOx ReRAM Cells: System-Theoretic Dynamic Route Map Analysis and Experimental Verification

| Original A Deep Study of Resistance Switching Phenomena in TaOx ReRAM Cells: System-Theoretic Dynamic Route Map Analysis and Experimental Verification / Ascoli, A; Menzel, S; Rana, V; Kempen, T; Messaris, I; Demirkol, As; Schulten, M; Siemon, A; Tetzlaff, R In: ADVANCED ELECTRONIC MATERIALS ISSN 2199-160X ELETTRONICO 8:8(2022), pp. 1-31. [10.1002/aelm.202200182] |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2988452 since: 2024-05-11T10:45:54Z                                                                                                                                                                                                                                                                                        |

| Publisher:<br>Wiley                                                                                                                                                                                                                                                                                                                                                          |

| Published<br>DOI:10.1002/aelm.202200182                                                                                                                                                                                                                                                                                                                                      |

| Terms of use:                                                                                                                                                                                                                                                                                                                                                                |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                              |

| Publisher copyright                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                              |

| (Article begins on next page)                                                                                                                                                                                                                                                                                                                                                |

# A Deep Study of Resistance Switching Phenomena in TaO<sub>x</sub> ReRAM Cells: System-Theoretic Dynamic Route Map Analysis and Experimental Verification

Alon Ascoli,\* Stephan Menzel, Vikas Rana, Tim Kempen, Ioannis Messaris, Ahmet Samil Demirkol, Michael Schulten, Anne Siemon, and Ronald Tetzlaff

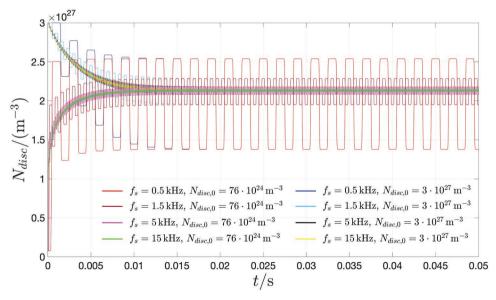

The multidisciplinary field of memristors calls for the necessity for theoreticallyinclined researchers and experimenters to join forces, merging complementary expertise and technical know-how, to develop and implement rigorous and systematic techniques to design variability-aware memristor-based circuits and systems. The availability of a predictive physics-based model for a memristor is a necessary requirement before commencing these investigations. An interesting dynamic phenomenon, occurring ubiquitously in non-volatile memristors, is fading memory. The latter may be defined as the appearance of a unique steady-state behavior, irrespective of the choice of the initial condition from an admissible range of values, for each stimulus from a certain family, for example, the DC or the purely-AC periodic input class. This paper first provides experimental evidence for the emergence of fading memory effects in the response of a TaO<sub>x</sub> redox-based random access memory cell to inputs from both of these classes. Leveraging the predictive capability of a physics-based device model, called JART VCM v1, a thorough system-theoretic analysis, revolving around the Dynamic Route Map graphic tool, is presented. This analysis allows to gain a better understanding of the mechanisms, underlying the emergence of history erase effects, and to identify the main factors, that modulate this nonlinear phenomenon, toward future potential applications.

1. Introduction

The predictive power of Moore's law[1] is about to fade away, as CMOS technology scaling approaches atomic boundaries. Moreover, as the technology minimum feature size is progressively reduced toward the lowest physically-possible limit, the resulting increase in leakage currents poses serious issues in

A. Ascoli, I. Messaris, A. S. Demirkol, R. Tetzlaff Technische Universität Dresden School of Engineering Sciences Faculty of Electrical and Computer Engineering Institute of Principles of Electrical and Electronic Engineering (IEE) Chair of Fundamentals of Electrical Engineering Toeplerbau, Mommsenstraße 12, 01069 Dresden, Germany E-mail: alon.ascoli@tu-dresden.de

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202200182.

© 2022 The Authors. Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is

DOI: 10.1002/aelm.202200182

two significant directions. First, it results in serious heat issues, which may jeopardize the life-time of circuits, and create dangerous positive feedback effects in the thermally-activated physical mechanisms, underlying the operating principles of certain devices. Concurrently, it leads to an inevitable upsurge in power consumption across a CMOS chip, which sheds shadows on the reliability of Dennard's law, [2] and prevents further increases in the clock frequency. Taking also into account the extremely-high costs associated with the production of cutting-edge sub-10 nm chips, semiconductor manufacturers are questioning whether keeping the aggressive transistor downscaling rate, dictated by Moore's law, is still profitable.[3] An additional aspect, which limits the maximum information management rate, is related to the classical von Neumann architecture of state-of-the-art computers, in which the physical separation between central processing unit and data storage system causes inevitable delays in the accomplish-

ment of memory and computing tasks. Besides the proposal of clever ideas to resolve some of these open issues, for example, exploiting the third vertical direction to increase the transistor count on the available chip area, and developing multi-core computing machines with distributed memory to increase the data processing rate, device engineers are devoting considerable efforts in the search for special materials, allowing to develop

S. Menzel Peter Grünberg Institut 7 (PGI-7) Forschungszentrum Jülich GmbH Wilhelm-Johnen-Strasse, 52425 Jülich, Germany V. Rana, T. Kempen Peter Grünberg Institut 10 (PGI-10) Forschungszentrum Jülich GmbH Wilhelm-Johnen-Strasse, 52425 Jülich, Germany M. Schulten, A. Siemon Institut für Werkstoffe der Elektrotechnik 2 **RWTH Aachen University** Sommerfeldstraße 24, 52074 Aachen, Germany

novel devices, which, featuring multiple functionalities within a single nanoscale physical volume, would allow to boost the performance of integrated circuits beyond the technology, heat, energy, and architecture walls, in the years to come.<sup>[4]</sup>

In this regard, one of the most promising class of devices are the memory-resistors, for short memristors, [5,6] which may be essentially defined as nonlinear resistors endowed with a statedependent Ohm law, [7,8] similarly as the constitutive units of biological neural networks, that is, synapses and neuronal ion channels, which explains why they may pave the way toward the design of brain-like computing machines in the near future. [9-11] In particular, depending upon fabrication process, constitutive material, and operating conditions, memristor physical realizations, often referred to as resistance switching devices in the material engineering community,<sup>[12]</sup> may either be non-volatile or volatile.<sup>[13]</sup> In the first (latter) case, switching the power off, each device of this kind freezes instantaneously at one of an analogue continuum of memory states<sup>[14]</sup> (settles down, after some transient phase, on one and only one memory state, irrespective of the initial condition<sup>[15]</sup>). Besides realizing an innovative resistance-based data storage concept, and reproducing synaptic plasticity, [16] non-volatile memristors may allow to implement in-memory computing paradigms.<sup>[17,18]</sup> Volatile memristors are typically employed as selector devices<sup>[19]</sup> to regulate the current flow in crossbar arrays of non-volatile memristors, but they may be also utilized to implement spike-based computing paradigms, [10] or to develop biologically-plausible electronic implementations of neurons, [20-22] if, similarly as sodium and potassium ion channels in axon membranes, [23] exhibit the capability to amplify the small-signal upon suitable polarization, [15,24,25] a property which is referred to as local activity.<sup>[26]</sup>

The research work, presented in this manuscript, aims to highlight the pivotal role that nonlinear system theory may assume in deepening the understanding of intrinsically-nonlinear devices<sup>[27]</sup> toward a systematic analysis and design of circuits based upon them. [28] Back in 2016 TU Dresden and Hewlett Packard (HP) Labs announced the discovery of a very interesting input-induced dynamic phenomenon, referred to as fading memory<sup>[29]</sup> or history erase effect, [30] in a tantalum oxide-based non-volatile nano-device. Due to the application of a purely-AC periodic voltage across the memristor, its current was found to feature, asymptotically, one and only one oscillatory behavior, irrespective of the memory content preliminarily programmed into the device resistance. Further investigations revealed that history erase effects appear in the nonvolatile memory cell from HP Labs also under a constant voltage stimulus of either polarity, resulting in a unique steady-state level for the current through its physical stack, irrespective of the device resistance prior to the DC stress test.

While input-induced memory loss effects were later observed in various other non-volatile memristors, [31,32] this manuscript conducts a deep study, combining experimental work and nonlinear system-theoretic methods, to gain a deep insight into the origin of this nonlinear phenomenon, and to determine the key parameters enabling its modulation in view of future potential applications. The object of the investigations is an illustrative example of a filamentary valence change memory (VCM) cell, specifically a tantalum oxide redox-based random access memory (ReRAM) device fabricated at Peter Grünberg Institut (PGI-7), Forschungszentrum Jülich GmbH. As for all filamentary VCM cells, the modulation of the resistance of the physical

stack under focus is enabled by the restoration and rupture of a tiny conductive filament region, featuring a high concentration of oxygen vacancies, which occur under complementary polarities of the voltage let to drop across the device terminals. In this paper, experimental evidence for the fading memory behavior of the ReRAM cell under either DC or purely-AC periodic excitation is first provided. Furthermore, a powerful system-theoretic tool, called *dynamic route map* (DRM),<sup>[33]</sup> is applied to an accurate physics-based first-order model of the non-volatile memory cell, allowing for a deeper understanding of the unique device behavior. Moreover, a novel graphic tool, called *current DRM* (C-DRM), is proposed, so as to enable a similar circuit-theoretic analysis based on experimentally available data.

## 2. Experimental Results on DC Stress Tests

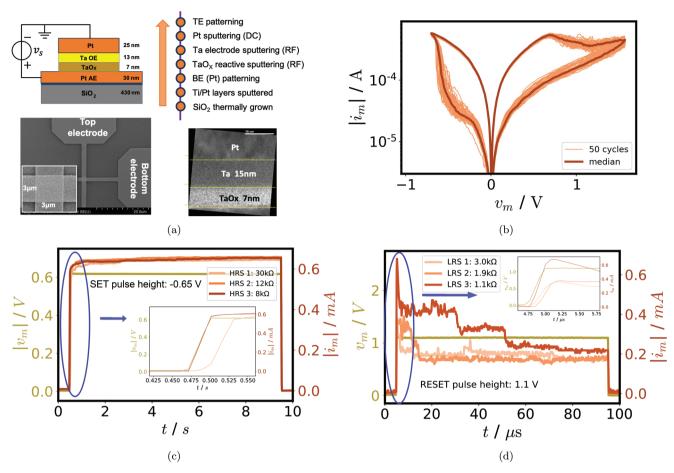

In order to enable the investigation of the typical resistance switching characteristics of VCM cells, an exemplary ReRAM device, composed of a platinum (Pt) / tantalum oxide  $(TaO_x)$ / tantalum (Ta)/Pt physical stack (refer to **Figure 1a**), was preliminarily fabricated, and electrically characterized in house.

Figure 1b shows also a top-view scanning electron microscope (SEM) image of a micro-crossbar VCM cell, featuring a junction area of  $3\times3~\mu\text{m}^2$ , and its TEM cross-section, revealing the thickness of each layer of the device stack. Details on the device fabrication are reported in Section 7.

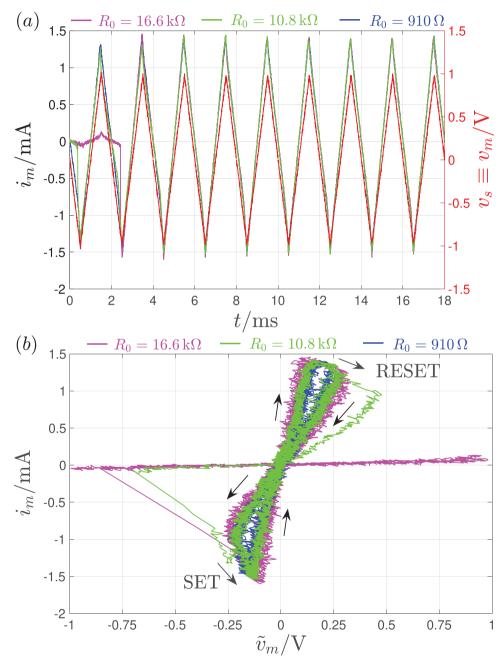

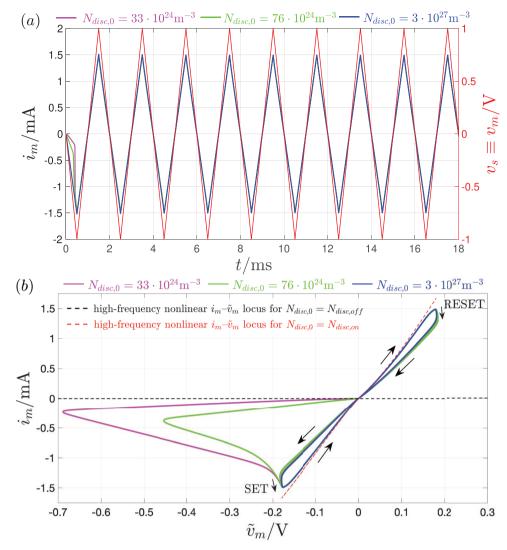

The electrical characterization of the crosspoint devices is performed at room temperature using a custom setup<sup>[34]</sup> designed in house. Figure 1b shows 50 cycles of a current  $i_{\rm m}$ –voltage  $\nu_{\rm m}$  characteristic of the Pt/TaO<sub>x</sub>/Ta/Pt ReRAM device, as acquired through the application of a slowly-varying asymmetric AC periodic triangular voltage stimulus with a frequency of 2 kHz, a minimum value of –0.7 V, and a maximum value of +1.6 V to the bottom electrode, with the top electrode grounded. Over each cycle, the VCM cell undergoes a SET (RESET) transition over the negative (positive) half cycle of the input waveform. Stimulating the bipolar ReRAM device through a high-frequency asymmetric AC periodic voltage pulse train, it is found to exhibit a very reliable resistance switching behavior, undergoing consecutive SET and RESET transitions for as many as  $10^6$  cycles.<sup>[35]</sup>

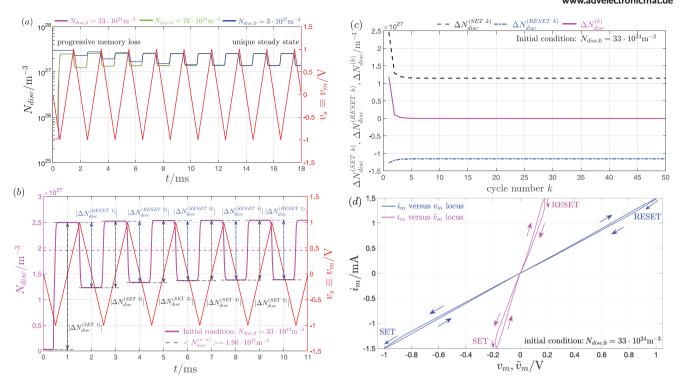

Focusing again on the I-V characteristic in Figure 1b, it becomes clear that, over the SET process, the resistance of the device initially undergoes a rather abrupt thermally-activated decrease, while, later on, as the current attains higher values, the increase in the voltage across the internal series resistance limits its further reduction.<sup>[36]</sup> Similarly, over the RESET process, which starts at high current levels, the device resistance undergoes initially a noticeable thermally-activated increase, until its further growth is counteracted by the negative feedback mechanism that naturally comes into play as the device draws less current.<sup>[36]</sup> Importantly, the saturation phenomena, emerging in the second phase of each of the SET and RESET resistance switching transitions, are responsible for the memory loss induced in the device by DC inputs, which clearly reveals the fundamental role of the internal series resistance on the emergence of the *fading* memory phenomenon. Section S1, Supporting Information, provides more details on the system-theoretic concept of fading memory. Figure 1c(d) provides evidence for the fading memory of

Figure 1. a) Schematic diagram and fabrication process flow of a Pt(25 nm)/Ta(15 nm)/Ta(0,7nm)/Pt(30 nm) ReRAM device, including a top-view SEM image of a  $3 \times 3 \mu m^2$  VCM cell, and its TEM cross-section providing clear evidence for the thickness of each layer in the physical stack. b) Current  $i_m$ -voltage  $v_m$  characteristic of a Pt/Ta/TaO<sub>x</sub>/Pt VCM cell for 50 switching cycles of a quasi-static asymmetric triangular voltage stimulus cycling periodically at a frequency of 2 kHz and featuring minimum and maximum values -0.7 V and +1.6 V, respectively (light orange). The median cycle is shown in dark orange. The application of the voltage stimulus to the bottom electrode, with the top electrode grounded, explains why, over each 0.5 ms-long cycle, the device undergoes a SET (RESET) resistance switching transition in the negative (positive) half of the input waveform. c,d) Experimental evidence for the memory loss, which DC inputs induce in the device. Transients in the device current under the application of a given set voltage pulse for three different initial conditions established preliminarily through distinct reset operations (c). Transients in the device current under the application of a given reset voltage pulse for three different initial conditions established preliminarily through distinct set operations (d). The insets in (c) and (d) are close-up views across the pulse rise time interval, indicated through blue ellipses in the original plots. A high resistance state (HRS) is preliminarily programmed into the device through the selection of a particular value for the peak, called *reset-stop voltage*, [12] of a purely-positive slowly-and-stepwise-varying triangular pulse signal applied across the physical structure. In order to program a low resistance state (LRS) into the device, prior to the DC stress reset test, the current response of the physical stack to a purely-negative slowly-and-stepwise-varying triangular pulse signal is hard limited by specifying a particular *compliance level* in t

the ReRAM device under a negative (positive) DC input voltage. Preliminarily, the device was programmed into one of three low (high) resistance states, as indicated in the legend. A negative (positive) voltage pulse, featuring a height of -0.65 V (1.1 V), a width of 9.007 s (90.07 µs), and a rise and fall time of 40.1 ms (401 ns), was then found to induce a progressive memory loss, which results in the appearance of a unique steady state for the current flowing through the physical stack. With reference to the SET transition of Figure 1c, the dynamics of the device are first accelerated by the positive feedback induced by Joule heating effects, but are then slowed down and limited by the inherent series resistance. Consequently, the device current attains a unique saturation plateau, for each of the three initial conditions (HRS stands for high resistance state), before returning to zero in all cases, when the power

is switched off. This experiment shows how DC fading memory coexists with non-volatility in the VCM cell. The initial condition affects only the onset of the VCM device response, which commences with some small delay after (commences directly after) the pulse stimulus begins its ascent in the most resistive case (in the two least resistive cases). Looking now at the experimental results from Figure 1d, the pulse rise causes an initial upsurge in the device current. Then, when the RESET transition commences, the device current first experiences a strong decrease. This is induced by the positive feedback mechanisms, setting in as, by nonlinear voltage division, the fraction of the total ReRAM cell voltage, falling across the core memristor, progressively and inevitably dominates more and more over the remainder, dropping across the internal series resistance. Later, when most of the

positive bias voltage stimulus falls across the core memristor, the low device current levels determine a thermal deactivation of the RESET switching dynamics. In fact, due to the negative feedback effects, associated with the ongoing cooling of the internal filament, in this second phase the device current is found to decrease more gradually. Importantly, the current, flowing through the device stack, is found to tend toward a common asymptotic level, for each of the three initial conditions (LRS stands for low resistance state). Finally, in all scenarios, when the input is removed, the device current drops to zero. This result reveals, once again, the coexistence between fading memory, as induced by DC stimulation, and non-volatility, appearing when the power is switched off, in the ReRAM device.

## 3. System-Theoretic Insights into the Device Resistance Switching Transitions under DC Stress

The next section reports the main equations of the physics-based mathematical model,  $^{[37-39]}$  which reproduces accurately the response of our  ${\rm TaO_x}$  ReRAM device to any input of interest and for all admissible initial conditions. More details on the VCM cell mathematical description are given in Section S2, Supporting Information, which includes also the complete list of model parameters. A deep system-theoretic analysis of the DC SET and RESET transitions of the VCM cell is then conducted on the basis of this model.

#### 3.1. JART VCM v1 ReRAM Model

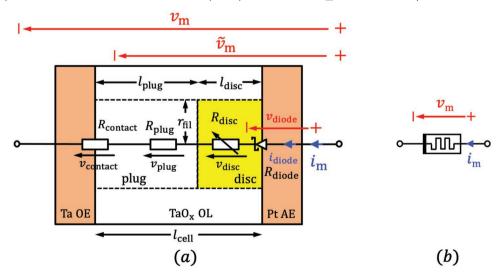

**Figure 2**a depicts the equivalent circuit-theoretic description of the JART VCM v1 model. Its consists of the series combination between a number of resistances identifiable along the longitudinal extension of the ReRAM device. With the physical stack rotated by  $-90^{\circ}$  relative to its view in Figure 1a, the Ta-based top (Pt-based bottom) electrode, which is referred to as ohmic (active)

electrode, or OE (AE) for short, throughout the manuscript, is adjacent to the left (right) end of the TaOx-based oxide layer. Here  $v_{\rm m}$ , and  $i_{\rm m}$ , respectively denote the voltage falling across and the current flowing through the device, which, as shown in Figure 2b, is symbolized as a memristor<sup>[5]</sup> in circuit and system theory. The physical origin for the SET and RESET switching processes is known as VCM mechanism.[40] It is associated with the motion of ionic defects—in particular, the positivelycharged oxygen vacancies—from the OE/oxide interface toward the oxide/AE interface (from the oxide/AE interface toward the OE/oxide interface) as a negative (positive)-valued voltage  $v_m$  is let fall across the device. In the first (latter) case, this results in the formation (dissolution) of a conductive filament, bridging (opening up) a gap between the two electrodes, at the oxide/AE interface. As a basic assumption of the JART VCM v1 model, the oxygen vacancy-rich conductive filament, which is first created within the oxide film through an electro-forming step, is composed of two main resistive regions. One of them, called plug, features a large number of ionic defects, and, as a result, acts as an oxygen vacancy reservoir for the other less conductive region, named disc. The motion of ionic defects toward the AE (OE) under a negative (positive) voltage stimulus  $v_s$  across the microscale device determines an increase (decrease) in the disc oxygen vacancy concentration  $N_{\text{disc}}$ , which defines the VCM cell state. Importantly,  $N_{

m disc}$  is constrained to lie at all times within a closed set, defined as  $\mathcal{D} \triangleq [N_{\text{disc,off}}, N_{\text{disc,on}}]$ , where the lower (upper) bound is associated to the device highest (lowest) possible resistance state. The ordinary differential equation (ODE), governing the time evolution of the disc oxygen vacancy concentration, is then expressed by

$$\frac{\mathrm{d}N_{\mathrm{disc}}}{\mathrm{d}t} = f(N_{\mathrm{disc}}, \nu_{\mathrm{m}}, i_{\mathrm{m}}) = -\frac{i_{\mathrm{ion}}}{z_{\mathrm{Vo}} \times e \times A \times l_{\mathrm{disc}}} \tag{1}$$

in which  $i_{\rm ion}$  stands for the ion-hopping current, related through complex implicit equations to memristor state  $N_{\rm disc}$ , voltage  $\nu_{\rm m}$ , and current  $i_{\rm m}$ , as established by the Mott– Gurney law, while the

Figure 2. a) Circuit-theoretic model and b) symbol of the  $TaO_x$ -based VCM cell. The memristor state is defined as the oxygen vacancy concentration  $N_{disc}$  in the disc region. The device voltage, and current are indicated as  $\nu_m$ , and  $i_m$ , respectively. The VCM cell may be interpreted as a one resistor-one memristor two-terminal device. The role of the resistive element is assumed by the contact resistance  $R_{contact}$ , which forms naturally at the OE/oxide interface. OE, AE, and OL, respectively stands for ohmic electrode, active electrode, and oxide layer.

other symbols are constant parameters. Given that the OE/oxide interface operates purely as a linear resistor, it is the electric field-induced modulation of the energy barrier at the oxide/AE interface, acting as a Schottky-like diode, which regulates the electron transport in the VCM cell. The current  $i_{\rm m}$ , flowing through the ReRAM device, is then equivalent to the Schottky diode current  $i_{\rm diode}$ . The relationship between device current  $i_{\rm m}$ , voltage  $v_{\rm m}$ , and memory state  $N_{\rm disc}$  is dictated by an implicit Ohm law of the form

$$h(N_{\rm disc}, \nu_{\rm m}, i_{\rm m}) = 0 \tag{2}$$

which bifurcates into a couple of involved expressions. One of them, due to thermal emission over a forward-biased Schottky junction, applies for the positive polarity of the device voltage, that is, over a RESET transition. Differently, the other one, due to tunneling via thermionic field emission through a reverse-biased Schottky junction, holds true for the negative polarity of the device voltage, that is, over a SET transition. Importantly, being responsible for the self-heating positive (self-cooling negative) feedback effects, which accelerate (decelerate) the device SET and RESET transition dynamics, the internal temperature T of the filament is linearly proportional to the power  $P_{\rm el} = \nu_{\rm m} \times i_{\rm m}$  dissipated in the physical stack, according to

$$T = T_0 + R_{\text{th}} \times P_{\text{el}} \tag{3}$$

where  $T_0$  and  $R_{\rm th}$  denote ambient temperature and device thermal resistance, respectively.

When, in the system-theoretic analysis to follow, the voltage across  $R_{\text{contact}}$  shall be subtracted from the overall device voltage  $v_{\rm m}$ , the resulting expression, namely  $\tilde{v}_{\rm m} = v_{\rm m} - R_{\rm contact} \times i_{\rm m}$ , where  $i_{

m m} \equiv i_{

m diode}$ , represents the voltage across the core memristor. Moreover, in all the investigations discussed in this paper, the voltage stimulus  $v_s$  is applied directly across the VCM cell, implying  $v_{\rm m} \equiv v_{\rm s}$ . The VCM cell memristance R may be estimated as the sum of four contributions, specifically the contact  $R_{contact}$ , plug  $R_{\text{plug}}$ , disc  $R_{\text{disc}}$ , and Schottky junction  $R_{\text{diode}} = v_{\text{diode}}/i_{\text{diode}}$  resistances. Applying a given voltage  $v_s$  across the ReRAM device, the resulting modulation in the physical stack resistance may be easily computed via  $R = v_{\rm s}/i_{\rm m}$ . Despite the implicit form of both state equation and the Ohm law, the VCM cell under study is typically controlled in voltage. In order to reflect this aspect in the model investigations, the differential algebraic equation (DAE) set in Equations (1) and (2) is numerically solved through an implicit Euler numerical integration method so as to determine the device state  $N_{\rm disc}$  and current  $i_{\rm m}$  in correspondence to the control voltage  $v_{

m m}$  for all simulation time points at once. Finally, it is instructive to note that, very recently, an analytical method was developed to reformulate the JART VCM v1 model so as to let it admit an explicit formula for the current through the ReRAM cell as a function of its memory state, namely the disc oxygen vacancy concentration, as well as of the voltage dropping across its terminals.<sup>[41]</sup>

## 3.2. System-Theoretic Analysis of the JART VCM v1 Model Predictions

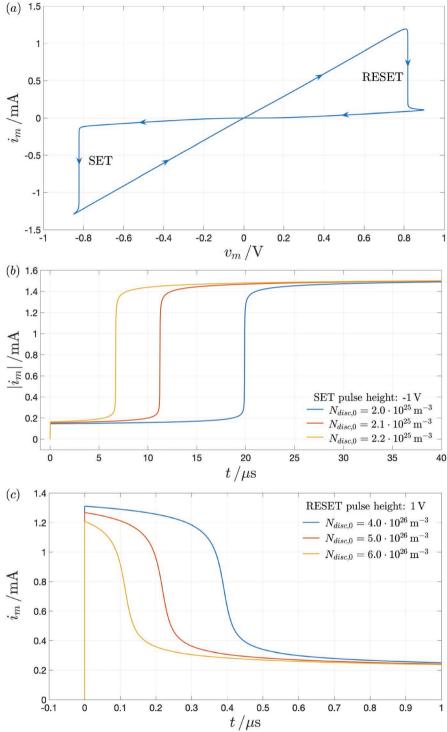

Figure 3a shows the current- voltage characteristic of the ReRAM cell, as predicted by the JART VCM v1 model, under

the hypothesis that an AC periodic triangular voltage stimulus, cycling at a sweep rate (SR) of 5 V s<sup>-1</sup>, is let drop across the physical stack. With the VCM cell preliminary initialized in a HRS, over the negative input half cycle, the modulus<sup>[42]</sup> of the current is found to undergo an abrupt upsurge, as soon as the voltage, falling between the device terminals, attains a value of about -0.822 V. The indefinite increase is prevented by the limiting action of the contact resistance. Similarly, over the succeeding positive input half cycle, as soon as the voltage across the physical stack increases up to a value of about +0.818 V, the device current is found to experience a sharp decrease, before undergoing a gradual descent, as induced by the contact resistance, thereafter. Acquiring a deeper understanding of the initial positive and later negative feedback mechanisms, accompanying both the SET and RESET switching transitions of the ReRAM device, under the application of voltage stimuli across its physical stack, is not a simple task. On the other hand, a deeper insight into the complex resistance switching phenomena, emerging in the VCM cell, may be gained through the analysis of its response to DC inputs.

Figure 3b shows the model prediction of the time waveform of the modulus of the device current in response to a negative SET voltage pulse of height -1 V and rise time 1 ns, for each of three distinct relatively-low initial conditions assigned to the disc oxygen vacancy concentration  $N_{\rm disc}$ , as provided in the caption. The qualitative behavior of the device current is similar in each of the three scenarios. After an early jump to a level, dependent upon the initial device resistance (the larger is  $N_{\text{disc. 0}}$ , the more conductive is the device, and, correspondingly, the higher is such a step), occurring over the pulse rise time, the modulus of the current through the physical stack exhibits a rather slow ascent, at an initial condition-dependent rate, subsequently. However, at some point in time, known as SET time  $t_{SFT}$ , and differing on the basis of the initial value assigned to the disc oxygen vacancy concentration, the modulus of the current through the ReRAM device undergoes a rather fast transition. Later on, at some other point in time, known as SET saturation time  $t_{SET, sat}$ ,  $|i_m|$  is found to saturate toward the very same asymptotic level, when the disc oxygen concentration attains the highest possible value in the admissible domain, for all the three scenarios, which reveals the fading memory of the VCM cell under the DC stress SET test, and agrees with the experimental observations illustrated in Figure 1c. It is important to observe, here, that in a past work [43] from the literature, the very same time instants, defining beginning and end of the abrupt SET switching regime, were respectively named  $t_{\text{delay, SET}}$  and  $t_{\text{SET}} \triangleq t_{\text{delay, SET}} + t_{\text{trans, SET}}$ , with  $t_{\text{trans, SET}}$  indicating the fast SET transition time interval. The impact of the initial condition on the rate of the slow ascent in  $|i_{\rm m}|$ , and on the delay time stems from the highly-nonlinear switching kinetics of the device as ions migrate toward the AE during the SET transition, as revealed in previous publications.[44–47] Focusing on the slow ascent of the device current modulus after the initial jump, this originates from a correspondingly low increase rate in the disc oxygen vacancy concentration, which typically characterizes the early phase of the SET transition of a device initiated in a relatively high resistance state. However, as the oxygen vacancies slowly move toward the AE, the resistance of the physical stack undergoes a minor yet progressive reduction, which inevitably

Figure 3. Predictions from the JART VCM v1 model. a) Device current  $i_m$ -voltage  $\nu_m$  characteristic observed under the application across the VCM cell of an AC periodic triangular voltage stimulus  $\nu_s$ , featuring an asymmetric shape, with minimum  $\nu_{s, min}$  and maximum  $\nu_{s, max}$  values equal to -0.85, and 0.9 V, respectively, and varying slowly, at a SR of 5 Vs<sup>-1</sup>, that is, equivalently, at a frequency f of SR/ $(2 \times (|\nu_{s, min}| + \nu_{s, max})) = 1.4286$  Hz). The arrows superimposed on the pinched hysteresis loop indicate the sweep direction over time. b) Time evolution of the device current modulus  $|i_m|$  under a DC stress SET test, in which a negative voltage pulse, featuring a height of -1V, is let fall across the ReRAM device, for all times following its 1 ns-long rise time, for three different values assigned to the initial disc oxygen vacancy concentration  $N_{\text{disc.}\,0} \triangleq N_{\text{disc}}(0)$ , specifically  $2 \times 10^{25}$ ,  $2.1 \times 10^{25}$ , and  $2.2 \times 10^{25}$  m<sup>-3</sup>. c) Time evolution of the device current im under a DC stress RESET test, in which a positive voltage pulse, featuring a height of 1 V, is let drop between the VCM cell terminals, for all times, which follow its 1 ps-long rise time, for three distinct initial conditions assigned to the disc oxygen vacancy concentration  $N_{\rm disc}$  namely  $3 \times 10^{26}$ ,  $4 \times 10^{26}$ , and  $5 \times 10^{26}$  m<sup>-3</sup>.

raises the current flowing through it. The resulting increases in the temperature inside the filament increments the ion drift velocity. This speeds up the device switching transition, which further reduces the resistance of the VCM cell, activating a positive feedback mechanism, which finally leads to a dramatic upsurge in the current through its various layers.[38-41,43-48] If no measure were set in place to limit the device current, this process would finally cause an irreversible damage to the physical stack. In regard to the ReRAM device, fabricated in house at the PGI-7 facilities of the Forschungszentrum Jülich (FZJ), it is the internal series resistance  $R_{\text{contact}}$ , which prevents an uncontrollable runaway of the current in the stress SET test, as discussed in previous publications.<sup>[36]</sup> As the device current attains high levels, the consequent progressive increase (decrease) in the voltage drop across the contact resistance (across the core memristor), due to the voltage division rule, activates a negative feedback mechanism, whereby the power dissipated in the cell, due to Joule heating, reduces over time, which inevitably slows down the SET switching transition. It is clear that the filament temperature T plays a key role in both the positive and negative feedback mechanisms affecting the device dynamics during the SET transition (the interested reader is invited to consult Section S4, Supporting Information, for further insights).

Figure 3c depicts the time evolution of the device current, as observed in a numerical simulation of the Jülich Aachen Resistive Switching Tools (JART) VCM v1 model, under the specification of a RESET voltage stimulus in the form of a positive pulse of height 1 V and rise time 1 ps, for each of three different relatively-high initial values assigned to the disc oxygen vacancy concentration  $N_{\rm disc}$  (see the caption for details).

The time course of the device current is similar for each of the three scenarios. Initially, during the pulse rise time, the current flowing through the VCM cell experiences a fast increase to an initial condition-dependent level (the larger is  $N_{\text{disc. 0}}$ , and the higher is the increment in  $i_{\rm m}$ ). Afterward, the current through the physical stack undergoes a slow descent at a rate dependent upon the initial condition. It is then found to exhibit an abrupt decrease at some point in time, which we call RESET time  $t_{RESET}$ , and is found to depend upon the initial resistance programmed into the device. However, later on, at some other point in time, known as RESET saturation time  $t_{RESET, sat}$ , the RESET transition rate is subject to a significant reduction, which explains the rather gradual concurrent decrease in the device current  $i_{\rm m}$ . Importantly, this results in the asymptotic appearance of a unique steady state for the cell current, which, irrespective of the initial condition, eventually approaches a constant level, when the disc oxygen vacancy concentration  $N_{\rm disc}$  attains the highest possible value in the admissible domain. This confirms the emergence of fading memory effects in the device under the DC stress RESET test, confirming the experimental observation illustrated in Figure 1d. Similarly as pinpointed for the SET transition scenario, earlier on, it is relevant to note, here, that in a previous publication, [43] the very same time instants, which mark beginning and end of the abrupt RESET switching regime, were respectively named  $t_{\text{delay, RESET}}$  and  $t_{\text{RESET}} \triangleq t_{\text{delay, RESET}} + t_{\text{trans, RESET}}$ , with  $t_{\text{trans, RESET}}$ indicating the fast RESET transition time interval.

Focusing now on the slow initial condition-dependent rate of decrease in the device current, which follows its initial

abrupt upsurge, it can be explained through the voltage division between the contact resistor and the core memristor. [36,43,49] In fact, at the beginning of this phase, a large fraction of the voltage, corresponding to the pulse height, falls across the internal series resistance. As a result, the remainder of the stimulus voltage provides a weak force to drive the ReRAM device resistance increase. However, as the VCM cell slowly resets, the portion of the input voltage falling across the core memristor progressively increases. This results in an inevitable increase in the RESET transition speed over time. Joule heating effects accelerate the device switching dynamics further, and a positive feedback mechanism sets in, explaining the sharp decrease in the current through the physical stack. However, at some point in time, most of the input voltage is found to fall across the core memristor. Negligible further increments in the voltage across the physical stack are thus appreciated, thereafter. Since a reduction in the device current is still noticeable, the resulting decrease in the power, dissipated in the physical stack, progressively cools down the filament, reducing its temperature. In its turn, this decelerates the device RESET switching process over time.<sup>[50,51]</sup> Such a negative feedback mechanism explains the gradual phase of the RESET transition over the last part of the DC stress RESET test. It is clear that the filament temperature T plays a key role also in both the positive and negative feedback mechanisms affecting the device dynamics during the RESET transition (the interested reader is invited to consult Section S4, Supporting Information, for further insights). It is instructive to note that, in practice, ion diffusion mechanisms, due to oxygen vacancy concentration gradients across the physical stack, also play a role in the time behavior of the device current, especially under the DC stress RESET test, where they counteract the ion drift process effects. In fact, the final value attained by the current, flowing through the physical stack, under a DC stress RESET test, depends upon the balance between the ion drift toward the OE, as modulated by the electric field, and the counteractive ion diffusion toward the AE, due to the accumulation of oxygen vacancies in the most conductive region of the VCM cell.[51-53] Since the JART VCM v1 model does not account for ion diffusion mechanisms, its later development, known as JART VCM v2,[54] will be employed in a later publication to explore how the fading memory of the ReRAM device may be best leveraged for future electronics applications.

Comparing the model numerical simulations, discussed in this section, with the experimental data analyzed in Section 2, it is clear that the JART VCM v1 model is capable to reproduce rather well the dynamics of the ReRAM cell in both the DC and AC modes. This provides clear evidence for the reliability of the device model analysis to follow here and in the remainder of the manuscript. In order to allow for a thoroughly comprehensive analysis of the device nonlinear dynamics, its SET and RESET switching transitions under negative and positive pulse voltage stimuli, respectively, are studied in Sections 3.2.1 and 3.2.2, respectively, on the basis of system-theoretic investigations of the JART VCM v1 model and of its numerical integrations, over the entire variation range for the disc oxygen vacancy concentration  $N_{\rm disc}$ , namely from  $N_{\rm disc}$ , off = 1 × 10<sup>24</sup> m<sup>-3</sup> to  $N_{\rm disc}$ , on = 3 × 10<sup>27</sup> m<sup>-3</sup>.

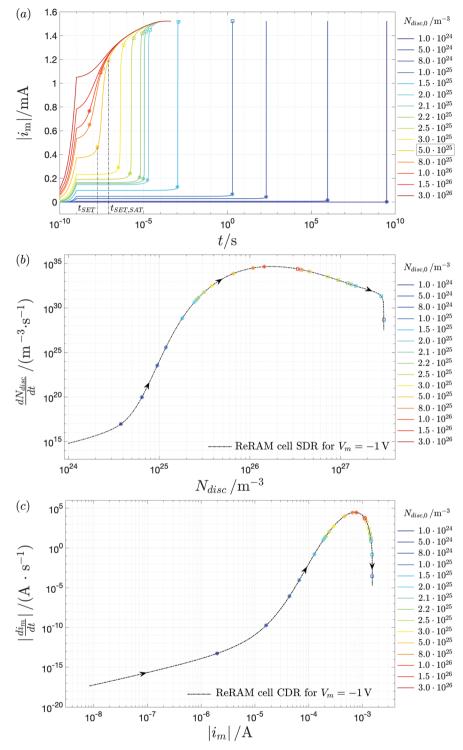

#### 3.2.1. System-Theoretic Analysis of the SET Process

Figure 4a illustrates the time course of the device current modulus  $|i_m|$  under the application of the same negative SET voltage pulse of height -1 V, as defined for the simulations from Figure 3b, for a very wide set of initial conditions, preliminarily assigned to the disc oxygen vacancy concentration. The association between each of the 15 distinct traces in Figure 4a and the corresponding initial condition may be inferred from the color coding map illustrated as legend. Importantly, here a logarithmic scale is chosen to report values on the time axis, which enables to visualize the dynamical behavior of the current for all initial conditions. Inspecting the various curves in Figure 4a, all of them exhibit an initial fast increase to an initial condition-dependent level (the higher is  $N_{\text{disc. 0}}$ , the larger is the increment in  $|i_{\rm m}|$ ), as it was observed in the simulations of Figure 3b, as well as in the experiments of Figure 1c, during the pulse rise time. Subsequently, all traces feature a slow increase at some initial condition-dependent pace (the ascent in  $|i_m|$  is slower and slower as the resistance, initially programmed into the VCM cell, is higher and higher). After this phase, except for the two highest initial conditions from the legend, the VCM cell is found to enter an abrupt SET switching regime. At each time t, within such a regime, the device current upsurge is so significant to satisfy the constraint

$$|di_{\rm m}/d\log_{10}(t)| \ge 10^{-4} \,\mathrm{As}^{-1}$$

(4)

with

$$N_{\rm disc, off} < N_{\rm disc} < N_{\rm disc, on}$$

(5)

that is, while, concurrently,  $N_{\rm disc}$  lies within the bounds of its admissible existence domain  $\mathcal{D}$ . In the definition of an appropriate abrupt SET switching regime measure, the device current in Equation (4) is differentiated with respect to the base-10 logarithm of the time, which allows to express through an ad hoc mathematical formula the slope visualizable along each of the traces, plotted on a logarithmic time scale, in Figure 4a. An asterisk marker indicates the first point in time, earlier referred to as SET time  $t_{\text{SET}}$ , at which the inequality in Equation (4) holds true, for each of the traces, except those associated to the two largest initial conditions from the legend. For these two initial conditions, in fact, it is not possible to identify, clearly, a point in time, at which the modulus of the derivative of the device current with respect to the time, expressed in logarithmic scale, attains the threshold of 10<sup>-4</sup> As<sup>-1</sup>, as established by the inequality in Equation (4). Under these circumstances, the entire on-switching process appears rather gradual, which allows to tune the VCM cell resistance finely in a potential experiment. Importantly, for all initial conditions, where the ReRAM device is found to enter an abrupt switching regime, the lower is  $N_{\text{disc}, 0}$ , and the larger is the set time  $t_{SET}$ . Importantly,  $t_{SET}$  is found to span over 17 orders of magnitude in time, which provides clear evidence for the strongly-nonlinear on-switching kinetics of the VCM cell. Furthermore, for each trace, which hosts an asterisk marker, except for the curves corresponding to the three lowest initial conditions from the legend in Figure 4a, the abrupt switching phase is followed by another gradual one. In fact, analyzing the time series of the device current modulus in each of these SET transition scenarios, a further initial condition-dependent point in time, earlier referred to as SET saturation time  $t_{\rm SET, \ sat}$ , may be identified (refer to the square marker), at which the inequality in Equation (4) holds true with  $N_{\rm disc} < N_{\rm disc, \ on}$ , that is, under the hypothesis expressed by Equation (5). At the SET saturation time the physical stack is found to enter a new gradual switching phase, referred to as SET saturation regime, where further increments in  $|i_{\rm in}|$  are limited by the presence of the internal series resistance  $R_{\rm contact}$ . The SET saturation regime may not be identified on either of the three rightmost traces, since, in each of these cases, the disc oxygen vacancy concentration attains the upper bound in its existence domain, while the inequality in Equation (4) still holds true.

As a further aspect of interest, the increment in the device current modulus over the abrupt phase, as may be estimated for all traces, which host both an asterisk and a square marker, differs from initial condition to initial condition. In fact, inspecting Figure 4a, it is clear that the vertical distance between the asterisk and square markers varies across these traces. It increases as the resistance initially programmed into the device increases, which means that  $t_{\text{SET,sat}} - t_{\text{SET}}$  actually gets larger and larger as the value assigned to  $N_{\text{disc}, 0}$  is smaller and smaller. As an additional significant note, with reference to Figure 4a, it is worth to observe that, from each of the initial conditions, the device current modulus eventually attains a constant level, which is determined uniquely by the device voltage and by the unique asymptotic value of the disc oxygen vacancy concentration, namely  $N_{\rm disc, on}$ , as established by the implicit Ohm law (Equation (2)). Section S4, Supporting Information, file visualizes the time evolution of other physical variables of interest, specifically the filament temperature T, and the voltages  $\tilde{\nu}_{\rm m}$ , and  $v_{\text{contact}}$ , falling across core device and contact series resistance, respectively, as recorded during each of the numerical simulations, which resulted in the  $|i_{\rm m}|$  versus t loci of Figure 4a.

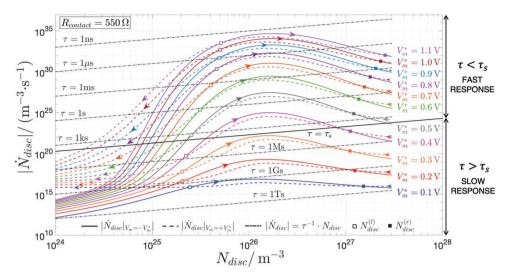

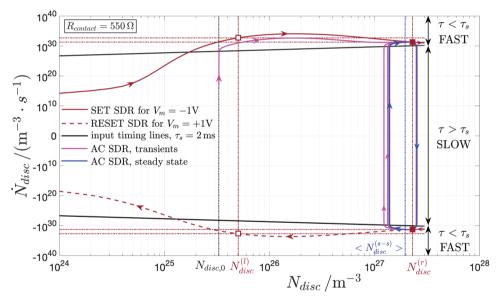

In order to gain a deeper understanding of the resistance switching phenomena, emerging in the physical stack under the DC stress SET test, it is important to analyze the device dynamics along its state dynamic route (SDR) for a negative DC voltage  $V_m$ , let fall between its two terminals, of value equal to the pulse height, here set to -1 V. Given that a negative DC voltage stimulus induces a SET transition in the ReRAM cell, a SDR, associated to a negative-valued  $V_{\rm m}$ , is also referred to as SET SDR. Grouping a number of SET SDRs, one for each negative DC voltage, let fall across the ReRAM cell, the resulting family of loci forms the device SET DRM. As discussed later on in Section 3.2.2, a complementary family of loci, referred to as RESET DRM, allows to gain insights into the device resistance switching transitions under positive DC voltage stimuli (see Section S3, Supporting Information, file for more details about the system-theoretic graphic tool called DRM, which obviously combines together both the SET and the RESET DRMs). As established by the ReRAM cell state Equation (1), the locus of  $|dN_{disc}/dt| \equiv dN_{disc}/dt$  versus  $N_{disc}$  for  $V_m = -1$  V is illustrated in Figure 4b. Since the disc oxygen vacancy concentration  $N_{\rm disc}$ is unaccessible in practice, it is insightful to introduce a current-based variant of each SET SDR, which we call SET current dynamic route (CDR), and define as the locus of the modulus of the time derivative of the device current  $|di_m/dt| \equiv d|i_m|/dt$

Figure 4. System-theoretic analysis of the JART VCM v1 model predictions of the device response to negative DC voltage excitations. a–c) Investigation of a DC stress SET test, in which a voltage source, generating a negative pulse of height –1 V and rise time 1 ns, is inserted in parallel to the VCM cell for 15 different values assigned to its initial disc oxygen vacancy concentration  $N_{\rm disc,0}$ , as reported in the common legend from either of the plots. a) Time evolution of the device current modulus  $|i_m|$ . b)  $dN_{\rm disc}/dt$  versus  $N_{\rm disc}$  locus of the VCM cell for  $V_m = -1$  V. In system-theory, an arrowed locus of this kind is known as a SDR. Since here the DC voltage across the ReRAM cell induces its SET transition, a SDR of this kind is referred to as a SET SDR. c)  $|di_m/dt|$  versus  $|i_m|$  locus of the VCM cell, for  $V_m = -1$  V. An arrowed locus of this kind is a current-based variant of a SET SDR, referred to as SET current dynamic route (SET CDR). In each plot from the triplet (a– c), an asterisk and a square, sharing the same color, mark beginning and end of the abrupt switching phase in the device SET transition. Referring to plot (a), for the current trace associated to the initial condition, shown within a rectangular frame on the respective legend, specifically  $N_{\rm disc,0} = 5 \times 10^{25}$  m<sup>-3</sup>, the SET time  $t_{\rm SET}$  and the SET saturation time  $t_{\rm SET, sat}$  are clearly marked as abscissas of the asterisk and square markers, respectively.

versus the device current modulus  $|i_m|$  for a given negative bias value assigned to the voltage  $V_m$  across the physical stack. This novel graphic tool is intended to enable the application of the system-theoretic analysis method, centered on the DRM graphic tool, to data measured from device samples, in future research investigations, where a family of SET CDRs, one for each negative  $V_m$  value of interest, would be recorded to form a SET current dynamic route map (SET C-DRM).

Figure 4c depicts the CDR of the VCM cell for  $V_{\rm m} = -1$  V, as it descends from the device DAE sets in Equations (1) and (2). As it is the case under any negative DC voltage, the sign of the time derivative of the disc oxygen vacancy concentration (device current modulus) keeps positive for all admissible  $N_{\rm disc}$  $(|i_m|)$  values over a SET transition, as indicated by the eastward direction of the arrows superimposed on the SET SDR (SET CDR) from plot (b) ((c)) in Figure 4. This implies that the device may asymptotically exhibit one and only one possible steadystate behavior, sitting on its lowest admissible resistance state, as inferable from Figure 4a, provided the stimulus were not removed beforehand. With reference to Figure 4, processing the numerical data, extracted from all the DC stress SET tests, which resulted in the traces from Figure 4a, from the end of the pulse rise time, for each of the initial conditions the trajectory point ( $N_{\rm disc}$ ,  $dN_{\rm disc}/dt$ ) (( $i_{\rm m}$ ,  $|di_{\rm m}/dt|$ )) draws over time a path, which lies entirely on the SDR (CDR) from plot (b) ((c)), and terminates eventually on its rightmost location, where the device attains the lowest possible resistance state.

It is instructive to note that there exists a specific one-to-one function, which maps the disc oxygen vacancy concentration to the device current modulus for each negative DC voltage let fall across the physical stack. Such a function, which does not have a closed-form expression, but can nevertheless be numerically derived from the implicit Ohm law (Equation (2)), is highly nonlinear. This notwithstanding, the SET SDR and SET CDR, shown in Figure 4b,c, respectively, share common features. First of all, as anticipated earlier, the sign of the time derivative of the disc oxygen vacancy concentration (device current modulus) is positive throughout the admissible variation range for the disc oxygen vacancy concentration (device current modulus), as is the case under any other negative DC value assigned to the voltage across the physical stack. Importantly, moving from the lowest possible to the highest possible disc oxygen vacancy concentration (device current modulus), the SET SDR (CDR) of the VCM cell for  $V_m = -1 \text{ V}$ , as shown in Figure 4a(b), undergoes a monotonic increase up to a maximum, and decreases monotonically, thereafter. Moreover, the region to the left of the hump in the SET SDR (SET CDR) from plot (b) ((c)), where the positive-valued time derivative of the disc oxygen vacancy concentration (device current modulus) gets larger as  $N_{\rm disc}$  ( $|i_{\rm m}|$ ) increases, defines the domain, where positive feedback mechanisms, due to Joule heating effects, accelerate the device dynamics during the SET transition under  $V_{\rm m}$  = -1 V. On the other hand, the region to the right of the hump in the SET SDR (SET CDR) from plot (b) ((c)), where the positive-valued time derivative of the disc oxygen vacancy concentration (device current modulus) gets smaller as  $N_{

m disc}$  ( $|i_{

m m}|$ ) increases, defines the domain, where negative feedback mechanisms, due to the limiting action exerted by the series resistor, decelerate the device dynamics

during the SET transition under  $V_m = -1$  V. Now, as a further aspect of interest, if the trajectory point  $(N_{\text{disc}}, dN_{\text{disc}}/dt)$  ( $(|i_{\text{m}}|,$  $|di_m/dt|$ )), which is sampled directly at the end of the pulse rise time, when the voltage across the VCM cell is first found to be equal to -1 V, lies to the right of the hump, only negative feedback mechanisms affect the device SET transition, which may appear gradual throughout the DC stress SET test. Conversely, if this very same trajectory point lies to the left of the hump, then, at some stage, the device dynamics are accelerated by thermal effects, which explains why, in a scenario of this kind, the device is found to enter an abrupt switching regime, as defined in Equation (4). While, at first glance, with reference to the SET SDR from Figure 4b (the SET CDR from Figure 4c), one could conclude that, when  $N_{\text{disc}}$  ( $|i_{\text{m}}|$ ) visits points at positive/negative slope, the device undergoes abrupt/gradual switching transition, this is not always the case, according to the measure established via inequality in Equation (4). In order to clarify this point, for each of the initial conditions, from which the device enters an abrupt regime, as established by such inequality, the SET time  $t_{SET}$ , and, if it exists, the SET saturation time  $t_{\rm SET, \, sat}$ , are respectively marked along the associated SET SDR from Figure 4b as well as along the associated SET CDR from Figure 4c, similarly as indicated in Figure 4a, that is, through an asterisk and a square marker of relevant initial condition-dependent color (the color coding map, graphically illustrated as legend in Figure 4a, is reported for reference also adjacent to each of Figure 4b,c).

Very importantly, according to the nonlinear mapping, which relates  $N_{\rm disc}$  and  $|i_{\rm m}|$  under  $V_{\rm m}$  = -1 V, the current modulus, which corresponds to the disc oxygen vacancy concentration, at which the SET SDR from Figure 4b features a maximum, is approximately the same value as the abscissa of the maximum in the SET CDR from Figure 4c. With this in mind, let us now focus on any of the 13 initial conditions, from which the device is found to enter an abrupt regime, according to the measure from inequality in Equation (4), and follow the evolution of the respective disc oxygen vacancy concentration (current modulus) on the SET SDR (SET CDR) of Figure 4b(c). In each of these cases, the trajectory point ( $N_{\rm disc}$ )  $dN_{\rm disc}/dt$ ) (( $|i_{\rm m}|$ ,  $|di_{\rm m}/dt|$ )) first enters the path established by the SET SDR (SET CDR) from plot (b) ((c)) to the left of its hump. From that time instance, and while the trajectory point  $(N_{\rm disc}, dN_{\rm disc}/dt)$   $((|i_{\rm m}|, |di_{\rm m}/dt|))$  keeps to the left of the hump of the respective SET SDR (SET CDR),  $N_{

m disc}$  ( $|i_{

m m}|$ ) first experiences a slow increase, and then an abrupt upsurge. Importantly, the device keeps in the abrupt regime also during part or all of the descent of the trajectory point ( $N_{\text{disc}}$ ,  $dN_{\text{disc}}/dt$ )  $((|i_{

m m}|,\,|{

m d}i_{

m m}/{

m d}t|))$  along the route at negative slope to the right of the hump of the SET SDR (SET CDR) of Figure 4b(c), for ten and three of the 13 scenarios under consideration, respectively. This observation shows that the existence of a hump on the SET SDR (SET CDR), associated to a given negative DC voltage, constitutes a necessary condition for the device to undergo three main phases in the underlying SET process, namely two gradual transitions, separated by an abrupt one, provided the resistance state of the ReRAM device at the time, when the physical stack is first subject to the fixed negative voltage stimulus, corresponds to a disc oxygen vacancy concentration (device current modulus), which lies to the left of the maximum of the respective arrowed  $dN_{\rm disc}/dt$  versus  $N_{\rm disc}$  ( $|di_{\rm m}/dt|$  vs  $|i_{\rm m}|$ ) locus. However, for any scenario, where the disc oxygen vacancy concentration (device current modulus) is found to undergo an abrupt upsurge, the eventual evolution of the respective trajectory point ( $N_{\rm disc}$ ,  $dN_{\rm disc}/dt$ ) (( $|i_{\rm m}|$ ,  $|di_{\rm m}/dt|$ )) along the path at negative slope to the right of the hump on the SET SDR (SET CDR) does not constitute a sufficient condition for the appearance of a saturation in the response of the ReRAM device in the final phase of the DC stress SET test.

The deep system-theoretic analysis, presented in this section, enables to explain certain typical observations, related to the SET process in ReRAM cells, reported in the past by device physics researchers. [43] In particular, the SET transition in memory devices of this kind may appear gradually, even during the time interval, when the modulus of the current undergoes an abrupt upsurge, if the abrupt switching regime time span becomes comparable to the SET time, that is, equivalently, adopting the terminology introduced in ref. [43], the delay time. This happens when the VCM cell features a relatively-low resistance state, when a certain constant voltage of negative polarity is first applied across its two terminals. The following remark gains a deeper insight into this important aspect.

Remark 1: Despite inequalities in Equations (4)-(5) set a rigorous absolute measure for identifying an abrupt phase in the device resistance switching transition due to the application of a given negative DC pulse voltage across the ReRAM cell, whether, in a practical lab measurement, the change in the device resistance from a higher value to a lower one would appear sharp or gradual, to the eyes of an external observer, actually depends, crucially, on the ratio between the given ontransition time interval and the time elapsed since the beginning of the experiment. Let us gain a deeper understanding. From the implicit Ohm law in Equation (2), fixing the device voltage  $v_{\rm m}$  to a given negative value, as done here, each current modulus level  $|i_{\rm m}|$  is uniquely associated to one and only one value for the disc oxygen vacancy concentration  $N_{\rm disc}$ , and, as a result, to one and only one value for the time derivative of the disc oxygen vacancy concentration  $dN_{disc}/dt$ . With this in mind, as, under the given negative DC voltage input, the device current modulus increases from any positive value, say  $I_{m,1}$ , to any other one, say  $I_{m,2}$ , the device switching speed is unequivocally determined by the state Equation (1), for each choice of the initial condition, which drives the device current through the target transition range  $[I_{m, 1}, I_{m, 2}]$ . As a result, the time interval, which elapses as  $|i_{\rm m}|$  is subject to the desired increment, is the same for each of these initial conditions. As an example, with reference to Figure 4a, each of the 15 traces increases from  $I_{m,1} = 0.6$  mA to  $I_{m,2} = 0.8$  mA within a common time interval. However, to the eyes of an experimenter, this very same time interval appears shorter and shorter, the higher and higher is the resistance initially programmed into the ReRAM cell. This is because, as we move from the leftmost trace to the rightmost trace in Figure 4a, the device response time span, defined as the time interval, over which the device current modulus is subject to the given incremental transition, becomes smaller and smaller in comparison to the experiment time span, defined as the delay time of the onset of the transition under consideration as compared to the time of application of the SET pulse.

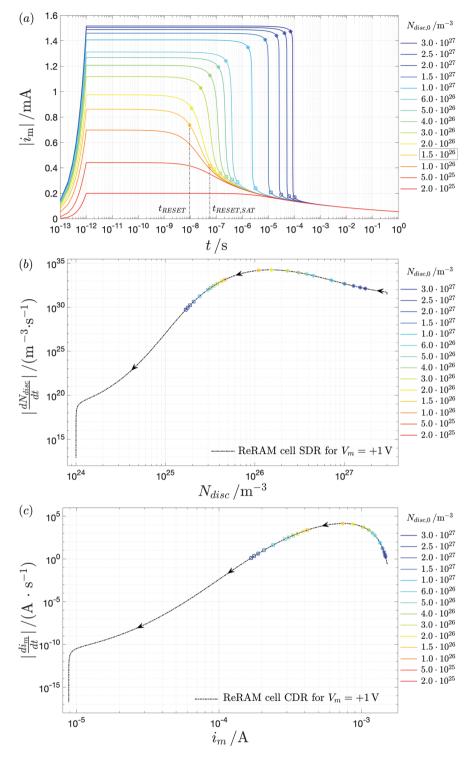

### 3.2.2. System-Theoretic Analysis of the RESET Process

A similar analysis, as carried out for a SET transition of the VCM cell in Section 3.2.1, is now performed under a DC stress RESET test. With reference to Figure 5a which illustrates the time evolution of the current  $i_{\rm m}$  as a positive voltage pulse of height 1 V, as specified for the simulations of Figure 3c is let to fall across the device terminals, for each of 14 different initial conditions, as indicated in the legend. A RESET SDR (RESET CDR) of the VCM cell, defined as the  $|dN_{disc}/dt|$  versus  $N_{disc}$  $(|di_m/dt| \text{ vs } |i_m| \equiv i_m) \text{ locus, and derived from the JART VCM v1}$ model, is shown in plot (b) ((c)) of the same figure for  $V_m = 1 \text{ V}$ . Note that, as it is the case under any positive DC voltage, let fall across the physical stack, the time derivative of the disc oxygen vacancy concentration (device current) keeps negative for all possible  $N_{\rm disc}$  ( $i_{\rm m}$ ) values throughout a RESET transition, as indicated by the arrows, pointing westward, drawn along the RESET SDR (RESET CDR) from Figure 5b(c). The strictly-negative polarity, which  $dN_{disc}/dt$  features under any positive DC stimulus, implies that, provided the stimulus were not removed over the course of the RESET transition, the VCM cell may asymptotically feature one and only one admissible steady-state behavior, sitting on its highest possible resistance state, which would happen way after the final time of 1 s in the simulations from Figure 5a. With reference to this plot, all the device current traces feature an initial fast increase to an initial condition-dependent level (the higher is  $N_{\text{disc}, 0}$ , and the larger is the increment in  $i_m$ ), as it was observed in the simulations of Figure 3c, as well as in the experiments of Figure 1d, during the pulse rise time. Subsequently, all traces feature a slow decrease at some initial condition-dependent pace (the descent in  $i_m$  is slower and slower as the resistance, initially programmed into the VCM cell, is lower and lower). After this phase, except for the three lowest initial conditions from the legend, the device enters an abrupt RESET switching regime, where, at each time instant t, its current decreases so significantly to satisfy the constraint

$$|di_{\rm m}/d\log_{10}(t)| \ge 10^{-3} \text{ As}^{-1}$$

(6)

In the proposed abrupt RESET switching regime measure the differentiation of the device current is made with respect to the base-10 logarithm of the time. This measure allows to monitor the slope of the device current versus time locus, when the horizontal axis is scaled logarithmically, as is the case for the traces in Figure 5a.

With reference to this plot, an asterisk marker indicates the first point in time, earlier referred to as RESET time  $t_{\rm RESET}$ , at which the inequality in Equation (6) holds true, for each of the 14 traces, except those associated to the three smallest initial conditions from the legend, where this condition is never met. Importantly, for all initial conditions, where the ReRAM device is found to enter an abrupt switching regime the higher is  $N_{\rm disc,\,0}$ , and the larger is the RESET time  $t_{\rm RESET}$ . Importantly,  $t_{\rm RESET}$  is found to span over four orders of magnitude in time, which, as compared to the multi-decade variation in the SET time, demonstrates the lower degree of nonlinearity of the RESET switching kinetics of the VCM cell relative to its SET switching kinetics. Preliminarily programming the device in

Figure 5. System-theoretic analysis of the JART VCM v1 model predictions of the device response to positive DC voltage excitations. a–c) Investigation of a DC stress RESET test, where the voltage across the VCM cell is supplied by a source, producing a pulse of height 1 V and rise time 1 ps, under 14 initial values for  $N_{\rm disc}$ , o, as specified in the common legend from either of the plots. a) Time evolution of the device current  $i_{\rm m}$ . b)  $|dN_{\rm disc}/dt|$  versus  $N_{\rm disc}$  locus of the VCM cell for  $V_{\rm m}=1$  V. In system-theory, an arrowed locus of this kind is known as a SDR. Since here the DC voltage across the ReRAM cell induces its RESET transition, a SDR of this kind is referred to as a RESET SDR. c)  $|di_{\rm m}/dt|$  versus  $i_{\rm m}$  locus of the VCM cell for  $V_{\rm m}=1$  V. An arrowed locus of this kind is a current-based variant of a RESET SDR, and is referred to as RESET current dynamic route (RESET CDR). In each of the three plots (a– c), an asterisk and a square, marked in a common color, respectively indicate the onset and the conclusion of the abrupt switching phase in the device RESET transition, as computed from the numerical simulation corresponding to the associated initial condition. With reference to plot (a), for the device current trace associated to the initial condition, shown within a rectangular frame on the respective legend, specifically  $N_{\rm disc}$ ,  $0=1.5\times10^{26}$  m<sup>-3</sup>, the RESET time  $t_{\rm RESET}$  and the RESET saturation time  $t_{\rm RESET}$ , sat are clearly marked as abscissas of the asterisk and square markers, respectively.

either of the three highest resistance states, which correspond to the lowest initial conditions in the range, indicated in the legend of Figure 5a, it is not possible to identify, clearly, a point in time, at which the modulus of the derivative of the current with respect to the time, expressed in logarithmic scale, attains the threshold of  $10^{-3}~{\rm As}^{-1}$ , as established by the inequality in Equation (6). Under these circumstances, the entire RESET switching process appears rather gradually, which allows to tune the VCM cell resistance finely in a potential experiment.

Differently from what is the case during the DC stress SET tests of Figure 4a, each trace, which hosts an asterisk marker in Figure 5a, eventually leaves the abrupt switching phase, entering a new gradual one. In fact, from the analysis of the time series of the device current in each of these RESET transition scenarios, an additional initial condition-dependent point in time may be detected (as indicated with a square marker), at which the inequality in Equation (6) is last satisfied. This time instant is referred to as RESET saturation time  $t_{RESET, sat}$ , because, thereafter, the ReRAM cell is found to enter a new gradual switching phase, referred to as RESET saturation regime, where further decrements in  $i_{\rm m}$  are limited by the cooling of the filament, due to the progressive reduction in the power dissipated in the physical stack. As a further aspect of interest, the duration of the abrupt switching regime, defined as  $t_{RESET, sat} - t_{RESET}$ depends crucially upon the resistance initially programmed into the device, and, particularly, increasing for larger values assigned to  $N_{\mathrm{disc, 0}}$ . As an additional note, differently from what happens during a SET transition (see Figure 4a), any trace from Figure 5a converges to the same solution well before the device shows a unique steady-state behavior, when the disc oxygen vacancy concentration  $N_{\text{disc}}$  attains the lower bound  $N_{\text{disc, off}}$  in its existence domain, and the ReRAM cell features the highest possible resistance. Section S4, Supporting Information, visualizes the time evolution of other physical variables of interest, specifically the filament temperature T, and the voltages  $\tilde{\nu}_{\rm m}$ , and  $v_{\text{contact}}$ , falling across core device and contact series resistance, respectively, as recorded during each of the numerical simulations, which resulted in the  $|i_m|$  versus t loci of Figure 5a.

Processing the numerical data in Figure 5a allows us to gain a deeper insight into the RESET switching transition of the device physical stack, preliminary initialized into any of the resistance states, inferable from the legend, in response to the aforementioned 1 V-high positive voltage pulse stimulus. The aim is to analyze the time evolution of the trajectory point ( $N_{\rm disc}$ ,  $|dN_{\rm disc}/dt|$ ) (( $i_{\rm m}$ ,  $|di_{\rm m}/dt|$ )) on the unique RESET SDR (RESET CDR) of the VCM cell, corresponding to a fixed unitary value assigned to the device voltage, from the first point in time, at which the source voltage  $v_{\rm s}$  attains its final value, that is, directly after the pulse rise time.

As was the case for any SET transition, for each positive DC voltage across the ReRAM device, there exists a specific one-to-one map between the disc oxygen vacancy concentration and the current through the physical stack. Despite the nonlinearity of the map, the RESET SDRs of Figure 5b and RESET CDRs of Figure 5c share common characteristics. First, the sign of  $dN_{\rm disc}/dt$  ( $dt_{\rm m}/dt$ ) is negative for all values, which  $N_{\rm disc}$  ( $t_{\rm m}$ ) may ever assume during the RESET transition. Importantly, moving from the highest possible to the lowest possible disc oxygen vacancy concentration (device current), the RESET SDR (RESET CDR) of

the VCM cell for  $V_m = 1$  V, as shown in Figure 5b(c), undergoes a monotonic increase up to a maximum, and decreases monotonically thereafter. Moreover, the region to the right of the hump in the RESET SDR (RESET CDR) from plot (b) ((c)), defines the domain, where positive feedback mechanisms, due to the series resistor-core memristor voltage division, inducing self-heating effects in the ReRAM cell, as the resistance of its physical stack progressively increases, accelerate the device dynamics during the RESET transition under  $V_{\rm m}=1$  V. On the other hand, the region to the left of the hump in the RESET SDR (RESET CDR) from plot (b) ((c)) defines the domain, where negative feedback mechanisms, due to the progressive decrease, which the power, entering the ReRAM cell undergoes, when the current through the physical stack drops more than the ongoing increase in the voltage between its terminals, decelerate the device dynamics during the RESET transition under  $V_m = 1 \text{ V}$ .

Now, if the trajectory point  $(N_{\rm disc}, |{\rm d}N_{\rm disc}/{\rm d}t|)$   $((i_{\rm im}, |{\rm d}i_{\rm m}/{\rm d}t|))$ , which is sampled directly at the end of the pulse rise time lies to the left of the hump, only negative feedback mechanisms affect the RESET transition, which may appear gradually throughout the DC stress RESET test. Conversely, if this very same trajectory point lies to the right of the hump, then, at some stage, the device dynamics are accelerated as a progressively larger portion of the stimulus bias voltage drops across the core memristor, which explains why, in a scenario of this kind, the device is found to enter an abrupt switching regime, as defined in Equation (6). While, at first glance, with reference to the RESET SDR (RESET CDR) from Figure 5b(c), one could conclude that, when  $N_{\rm disc}$   $(i_{\rm im})$  visits points at negative (positive) slope, the device undergoes an abrupt (a gradual) switching transition, this is not always the case, according to the measure established via inequality in Equation (6).

In order to clarify this point, for each of the initial conditions, from which the device enters an abrupt regime, established by the inequality in Equation (6), the RESET time  $t_{\rm RESET}$ , and the RESET saturation time  $t_{\rm RESET}$ , sat, are marked in the RESET SDR from plot (b) (RESET CDR from plot (c), similarly as indicated in plot (a), that is, through an asterisk and a square marker of relevant initial condition-dependent color. The same color coding map, graphically illustrated as legend in plot (a), is reported for reference also alongside each of plots (b) and (c).

Very importantly, according to the nonlinear mapping, which relates  $N_{\rm disc}$  and  $i_{\rm m}$  under  $V_{\rm m}=1$  V, the device current, which corresponds to the disc oxygen vacancy concentration, at which the RESET SDR from plot (b) features a maximum, is approximately the same value as the abscissa of the maximum in the RESET CDR from plot (c).

With this in mind, let us now focus on any of the 11 initial conditions, from which the device is found to enter an abrupt regime, and follow the evolution of the respective disc oxygen vacancy concentration (device current) on the RESET SDR (RESET CDR) of Figure 5b(c) directly after the pulse rise time. In each of these cases, the trajectory point ( $N_{\rm disc}$ ,  $|dN_{\rm disc}/dt|$ ) (( $i_{\rm m}$ ,  $|di_{\rm m}/dt|$ )) first enters the path established by the RESET SDR (RESET CDR) from plot (b) ((c)) to the right of its hump. From that time instant, and while the trajectory point ( $N_{\rm disc}$ ,  $|dN_{\rm disc}/dt|$ ) (( $i_{\rm m}$ ,  $|di_{\rm m}/dt|$ )) keeps to the right of the hump of the respective RESET SDR (RESET CDR),  $N_{\rm disc}$  ( $i_{\rm m}$ ) first experiences a slow descent, and then an abrupt decrease. Importantly, the device keeps in the abrupt regime also during part of the

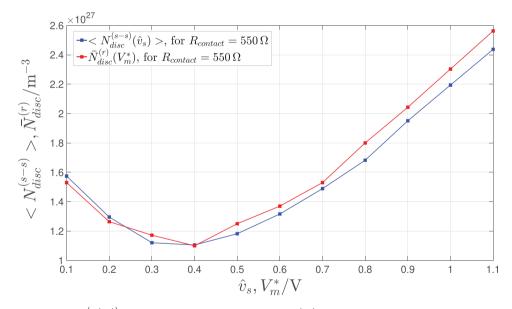

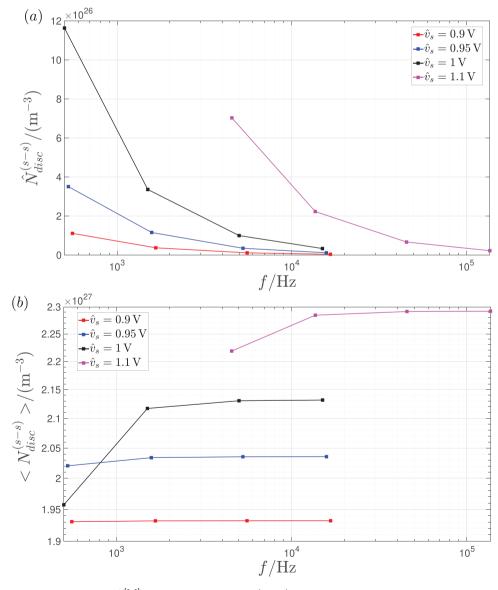

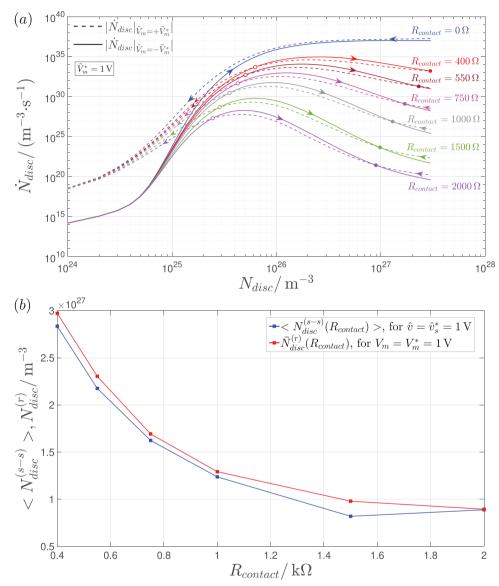

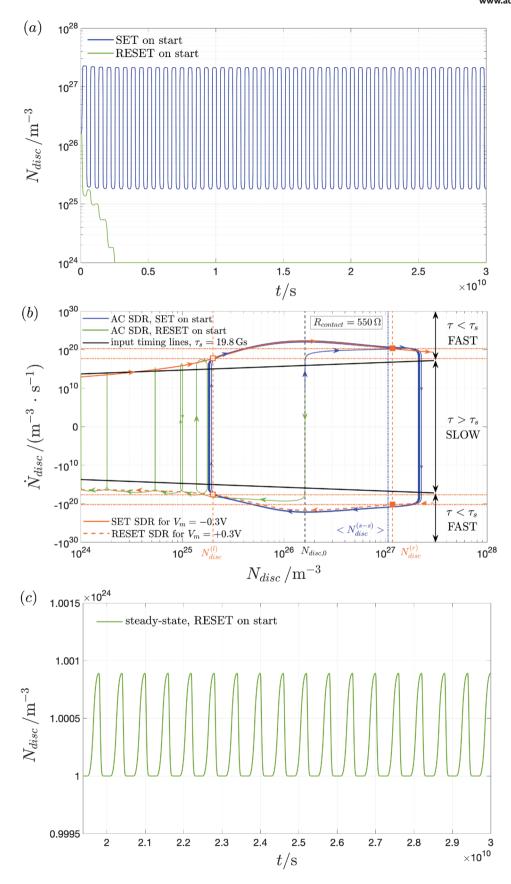

descent of the trajectory point  $(N_{\text{disc}}, |dN_{\text{disc}}/dt|)$   $((i_{\text{m}}, |di_{\text{m}}/dt|))$ along the route at positive slope to the left of the hump of the RESET SDR (RESET CDR) of Figure 5b(c) for each of the 11 scenarios under consideration. This observation shows that the existence of a hump on the RESET SDR (RESET CDR), associated to a given positive DC voltage, let fall across the VCM cell, constitutes a necessary condition for the device to undergo three main phases in the underlying RESET process, namely two gradual transitions, separated by an abrupt one, provided the resistance state of the ReRAM device, at the time, when the physical stack is first subject to the fixed positive voltage stimulus, corresponds to a disc oxygen vacancy concentration (device current), lying to the right of the hump. Moreover, as compared to the curvature around the respective maximum and the multi-decade modulation in  $dN_{\rm disc}/dt$  ( $|di_{\rm m}/dt|$ ) for the SET SDR (SET CDR) for  $V_{\rm m} = -1~{\rm V}$  from Figure 4b(c), the RESET SDR (RESET CDR) for  $V_{\rm m} = +1$  V from Figure 5b(c) is flatter in the region around the respective hump, which reduces the range of variation for  $|dN_{disc}/dt|$  ( $|di_m/dt|$ ) across the allowable set of values, which  $N_{\rm disc}$  ( $i_{\rm m}$ ) may ever assume over a RESET transition under the unitary bias voltage stimulus. This explains why, for any RESET transition scenario from Figure 5a, where the disc oxygen vacancy concentration (device current) is found to undergo an abrupt decrease, eventually a saturation in the response of the ReRAM device appears, before the device attains its highest possible resistance state. The thorough system-theoretic analysis, reported in this section, allows to explain phenomena observed in experimental RESET tests on ReRAM cells. Specifically, the RESET transition in memory devices of this kind may appear gradual, even over the time interval, when the current through the physical stack undergoes an abrupt decrease, provided the VCM cell features a relativelyhigh resistance state, when, first, a certain constant voltage of positive polarity is let fall across its two terminals, which ensures that the abrupt switching regime time span is comparable to the RESET time, that is, equivalently, adopting the terminology introduced in ref. [43], the delay time. In fact, the above remark on the impact of the time span of the experiment on the speed of the SET switching transition holds its validity for the RESET switching process as well. Particularly, for a given positive DC voltage  $V_{\rm m}$ , let fall across the VCM cell, the time necessary for observing a decrement in its current  $i_{\rm m}$  from any positive value, say  $I_{m, 1}$ , to any other one, say  $I_{m, 2}$ , is independent of the initial condition, which drives the device current through the desired transition range. However, whether, during a laboratory measurement, under the given positive bias voltage stimulus, the transition of the device current from the upper value to the lower one in the range  $[I_{m, 1}, I_{m, 2}]$  would appear gradual or abrupt to the eyes of an external observer depends critically upon the ratio between the experiment time span, that is, the delay time of the onset of the transition under focus, and the device response time span, defined as the time interval, over which the device current is subject to the target decrement. In fact, with reference to Figure 5a, the lower is the resistance, initially programmed into the ReRAM cell, and the higher is such a time span ratio, which explains why, to the eyes of an experimenter, the device response would appear faster.