## POLITECNICO DI TORINO Repository ISTITUZIONALE

High-Level Design of Precision-Scalable DNN Accelerators Based on Sum-Together Multipliers

Original

High-Level Design of Precision-Scalable DNN Accelerators Based on Sum-Together Multipliers / Urbinati, Luca; Casu, Mario R., - In: IEEE ACCESS. - ISSN 2169-3536. - ELETTRONICO. - 12:(2024), pp. 44163-44189. [10.1109/access.2024.3380472]

Availability: This version is available at: 11583/2987476 since: 2024-04-02T09:25:09Z

Publisher: IEEE

Published DOI:10.1109/access.2024.3380472

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

Received 27 February 2024, accepted 17 March 2024, date of publication 21 March 2024, date of current version 28 March 2024. Digital Object Identifier 10.1109/ACCESS.2024.3380472

## **RESEARCH ARTICLE**

# High-Level Design of Precision-Scalable DNN Accelerators Based on Sum-Together Multipliers

LUCA URBINATI<sup>®</sup>, (Graduate Student Member, IEEE), AND MARIO R. CASU<sup>®</sup>, (Senior Member, IEEE)

Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Turin, Italy Corresponding author: Luca Urbinati (luca.urbinati@polito.it)

ABSTRACT Precison-scalable (PS) multipliers are gaining traction in Deep Neural Network accelerators, particularly for enabling mixed-precision (MP) quantization in Deep Learning at the edge. This paper focuses on the Sum-Together (ST) class of PS multipliers, which are subword-parallel multipliers that can execute a standard multiplication at full precision or a dot-product with parallel low-precision operands. Our contributions in this area encompass multiple aspects: we enrich our previous comparison of SoA ST multipliers by including our recent radix-4 Booth ST multiplier and two novel designs; we extend the explanation of the architecture and the design flow of our previously proposed ST-based PS hardware accelerators designed for 2D-Convolution, Depth-wise Convolution, and Fully-Connected layers that we developed using High-Level Synthesis (HLS); we implement the uniform integer quantization equations in hardware; we conduct a broad HLS-driven design space exploration of our ST-based accelerators, varying numerous hardware parameters; finally, we showcase the advantages of ST-based accelerators when integrated into System-on-Chips (SoCs) in three different scenarios (low-area, low-power, and low-latency), running inference on MP-quantized MLPerf Tiny models as case study. Across the three scenarios, the results show an average latency speedup of 1.46x, 1.33x, and 1.29x, a reduced energy consumption in most of the cases, and a marginal area overhead of 0.9%, 2.5% and 8.0%, compared to SoCs with accelerators based on fixed-precision 16-bit multipliers. To sum up, our work provides a comprehensive understanding of ST-based accelerators' performance in an SoC context, paving the way for future enhancements and the solution of identified inefficiencies.

**INDEX TERMS** Deep learning, hardware accelerators, high-level synthesis, mixed-precision quantization, precision-scalable MAC unit, sum-together multipliers.

## I. INTRODUCTION

In the context of Deep Learning (DL) at the edge, quantization is an established method for reducing memory footprint and bandwidth, saving energy, and performing faster inference when dealing with Deep Neural Networks (DNNs) on resource limited devices [1]. Recently, there has been a growing interest in academia and industry towards Mixed-Precision Quantization (MPQ) [2]. This technique

The associate editor coordinating the review of this manuscript and approving it for publication was Mario Donato Marino<sup>(b)</sup>.

leverages the different sensitivity to quantization of each DNN layer [3], [4] to search for the optimal number of activation and weight bits for each individual layer, enabling accuracy vs latency and accuracy vs energy trade-offs [5].

To take advantage of MPQ, several Precision-Scalable (PS) multipliers, Multiply-and-Accumulate (MAC) units, and DNN accelerators have been recently proposed targeting Machine-Learning (ML) workloads [6], [7], [8], [9], [10], [11], [12]. In this paper, we focus on a particular family of PS multipliers called Sum-Together (ST). These are special reconfigurable subword-parallel multipliers that, depending

on the selected configuration, not only perform N multiplications in parallel among multiple low-precision operands, but also sum together the results of these N multiplications within the multiplier itself, i.e., without requiring external addition. At full precision, they perform N = 1 standard multiplications (e.g., on 16 bits), whereas at reduced precision they compute N = 2 or 4 parallel dot-products using the low-precision operands packed in the multiplier's inputs (e.g., operands on 8 or 4 bits). In other words, the bitwidth of the operands is inversely proportional to N (e.g., 16/N bits). ST multipliers are well-suited for integration within MAC units [6], [9]. They enable parallel multiplications of low-precision quantized data in a Single Instruction Multiple Data (SIMD) fashion and, at the same time, their sum together feature contributes to further speeding up MAC operations, by saving N--1 MAC additions compared to conventional MAC units. For this reason, ST-based PS MAC units have recently found application in layer-specific DNN hardware accelerators, providing MPQ support and speeding up the overall layer computation by a factor up to N [8], [10], [11].

The contributions of this paper in this field cover multiple aspects:

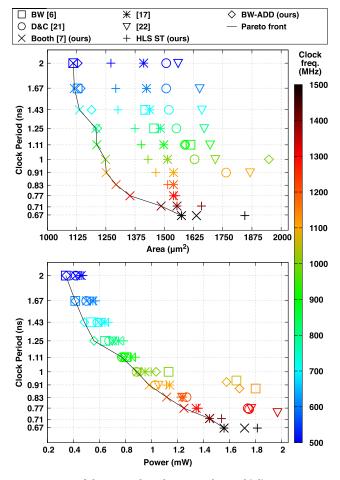

- We enrich our previous performance, power, and area (PPA) comparison of SoA ST multipliers [8] by introducing two novel designs. The first, which we name BW-ADD, is an improved Baugh-Wooley (BW) multiplier with a modified final adder that provides a shorter critical path than the original Ripple Carry Adder (RCA) used in [6]. The second, which we call HLS ST, is an ST multiplier derived from High-Level Synthesis (HLS). Indeed, one of our objectives is to evaluate the capability of HLS to generate a competitive ST multiplier in terms of PPA compared to manually-designed Register-Transfer Level (RTL) implementations. We also add to the PPA comparison our radix-4 Booth ST multiplier, recently presented in [7].

- We provide an extended explanation of the architecture of our ST-based PS hardware accelerators for 2D-Convolution (2D-Conv), Depth-wise Convolution (DW-Conv) and Fully-Connected (FC) layers, developed using HLS and previously proposed in [8], [10], and [11], respectively. Specifically, we present a comprehensive overview of our accelerators design flow, from C/C++ to final hardware implementation.

- 3) We also add the hardware support for uniform integer quantization (UIQ) [1], [13], [14] to quantize the output activations, which was not present in our previous accelerators' designs.

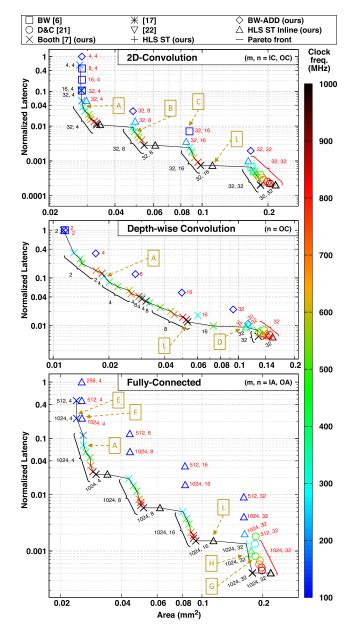

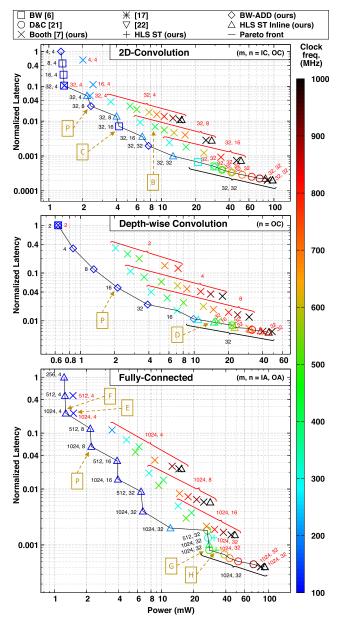

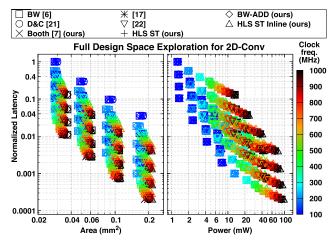

- 4) We perform an extensive design space exploration (DSE) for our ST-based accelerators using HLS. This involves varying many knobs, including parallelism, clock frequency, and especially the type of ST multiplier, which is a novelty of this work with respect to [8].

- 5) We illustrate the advantages achieved by our ST-based accelerators in terms of reduced latency and energy

consumption, comparing them to accelerators equipped with non-ST fixed-precision 16-bit multipliers, which we call *standard* accelerators and *standard* multipliers, respectively. For this assessment, we integrate the accelerators into System-on-Chips (SoCs) under three different scenarios (low-area, low-power, and lowlatency) and, as case study, we execute the models of the MLPerf Tiny benchmark [15], previously quantized in mixed-precision (MP) with a custom version of OKeras [16] for which we release the source code.

The results of the PPA comparison of ST multipliers showed that architectures having dedicated multipliers for each precision configuration tend to be less area-efficient than those employing a single but reconfigurable multiplier. Moreover, there is not a single winner that satisfy all PPA scenarios, but rather a set of optimal ST multipliers depending on the specific PPA constraints.

The results of the execution of the four MP-quantized MLPerf Tiny networks, using SoCs integrating ST-based accelerators tailored to different PPA scenarios (i.e., low-area, low-power, and low-latency), revealed: an average inference latency speedup, across the four models, of 1.46x, 1.33x, and 1.29x, respectively; a reduced average energy consumption, in most of the cases; and a marginal area overhead compared to SoCs equipped with standard accelerators.

The article is structured as follows. In Sec. II we present the related work, whereas in Sec. III we provide some background on DNN quantization, UIQ and the four MLPerf Tiny models. In Sec. IV we describe the concept of ST multiplier, we outline the architectures of the SoA ST multipliers, and we present the newly proposed ones. In Sec. V we detail the working principle and hardware architecture of our ST-based DNN accelerators, whereas in Sec. VI we describe the accelerators design flow. Finally, in Sec. VII we present the results in three parts: in the first we compare the ST multipliers in terms of PPA; in the second we report the Pareto-optimal accelerators, resulting from the HLS-driven DSE, in Latency vs Area and Power vs Area spaces; in the last we showcase the achievable latency speedup and energy reduction of the ST-based accelerators when running inference on MP-quantized MLPerf Tiny models, against standard accelerators.

## **II. RELATED WORK**

Although the definition of ST mode was introduced with the subword-parallel BW ST multiplier of [6], earlier works already proposed reconfigurable multipliers that support both single high-precision multiplications and parallel lowprecision dot-products.

The authors of [17] and [18] introduce SIMD extensions to the Instruction Set Architecture (ISA) of a RISC-V processor featuring a multiplication unit that behaves like an ST multiplier.

In [19], a general-purpose systolic array for DL is proposed. It is made of reconfigurable Fusion Units (FUs) that exploit low-precision multipliers by dynamically merging or

keeping their results separate. The architecture of these FUs falls within the *divide-and-conquer* (D&C) category, as per the taxonomy outlined in [9]. To this category also belong the optimized versions in [12] and [20], and their ancestor in [21].

In [22], the authors present a reconfigurable fixed-point multiplier originally designed for digital signal processing (DSP) applications.

In [9], various PS MAC unit (PSMAC) architectures are benchmarked and categorized in subword-parallel, D&C and bit-serial. However, in [6] and [19] are the only ST-based PSMACs considered here. In [8], instead, we compared all the main previously described SoA ST multipliers in PPA.

Recently, we have also contributed to the SoA of ST multipliers with a subword-parallel radix-4 Booth architecture that requires a light-weight reconfiguration logic [7].

Regarding ST-based DNN accelerators, there are a few examples in the literature: in [19] the authors proposed a general-purpose systolic array architecture, in [6] the authors describe their implementation of an FC kernel, whereas we derived 2D-Conv [11], DW-Conv [10] and FC [8] layer-specific accelerators using an HLS flow. In particular, in [8] we also carried out a DSE varying several hardware knobs, from clock frequency to HLS directives, to explore a wide range of Pareto-optimal solutions in area, power or latency. The authors of [9] and [12] have already conducted an exhaustive comparison of various PS hardware accelerators, including [6], [19], [23], [24], [25], and [26]. To the best of our knowledge, no other works have focused on employing HLS techniques for the development of ST-based hardware accelerators in general.

In this work, we enrich the SoA portfolio by introducing two novel ST multipliers (a BW multiplier with a modified final adder and an ST multiplier derived from a functional C/C++ description by an HLS tool) and we perform a comprehensive PPA analysis of all the SoA ST multipliers. We then derive ST-based PS DNN accelerators, like in [8]; however, a distinctive feature of our work is the support for UIQ for the quantization of the final result, which is not mentioned in any of the previously cited accelerators. In this regard, we propose an accelerator design flow that includes minimizing the bitwidths of the fixed-point variables required by the UIQ formulas. We also expand our previous DSE [8] by introducing new hardware knobs. One of these is the selection of the type of ST multiplier inside the accelerators' MAC units, which can be chosen among all the manually-designed RTL descriptions of SoA ST multipliers (like in [8]), and also among the ST multipliers inferred by the HLS tool from a high-level description. Furthermore, we show the latency and energy benefits of ST-based accelerators, against equivalent accelerators based on standard multipliers, when running entire MP-quantized DNNs. Such comparison, except for our previous work that focused solely on isolated DNN layers [10], [11], has not been extensively examined in the literature.

## **III. BACKGROUND**

## A. DEEP NEURAL NETWORKS' QUANTIZATION

The quantization of DNNs is now a common practice that decreases the numerical precision of weight parameters and activation values of neural networks layers. This process reduces the model size, lowering memory requirements to store weights and activations, as multiple low-precision feature maps and weights can be efficiently packed into the same memory word [14]. For the same reason, it also reduces data transfers costs. Additionally, quantization can improve inference latency, throughput and energy by taking advantage of high-throughput integer instructions, such as SIMD instructions in microprocessors [18], or specialized hardware operators like subword-parallel ST multipliers [7].

In this paper we focus on UIQ, even though various other quantization techniques exist [1]. This choice is driven by the simple mathematical formulation, the availability in common ML frameworks (e.g., TensorFlow Lite), its efficient mapping on existing hardware (e.g., on 8-bit microcontrollers), and thus its widespread adoption on embedded devices for non-extreme quantization (> 2 bits) [1], [13], [27]. Moreover, when it comes to ASIC implementation, integer/fixed-point math pipelines are more efficient in terms of silicon area and power consumption when compared to floating-point (FP) ones [28], not to mention the faster execution times. In the following, we introduce the UIQ mathematical background in the context of DNNs, borrowing some definitions from [13] and [14]. Notice that, since we target ST-based accelerators only for the inference phase of DNNs, our focus is only on UIO for inference, and not for training.

## 1) UNIFORM INTEGER QUANTIZATION

Given a set of real numbers in the *real range*  $[\alpha, \beta]$  (e.g., a tensor with a high-precision FP format like FP32), UIQ maps each  $x \in [\alpha, \beta]$  to an integer value  $x_q \in [\alpha_q, \beta_q]$  represented uniformly on *b* bits, where  $[\alpha_q, \beta_q]$  is the *quantized range*: for asymmetric or symmetric signed integers it is equal to  $[-2^{b-1}, 2^{b-1}-1]$  or  $[-2^{b-1}-1, 2^{b-1}-1]$ , respectively; for unsigned integers it is  $[0, 2^b - 1]$ . The process of quantization is defined as:

$$x_q = \operatorname{clip}\left(\operatorname{round}\left(\frac{1}{s}x + z\right), \alpha_q, \beta_q\right)$$

(1)

where *s* is the *scaling factor*, *z* is the *zero-point* (i.e., the integer value to which the real value zero is exactly represented), *round* is the rounding function (e.g., round-to-nearest), and *clip* keeps the output range within the quantized range by saturating the outliers. In turn, *s* and *z* are defined from the chosen real and quantized ranges as:

$$s = \frac{\beta - \alpha}{\beta_a - \alpha_a} \tag{2}$$

$$z = \operatorname{round}\left(\frac{\beta\alpha_q - \alpha\beta_q}{\beta - \alpha}\right) \tag{3}$$

The opposite operation, which brings back  $x_q$  to the real range, is defined as:

$$\hat{x} = s(x_q - z) \tag{4}$$

where  $\hat{x}$  is the closest real value (but not necessarily equal) to the original *x*, because rounding and clipping functions may introduce an irrecoverable error.

The quantization mapping discussed so far, with asymmetric ranges and  $z \neq 0$ , is known as *affine* quantization. Instead, when both ranges are symmetric, z becomes zero and (1) performs only the scale transformation. In this case, the quantization mapping is commonly known as *scale* or *symmetric* [29] quantization. Moreover, when s is a unique scalar value for all the channels of a tensor, quantization is referred to as *per-layer*; instead when s is a one-dimensional vector of scalars, each corresponding to a different channel of a tensor, quantization is called *per-channel*.

## 2) INTEGER-ONLY DNN KERNELS

Now consider the expression of an FC layer:

$$Y_{k} = b_{k} + \sum_{c=1}^{C} X_{c} W_{c,k} \quad \forall k \in [1, K]$$

(5)

where  $X \in \mathbb{R}^C$  is the input vector of neurons,  $W \in \mathbb{R}^{K \times C}$ is the weight matrix,  $b \in \mathbb{R}^K$  is the bias array,  $Y \in \mathbb{R}^K$ is the output array, C and K are the number of input and output activations processed by the FC layer, respectively. By applying (4) to each of the four real variables in (5), setting their own quantized ranges a priori, and moving the quantized output array  $Y_{q,k}$  to the left hand side, we obtain the quantized FC expression valid for the *k*-th output activation:

$$Y_{q,k} = \underbrace{z_Y}_{(a)} + \underbrace{\frac{s_b}{s_Y}(b_{q,k} - z_b)}_{(b)} + \underbrace{\frac{s_X s_W}{s_Y}}_{(c)} \left[ \underbrace{\left(\sum_{c=1}^C X_{q,c} W_{q,c,k}\right)}_{(c)} - \underbrace{\left(z_W \sum_{c=1}^C X_{q,c}\right)}_{(d)} - \underbrace{\left(z_X \sum_{c=1}^C W_{q,c,k}\right)}_{(c)} + \underbrace{Cz_X z_W}_{(f)} \right]}_{(f)}$$

$$\forall k \in [1, K]$$

(6)

where  $X_q$ ,  $W_q$ ,  $b_q$ ,  $Y_q$  are the integer values;  $s_X$ ,  $s_W$ ,  $s_b$ ,  $s_Y$ are the scaling factors; and  $z_X$ ,  $z_W$ ,  $z_b$ ,  $z_Y$  are the zero-points, associated with X, W, b, Y, respectively. Term (c) in (6) is the integer dot product, i.e., the core of the computation, instead term (d) introduces an overhead that causes a performance penalty. Both of them must be computed online because they depend on  $X_q$ , which is known only at runtime. On the contrary, terms (a), (b), (e), and (f) are constant, thus can be computed offline. Notice that in case of scale quantization for weights and affine quantization for activations, which is a common practice in the literature [13], [14],  $z_W$  and  $z_b$  become null, and so also terms (d) and (f), while (b) simplifies. This is also our assumption in this work. The result of (6), before being assigned to  $Y_q$ , is also rounded and clipped to fit the desired output quantized range of  $Y_q$  (not shown in the formula for better readability).

The mathematical derivations of the integer-only kernels for 2D- and DW-Conv closely follow that of FC. We report them in Appendix A. Hereafter, we will refer to (14), (16), and (6) as the *UIQ formulas*.

Now we focus on the integration of the rectified linear unit (ReLU) into the expressions of the integer-only kernels. In fact, to optimize inference on DNNs in embedded devices, some adjacent DNN layers can be typically combined into a single one. This operation, called Layer Fusion, is usually performed between convolutional/fully-connected layers and the Batch Normalization (BN) or activation layers (e.g., ReLU), and can be applied to both FP and quantized models. Since our ST-based accelerators support layer fusion with ReLU, as elaborated in Sec. V-B, we explain here the fusion process considering an FC layer with a subsequent ReLU layer. We choose ReLU because it stands out as the most common activation function when it comes to efficient hardware implementations of DNNs. By applying the ReLU non-linearity to the FP output  $Y_k$  of (5), we derive the expression of the FP FC-ReLU fused layer:

$$R_k = \begin{cases} 0 & \text{if } Y_k < 0\\ Y_k & \text{if } Y_k \ge 0 \end{cases} \quad \forall k \in [1, K]$$

(7)

where  $R_k$  is the *k*-th output of the ReLU layer. By repeating the same steps that brought to the derivation of (6) from (5) applying (4) to each real variable of (7), setting their quantized ranges, and moving the quantized ReLU output  $R_{q,k}$  to the left hand side—we obtain the quantized FC-ReLU fused layer valid for the *k*-th ReLU element:

$$R_{q,k} = \begin{cases} z_R & \text{if } T < 0\\ z_R + s_R \cdot T & \text{if } T \ge 0 \end{cases} \quad \forall k \in [1, K] \quad (8a)$$

where

$$T = s_b(b_{q,k} - z_b) + s_X s_W \left[ \left( \sum_{c=1}^C X_{q,c} W_{q,c,k} \right) - \left( z_W \sum_{c=1}^C X_{q,c} \right) - \left( z_X \sum_{c=1}^C W_{q,c,k} \right) + C z_X z_W \right].$$

(8b)

$s_R$  and  $z_R$  are the scaling factor and the zero-point associated to  $R_{q,k}$ , whereas all the other variables are the same of those that appear in (6). Notice that  $R_{q,k}$  undergoes a roundand-clip operation, not shown for clarity in (8), to fit into the desired quantized range of the ReLU layer.

The expressions for the quantized 2D-Conv-ReLU and DW-Conv-ReLU fused layers can be obtained through the same steps shown here for the quantized FC-ReLU.

## **B. MLPERF TINY BENCHMARK**

The Machine Learning Performance Benchmark (MLPerf) is a widely recognized set of benchmarks in the field

of ML created by the collaborative effort of more than fifty organizations from both academia and industry [15]. In particular, the *Tiny* benchmark is a suite of four lightweight ML models representing real-world applications: Visual Wake Words (VWW), Image Classification (ImgClass), Keyword Spotting (KS), and Anomaly Detection (AD). MLPerf Tiny was designed to assess the performance of edge devices and ultra-low-power tiny ML systems with a limited energy, memory and/or computational power budget (such as mobile phones, microcontrollers, Internet of Things devices), by measuring accuracy, latency and energy during inference on those four ML models. In this respect, MLPerf Tiny is also a competition that encourages innovation in the field of Tiny ML [30]. For these reasons, each application not only comes with its own dataset for development and testing, but also with a dedicated performance evaluation dataset (Perf test set).

## 1) VISUAL WAKE WORDS

The VWW dataset [31] is a collection of  $10961996 \times 96$  RGB images which contain persons or not-persons, derived from the MSCOCO 2014 dataset [32]. The use-case of this dataset is for a device to wake up when a person is present, covering smart doorbell and occupancy applications. The model to use with this dataset is a smaller version of MobilenetV1, [33] that we define *MobileNetV1Tiny*.

## 2) IMAGE CLASSIFICATION

The ImgClass benchmark uses the CIFAR-10 dataset [34], which consists of 60000  $32 \times 32$  RGB images belonging to 10 unique classes of 6000 images each. The use-case is for compact vision systems, including manufacturing, Internet-of-Thing sensor nodes, and autonomous agents and vehicles. The model to use is a custom ResNetV1 [35] that we define *ResNetV1Tiny*, which has no pooling layer after the first convolutional layer, fewer residual stacks, and lower dimension of filters and convolution strides than the original ResNetV1.

#### 3) KEYWORD SPOTTING

The KS benchmark uses a large collection of English words, pronounced by persons with various accents, and derived from the Speech Commands v2 dataset [36]. It contains twelve classes: ten with keywords (down, go, left, no, off, on, right, stop, up, yes), one with background noises and one with silence. The use-case is for human-machine interaction, including wakeword detection and remote control of smart devices by voice. The benchmark's target network is the small Depth-wise Separable Convolutional Neural Network (*DS-CNN*) of [37].

#### 4) ANOMALY DETECTION

This benchmark uses one of the six machine types present in the DCASE2020 competition's dataset [38], the toy-car machine type (ToyADMOS [39]), which contains singlechannel 10-seconds length audio samples recorded from

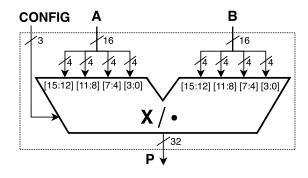

**FIGURE 1.** Reference ST multiplier, modified from [7]. The 16-bit inputs (A and B) are partitioned in 4-bit chunks to enable multiple operations, as defined by the 3-bit configuration input (*CONFIG*) and shown in Table 1. The  $X/\cdot$  symbol indicates that the multiplier is capable of multiplication and *dot-product* operations, depending on the configuration.

**TABLE 1.** Supported precision configurations and operations of the reference ST multiplier of Fig. 1. The last three configurations correspond to dot-product operations at low precision.

| CONFIG          | ST multiplier's output                                                                                                                                                  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16×16<br>(000b) | $P_{[31:0]} = A_{[15:0]} \times B_{[15:0]}$                                                                                                                             |

| 16×8<br>(100b)  | $P_{[31:0]} = A_{[15:0]} \times B_{[7:0]}$                                                                                                                              |

| 8×8<br>(010b)   | $P_{[16:0]} = A_{[15:8]} \times B_{[7:0]} + A_{[7:0]} \times B_{[15:8]}$                                                                                                |

| 8×4<br>(011b)   | $P_{[16:0]} = A_{[15:8]} \times B_{[3:0]} + A_{[7:0]} \times B_{[11:8]}$                                                                                                |

| 4×4<br>(001b)   | $ \begin{array}{c} P_{[9:0]} = A_{[15:12]} \times B_{[3:0]} + A_{[11:8]} \times B_{[7:4]} + \\ A_{[7:4]} \times B_{[11:8]} + A_{[3:0]} \times B_{[15:12]} \end{array} $ |

seven different toy cars (1000 each) mixed with environmental noise. The use-case is early detection of machine anomalies, a common industrial problem. The model of this benchmark is the reference implementation of DCASE2020 which is an FC-based autoencoder [38] (thus, we name it *FC-AutoEncoder*). Differently from the other MLPerf Tiny models, the main metric used in AD is not accuracy, but the Area Under The Receiver Operating Characteristics Curve (AUC).

## **IV. SUM-TOGETHER MULTIPLIERS**

The new ST multipliers that we introduce, as well as all the others that we analyze in this work, have I/O signals and behave as the reference component described in Fig. 1 and Table 1. Depending on the *CONFIG* configuration signal, this can perform one  $16 \times 16.16 \times 8$  multiplication, or two  $8 \times 8.8 \times 4$  or four  $4 \times 4$  dot-products in parallel, using the signed operands packed in the 16-bit inputs *A* and *B*. Depending on the configuration, a subset or the entire 32 bits of the multiplier's output *P* contain the operation result.

We focus on these precisions for the following reasons. In applications that require utmost accuracy, a common choice is to use 16 bits to quantize activations and weights. Some examples are safety-critical applications, such as image segmentation in foggy environments for autonomous driving [5]; others are image processing applications that work with high-resolution satellite images, or high dynamic range (HDR) images and super-resolution [27]. 8 bits is the default precision to quantize DNNs while avoiding performance degradation [27] and is therefore the most commonly used. When smaller bitwidths for inputs and weights are needed, quantization techniques targeting 4 bits already provide an acceptable tradeoff between model size reduction and retained performance for most applications [1], [40]. Instead, when dealing with extreme low-bit quantization (< 4 bits), existing methods incur a serious accuracy loss compared to the baseline, unless very extensive tuning and hyperparameter search is performed. Hence, this is still an active line of research [1]. In light of these motivations, we work with ST multipliers that support operands with precision between 16 and 4 bits.

Regarding the asymmetric configurations (i.e.,  $16 \times 8$  and  $8 \times 4$ ), we support them because they enable efficient packing of lower-precision operands, such as DNN weights, without compromising the precision of other operands, like DNN activations. Thus, they contribute to reducing the memory footprint of ML models. These configurations are used in SoA ML accelerators and processors [9], [18], and can also be found in commercial ML frameworks such as TFLite Micro.<sup>1</sup>

In the following, we first describe the architectures of the SoA ST multipliers as proposed in the literature and emphasize the differences between these and our reimplemented versions. Indeed, since the original SoA ST multipliers support a broad range of bitwidths for input and weights, we introduce minor modifications to align their configurations with the reference ST mentioned in Table 1. This is important to guarantee fair comparisons in all our experiments of Sec. VII. Lastly, we present the two newly proposed ST multipliers.

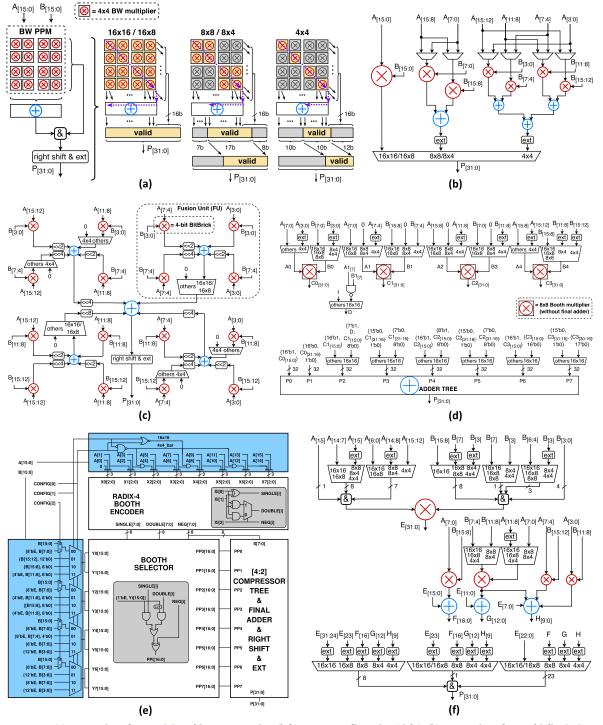

## A. SOA ST MULTIPLIERS

The original subword-parallel BW multiplier of [6] is composed of a reconfigurable partial product matrix (PPM) and a final RCA [41]. The PPM can be reconfigured to compute one  $16 \times 16$  multiplications or 16/m dot-products at m = 8, 4, or 2 bit precision in parallel. Our re-implementation of [6] (made with a structural RTL description) is reported on the left side of Fig. 2(a). From top to bottom, it has the same architecture of the original version. We also draw, for clarity, the output concatenation block (&), which merges the least significant output bits coming from the PPM with the most significant ones exiting from the final adder. However, in our version we introduce the following modifications. First, we remove the 2-bit support from the PPM, since we use precision between 4 and 16 bits as motivated before. This can be seen from the precision of the main building block of the PPM, which is a  $4 \times 4$  BW multiplier. Second, in low-precision configurations, we right shift the final output to the least-significant bit (LSB) position, sign-extending it to 32 bits (right shift & ext block). On the right side of Fig. 2(a), we illustrate how the PPM is reconfigured in the five operating modes of Table 1. In the  $16 \times 16$  and  $16 \times 8$  modes, all the PPs of the PPM contribute to the multiplier's output P and the result is represented on 32 bits, making valid-i.e., yellow in Fig. 2(a)—the entire result *P*. At lower precision, only the yellow PPs on the left-to-right diagonal of the PPM remain active and behave like two  $8 \times 8$  ( $8 \times 8 / 8 \times 4$  in Fig. 2(a)) or four  $4 \times 4$  ( $4 \times 4$  in Fig. 2(a)) BW multipliers, respectively. These PPs produce the valid (vellow) output bits of P, which are less than 32 in this case and require the alignment to the LSB position. The remaining grey PPs are gated, using AND gates, and generate the invalid (grey) output bits.

The multiplication unit of RI5CY [17], a RISC-V processor featuring a SIMD ISA extension, comprises a standard 32-bit integer multiplier, a 32-bit fixed-point multiplier and two subword-parallel dot-product units. These units accept two 16-bit or four 8-bit operands (packed in one 32-bit register) and accumulate the 32-bit result in one cycle, hence performing simultaneously up to four multiplications and accumulations. The architecture of the two dot-product units consists of either two 17-bit multipliers or four 9-bit multipliers, respectively, followed by a compression tree. In [18], the same authors extend the multiplication unit with other two subword-parallel dot-product units supporting 4- and 2-bit operands, respectively. They also added the ISA support for some asymmetric configurations  $(8 \times 4, 4 \times 8 \text{ and } 16 \times 2)$ . In this work, we implement the high-precision fixed-point multiplier and the two low-precision dot-product units of [17] as three mutually exclusive datapaths in a single design, scaling their precision to 16, 8 and 4 bits, respectively. Our re-implementation, illustrated in Fig. 2(b), uses a behavioral RTL description, as the authors of [17] declared that it gives the synthesizer the maximum optimization freedom.

The Fusion Unit of Bit Fusion [19] dynamically composes and decomposes 2-bit multipliers (called BitBricks) through a shift-and-add logic. It supports one  $8 \times 8$ , two  $4 \times 8$ , four  $4 \times 4$ , four  $2 \times 8$ , eight  $2 \times 4$ , sixteen  $2 \times 2$  input/weight multiplications in one clock cycle. Several optimizations to the original work of [19] are proposed in [12] and [20], which reduce complexity and reconfigurability overhead of the shift-and-add logic at the expense of a lower number of supported input/weight precisions  $(2 \times 2, 4 \times 4, 8 \times 8)$ . However, the ancestor of all these D&C architectures is the reconfigurable and parallel inner-product processor of [21]. This uses larger BitBricks on 4 or 8 bits and a higher input precision. In fact, each of the two input operands can accommodate one 64-bit, four 32-bit, sixteen 16-bit, or sixtyfour 8-bit items. It also maintains a fixed bitwidth for the two input operands, ensuring a constant memory bandwidth

<sup>&</sup>lt;sup>1</sup>An example of a TFLite Micro kernel for 2D-convolution supporting asymmetric configurations: https://github.com/tensorflow/tflitemicro/blob/main/tensorflow/lite/micro/kernels/conv.cc. Accessed on: Jan 19, 2024.

FIGURE 2. (a) Our version of BW ST [6]: architecture overview (left), PPM reconfiguration (right). (b) Our version of ST multiplier [17]: 16-bit high-precision multiplier (left), 8-bit and 4-bit low-precision dot-product units (middle, right). (c) Our version of D&C ST [21]: four FUS with four 4-bit BitBricks each, interconnected by shift-and-add logics. (d) Our version of ST multiplier [22]: four 8-bit Booth multipliers interconnected by muxes ending with an adder tree. (e) Radix-4 Booth ST (as in [7]): reconfiguration logic (blue), 16-bit Booth multiplier (white and gray). (f) HLS ST derived from HLS (proposed in this paper): four multipliers and three adders interconnected by a network of muxes and concatenations.

across different configurations. This contrasts with the D&C architectures in [12], [19], and [20], which suffer from memory bandwidth explosion at reduced precision, as noted in [9]. Among these D&C ST multipliers we implement the one from [21] for a fair comparison with the other

SoA ST multipliers on an equal memory bandwidth basis, avoiding the problem of bandwidth explosion. In particular, we re-implement it with 4-bit BitBricks to support 16, 8 and 4-bit precision, as shown in Fig. 2(c): four FUs based on four 4-bit BitBricks each, interconnected by shift-and-add

logic. We also right-shift its output to the LSB position and sign-extend it to 32 bits in low-precision modes (*right shift & ext* block as in [6]).

The reconfigurable fixed-point multiplier of [22] targets DSP applications and consists of four 16-bit Booth multipliers (without final adder), a configurable partial-products compression array and three configurable 33-bit adders. It supports symmetric (one  $32 \times 32$ , two  $16 \times 16$  or four  $8 \times 8$ ) and asymmetric (two  $16 \times 32$ ) signed/unsigned multiplication operations, and dot product/double dot product operations (one or two  $16 \times 16 \pm 16 \times 16$  with saturation, one or two  $16 \times 16 \pm 16 \times 16.16$  without saturation, and one  $8 \times 8.8 \times 8 + 8 \times 8.8 \times 8$ ). In our version of [22], we remove the extra logic that is not strictly necessary to implement the reference ST multiplier behavior, such as the saturation logic or the subtraction in the dot-products. Next, we change the way the dot product is computed for all precisions. For example, in configuration  $8 \times 8$ we swap the lower part with the upper part of operand B: A[15:8]×B[15:8]  $\pm$  aL[7:0]×bL[7:0] of [22] becomes  $A[15:8] \times B[7:0] + A[7:0] \times B[15:8]$ , as reported in Table 1. We also scale down maximum and minimum precision to 16 and 4 bits, respectively. The resulting architecture, shown in Fig. 2(d), features four 8-bit Booth multipliers connected by a network of multiplexers ending with an adder tree.

The subword-parallel radix-4 Booth architecture of [7] already supports operands at 16, 8, and 4-bit precision, as the reference ST multiplier in Table 1. As illustrated in Fig. 2(e), it is composed of a lightweight reconfiguration logic (in blue) placed between the two input operands and a standard 16-bit Booth multiplier. The latter, drawn in white and gray, features a Wallace's reduction tree with 4:2 compressors and a Carry Propagate Adder with Prefix Network [41]. We implement the architecture of this Booth ST multiplier with a structural description as in our original paper [7].

At last, within all SoA ST multipliers that do not natively support the asymmetric configurations  $16 \times 8$  and  $8 \times 4$ (i.e., [6], [17], [21]), we add a sign-extension logic (not shown in Fig. 2 for better readability) that extends the lower precision operand *B* to either 16 or 8 bits before the actual multiplication operation. For this reason, zero-padding of the low-precision operands is not necessary in any configuration, as these operands always fully utilize all the parallelism of the multipliers' inputs *A* and *B*.

As a final note, we implement all of these SoA ST multipliers as signed multipliers.

## B. BW-ADD: A BAUGH-WOOLEY ST MULTIPLIER WITH AN IMPROVED FINAL ADDER

In light of the results of our previous work [7], [8], we observe that the BW ST multiplier [6] is particularly area-efficient at clock frequencies lower than 600 MHz. At higher frequencies, the long diagonal critical path of the BW array and the carry chain of the final 16-bit RCA, highlighted by the purple dotted line in Fig. 2(a), are responsible for a significant area degradation [8], since the

#### LISTING 1. The C/C++ source code of the HLS ST multiplier.

| ı#ir  | nclude <ac_int.h></ac_int.h>                               |

|-------|------------------------------------------------------------|

| 2     |                                                            |

| 3 int | :32 st_multiplier_function(uint3 CONFIG,                   |

| 4     | int16 A, B) {                                              |

| 5 ir  | nt32 P;                                                    |

| 6 if  | f (CONFIG == 4) { // 16x8                                  |

| 7 E   | <pre>P = A*B.slc&lt;8&gt;(0);</pre>                        |

| 8 }   | else if (CONFIG == 2) { $// 8x8$                           |

| 9 E   | P = A.slc<8>(8)*B.slc<8>(0) + A.slc<8>(0)*B.slc<8>(8);     |

| 10 }  | else if (CONFIG == 3) { // 8x4                             |

| 11 E  | P = A.slc<8>(8)*B.slc<4>(0) + A.slc<8>(0)*B.slc<4>(8);     |

| 12 }  | else if (CONFIG == 1) { $//4x4$                            |

| 13 E  | P = A.slc<4>(12) *B.slc<4>(0) + A.slc<4>(8) *B.slc<4>(4) + |

| 14    | A.slc<4>(4) *B.slc<4>(8) + A.slc<4>(0)*B.slc<4>(12);       |

| 15 }  | else { // 16x16                                            |

| 16 E  | ? = A*B;                                                   |

| 17 }  |                                                            |

| 18 }  |                                                            |

logic synthesizer must infer large logic gates to meet the stricter timing constraints. Thus, in this paper we address this problem by letting the logic synthesizer select the most suitable final adder implementation that meets the specified timing constraints with the minimum area, rather than forcing it to use an RCA. We name this multiplier *BW-ADD*. With this change, we expect a lower multiplier's area at high frequency, while remaining unaltered at low frequency, compared to [6].

## C. HLS ST: AN ST MULTIPLIER DERIVED FROM HLS

As we present in Sec. V, we use HLS to generate the RTL of our PS DNN accelerators based on ST multipliers starting from a high-level description. To infer a specific implementation of an ST multiplier in the accelerators' MAC units, we force the HLS tool to import its RTL implementation. Usually, this RTL is described manually, as in the case of the SoA ST multipliers of Sec. IV-A. As an alternative, we decide to describe the ST functionality at a high-level and let the HLS tool, which in this work is Siemens Catapult, create automatically its RTL. The source code of this new ST multiplier, which we name *HLS ST*, is listed in Lst. 1. To easily access bit fields from integer data types, we use the method *slc* available in the Catapult C++ library *ac\_int.h* (line 1): for example, *A.slc*<4>(12) is a 4-bit subfield from bit 15 down to bit 12 of the int16 signal A (line 12).

By inspecting the RTL generated by the HLS tool, which corresponds to the schematic in Fig. 2(f), we notice that it contains one 16-bit, two 8-bit and two 4-bit multipliers, three adders with 8/12/16-bit bitwidth precision, and a network of multiplexers and concatenation blocks (&) that unpacks the 16-bit input operands, distributes them to the multipliers and merges their low-precision results into the final 32-bit output. Moreover, the result of low-precision configurations is already aligned to the rightmost LSB position.

## V. ST-BASED HARDWARE ACCELERATORS

## A. WORKING PRINCIPLE

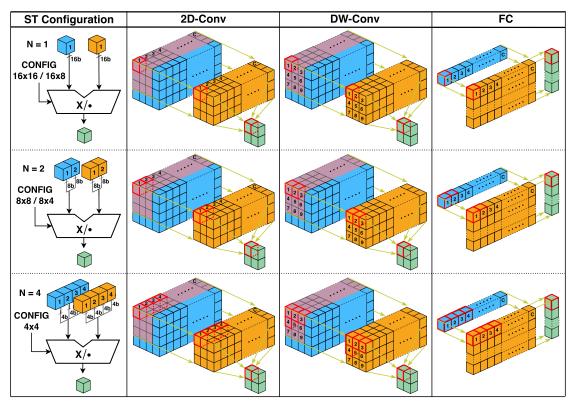

We now illustrate the working principle of our three DNN accelerators integrating ST multipliers in their MAC units. Fig. 3 shows the different access patterns (red) that the 2D-Conv, DW-Conv and FC accelerators use to read data

FIGURE 3. Working principle of our ST-based DNN accelerators: 2D-Convolution (2D-Conv), Depth-wise Convolution (DW-Conv) and Fully-Connected (FC).

from the activation (blue) and weight (orange) tensors, and how these data are packed in the 16-bit inputs of the ST multipliers.

## 1) 2D-CONV ACCELERATOR

For every orange filter with *C* kernels, a MAC unit of the 2D-Conv accelerator performs the multiplication of the *C* channels of the blue input tensor with the corresponding weight kernels, and the channel-wise accumulation of these multiplications. At full precision (N = 1), the ST multiplier within the MAC unit processes activations and weights from one input channel at a time. Instead, at lower precision the ST multiplier is fed with pairs of activation/weight data from two (N = 2) or four (N = 4) input channels at a time. This process is highlighted in red in the second column of Fig. 3 and allows to exploit the dot-product feature of the ST multiplier resulting in ideally fewer MAC cycles, which scale as C/N, and lower latency, which scales as 1/N.

## 2) DW-CONV ACCELERATOR

In DW-Conv, every output channel is the result of the convolution between the corresponding blue input channel and orange weight kernel, with no accumulation along the channel dimension, as it happens instead in the 2D-Conv case. Therefore, we need to use the ST multiplier in a different way than for 2D-Conv: we can accumulate the partial products between the N = 1, 2, or 4 input/weight pairs from the

receptive field of the input tensor and the corresponding weight kernel. This new dataflow is reported in red in the third column of Fig. 3.

Compared to 2D-Conv, this accelerator has an overhead that affects the reduction of both MAC cycles and latency, as we show later in Sec. VII-C. This is because the number of accumulations is given by the square of the kernel size  $(K^2)$ , which is not a multiple of N at lower precision (i.e., N = 2 or 4). Let us consider the  $3 \times 3$  kernel of Fig. 3 as an example. With N = 2 or 4, we need five or three iterations, respectively, to accumulate the products of input activations and kernel weights. In the last iteration, however, only one input pair is within the receptive field of the kernel. As a result, we need to feed the ST multiplier with zeros in place of the missing low-precision operands, but this clearly results in under-utilization of the ST hardware. The number of MAC cycles for DW-Conv is  $\lceil K^2/N \rceil$  and the latency reduction scales as  $[K^2/N/K^2]$ , which typically is greater than 1/N, with this overhead decreasing as K increases [10].

#### 3) FC ACCELERATOR

The working principle of this accelerator is shown in the last column of Fig. 3. To compute each element of the green output activation array (e.g., the one highligted in red), a MAC unit computes the dot product between the blue array of C input activations and one row of the orange weight matrix. The ST multiplier in the MAC unit takes N pairs

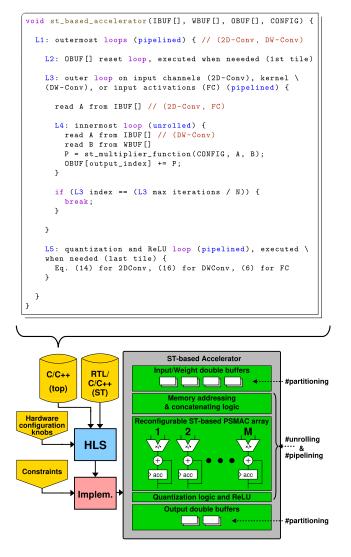

FIGURE 4. General architecture of the ST-based accelerators (bottom right), HLS flow (bottom left), and pseudo-code of the high-level C/C++ description (top) that produces the general architecture.

at a time from the two arrays and either multiplies them in high-precision mode (N = 1), or performs a dot-product in low-precision mode (N = 2, or 4). Similarly to 2D-Conv, C/N subsequent accumulations are needed to complete the calculation. The process is repeated for every row of the weight matrix, until the green output activation array is complete. As a result, the number of MAC cycles and the corresponding latency scale as C/N and 1/N, respectively, like in the 2D-Conv case.

## **B. ACCELERATORS ARCHITECTURE**

Our ST-based DNN accelerators share the same general architecture, outlined in the grey rectangle of Fig. 4. It consists of four parts as illustrated later in Secs. V-B1–V-B4: internal buffers (for input, weight, and output data), memory addressing and concatenating logics, reconfigurable ST-based PSMAC array, quantization logic and ReLU.

We obtain this architecture using the flow on the left side of Fig. 4, starting from a high-level C/C++ description of the ST-based accelerator (C/C++ (top) block) and using HLS techniques to generate the final RTL implementation. We provide a full description of this flow in Sec. VI-C.

Even though it is not the focus of our paper, we assume that the three accelerators share an on-chip global buffer (not shown in Fig. 4), as shown for example in [42] and other more recent papers on ML SoCs [43], [44]. In particular, we assume that the global buffer is large enough to store at least two *tiles* (two is for double buffering) of each of the three relevant tensors involved in the execution of a single accelerator: input activation, weight, and output activation tensor. Indeed, we assume that the complete tensors have been fragmented in tiles [45] to exploit data locality in this on-chip global buffer. Moreover, we assume that an on-chip embedded processor invokes each accelerator to process those tiles one at a time.

Table 2 shows the maximum tiles dimensions (Part I) and the maximum tiles sizes (Part II) that would be stored in the global buffer. We determined these dimensions through a statistical analysis of the layer shapes of the most common DNNs for edge devices [10], [11] that are available in public Model Zoos for computer vision applications, such as TensorFlow [46], [47], Intel [48], [49], Xilinx [50], and Nvidia [51], [52]. These networks include the well-known families of ResNet, MobileNet, and EfficientNet. Based on our survey, we select 18 and 22 as the input tile height/width (IH / IW) and output tile height/width (OH / OW) dimensions for 2D- and DW-Conv, respectively, because these values represent a reasonable trade-off between area of the global buffer and number of iterations over the tiles required by the accelerators to complete the DNN layers [10], [11]. Height and width of weight tiles (KH / KW) are instead 7 and 5 for 2D- and DW-Conv, respectively, to ensure that the accelerators support the majority of DNNs (e.g., ResNetV1 uses  $7 \times 7$  kernels).

Regarding the input tile channels/activations (IC / IA) and output tile channels/activations (OC / OA), we vary their size during the DSE of ST-based accelerators as discussed in Sec. VII-B. The values explored are in the first two rows of Table 3, which also contains HLS directives and implementation constraints that we let vary during the DSE. We call these variables hardware configuration knobs because they affect how the RTL is synthesized by the HLS tool. We use 32 as maximum value for IC and OC because we found that the number of input and output channels of activations and weight tensors of common DNNs are often divisible by this value. For the FC accelerator, we select values of IA and OA starting from those used in [6], which were 256 and 8, respectively. Then, we add values in a power-of-two fashion to expand the spectrum of solutions for our design space and to ensure that the area covered by all three accelerators ranges approximately from a minimum to a maximum in the same manner. We will describe the remaining hardware configuration knobs later in this section.

| Param.<br>name | Description 2D-Conv                |                                    | DW-Conv                                                      | FC               |

|----------------|------------------------------------|------------------------------------|--------------------------------------------------------------|------------------|

|                | Part I: N                          | Aaximum tiles dimensions           |                                                              |                  |

| IH / IW        | Input tile height / width          | 18                                 | 22                                                           | _                |

| KH / KW        | Weight tile height / width         | 7                                  | 5                                                            | _                |

| OH / OW        | Output tile height / width         | 18                                 | 22                                                           | _                |

| IC / IA        | Input tile channels / activations  | DSE                                | _                                                            | DSE              |

| OC / OA        | Output tile channels / activations | DSE                                | DSE                                                          | DSE              |

|                | Part 1                             | II: Maximum tiles sizes            |                                                              |                  |

| IS             | Input tile size                    | $IH \times IW \times IC$           | $IH \times IW \times IC$                                     | IA               |

| WS             | Weight tile size                   | $KH \times KW \times IC \times OC$ | $KH \times KW \times OC$                                     | OA 	imes IA      |

| OS             | Output tile size                   | $OH \times OW \times OC$           | $OH \times OW \times OC$                                     | OA               |

|                | Part III: Acc                      | elerators' internal buffers        | sizes                                                        |                  |

| IBS            | Input buffer (IBUF) size           | $KH \times KW \times 4$            | $KH \times KW \times 1$                                      | 128              |

| WBS            | Weight buffer (WBUF) size          | $KH \times KW \times 4 \times OC$  | $\textit{KH} \times \textit{KW} \times 1 \times \textit{OC}$ | $O\!A 	imes 128$ |

| OBS            | Output buffer (OBUF) size          | $1 \times 1 \times OC$             | $1 \times 1 \times OC$                                       | OA               |

TABLE 2. Description of accelerators' parameters related to the tiles (Part I and Part II) and accelerators' internal buffers sizes (Part III). The values of the parameters explored during the DSE of Sec. VII-B, denoted by the DSE entry, are listed in Table 3.

TABLE 3. Hardware configuration knobs explored in the DSE of Sec. VII-B, including maximum tiles size, HLS directives, and implementation constraints.

| Hardware configuration knob                                     | HLS directive                                          | 2D-Conv                             | DW-Conv                                                                        | FC                                                     |

|-----------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|

| IC / IA                                                         |                                                        | $\{4, 8, 16, 32\}$                  | _                                                                              | $\{256, 512, 1024\}$                                   |

| OC / OA                                                         |                                                        | $\{4, 8, 16, 32\}$                  | $\{2, 4, 8, 16, 32\}$                                                          | $\{8, 16, 32\}$                                        |

| PSMAC array parallelism $(M) =$<br>= Unroll loop <i>oc / oa</i> | unroll <unrolling (uf)="" factor=""></unrolling>       | OC                                  | OC                                                                             | OA                                                     |

| Partition IBUF                                                  | interleave <# of interleaved memories>                 | no                                  | OC                                                                             | no                                                     |

| Partition WBUF                                                  | interleave <# of interleaved memories>                 | OC                                  | OC                                                                             | OA                                                     |

| Partition OBUF                                                  | interleave <# of interleaved memories>                 | OC                                  | OC                                                                             | OA                                                     |

| Map st_multiplier_function<br>to ST multiplier IP               | map_to_operator <component (x)="" name=""></component> | yes (IP mode, X<br>/ no (Inline mod | <i>I</i> = { [6], [7], [17], [21]<br><i>le</i> , i.e., the <i>st_multiplie</i> | , [22], BW-ADD, HLS ST }) /<br>er_function is inlined) |

| Target clock frequency                                          |                                                        |                                     | $[100 \div 1000]$ MH                                                           | z, 10 steps                                            |

Let us now comment on the pseudo-code at the top of Fig. 4. It is a concise version of the high-level C/C++ description that produces the general architecture of the ST-based accelerators using HLS techniques. We first refer to this simplified code to highlight the commonalities between the high-level descriptions of the various accelerators. Then, we provide specific details on how the key parts of this code translate into the high-level C/C++ pseudo-codes of the three accelerators, reported in Lsts. 2, 3, and 4, for 2D-Conv, DW-Conv, and FC, respectively.

After a series of pipelined outermost loops L1–L3, the accelerator reads activations from the internal input buffer (*IBUF*) and prepares the first operand A for the ST multiplier through the memory addressing and concatenating logic. For 2D-Conv and FC, this operation takes place before the innermost loop L4; however, in the case of DW-Conv, it occurs within L4 because there is no input channels loop in the DW-Conv algorithm. Then, in L4 the accelerator reads weights from the internal weight buffer (*WBUF*) and fills the second operand *B*. Subsequently, it performs the multiplication/dot-product operation using the ST multiplier configured via *CONFIG* and accumulates the result in the internal output buffer (*OBUF*). The latter keeps stored

the result of the previous tile iteration, or is reset in L2 when the accelerator processes the initial input-weight pair of tiles of a layer execution (see the *RESET* signal in Lsts. 2-4).

Since L4 is unrolled, the HLS tool synthesizes it by generating the array of M parallel reconfigurable ST-based PSMAC units shown in Fig. 4. To comply with the working principle presented in Sec. V-A, loop L3 needs to terminate earlier in low-precision configurations: this happens when the index of L3 reaches its maximum number of iterations  $(L3_{max})$  divided by N, where  $L3_{max}$  corresponds to the number of input channels for 2D-Conv, the product of the kernel dimensions for DW-Conv, or the number of input activations for FC, of the current tile execution. This is implemented by variables *ic\_lim*, *k\_lim*, and *ia\_lim* in Lsts. 2, 3, and 4, respectively. As the number of iterations of loop L3 decreases at reduced precision, the remaining readings from IBUF and WBUF are not performed. Thus, there is no need to fill with zeros the unused parts of these buffers. Finally, only when the accelerator creates the last output tile, OBUF undergoes quantization using the corresponding UIQ formula (i.e, Eq. (14) for 2D-Conv, (16) for DW-Conv, (6) for FC), followed by ReLU (when

#### LISTING 2. Pseudo-code of our ST-based 2D-Conv accelerator.

```

#include <ac_int.h>

3 #pragma map_to_operator "X"

4 int32 st_multiplier_function(uint3 CONFIG, int16 A, B){...}

6 void conv2d(

int4 IBUF_A[IS], IBUF_B[IS], IBUF_C[IS], IBUF_D[IS],

int4 WBUF_A[WS], WBUF_B[WS], WBUF_C[WS], WBUF_D[WS],

ac_int<28, true> OBUF[OS],

uint3 CONFIG, uint1 RESET) {

int ic lim;

if (CONFIG==(8x8 || 8x4)) { ic_lim = IC/2-1; }

else if (CONFIG==4x4) { ic_lim = IC/4-1; }

14 else { ic_lim = IC-1; }

16 #pragma pipeline init interval 1

for (int oh=0; oh<OH; oh++) {</pre>

17

#pragma pipeline_init_interval 1

for (int ow=0; ow<OW; ow++) {</pre>

#pragma pipeline_init_interval 1

for (int oc=0; oc<OC; oc++) {</pre>

if (RESET==1) { OBUF[OC * (OH * oh + ow) + oc] = 0; }

.

#pragma pipeline_init_interval 1

for (int ic=0; ic<IC; ic++) {</pre>

#pragma pipeline_init_interval 1

26

for (int kh=0; kh<KH; kh++) {

28

#pragma pipeline_init_interval 1

for (int kw=0; kw<KW; kw++) {

29

// Memory addressing and concatenating logics for A

30

int A_idx = IC*(IW*(oh+kh)+(ow+kw))+ic;

int4 A_HH = IBUF_A[A_idx];

int4 A_HL = IBUF_B[A_idx];

int4 A_LH = IBUF_C[A_idx];

34

int4 A_LL = IBUF_D[A_idx];

35

int16 A = ((A_HH<<12)&0xF000) | ((A_HL<<8)&0x0F00) |

36

((A_LH<< 4)&0x00F0) | ( A_LL

&0x000F);

#pragma unroll OC

38

39

for (int oc=0; oc<OC; oc++) {</pre>

// Memory addressing and concatenating logics for B

40

int B_idx = OC*(IC*(KH*kh+kw)+ic)+oc;

41

42

int4 B_HH = WBUF_A[B_idx];

int4 B_HL = WBUF_B[B_idx];

44

int4 B_LH = WBUF_C[B_idx];

int4 B_LL = WBUF_D[B_idx];

45

int16 B = ((B_HH<<12)&0xF000) | ((B_HL<<8)&0x0F00) |

46

((B_LH<< 4)&0x00F0) | ( B_LL

&0x000F);

47

// Reconfigurable ST-based PSMAC arra

48

int28 P = st_multiplier_function(CONFIG, A, B);

49

OBUF[OC*(OH*oh+ow)+oc] += P;

50

51

} //oc

} //kw

52

} //kh

54

if (ic==ic_lim) { break; }

55

56

#pragma pipeline_init_interval 1

for (int oc=0; oc<OC; oc++) {</pre>

57

58

// Quantization logic (Eq. 14) and ReLU (when needed)

59

. . .

}

60

} //ow

61

} //oh

62

63 }

```

needed), preparing the output for the computation of the next layer. Otherwise, *OBUF* keeps accumulating the partial result/output inside the accelerator to avoid data transfers in the external memory, thus following an *output-stationary* dataflow [42].

Below we delve into the details of each architectural block of the ST-based accelerator illustrated in Fig. 4, highlighting the key differences between the three accelerators.

## 1) INTERNAL BUFFERS

Part III of Table 2 reports the accelerators' internal buffers sizes. These follow the same ordering of the parameters used

#### LISTING 3. Pseudo-code of our ST-based DW-Conv accelerator.

```

#include <ac int.h>

3 #pragma map_to_operator "X"

4 int32 st_multiplier_function(uint3 CONFIG, int16 A, B){...}

6 void dwconv(

int4 IBUF_A[IS], IBUF_B[IS], IBUF_C[IS], IBUF_D[IS],

int4 WBUF_A[WS], WBUF_B[WS], WBUF_C[WS], WBUF_D[WS],

ac_int<28, true> OBUF[OS],

0

uint3 CONFIG, uint1 RESET) {

10

11 int k_lim,i0,i1,i2,i3,j0,j1,j2,j3;

12 if (CONFIG==(8x8 || 8x4)) { k_lim = (KH*KW)/2; }

13 else if (CONFIG==4x4) { k_lim = (KH*KW)/4; }

14 else { k_lim = (KH*KW)-1; }

16 #pragma pipeline_init_interval 1

(int oh=0; oh<OH; oh++) {

17 for

#pragma pipeline_init_interval 1

18

19

for (int ow=0; ow<OW; ow++) {</pre>

#pragma pipeline init interval 1

2.0

for (int oc=0; oc<OC; oc++) {</pre>

if (RESET==1) { OBUF[OC*(OH*oh+ow)+oc] = 0; }

#pragma pipeline_init_interval 1

24

for (int k=0; k<KH*KW; k++) {</pre>

#pragma unroll OC

26

for (int oc=0; oc<OC; oc++) {</pre>

28

' Memory addressing and concatenating logics for A

29

i0, i1, i2, i3 = LUT_i (CONFIG, k);

j0, j1, j2, j3 = LUT_j(CONFIG, k);

30

31

int4 A_HH = IBUF_A[OC*(IN_W*(oh+i0)+(ow+j0))+oc];

32

int4 A_HL = IBUF_B[OC*(IN_W*(oh+i1)+(ow+j1))+oc];

int4 A_LH = IBUF_C[OC*(IN_W*(oh+i2)+(ow+j2))+oc];

33

int4 A_LL = IBUF_D[OC*(IN_W*(oh+i3)+(ow+j3))+oc];

34

int16 A = ((A_HH<<12)&0xF000) | ((A_HL<<8)&0x0F00)

&0x000F);

((A_LH<< 4)&0x00F0) | ( A_LL

36

// Memory addressing and concatenating logics for \ensuremath{\mathsf{B}}

37

int4 B_HH = WBUF_A[OC*(KH*i3+j3)+oc];

38

int4 B_HL = WBUF_B[OC*(KH*i2+j2)+oc];

39

40

int4 B_LH = WBUF_C[OC*(KH*i1+j1)+oc];

int4 B_LL = WBUF_D[OC*(KH*i0+j0)+cc];

int16 B = ((B_HH<<12)&0xF000) | ((B_HL<8)&0x0F00) |

((B_LH<<4)&0x00F0) | (B_LL & 0x000F);</pre>

41

42

43

44

if ((k==k_lim) && (CONFIG==(8x8 || 8x4) || CONFIG==4x4)) {

45

// Force two or three 4-bit chunks of a and b

// to zero in place of the missing elements

46

47

. . .

48

}

49

// Reconfigurable ST-based PSMAC array

50

int28 P = st_multiplier_function(CONFIG,A,B);

OBUF[OC*(OH*oh+ow)+oc] += P:

51

52

if

(k==k_lim) { break; }

1/2

5.4

#pragma pipeline_init_interval 1

55

for (int oc=0; oc<OC; oc++) {</pre>

56

57

// Quantization logic (Eq. 16) and ReLU (when needed)

58

}

59

} //ow

60

61

} //oh

62 }

```

by the tile sizes in Part II. For *IBUF* and *WBUF* of 2Dand DW-Conv we choose the minimum sizes that allow to compute  $1 \times 1 \times OC$  output elements. In particular, we size *IBUF* of 2D-Conv to store 4 input channels, to allow ST multipliers to operate in all precision configurations. For *WBUF* we choose the kernel dimensions of 7 and 5, following the weight tile dimensions of Part I. For FC we size *IBUF* to store 128 activations and *OBUF* to store *OA* output elements, to have a buffer area comparable with that of the other two accelerators. The internal buffers use double buffering to ensure uninterrupted operations by the accelerators while fetching new data from the global buffer. Thus, from the accelerators' point of view, the whole memory hierarchy composed of global buffer and internal buffers behaves as a unified virtual memory that they can access transparently.

LISTING 4. Pseudo-code of our ST-based FC accelerator (inspired by [6]).

```

#include <ac int.h>

3 #pragma map_to_operator "X"

4 int32 st_multiplier_function(uint3 CONFIG, int16 A, B){...}

6 void fc(int4 IBUF1_A[IS/2], IBUF2_A[IS/2],

int4 IBUF1_B[IS/2], IBUF2_B[IS/2],

int4 IBUF1_C[IS/2], IBUF2_C[IS/2],

int4 IBUF1_D[IS/2], IBUF2_D[IS/2],

int4 WBUF1_A[WS/2], WBUF2_A[WS/2],

int4 WBUF1_B[WS/2], WBUF2_B[WS/2],

int4 WBUF1_C[WS/2], WBUF2_C[WS/2],

int4 WBUF1_D[WS/2], WBUF2_D[WS/2],

14

ac int<28, true> OBUF[OS]

uint3 CONFIG, uint1 RESET) {

int ia lim;

16

if (CONFIG==(8x8 || 8x4)) { ia_lim = IA/4-1; }

else if (CONFIG==4x4) { ia_lim = IA/8-1; }

18

else { ia_lim = IA/2-1; }

#pragma pipeline_init_interval 1

for (int oa=0; oa<OA; oa++) {

if (RESET==1) { OBUF[oa] = 0; }

24

#pragma pipeline_init_interval 1

25

for (int ia=0; ia<IA/2; ia++) {</pre>

26

// Memory addressing and concatenating logics for A1, A2

int a_idx = ia;

int4 A1_HH = IBUF1_A[a_idx], A2_HH = IBUF2_A[a_idx];

29

int4 A1_HL = IBUF1_B[a_idx], A2_HL = IBUF2_B[a_idx];

30

int4 A1_LH = IBUF1_C[a_idx], A2_LH = IBUF2_C[a_idx];

int4 A1_LL = IBUF1_D[a_idx], A2_LL = IBUF2_D[a_idx];

int16 A1 = ((A1_HH<<12)&0xF000) | ((A1_HL<<8)&0x0F00)

((A1_LH<< 4)&0x00F0) | ( A1_LL

&0x000F);

int16 A2 = ((A2_HH << 12) \& 0xF000)

((A2_HL<<8)&0x0F00)

Т

((A2_LH<< 4)&0x00F0) | ( A2_LL

&0x000F);

36

#pragma unroll OA

for (int oa=0; oa<OA; oa++) {</pre>

38

// Memory addressing and concatenating logics for B1, B2

39

int b idx = OA*ia+oa;

40

int4 B1_HH = WBUF1_A[b_idx], B2_HH = WBUF2_A[b_idx];

int4 B1_HL = WBUF1_B[b_idx], B2_HL = WBUF2_B[b_idx];

int4 B1_LH = WBUF1_C[b_idx], B2_LH = WBUF2_C[b_idx];

int4 B1_LL = WBUF1_D[b_idx], B2_LL = WBUF2_D[b_idx];

int16 B1 = ((B1_HH<<12)&0xF000) | ((B1_HL<<8)&0x0F00) |

45

46

((B1_LH<< 4)&0x00F0)

| ( B1_LL

&0x000F);

int16 B2 = ((B2_HH <<12) \& 0xF000) | ((B2_HL <<8) \& 0x0F00) |

47

((B2_LH<< 4)&0x00F0) | ( B2_LL

&0x000F);

48

// Reconfigurable ST-based PSMAC arr

int28 P1 = st_multiplier_function(CONFIG, A1, B1);

int28 P2 = st_multiplier_function(CONFIG, A2, B2);

int28 P1_plus_P2 = P1+P2;

OBUF[oa] += P1_plus_P2;

54

if (ia==ia lim) { break; }

56

} //ia

#pragma pipeline_init_interval 1

57

for (int oa=0; oa<OA; oa++) {</pre>

// Quantization logic (Eq. 6) and ReLU (when needed)

59

60

61

}

62 }

```

The internal input and weight buffers are organized in four 4-bit memory banks, named  $IBUF_A/B/C/D$  and  $WBUF_A/B/C/D$ , respectively, to enable reading low-precision data according to the memory access patterns shown in Fig. 3. This is visible from the *int4* datatype in the function signatures of Lsts. 2–4. The output buffer is organized in 28-bit banks to match the bitwidth of the accumulators in the PSMAC array, as we will see in Sec. V-B3.

To guarantee the proper accelerators' execution, the internal buffers are filled by a Direct Memory Access (DMA) engine following the working principle illustrated in Fig. 3. For 2D-Conv, in configurations  $16 \times 16$  and  $16 \times 8$ , *one*

element of the input and weight tiles, once read from the global buffer, is extended to 16-bit (if needed) and split into four 4-bit chunks. Each input and weight chunk is then stored, from the most to the least significant, into IBUF\_A-D and WBUF\_A-D, respectively. In configurations  $8 \times 8$  and  $8 \times 4$ , two input and two weight elements from the channels dimension of the corresponding tiles are extended to 8-bit (if needed) and split into 4-bit chunks. The chunks of the first input and the first weight are stored in IBUF\_A-B and WBUF C-D, respectively; the chunks of the second input and the second weight are stored in IBUF\_C-D and WBUF\_A-B, respectively. The 4-bit chunks are always stored from most to least significant. In the  $4 \times 4$  case, four input and *four* weight elements from the channels dimension of the corresponding tiles are all extended to 4-bit (if needed), and then packed in IBUF\_A/WBUF\_D, IBUF\_B/WBUF\_C, IBUF\_C/WBUF\_B, and IBUF\_D/WBUF\_A, respectively.

For the FC accelerator, the process to fill the memory banks is similar to that of 2D-Conv. However, the number of the 4-bit memory banks is twice that of 2D-Conv (see lines 6–13 in Lst. 4) for a reason clarified in Sec.V-B3. In configurations  $16 \times 16$  and  $16 \times 8$ , two consecutive activations from the input tile and two consecutive weights from the same row of the weight tile are read from the global buffer, extended to 16-bit (if needed) and split into four 4-bit chunks. From the most to the least significant, the four chunks of the two inputs are stored into IBUF1 A-D and IBUF2 A-D, while those of the two weights are stored into WBUF1 A-D and WBUF2\_A-D, respectively. In configurations  $8 \times 8$  and  $8 \times 4$ , four consecutive activations and weights are read along the input array and the same weight matrix row, respectively. Then, they are all extended to 8-bit (if needed) and each is split into two 4-bit chunks. The two chunks of the four inputs are stored in this order: IBUF1\_A-B, IBUF1\_C-D, IBUF2\_A-B, and IBUF2\_C-D, whereas those of the four weights are stored in this order: WBUF1\_C-D, WBUF1\_A-B, WBUF2\_C-D, and WBUF2\_A-B. 4-bit chunks are always stored from most to least significant. In the  $4 \times 4$  case, *eight* pairs of consecutive inputs and weights are read, extended to 4-bit (if needed), and stored in the internal memory banks as follows: 1st in IBUF1\_A/WBUF1\_D, 2nd in IBUF1\_B/WBUF1\_C, 3rd in IBUF1\_C/WBUF1\_B, 4th in IBUF1\_D/WBUF1\_A, 5th in IBUF2 A/WBUF2 D, 6th in IBUF2 B/WBUF2 C, 7th in IBUF2\_C/WBUF2\_B, 8th in IBUF2\_D/WBUF2\_A.

Filling the memory banks of DW-Conv for configurations  $16 \times 16$  and  $16 \times 8$  follows the same steps of 2D-Conv. However, for low-precision operating modes the filling process is different. For configurations  $8 \times 8$  and  $8 \times 4$ , *two* consecutive input elements from the receptive field of the activation tile and *two* consecutive weights from the corresponding kernel of the weight tile are extended to 8-bit (if needed) and split into 4-bit chunks. The chunks of the first and second inputs are stored in IBUF\_A-B, whereas those of the first and second weights are stored in WBUF\_C-D, leaving IBUF\_C-D and WBUF\_A-B unused.

For configuration  $4 \times 4$ , *four* consecutive input elements from the receptive field of the activation tile and *four* consecutive weights from the corresponding kernel of the weight tile are extended to 4-bit (if needed) and then stored in IBUF\_A and WBUF\_D only, leaving the other banks unused.

The data organization discussed above for the three accelerators is important as it enables the partitioning of the internal buffers into smaller memory banks (through the HLS directive interleave). This ensures that each bank contains all the data required by a single PSMAC unit to compute its own channel/activation output elements independently. In this way, the PSMAC array can compute M output channels/activations in parallel, as we show in detail in Sec. V-B3. However, to provide the input operands of ST multipliers in the PSMAC array in one clock cycle for all configurations, as it happens for 2D-Conv and FC, the memory organization of DW-Conv requires that IBUF\_B and WBUF\_C have two reading ports, and IBUF\_A and WBUF\_D have four reading ports, whereas all the other banks still have one reading port. As implementing four ports in SRAM ASIC technology would be critical, we decide to use latch-based memories for IBUF\_A and WBUF\_D.

## 2) MEMORY ADDRESSING AND CONCATENATING LOGIC

These two logic circuits are designed to implement the working principles outlined in Sec. V-A. Depending on the type of accelerator and selected configuration (as depicted in Fig. 3), the first is responsible for preparing the addresses to properly access IBUF and WBUF and retrieve the four 4-bit data from each memory bank (e.g., lines 31-35 and 41-45 of Lst. 2 for operand A and B, respectively). The second organizes these data into the 16-bit input operands of the ST multipliers through shift-and-mask operations (e.g., lines 36–37 and 46–47 of Lst. 2). For DW-Conv, these logic circuits are a bit more complex. Indeed, a pair of Look-Up Tables (LUTs) is required to retrieve the proper indexes, pre-computed offline, based on the values of CONFIG and k, where k is the iteration counter of the loop over the kernel (line 25 of Lst. 3). Moreover, as already discussed in Sec. V-A2, DW-Conv requires that two or three 4-bit chunks of A and B are filled with zeros in place of the missing lowprecision operands, in the last kernel iteration for N = 2 or N = 4, respectively (lines 44–48 of Lst. 3).

## 3) RECONFIGURABLE ST-BASED PSMAC ARRAY

The PSMAC array of our ST-based accelerators contains *M* MAC units, as shown in Fig. 4. Each MAC unit works on a distinct output channel/activation, processing a different filter for 2D-Conv, kernel for DW-Conv, or row of the weights matrix for FC.

The *PSMAC array parallelism* (M), as listed in Table 3, corresponds to the unrolling factor applied to the innermost loops of the accelerators' high-level code through the HLS directive *unroll*. Specifically, M is equal to *OC* for 2D- and DW-Conv, and to *OA* for FC. This causes the HLS tool to fully unroll the innermost loops (line 39 for Lst. 2, 27 for Lst. 3)

and 38 for Lst. 4), because the unrolling factor matches their upper bound, thus replicating M times the ST-multiplier and the accumulation adder. As introduced in Sec. V-B1, to fully leverage this parallelism, we partition the internal buffers into M memory banks, enabling the PSMAC units to access their required data concurrently. For this purpose, we use the *interleave* directive with OC (for 2D- and DW-Conv) or OA (for FC) as argument. Table 3 also shows that the partitioning is not required for *IBUF* of 2D-Conv and FC since operand A is read outside the innermost unrolled loop (lines 31–37 in Lst. 2, lines 28–36 in Lst. 4).

For 2D- and DW-Conv, each MAC unit consists of one 16-bit ST multiplier (see the function call *st\_multiplier\_function*), one 28-bit adder and one 28-bit accumulation register (*P*) (lines 49–50 and lines 50–51 in Lsts. 2 and 3). For FC, we got inspired from [6], thus each MAC unit comprises two 16-bit ST multipliers (to process two activation/weight pairs in parallel), two 28-bit adders (to sum the outputs of the two multipliers and accumulate this result, respectively), and one 28-bit accumulation register (*P1\_plus\_P2*) (lines 50–53 in Lst. 4). This is also the reason why we have twice the input and weight buffers at the interface (lines 6–13 in Lst. 4).

The bitwidth of adders and accumulation registers is the result of the ablation study discussed in Sec. VI-B.

## 4) QUANTIZATION AND RELU BLOCK

This block implements the UIQ formulas (14), (16), and (6) (with  $z_W = 0$  and  $z_b = 0$  [13], [14]) into 2D-Conv, DW-Conv and FC, respectively. For an efficient hardware implementation, we convert the division by the output scaling factor  $s_Y$  into a multiplication by its inverse. Additionally, we minimize the bitwidth of the C/C++ variables of the UIQ formulas through the ablation study described in Sec. VI-B. When the accelerator has processed the last pair of input/weight tiles needed to complete a specific output tile, the accumulated results in the PSMAC array are ready to be quantized using the UIQ formulas. In fact, the accumulated results correspond to term (c) in all the UIQ formulas (14), (16), and (6). The remaining variables of the UIQ formula are passed to the accelerator as inputs because they can be computed offline.

Furthermore, this block implements layer fusion between UIQ formulas and ReLU as described in Sec. III-A1. Thus, when ReLU is needed, the accelerators can be configured to execute it in hardware. The related pseudo-code, omitted for simplicity, would be at lines 58, 57, and 59 of Lst. 2, Lst. 3, and Lst. 4, respectively.

Finally, all accelerators support per-layer quantization for activations, and per-layer or per-channel quantization for weights, as the latter offers superior performance for DNN quantization, as shown in [14] and [27].

## **VI. ACCELERATORS DESIGN FLOW**

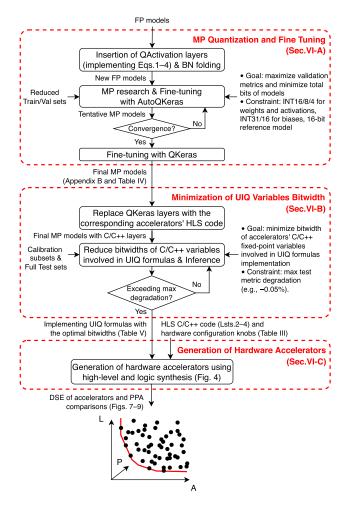

To obtain our ST-based hardware accelerators, we use the design flow outlined in Fig. 5. It consists of the following three steps, which are analyzed in detail in Secs. VI-A–VI-C:

FIGURE 5. Accelerators design flow.