# POLITECNICO DI TORINO Repository ISTITUZIONALE

# A Stacked Doherty Power Amplifier For Ka-Band Space Applications

Original

A Stacked Doherty Power Amplifier For Ka-Band Space Applications / Furxhi, Stela; Giofrè, Rocco; Piacibello, Anna; Camarchia, Vittorio; Colantonio, Paolo. - ELETTRONICO. - (2023), pp. 1-4. (Intervento presentato al convegno 2023 International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits (INMMIC) tenutosi a Aveiro, Portugal nel 08-11 November 2023) [10.1109/INMMIC57329.2023.10321793].

Availability: This version is available at: 11583/2984275 since: 2023-12-02T16:43:57Z

Publisher: IEEE

Published DOI:10.1109/INMMIC57329.2023.10321793

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A Stacked Doherty Power Amplifier For Ka-Band Space Applications

Stela Furxhi<sup>1</sup>, Rocco Giofrè<sup>1</sup>, Anna Piacibello<sup>2</sup>, Vittorio Camarchia<sup>2</sup>, Paolo Colantonio<sup>1</sup>, <sup>1</sup>E.E.Dept. University of Roma Tor Vergata, Roma, Italy

<sup>2</sup>Department of Electronics and Telecommunications, Politecnico di Torino, Torino, Italy *email: stela.furxhi@uniroma2.it*

Abstract—This paper presents the design and preliminary experimental characterization of a Monolithic Microwave Integrated Circuit (MMIC) Doherty Power Amplifier (DPA) conceived for satellite downlink Ka-band (17.3-20.3 GHz), manufactured in Gallium Nitride on Silicon (GaN-Si) High Electron Mobility Transistor technology with 0.1 µm gate length available at OMMIC foundry. The DPA is based on a three-stage architecture in which the devices in the output stage of both Carrier and Peaking branches are implemented in a stacked configuration. The MMIC shows preliminary experimental results in agreement with the simulations achieving a small signal gain larger than 25 dB and input and output return losses better than 10 dB. Expected nonlinear performances show a saturation output power of 38 dBm, a gain better than 22 dB, and a Power-Added Efficiency of 37%, which remains higher than 25% at 6dB of output power back-off.

## I. INTRODUCTION

Space communication systems are rapidly evolving toward higher carrier frequencies, multi-beam active antenna arrays, and signals based on complex modulation schemes [1]. If, from one side, these innovations allow to achieve higher data rates and flexible and better area coverage, on the other side they put more stringent requirements on the RF components of the payload and, above all, on the adopted power amplifier (PA), which has to be more linear and efficient as compared to the past. In fact, the adoption of spectrally efficient modulated signals, which are characterized by high Peak-to-Average Power Ratio (PAPR), asks for a PA with high efficiency not only at saturation but also in back-off. Efficiency is of paramount importance in space since power budget, thermal and mechanical design, as well as the weight of the overall payload is heavily affected by it. Additionally, the PA should also guarantee an acceptable linearity along its dynamic to reduce at minimum the need for additional linearizing blocks, thus leading to a system with low complexity, which is really important to assure good reliability.

Therefore, high-efficiency PA architectures, such as the Doherty Power Amplifier (DPA), which is nowadays the most adopted solution in the ground communication systems, at least in the sub-6 GHz range, are also starting to be investigated for high frequency space applications [2]–[9].

From a technological point of view, considering that the typical output power requirement at chip level is in the order of 6 W to 10 W minimum, in downlink Ka-band (i.e., 17.3-20.3 GHz), the most suitable Monolithic Microwave Integrated

Circuit (MMIC) technology to be used seem to be the Gallium Nitride (GaN) one, either on silicon carbide (SiC) or on pure silicon (Si) substrate [1]. In fact, such power levels are typically beyond the possibility of other semiconductor technologies usually adopted for space systems.

This paper focuses on this quite novel research trend, presenting the design and the preliminary experimental characterization of a Ka-band DPA MMIC in which the active devices of the final stage are in a stacked cell (SC) configuration. The latter consists of one or more devices in a pseudocommon-gate (CG) configuration stacked on top of a commonsource (CS) one, which theoretically allows to achieve better performance with respect to the more traditional parallel configuration. Indeed, the SC has the advantage of having an optimum output impedance higher than that of the single active device, resulting in a lower impedance transformation ratio required to match the 50  $\Omega$  termination, thus leading to benefits in terms of broadband behavior and lower losses [10], [11]. The reported DPA is implemented in the D01GH GaN-Si process with a gate length of 0.1 µm from OMMIC. It achieves a peak power of 38 dBm, a Power-Added Efficiency (PAE) of more than 37%, and an associated gain of approximately 22 dB in the downlink Ka-band.

# II. DPA DESIGN

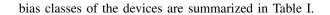

The design goals of the DPA are to achieve a saturated output power of 6W and a high efficiency at both saturation and 6 dB output power back-off (OBO) in the 17.3-20.3 GHz band. In this DPA, the SC was used in the final stage of both Carrier and Peaking branches. A load pull analysis was carried out to select the devices to be used for CS and CG, considering that the chosen technology provides a power density of approximately 2 W/mm. To achieve the output power requirements, a gate periphery of the final stage of about 3 mm must be chosen. Therefore, as a first step in the design flow, the SC was assembled according to the compact, symmetrical, and high-performing topology presented in [5], where the CS is divided into two devices with 4x100 µm gate periphery each, and the CG is implemented by using a single 8x100 µm device. Electromagnetic simulations are essential at this stage, to correctly evaluate the coupling and crosstalk effects present among the components of the SC [12] and thus optimize its performance.

#### (b) Photo

Fig. 1. DPA Schematic (a) with the different sub-networks highlighted: the SC is realized by two  $4x100 \,\mu\text{m}$  CS devices and single  $8x100 \,\mu\text{m}$  CG. There are two cascaded CS driver stages,  $4x100 \,\mu\text{m}$  and  $2x75 \,\mu\text{m}$ , respectively. The OMN consists of two short-circuited stubs in parallel to the drain of the SCs and three  $\lambda/4 - f_0$  transmission lines with different characteristic impedances (Z1, Z2, Z3). Between the final-driver and driver-pre-driver stages are the ISMN and ISMND matching networks, respectively. Finally, at the input there are the IMNs and the input splitter realized by a Lange uneven coupler. Photo (b) of the realized Stacked DPA: chip size 5x4 mm<sup>2</sup>.

In Fig.1 are reported the schematic (a) and photo (b) of the realized chip of the DPA (chip size  $5x4 \text{ mm}^2$ ). As can be noted, together with the SCs in the final stage, two cascaded CS driver stages, with a gate periphery of  $4x100 \,\mu\text{m}$  and  $2x75 \,\mu\text{m}$ , respectively, were added in both branches with the aim of increasing the gain of the entire amplifier. The drain bias voltage is set to  $18 \,\text{V}$  for the SCs and  $9 \,\text{V}$  for the single-ended devices in the driver and pre-driver stages. Such values result to be a good trade-off between performance and reliability since they allow to limit the junction temperature of the devices to  $160 \,^{\circ}\text{C}$  in the worst case, i.e., when the backside temperature of the MMIC is assumed to be  $T_{\text{BS}} = 75 \,^{\circ}\text{C}$ . The thermal behaviour of power devices for space applications, especially if GaN-Si technology is employed, is fundamental for its impact on the lifetime of satellite MMICs [13]. The

| TABLE I              |

|----------------------|

| DPA BIAS CONDITIONS. |

| Stage      | Carrier Branch         |                |      |       |  |

|------------|------------------------|----------------|------|-------|--|

|            | Parameter              | Value          | Unit | Class |  |

| Pre-Driver | V <sub>GG,PreD,C</sub> | -1.4           | V    |       |  |

|            | V <sub>DD,PreD,C</sub> | 9              | V    | AB    |  |

|            | I <sub>D,PreD,C</sub>  | 3.7            | mA   |       |  |

| Driver     | V <sub>GG,D,C</sub>    | -1.44          | V    |       |  |

|            | V <sub>DD,D,C</sub>    | 9              | V    | AB    |  |

|            | I <sub>D,D,C</sub>     | 5.4            | mA   |       |  |

| SC         | V <sub>GG,C</sub>      | -1.32          | V    |       |  |

|            | VSTACK                 | 7.6            | V    | AB    |  |

|            | V <sub>DD,C</sub>      | 18             | V    |       |  |

|            | I <sub>D,C</sub>       | 45.7           | mA   |       |  |

|            |                        | Peaking Branch |      |       |  |

| Pre-Driver | V <sub>GG,PreD,P</sub> | -1.4           | V    |       |  |

|            | V <sub>DD,PreD,P</sub> | 9              | V    | AB    |  |

|            | I <sub>D,PreD,P</sub>  | 3.7            | mA   |       |  |

| Driver     | V <sub>GG,D,P</sub>    | -2             | V    |       |  |

|            | V <sub>DD,D,P</sub>    | 9              | V    | C     |  |

|            | I <sub>D,D,P</sub>     | -              | mA   |       |  |

| SC         | V <sub>GG,P</sub>      | -2.6           | V    |       |  |

|            | VSTACK                 | 7.6            | V    | С     |  |

|            | V <sub>DD,P</sub>      | 18             | V    |       |  |

|            | I <sub>D.P</sub>       | 7.7            | mA   |       |  |

The unconditional stability of the SC under small signal conditions was ensured through an R-C series network connected to the gate of the CG device an a stabilization network connected to the gate of the CS, consisting of a parallel R-C and series R-L. The latter network topology was also used to stabilize the devices in the driver and pre-driver stages.

Referring to Fig.1, the synthesized output combiner (OMN) includes two short-circuited stubs connected in parallel to the drain of the SCs, and three  $\lambda/4 - f_0$  transmission lines with different characteristic impedances (Z1, Z2, and Z3), whose values have been selected according to [14]. The length of the parallel stubs was properly selected to resonate out the output parasitic of the SC, whereas through a careful selection of the characteristic impedances Z1, Z2 and Z3, it was possible to achieve a broadband matching to 50  $\Omega$  without adding any further post-matching components. The designed OMN ensures the correct modulation of the load seen by the SCs in the final stage, i.e., from  $2R_{opt} = 44 \Omega$  to  $R_{opt} = 22 \Omega$  for the Carrier and from  $\infty$  to  $R_{opt} = 22 \Omega$  for the Peaking one, as shown in Fig.2, being  $R_{opt}$  the intrinsic optimum load of the device inferred from the Load Pull analysis.

The matching networks between final and driver stages (ISMNs) were synthesised to transform the input loads of the two CS of the SCs into the optimal output load of the stabilized driver devices. A similar approach was applied to design the matching networks between the driver and pre-driver stages (ISMNDs).

Finally, the 50  $\Omega$  pre-driver input matching networks (IMNs) and the input splitter were implemented. The latter consists of a uneven Lange coupler that provides more power to the Peaking branch with respect to the Carrier one (P<sub>IN,P</sub>/P<sub>IN,C</sub> = 1.6) and simultaneously compensates for the phase shift introduced by the output combiner.

(b) Peaking

Fig. 2. Synthesised load modulation by output combiner (OMN) of Carrier (a) and Peaking SCs (b) at 17.3, 18.8 and 20.3 GHz.

The design of the DPA was carried out using Keysight PathWave Advanced Design System (ADS) software.

# III. RESULTS

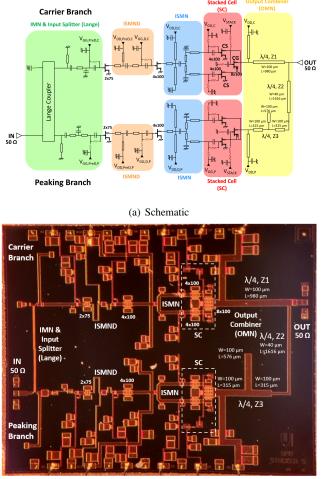

The realized MMIC DPA was measured under small signal excitation at the nominal bias condition reported in Section II. Fig.3 shows the comparison between measured and simulated scattering parameters. Notably, a good agreement is achieved with a measured small signal gain  $(S_{21})$  and input return loss  $(S_{11})$  that are better than 25 dB and 10 dB, respectively, in the band from 17.3 GHz to 20.3 GHz.

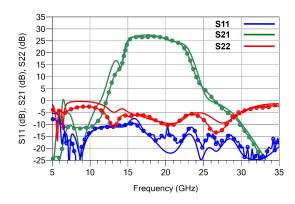

The simulated nonlinear performance, as a function of the output power, are shown in Fig.4. The realized MMIC shows the typical DPA behaviour achieving a saturated output power of  $P_{out,sat}$ =38 dBm (6 W) with a PAE peak around 37 %, which remains higher than 25 % at 6 dB of OBO. The gain is around 22 dB in the Doherty region.

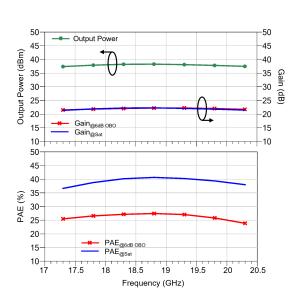

The output power, PAE and gain as functions of the frequency are shown in Fig.5, at both saturation and 6 dB OBO. Notably, these features show an almost flat behaviour all over the bandwidth.

Fig. 3. Comparison between simulated (solid lines) and measured (lines with circles) scattering parameters of the DPA.

Fig. 4. Simulated DPA performance at 17.3 GHz, 18.8 GHz and 20.3 GHz as a function of the output power.

Fig. 5. Output power, PAE and gain at saturation and 6 dB OBO as a function of the frequency.

# IV. CONCLUSION

This work presents the design and preliminary results of a DPA for Ka-Band space applications, in which the output stage devices of the Carrier and Peaking branches are implemented in a stacked configuration. The MMIC is realized in the GaN-Si High Electron Mobility Transistor (HEMT) technology with 0.1 µm gate length available at OMMIC foundry. The measured performance are in good agreement with the expected one, at least in terms of small-signal, whereas nonlinear characterization is still on going. The small-signal gain and input return loss are greater than 25 dB and 10 dB, respectively, while nonlinear simulations show a peak power of 38 dBm (6 W), with a PAE of 37 % and a gain around 22 dB.

## ACKNOWLEDGMENT

This work was supported by ESA under the contract "Single-chip Ka-band Doherty amplifier" ITT: AO/1-9088/17/NL/HK Ref: Item no. 17.1ET.01.

### REFERENCES

- V. Valenta and I. Davies, "Power Amplification and Integration Challenges of Reconfigurable Antennas for Space Applications," in 2019 European Microwave Conference in Central Europe (EuMCE), 2019, pp. 457–460.

- [2] A. Piacibello, R. Giofré, R. Quaglia, and V. Camarchia, "34 dBm GaN Doherty Power Amplifier for Ka-band satellite downlink," in 2020 15th European Microwave Integrated Circuits Conference (EuMIC), 2021, pp. 25–28.

- [3] A. Piacibello, R. Giofrè, R. Quaglia, R. Figueiredo, N. Carvalho, P. Colantonio, V. Valenta, and V. Camarchia, "A 5-W GaN Doherty Amplifier for Ka-Band Satellite Downlink With 4-GHz Bandwidth and 17-dB NPR," *IEEE Microwave and Wireless Components Letters*, vol. 32, no. 8, pp. 964–967, 2022.

- [4] F. Costanzo, R. Giofrè, V. Camarchia, P. Colantonio, and E. Limiti, "A Ka-band Doherty Power Amplifier using an innovative Stacked-FET Cell," in 2019 15th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), 2019, pp. 165–168.

- [5] F. Costanzo, A. Piacibello, M. Pirola, P. Colantonio, V. Camarchia, and R. Giofrè, "A Novel Stacked Cell Layout for High-Frequency Power Applications," *IEEE Microwave and Wireless Components Letters*, vol. 31, no. 6, pp. 597–599, 2021.

- [6] V. Valenta, I. Davies, N. Ayllon, S. Seyfarth, and P. Angeletti, "High-gain GaN Doherty power amplifier for Ka-band satellite communications," in 2018 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), 2018, pp. 29–31.

- [7] S. Madhuwantha, P. Ramabadran, R. Farrell, and J. Dooley, "N-way Digitally Driven Doherty Power Amplifier Design and Analysis for Ku band Applications," in 2018 29th Irish Signals and Systems Conference (ISSC), 2018, pp. 1–6.

- [8] E. Richard, T. Huet, H. M. Karimdjy, M. Camiade, C. Chang, V. Serru, F. Fernandez, J. Suedois, I. Davies, and V. Valenta, "A 17.3-20.3 GHz Doherty Power Amplifier with 14W Saturated Output Power and 28% PAE at 6dB OPBO in 150nm GaN Technology," in 2022 IEEE/MTT-S International Microwave Symposium - IMS 2022, 2022, pp. 422–425.

- [9] E. Heidebrecht, R. Negra, V. Valenta, I. Davies, O. Jardel, and E. Richard, "5 Watts, MMIC, K-Band Doherty PA for Satellite Communications," in 2022 17th European Microwave Integrated Circuits Conference (EuMIC), 2022, pp. 91–94.

- [10] H.-T. Dabag, B. Hanafi, F. Golcuk, A. Agah, J. F. Buckwalter, and P. M. Asbeck, "Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 4, pp. 1543–1556, 2013.

- [11] G. van der Bent, P. de Hek, and F. E. van Vliet, "Design Procedure for Integrated Microwave GaAs Stacked-FET High-Power Amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 67, no. 9, pp. 3716–3731, 2019.

- [12] C. Ramella, A. Piacibello, V. Camarchia, and M. Pirola, "Electromagnetic Crosstalk Effects in a Millimeter-wave MMIC Stacked Cell," in *INMMIC 2020*, 2020, pp. 1–3.

- [13] C. Ramella, M. Pirola, A. Reale, M. Ramundo, P. Colantonio, M. A. D. Maur, V. Camarchia, A. Piacibello, and R. Giofrè, "Thermal-aware GaN/Si MMIC design for space applications," in 2019 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS), 2019, pp. 1–6.

- [14] R. Giofrè, L. Piazzon, P. Colantonio, and F. Giannini, "An Ultra-Broadband GaN Doherty Amplifier with 83 % of Fractional Bandwidth," *IEEE Microwave and Wireless Components Letters*, vol. 24, no. 11, pp. 775–777, 2014.