## POLITECNICO DI TORINO Repository ISTITUZIONALE

### A Balanced Stacked GaN MMIC Power Amplifier for 26-GHz 5G applications

Original

A Balanced Stacked GaN MMIC Power Amplifier for 26-GHz 5G applications / Piacibello, Anna; Ramella, Chiara; Camarchia, Vittorio; Pirola, Marco. - ELETTRONICO. - (2023), pp. 331-334. (Intervento presentato al convegno 2023 IEEE/MTT-S International Microwave Symposium - IMS 2023 tenutosi a San Diego, CA, USA nel 11-16 June 2023) [10.1109/IMS37964.2023.10187989].

Availability: This version is available at: 11583/2983504 since: 2023-12-02T10:06:52Z

Publisher: IEEE

Published DOI:10.1109/IMS37964.2023.10187989

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A Balanced Stacked GaN MMIC Power Amplifier for 26-GHz 5G applications

Anna Piacibello<sup>#1</sup>, Chiara Ramella<sup>#2</sup>, Vittorio Camarchia<sup>#3</sup>, Marco Pirola<sup>#4</sup>

<sup>#</sup>Department of Electronics and Telecommunications, Politecnico di Torino, Italy

<sup>1</sup>anna.piacibello@polito.it, <sup>2</sup>chiara.ramella@polito.it, <sup>3</sup>vittorio.camarchia@polito.it, <sup>4</sup>marco.pirola@polito.it

*Abstract* — This work reports the design and experimental characterization of a 4 W Ka-band MMIC power amplifier in GaN/SiC technology, featuring a balanced stacked architecture. The proposed amplifier is composed of a pair of 2-stage amplifier branches, each including a single-transistor driver stage and a 2-stacked-transistor power stage. Small-signal characterization exhibits very good agreement between measurements and simulations, while system-level characterization, employing a 50 MHz instantaneous bandwidth, 10 dB PAPR 5G FR2 signal, demonstrates the very promising linearity performance of the proposed amplifier. The measured minimum ACPR is better than -27 dBc up to an average output power of 24 dBm, from 25 GHz to 27 GHz.

Keywords - GaN, MMIC, power amplifiers, 5G.

#### I. INTRODUCTION

The need for higher capacity for the next generations of wireless communication standards (5G/6G) requires adapting and partially redefining the architecture of the infrastructure. Traditional frequency bands below 6-GHz (5G FR1) are very crowded but pose fewer challenges from the architecture standpoint, and are therefore very attractive for industry. On the other hand, exploiting mm-wave frequency bands (FR2) would enable the adoption of very dense modulation schemes (up to 1024 Quadrature Amplitude Modulation (QAM)) with wider channel bandwidths (up to 400 MHz) [1].

The power amplifier (PA) plays in this context a key role; it must operate linearly and efficiently at mm-wave frequencies, keeping a high gain over wide bandwidths, handling signals with peak-to-average power ratio (PAPR) increasing from the classical 6 dB to 9-10 dB, and often operating with a variable load due to the presence of phased arrays at its output [2].

From a technology standpoint, Gallium Nitride (GaN) is reaching the competitive stage also at mm-wave frequencies thanks to the availability of short-gate-length (<150 nm) Microwave Monolithic Integrated Circuit (MMIC) processes. However, the gain is still an issue of this technology when Ka-band applications are targeted. Furthermore, size and absolute power at MMIC level are fundamental to increase the overall efficiency of the entire transmission system.

For these reasons, we designed, fabricated, and experimentally characterized a balanced stacked Ka-band MMIC power amplifier. Thanks to device stacking we increased the gain of the cell [3], [4] with benefits also in terms of bandwidth thanks to the increased optimum load, closer to  $50 \Omega$ . The balanced structure was conceived for a two-fold task: doubling the output power and, at the same time, increasing the load insensitivity of the stage [5]. Finally, the intrinsic linearity of this class-AB amplifier has been optimized by careful selection of the bias levels. The amplifier has promising expected performance in terms of output power (36 dBm) and gain (10 dB) over a 2 GHz bandwidth from 25 GHz to 27 GHz. At the system level, when excited with a 5G 64-QAM signal with 50 MHz bandwidth, the measured Adjacent Channel Power Ratio (ACPR) remains better than -27 dBc over the whole dynamic range, from 25 GHz to 27 GHz with a corresponding average efficiency of the order of 5%.

#### II. DESIGN AND FABRICATION

The proposed PA is designed adopting the 150 nm GaN HEMT technology of WIN Semiconductors. This GaN process is grown on a 100  $\mu$ m SiC substrate, and achieves an output power density of about 2.5 W/mm at 20 V bias operation. The cut-off frequency  $f_T$  is 35 GHz, while the maximum oscillation frequency  $f_{\text{max}}$  is much higher, which makes this process suitable for 5G applications up to 29 GHz.

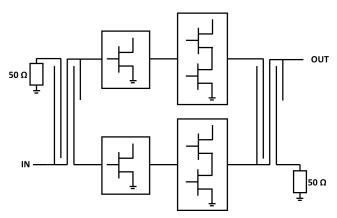

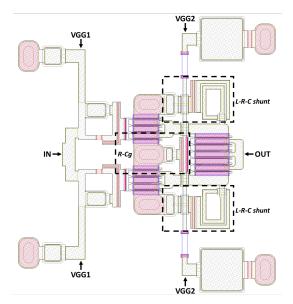

The PA architecture is shown in Fig. 1: it is a 2-stage balanced PA adopting a 2-transistor stacked cell in the final stage. The layout of the designed cell is shown in Fig. 2: as the main feature, the cell shows a symmetrical layout, achieved by splitting the common-source (CS) stage and the inter-stage matching elements into two parallel circuits. This layout ensures better performance at high frequency with respect to more conventional combinations, as it avoids uneven electromagnetic (EM) coupling effects, which may impair voltage and current distributions inside the cell and thus degrade the stacking efficiency. On the other hand,

Fig. 1. Block diagram of the proposed balanced stacked PA.

Fig. 2. Layout of the designed stacked cell.

duplication of components increases the required chip area, hence demanding a very dense layout not to compromise cell compactness.

A  $6x100 \,\mu\text{m}$  transistor is selected as base device: at 26 GHz, at 10% class-AB bias, on its optimum load  $(9.5+i14.7)\Omega$ , it provides around 32 dBm of output power at 2 dB gain compression, with associated gain and efficiency around 7 dB and 50%, respectively. This device is adopted for the common gate (CG), while the CS is implemented by adopting two  $4x75 \,\mu m$  devices in parallel. The use of smaller devices, besides ensuring cell symmetry, can be beneficial in terms of transistor's gain [6]. Each  $4x75 \,\mu m$ device is individually stabilized with an R-C pair in series to the gate. Small resistances are added in series to the gate capacitance and to the two L-C shunt pairs adopted for inter-stage matching to further improve small- and large-signal cell's stability. To ensure layout compactness, relatively small AC-shunt capacitors (not shorted at the operating frequency) should be adopted, whose value has been carefully optimized through extensive EM simulations of the whole passive structure [7]. Finally, independent gate bias voltages for the CS and CG stages are supplied, symmetrically from both sides, to allow bias tuning during characterization. A detailed analysis of the cells is reported in [8].

A single-stub output matching network matches the cell on  $50 \Omega$  and provides the 40 V drain bias. The saturated output power is nearly 34 dBm, with an associated efficiency of around 30%. A driver stage, made of a single  $6x100 \mu m$ device matched on the same optimum load of the final stages, and a  $\Pi$ -type input matching network to  $50 \Omega$  complete the PA branch. The balanced PA combines with Lange couplers at the input and output two identical single stacked PAs. The balanced configuration assures good input and output matching together with good load insensitivity. The Lange couplers

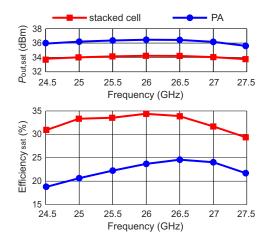

Fig. 3. Expected CW performance of the stacked cell under optimum loading conditions (red, squares) and of the balanced stacked PA (blue, circles) at saturation: output power and efficiency in the 24.5 GHz-27.5 GHz range.

are ideal candidates for power combination at high-frequency thanks to their superior performance in terms of bandwidth, directivity and isolation, as well as losses, symmetry, and area occupation.

Fig. 3 reports the expected large-signal performance of the individual stacked cell and of the complete 2-stage balanced stacked PA under continuous wave (CW) excitation in the 24.5 GHz-27.5 GHz range. The performance of the stacked cell refers to optimum loading conditions, i.e., where its output is terminated on a port with an impedance equal to its optimum load at each frequency. At around 3 dB of gain compression, the stacked cell can provide up to 34 dBm output power with an associated efficiency of 30-35% in the range 25 GHz-27 GHz. In similar gain compression conditions, the overall PA is expected to achieve an output power in excess of 36 dBm (4 W) in the same frequency range, which is consistent with the estimated losses of the output matching network and of the Lange coupler and with a slightly sub-optimal loading condition selected to equalize performance over frequency. As a consequence of the output losses as well as the presence of the driver stages, the efficiency expected from the PA is around 10 points lower than the best performance of the stacked cell, i.e., around 20%-25% in the 25 GHz-27 GHz range.

#### III. EXPERIMENTAL CHARACTERIZATION

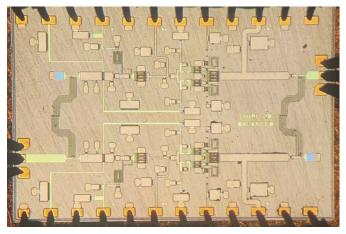

The balanced stacked PA has been characterized both in small-signal and at system-level, adopting a standard 5G FR2 modulated input signal. The photograph of the manufactured chip in the characterization setup is shown in Fig. 4. The nominal bias point is:  $V_{\rm DD} = 20$  V,  $V_{\rm GG} = -2$  V,  $I_{\rm D} = 30$  mA, for the driver stages and  $V_{\rm DD} = 40$  V,  $V_{\rm GG_{CS}} = -2$  V,  $V_{\rm GG_{CG}} = 18$  V,  $I_{\rm D} = 30$  mA for the stacked stages.

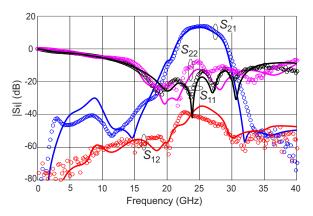

The scattering parameters have been measured in the 0.1 GHz-40 GHz range: simulation (solid lines) and measurement (symbols) results are compared in Fig. 5. The agreement is good in the whole frequency range. The small-signal gain is higher than 10 dB from 23 GHz to

Fig. 4. Photograph of the fabricated balanced stacked MMIC power amplifier (chip size is  $3.7 \text{ mm} \times 2.4 \text{ mm}$ ).

Fig. 5. Simulated (solid) and measured (symbols) scattering parameters of the manufactured balanced stacked PA at the nominal bias in the 0.1 GHz-40 GHz range.

27.5 GHz and around 13 dB in the 25 GHz-26.5 GHz range. The input and output insertion losses are both better than -10 dB from 22 GHz to 30 GHz, also thanks to the presence of the Lange couplers.

The system-level characterization has been carried out with a 5G 64-QAM input signal, featuring 50 MHz instantaneous bandwidth and 10 dB peak-to-average power ratio (PAPR). The carrier frequency was varied from 25 GHz to 27 GHz in 1 GHz step, and a linear pre-amplifier with 35 dB gain and 35 dBm saturated output power was adopted to properly drive the PA. The baseline ACPR related to the test-bench only, has been evaluated using an on-wafer thru and resulted -48 dBc.

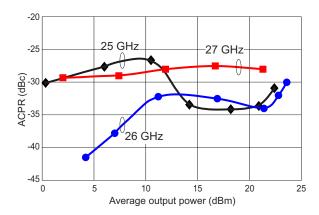

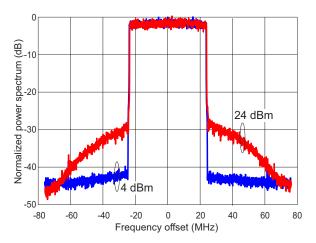

Fig. 6 presents the obtained ACPR curves as a function of the average output power up to around 24 dBm, from 25 GHz to 27 GHz. The designed amplifier is almost compliant with the 3GPP 64-QAM 5G NR standard[1] (maximum ACPR lower than -28 dBc) over the whole frequency range, where the ACPR is maintained below -26 dBc. The best linearity performance (ACPR better than -30 dBc) is obtained at the center frequency of 26 GHz, as demonstrated also in Fig. 7, showing the measured output power spectra (normalized) at

Fig. 6. Measured ACPR versus average output power in the 25-27 GHz band.

Fig. 7. Normalized measured output power spectrum at 26 GHz at low (4 dBm, blue) and high (24 dBm, red) average output power.

two different average power levels. The average efficiency achieved under modulated signal excitation is around 3-5%, compatible with the performance at 10 dB back-off of a class-AB PA with a saturated efficiency around 20-25%.

The amplifier performance is compared to literature results in Tab. 1. The proposed balanced stacked PA compares well with the state of the art at the target frequency, and represents a valid solution for 5G applications in the FR2 band.

Table 1. Comparison with state-of-the-art GaAs and GaN MMICs in the  $24\,\mathrm{GHz}\text{-}29\,\mathrm{GHz}$  range.

| Ref       | Tech     | Freq. | Psat | Gain | ACPR, dBc  |

|-----------|----------|-------|------|------|------------|

| #         | nm       | GHz   | dBm  | dB   | @ PAPR, dB |

| [9]       | 150 GaAs | 28    | 26   | 12   | -28 @ 7.3  |

| [10]      | 150 GaAs | 28    | 28.5 | 23   | -30.1 @ 7  |

| [11]      | 150 GaAs | 28    | 28.7 | 14.4 | -32 @ 10.5 |

| [12]      | 150 GaN  | 28    | 30   | 6.2  | -28.5 @ 9  |

| [13]      | 150 GaAs | 24    | 30.9 | 12.5 | -30 @ 7.5  |

| [14]      | 150 GaN  | 28.5  | 35.6 | 12   | -27 @ 8    |

| [15]      | 150 GaN  | 27.5  | 36   | 19   | NA         |

| [16]      | 150 GaN  | 28.5  | 39   | 30   | -35 @ 10   |

| This work | 150 GaN  | 26    | 36*  | 10   | -30 @ 10   |

\* simulated value

#### IV. CONCLUSION

In this contribution we presented a 4 W Ka-band balanced stacked power amplifier based on a super-symmetrical Stacked power cell in 150-nm GaN/SiC technology. The proposed amplifier has been characterized on-wafer in small-signal conditions, showing a very good agreement between measurements and simulations, and under modulated signal excitation. Adopting a 50 MHz-BW, 10 dB-PAPR 5G signal the obtained ACPR is better than -26 dBc up to 24 dBm of average output power in the full 25 GHz-27 GHz frequency range, a results that is well in line with the state of the art at this frequency and for this application.

#### ACKNOWLEDGMENT

This research was supported by the project Programma Operativo Nazionale (PON) Ricerca e Innovazione "Tecnologie abilitanti e architetture innovative per future generazioni (6G) di trasmettitori intelligenti green" (DM 1062/21, CUP E15F21003760001) funded by the Italian Ministry of Universities and Research (MUR).

The authors would also like to thank WIN Semiconductors for the fabrication of the prototype, within the framework of the "mmWave Multi-Project Runs for Selected Universities" agreement with the Italian Microwave Engineering Center for Space Applications (MECSA), and Keysight Technologies for providing the measurement instruments adopted for the system-level characterization.

#### REFERENCES

- "3<sup>rd</sup> Generation Partnership Project; Technical Specification Group Radio Access Network; NR; Base Station (BS) radio transmission and reception (release 15)," 3<sup>rd</sup> Generation Partnership Project-3GPP, TS 38.104, v.15.5.0, section 9, Standard, March 2019.

- [2] P. Choi, D. A. Antoniadis, and E. A. Fitzgerald, "Towards Millimeter-Wave Phased Array Circuits and Systems For Small Form Factor and Power Efficient 5G Mobile Devices," in 2019 IEEE International Symposium on Phased Array System & Technology (PAST), 2019, pp. 1–5.

- [3] A. K. Ezzeddine and H. C. Huang, "Ultra-Broadband GaAs HIFET MMIC PA," in 2006 IEEE MTT-S International Microwave Symposium Digest, 2006, pp. 1320–1323.

- [4] A. Piacibello, M. Pirola, V. Camarchia, C. Ramella, and R. Quaglia, "A Ku-band Compact MMIC PA based on Stacked GaAs pHEMT cells," in 2018 International Workshop on Integrated Nonlinear Microwave and Millimetre-wave Circuits (INMMIC), 2018, pp. 1–3.

- [5] H. Jeon, Y. Park, Y.-Y. Huang, J. Kim, K.-S. Lee, C.-H. Lee, and J. S. Kenney, "A Triple-Mode Balanced Linear CMOS Power Amplifier Using a Switched-Quadrature Coupler," *IEEE Trans. Syst. Sci. Cybern.*, vol. 47, no. 9, pp. 2019–2032, 2012.

- [6] F. Costanzo, A. Piacibello, M. Pirola, P. Colantonio, V. Camarchia, and R. Giofrè, "A Novel Stacked Cell Layout for High-Frequency Power Applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 6, pp. 597–599, 2021.

- [7] C. Ramella, A. Piacibello, V. Camarchia, and M. Pirola, "Electro-magnetic Crosstalk Effects in a Millimeter-wave MMIC Stacked Cell," in *INMMiC 2020*, 2020, pp. 1–3.

- [8] A. Piacibello, C. Ramella, V. Camarchia, and M. Pirola, "Compact GaN-based Stacked Cells for 5G Applications at 26 GHz," in 2022 *Microwave Mediterranean Symposium (MMS)*, 2022, pp. 1–5.

- [9] D. P. Nguyen, B. L. Pham, and A.-V. Pham, "A compact 29% PAE at 6 dB power back-off E-mode GaAs pHEMT MMIC Doherty power amplifier at Ka-band," in *IEEE MTT-S IMS 2017*, 2017, pp. 1683–1686.

- [10] H. D. Lee, S. Kong, B. Park, K. C. Lee, J.-S. Park, and J.-G. Kim, "A 28-GHz 28.5-dBm power amplifier using 0.15-µm InGaAs E-mode pHEMT technology," in *ISOCC 2018*, 2018, pp. 257–258.

- [11] D. P. Nguyen, T. Pham, and A.-V. Pham, "A 28-GHz Symmetrical Doherty Power Amplifier Using Stacked-FET Cells," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 6, pp. 2628–2637, 2018.

- [12] R. Ishikawa, T. Seshimo, Y. Takayama, and K. Honjo, "A 28-GHz-Band GaN HEMT MMIC Doherty Power Amplifier Designed by Load Resistance Division Adjustment," in *EuMIC 2021*, 2022, pp. 241–244.

- [13] R. Quaglia, V. Camarchia, T. Jiang, M. Pirola, S. Donati Guerrieri, and B. Loran, "K-Band GaAs MMIC Doherty Power Amplifier for Microwave Radio With Optimized Driver," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 11, pp. 2518–2525, 2014.

- [14] K. Nakatani, Y. Yamaguchi, Y. Komatsuzaki, and S. Shinjo, "Millimeter-Wave GaN Power Amplifier MMICs for 5G Application," in *IEEE ISCAS 2019*, 2019, pp. 1–4.

- [15] M. Bao, D. Gustafsson, R. Hou, Z. Ouarch, C. Chang, and K. Andersson, "A 24–28-GHz Doherty Power Amplifier With 4-W Output Power and 32% PAE at 6-dB OPBO in 150-nm GaN Technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 6, pp. 752–755, 2021.

- [16] D. Wohlert, B. Peterson, T. R. Mya Kywe, L. Ledezma, and J. Gengler, "8-Watt Linear Three-Stage GaN Doherty Power Amplifier for 28 GHz 5G Applications," in *IEEE BCICTS 2019*, 2019, pp. 1–4.