Doctoral Dissertation Doctoral Program in Electrical, Electronics and Communications Engineering (35<sup>th</sup>cycle)

# Heterogeneous Acceleration for 5G New Radio Channel Modelling

## **Using FPGAs and GPUs**

By

### Nasir Ali Shah

\*\*\*\*\*

### Supervisor(s):

Prof. Luciano Lavagno, Supervisor Eng. Roberto Quasso, Industrial Supervisor

### **Doctoral Examination Committee:**

Prof. Roberto Passerone, Referee, University of Trento, Italy Dr. Osama B. Tariq, Referee, Newcastle University, UK Prof. Mohammad Mozumdar, California State University, USA Prof. Mario R. Casu, Politecnico di Torino, Italy Prof. Mihai T. Lazarescu, Politecnico di Torino, Italy

> Politecnico di Torino 2023

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Nasir Ali Shah 2023

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my loving parents and my beloved wife, whose unwavering support has been instrumental in my journey. I am forever grateful for your encouragement and sacrifices. Their belief in my abilities and relentless encouragement have propelled me forward. I am deeply grateful for their presence in my life, and this thesis stands as a testament to their unwavering dedication and invaluable contributions.

### Acknowledgements

Completing my doctoral thesis fills me with a sense of accomplishment, and writing this acknowledgment serves as the final touch. Undertaking this doctoral journey has profoundly influenced both my research and personal growth. Thus, I would like to take a moment to acknowledge and express my gratitude to those who have provided unwavering support and assistance throughout this transformative period. Without the guidance of my supervisors, the invaluable contributions of my research group members, and the unwavering support of my family and friends, this work would not have reached its completion.

I would like to express my heartfelt gratitude and deep appreciation to my advisor Prof. Luciano Lavagno and Prof. Mihai Teodor Lazarescu for their invaluable assistance and humble guidance throughout the duration of my Ph.D. Their unwavering support, valuable insights, and approachable nature have greatly contributed to my academic and personal growth. I am truly grateful for their mentorship and the positive impact they have had on my research journey. I could not have imagined having better supervisors.

Further, I extend my sincere gratitude to my external advisors Eng. Scarpina Salvatore and Eng. Roberto Quasso for their assistance at every stage of the research project. I would like to acknowledge TIM for providing the necessary resources and financial support for this research.

I would like to express my sincere appreciation to my lab mates from the HLS group for their invaluable support and collaboration throughout my Ph.D. Their expertise and shared insights have greatly enriched my research experience. I am grateful for the fruitful discussions, the exchange of ideas, and the sense of community we have built together. Their contributions have played a significant role in the success of my thesis, and I am honored to have had the opportunity to work alongside such talented individuals.

Finally, I would like to express my deepest gratitude to my parents and my wife for their unwavering love, support, and sacrifices throughout my Ph.D. journey. Their constant encouragement, belief in my abilities, and understanding of the demanding nature of doctoral research have been the cornerstone of my success.

### Abstract

The channel model is the most computationally demanding element in link-level simulations for multiple-input and multiple-output (MIMO)-based fifth-generation new radio (5G-NR) communication systems. Accurately modeling the wireless channel is crucial for developing and assessing wireless networks beyond 5G-NR. The use of realistic geometry-based channel models, such as the three-dimensional spatial channel model (3D-SCM), requires more computational resources for simulation. Channel emulation is employed to validate the functionality and performance of channel models during the network planning phase. General-purpose central processing unit (CPU)-based emulation platforms have limitations in accurately replicating propagation environments because they are either too simplified or have impractical execution time. Hardware accelerators based on specialized computing platforms such as FPGAs and GPUs can be employed to alleviate the load of complex computations and enhance the quality of results.

This study aims to tackle this matter by investigating diverse methodologies and optimization techniques for building an efficient hardware accelerator from a high-level specification. The process of developing applications for specialized architectures is intricate and requires thorough knowledge of hardware design languages and target architectures.

The first part of this study proposes an efficient re-configurable implementation of the 3<sup>rd</sup> Generation Partnership Project (3GPP) 3D-SCM for 5G-NR on Xilinx and Intel FPGA platforms using high-level synthesis (HLS)-based design flow. It explores the effect of various HLS optimization techniques on the total latency and hardware resource utilization on the target acceleration platforms. By using the proposed methodologies, the accelerated designs on Xilinx Alveo U280 and Intel Arria 10 FPGA achieved speedups of **65X** and **95X**, respectively, compared to the baseline CPU implementation. This speedup enhances to **173X** by optimizing the

design to utilize specialized resources present on Xilinx FPGA, such as UltraRAM (URAM) and High-Bandwidth Memory (HBM).

This study's second part focuses on accelerating the 3GPP channel model using GPU platforms. This study investigates different optimization techniques to exploit the parallelism and memory hierarchy of the GPU, specifically focusing on CUDA-based approaches. The experimental results demonstrate that the developed system achieves a significant speedup of approximately **240X** over CPU-based implementation. The GPU design exhibits a 33.3 % increase in single precision performance compared to the design accelerated on a datacenter-class FPGA. However, it also consumes 7.5 % more energy.

## Contents

|   |      |                                  |                                             | xi   |

|---|------|----------------------------------|---------------------------------------------|------|

|   |      |                                  |                                             | xiii |

| 1 | Intr | oductio                          | n                                           | 1    |

|   | 1.1  | Wirele                           | ess Network Planning and Channel Simulation | 2    |

|   |      | 1.1.1                            | Wireless channel simulation                 | 3    |

|   | 1.2  | Thesis                           | Outline                                     | 6    |

| 2 | Fift | h-gener                          | ation Mobile Network and Channel Modeling   | 8    |

|   | 2.1  | Key Enabling Technologies for 5G |                                             | 11   |

|   |      | 2.1.1                            | Massive-MIMO systems                        | 11   |

|   |      | 2.1.2                            | Network slicing                             | 13   |

|   |      | 2.1.3                            | Network functions virtualization            | 14   |

|   |      | 2.1.4                            | Vehicle-to-everything communication         | 15   |

|   |      | 2.1.5                            | Device-to-Device communications             | 16   |

|   | 2.2  | Wirele                           | ess Channel Modeling Methodologies          | 17   |

|   |      | 2.2.1                            | Analytical channel models                   | 18   |

|   |      | 2.2.2                            | Physical channel models                     | 19   |

|   |      | 2.2.3                            | Standard channel models                     | 22   |

|   |      | 2.2.4                            | 3GPP 3D channel model for 5G-NR             | 25   |

| 3 | 3GP | P Chan                                    | nnel Model for 5G-NR                            | 26 |

|---|-----|-------------------------------------------|-------------------------------------------------|----|

|   | 3.1 | Three-dimensional (3D) Channel Modeling   |                                                 |    |

|   | 3.2 | Proced                                    | lure for Channel Generation                     | 29 |

|   |     | 3.2.1                                     | Large-scale fading                              | 29 |

|   |     | 3.2.2                                     | Small-scaling fading                            | 32 |

|   |     | 3.2.3                                     | Channel models for link-level evaluations       | 40 |

| 4 | FPG | GA Base                                   | ed Acceleration and HLS                         | 41 |

|   | 4.1 | Desigr                                    | n Flow                                          | 42 |

|   | 4.2 | High-l                                    | evel synthesis                                  | 44 |

|   |     | 4.2.1                                     | HLS flow for FPGAs                              | 45 |

|   |     | 4.2.2                                     | OpenCL in hardware acceleration                 | 46 |

|   |     | 4.2.3                                     | Key advantages of HLS                           | 48 |

|   | 4.3 | HLS T                                     | Cools and Optimizations                         | 51 |

|   |     | 4.3.1                                     | Vitis HLS                                       | 51 |

|   |     | 4.3.2                                     | Intel FPGA SDK for OpenCL                       | 51 |

|   | 4.4 | Implementation and Optimization for FPGAs |                                                 | 54 |

|   |     | 4.4.1                                     | Loop based optimizations                        | 55 |

|   |     | 4.4.2                                     | Memory oriented optimizations                   | 59 |

| 5 | FPG | GA Acce                                   | eleration of 3GPP 3D Channel Model              | 62 |

|   | 5.1 | Chann                                     | el Coefficients Calculation using FPGA          | 64 |

|   |     | 5.1.1                                     | FPGA Implementation                             | 67 |

|   |     | 5.1.2                                     | Roofline model                                  | 68 |

|   |     | 5.1.3                                     | ALVEO U280                                      | 70 |

|   |     | 5.1.4                                     | Intel Arria10 1150GX                            | 72 |

|   |     | 5.1.5                                     | Optimizations for efficient FPGA implementation | 73 |

|                             | 5.2    | Result                 | s and Analysis                    | . 78  |

|-----------------------------|--------|------------------------|-----------------------------------|-------|

|                             |        | 5.2.1                  | Latency                           | . 79  |

|                             |        | 5.2.2                  | Resource utilization              | . 83  |

|                             |        | 5.2.3                  | Power and energy                  | . 86  |

|                             | 5.3    | Conclu                 | usion                             | . 89  |

| 6                           | GPU    | J Accele               | eration of 3GPP 3D Channel Model  | 91    |

|                             | 6.1    | Relate                 | d Work                            | . 92  |

|                             | 6.2    | GPU E                  | Based Hardware Acceleration       | . 93  |

|                             |        | 6.2.1                  | Global memory                     | . 94  |

|                             |        | 6.2.2                  | Shared memory                     | . 95  |

|                             |        | 6.2.3                  | Thread synchronization            | . 95  |

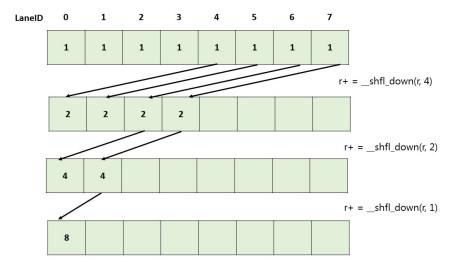

|                             |        | 6.2.4                  | Register-based parallel reduction | . 96  |

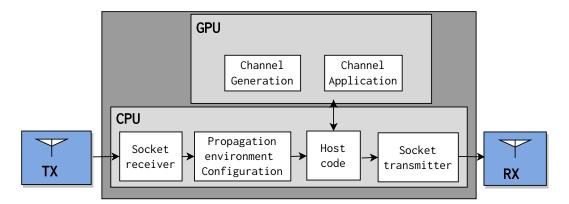

|                             | 6.3    | Chann                  | el Emulator Acceleration on GPU   | . 97  |

|                             | 6.4    | Results and Discussion |                                   | . 100 |

|                             |        | 6.4.1                  | Coding Style: CUDA vs. HLS        | . 104 |

|                             | 6.5    | Conclu                 | usion                             | . 106 |

| 7                           | Con    | clusion                | and Future work                   | 108   |

| Re                          | eferen | ices                   |                                   | 110   |

| Ap                          | opend  | lix A 3                | GPP Channel Parameters            | 121   |

| Appendix B FPGA HLS code 12 |        |                        |                                   | 126   |

## **List of Figures**

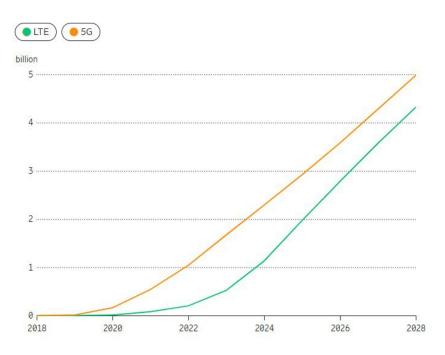

| 2.1 | 5G and 4G subscription uptake in the first years of deployment | 9  |

|-----|----------------------------------------------------------------|----|

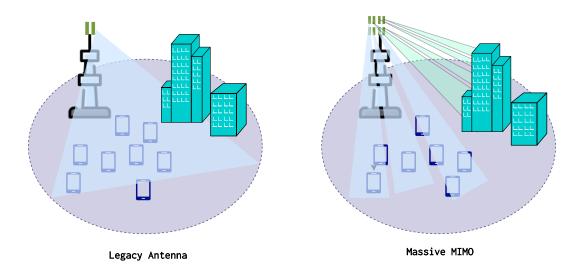

| 2.2 | Comparison of legacy antenna and massive-MIMO coverage         | 12 |

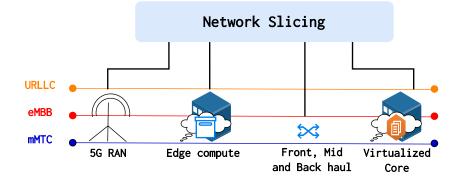

| 2.3 | Network slicing in 5G-NR                                       | 13 |

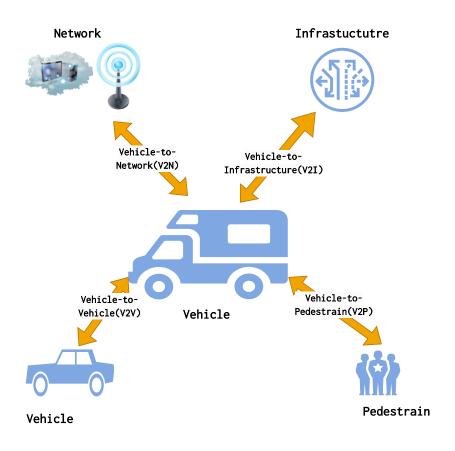

| 2.4 | Vehicle-to-everything communication                            | 16 |

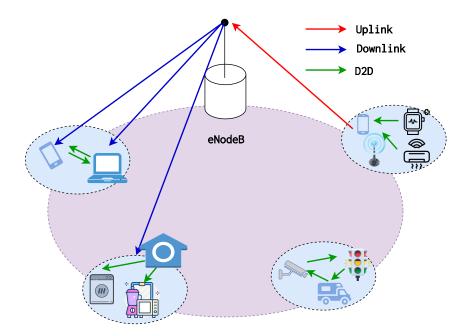

| 2.5 | D2D communication                                              | 17 |

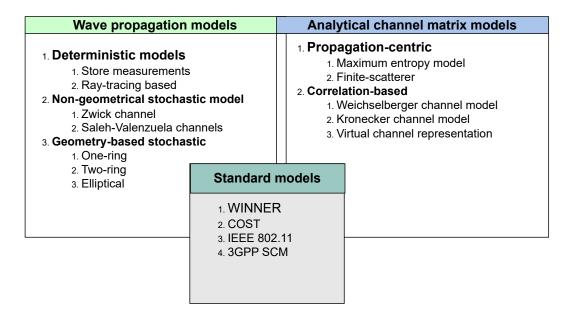

| 2.6 | MIMO channel modelling methodologies                           | 18 |

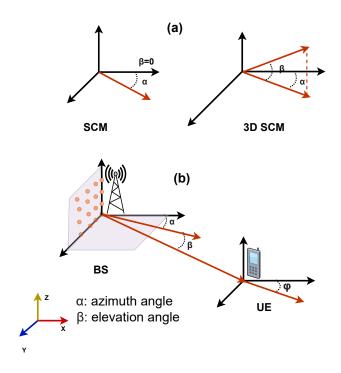

| 3.1 | 2D SCM to 3D                                                   | 28 |

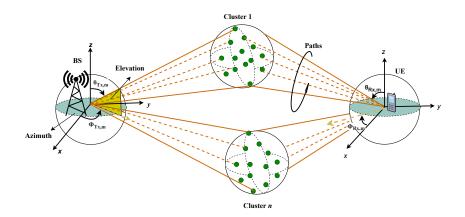

| 3.2 | Multi-path scattering in 3GPP channel model                    | 28 |

| 3.3 | Channel coefficient generation in 3GPP 3D channel model        | 30 |

| 3.4 | Pathloss distances in outdoor and indoor environments          | 31 |

| 3.5 | Angles of arrival and departure in fast fading model           | 34 |

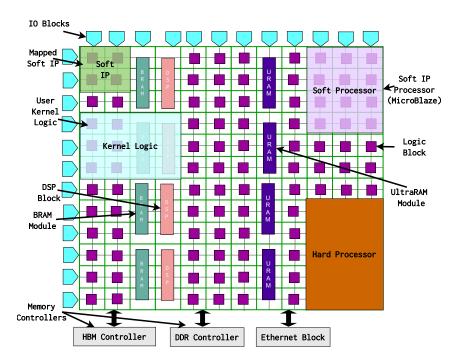

| 4.1 | Modern FPGAs with hard logic components                        | 42 |

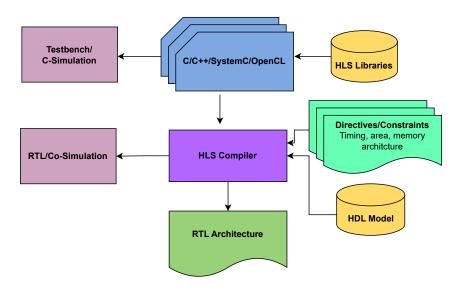

| 4.2 | High-level synthesis Flow                                      | 46 |

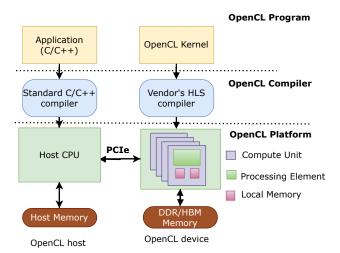

| 4.3 | OpenCL based hardware acceleration flow.                       | 47 |

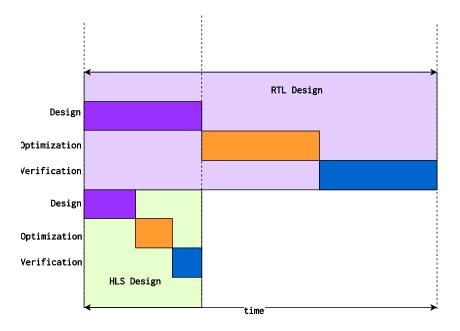

| 4.4 | HLS and RTL flow for FPGA design                               | 49 |

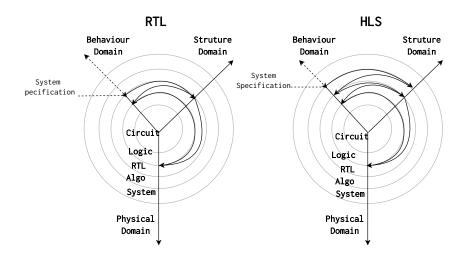

| 4.5 | RTL vs HLS design space exploration                            | 50 |

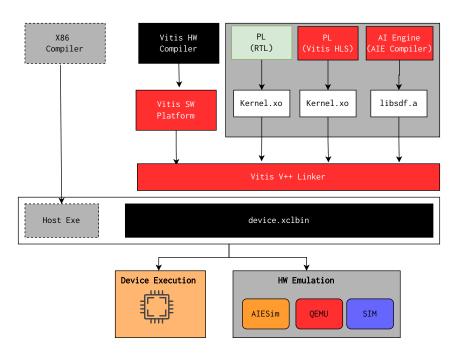

| 4.6 | Vitis development flow for acceleration kernels                | 52 |

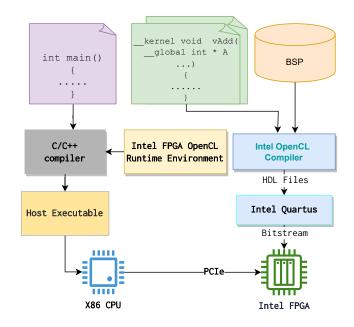

| 4.7 | Intel FPGA SDK for OpenCL                                      | 53 |

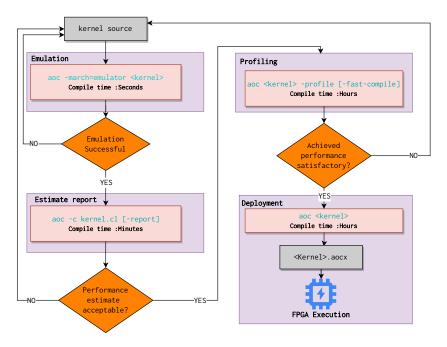

| 4.8  | Intel FPGA SDK flow                                                                           |

|------|-----------------------------------------------------------------------------------------------|

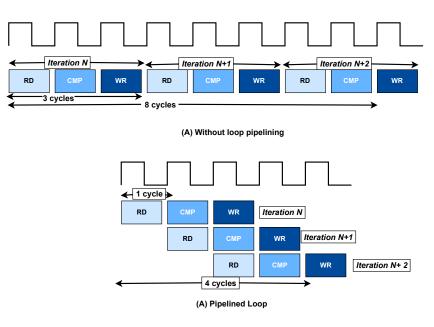

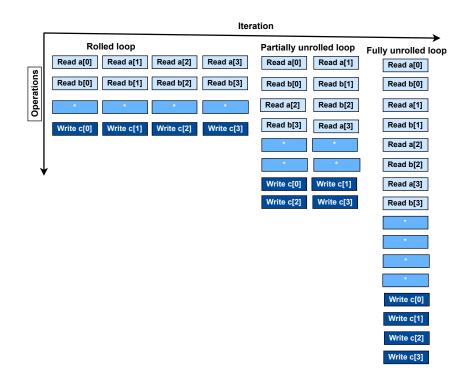

| 4.9  | Loop pipelining                                                                               |

| 4.10 | Loop unrolling/vectorization                                                                  |

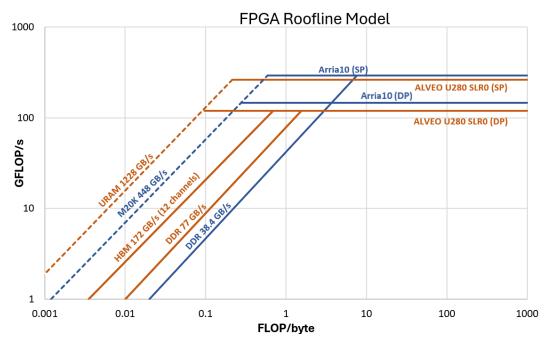

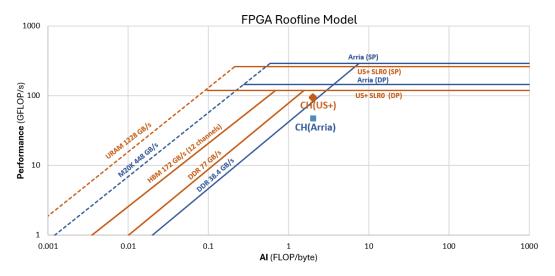

| 5.1  | Roofline model for Alveo U280 and Arria 10 FPGAs 73                                           |

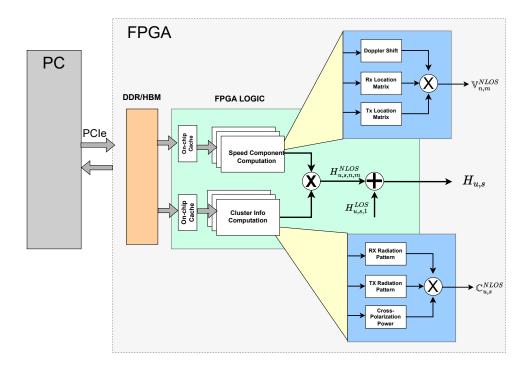

| 5.2  | Channel coefficient computation                                                               |

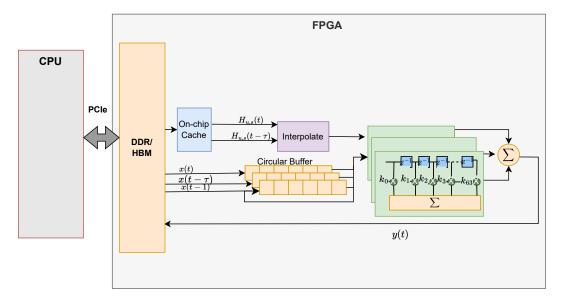

| 5.3  | Coefficient application to channel samples                                                    |

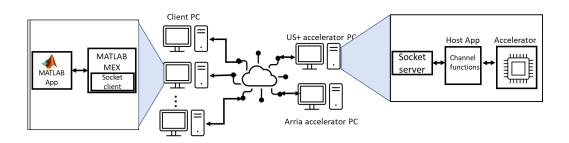

| 5.4  | Emulation system setup                                                                        |

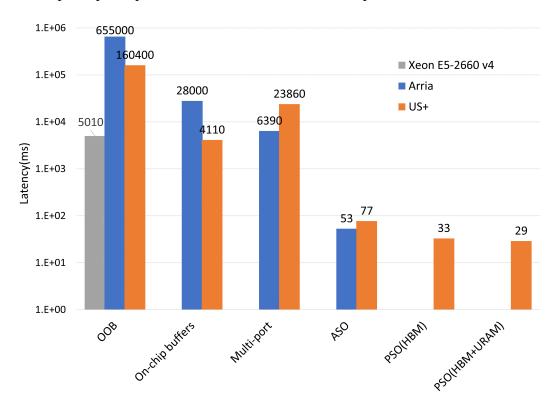

| 5.5  | Average execution latency (log scale)                                                         |

| 5.6  | Roofline performance on the target platforms                                                  |

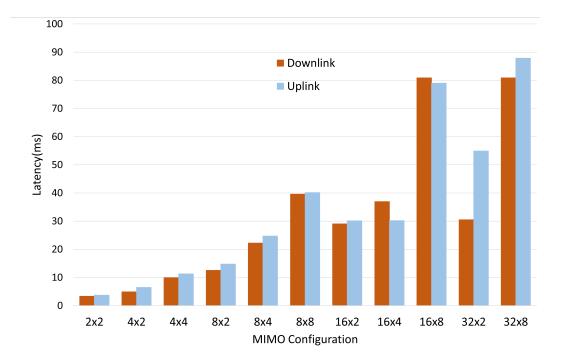

| 5.7  | Latency for Uplink and Downlink MIMO configuration 83                                         |

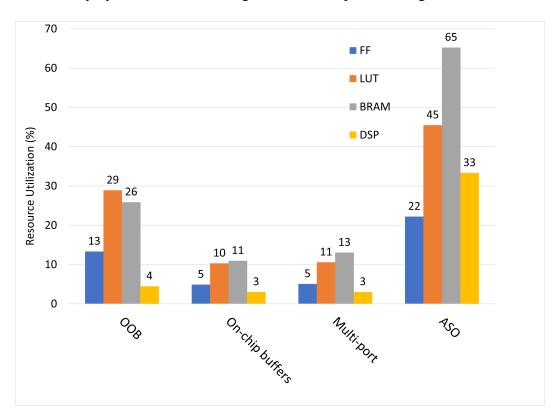

| 5.8  | Resource utilization on Arria                                                                 |

| 5.9  | Single SLR resource utilization on US+                                                        |

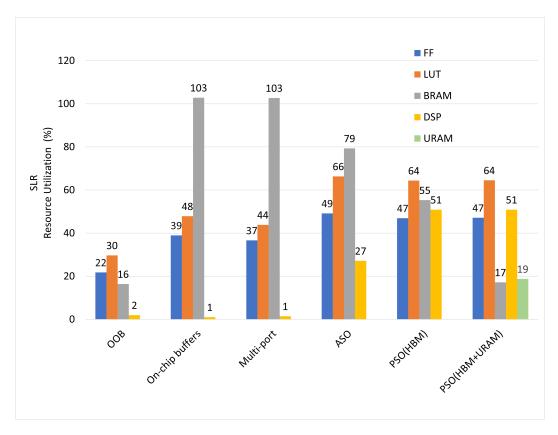

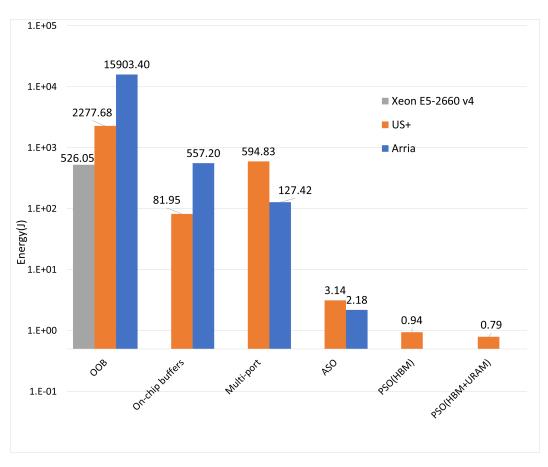

| 5.10 | Energy utilization on target platforms (log scale)                                            |

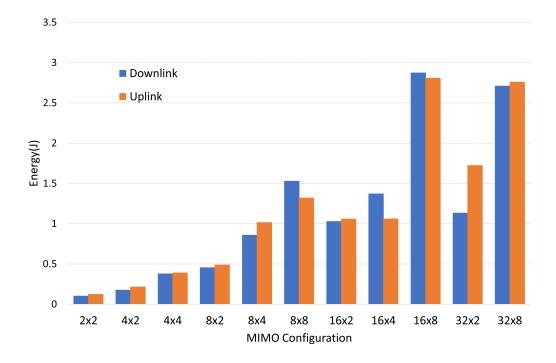

| 5.11 | Energy utilization on for various MIMO downlink and uplink con-<br>figuration on US+ platform |

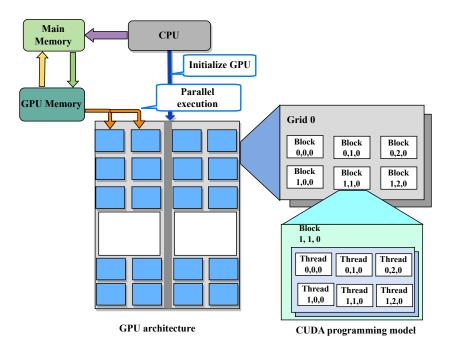

| 6.1  | GPU architecture and CUDA programming model                                                   |

| 6.2  | Parallel reduction using registers                                                            |

| 6.3  | 3GPP 3D channel model on GPU                                                                  |

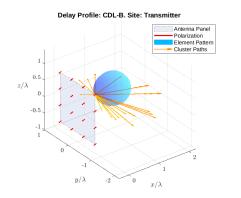

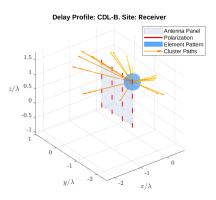

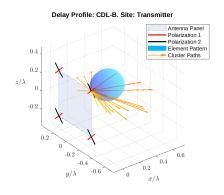

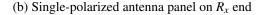

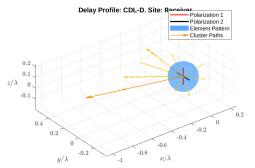

| 6.4  | MIMO antenna configuration in CDL-B profile for non-line-of-sight (NLOS) clusters             |

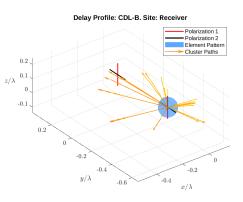

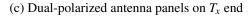

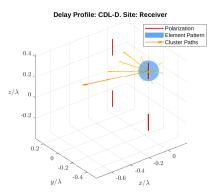

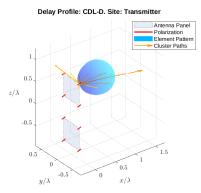

| 6.5  | MIMO antenna configuration in CDL-D profile for line-of-sight (LOS) clusters                  |

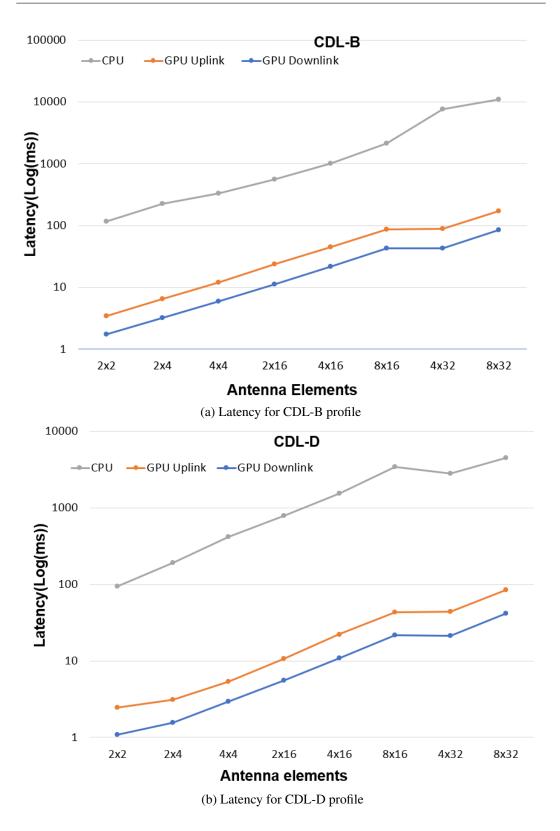

| 6.6  | Execution time on CPU and GPU platforms                                                       |

## **List of Tables**

| 2.1 | Physical vs. Analytical channel models                                                                       |

|-----|--------------------------------------------------------------------------------------------------------------|

| 2.2 | Comparison of 5G Channel Models                                                                              |

| 3.1 | Notations in 3GPP channel generation                                                                         |

| 5.1 | FPGA acceleration platforms specification                                                                    |

| 5.2 | Summary of channel model emulator parameters                                                                 |

| 5.3 | Kernel latency and speed up achieved compared to OOB and CPU implementation, with ASO, PSO, HBM, and URAM 80 |

| 5.4 | Resource Utilization                                                                                         |

| 5.5 | Power and energy utilization of baseline and accelerated designs 87                                          |

| 6.1 | Kernel latency for a combination of MIMO elements in CDL-B NLOS103                                           |

| 6.2 | Kernel latency for a combination of MIMO elements in CDL-D LOS 103                                           |

| 6.3 | Accelerated kernel latency and energy consumption                                                            |

| 6.4 | Resource utilization of accelerated designs                                                                  |

## Acronyms

| Abbreviation | Explanation                                    |

|--------------|------------------------------------------------|

| 2D           | Two-dimensional                                |

| 2D-SCM       | Two-dimensional spatial channel model          |

| 3D           | Three-dimensional                              |

| 3D-SCM       | Three-dimensional spatial channel model        |

| 3D-UMa       | 3D urban macro                                 |

| 3GPP         | 3 <sup>Rd</sup> Generation Partnership Project |

| 4G           | Fourth-generation                              |

| 5G           | Fifth-generation                               |

| 5G-NR        | Fifth-generation new radio                     |

| AOA          | Azimuth angle of arrival                       |

| AOD          | Azimuth angle of departure                     |

| ASIC         | Application-specific integrated circuit        |

| ASO          | Application-specific optimizations             |

| BRAM         | Block RAM                                      |

| BS           | Base station                                   |

| BSP          | Board support package                          |

| CDFG         | Control and data flow graph                    |

| CDL          | Cluster delay line                             |

| CIR          | Channel impulse response                       |

| CLB          | Configurable logic block                       |

| CPU          | General-purpose central processing unit        |

| CU           | Compute unit                                   |

| CUDA         | Compute Unified Device Architecture            |

| D2D          | Device-to-device                               |

| DDR          | Double Data Rate                               |

|              |                                                |

| Abbreviation | Explanation                             |

|--------------|-----------------------------------------|

| DP           | Double-precision                        |

| DRAM         | Dynamic RAM                             |

| DSP          | Digital signal processor                |

| FIR          | Finite impulse response                 |

| FP           | Floating-point                          |

| FPGA         | Field programmable gate array           |

| gNB          | Next generation NodeB                   |

| GPU          | Graphics processing unit                |

| GSCM         | Geometry-based stochastic channel model |

| HBM          | High-Bandwidth Memory                   |

| HDL          | Hardware Description Language           |

| HLL          | High-level language                     |

| HLS          | High-level synthesis                    |

| II           | Initiation interval                     |

| InH          | Indoor-Office                           |

| IOT          | Internet-of-things                      |

| LOS          | Line-of-sight                           |

| LSP          | Large-scale parameter                   |

| LTE          | Long-term evolution                     |

| LUT          | Look-up tables                          |

| MIMO         | Multiple-input and multiple-output      |

| MPC          | Multipath component                     |

| MS           | Mobile station                          |

| NFV          | Network functions virtualization        |

| NGSM         | Non-geometrical stochastic model        |

| NLOS         | Non-line-of-sight                       |

| O2I          | Outdoor to indoor                       |

| OOB          | Out-of-the-box                          |

| OpenCL       | Open Computing Language                 |

| PAS          | Power angular spectrum                  |

| PE           | Processing element                      |

| PSO          | Platform-specific optimizations         |

| RF           | Radio frequency                         |

| RMa          | Rural-Macrocell                         |

|              |                                         |

| Abbreviation | Explanation                      |

|--------------|----------------------------------|

| RTL          | Register-Transfer-Level          |

| SCM          | Spatial channel model            |

| SIMD         | Single instruction multiple data |

| SM           | Streaming multiprocessor         |

| SP           | Single-precision                 |

| SRAM         | Static RAM                       |

| SSP          | Small-scale parameter            |

| TDL          | Tapped delay line                |

| TDP          | Thermal design profile           |

| UE           | User equipment                   |

| UMa          | Urban-Macrocell                  |

| UMi          | Urban-Microcell                  |

| URAM         | UltraRAM                         |

| V2V          | Vehicle-to-vehicle               |

| WG           | Work-group                       |

| WI           | Work-item                        |

| ZOA          | Zenith angle of arrival          |

| ZOD          | Zenith angle of departure        |

|              |                                  |

### Chapter 1

## Introduction

The emergence of always-on systems, internet-of-things (IOT), self-driving vehicles, and other digital systems, has led to the development of a novel networking infrastructure capable of accommodating the demands of these devices. The available spectrum is becoming increasingly congested because of the massive increase in the number of these devices. Consumers may experience poor service quality, unreliable connections, reduced speeds, or even complete outages in highly congested regions or during peak usage hours. Long-term evolution (LTE) system which was an incremental improvement to fourth-generation (4G) mobile network has already reached its maturity. The LTE technology has undergone a subsequent improvement to LTE-Advanced, which satisfies the established standards for 4G networks. The fifth-generation (5G) standard is currently forthcoming and presents numerous modifications in comparison to its predecessor, 4G. A great deal of focus has been devoted to the physical features of radio communication, including frequency and cell positioning, hence the substitute designation of the standard as fifth-generation new radio (5G-NR) [1]. Mobile broadband is the main motivating factor behind the development of 5G cellular communication network since the enhancement of user data rates has long been a top goal in the research and development of mobile communications systems. Broadband human-oriented communications, time-sensitive applications with ultra-low latency, and massive connectivity for the IOT are just some of the use cases that 5G-NR hopes to address [2].

Before and during the physical deployment phase, new cellular technology must first be tested in a simulation environment. The term "simulation" refers to the practice of creating a computerized model of a physical or hypothetical system to test its functionality. Mathematical channel models are created to obtain a greater understanding of the factors that impact the transmission of wireless signals through a communication medium [3]. These models also facilitate the extraction and development of channel state information (CSI) from channel impulse response (CIR) such as fading, Doppler, delay, and azimuth [4].

The simulation of channel models has emerged as a vital tool in the mobile network planning process. Accurately modeling the channel is a crucial aspect in the design and evaluation of wireless networks beyond 5G-NR. In order to achieve a precise depiction of propagation conditions, a multitude of radio frequency parameters must be meticulously calibrated. It is necessary to recalculate parameters even after deployment in the event of any changes to the network configuration or propagation conditions, such as alterations to the number or positioning of antennas.

### 1.1 Wireless Network Planning and Channel Simulation

The process of network planning involves the conceptualization and design of wireless networks prior to their actual physical implementation. The process comprises multiple phases, including network dimensioning, pre-planning, detailed planning, verification, and optimization. The primary objective of the network planning process is to attain the utmost network efficiency while minimizing expenses.

Optimal performance at minimal cost is a difficulty faced by the majority of network operators due to the rising demand for high data-rate network traffic and the growing cost of operating communication networks. For best network performance, planners today often use computer-aided network tools to simplify the tedious task of network planning. Locating the most suitable spots for setting up network nodes is a crucial part of every network design process. This analysis can be performed depending on the network coverage requirement and the network capacity requirement by means of a channel information map. Network planning evaluations can be broken down into three tiers: regional, cluster, and link level [5].

**Regional level** This includes a high-level assessment to estimate investment cost and population coverage in a given region.

- **Cluster level** This stage consists of immediate-fidelity simulations and estimates bit-rate targets, frequency channels, etc.

- **Link level** This stage of network planning is used to optimize radio frequency parameters such as shadowing, path-losses antenna design, etc.

### **1.1.1** Wireless channel simulation

When it comes to channel planning, the wireless channel model is the most crucial component. It should be able to model a wide range of frequency bands, a substantial number of design parameters, and a variety of different alternatives for deployment. It is extremely vital to model and simulate the impact that a physical channel has on a transmitted signal due to environment. Because of the significant differences in the propagation medium across location, time, and frequency, it is of even greater significance for wireless communication systems.

Link-level simulation, analysis, and measurements are crucial in creating novel wireless communication systems. Each of these methods has its own set of benefits, thus it is important to use all three of them. Measurements serve as the foundation for channel modeling and give the definitive performance standard for any transceiver architecture. As a result, measurements are required in order to conduct analysis and simulations. However, carrying out measures is not only very expensive but also very time intensive, and it is difficult to adjust them to certain communication scenarios. Analytical models have the capacity to show correlations between the important parameters of a system, which is one of the many benefits of these studies. However, to make analytical models tractable, it is often necessary to apply several restrictive assumptions and simplifications. This reduces the value of analytical conclusions when applied to more realistic settings.

Channel simulators are the tools to evaluate the efficiency and performance of a communication system in a controlled environment. The outcomes of the simulations are employed as input by planning tools, which are adopted by all network operators, to ascertain the network infrastructure, including network nodes, and its configuration. The creation of a theoretical model enables the evaluation of the operational efficiency of real devices. The vast majority of today's network service providers construct these models through the use of computer simulations, as well as carrying out laboratory and real-world assessments on commercial gadgets to verify the attainment of anticipated outcomes.

Channel simulators are an extremely efficient way for carrying out performance evaluations on the various components of a wireless communication system. The evaluation of compliance with communication standards is crucial in the testing of novel communication algorithms. This enables the determination of how effective they are in meeting the essential communication standard requirements. One of the assessments involves the assessment of system performance in the presence of a communication channel. These simulations are considered to be a more dependable and authentic means of conducting experiments due to their ability to replicate real-life scenarios. However, they are often characterized by their complex nature, high costs, and time-consuming processes, which may render them impractical for deploying a large number of nodes. It is feasible to represent the wireless channel as an finite impulse response (FIR) filter that possesses random coefficients that vary over time. Increasing the number of coefficients can lead to a more effective approach in addressing real-world scenarios [6]. However, this may result in an increase in computational complexity.

Historically, network planners prioritized the implementation of simplified channel models designed for execution on general-purpose central processing unit (CPU) platforms, resulting in significantly longer execution times. An alternative method that has been previously employed to enhance the quality of results and energy efficiency involves the use of emulation platforms based on hardware. Applicationspecific integrated circuits (ASICs) have been predominantly utilized due to their ability to facilitate high throughput and low power consumption. Nevertheless, this category of circuits lacks flexibility and requires describing the functionality of the application at the Register-Transfer-Level (RTL) through a Hardware Description Language (HDL) like VHDL or Verilog, which can be a challenging undertaking.

Network planning tools must have a high degree of flexibility, as they must be able to adjust their parameters to accommodate various propagation scenario simulations. Hardware acceleration is a technology that shows potential in addressing these requirements [7]. This technology facilitates the rapid creation of a channel model emulator from a high-level description, typically in C/C++/CUDA, and implementing it on a reconfigurable hardware device. The software-controlled emulator can be conveniently configured to simulate various propagation scenarios.

Field programmable gate arrays (FPGAs) are one of the candidate technology which is frequently used as hardware acceleration platform and provide a compelling trade-off between power consumption and performance. FPGAs present a compelling trade-off between power consumption and performance, and facilitate the creation of customized computing architecture by means of a configuration file (also called bitstream). These accelerators can be adopted to new applications by using a different configuration file designed with the required specifications. FPGA-based emulators provides, in theory, a suitable compromise between adaptability and processing power. However, the platform's programmability becomes restricted because FPGAs require an HDL description as part of the conventional design flow.

Another candidate technology for hardware acceleration is graphics processing unit (GPU). With the advancement of technology, the GPU has undergone significant improvements, rendering it a powerful, programmable, and extensively parallel unit [8]. Consequently, it has emerged as a crucial constituent in High performance computing (HPC) systems and is currently the most prominent form of hardware accelerator. Due to their significant computational throughput and parallelism, GPUs have been deemed appropriate for general-purpose computing. Researchers have been using GPUs for a wide variety of scientific applications [9]. Efficient management of GPU resources can be achieved through high-level programming languages (such as Compute Unified Device Architecture (CUDA) from NVIDIA) based on the underlying computing architectures, resulting in improved performance.

The proposed solution aims to tackle the aforementioned problem by introducing a design methodology that utilizes hardware acceleration platforms such as FPGAs and GPUs that are designed to compute the time-varying coefficients of fading channel simulators. By utilizing these acceleration platforms and the suggested approaches, individuals without specialized knowledge in specialized computing architectures can enhance the pace of their simulation advancements in comparison to traditional software. The results of the implementation demonstrate that the suggested methodology facilitates the efficient creation of communication channels, while concurrently decreasing the processing duration. In light of the dispersed nature of the channel, the hardware emulation technologies have higher advantages in terms of performance and power consumption over the CPU-based implementation.

This doctoral thesis seeks to enhance the programmability of heterogeneous FPGA and GPU-based emulation platforms by replacing HDL-based flow with

higher-level ones. Use of high-level synthesis (HLS)high-level language (HLL) methodologies and associated tools to produce specialized architectures enables rapid prototyping [10].

### **1.2** Thesis Outline

The present doctoral dissertation is structured into two primary sections. The first part is the background, presented in chapter 2 and chapter 3. This section presents an extensive review of the 5G-NR cellular technology, channel modelling concepts and methodologies, standard channel models, hardware acceleration platforms, HLS flow and optimizations, and other relevant concepts. The subsequent section, encompassing chapter 4 to chapter 6, relates to the various contributions to research. The work covers extensive details relating to our proposal of a reconfigurable channel model on FPGA and GPU acceleration platforms compiled from HLL specifications.

**Chapter 2**: provides the background information on 5G-NR, key benefits associated with the new cellular technology, and a short survey of channel modeling methodologies.

**Chapter 3**: provides background on three-dimensional (3D) channel modelling and discusses various steps and procedures in generation of 3<sup>Rd</sup> Generation Partnership Project (3GPP) channel model.

**Chapter 4**: discusses design flow for FPGA acceleration platforms. It presents a detailed discussion of HLS tools and the associated benefits for modeling hardware designs using a high-level specification. It introduces the two HLS tools from Xilinx and Intel for FPGA-based acceleration. It also discusses a variety of optimizations and strategies that can improve the quality of result for HLS-based designs.

**Chapter 5**: is dedicated to the design space exploration of Chapter 5 discusses the implementation and design space exploration of the 3GPP 3D channel model on Xilinx and Intel FPGA platforms using HLS tools. HLS-based optimizations and their respective on the implementation are presented. This chapter also analyzes the effort required to accelerate applications on FPGA platforms from different vendors. **Chapter 6**: presents the optimization techniques and methodologies for accelerating 3GPP channel model on GPU using NVIDIA CUDA tools. It provides a brief analysis of the achieved performance for GPU compared to that on the FPGA platforms.

Chapter 7: Concludes the thesis and suggests potential future directions

### Chapter 2

## Fifth-generation Mobile Network and Channel Modeling

The 5G mobile communication network also known as 5G-NR offers significant features, including but not limited to low latency, high data rates, and the ability to accommodate a high density of devices and base stations. The anticipated impact of this new cellular network technology is significant and poised to benefit various sectors, such as corporate networks, public networks, and infrastructure. Despite the challenging economic conditions and geopolitical instabilities, service providers are persistently implementing 5G technology. Ericsson's mobility report [11] projects that there will be a total of 5 billion 5G subscriptions worldwide, representing 54 % of all mobile subscriptions, by the end of 2028.

The adoption rate of 5G subscriptions has surpassed that of 4G, which was launched in 2009. It is anticipated that the new mobile communication technology will attain 1 billion subscriptions earlier than 4G by two years, owing to the timely availability of devices from multiple vendors, and a more rapid decline in prices compared to previous generations of the technologies. Figure 2.1 presents a quantitative analysis of the adoption rates of 5G and 4G subscriptions during the initial years of their respective deployments. Some of the key benefits associated with the new cellular technology are listed as follows.

• The implementation of 5G mobile communication technology is expected to serve as a crucial factor in facilitating the efforts of government entities and policymakers to convert their urban areas into smart cities. This will enable res-

Fig. 2.1 5G and 4G subscription uptake in the first years of deployment [11]

idents and communities to effectively leverage the socioeconomic advantages that are associated with a sophisticated, data-driven digital economy.

- The advent of 5G presents a promising prospect for wireless service providers to expand their offerings beyond mere connectivity services and, instead, create comprehensive solutions and services that cater to the needs of both consumers and various industries across diverse sectors.

- The new wireless communication technology is anticipated to significantly enhance data rates and decrease latency to less than 1 ms, rendering it appropriate for time-sensitive mission-critical services [12]. The high bandwidth available on 5G networks enables the provision of a variety of high-speed broadband services, thereby presenting a viable alternative to last-mile access technologies such as Fiber to the Home (FTTH) or copper connections.

- The new cellular network technology is expected to enhance the overall user experience by providing novel applications and services through faster data transfer rates, as well as substantially improved performance and dependability.

- It adds support for the implementation of virtual networks, also known as network slicing, which is made possible by the 5G technology. This feature enables the creation of subnets that offer connectivity tailored to meet specific requirements. The subnetworks can assign specific characteristics to a segment

of the network, rendering it programmable and enabling the prioritization of connections. This prioritization may involve a higher priority of emergency services over other users, through the application of varying latencies or the elevation of their connection status, thereby safeguarding them from potential disruptions caused by mobile network overloads.

The ITU roadmap for 5G communications systems groups the use case scenarios into three major categories [13];

**Enhanced Mobile Broadband (eMBB)** The primary application of 5G is considered to be the advancement of long-term evolution (LTE) mobile broadband services, with the aim of delivering improved connectivity, increased throughput, and greater capacity [14]. This particular use case is closely associated with the steady rise in mobile data traffic, which is primarily driven by the growing number of data-intensive devices and multimedia applications. Therefore, eMBB encompasses various applications aimed at enhancing the quality of communication from a human perspective, such as optimizing hotspots to accommodate a larger number of users and expanding coverage for scenarios involving greater mobility.

**Ultra-reliable low latency communications (URLLCs)** is a communication service designed to effectively transmit packets with strict demands, particularly with regard to availability, latency, and reliability [15]. It promises to facilitate the provision of nascent applications and services. Exemplary services comprise wireless control and automation within industrial factory settings, inter-vehicular communications to enhance safety and efficacy, and the tactile internet. The effective support of verticals is crucial for the success of 5G, as it has the potential to introduce new business opportunities to the telecommunications industry as a whole.

**Massive Machine–Type Communications (mMTCs)** The purpose of this usage scenario is to facilitate the collection of an enormous number of small data packets from numerous devices in a concurrent manner [16]. The mMTC technology facilitates the deployment of applications that rely on IOT sensors. This enables the utilization of data to optimize energy consumption, enhance work productivity, and enhance the quality of life. This particular use case involves a range of applications including but not limited to IoT, asset tracking, energy monitoring, smart agriculture, smart cities, smart home, and remote monitoring.

Some of the key features promised by the new cellular communication technology are peak data rate, low latency, greater network energy efficiency, improved spectrum efficiency, increased area traffic capacity, support for higher mobility, higher connection density, improved reliability, and more security and privacy.

### 2.1 Key Enabling Technologies for 5G

Future 5G networks will need revolutionary breakthrough technology to suit this wide variety of needs. As an added bonus, 5G technology is anticipated to be more welcoming to older technologies than its predecessors, with Wi-Fi, UMTS, and LTE all likely to play significant roles in the 5G ecosystem. A major paradigm shift in the planning of wireless communication systems is needed for this to happen.

### 2.1.1 Massive-MIMO systems

Massive-multiple-input and multiple-output (MIMO) also known as large-scale antenna systems is a wireless communication technique that employs many transmit and receive antennas to multiplex messages for various devices. The objective is to direct the emitted energy in the desired directions while reducing both inter and intracellular interference [17]. In contrast to traditional MIMO systems, massive-MIMO systems typically feature a large number of transmitting and receiving antennas, such as 32 or 64. The utilization of large antenna arrays provides a substantial degree of freedom and versatility in antenna usage, including multi-user beamforming and interference [18].

In the beginning, MIMO technology was conceptualized in two modes, namely single-user MIMO (SU-MIMO) and multi-user MIMO (MU-MIMO). In a given time slot, a conventional SU-MIMO base station (BS) transmits data to a single user-terminal using multiple antennas on both ends. However, BS can transmit data to multiple users simultaneously and the user-terminal is not necessarily required to be equipped with multiple antennas. This allows for better efficiency of the network and reduced equipment cost for user terminals. However, the scalability of MU-MIMO is limited in its initial design, which aimed to target nearly equal numbers of base station antennas and user mobile stations. This is due to the necessity of CSI being available at both ends. Massive MIMO employs channel information that is obtained through direct measurement, as opposed to being assumed. This allows the network

Fig. 2.2 Comparison of legacy antenna and massive-MIMO coverage[19]

to be scalable, as it can effectively utilize any number of BS antennas without any increase in array tolerances. The concept of massive-MIMO is depicted in fig. 2.2.

The idea behind massive-MIMO is to provide the BS with a very high number of antennas so that it may simultaneously serve a relatively smaller number of user terminals. This is accomplished through time division duplexing and calculating only the up-link CSI which is achieved through spatial multiplexing. Massive-MIMO technology supports beamforming, which refers to the capability of directing radio signals in specific directions. It is recommended that massive MIMO systems be constructed using low-power components, typically in the milliwatt range, and at a low cost. This is due to the fact that the necessary transmit power per antenna diminishes as the number of antennas increases. The implementation of beamforming techniques can effectively mitigate the negative impact of fading phenomena, leading to a reduction in latency [20].

Massive-MIMO technology has the potential to significantly enhance capacity by a factor of 10 or more, while concurrently improving radiated energy efficiency by approximately 100 times. The augmentation in capacity is attributed to the implementation of intensive spatial multiplexing techniques in the massive MIMO system. The underlying principle that enables a significant enhancement in energy efficiency is the ability to concentrate energy into highly localized regions in space through the utilization of a multitude of antennas [21].

#### 2.1.2 Network slicing

The implementation of network slicing is considered a highly innovative aspect of the 5G-NR cellular network. The notion of network slicing involves partitioning the network into distinct logical networks that are isolated from one another, which is a crucial aspect of the implementation of the 5G communication technology. The implementation of network slicing enables network providers to establish a tailored virtual network that caters to specific use cases [22]. The customization of each slice to suit specific use cases is facilitated by the virtualized nature of the network, which is less reliant on hardware than previous iterations of cellular technology.

The 3GPP has established a standardized network element, referred to as Dedicated Core (DECOR), which involves the Core Network (CN). The deployment of multiple CNs over a single physical network infrastructure enables mobile network carriers (MNCs) to provide varying levels of flexibility and resource sharing to diverse service consumers. The concept of network slicing surpasses the capabilities of DECOR by granting the MNC complete autonomy in regulating various communication services, each of which has distinct performance prerequisites. Figure 2.3 depicts the concepts of network slicing for various use cases in 5G-NR.

Fig. 2.3 Network slicing in 5G-NR

The feasibility of this objective can be achieved by tools such as network functions virtualization (NFV) and software defined network (SDN). Through the virtualization of network functions, the former enables the MNCs to offer a modular logical architecture and a flexible placement of network functions within its infrastructure. The utilization of the latter enables the MNCs to streamline the forwarding functions and implement a more sophisticated segregation of control and user plane functionalities.

### 2.1.3 Network functions virtualization

Deploying a new network service to large operator networks sometimes involves deploying more hardware. Special-purpose equipment is costly, space-consuming, and energy-intensive. Managing, upgrading, and deploying a big network using hardware-based network devices from numerous suppliers is difficult. Thus, adding hardware considerably raises network capital and operational costs [23]. Network operators want to offer new services to increase revenue, yet hardware-based network infrastructures are too expensive and complicated. Software on general-purpose computers can replace special-purpose hardware. The software provides advantages over dedicated hardware. It's flexible and affordable.

To address cost and complexity, the software might integrate network functionalities. The virtualized network function framework (VNF) supports software-based network functions on cheap commodity servers, such as virtual network functions [24]. The concept of "virtualization" has been employed across multiple fields of computer science for many years now. These include the virtualization of servers, disks, and applications. In essence, virtualization serves to create a level of abstraction between a user and a computing resource, thereby concealing the underlying physical attributes of said resource. Virtualization is commonly employed to attain goals such as streamlined resource utilization and simplified management.

The objective of NFV is to revolutionize the network architecture of network operators by means of conventional IT virtualization technology to merge various network equipment categories onto high-volume servers, switches, and storage that comply with industry standards. The vast majority of telecommunication operators are interested in the segregation of network functions from specialized devices and their conversion into software that can be installed on readily available, standard hardware. These components can be placed in data centers, network nodes, and end-user terminals. The process includes the deployment of software-based network functions that are compatible with a variety of server hardware commonly used in the industry. These functions can be relocated or established at different network locations as needed, without requiring the installation of additional equipment. Some key benefits associated with NFV are;

- The implementation of NFV can lead to a reduction in costs, a decrease in the time required for product updates or releases, and an enhancement in the scalability and resource allocation for applications and services.

- Organizations have the flexibility to avoid being constrained by proprietary, inflexible devices that require on-site visits and substantial resources to implement and customize.

- Virtualization with data center infrastructure allows more to be done with less, making it more efficient. With an improved data center footprint, electricity, and cooling power consumption can be reduced. This is possible because a single server is able to run many virtual network functions, and fewer servers are needed to complete the same task. Software updates can replace truck rolls when network demand changes. Physical network and data center updates are infrequent [25].

- A network that has undergone NFV possesses the capability to promptly and effortlessly adapt to variations in resource requisites in response to fluctuations in incoming traffic to the data center.

### 2.1.4 Vehicle-to-everything communication

The adoption of advanced traffic information systems, autonomous vehicles, and dependable safety services has facilitated the progress of technology in the domain of vehicles with enhanced features such as low latency, high data rate, and reliability. This technology offers an extensive transmission range and minimal end-to-end latency, making it ideal for cellular networks and includes various vehicular communication scenarios such as vehicle-to-infrastructure, vehicle-to-vehicle, and vehicle-to-pedestrian communication [26].

Fig. 2.4 Vehicle-to-everything communication [27]

### 2.1.5 Device-to-Device communications

Device-to-device communication (D2D) is a pioneering technology in the 5G cellular network that facilitates the establishment of a direct link between devices. D2D communication refers to the transmission of data between two devices in a point-to-point radio technology, without the involvement of a base station. This type of communication is commonly observed in cellular networks that operate on either the in-band or out-band spectrum. This technology is particularly useful during periods of network congestion or at cell boundaries, as it creates an ad hoc mesh network where intermediate devices can serve as relays for other devices. It provides a diverse range of services, that includes safety, traffic offloading, expansion of cellular coverage, reduced battery consumption, dependable communication, and proximity services based on location [28]. Additional advantages of D2D data transmission include its ability to effectively alleviate network congestion and enhance frequency

and space utilization, thereby enabling direct communication between nearby devices without necessitating the use of network infrastructure.

Fig. 2.5 D2D communication [29]

### 2.2 Wireless Channel Modeling Methodologies

In recent years, several MIMO channel models have been documented, with many of them being derived from empirical measurements. One possible approach to distinguish between the various models is by examining the specific type of channel under consideration, such as narrowband (characterized by flat fading) versus wideband (frequency selectivity) models, as well as time-varying versus time-invariant models, among others [30]. The spatial structure of flat fading MIMO channels provides a complete characterization. Channels with frequency-selectivity involve further modeling of the characteristics of the multipath channel. In the case of time-varying channels, it is necessary to incorporate a model that accounts for the evolution of the channel over time based on specific Doppler characteristics. In addition, it is imperative that the models are straightforward to facilitate their implementation and ensure efficient computational performance [31]. Balancing simplicity and accuracy in wireless channel modeling can be a challenging task.

Channel models reported in the literature can broadly be grouped into the following categories [30];

- 1. Analytical models

- (a) Propagation models

- (b) Correlation-based models

- 2. Physical models

- (a) Deterministic channel models

- (b) Stochastic channel models

- (c) Geometry-based stochastic models

Fig. 2.6 MIMO channel modelling methodologies [32]

### 2.2.1 Analytical channel models

Analytical models typically represent the impulse response of the radio channel between transmitters and receivers on an individual level but do not offer sufficient insight into wave propagation. Analytical modeling focus on spatial channel coefficient correlation rather than the physical features of the scatterers in the environment [33]. *Propagation-based* and *correlation-based* models are the two sub-categories of analytical models. Maximum entropy model [34] and finite scatterer model [35] are examples of propagation-based models. Kronecker model [36–38] and Weichselberger channel model [39] are examples of correlation-based channel models that

characterize the channel statistically from the correlation between MIMO matrix elements.

### 2.2.2 Physical channel models

In wireless communication channels, a signal propagates from the transmitter to the receiver along specific geometric pathways and is susceptible to a range of physical phenomena, such as reflection, and scattering [40]. Scattering refers to the phenomenon in which a radio frequency (RF) wave interacts with an object and subsequently disperses into a number of waves. The electromagnetic properties of the environment are employed in wave propagation-based physical models to characterize the channel between the transmitter and receiver. These models consider the radio-wave parameters such as the direction of arrival and departure and delay of MPCs to compute the impulse response of the channel.

#### **Deterministic channel models**

These models replicate the channel's transfer characteristics and radio coverage for a specific environment using a well-defined system setup. Deterministic models are valuable tools for channel modeling, as they enable visualization of the propagation mechanism [41]. Nevertheless, they exclusively provide a representation of the specific environment under consideration, and it is often necessary to conduct multiple iterations utilizing various environments [42]. Ray-tracing [43] and stored measurement-data-based models [44] are some examples of deterministic models.

#### Geometry-based stochastic channel model

In this type of model, scatterers are observed to be stochastically distributed at both ends of the link [45]. GSCMs are constructed by randomly deploying (diffuse or discrete) scatterers while assigning them (scattering) attributes according to specific statistical distributions [46]. The scatterers' signal contributions are determined through simplified ray tracing and then summed at the receiver. The approach not only provides delay and Doppler spectra, but also enables modeling MIMO properties of the channel. GSCM models are flexible in changing antenna influence and environment and are faster when simulating single or double scattering compared to deterministic ray tracing [47]. The structure of the scattering region provides insights into the tested scenario. For an accurate simulation of the given propagation scenario, it is essential to account for the total number of scatterers in the scattering region and to organize them into clusters. One-ring model [48] and elliptical-ring model [49] are examples of GSCM.

#### Non-geometrical stochastic model

This category of models solely relies on statistical methods to establish communication paths between the transmitter and receiver, without taking into account the physical geometry of the surrounding environment. Zwick model [50] and Saleh-Valenzuela model [51] are examples of non-geometrical stochastic models. In Zwick model, each MPC is treated individually, while the Saleh-Valenzuela model uses clusters of MPCs.

| Parameter        | Physical Model                                      | Analytical Model                                      |

|------------------|-----------------------------------------------------|-------------------------------------------------------|

| Approach         | Emulates wave propaga-                              | Mathematical simplification                           |

|                  | tion and electromagnetic effects                    | using statistics                                      |

| Accuracy         | Very high, closely matches real-world channel       | Approximate, depends on for-<br>mulation accuracy     |

| Complexity       | Extremely high, computes detailed physics           | Lower complexity, abstrac-<br>tions used              |

| Flexibility      | Scenario specific parame-<br>ters                   | Can adapt model formulation for scenarios             |

| Simulation speed | Very slow due to intensive computations             | Much faster due to simplified model                   |

| Calibration      | Requires extensive mea-<br>surements for validation | Validate by fitting model statistics to real-world    |

| Bandwidth        | Wideband, captures fre-<br>quency selective fading  | Can be wideband or narrow-<br>band                    |

| Time-variation   | Can model dynamic chan-<br>nels and mobility        | Typically static but some sup-<br>port time-variation |

| Antennas         | Accurate modeling of an-<br>tenna patterns          | Abstracted using antenna cor-<br>relations            |

| Implementation   | Require HPC systems,<br>GPU clusters                | Can be implemented on stan-<br>dard computers         |

| Use Cases        | Final validation, field trials                      | System-level simulation, para-<br>metric analysis     |

Table 2.1 Physical vs. Analytical channel models

The deterministic models rely on a digital map and leverage electromagnetic wave propagation theory to predict various channel parameters. Nevertheless, the precision of digital maps significantly impacts the effectiveness of such models, although the application of electromagnetic wave propagation theory requires significant processing resources. Parametric channel models for NGSM are obtained by the application of statistical information processing techniques. Despite the fact that the generated models include simplistic structures, they are unable to adequately capture the fundamental characteristics of true propagation environments. In conclusion, the imitation of stochastically distributed scatterers for multipath fading in GSCM is achieved by utilizing available geometry information. In recent decades, GSCM have gained significant popularity as a modeling approach due to their ability to balance computational complexity with model correctness. Consequently, they have been extensively utilized in the development of 3GPP channel models.

## 2.2.3 Standard channel models

While developing new radio-communication systems, standardized channel models play a very crucial role in assessing key performance parameters such as bit rate, multiple-access, and signal processing. The establishment of standardized channel models helps a more easy understanding of natural laws and can be helpful in unifying the results of extensive field measurements from scientific research, academia, and industry [52]. Several channel models have been developed by different standardization bodies groups, such as 3GPP [2], WINNER II[53], COST 2100 [54], METIS [55], ITU-R [56], MiWEBA [57] and NYUSIM [58]. These channel models share many similarities and can be grouped into two main categories:

- 3GPP/ITU-based channel models for frequencies below 6 GHz, with modifications to accommodate up to 100 GHz

- NYUSIM [59] based channel models for frequencies ranging from 0.5 GHz to 100 GHz that provide new features and enhancements, such as spatial consistency, mobility, and spherical wave propagation.

### COST

The European Cooperation in Science and Technology (COST) has formulated various models, encompassing the directional characteristics of wireless channels, that apply to simulations of MIMO and smart antennas [60]. COST 2100 [54] is a GSCM for frequency bands below 6 GHz was based on the pre-existing COST 259 [61] and COST 273 channel models [62]. Cluster power, delays, and angles in the COST 2100 model are drawn from fixed geometry locations. This model suffers from a limited frequency range and lack of support for scenarios requiring dual mobility, such as device-to-device and vehicular-to-vehicular communication.

### METIS

These channel models employ a hybrid approach, combining a map-based model and a stochastic model, to achieve adaptable and scalable channel modeling for mobile and wireless communications [55]. The map-based model was developed through the use of a ray tracing methodology, a simplified 3D geometric representation of a propagation environment, and the addition of random shadowing objects. These models support various propagation scenarios such as diffused scattering, blocking, specular reflection, and diffraction.

### **IEEE 802.11ay**

IEEE 802.11ay is an improved standard for wireless networks that achieves high throughput and power efficiency, building upon the IEEE 802.11ad standard [63]. The wireless transceiver in this design utilizes directional antenna beams to function in the 60 GHz mmWave band [64].

| Model         | Scope                                                     | <b>Frequency</b><br>bands | Scenario Focus                  | Applicability                                                                 |

|---------------|-----------------------------------------------------------|---------------------------|---------------------------------|-------------------------------------------------------------------------------|

| 3GPP [2]      | Cellular networks, stan-                                  | Sub-6 GHz and             | Urban, suburban,                | Cellular system design and standard-                                          |

| COST2100 [54] | Urban and indoor wire-<br>less environments mod-<br>eling | Sub-6 GHz                 | utuat<br>Urban, indoor          | Modeling urban and indoor wireless<br>environments, performance analysis      |

| MIWEBA [57]   | Millimeter-wave mobile<br>broadband access                | Millimeter-wave           | Millimeter-wave<br>(mmWave)     | Enhancing mobile broadband access<br>with mmWave, 5G and beyond re-<br>search |

| QuaDRiGa [65] | Various wireless com-<br>munication scenarios             | Various frequency         | Various (outdoor, indoor,       | Simulating channel conditions in diverse wireless scenarios, research         |

| METIS [55]    | Research and develop-<br>ment for 5G and beyond           | Various frequency         | Diverse (urban,<br>rural, etc.) | Shaping the 5G and beyond-5G com-<br>munication landscape, system de-<br>sign |

| IMT-2020 [56] | Millimeter-wave-based<br>mobile radio access              | Millimeter-wave           | Millimeter-wave<br>(mmWave)     | Research and development related<br>to mmWave communication, 5G and<br>beyond |

| NYUSIM [59]   | Highly configurable<br>channel simulator                  | Sub-6 GHz and mmWave      | Configurable for various        | Simulating channel conditions and system performance, research                |

Table 2.2 Comparison of 5G Channel Models

## 2.2.4 3GPP 3D channel model for 5G-NR

The 3GPP has developed a standardized map-based hybrid channel model that combines the ray-tracing method and GSCM. This model for 5G-NR[2] supports channel bandwidth up to 2 GHz and frequencies ranging from 0.5 GHz to 100 GHz. It provides accurate simulation at the cost of higher complexity than alternatives, and can also model additional components, such as oxygen absorption, blockage, large antenna arrays, and spatial consistency. The parameters of the channel are split into two distinct categories, namely deterministic parameters that are acquired through the ray-tracing method, and random parameters obtained through measurement data. This concept has the ability to achieve a balance between complexity and accuracy [66]. In the next chapter, we discuss in detail the 3GPP channel model based on release 15 of TR 38.901 [67].

The 3GPP 3D model combines the key desirable attributes of wideband, timevarying, spatial, and optimized for cellular systems, making it a robust choice for 5G-NR system simulation. Some key benefits of 3GPP channel model are;

**Standardization:** 3GPP is highly standardized and is the basis for many global 5G deployments. This makes it easier for vendors and operators to adopt it.

**Comprehensive Scenarios:** 3GPP covers a wide range of scenarios from urban to rural and indoor environments, making it versatile.

**Moderate Complexity:** While detailed enough to be accurate, 3GPP channel model for 5G is not as computationally intensive as some other models, making it more practical for real-world applications.

**Frequency Range:** It covers both sub-6 GHz and mmWave frequencies, making it adaptable to various types of 5G deployments.

**MIMO Support:** 3GPP fully MIMO technologies, which are crucial for 5G's high data rates.

**Industry Adoption:** Being one of the most widely adopted models, 3GPP has a large ecosystem, which makes it easier for operators to find compatible equipment and solutions.

n summary, the 3GPP 3D channel model is often considered superior due to its balance between complexity and practicality, its wide range of covered scenarios, and its high level of industry adoption and standardization.

# Chapter 3

# **3GPP Channel Model for 5G-NR**

A system-level simulation with many detailed scenarios, many configuration parameters, and sophisticated evaluation metrics requires both significant on-chip data storage and high computational power. Interference calculation becomes even more sophisticated with the inclusion of more complex scenarios. Thus, the requirements for system-level simulators must evolve in different directions, such as propagation channel modeling, interference modeling, and clustering. The propagation effect of a wireless channel can be modeled by combining a large-scale propagation model with a small-scale fading model of the channel. The former predicts the characteristics of the wireless channel model that change slowly, such as shadowing and path losses. The latter models the effect due to the Doppler shift or multipath effects on a wireless channel.

The 3GPP was established by the European Telecommunication Standards Institute (ETSI) and various standard development organizations worldwide with the aim of creating novel cellular network technology. The Technical Specification Group for Radio Access Network (TSG RAN) within the 3GPP has undertaken a study item entitled *Study on Channel Model for Frequency Spectrum Above* 6 GHz. This study item pertains to the modeling of channels for frequencies ranging up to 100 GHz. The model involves a range of scenarios, including Urban-Microcell (UMi) street canyon, Urban-Macrocell (UMa), Rural-Macrocell (RMa), and Indoor-Office (InH) environments. The model offers several notable features, including the ability to accommodate a substantial bandwidth of up to 10% of the center frequency, with a maximum limit of 2 GHz. Additionally, the model maintains spatial consistency, incorporates large antenna arrays, and accounts for blockage and oxygen attenuation phenomena. Furthermore, identical to the METIS approach, a hybrid model was suggested as a more accurate alternative. This model incorporates deterministic environmental factors into the stochastic model.

Analytical studies for 5G often integrate Rayleigh fading with simplified propagation loss models [68]. These models lack the ability to capture the spatial aspect of the channel and cannot be integrated with accurate beamforming models, despite being computationally efficient. The 3GPP channel model has the ability to model interactions with beamforming due to its stochastic properties.

## 3.1 3D Channel Modeling

Transmission techniques using multi-antenna configurations and MIMO channels are crucial for enhancing the reliability and spectral efficiency of a radio link. For assessing standardized technologies operating with a BS equipped with horizontally arranged antennas, 3GPP has used two-dimensional spatial channel model (2D-SCM) on the horizontal cross-section of wireless channels [69]. The models exhibit a poor representation of the characteristics of an actual channel due to their confinement to a two-dimensional plane. Additionally, the transmission methods for MIMO systems, such as spatial multiplexing, beamforming, and precoding, are restricted solely to the azimuth dimension. To assess communication techniques like vertical sectorization, it is necessary to employ a 3D channel model. A customized narrow elevation beam is designed for individual vertical sectors or specific user equipment (UE) elevations to effectively adjust both the transmission elevation and azimuth for the UE [69].

The model used in this thesis is a 3D channel model [53] and takes into account the elevation angles and the azimuth angle to model small-scale fading effects and correlation among the antenna elements. Figure 3.1a and fig. 3.1b show the different angles used in two-dimensional (2D) and 3D spatial channel model (SCM).

In 3GPP GSCM, a cluster refers to a group of Multipath components (MPCs) that arrive at the receiver within a close time interval and from similar directions. These clusters represent reflections, diffractions, and scatterings of the radio signal from large objects or structures in the environment, such as buildings, hills, or other significant obstacles. The concept of clusters is crucial in understanding and

Fig. 3.1 2D SCM to 3D.

modeling the behavior of radio signals in real-world environments. By grouping MPCs into clusters, the 3GPP 3D channel model can more accurately represent the complex interactions between radio waves and the environment, leading to more realistic simulations and better system designs.

Fig. 3.2 Cluster scattering in 3GPP channel model [59]

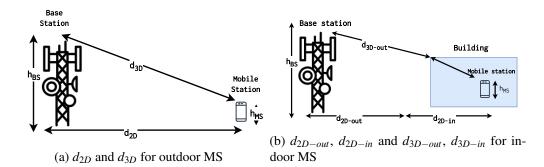

Figure 3.2 depicts a stochastic channel model based on geometry for a communication link pairing a transmitter and a receiver. The model incorporates scattering regions, also known as clusters, which are depicted as large circles consisting of multiple scattering objects. The total number of clusters and rays is subject to variation depending on different scenarios and propagation conditions. Several usage scenarios are defined in the 3GPP specification for elevation beamforming, the urban micro street canyon and open area, 3D urban macro (3D-UMa) with outdoor next generation NodeBs (gNBs), Backhaul, device-to-device (D2D), vehicle-to-vehicle (V2V), and outdoor to indoor (O2I) are examples of some common usage scenarios. For each of these propagation scenarios, different parameters are defined to calculate path losses and microscopic and macroscopic fading. Large-scale parameters (LSPs) are generated for each UE according to the propagation conditions at its location and geographical position. Delay spread, shadow fading,, azimuth angle of arrival (AOA), azimuth angle of departure (AOD), zenith angle of arrival (ZOA), and zenith angle of departure (ZOD) are considered as LSPs, while cluster powers, delays, ZOA, ZOD, and elevation direction are considered as small-scale parameters (SSPs), which change frequently.

# 3.2 Procedure for Channel Generation

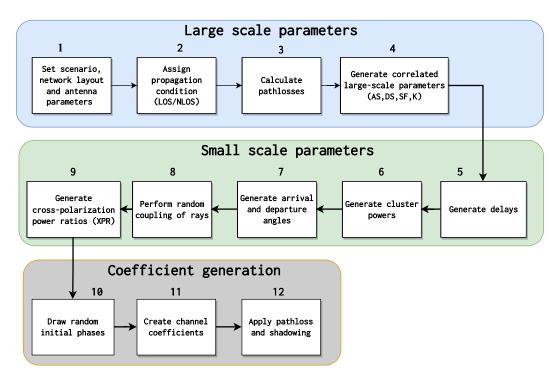

The 3GPP channel model is a hybrid model in which the deterministic part is represented by a path-loss model whereas the stochastic part is modeled by means of LSPs and SSPs. Figure 3.3 shows the steps required for channel generation.

- LSPs generation requires target scenarios selection such as RMa, UMa, UMi, and InH, as well as the network layout such as antenna configuration and velocity parameters. It defines the parameters that fluctuate less frequently over larger distances and mobility such as shadow fading (SF), Ricean K-factor, delay spread (DS), angular spread of arrival and departure in elevation and azimuth (AS), etc.

- SSPs are the parameter that fluctuates over smaller distances and requires remodeling more frequently. It characterizes the propagation of multipath components in terms of power, delay, and angles of arrival and departure in 3D space.

## 3.2.1 Large-scale fading

This model defines the large-scale link level parameters such as angular spread (AS), delay spread (DS), Ricean K-factor  $K_R$  (for line-of-sight (LOS)), shadow fading (SF)

Fig. 3.3 Channel coefficient generation in 3GPP 3D channel model

( $\sigma_{SF}$ ), and azimuth and zenith angular spread of arrival and departure (ASA, ZSA, ASD, ZSD) and corresponds to step 4 in 3GPP channel generation procedure fig. 3.3. LSPs in 3GPP specifications are considered as log-normal random variables and provides the mean and variances in [2, Table 7.5-6].