Doctoral Dissertation Doctoral Program in Electrical Engineering (35<sup>th</sup>cycle)

# Improving Quality of Results (QoR) for High-Level Synthesis (HLS) based FPGA designs

By

### M. Usman Jamal

\*\*\*\*\*

#### Supervisor(s):

Prof. Luciano Lavagno, Supervisor

#### **Doctoral Examination Committee:**

Prof. Roberto Passerone, Referee, Universita degli Studi di Trento

Prof. Mohammad Mozumdar, Referee, California State University at Long Beach

Prof. Mario R. Casu, Politecnico di Torino

Prof. Mihai T. Lazarescu, Politecnico di Torino

Dr. Osama B. Tariq, Newcastle University

Politecnico di Torino 2023

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

M. Usman Jamal 2023

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my loving parents

### Acknowledgements

I extend my heartfelt and sincere, gratitude and appreciation to my advisor, Prof. Luciano Lavagno, for his exceptional guidance, unwavering support, and significant contributions throughout the completion of this thesis. His mentor-ship and expertise have been instrumental in achieving this milestone. I consider myself fortunate to have had the privilege of working under his guidance.

I would specially like to thank, Giovanni Brignone, with whom I had the pleasure to work with. I would also like to express my gratitude to my friends, Weixi, Filippo, Teodoro, and other colleagues for their support and camaraderie.

Lastly, I sincerely acknowledge the love and encouragement of my family during this challenging process.

#### Abstract

High-level synthesis (HLS) is an Electronic design automation (EDA methodology that work towards designing complex digital systems using high level programming languages like C, C++ or SystemC and automatically transforms them into a hardware description language (HDL) in a relatively short time. This not only increases designer productivity but also helps in exploring different designs faster and trade offs between cost and performance. One of the open issues of HLS is the memory bandwidth bottleneck which limits the performance which is extremely important for the memory bound algorithms. Thus, designs implemented on Field-programmable gate array (FPGA) via HLS suffer from this bandwidth bottleneck and off chip memory latency. Current HLS tools are incapable of automatically exploiting the memory hierarchy on FPGAs and the only way to exploit the memory hierarchy is in a scratchpad fashion, but this requires considerable design effort and therefore, time-consuming. Secondly, the existing HLS tools currently exhibit a deficiency in providing dependable estimates of final Quality of results (QoR), thereby impeding designers ability to make well-informed decisions regarding the trade-offs between cost and performance.

This thesis explores and examines both these issues and addresses them by developing solutions in order to overcome aforesaid matters in question.

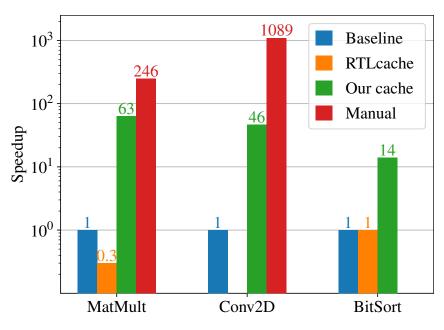

The first part of this thesis addresses the issue of off-chip memory latency and bandwidth bottlenecks in FPGA designs implemented via HLS. We propose an automated FPGA memory management approach using a fully-configurable source-level cache in Xilinx *Vitis HLS*. The primary objective of our cache implementation is to minimise the amount of design effort required while enabling the designer to focus on algorithmic optimizations, specifically for memory access patterns that are data-dependent or irregular in nature. Experimental results shows that our cache

implementation improve the performance of different benchmarks by up to 60 times compared to the out-of-the-box HLS solution.

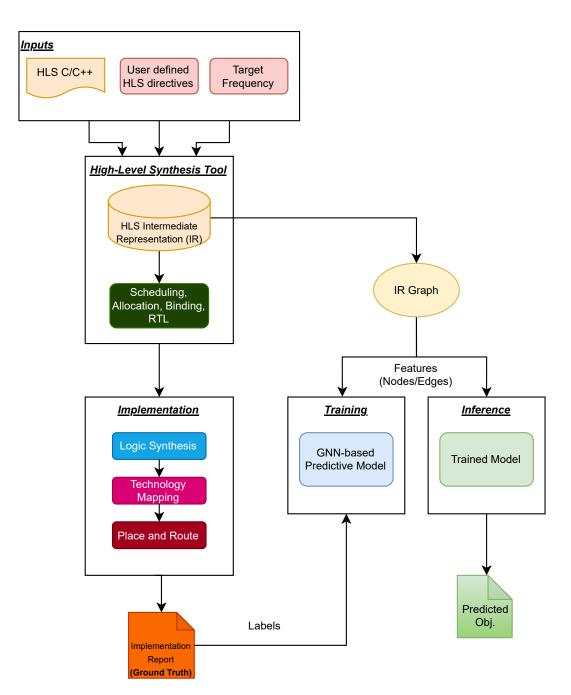

The second part pertains to the enhancement of QoR estimation in HLS. For this purpose, by taking advantage of the widespread use of Machine learning (ML), we propose Graph neural network (GNN)-based model that learn and predict post-implementation QoR using pre-schedule control data flow graphs (CDFGs) and HLS optimization directives. Experimental results show that our model can estimate the timing and resource usage of a previously unseen design (i.e, a completely new CDFG) within milliseconds with high accuracy, reducing prediction errors by up to 74 % compared to the estimate generated by the HLS tool.

## Contents

| Li                   | st of l | Figures xiii                                                                   | l |  |  |

|----------------------|---------|--------------------------------------------------------------------------------|---|--|--|

| List of Tables xviii |         |                                                                                |   |  |  |

| 1                    | Intr    | oduction 2                                                                     | , |  |  |

|                      | 1.1     | High-level synthesis                                                           |   |  |  |

|                      | 1.2     | Problem Statement                                                              |   |  |  |

|                      | 1.3     | Contribution                                                                   |   |  |  |

|                      | 1.4     | Thesis Structure    6                                                          |   |  |  |

| 2                    |         | ay-Specific Dataflow Caches for HLS of Memory-Intensive Algo-<br>ns on FPGAs 9 | ) |  |  |

|                      | 2.1     | Related Work                                                                   | ) |  |  |

|                      | 2.2     | Dataflow Cache                                                                 | , |  |  |

|                      |         | 2.2.1 Dataflow cache implementation                                            |   |  |  |

|                      | 2.3     | Multi-Level Cache                                                              |   |  |  |

|                      | 2.4     | Multi-Port Cache                                                               | ) |  |  |

|                      | 2.5     | Experiments                                                                    | , |  |  |

|                      |         | 2.5.1 Reference designs                                                        |   |  |  |

|                      |         | 2.5.2 Matrix Multiplication                                                    |   |  |  |

|                      |         | 2.5.3 2D Convolution                                                           | , |  |  |

|   |     | 2.5.4    | Bitonic Sorting                      | 42 |

|---|-----|----------|--------------------------------------|----|

| 3 | GNN | N-based  | Prediction Model for HLS QoR         | 48 |

|   | 3.1 | Backgi   | ound                                 | 50 |

|   |     | 3.1.1    | Low Level Virtual Machine            | 50 |

|   |     | 3.1.2    | Design as Graph                      | 51 |

|   |     | 3.1.3    | Embedding Layer                      | 52 |

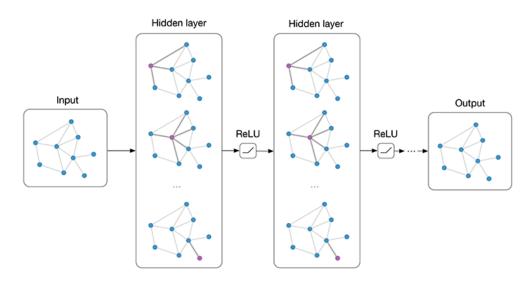

|   | 3.2 | Graph    | Neural Network                       | 52 |

|   |     | 3.2.1    | Graph Neural Network Models Variants | 54 |

|   |     | 3.2.2    | Graph Convolutional Network          | 54 |

|   |     | 3.2.3    | Dynamic Graph Attention Network      | 55 |

|   |     | 3.2.4    | Graph Isomorphism Network            | 55 |

|   |     | 3.2.5    | Deep Adaptive Graph Neural Network   | 56 |

|   | 3.3 | Transd   | uctive and Inductive Learning        | 56 |

|   | 3.4 | Related  | d work                               | 57 |

|   | 3.5 | DataSe   | t Generation                         | 59 |

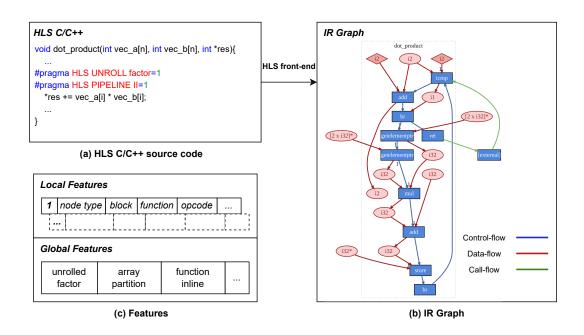

|   |     | 3.5.1    | Data Collection                      | 59 |

|   |     | 3.5.2    | Graph Generation                     | 62 |

|   | 3.6 | Feature  | es                                   | 64 |

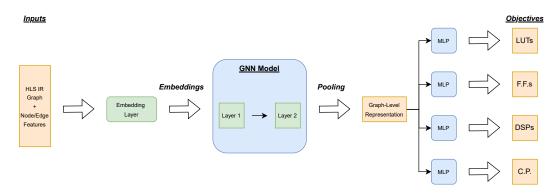

|   | 3.7 | Model    |                                      | 65 |

|   | 3.8 | Experi   | mental Results                       | 69 |

|   |     | 3.8.1    | Setup                                | 69 |

|   |     | 3.8.2    | Model Evaluation and Model Selection | 71 |

|   |     | 3.8.3    | Generalization and Comparison        | 75 |

| 4 | Con | clusions | and Future Work                      | 79 |

|   | 4.1 | Array-   | Specific Dataflow caches             | 79 |

| 4.2 GNN bas | sed QoR Prediction | <br>81 |

|-------------|--------------------|--------|

| References  |                    | 83     |

# **List of Figures**

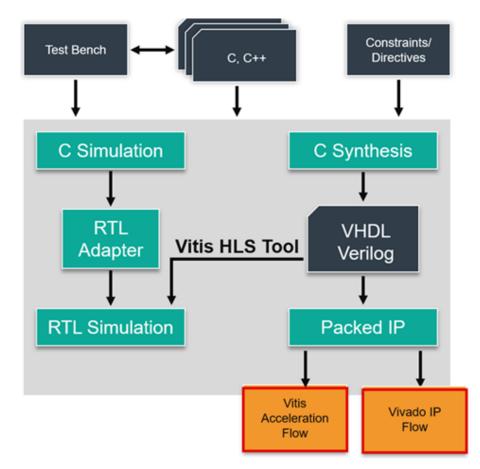

| 1.1 | Vitis HLS workflow [56]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

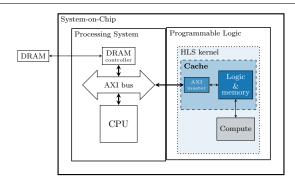

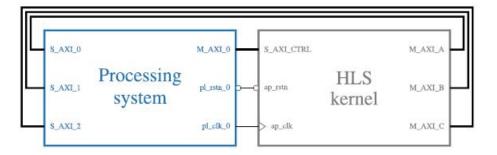

| 2.1 | Our cache embedded in a hardware (HW) setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 |

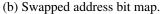

| 2.2 | Configurable address bit mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |

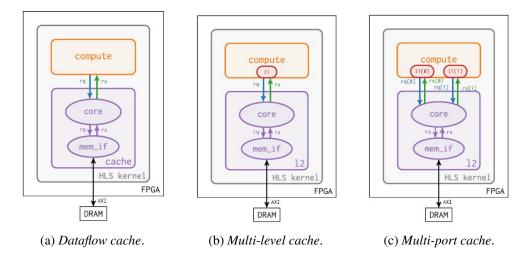

| 2.3 | Baseline <i>Dataflow cache</i> architecture, and its extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

| 2.4 | Multiple-reader dynamic RAM (DRAM)-mapped array, associated with our cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21 |

| 2.5 | Block design with three dynamic RAM (DRAM) arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23 |

| 2.6 | <i>MatMult</i> : sequence of addresses of <i>B</i> accessed during the first 8 iterations, where $B \in \mathbb{R}^{4 \times 8}$ has a 4-set direct-mapped cache                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |

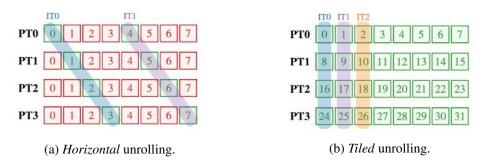

| 2.7 | <i>MatMult</i> : content of level 1 (L1) caches of <i>A</i> during the first iter-<br>ations, where $A \in \mathbb{R}^{4 \times 8}$ is associated with a four-port single-line<br>cache with eight words. <i>PTn</i> identifies the <i>n</i> -th port. The green<br>boxes represent elements that read during execution, red boxes are<br>elements loaded in cache but never accessed. The numbers inside the<br>boxes are the addresses of the elements of the <i>A</i> matrix. <i>ITi</i> highlight<br>the elements accessed in parallel at the <i>i</i> -th iteration. | 29 |

| •   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 2.8 | <i>MatMult</i> : tested dataflow architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31 |

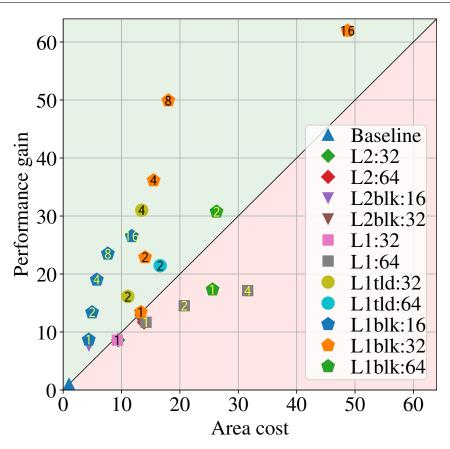

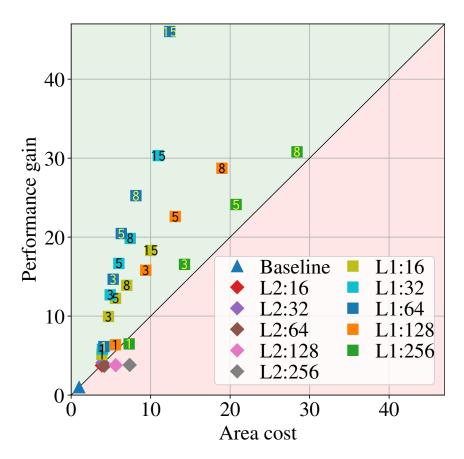

| 2.9  | <i>MatMult</i> : performance gain ( $t_{ex}$ relative to <i>Baseline</i> ) with respect to<br>area cost (average of lookup tables (LUTs), flip-flops (FFs), block<br>RAMs (BRAMs), and digital signal processing units (DSPs) usage<br>relative to <i>Baseline</i> ). <i>StdMatMult Single-level</i> is labelled <i>level 2</i><br>( <i>L2</i> ):WORDS, Horizontal is level 1 ( <i>L1</i> ):WORDS, and Tiled is level 1<br>( <i>L1</i> )tld:WORDS (WORDS are the number of words per line of B and<br>C caches). <i>BlkMatMult Single-level</i> is labelled <i>level 2</i> ( <i>L2</i> )blk:BLK,<br>and <i>Multi-level</i> is <i>level 1</i> ( <i>L1</i> )blk:BLK ( <i>BLK</i> are the block sizes).<br>The numbers over the markers are the unrolling factors | 32 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

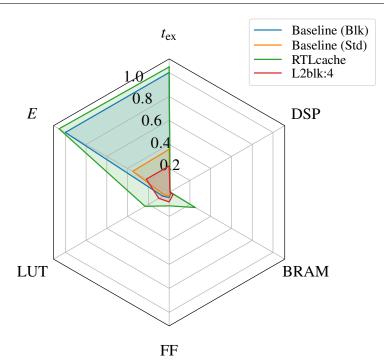

| 2.10 | <i>MatMult</i> : power, performance, and area (PPA) of some significant test cases. $t_{ex}$ and $E$ are relative to the <i>Baseline</i> . The resource usages are relative to the total resources provided by the target FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32 |

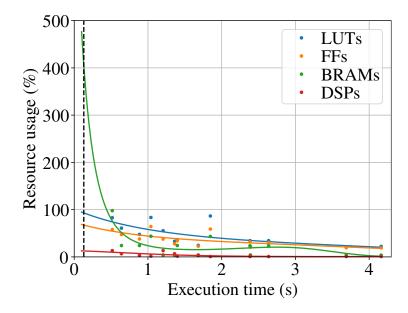

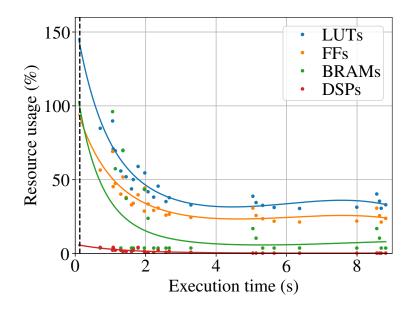

| 2.11 | <i>BlkMatMult</i> : regression estimating the resource usage with respect to the execution time of the test cases with our caches. The dashed vertical line highlights the execution time of the <i>Manual</i> test case. The dots are the real data, the lines are the regression predictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 |

| 2.12 | MatMult: power, performance, and area (PPA) of some test casesrelated to the $RTLcache$ case. $t_{ex}$ and $E$ are relative to the Baseline(Blk).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

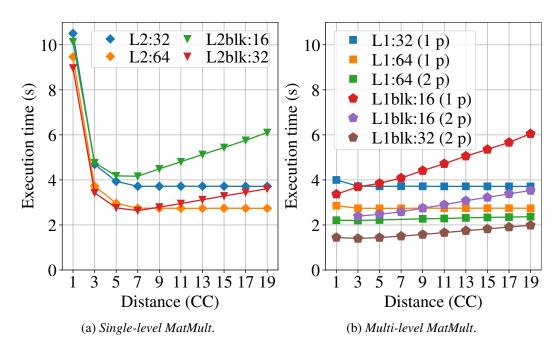

| 2.13 | <i>MatMult</i> : execution time with respect to level 2 (L2) cache request-response distance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37 |

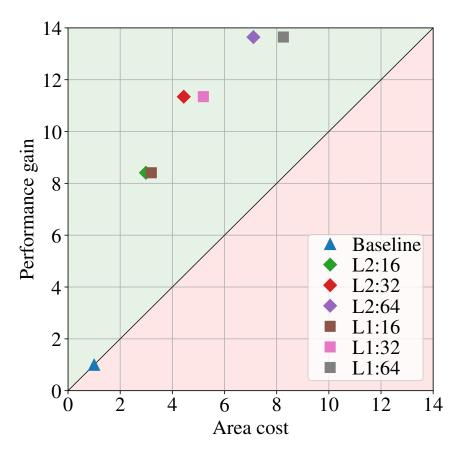

| 2.14 | <i>Conv2D</i> : performance gain with respect to area cost. <i>Single-level</i><br><i>Cache</i> is labelled as <i>level 2 (L2):WORDS</i> , and <i>Multi-level</i> as <i>level 1</i><br><i>(L1):WORDS</i> . The <i>WORDS</i> suffix stands for the number of words<br>per line of the <i>A</i> cache                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

| 2.15 | <i>Conv2D</i> : power, performance, and area (PPA) of some significant test cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |

| 2.16 | <i>Conv2D</i> : regression of resource usage with respect to the execution time of the test cases with our caches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41 |

| 2.17 | <i>BitSort</i> : performance gain with respect to area cost. <i>Single-level</i><br><i>Cache</i> is labelled as <i>level 2 (L2):WORDS</i> , and <i>Multi-level</i> as <i>level 1</i><br><i>(L1):WORDS</i> . The <i>WORDS</i> suffix stands for the number of words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | per line of the <i>a</i> cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

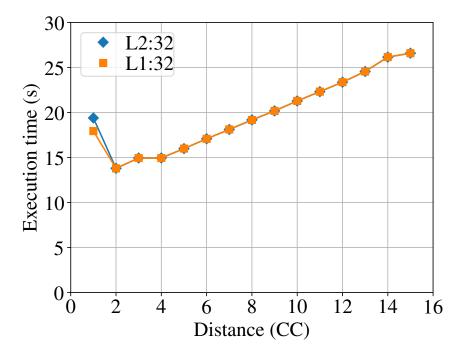

| <ul> <li>2.19 <i>BitSort</i>: execution time with respect to level 2 (L2) cache request-response distance</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

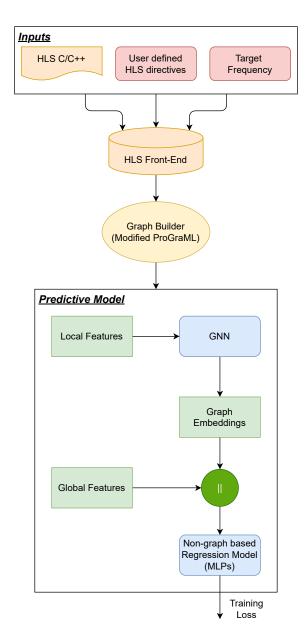

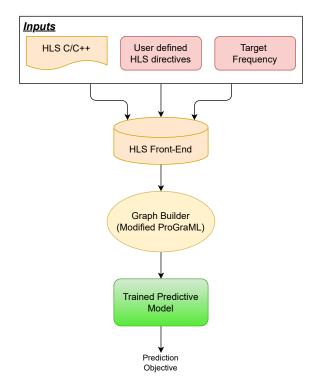

| <ul> <li>HLS-based hardware design work flow (left-hand side) and our proposed framework (right-hand side) for estimating quality of results (QoR) of an HLS-based design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>3.3 An High-level synthesis (HLS) design example with its graph representation (a) shows the HLS code for an implementation of dot product with two sample synthesis directives provided as an input to the HLS tool (b) shows its graph representation based on an intermediate-representation (IR) which is extracted after the HLS front-end compilation (c) shows the local and global features used by the model. Local features are extracted directly from the intermediate-representation (IR) graph. Global features are user-defined synthesis directives</li></ul> |

| <ul> <li>resentation (a) shows the HLS code for an implementation of dot product with two sample synthesis directives provided as an input to the HLS tool (b) shows its graph representation based on an intermediate-representation (IR) which is extracted after the HLS front-end compilation (c) shows the local and global features used by the model. Local features are extracted directly from the intermediate-representation (IR) graph. Global features are user-defined synthesis directives</li></ul>                                                                    |

| network (GNN) models. Features are passed to the trainable em-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>vector representation with the corresponding HLS intermediate-representation (IR) based graph is fed as an input to GNN model.</li> <li>A pooling operation is applied across all the nodes to create a single graph-level feature vector which is fed to four separate multi-layer perceptrons (MLPs) for each prediction objective (lookup table (LUT), flip-flop (FF), digital signal processing unit (DSP) and critical path (C.P.)).</li> </ul>                                                                                                                          |

| 3.5 Training phase of the proposed framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.6 Inference phase of the proposed framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

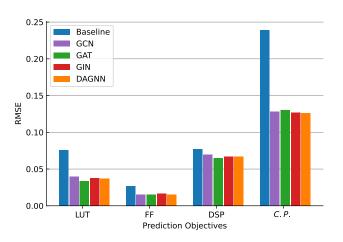

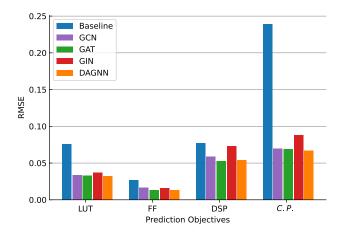

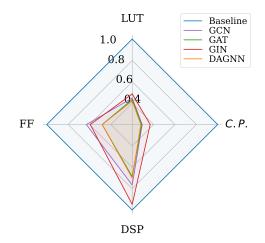

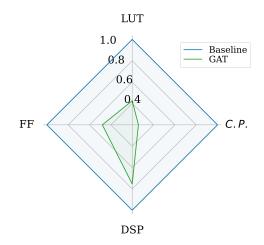

| 3.7  | Performance comparison of different GNN-based predictive models<br>for lookup table (LUT), flip-flop (FF), digital signal processing unit<br>(DSP) and critical path (C.P.) with HLS <i>Baseline</i> on the <i>test set</i> (the<br>lower the better). Only Local Features are considered                                                                                        | 71 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

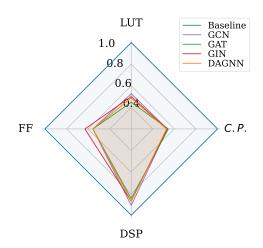

| 3.8  | Quality of results (QoR) prediction improvements of different GNN-<br>based predictive models for lookup table (LUT), flip-flop (FF), digi-<br>tal signal processing unit (DSP) and critical path (C.P.) with respect<br>to HLS <i>Baseline</i> on the <i>test set</i> . Only Local features are used                                                                            | 72 |

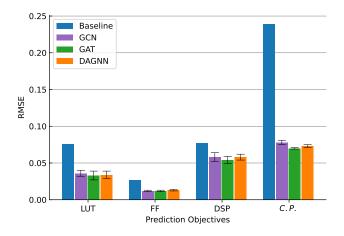

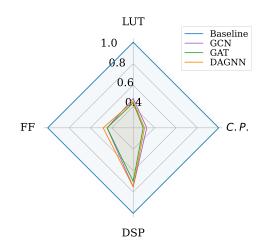

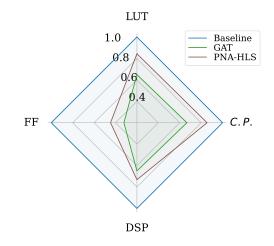

| 3.9  | Performance comparison of different GNN-based predictive models<br>for lookup table (LUT), flip-flop (FF), digital signal processing unit<br>(DSP) and critical path (C.P.) with HLS <i>Baseline</i> on the <i>test set</i> (the<br>lower the better). In addition to Local features, Global features are<br>also considered to evaluate their impact on performance             | 73 |

| 3.10 | Quality of results (QoR) prediction improvements of different GNN-<br>based predictive models for lookup table (LUT), flip-flop (FF), digi-<br>tal signal processing unit (DSP) and critical path (C.P.) with respect<br>to HLS <i>Baseline</i> on the <i>test set</i> . In addition to Local features, Global<br>features are also used to evaluate their impact on performance | 73 |

| 3.11 | Performance comparison of best performing GNN-based predictive models for lookup table (LUT), flip-flop (FF), digital signal processing unit (DSP) and critical path (C.P.) with HLS <i>Baseline</i> (the lower the better). A <i>5-fold cross-validation</i> with the <i>holdout set</i> is performed. Both Local and Global features are considered                            | 74 |

| 3.12 | Quality of results (QoR) prediction improvements of best performing GNN-based predictive models for lookup table (LUT), flip-flop (FF), digital signal processing unit (DSP) and critical path (C.P.) with respect to HLS <i>Baseline</i> . A <i>5-fold cross-validation</i> with the <i>holdout set</i> is performed. Both Local and Global features are used                   | 75 |

| 3.13 | Quality of results (QoR) prediction improvements of the selected GNN-based predictive model for lookup table (LUT), flip-flop (FF), digital signal processing unit (DSP) and critical path (C.P.) with respect to HLS <i>Baseline</i> . A <i>5-fold cross-validation</i> over the <i>whole</i>                                                                                   |    |

|      | dataset is performed.                                                                                                                                                                                                                                                                                                                                                            | 76 |

| 3.14 | Quality of results (QoR) prediction improvements of our best per-   |    |

|------|---------------------------------------------------------------------|----|

|      | forming GNN-based model for lookup table (LUT), flip-flop (FF),     |    |

|      | digital signal processing unit (DSP) and critical path (C.P.) with  |    |

|      | respect to HLS Baseline and the state-of-the-art on Unseen Kernels. | 77 |

|      |                                                                     |    |

| 4.1  | Speedup of the tested benchmarks                                    | 80 |

# **List of Tables**

| 2.1 | <i>StdMatMult</i> : tested cache configurations                                                                                                                                                                                      | 30 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | <i>BlkMatMult</i> : tested cache configurations                                                                                                                                                                                      | 30 |

| 2.3 | <i>MatMult</i> : maximum achievable clock frequency of some test cases.<br>The relative maximum clock frequency is normalized over the max-<br>imum clock frequency of the advanced extensible interface (AXI)<br>adapter (330 MHz). | 36 |

| 2.4 | MatMult: Performance achieved for some test cases                                                                                                                                                                                    | 36 |

| 2.5 | <i>Conv2D</i> : tested cache configurations                                                                                                                                                                                          | 39 |

| 2.6 | Conv2D: maximum achievable clock frequency of some test cases                                                                                                                                                                        | 41 |

| 2.7 | <i>BitSort</i> : tested cache configurations                                                                                                                                                                                         | 43 |

| 2.8 | <i>BitSort</i> : maximum achievable clock frequency of some test cases.<br>The relative maximum clock frequency is normalized over the max-<br>imum clock frequency of the advanced extensible interface (AXI)<br>adapter.           | 46 |

| 2.9 | <i>BitSort</i> : Performance achieved for some test cases                                                                                                                                                                            | 46 |

| 3.1 | Comparison of ML-based Approaches for high-level synthesis (HLS)<br>Prediction Tasks                                                                                                                                                 | 59 |

| 3.2 | HLS-based Designs used in DATASET                                                                                                                                                                                                    | 59 |

| 3.3 | Synthesis Pragma configurations                                                                                                                                                                                                      | 61 |

| 3.4 | Overall Summary of designs in our DATASET                                                                                                                                                                                            | 61 |

| 3.5 | Local Features: Nodes and Edges                                                                                                                                                                                                      | 65 |

## Acronyms

API application programming interface **AXI** advanced extensible interface **BRAM** block RAM C.P. critical path CC clock cycle CPU central processing unit DAGNN deep adaptive graph neural network **DDR4** double data rate 4 **DRAM** dynamic RAM **DSE** design space exploration **DSP** digital signal processing unit EDA electronic design automation FF flip-flop FIFO first-in first-out **FPGA** field-programmable gate array **GAT** dynamic graph attention network GCN graph convolutional network

- GIN graph isomorphism network

- GNN graph neural network

- HBM high-bandwidth memory

- HLS high-level synthesis

- HW hardware

- II initiation interval

- **IR** intermediate-representation

- ISA Instruction Set Architecture

- L1 level 1

- **L2** level 2

- LCS load, compute, store

- LLVM low level virtual machine

- LSU load-store unit

- LUT lookup table

- MAC multiply-acccumulate

- ML machine learning

- MLP multi-layer perceptron

- **OS** operating system

- PPA power, performance, and area

- QoR quality of results

- RAW read after write

- **RMSE** root mean square error

- RO read-only

RW read-write

SSA static single assignment

SW software

WO write-only

## Chapter 1

## Introduction

### **1.1 High-level synthesis**

With the rapid expansion of hardware development and the increase in design complexity, there is a growing need for more efficient and effective design techniques. Traditionally, hardware design has been an expensive and a time-consuming process requiring a high level of expertise and specialized knowledge. In recent years, HLS has emerged as an important method for hardware design, allowing high-level programming languages such as C/C++ to be automatically transformed into hardware designs [10]. The introduction of HLS has allowed designers to create hardware using high-level programming languages, allowing both faster design and faster simulation than register-transfer level (RTL). By using HLS, designers can benefit from the abstraction and modularity of high-level languages, enabling them to produce more sophisticated, powerful, and portable hardware designs in less time. In addition, designers can use HLS directives (also called pragmas) to optimize hardware implementations by tradeoffs between cost and performance. This flow allows designers to quickly and effectively experiment with different design configurations before working on the final implementation.

The primary purpose of HLS to streamline the hardware design process, enabling designers to allocate more attention to algorithmic-level design while abstracting the intricacies of low-level implementation. By raising the level of abstraction, HLS aims to enhance productivity, reduce design cycles, and enable efficient design exploration and optimization.

High-level synthesis tools utilise sophisticated algorithmic techniques to analyse and optimize high-level descriptions and help in mapping complex digital designs onto Field-programmable gate array (FPGA) or ASIC (Application-Specific Integrated Circuit) architectures in a relatively short time. These tools perform various optimizations, including scheduling, resource allocation, loop pipelining and loop unrolling etc, to generate efficient RTL designs.

Furthermore, HLS provide opportunities for hardware/software co-design. With HLS, designers can seamlessly integrate hardware accelerators or custom processing units with software components, enabling the design of heterogeneous systems that leverage the strengths of both hardware and software. This approach helps in attaining the goal of best design point while considering various limitations such as cost, performance, power-consumption and time-to-market [48].

Fig. 1.1 Vitis HLS workflow [56]

Fig. 1.1 shows the *Vitis HLS* development flow which has been used in this research work.

#### **1.2 Problem Statement**

HLS can greatly decrease the amount of design effort, allowing the use of convenience software (SW)-like tools and development processes but it still suffers from some issues.

An HLS open issue is the off-chip memory latency and bandwidth bottleneck, which limits performance and is especially critical for memory-bound algorithms. The FPGA memory system is composed of two main kinds of resources: fast small on-chip memories (registers and block RAMs (BRAMs)), and slow large off-chip memories (dynamic RAMs (DRAMs)) interfaced through double data rate 4 (DDR4) or high-bandwidth memory (HBM) protocols (the latter characterized by even larger latency [51]). Current HLS tools, in particular those from the leading producer Xilinx, allow the designer to exploit this memory hierarchy only manually, in a scratchpad-like way, which often requires significant design and verification effort. *This makes harder to achieve the deployment of accelerated applications using FPGAs for a large number of applications*. Our work aims directly at filling this gap, thus *making HLS design more software-like* for use cases in which the ultimate performance need not be achieved, but *design time and effort are paramount*.

Another issue is the prediction of post-implementation Quality of results. Current commercial HLS tools do not provide reliable estimates of the final QoR [9]. As a result, designers are unable to make cost/performance trade-offs and guarantee that the design will meet the requirements because the estimation results in terms of timing and resource usage often significantly differ from the actual QoR after implementation. Graphs are a widely used model in EDA tools [40]. In recent years, EDA tools have recently begun to use machine learning approaches, especially for analysis tasks [35]. Recent research has shown that *graph-based machine learning* techniques can be successfully applied to various phases of the EDA flow, including logic synthesis [20, 50], placement and routing [37, 38, 19, 31], power estimation [33], verification [62], and testing [41]. By using the Graph neural network, in this work, we aim to predict the post-implementation QoR of an HLS design, starting from both the user C/C++ code and the user-defined optimization directives.

### **1.3** Contribution

In this thesis, the focus of the research is to improve Quality of results (QoR) for High-level synthesis (HLS) based Field-programmable gate array (FPGA) designs by overcoming the issues discussed in Section 1.2. One part of the research deals with the automation of FPGA memory system while the other part proposes a graph neural network-based framework to predict the post-implementation quality of results for a given HLS-based design.

The first part (Chapter 2) of the thesis proposes array-specific dataflow caches to automate FPGA memory management to overcome the off-chip memory latency and memory-bandwidth bottleneck, thus allowing the designer to focus on algorithmic optimizations. For this, a cache module is developed which works as an interface with the off-chip memory (DRAM), accessible through an advanced extensible interface (AXI) bus and sores its data to on-chip blocks RAMs (BRAM) and registers. We first developed a single port cache module in the form of a C++ class which is configurable through templates in terms of number of sets, ways, words per line and replacement policy. During the second phase, the emphasis was put on performance optimization. For this purpose, a multi-level cache is proposed which increases the memory hierarchy of the cache by adding a level 1 (L1) on the top of dataflow cache (level 2 cache). This architecture helps in further reducing the memory access latency and provides a basis for building a cache architecture with multiple concurrent accesses. Dataflow and Multi level caches provide a maximum throughput of one access per iteration. This is not efficient for cases where the array is accessed multiple times in a single iteration. Therefore, a multi-port cache is developed that enables multiple concurrent read accesses to the same array. This is implemented as an extension of the multi-level cache. The number of ports can be configured through a template parameter. This also allows to overcome Vitis HLS limitation of a single reader per AXI interface. To adhere to the HLS highproductivity philosophy, we paid a special attention to the HLS user-friendliness in terms of (a) *configurability* (the cache characteristics can be set through parameters), (b) ease of use (the cache can be inserted into existing designs with just a few lines of boilerplate code), (c) observability (cache information critical for parameter tuning, e.g., hit ratio, can be profiled during SW simulation).

The second part (Chapter 3) proposes a graph neural network (GNN) based framework is developed to predict the post-implementation QoR from the preschedule control data flow graph (CDFG) representation of an HLS design targeting FPGA implementation, also considering the user HLS optimization directives. For this purpose, a dataset is built from a variety of designs covering a wide range of different applications from the well known HLS benchmark suites. To create multiple hardware implementations for each design, different HLS synthesis directive and various clock periods are used. Each design point is synthesized and implemented with Vitis HLS and Vivado respectively. A method is proposed that exploits a graph based representation of an HLS design that includes both program semantics and synthesis directive information but not scheduling and binding information. This graph is extracted from the low level virtual machine (LLVM) model generated by the open source front end of Vitis HLS. QoR prediction problem is formulated as a multi-objective regression task to estimate post-implementation resource usage and timing without invoking the back end of the HLS tool. A multi-objective GNN based learning model is trained to learn the underlying heuristics and optimizations techniques to predict the desired objectives, namely lookup table (LUT), flip-flop (FF), digital signal processing unit (DSP) and critical path timing (C.P.).

### **1.4 Thesis Structure**

The main objective of this research is to improve Quality of results (QoR) for Highlevel synthesis (HLS) based Field-programmable gate array (FPGA) designs by studying the two important problems in HLS which are related to memory bandwidth bottleneck and estimation of final QoR. In this regard, the thesis is divided into two major parts and structured in different chapters as follows:

- Chapter 1 presents a thesis statement and offers an overview of the underlying motivation that motivates the research.

- Chapter 2 proposes an automated FPGA memory management flow using a user-friendly cache in order to improve the performance of memory-bounded algorithms.

- Chapter 3 proposes a GNN-based predictive model to predict the post-implementation QoR.

• Chapter 4 summarizes the thesis work and offers insights into potential avenues for future research.

### Chapter 2

# Array-Specific Dataflow Caches for HLS of Memory-Intensive Algorithms on FPGAs

Part of the work described in this chapter has been previously published in [5].

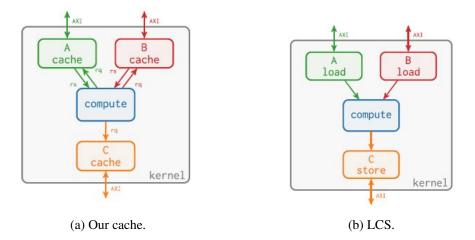

According to the best design practice from Xilinx [56], efficient HLS kernels should comply with the load, compute, store (LCS) paradigm to mitigate the off-chip memory bottleneck, i.e., access external DRAM only by load and store dataflow tasks, which are then responsible for buffering on the on-chip memory the data consumed and produced by the compute task(s). The main drawback of the LCS approach is the significant design effort needed for converting a generic algorithm into LCS form, which often requires full rewriting and redesigning of the source code.

A cache is in general helpful to implement well-performing designs in a short time. Moreover, techniques such as manual buffering or polyhedral transformations [11, 45] cannot be applied to programs with irregular or input-dependent memory access patterns, and are only partially implemented in commercial design tools such as *Vitis HLS*. Therefore, a cache could be the only solution for quickly optimizing the performance of such designs using commercial tool flows.

The aim of the work in this chapter is to automate efficient off-chip memory accesses through an easy to use and fully customizable cache system for HLS, which works as an interface with the off-chip DRAM, accessible through an AXI bus, and

Fig. 2.1 Our cache embedded in a hardware (HW) setup.

*stores its data to on-chip BRAMs and registers*. Figure 2.1 shows the resulting system when our cache is used to accelerate an HLS kernel. Our cache is placed within the HLS kernel. The computation logic of the kernel accesses the cache, rather than the AXI bus directly.

From a high-level point of view, the cache has the objective of isolating the off-chip memory accesses into a dataflow task, in accordance with the LCS pattern.

From a low-level point of view, the cache has the dual purpose of (a) reducing the number of DRAM accesses, i.e., the data stored in the cache is reused as long as it hits, and only the misses need to access the DRAM, and (b) optimizing DRAM accesses, i.e., the DRAM is accessed in lines (aligned groups of consecutive words), which allows taking advantage of AXI bursts and interface widening, even with hard to analyze or totally irregular access patterns.

### 2.1 Related Work

10

The need for automated memory management for FPGAs is attested by the multiple works on this topic.

Matthews et al. [44], Choi et al. [7] designed FPGA-based caches. These works differ from ours as they are aimed to accelerate specific soft-processors implementations instead of generic HLS designs.

Jo et al. [27] developed an OpenCL framework whose memory subsystem inserts direct-mapped, single-level, and single-port caches in between the kernel accessing the memory, and the external memory. They implemented at RTL both the kernels (which consist of a predefined set of intellectual property blocks) and the cache. Our work therefore differs both in terms of cache architecture complexity (our caches provide set associativity, two levels, and multiple ports), and in terms of technology (our cache is compatible with any HLS design).

Several works focused on optimizing the memory accesses through RTL cache modules inserted between the kernel accessing the off-chip memory and the off-chip memory interface. These modules can be either inserted manually or through a dedicated framework, such as the one proposed by Adler et al. [3] which virtualizes the FPGA memory hierarchy and includes some caching capabilities. Winterstein et al. [52] improved this framework specifically for HLS by allocating the unused BRAMs to maximize the cache sizes. However, an RTL cache module fails to provide significant speedup when coupled with an HLS kernel. For example, the *Vitis HLS* scheduler, unaware of the external cache module, inserts a minimum latency between a memory request operation and its corresponding response based on the architecture of the memory adapter, thus preventing the exploitation of the cache acceleration. Our cache is instead implemented at the source level, and it is specifically designed to avoid scheduling based on the worst case (cache miss). This allows the HLS tool to optimize the circuit accordingly.

We ran some experiments adding an RTL cache module (specifically the Xilinx System Cache [60]) to the interface of an HLS kernel. The results show that the RTL cache did not provide any advantage. It simply introduced an overhead, as discussed in Section 3.8.

Cong et al. [11], Pouchet et al. [45] designed a workflow for improving data locality of HLS programs through compiler-level loop transformations, taking advantage of the polyhedral representation. Moreover, they exploited this locality by automatically inserting on-chip buffers. These techniques are limited to programs with affine loop bounds and memory accesses, while a cache can be used with any program, including those with irregular or data-dependent memory accesses. A cache could benefit from their improved locality by achieving higher hit ratios with simpler cache configurations.

The Intel HLS [25] tool provides load-store units (LSUs) that can cache DRAM data in BRAM in case of read-only (RO) memories. Our experiments described in Section 3.8 suggest that the tool fails to determine the optimal cache configuration and the user has limited control to improve it.

Array-Specific Dataflow Caches for HLS of Memory-Intensive Algorithms on FPGAs

The work by Ma et al. [39] is closest to ours. They proposed an open-source array-specific HLS cache module as a set of C++ classes, compatible with Vivado *HLS 2016.2.* Different from our work, the cache logic is inlined in the application. While this helps keeping the hit latency low in simple cases, it violates the LCS pattern. Moreover, their architecture increases the pipelining complexity. To mitigate this problem, they mapped the whole cache data to registers. However, in the experiments discussed in Section 3.8, we verified that the pipelines embedding their cache require higher initiation intervals (IIs), or are not pipelineable at all. Moreover, mapping all the data to registers limits strongly the cache size scalability due to HW resources constraints. Instead, our architecture completely hides the cache logic and the memory interface from the main computations performed by the kernel. This allows the HLS to synthesize pipelines with low II while mapping cache data to cheaper BRAMs. Finally, their cache automatically handles only one access port thus providing only one read or write per clock cycle (CC). The only way to perform multiple accesses per CC is to guarantee that other accesses, beyond the first one in a given CC, will always be hits, and make it explicit through the retrieve and modify functions. This is both difficult and error-prone to analyze manually in complex cases.

### 2.2 Dataflow Cache

12

The *Dataflow cache* architecture (Fig. 2.3a) is isolated into a dedicated dataflow process. An HLS kernel that is configured to use the cache for one of its top-level DRAM-mapped arrays is split into two dataflow tasks: (i) the compute task, which includes all the application logic except for the external memory interface, which is replaced with the simpler cache interface, and (ii) the cache task (or, in general, one cache task per array that uses the cache), which buffers data and interfaces with the external DRAM. Thus, the kernel automatically complies with the LCS architecture without any manual code change.

This architecture is characterized by information flow from the compute task to the cache (the address to be accessed and the data to be written), and from the cache to the compute task (the read data).

Algorithm 1 describes the *Dataflow cache* functionality. The cache task waits for a request and executes the standard cache operations: it checks if the request is a hit

#### Algorithm 1 Dataflow cache functionality.

**Require:** Compute needs to access an array associated with Cache at address addr in read mode (op = R) or write mode (op = W, data = element to be written).

Ensure: The operation requested by *Compute* is fulfilled by *Cache*.

#### procedure COMPUTE

Send op to Cache Send addr to Cache if op = W then Send data to Cache else Wait for Cache response Receive data from Cache end if end procedure procedure CACHE Wait for Compute request Receive op from Compute Receive addr from Compute if op = W then Receive data from Compute end if *line* :  $addr \in line$ if *line*  $\Rightarrow$  *MISS* then **if**  $line_{old} \Rightarrow DIRTY$  **then**  $DRAM(line_{old}) \leftarrow BRAM(line_{old})$ end if  $BRAM(line) \leftarrow DRAM(line)$ end if if op = W then  $BRAM(addr) \leftarrow data$ else  $data \leftarrow BRAM(addr)$ Send data to Compute end if end procedure

Array-Specific Dataflow Caches for HLS of Memory-Intensive Algorithms on FPGAs

TAGSETOFFMSBLSBMSB(a) Standard mapping.(b) Swapped mapping.

Fig. 2.2 Configurable address bit mapping.

LISTING 2.1 Source code modifications for accelerating the compute function with our cache.

```

+#include "cache.h"

+typedef cache<DATA_TYPE, RD_ENABLED, WR_ENABLED,

MAIN_SIZE, N_SETS, N_WAYS, N_WORDS_PER_LINE, LRU,

SWAP_TAG_SET, LATENCY> cache_type;

template <typename T>

void compute(T &a) {

for (auto i = 0; i < (N - 1); i++) \{

#pragma HLS pipeline

a[i] = a[i + 1];

}

}

extern "C" void top(DATA_TYPE *a) {

#pragma HLS interface m_axi port=a bundle=gmem0

+#pragma HLS dataflow

cache_type a_cache(a);

compute(a):

+

cache_wrapper(compute<cache_type>, a_cache);

}

```

14

or a miss, it updates the cache data structures (valid bits, dirty bits, tag bits, ...), and it performs the DRAM read or write operation. For reads, it also sends back the data. The compute task sends the read or write request to the cache. For reads, it waits for the response containing the read data.

The *Dataflow cache* uses the set associative mapping and the write-back consistency policy. It is configurable in terms of (a) word size, (b) number of words per line, sets, and ways, (c) replacement policy, least recently used or first-in first-out (FIFO), (d) address bit mapping, standard (Fig. 2.2a) or swapped (Fig. 2.2b, convenient in use cases like the one discussed in Section 2.5.2, i.e., a matrix accessed by columns). It can implement a fully associative policy if the number of sets is one, or a direct mapped policy if the number of ways is one.

Listing 2.1 highlights the modifications needed for accelerating the compute function with our cache. Users simply need to (1) set the cache parameters through the cache class template arguments, and (2) instantiate the cache and call the compute function through the cache\_wrapper function in a dataflow region.

Fig. 2.3 Baseline Dataflow cache architecture, and its extensions.

It is worth noting that the compute function is unchanged, since we overloaded the operator[], like Ma et al. [39], to allow using a cache object as if it were a traditional array.

In the presence of feedback between different tasks, the HLS-generated HW circuit would deadlock. Moreover, we have to carefully specify cycle by cycle the scheduling of the operations to avoid losing performance or causing unexpected deadlocks.

To avoid the deadlock, the *write request* and *read response* must be scheduled into separate pipeline stages by:

- 1. Explicitly declaring a dependency between *write request* and *read response* using the write\_dep and read\_dep FIFO access functions provided by *Vitis HLS* to define a partial ordering between accesses to different streams.

- 2. Setting the dependency distance to 1 CC by delaying it with the reg function, also provided by *Vitis HLS*.

While this solution guarantees the functionality of the generated HW, it fails to achieve high throughput. In fact, assuming that both the *Core* and the *Memory Interface* are pipelined with an II of 1 CC (i.e., the most performance-critical case) and the *Memory Interface* pipeline depth is D > 1, the HLS scheduler schedules the *read response* in the CC following the *write request* because it is unaware of

the latency between *write request* and *read response*. This reduces the overall performance.

However, if we set the dependency distance between *write request* and *read response* to D CCs, the scheduler inserts D - 1 pipeline stages between them. In each CC, the *Core* writes one request and receives one response. Our solution allows optimally exploiting the pipeline with an II of 1 CC, without incurring stalls.

# 2.2.1 Dataflow cache implementation

The *Dataflow cache* is implemented as a C++ class, compatible with *Vitis HLS*. All the configurable parameters are set using class template arguments.

The cache task provides high throughput in steady-state (it serves a hitting request in one CC), since it is optimally pipelined with II = 1 CC.

## **AXI** interface

The *Memory interface* task accesses the AXI bus at every request from the *Core* task. To save resources, it is not pipelined. Pipelining would rarely help, because a well-configured cache should never get multiple sequential misses, especially considering that there is one dedicated cache per source code array.

All DRAM accesses handle whole cache lines, which are sequential and aligned to the line size. To enable the HLS tool to infer that accesses are aligned, we explicitly zeroed the least significant bits of the address. This enables automated port widening and burst inference. If the line size is at most the maximum AXI interface width, it is accessed in a single request, else (more commonly) it is accessed in a burst request.

By default, *Vitis HLS* assumes *AXI latency* 64 CCs. This is useful to send pipelined requests on the AXI interface. However, our *Memory interface* is not pipelined. Thus, we set the AXI latency to zero, which makes the *Memory interface* stall after issuing an AXI request and resume right after the response, saving resources without losing performance.

16

#### **Cache interface**

To interface with the cache, we exposed the user-callable application programming interfaces (APIs) for managing requests and responses between the compute task and the cache.

- The get function accepts as input the address to read from cache and returns the read data. Internally it sends a read request (writing the address to the request FIFO), waits for the request-response latency (discussed later) in case of a hit or for longer in case of a miss, reads the data from the response FIFO, and returns the received data.

- The set function accepts as input the address and the data to write to the cache. Internally, it sends a write request (writing the address and the data to the request FIFO).

We overloaded the operator[] to automatically call the get and set functions, e.g., in Listing 2.1, a[i] = a[i + 1] is automatically compiled to a.set(a.get(i + 1), i).

As discussed in Section 2.2, the request-response distance should match the cache latency. The request-response distance value has an importance in terms of achieving a steady state without stalling. If the correct distance value is not set, it prevents exploiting the cache pipelining. In Section 2.5.2, the impact of this value on the execution time is studied. However, cache latency varies at runtime, as hits and misses (which have different latencies) are interleaved, depending on the access pattern and the cache configuration. Moreover, we need to distinguish between the different memory access types.

• For RO caches, the optimal distance value is typically around the average memory access latency *lat*

$$\overline{lat} = lat_{cache} \cdot hit\,ratio + lat_{DRAM} \cdot miss\,ratio.$$

(2.1)

$lat_{cache}$  varies from 3 CCs to 5 CCs based on cache configuration and timing constraints,  $lat_{DRAM}$  depends on the target FPGA board, and *hit ratio* and *miss ratio* depend on the application and cache configuration.

Array-Specific Dataflow Caches for HLS of Memory-Intensive Algorithms on FPGAs

- Read-write (RW) caches are affected by data dependencies with distances corresponding to the request-response distance. The latter should therefore balance cache performance and computation task performance (task II depends on the dependency distance). Experimental results (Section 2.5.4) show that a 2 CCs distance typically gives the best overall performance.

- For write-only (WO) caches, the request-response distance has no meaning because there is no response.

A template parameter is available to the users willing to fine-tune the distance of the caches in their designs.

# 2.3 Multi-Level Cache

18

The *Multi-level cache* extends the memory hierarchy of the cache by adding a level 1 (L1) cache on top of the *Dataflow cache*, i.e., the level 2 (L2) cache, as shown in Fig. 2.3b. This architecture is aimed at reducing the latency between a read access request and the corresponding response.

We are not interested in further accelerating the writes. Write latency has a negligible impact on performance, considering that they never stall the compute task (there is no response from the cache to the main computation), provided that the request FIFO is deep enough to accommodate all the pending writes. Moreover, write accesses are usually less frequent than reads.

Finally, the *Multi-level cache* is the starting point for enabling multiple concurrent accesses in the *Multi-port cache* described in Section 2.4.

Similarly to the cache by Ma et al. [39], the L1 cache is inlined in the compute logic. This reduces the latency of the memory accesses by avoiding the inter-task communication. Even if the L1 cache is inlined, the compute task pipeline II is preserved, unlike the cache by Ma et al. [39]. This is because (i) in case of miss the L1 cache interacts with the L2 cache instead of with the external DRAM. Furthermore, (ii) the L1 cache complies with the write-through policy (the L1 cache aims at accelerating only the reads), introducing fewer dependencies compared with the write-back policy.

To implement the *Multi-level cache* architecture, we extended the *Dataflow cache* source code. In the *Dataflow cache*, the response flows from the L2 to the compute task and contains a single word. In the *Multi-level cache* architecture, the response flows from the L2 to the L1 cache, and holds a whole cache line.

The *Dataflow cache* APIs were updated to support the L1 cache by adding the get\_line function. Moreover, we upgraded the implementation of the get and set functions, while keeping their signature unchanged.

- The get\_line function receives as input the address to read from cache and returns the line to which the address belongs. In particular, if the address hits the L1 cache, the line is read from the L1 cache. Otherwise, the request is issued to the L2 cache, as with the get function of the *Dataflow cache*.

- The get function calls the get\_line function and returns the requested word only.

- The set function marks the L1 cache line as dirty, if it hits, according to the write-through policy. Additionally it forwards the write request to the L2 cache as with the *Dataflow cache*.

The L1 cache supports the set-associative mapping policy. The number of sets and ways of the L1 cache are configurable through template parameters. Note that when the L1 cache parameters are set to zero, the resulting architecture is equivalent to the *Dataflow cache*.

Similarly to the L2 cache, the L1 cache memory is bound to BRAMs and the helper data is bound to registers. Both the L1 and the L2 caches use the same memory technologies, therefore the L1 cache could have comparable or even bigger size than the L2 cache. In experiment sections, Section 2.5.2 and Section 2.5.3, there are cases where L1 cache is larger than L2 cache. In these cases, L2 cache works as a memory arbiter. The results show the advantage in terms of performance.

According to our experimental results (Section 2.5.2), when an L1 cache is included on top of the L2 cache a convenient default value for the L2 request-response distance is 3 CCs for RO accesses, and 2 CCs for RW accesses.

Note that the default RW distance is lower than the RO one because higher distance values would make the read after write (RAW) dependencies distance longer and reduce the overall performance, as discussed in Section 2.2.1.

# 2.4 Multi-Port Cache

The *Dataflow* and *Multi-level* cache architectures provide a maximum throughput of one access per CC. This is efficient for pipelined algorithms, which access each cached array at most a single time per iteration. To efficiently implement algorithms which access the same array multiple times per iteration (either due to the user code or after a loop unrolling), we designed the *Multi-port cache* that enables multiple concurrent read accesses to the same array.

With the *Multi-port cache* architecture, a shared L2 cache exposes an arbitrary number of ports, each with a private L1 cache, as shown in Fig. 2.3c. The private L1 caches enable scheduling multiple memory accesses at the same time, without increasing the II of the compute task.

Hence, unlike Ma et al. [39], the L1 cache does not use directly the single DRAM interface, but goes through the shared L2 cache. Thus, we do not require users to manually mark explicitly some accesses as "always hit" (through the retrieve and modify functions), which would require extensive manual analysis and code changes and may lead to incorrect behavior.

To keep the cache logic simple and to avoid negatively affecting the compute task II, we did not implement any coherency mechanism. To guarantee the correct functionality, the *Multi-port cache* only supports read accesses. The extension to concurrent write or RW accesses is left to future work.

The *Multi-port cache* is implemented as an extension of the *Multi-level cache*. The number of ports *P* can be configured through a template parameter. When it is set to one, the architecture is equivalent to the *Multi-level cache*.

The *Core* task of the L2 cache was updated to cycle over each port, i.e., it sequentially serves the requests from the first to the last port, before restarting from the first one. Any port that did not send any request is skipped. This code pattern (hidden from the user behind the cache operator[]) can be optimized by the HLS tool to statically schedule *P* array accesses with II = 1 CC in most cases.

For each port, we allocate a private L1 cache, and the related pair of request and response FIFOs (to communicate with the shared L2 cache).

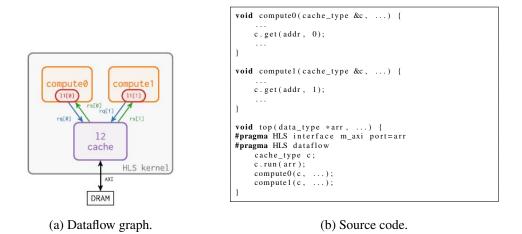

Fig. 2.4 Multiple-reader DRAM-mapped array, associated with our cache.

The access port can be selected either automatically or manually, when the userfriendly automatic port selection does not lead to the desired II for the algorithm pipeline.

- With the automatic selection, each call to get\_line (which is in turn called by get) is automatically associated to a specific port by means of a member variable holding the port index, which is updated after each access. This is implemented directly in the get function, that keeps track of the last accessed port and uses this information to bind a specific request to a specific port.

- The manual port selection allows one to explicitly inform the tool that each access uses different address and data streams, and that the dependencies are false. It is implemented by adding the port parameter (which identifies the number of the port to be accessed) to the get function (in this case the operator[] cannot be used).

In addition to the performance advantage, our *Multi-port cache* allows overcoming the *Vitis HLS* limitation of a single reader per AXI interface. Indeed, each L2 cache (associated with a single AXI interface) can expose multiple ports in the form of pairs of request/response FIFOs. These ports can connect the L2 cache to one or more compute dataflow tasks. Since the L2 cache ignores the ports with no pending requests, the compute tasks can seamlessly issue requests to the L2 cache at different rates. Figure 2.4 shows the dataflow graph of a kernel with a DRAM-mapped array that is read from two compute dataflow tasks, through a single L2 cache. Additionally, each compute task has its own private L1 cache. In *Vitis HLS*, if designers need to access the same DRAM array from different dataflow tasks, they must instantiate multiple AXI bundles, associated to the same underlying buffer in DRAM. Note that, due to the loose synchronization between dataflow tasks in *Vitis HLS*, both a dual-ported cache and a pair of bundles can be used meaningfully only for read-only arrays. Otherwise enforcing cache coherency or preserving data dependencies in a shared array between two processes would be very difficult.

# 2.5 Experiments

22

To evaluate the impact of the proposed cache architecture in terms of power, performance, and area (PPA), we used the cache in some memory-intensive benchmarks with very different access patterns. *We selected two "classical", frequently used algorithms (matrix multiplication and convolution), since they are widely known and provide good and easy to understand examples. In practice, our caches should be used either (i) for seldom used algorithms, for which a manual optimization effort would not be justified, or (ii) for those that do not exhibit regular access patterns, such as bitonic sorting, which is our third benchmark.*

We synthesized the benchmarks as *Vitis HLS* kernels and deployed them on a physical FPGA board to measure the resulting PPA. The experimental workflow consists of: (1) SW simulation, (2) HLS synthesis, (3) logic synthesis, place and route, and bitstream generation, and (4) execution and measurements.

Steps (1) and (2) were performed in *Vitis HLS* 2021.2 (using *Vitis* flow defaults), and step (3) in *Vivado* 2021.2 [57] (using *Vivado* defaults for synthesis and implementation). All steps targeted the *Avnet Ultra96v1* [4] board, hosting a *Xilinx Zynq UltraScale*+ FPGA. Figure 2.5 shows the block design for implementing an HLS kernel with three DRAM-mapped arrays (such as the matrix multiplication and convolution test cases). Given an algorithm (which determines the number of inputs and outputs, and by consequence of the AXI interfaces), the HLS kernel exposes the same interface, even when it is optimized with our cache, since the cache is fully implemented with HLS inside the kernel itself.

The board runs the *PYNQ Linux 2.7.0* [59] operating system (OS), whose *PYNQ* library is exploited in step (4).

Fig. 2.5 Block design with three DRAM arrays.

We collected the data from different sources:

- SW simulation reports

- *Hit ratio*: ratio between the number of requests that hit data in cache and the number of all requests for a specific cache memory.

- Post place and route reports

- *Area*: number of LUTs, FFs, BRAMs and DSPs required to implement the whole design.

- Maximum clock frequency: the maximum frequency at which timing was met by the implementation flow, achieved by gradually increasing the clock frequency constraint. The frequency higher bound is 333 MHz, that is the maximum supported frequency for the AXI adapter (330 MHz in practice, due to the clock generation logic limited precision).

- Runtime measurements

- *Performance*  $(t_{ex})$ : execution time, measured between the assertions of the start and the end signals of the kernel.

- Power (P): average power, measured by the sensor on the system power rail during kernel execution. Note that the selected board does not allow measuring the power of the FPGA only, therefore P is the power consumed by the whole board, including the CPU.

The measured quantities are not fully deterministic. The timer measuring  $t_{ex}$  may not be stopped at the exact time when the kernel asserts its end

signal, since it checks this condition through polling and the CPU might be busy running other tasks of the OS. Also, power consumption is affected by different factors, such as the CPU load or the temperature. Thus, each runtime measurement was taken five times and is collected as the average and the standard deviation of these measurements. The energy consumption (*E*) is computed as the average energy,  $E := Pt_{ex}$ .

To limit the design space, in all the cache configurations we used a default L2 cache request-response latency. For single-level RO configurations, we computed the default distance value as 7 CCs, according to (2.1), where the lat<sub>cache</sub> was set to the worst-case, i.e., 5 CCs, lat<sub>DRAM</sub> was set to 40 CCs according to the measurements by Marjanovic [43] of the read latency of the high-performance coherent ports of the target board, and hit ratio was assumed to be 95 % (these values were only used to set the cache parameters, while the runtime results reflect the real latencies and hit ratios). The experiments show that these approximations achieve good pipeline performance. A significant performance degradation is observed only if one assumes very low (1 CC), or very high (more than lat<sub>DRAM</sub>) distance values. We used a default distance of 3 CCs for multi-level, and 2 CCs for RW cache configurations. WO cache configurations are unaffected by the distance parameter.

In order to compare directly the cycle count performance of the various designs, we constrained the clock frequency to 100 MHz in all experiments, except for those that are related to the timing impact of the cache (Sections 2.5.2 to 2.5.4).

We manually chose the cache parameters, such as the line size, number of lines, and so on, based on the array access patterns. However, there are multiple methods to automate the selection of these parameters, as attested by a large amount of past work, for example those analyzed by Upadhyay and Sudarshan [49]. Integration of those approaches with our cache is left to future work.

# 2.5.1 Reference designs

We compared the collected results with:

1. *Baseline*: the kernel generated by default by the HLS tool, whose computational core directly accesses the external DRAM through the AXI interface.

24

- 2. *RTLCache*: the *Baseline* HLS kernel, with the Xilinx System Cache RTL module inserted in between the HLS kernel and the AXI DRAM interface (when the cache module configurability allows a setup with non-zero hit ratios).

- 3. *Manual*: the kernel manually optimized for buffering the data using the on-chip memories (when the memory access patterns allow it).

#### Ma et al. cache reference