## POLITECNICO DI TORINO Repository ISTITUZIONALE

### A Novel Quasi-Resonant Battery Charger for Photovoltaic Applications

Original

A Novel Quasi-Resonant Battery Charger for Photovoltaic Applications / Cerutti, Stefano; Musolino, Francesco; Crovetti, Paolo S.. - ELETTRONICO. - (2023), pp. 740-745. (Intervento presentato al convegno IEEE EUROCON 2023 - 20th International Conference on Smart Technologies tenutosi a Torino, Italy nel 06-08 July 2023) [10.1109/EUROCON56442.2023.10199050].

Availability: This version is available at: 11583/2981778 since: 2023-09-08T07:46:20Z

Publisher: IEEE

Published DOI:10.1109/EUROCON56442.2023.10199050

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A Novel Quasi-Resonant Battery Charger for Photovoltaic Applications

Stefano Cerutti, Francesco Musolino, Paolo S. Crovetti Department of Electronics and Telecommunications Politecnico di Torino Torino, Italy {stefano.cerutti, francesco.musolino, paolo.crovetti}@polito.it

Abstract—This work presents the analysis, design, PCB implementation and testing of a quasi-resonant low-voltage battery charger intended to be supplied by a photovoltaic (PV) module. The proposed battery charger exploits the Discontinuous Voltage Mode operation to transfer to the load a controlled and discrete amount of energy, alternately stored and released by two half-bridge capacitors. A small resonant inductance is added to assist the soft commutation of all the converter MOSFETs. The mathematical description of the operating principle and the main design equations of the converter are reported. Based on experiments, a 100 W prototype of the proposed battery charger achieves a flat conversion efficiency higher than 92 % over the wide 20 W – 95 W power range, with a peak of nearly 94 % at 40 W.

*Index Terms*—Quasi-resonant converter, battery charger, photovoltaic, soft-switching, Zero-Voltage Switching.

#### I. INTRODUCTION

Sustainable Development Goal (SDG) 7 of the 2030 Agenda of the United Nations, by promoting the extension of affordable, reliable and sustainable energy systems, addresses the need to increase the Renewable Energy Sources (RES) inside the countries energy mix [1]. Beside generation, a consistent effort should be devoted to more reliable and efficient conversion and distribution systems. Among the photovoltaic (PV)-fed applications, increasing attention is devoted to battery charging, especially for stand-alone systems [2]. Battery chargers for PV-fed applications should be designed to achieve a high efficiency over a wide range of operating powers, to address the intrinsic variability of RES.

To achieve a high efficiency conversion, resonant power converters have become a promising alternative to conventional Pulse-Width Modulated (PWM) converters, thanks to the possibility to reduce or eliminate the switching losses, reduce the Electromagnetic Interference (EMI) and increase the power density [3].

While extensive attention is devoted to resonant power converters for photovoltaic-to-grid applications [4], fewer works are devoted to resonant PV-fed low-voltage battery chargers. Most of the low-voltage battery chargers exhibit buck-derived topologies endowed with auxiliary resonant networks to achieve the soft commutation of their switches. The quasi-resonant buck-derived converter in [5] includes an additional LC resonant network to achieve the Zero-Voltage Switching (ZVS) of the main MOSFET. However, a resonant peak across

the main MOSFET requires to double its voltage rating, and the measured peak and average charging efficiencies of the proposed converter are 87% and 84% respectively. Another buck-derived topology is presented in [6], which achieves the Zero-Current Switching (ZCS) turn-OFF of the main switch thanks to an additional LC tank and an auxiliary switch. However, the large current peak on the input MOSFET, the large voltage peak on the output diode and the 90.3% peak efficiency remain the main issues of this converter. A PV-fed dual-stage converter is presented in [7], where a PWM booststage responsible for the Maximum Power-Point Tracking (MPPT) is followed by a half-bridge parallel-loaded resonant converter. Despite the desirable integration of MPPT, the relatively large component count and the adoption of a passive full-bridge rectifier results in a 88.7% average and 92% peak charging efficiency.

Aiming to achieve high conversion efficiency over a wide power range, a new PV-fed quasi-resonant converter is presented in this work. The topology is based on the gridsupplied constant power charger previously proposed in [8], but modified and optimized for a PV source. Differently from the above-mentioned topologies, the converter presented here exploits the parasitic capacitances of its switches to obtain soft commutation with an increase in power density. The rest of the paper is organized as follows: Section II describes the topology and operation of the converter. In Section III, the design of the converter is discussed in details. In order to validate the proposed approach, a 100 W prototype is built and the experimental results are presented in Section IV, while Section V draws the conclusions of this work.

#### II. ANALYSIS

#### A. Operating principle

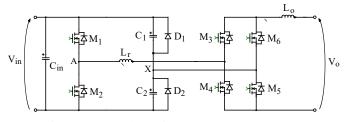

This work explores the possibility to apply the operating principle adopted in the constant-power charger described in [8] to a different topology optimized for a PV-sourced application. The topology, illustrated in Fig. 1, consists in a quasi-resonant, frequency-modulated half-bridge inverting stage (MOSFETs  $M_1$  and  $M_2$  and capacitors  $C_1$  and  $C_2$ , with  $C_1 = C_2 = C$ ) followed by an active rectifier stage.

The input MOSFETs are controlled with  $180^{\circ}$  phase shift and nearly 50% duty cycle, so as to generate a pure AC

Fig. 1: Proposed quasi-resonant battery charger.

voltage between nodes A and X. Unlike conventional halfbridge converters, in which the capacitances are selected to be large enough to maintain a stable voltage at node X,  $C_1$  and  $C_2$  are designed here to be alternately charged and discharged between 0 V and the input voltage. The output current is responsible for the charge and discharge of the half-bridge capacitances.

Clamping diodes  $D_1$  and  $D_2$  are added in anti-parallel connection to avoid charging  $C_1$  and  $C_2$  above  $V_{in}$  or discharging them below 0 V. This principle, denoted in [8] by Discontinuous Voltage Mode (DVM), allows to generate a triangular voltage across each capacitor and to transfer to the output a discretized amount of energy at each switching cycle.

An input capacitor  $C_{in}$  is added to the input port to stabilize the working point of the PV module.

The step-down transformer originally present in the gridfed topology in [8] is here removed because of the lower input voltage of the targeted PV-fed application. A typical crystalline-Silicon PV module (with 48 up to 72 cells), indeed, exhibits Maximum Power Point voltages ( $V_{\rm MPP}$ ) around few tens of volts, which do not need significant step-down to the low-voltage batteries.

An active rectifier, consisting of MOSFETs  $M_3$ ,  $M_4$ ,  $M_5$ and  $M_6$ , provides a full-wave rectification of the intermediate AC voltage. The choice of an active rectifier, despite the additional gate driving complexity, allows to eliminate the forward voltage drops of a passive diode-based rectifier. By considering, for instance, a 12 V battery and Schottky diodes with 0.4 V forward voltage, indeed, the diode conduction losses alone would imply almost 7% efficiency loss. Low  $R_{\rm DS,ON}$  transistors are required to limit the influence of conduction losses on the conversion efficiency.

The additional small resonant inductor  $L_r$ , connected to the switching node A between the half-bridge MOSFETs, is specifically added to assist the ZVS turn-ON of  $M_1$  and  $M_2$ .

An inductor  $L_{\rm o}$  filters the high-frequency harmonics of the output current  $I_{\rm o}$  to provide a smooth charging of the output battery.

#### B. Analysis of a switching cycle

This section provides the analysis of the main converter voltage and current waveforms through a switching period. Since the operation of the converter is symmetric, the description only considers a half period.

The mathematical analysis of a switching period presented here is based on the following assumptions:

- the input capacitor C<sub>in</sub> is assumed to keep a constant DC input voltage V<sub>in</sub>;

- the output filter inductor L<sub>o</sub> is assumed to keep a constant DC output current I<sub>o</sub>;

- the half-bridge MOSFETs  $M_1$  and  $M_2$  are ideal, except for their output parasitic capacitance  $C_s$ ;

- the forward voltage drops of the clamping diodes and MOSFETs body diodes are neglected;

- the reactive components  $C_1$ ,  $C_2$ ,  $L_r$  and  $L_o$  are lossless and ideal.

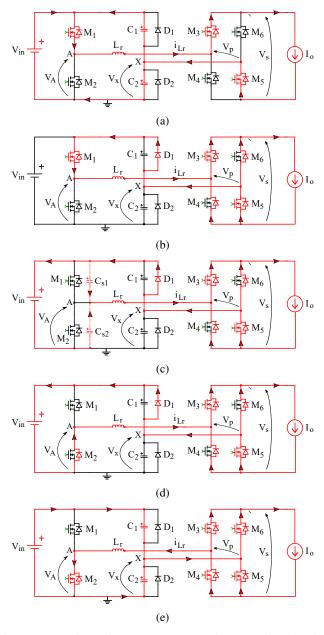

The working operation of the converter in a half switching period can be subdivided into 3 phases that are illustrated in Fig. 2.

1) Power transfer phase (PT, Fig. 2a): During this phase,  $M_1$ ,  $M_3$  and  $M_5$  conduct the output current  $I_0$ , whereas  $M_2$ ,  $M_4$  and  $M_6$  are turned OFF. At node X,  $I_0$  splits equally, gradually charging  $C_2$  and discharging  $C_1$ .  $V_x$  increases linearly from 0 V to  $V_{\rm in}$ , as shown in Fig. 3:

$$V_{\rm x}(t) = \frac{I_{\rm o}}{2C}t.$$

(1)

During this phase,  $L_{\rm r}$  is connected in series to  $L_{\rm o}$ . As a consequence, since  $I_{\rm o}$  is assumed to be constant, no voltage drop appears across it. The rectifier primary voltage  $V_{\rm p}$  assumes a triangular behaviour:

$$V_{\rm p}(t) \approx V_{\rm A} - V_{\rm x} = V_{\rm in} - \frac{I_{\rm o}}{2C}t.$$

(2)

The secondary voltage  $V_{\rm s}$  temporarily coincides with  $V_{\rm p}$ . This phase ends when  $V_{\rm x}$  has reached  $V_{\rm in}$ .

2) Current circulating phase (CC, Fig. 2b):  $M_1$ ,  $M_3$  and  $M_5$  are still ON. When  $V_x$  has reached  $V_{in}$ , the bypass diode  $D_1$  gets forward biased and clamps  $V_x$ , as shown in Fig. 3. The rectifier primary voltage  $V_p$  becomes zero and forces the body diodes of  $M_4$  and  $M_6$  to turn-ON, which start sinking current from  $M_3$  and  $M_4$ . A free-wheeling path for  $I_o$  is created and no power is temporarily transferred to the battery.

3) Crossover resonant phase (CR, Fig. 2c-2e): This phase begins when  $M_1$  is turned OFF. During the dead-time,  $L_r$ starts resonating with the output parasitic capacitances of  $M_1$ and  $M_2$  ( $C_{s1} = C_{s2} = C_s$ ), as shown in Fig. 2c, pushing  $V_A$ below 0 V, as illustrated in Fig. 3. This behaviour only occurs if the energy stored in the tank inductor  $L_r$  is sufficient to completely charge  $C_{s1}$ . This condition translates into a lower boundary for  $L_r$ :

$$L_{\rm r} > \frac{2C_{\rm s}V_{\rm in}^2}{I_{\rm o}^2}$$

(3)

Once  $V_{\rm A}$  reaches 0 V, the body diode of  $M_2$  gets forwardbiased and conducts the  $L_{\rm r}$  current  $i_{\rm L_r}$ , as shown in Fig. 2d. The voltage  $V_{\rm x}$  (almost constant during this phase) appears across  $L_{\rm r}$  and forces  $i_{\rm L_r}$  to a linear decrease:

$$i_{\rm L_r} = I_o - \frac{V_{\rm in}}{L_{\rm r}}t\,. \tag{4}$$

The difference between  $i_{L_r}$  and  $I_o$  flows through the body diodes of  $M_4$  and  $M_6$ .

Fig. 2: Operation of the converter during a half switching period: (a) PT phase; (b) CC phase; (c) CR phase:  $L_r$  resonates with  $C_{s1}$  and  $C_{s2}$ ; (d) CR phase: the body diode of  $M_2$  starts conducting; (e) CR phase:  $M_2$ ,  $M_4$  and  $M_6$  turn-ON at zero voltage, and  $i_{L_r}$  inverts its polarity.

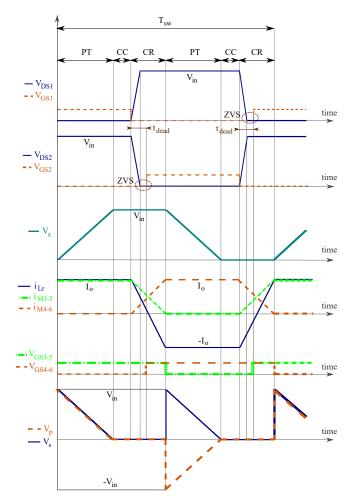

After a deadtime  $t_{dead}$ ,  $M_2$  is turned ON, as shown in Fig. 2e. If its body diode is still conducting, the commutation occurs at zero voltage, as schematically represented in Fig. 3. In this case, the energy stored in the parasitic capacitance of the turned-OFF MOSFET, instead of being dissipated, is recovered at the input. The maximum allowed deadtime  $t_{dead,max}$  to achieve ZVS is limited by the time required by the parasitic output capacitance  $C_{s2}$  of  $M_2$  to be fully discharged (denoted by  $t_1$ ), and by  $i_{L_r}$  to become null: when it inverts its polarity, indeed,  $L_r$  starts resonating again with the output

Fig. 3: Main voltage and current waveforms in a switching period.

capacitances of  $M_1$  and  $M_2$ , and the ZVS condition is lost. This maximum time can be analytically estimated assuming a linear current discharge:

$$t_{\rm dead,max} \approx t_1 + \frac{L_{\rm r}I_{\rm o}}{V_{\rm in}}$$

(5)

Together with  $M_2$ , also  $M_4$  and  $M_6$  are turned ON, at zerovoltage. The Kirchhoff Current Law (KCL) applied at the output nodes allows to derive the source-to-drain MOSFETs currents as:

$$i_{\rm M_3} = i_{\rm M_5} = \frac{I_{\rm o}}{2} + \frac{i_{\rm L_r}}{2}$$

(6)

$$i_{\rm M_4} = i_{\rm M_6} = \frac{I_{\rm o}}{2} - \frac{i_{\rm L_r}}{2}$$

(7)

From (6), if  $M_3$  and  $M_5$  are turned OFF when  $i_{L_r} = -I_o$ , ZCS commutation is achieved, as shown in Fig. 3. The CR phase is concluded when  $M_3$  and  $M_5$  are turned OFF. It is important to observe that the duration of this phase is exaggerated in Fig. 3 for a better visualization.

The previous analysis assumes that the switching period is long enough to allow  $I_0$  charging and discharging  $C_1$  and  $C_2$  between 0 V and  $V_{in}$ . If this is true, the transferred power can be simply computed by multiplying the energy stored and released by each capacitor  $C_1$  and  $C_2$  by the switching frequency:

$$P \approx 2CV_{\rm in}^2 f_{\rm sw}.\tag{8}$$

However, this condition occurs only if  $I_o$  can raise/lower the  $V_x$  voltage by  $V_{in}$ . Given a target peak current  $I_{o,max}$ , the condition holds for:

$$\frac{T_{\rm sw}}{2} \ge 2C \frac{V_{\rm in}}{I_{\rm o,max}} \Rightarrow f_{\rm sw} \le \frac{I_{\rm o,max}}{4CV_{\rm in}} \stackrel{\Delta}{=} f_{\rm limit}.$$

(9)

For  $f_{\rm sw} > f_{\rm limit}$ , the output power starts decreasing nonlinearly with the switching frequency. In this second operating mode,  $I_{\rm o}$  charges and discharges only partially  $C_1$  and  $C_2$ , causing  $D_1$  and  $D_2$  to never enter in conduction. As a result,  $V_{\rm x}$  assumes a triangular shape centered around  $V_{\rm in}/2$  and the CC phase is not achieved.

Beside this, the PT and CR operating phases remain as before. Due to the partial charging of the dividing capacitors,  $V_{\rm p}$  and  $V_{\rm s}$  assume a trapezoidal behaviour.

It is important to observe that the battery charging voltage is the average of  $V_s$ , which is a direct consequence of the voltsecond balance applied to  $L_o$ . This implies that, to ensure the desired battery charging:

$$\overline{V_{\rm s}} \approx \frac{V_{\rm in}}{2} \ge V_{\rm batt} \Rightarrow V_{\rm in} \ge \frac{V_{\rm batt}}{2}.$$

(10)

Condition (10) dictates the minimum input voltage, i.e. the minimum number of series-connected cells that the input PV source should exhibit to satisfy the voltage constraint. Assuming monocrystalline silicon, a good estimate for the open circuit voltage is 0.55 V [9]: as such, a minimum number of 48 cells is required to ensure net power flow to a 12 V battery.

#### III. DESIGN OF A 100 W PROTOTYPE

A physical prototype was designed and tested to validate the predicted theoretical and simulation results on the working operation, and to derive the converter performances in terms of conversion efficiency. The designed input voltage was selected to be below 30 V, corresponding to typical open-circuit voltages of 48-cell PV panels.

The converter MOSFETs exhibit the same current stresses  $(I_o/2 \text{ RMS} \text{ current} \text{ and } I_o \text{ peak current})$ , but different voltage stresses. While  $M_1$  and  $M_2$  voltage is bounded by  $V_{\text{in}}$ , the rectifier MOSFETs are subjected to large voltage spikes when they are turned OFF. This phenomenon occurs because the difference between  $i_{L_r}$  and  $I_o$  flows in their parasitic capacitances, producing resonant spikes that require to increase their voltage rating. Due to the temporary shortage of silicon power devices, the same 100 V rated transistor was selected. Since the topology is designed to reduce or eliminate the switching losses, a low conduction resistance  $R_{\text{DS,ON}}$  (below  $10 \text{ m}\Omega$ ) is determinant to obtain a high-efficiency conversion.

The adopted Si-MOSFETs, can be turned ON with  $V_{\rm GS} = 5$  V. A dual-output DC-DC converter was adopted to generate the supply voltages for the half-bridge and rectifier MOSFETs from  $V_{\rm in}$ . Three half-bridge gate drivers were selected, which rely on external bootstrap networks to drive the high-side MOSFETs.

The dividing capacitors  $C_1$  and  $C_2$  are subjected to a significant RMS current stress  $\frac{I_0}{2}$ , requiring a low ESR and large stability to frequency variations. On the other hand, their working voltage is limited by  $V_{in}$ , thanks to the clamping diodes action. The capacitance value is a design parameter linked to the desired rated power, at rated source voltage and boundary frequency conditions, as determined in Eq. (9). In the present design, assuming 100 W rated power at 28 V input voltage, 12 V battery voltage and 60 kHz operation, the required capacitance must satisfy:

$$C \le \frac{P_{\text{rated}}}{4f_{\text{limit}}V_{\text{in}}V_{\text{batt}}} \approx 1.24\,\mu\text{F}.$$

(11)

The adopted Multi-Layer Ceramic Capacitor (MLCC) is characterized by  $50\,V_{\rm DC}$  rated voltage,  $12\,A_{\rm RMS}$  rated current at  $100\,\rm kHz$  and  $940\,\rm nF$  capacitance.

The input capacitor  $C_{in}$ , responsible for stabilizing the working point of the PV panel was selected according to the allowed input current ripple. This limit can be linked to the deterioration of the output power of a PV panel when it is forced to provide strongly rippled current.

Elkhateb et al. in [10], exploiting a Single-Diode Model (SDM), derived an analytic relation between the current ripple  $\Delta I_{\rm RMS}$  and the power decrease  $\Delta P_{\rm ripple}$  of a PV panel:

$$\frac{\Delta P_{\rm ripple}}{P_{\rm MPP}} \approx 10.67 \left(\frac{\Delta I_{\rm RMS}}{I_{\rm MPP}}\right)^2.$$

(12)

By applying this approach to the equivalent SDM of a commercial poly-crystalline silicon 48-cell, an approximated constraint was derived for the capacitor ESR:

$$ESR \ll 650 \,\mathrm{m}\Omega.$$

(13)

From the relation of the RMS currents applied at the input node, an approximated expression for the RMS capacitor current  $i_{C_{in,RMS}}$  can be derived:

$$i_{\mathrm{C}_{\mathrm{in,RMS}}} \approx 2C f_{\mathrm{sw}} (V_{\mathrm{in}} + 2V_{\mathrm{fd}}) \sqrt{\frac{V_{\mathrm{in}}}{2V_{\mathrm{batt}}} - 1}$$

, (14)

where  $V_{\rm fd}$  is the forward voltage drop of the clamping diodes. Assuming the above-mentioned worst-case conditions,  $i_{\rm C_{in,RMS}} \approx 1.34 \,\rm A$ . An aluminum electrolytic capacitor was selected, exhibiting 63 V rated voltage, 750 µF capacitance, 68 m $\Omega$  ESR and 2.5 A rated ripple current.

The inductor  $L_{o}$  was sized according to the maximum allowed current ripple overimposed to the average charging current. Application Notes like [11] recommend to limit the ripple current in *ampere* below a value equal to 1/20 of the battery capacity, expressed in *ampere-hour*. Considering a 50 A h battery, for instance, the ripple current should be maintained below 2.5 A.

By integrating the  $L_{o}$  voltage, an approximated value of the parabolic current ripple can be determined:

$$\Delta I_{\rm o,ripple} \approx \frac{V_{\rm in}}{12 f_{\rm sw} L_{\rm o}} < 2.5 \,\mathrm{A}\,. \tag{15}$$

The current rating should consider the maximum charging current ( $\approx 8 \text{ A}$  for a 100 W operation). A ferrite-core, wirewound inductor was selected, with  $8.8 \text{ m}\Omega$  DC resistance, 13 A saturation current for 30% inductance decrease, and 17.5 A maximum current for a temperature increase of 40 °C. Its 47 µH inductance satisfies Eq. (15) for the rated power condition. The DC losses of this component at the maximum power condition are estimated to weigh for around the 0.6% of the total power.

The inductance value of  $L_r$ , investigated in details in this work, determines two concurrent consequences:

- the maximum allowed deadtime to achieve ZVS of the half-bridge MOSFETs, as described in (3).  $L_r$  should be large enough to relax the timing constraints imposed on the controller and the gate drivers;

- on the other hand, an increased inductance value increases the reactive power absorbed by  $L_r$ , in turns decreasing the power peak of the static characteristic and reducing  $f_{\text{limit.}}$

A trade-off value of 330 nH was selected iteratively relying on *LTspice XVII* simulations [12]. According to (3), this value, combined with the MOSFETs parasitic  $C_s = 640 \text{ pF}$  and with  $V_{in} = 28 \text{ V}$ , satisfies the necessary condition for ZVS for any output current larger than 1.23 A. This consideration has important consequences on the behaviour of the conversion efficiency: it states that  $L_r$  value provides a minimum operating power above which a deadtime exists such that ZVS can be achieved. As a result, the switching losses, which may be impactful at light loads conditions, are basically eliminated on a wide range of larger operating powers, if a proper deadtime is selected. It is meaningful to observe that the ZVS condition is achieved exploiting a small inductor and the output parasitic capacitances of the half-bridge MOSFETs, with benefits on the power density.

A ferrite-core inductor was selected, exhibiting low DC resistance  $(1.3 \text{ m}\Omega)$ , 36.5 A rated current for  $40 \text{ }^{\circ}\text{C}$  temperature increase, and 62 A saturation current for a 20% inductance decrease.

Tab. I summarizes the selected components for the physical prototype, while Fig. 4 shows the top view of the physical PCB prototype of quasi-resonant battery charger.

#### IV. EXPERIMENTAL RESULTS

The aim of the experimental testing was to prove the coherence of the measured open-loop operation with the theoretical analysis and extract meaningful measurements of efficiency. The experimental testbench is illustrated in Fig.

TABLE I: Main converter components for the physical prototype.

| Component                        | Part code          | Manufacturer     |

|----------------------------------|--------------------|------------------|

| MOSFETs $M_{1,6}$                | TPH4R10ANLL1Q      | Toshiba          |

| Resonant inductor $L_r$          | IHLP5050CEERR33M01 | Vishay           |

| Dividing capacitors $C_{1,2}$    | C1812C944J5JLC7805 | KEMET            |

| Input capacitor $C_{in}$         | UCZ1J751MNS1MS     | Nichicon         |

| Output filter inductor $L_0$     | 74437529203470     | Würth Elektronik |

| Clamping diodes D <sub>1,2</sub> | V8PAL45HM3_A/I     | Vishay           |

| Half-bridge gate drivers         | ADUM3223WARZ       | Analog Devices   |

| Dual-output DC-DC converter      | PRQ3W-Q48-D55-S    | Cui Inc.         |

Fig. 4: Top view of the 100 W PCB prototype.

5. A DC power supply and a programmable electronic load were adopted as source and load, respectively. The switching functions to drive the MOSFETs were generated by Intel Cyclone V FPGA on Terasic De1-SoC board, through a Finite State Machine algorithm.

Fig. 6 shows some of the acquired experimental waveforms. Specifically, Fig. 6a depicts the steady-state behaviour of  $V_{\rm DS2}$ ,  $V_{\rm x}$  and  $i_{\rm Lr}$ . The measurements refer to  $V_{\rm in} = 27.5$  V,  $V_{\rm batt} = 12$  V,  $f_{\rm sw} = 45$  kHz and  $t_{\rm dead} = 80$  ns. The measured waveforms are coherent with the predicted behaviour of the converter in the DVM, since  $f_{\rm sw} < f_{\rm limit} \approx 48.4$  kHz.

Fig. 6b shows a detail of the ZVS turn-ON of  $M_2$  with the adopted deadtime value. As visible, since  $V_{\text{GS1}}$  toggles to 5 V before  $i_{\text{L}_r}$  reverses polarity, the body diode of  $M_2$  is conducting and ensures the zero-voltage turn-ON.

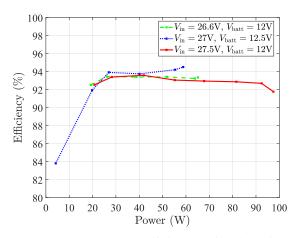

Fig. 7 reports some efficiency plots referring to different source and load voltage conditions, at a fixed 80 ns deadtime. The switching frequency was varied up to  $f_{\text{limit}}$  to modify the operating power: for each working point, the conversion

Fig. 5: Testbench for the experimental validation of the prototype.

Fig. 6: Experimental waveforms of the converter: (a)  $V_{\rm DS2}$ ,  $V_{\rm x}$  and  $i_{\rm L_r}$ ; (b) Zoom on  $V_{\rm DS2}$ ,  $V_{\rm GS2}$  and  $i_{\rm L_r}$  during the ZVS turn-ON of  $M_2$ .

efficiency was computed by including also the gate driving losses. The results show an almost flat efficiency curve independently on the source and load conditions, for operating powers larger than 20 W, and a peak efficiency of 94.5%. The selected deadtime ensures ZVS for almost all the power range, allowing to avoid the frequency-dependent increase of the switching losses. A flat efficiency curve is a desirable feature of PV-fed systems, due to the need to ensure high efficiency over a wide range of operating powers, intrinsic characteristic of RES. This is the reason why this converter is considered to be suitable for PV applications. At low power operations, the ZVS condition is lost and a minimum of 84% efficiency is measured at 5 W.

#### V. CONCLUSIONS

This work proposed a new quasi-resonant battery charger designed to achieve the ZVS of its switches. The quasi-resonant behaviour exploits a small additional inductor and the parasitic capacitances of the MOSFETs, allowing to decrease the overall component count. The adoption of an active rectifier and the selection of low  $R_{\rm DS,ON}$  MOSFETs allow to decrease the conduction losses, while the ZVS minimizes the switching losses over a wide range of operating powers. A 100 W prototype is designed and tested to validate the operating principle and measure the conversion efficiency. The experimental results are in agreement with the expected operation and prove that the charger is able to achieve an almost flat efficiency over the wide  $20 \, {\rm W} - 95 \, {\rm W}$  operating range with

Fig. 7: Measured conversion efficiency as function of operating power, for different source and load voltages.

94% peak. Below 20 W operation, the efficiency decreases because of the absence of ZVS condition and reaches 84% at 5 W operation.

#### REFERENCES

- J. Sachs, C. Kroll, G. Lafortune, G. Fuller, and F. Woelm, Sustainable Development Report 2022, Cambridge: Cambridge University Press, 2022.

- [2] E. O. Ogunniyi and H. Pienaar, "Overview of battery energy storage system advancement for renewable (photovoltaic) energy applications," 2017 International Conference on the Domestic Use of Energy (DUE), Cape Town, South Africa, 2017, pp. 233-239, doi: 10.23919/DUE.2017.7931849.

- [3] M.K. Kazimierczuk, and D. Czarkowski, Resonant Power Converters, Hoboken: Wiley, 2012.

- [4] S. Kouro, J. I. Leon, D. Vinnikov and L. G. Franquelo, "Grid-Connected Photovoltaic Systems: An Overview of Recent Research and Emerging PV Converter Technology," in IEEE Ind. Electron. Mag., vol. 9, no. 1, pp. 47-61, March 2015, doi: 10.1109/MIE.2014.2376976.

- [5] Y. -C. Chuang and Y. -L. Ke, "A Novel High-Efficiency Battery Charger With a Buck Zero-Voltage-Switching Resonant Converter," in IEEE Trans. Energy Convers., vol. 22, no. 4, pp. 848-854, Dec. 2007, doi: 10.1109/TEC.2006.882416.

- [6] Y. -C. Chuang, "High-Efficiency ZCS Buck Converter for Rechargeable Batteries," in IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2463-2472, July 2010, doi: 10.1109/TIE.2009.2035459.

- [7] Y.-L. Ke, Y.-C. Chuang, M.-S. Kang, Y.-K.g Wu, C.-M. Lai and C.-C. Yu, "Solar power battery charger with a parallel-load resonant converter," 2011 IEEE-IAS Annu. Meet., Orlando, FL, 2011, pp. 1-8, doi: 10.1109/IAS.2011.6074300.

- [8] N. K. Poon, B. M. H. Pong and C. K. Tse, "A constant-power battery charger with inherent soft switching and power factor correction," in IEEE Trans. Power Electron., vol. 18, no. 6, pp. 1262-1269, Nov. 2003, doi: 10.1109/TPEL.2003.818823.

- [9] S. Chander, A. Purohit, A. Sharma, Arvind, S.P. Nehra, M.S. Dhaka, "A study on photovoltaic parameters of mono-crystalline silicon solar cell with cell temperature," Energy Reports, vol. 1, pp. 104-109, 2015, doi: 10.1016/j.egyr.2015.03.004.

- [10] A. Elkhateb, N. A. Rahim, J. Selvaraj and B. W. Williams, "The effect of input current ripple on the photovoltaic panel efficiency," 2013 IEEE Conf. Clean Energy Technol. (CEAT), Langkawi, Malaysia, 2013, pp. 478-481, doi: 10.1109/CEAT.2013.6775680.

- [11] S. Gerner, T. Ruhlmann, , "Effect of AC Ripple on VRLA Battery Performance", Emerson Network Power, Columbus, OH, Tech. Note TN-0008, 2010.

- [12] Analog Devices Design Center LTspice. Available: https://www.analog.com/en/design-center/design-tools-and-calculators/ \ltspice-simulator.html. Accessed: Feb. 9, 2023.