### POLITECNICO DI TORINO Repository ISTITUZIONALE

Recent Advances and Future Prospects for Memristive Materials, Devices, and Systems

| Original Recent Advances and Future Prospects for Memristive Materials, Devices, and Systems / Song, Min-Kyu; Kang, Ji-Hoon; Zhang, Xinyuan; Ji, Wonjae; Ascoli, Alon; Messaris, Ioannis; Samil Demirkol, Ahmet; Dong, Bowei; Aggarwal, Samarth; Wan, Weier; Hong, Seok-Man; George Cardwell, Suma; Boybat, Irem; Seo, Jae-sun; Lee, Jang-Sik; Lanza, Mario; Yeon, Hanwool; Onen, Murat; Li, Ju; Yildiz, Bilge; del Alamo, Jes('(u))s. A.; Kim, Seyoung; Choi, Shinhyun; Milano, Gianluca; Ricciardi, Carlo; Alff, Lambert; Chai, Yang; Wang, Zhongrui; Bhaskaran, Harish; Hersam, Mark C.; Strukov, Dmitri; Philip Wong, HS.; Valov, Ilia; Gao, Bin; Wu, Huaqiang; Tetzlaff, Ronald; Sebastian, Abu; Lu, Wei; Chaila Leon; Joshua Yang, J.; Kim, Jeehwan In: ACS NANO - ISSN 1936-0851 17:13(2023), pp. 11994-12039. [10:1021/acsnano.3c03505] |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Publisher: American Chemical Society                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Published DOI:10.1021/acsnano.3c03505                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Terms of use:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Publisher copyright                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (Article begins on next page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

www.acsnano.org

## Recent Advances and Future Prospects for Memristive Materials, Devices, and Systems

Min-Kyu Song,<sup>‡</sup> Ji-Hoon Kang,<sup>‡</sup> Xinyuan Zhang, Wonjae Ji, Alon Ascoli, Ioannis Messaris, Ahmet Samil Demirkol, Bowei Dong, Samarth Aggarwal, Weier Wan, Seok-Man Hong, Suma George Cardwell, Irem Boybat, Jae-sun Seo, Jang-Sik Lee, Mario Lanza, Hanwool Yeon, Murat Onen, Ju Li, Bilge Yildiz, Jesús A. del Alamo, Seyoung Kim, Shinhyun Choi, Gianluca Milano, Carlo Ricciardi, Lambert Alff, Yang Chai, Zhongrui Wang, Harish Bhaskaran, Mark C. Hersam, Dmitri Strukov, H.-S. Philip Wong, Ilia Valov, Bin Gao, Huaqiang Wu, Ronald Tetzlaff, Abu Sebastian, Wei Lu, Leon Chua, J. Joshua Yang, and Jeehwan Kim\*

Downloaded via POLITECNICO DI TORINO on July 18, 2023 at 09:02:37 (UTC). See https://pubs.acs.org/sharingguidelines for options on how to legitimately share published articles.

Cite This: ACS Nano 2023, 17, 11994-12039

ACCESS I

III Metrics & More

Article Recommendations

ABSTRACT: Memristive technology has been rapidly emerging as a potential alternative to traditional CMOS technology, which is facing fundamental limitations in its development. Since oxide-based resistive switches were demonstrated as memristors in 2008, memristive devices have garnered significant attention due to their biomimetic memory properties, which promise to significantly improve power consumption in computing applications. Here, we provide a comprehensive overview of recent advances in memristive technology, including memristive devices, theory, algorithms, architectures, and systems. In addition, we discuss research directions for various applications of memristive technology including

hardware accelerators for artificial intelligence, in-sensor computing, and probabilistic computing. Finally, we provide a forward-looking perspective on the future of memristive technology, outlining the challenges and opportunities for further research and innovation in this field. By providing an up-to-date overview of the state-of-the-art in memristive technology, this review aims to inform and inspire further research in this field.

KEYWORDS: memristor, compute-in-memory, resistive switching memory, ferroelectric memory, phase change memory, ion-intercalation resistors, memtransistors, neuromorphic computing, in-sensor computing

#### 1. INTRODUCTION

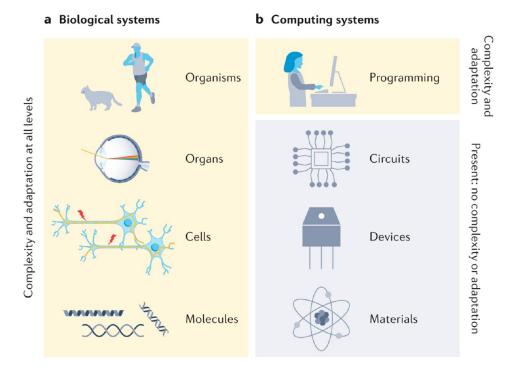

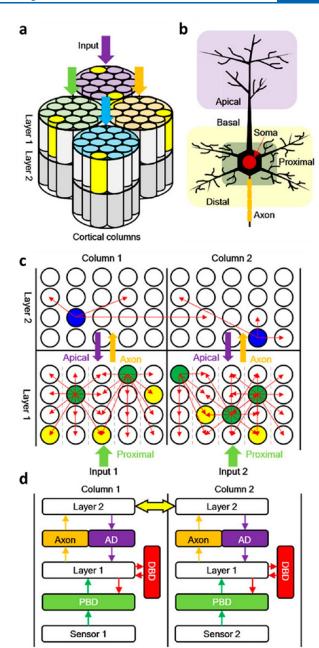

Over the past 70 years, Complementary Metal-Oxide Semiconductor (CMOS) technology has advanced rapidly, making it one of the most influential technologies in human history. Exponential scaling of the switching channel in CMOS devices, followed by Moore's law, is one of the key enablers for the advancement.1 However, CMOS scaling is approaching fundamental physical limits, which has necessitated the need to look for alternative switching devices to continue improving computational performance.<sup>2–4</sup> An ionic-based resistive switching device (i.e., a memristor) is a leading candidate in this context.<sup>5–8</sup> Due to its programmable analog memory effect, which resembles the function of biological synapses in the human brain, memristors have been regarded as a building block of neuromorphic (i.e., brain-like) electronics. This technology has the potential not only to provide biomimetic devices that support human-like data processing but also for influencing even the most basic forms of electronics (Figure 1).

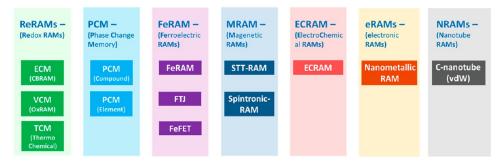

A memristor can be defined as a passive component that remembers the amount of charge that has passed through it.<sup>9,10</sup> In addition to redox-based resistive switching memory (also known as resistive random-access memory-ReRAM), which was regarded as the memristor, various types of devices,

Received: April 19, 2023 Accepted: June 5, 2023 Published: June 29, 2023

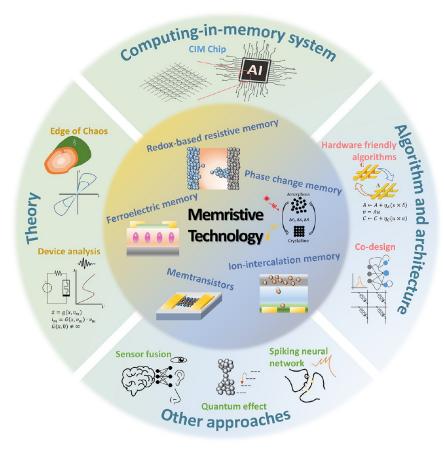

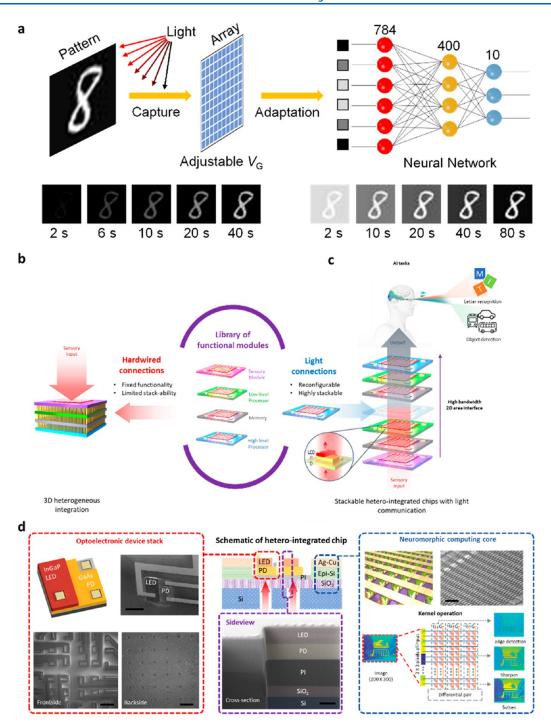

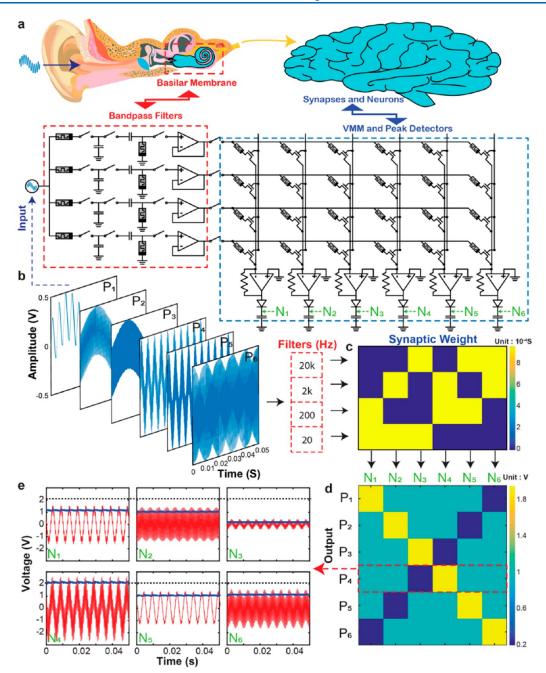

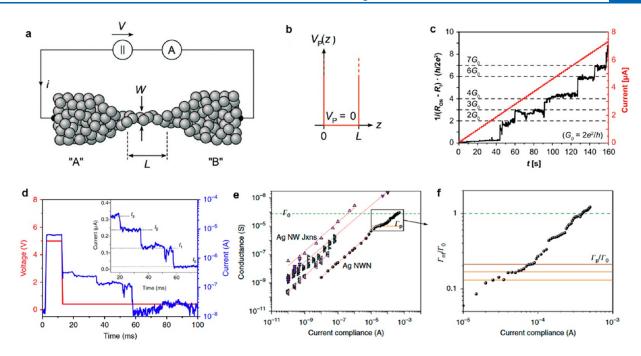

Figure 1. Development of memristive technology. Various memristive devices have been proposed including redox resistive switching memory, phase change memory, ferroelectric memory, ion-intercalation memory, and memtransistors. Four different categories of the research areas using such devices are presented in this review.

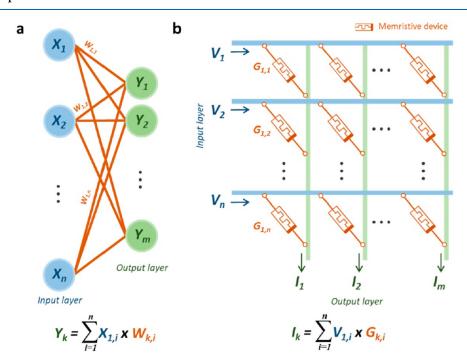

Figure 2. Artificial neural network (ANN) and hardware implementation using memristive devices of matrix-vector multiplication. (a) Single-layered perceptron model and (b) corresponding memristive crossbar array. Input, weight, and output values in ANN correspond to input voltage, conductance of memristive devices, and output current, respectively.

#### Memristors work, based on different physical phenomena

#### RRAMs - Resistive Random Access Memories

Figure 3. Memristive devices classified in accordance with different physical phenomena underlying their operational principle.

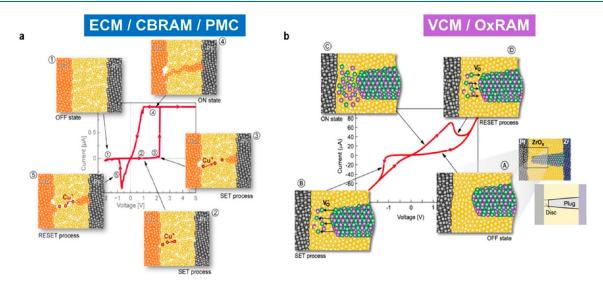

Figure 4. Different types of bipolar switching, depending on the predominant mobile species. (a) Electrochemical metallization memory and (b) valence change memory. The main difference is that for the establishment of high resistive and low resistive states in VCM devices, a formation and modulation of a Schottky barrier is essential. Reprinted with permission under a Creative Commons CC BY License from ref 31. Copyright 2022 John Wiley & Sons.

including two-terminal devices (i.e., phase-change memory and magnetic tunnel junctions) and three-terminal devices (i.e., ferroelectric transistors, ion-intercalation resistors, and memtransistors), have been proposed to show a "memristive" property. Thus, in this review, a memristive device refers to any device whose resistance is programmable under voltage or current inputs and is retained without a power supply. One of the key features of memristive devices is that they can be used as computing units in the form of crossbar arrays. By Ohm's law and Kirchhoff's law, a crossbar array can naturally perform matrix-vector multiplication (MVM) (Figure 2), 11,12 which is also called compute-in-memory (CIM). While the conventional von Neumann computing architecture suffers from the high energy costs of data transmission between processing units and memory units, CIM can significantly improve the computing power efficiency through massively parallel processing. Since data processing based on artificial neural networks for artificial intelligence (AI) requires numerous MVM, CIM has received great attention for AI accelerator development. Furthermore, memristive devices can be used for implementing alternative computing paradigms such as spiking neural networks, in-sensor computing, and probabilistic computing.

The purpose of this review is to comprehensively highlight recent advances in memristive technology and to discuss opportunities and challenges for future research. We first discuss recent advances in various types of memristive devices based on material properties before then focusing on studies of memristor theory. We also present the development of memristive algorithms, architectures, and systems, in addition to emerging memristive applications and AI accelerators. Finally, forward-looking perspectives on the future prospects of memristive technologies are presented.

## 2. MEMRISTIVE BEHAVIORS OF VARIOUS MATERIALS AND DEVICES

**2.1.** Material Design of Redox-Based Resistive Switching Memory. One of the most prominent examples for the important synergy between nanoionics and nanoelectronics are memristive devices. Three different research areas, namely resistive memories, <sup>13,14</sup> (nano)ionic-based devices, <sup>15</sup> and the memristor theory <sup>10,16</sup> were established in early 1970s and 1980s, that developed in parallel and finally merged in 2008, building the fundament for memristive technologies. In 2008, Strukov et al. <sup>9</sup> have proposed resistive switching memories as the missing fourth circuit element, the memristor, as theoretically proposed by L. Chua in 1970, thus initiating the fusion of

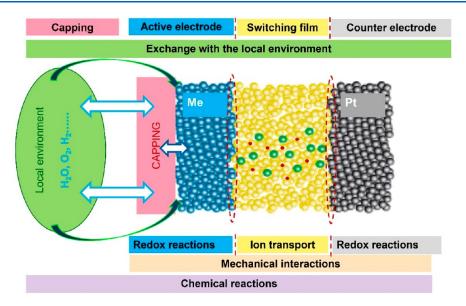

Figure 5. Structure of a memristive device and the processes and possible interactions between different components of the cell.

these three research fields. The modern developments in memristive technologies cover a variety of applications beyond memories such as sensors, nanoactuators, selector devices, memristive transistors, artificial neurons, and synapsis for brain inspired computing. A simple classification based on the physical processes responsible for the resistive switching is presented in Figure 3.

Among the most important categories of resistive switches are the electrochemical metallization cells (ECM, also known as conductive bridge RAM—CBRAM or programmable metallization cells), <sup>17</sup> valence change mechanism memories (VCM, also known as metal oxide resistive memory—OxRAM), <sup>18–20</sup> and thermochemical mechanism (TCM)<sup>21</sup> devices. Recent review papers focus on details on their basic operation principle, memory and computing related applications. <sup>5</sup> All types of resistive switches share a simple two-terminal MIM-structure where the resistance of the insulator can be tuned between at least two different resistance levels (a high resistive state, HRS, and a low resistive state, LRS). Many devices allow intermediate resistance levels (multilevel switching) or analogue switching, resulting in storing multiple bits in a single memory cell. A schematic presentation of filamentary switching ECM and VCM devices is shown in Figure 4. Redox reactions as nanoionic signature of the resistance transition have been widely accepted. <sup>22,23</sup>

Adapting memristive devices for different applications and controlling the functionalities are challenging but essential tasks of the current research in this field. In many cases, the function can be induced by using different pulse schemes or different amplitudes and/or magnitudes of the external stimuli. However, a more important but at the same time more challenging task is using an approach based on materials design. This approach requires a deep understanding of the relation among material properties, the physicochemical interactions and processes within the device, and the resulting charge dynamics and functionalities. Despite the apparent simplicity in structure and materials, memristive cells are complex nanoscale systems where mechanical, chemical, and electrochemical interactions are present, as shown in Figure 5.

The main electrochemical processes are redox reactions at the interfaces and ionic motion (diffusion or migration) within the switching film. However, chemical interactions at the interfaces and with the molecules from local environment often play important role in determining factors such as variability, state stability endurance, and retention. For example, it was recently found that the capping layer is significantly influencing the device performance, despite it is not directly participating into the switching process.<sup>24</sup> Moreover, not only the assembly of materials is important, but also their thicknesses should be adapted and coordinated. In macroscopic systems, electrolytes are

considered as an infinite source of ions and adding or removing some (e.g., due to reactions) is not changing the properties of the system. In nanoscale electrochemical cells, this is typically not the case. Adding or removing charges (ions and/or electrons) can have significant impact on the physicochemical properties and, thus, on the switching behavior and functionalities. Thus, the thicknesses of the different layers in one device should be carefully selected. In addition, extracting or adding ions, can change the kinetics from field accelerated to classical diffusion driven transport. <sup>25</sup>

Speaking on materials design, an essential factor is the purity of the used materials, and often impurities may unexpectedly play the role of doping. In many cases, the level of impurities is not considered where in the same time levels of ppm can significantly change the transport, switching kinetics and functionalities. Such impurities can be immobile, being part of the initial material, but they can be also introduced on a later stage due to incorporation of protons (for example introduced during preparation or incorporated from local environment) or ions from the electrochemically active electrodes. Impurities and doping are important considering not only the switching film but as well electrodes. It has been also demonstrated that introducing other components in the metallic films (alloying) can be essential for reaching optimal performance.

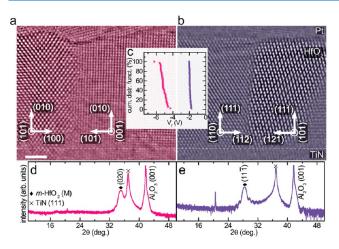

Specifically, the complex defect structure of oxide functional layers that leads to the formation of the conducting filament has been recently studied. While the important role of oxygen vacancies has been discussed extensively in the literature including quantization effects, 28-31 the interplay of (oxygen) point defects with twodimensional defects like grain and phase boundaries has been mostly neglected. In molecular beam epitaxy (MBE) grown HfO2 dielectric layers deposited onto TiN bottom electrodes, it is possible to enforce the growth of threading grain boundaries that all have an equivalent crystallographic orientation.<sup>32</sup> Using such model structures, the influence of grain boundaries could be directly studied. Surprisingly, different sets of grain boundaries lead to markedly different forming voltages,  $V_f$  Low-symmetry grain boundaries are connected to large  $V_f$ with a broad probability distribution, while high-symmetry grain boundaries show forming free behavior with a sharp distribution of values (Figure 6). It turns out that the symmetric grain boundary attracts to larger extent oxygen vacancies which, in turn, lead to a higher concentration of electronic states in the band gap of HfO2 close to the Fermi level. Therefore, this particular set of grain boundaries is an ideal precursor for the formation of a conductive filament.<sup>33</sup> The understanding and control of complex defects and their interaction is a key to manipulate conductive filament toward multiple resistive states. While HfO<sub>x</sub> is one of the mostly used materials in VCM, other materials

Figure 6. Cross-sectional high-angle annular dark-field (HAADF) scanning transmission electron microscopy (STEM) image of a metal—insulator—metal stack with (a) (010) and (b) (11 $\overline{1}$ ) textured HfO<sub>2</sub>. Scale bar is 2 nm. The TiN-HfO<sub>2</sub> interface is indicated by a dashed line. The X-ray diffraction (XRD) pattern reveals that a change in the growth temperature and rf-power for HfO<sub>2</sub> results in (d) (11 $\overline{1}$ ) (purple), and (e) (020) (pink) orientation. (c) Devices with (010) textured HfO<sub>2</sub> (pink) have an increased average forming voltage of  $\overline{V}_f = -5.3$  V compared to devices with (11 $\overline{1}$ ) HfO<sub>2</sub> having  $\overline{V}_f = -1.9$  V as shown by the cumulative distribution function measured from 50 30 × 30  $\mu$ m<sup>2</sup> devices. Reprinted with permission under a Creative Commons CC BY License from ref 33. Copyright 2022 John Wiley & Sons.

like  $Y_2O_3$  with a high amount of intrinsic oxygen vacancies might be even more suited to control the transition between a large number of resistive states. <sup>34,35</sup>

Two-dimensional (2D) layered materials have also been introduced as switching medium in memristors. <sup>36–39</sup> The best resistive switching performance for memory and neuromorphic applications has been obtained in multilayer hexagonal boron nitride (h-BN) produced using chemical vapor deposition (CVD). 40-42 The reasons are (i) h-BN is an insulator with a band gap ~6 eV, meaning that it can block current in HRS and reduce energy consumption; 40 and (ii) CVD provides the right amounts of native defects that enable stable RS. 43,44 A recent study reported crossbar arrays of small ( $<0.053 \mu m^2$ ) h-BN memristors with high endurance (>5  $\times$  10<sup>6</sup> cycles), and low energy consumption per state transition (~1.41 pJ).<sup>42</sup> It has been studied that the switching occurs by metal penetration from the electrodes 40,41 as in ECM. Native defects in CVD h-BN, as in VCM, also facilitate the formation of the filament (i.e., lower the energy-to-breakdown) and enable resistive switching. 41 The difference is that in CVD h-BN the native defects are surrounded by extremely stable 2D layered material.<sup>41</sup> This limits the number of atoms that are involved in the switching and avoids lateral propagation of the filament, which should have positive effects to reduce variability and increase endurance. <sup>44,45</sup> The fact that the resistive switching in CVD h-BN is oxygen-free, <sup>41</sup> should also prevent filament self-disruption, which should enhance the retention time. The problem of most studies in the field of 2D material-based memristors is that they report the performance of few (<5) large devices (>1  $\mu$ m<sup>2</sup>), while the community should be focusing on presenting data collected in multiple (>100) small devices (<0.1  $\mu$ m<sup>2</sup>), if possible arranged in a crossbar structure.46,47

Despite the impressive progress made in the field, materials design of memristive devices has not reached its full potential and fundamental studies on the relation between materials, processes, and functionalities are essential for the further progress in tuning and controlling memristive functionalities.

**2.2.** Optical Memory and Photonic Tensor Core Based on Phase Change Materials. Phase change materials (PCM) have long been employed as a storage medium for optical data storage such as compact disks since the 1980s due to their pronounced change in

dielectric function upon phase switching. Some families of PCM include chalcogenide glasses like GeSbTe and certain metal oxides like  $VO_2$ . The amorphous phase and crystalline phases of PCM exhibit longrange disorder and long-range order, respectively. To switch from the crystalline state to the amorphous state, a heat pulse is applied to PCM to elevate the temperature above the melting temperature, followed by a rapid quenching (cooling rate higher than  $10^9~{\rm K/s}$ ) to cool down the material. To crystallize PCM, a heat pulse with intermediate power is applied to heat up the material above the glass transition temperature, but not necessarily higher than the melting temperature. The prominent properties of PCM data storage include long data retention at room temperature (more than hundreds of years),  $^{48-50}$  low switching energy (hundreds of pico-Joule to few nano-Joule), fast switching dynamics at nanosecond scale, and many distinguishable stable intermediate states (tens of states).

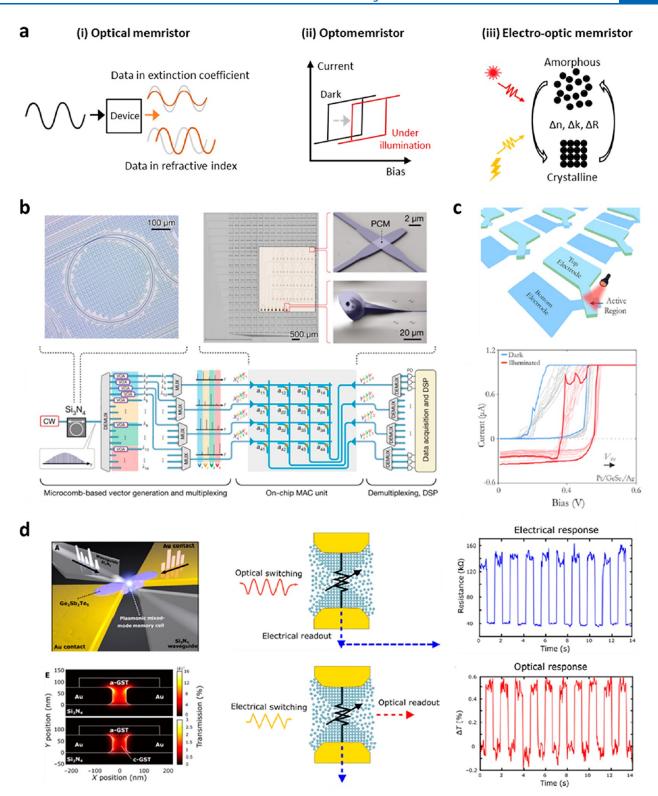

Microscale and nanoscale integrated optical memory has been a growing field in the past decade. As an emerging field, it is not surprising that this field creates several different names for different devices, depending on their properties and functionalities. Here, these emerging devices are categorized into three groups: optical memristor, optomemristor, and electro-optic memristor (Figure 7a). Optical memristors are optical devices that can store multilevel data in the nonvolatile physical states of materials similar to electrical memristors. But optical memristors read out data from the optical domain, requiring different physical states to have different optical properties. Optomemristors are essentially electrical memristors, whose switching dynamics and electrical response can be controlled optically. Electrooptic memristors are simultaneously optical and electrical data storage devices. This property is called "dual electrical-optical functionality", meaning electro-optic memristors can be programmed optically and readout electrically and vice versa.

For the PCM optical memristor, data are stored either in the absorption coefficient or the refractive index of PCM. In the first type, the amplitude of incoming light is modulated upon phase switching in conventional PCMs like Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) and AgInSbTe (AIST). In the second type, the phase of incoming light is modulated in low-loss PCMs like Sb<sub>2</sub>S<sub>3</sub><sup>51</sup> and Sb<sub>2</sub>Se<sub>3</sub>.<sup>52</sup> The change in absorption coefficient and refractive index of PCM upon phase switching can exceed unity, which is several orders higher than other mechanisms for nonvolatile optical memories. A simple PCM optical memristor can be constructed with thin film deposition of PCM on waveguide for interaction with the evanescent field of waveguide mode. 53,54 In the case of devices based on GST, the amorphous phase of GST has a lower extinction coefficient, resulting in weak attenuation of light. For the crystalline phase, a higher extinction coefficient leads to a strong attenuation of light. Therefore, by switching between amorphous and crystalline states, amplitude modulation can be achieved. Further, by varying the fraction of amorphous to crystalline phase, multiple intermediate transmission states or multiple memory levels can be achieved. 53,55 All-optical programming is adopted in PCM optical memristors; this effectively is a direct photonic analogue of electrical memristors, modulating transmission of light via absorption. The optical programming pulse is absorbed by the PCM thin film, resulting in heating of the thin film. By variation of the power and shape of such programming pulses, both amorphization and recrystallization can be achieved. Further by varying the power of programming pulses, multiple memory levels can be achieved. To date, a maximum of 5 bits in PCM optical memristor has been reported.<sup>55</sup> Using the all-optical programming approach to reconfigure integrated photonic circuits with PCM memory devices, inmemory matrix computation using photonic synapses and all-optical synaptic neural network have been demonstrated. 56-59 Besides the alloptical programming approach, there has been an increasing interest in the electrically controlled programming approach due to the rise in popularity of low-loss PCM for phase modulation. This has until recently been dominated by microheater-based systems. Unlike all optical approaches, microheater-based approaches are power-hungry due to large-area heating and efforts have been made to reduce the programming energy by optimizing microheater designs. 60-

Recently, the photonic tensor core for parallelized in-memory MVM is a significant advance in PCM photonics. <sup>63,64</sup> As shown in Figure 7b,

Figure 7. (a) Three categories of microscale and nanoscale integrated optical memory. (i) Optical memristor. (ii) Optomemristor. (iii) Electro-optic memristor. (b) A photonic tensor core using PCM optical memristors for parallelized in-memory matrix-vector multiplication. Wavelength division multiplexing is achieved by integrating a Si<sub>3</sub>N<sub>4</sub> microcomb. Reprinted with permission from ref 64. Copyright 2021 Springer Nature. (c) An optomemristor enabled by Pt/GeSe<sub>3</sub>/Ag stack. This device is essentially an electrical memristor with its hysteresis controlled by optical illumination. Reprinted with permission under a Creative Commons CC BY License from ref 65. Copyright 2022 Springer Nature. (d) An electro-optic memristor formed by integrating plasmonic nanogap with tapered dielectric waveguide. The electro-optic memristor features dual electrical-optical functionality, meaning the device can be programmed optically and read out electrically and vice versa. Reprinted with permission under a Creative Commons CC BY License from ref 66. Copyright 2023 American Association for the Advancement of Science.

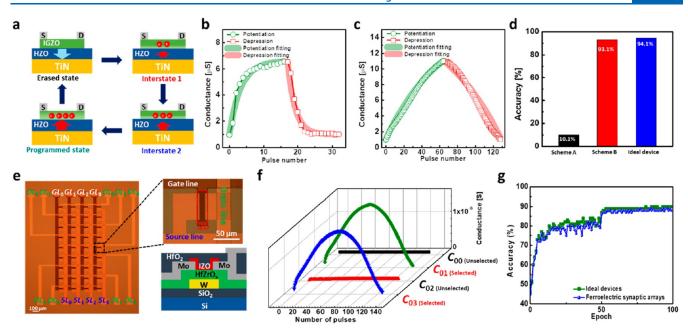

Figure 8. (a) Schematic illustration of conductance modulation mechanism in ferroelectric transistors. Reprinted with permission from ref 82. Copyright 2019 American Chemical Society. Conductance modulation characteristics of ferroelectric transistors using (b) identical and (c) incremental pulse schemes. (d) Classification accuracy of neural network based on the ferroelectric transistor and ideal synapses. Neural networks based on ferroelectric transistors showed higher classification accuracy when an incremental pulse scheme is used, compared to an identical pulse scheme. Reprinted with permission from ref 86. Copyright 2021 AIP Publishing LLC. (e) Optical image of ferroelectric synaptic transistor array (left). Optical image and schematic illustration of the ferroelectric transistor in the array (right). (f) Column-wise parallel weight update characteristics of the ferroelectric synaptic transistor array. The weight update was done simultaneously, but only the selected cells ( $C_{01}$  and  $C_{02}$ ) were kept in their original state. (g) Classification accuracy of neural networks based on ferroelectric transistor array and ideal synapse array. Reprinted with permission under a Creative Commons CC BY License from ref 91. Copyright 2022 American Association for the Advancement of Science.

by designing an all-optical integrated photonic circuit with spatially distributed PCM photonic memories and layout architecture analogous to electronic crossbar arrays, the photonic tensor core can perform parallel MVM using wavelength division multiplexing. The huge bandwidth provided by wavelength division multiplexing and fast photonic processing renders the photonic tensor core with ultrahigh computation speed (more than one trillion operations per second) and density (more than one trillion operations per mm<sup>2</sup>) for convolutional processing, which forms the backbone of modern artificial intelligence algorithms. An electro-optic version of photonic tensor core is also developed to reduce the complexity of programming PCM memories.<sup>6</sup> Other major advances in PCM photonics include optomemristor and electro-optic memristors, which link and synergize the optical and electrical properties of PCM. PCM optomemristor shows memristor functionalities that cannot be realized solely in the electrical domain but requires control from the optical domain. A PCM optomemristor formed by Pt/GeSe<sub>3</sub>/Ag stack<sup>65</sup> was recently reported with optoelectronic properties (Figure 7c). This device is essentially a redox type memristor, where a conductive channel is formed in the GeSe<sub>3</sub> between the two electrodes, but such resistive switching can be optically controlled. Optical illumination causes the shift of resistive switching voltage toward a smaller value. Hence, the device can be optically controlled to switch at a lower or higher voltage relative to its intrinsic switching voltage. Using this property presented in the Pt/ GeSe<sub>3</sub>/Ag optomemristor, i.e., resistive switching controlled by illumination, the emulation of multifactor neuromorphic computation is demonstrated as an example of reinforcement learning in hardware. Toward electro-optic memristors featuring dual electrical-optical functionality, meaning the device can be programmed optically and readout electrically and vice versa, a plasmonic nanogap enhanced PCM device has been demonstrated. 66,67 As shown in Figure 7d, a plasmonic nanogap is integrated with a tapered dielectric waveguide to achieve efficient dielectric waveguide to plasmonic mode conversion. The PCM sits at the center of the nanogap to bridge the two tapered electrodes and form a conductive path. Since PCMs are both electrically and optically active, this device can be switched and read out flexibly in both the electrical and optical domain, offering another dimension for on-chip addressing and control of PCM memories.

Moving forward to practical applications, the challenges of PCM optical memory devices include limited endurance due to phase segregation, long-term stability at elevated temperature, ultrafast programming, and integration with CMOS electronics. Phase segregation can be eliminated by using single-element PCM such as Te<sup>68</sup> or Sb.<sup>69–71</sup> However, the data retention time in Te or Sb -based optical memory should be improved to achieve nonvolatility. Long-term stability is limited by the typically low crystallization temperature of PCM, which can be enhanced by doping PCMs with high melting point elements such as Ge.<sup>72</sup> Achieving ultrafast programming speeds up to GHz and integration with CMOS electronics remain some of the most important daunting challenges in PCM material discovery.

2.3. Memristive Behavior of Ferroelectric Transistors and Arrays Based on Hafnia. Various types of materials such as perovskites, 2D materials, polymers, and fluorite oxides have been found to have ferroelectricity and studied for next-generation memory devices. 73-77 The memory effect of the ferroelectric materials is attributed to the switching of electric dipole alignments between an upward and downward direction, driven by electric field. Ferroelectric memories include ferroelectric random-access memory (FeRAM), ferroelectric tunnel junction (FTJ), and ferroelectric transistors. Similar to DRAM, FeRAM has a one transistor-one capacitor (1T-1C) structure and uses a ferroelectric capacitor to store charges, but the memory states determined by polarization switching of ferroelectric layer is nonvolatile. However, destructive readout process and large footprint are critical drawbacks of FeRAMs. In FTJs, ultrathin ferroelectric materials are sandwiched with two electrodes, which act as a tunneling barrier. Polarization switching induces resistive switching by changing the barrier height for tunneling. In ferroelectric transistors, the ferroelectric layer is used as a gate-insulating layer. 8 Polarization

Figure 9. (a) Operation of a nonvolatile ion-intercalation programmable resistor. Left: Device structure featuring ion reservoir that also serves as gate, an electrolyte and a channel material where the ions behave as dopants. Center: Device programming by ion insertion in (top) and extraction from (bottom) the channel. Right: Nonvolatility when gate is open; ions remain in channel. Reprinted with permission from ref 111. Copyright 2022 IEEE. (b) Schematic diagram of Pd/PSG/WO<sub>3</sub> nonvolatile protonic programmable resistor. (c) Top: False-color SEM micrograph of fabricated device. Bottom: TEM cross-section of fabricated device. (d) Modulation performance of a protonic device in response to a positive stream of 5 ns pulses followed by an identical negative stream. (e) Top: Conductance retention characteristics of protonic device during 100 s reads of the conductance state. Bottom: Endurance characterization of a protonic device displaying reproducible modulation over  $10^5$  pulses conducted over 30 h. Reprinted with permission from ref 110. Copyright 2022 American Association for the Advancement of Science. (f) Top: Channel current before, during, and after a 5 ns pulse applied to a protonic device clearly displaying impulse-like fast modulation characteristics. Bottom: Channel current under positive trapezoidal voltage pulse starting at  $t = 2 \mu s$  with  $1 \mu s$  rise time,  $1 \mu s$  hold time and  $1 \mu s$  fall time in air (red) and in forming gas under a low/high voltage pulse (blue/green). The experiment reveals the existence of transient displacement current, volatile field-effect current and nonvolatile proton intercalation current. Reprinted with permission from ref 111. Copyright 2022 IEEE.

charge in the ferroelectric layer modulates the channel conductivity, resulting in changing threshold voltage  $(V_t)$  of the transistor.

Recently, memristive devices using ferroelectricity and their array structure have been actively studied to achieve high-performance, high-density neural networks. <sup>79–82</sup> Using partial polarization characteristics of ferroelectric gate insulators, precise control of carriers inside the channel layer can be achieved, which can lead to conductance modulation in the channel layer. 82-86 Among diverse ferroelectric materials, hafnia-based ferroelectric materials have been widely investigated for neuromorphic applications due to their CMOS compatibility, fast switching speeds, and high scalability. 87-91 At the erased state (i.e., downward polarization), the electrons inside the channel are depleted, which leads to low channel conductance (Figure 8a). 79,82 When a programming pulse with increasing amplitude is applied to the gate, the direction of polarization gradually changes to an upward direction and electrons are accumulated at the interface between the ferroelectric layer and the channel layer. This gradual switching of polarization under incremental pulses results in a gradual increase in channel conductance. 82,86 Thus, voltage pulses with incremental pulse amplitude or width are usually used to achieve linear and symmetric conductance change in ferroelectric transistors. 82,92 With incremental pulse schemes, classification accuracy as high as 91% is expected for handwritten digits, which is similar to that of ideal synapses.<sup>82</sup> Although the incremental voltage scheme can result in highly linear and symmetric conductance modulation, the conductance

of the ferroelectric transistor should be determined prior to conductance modulation. Thus, incremental pulse schemes lead to longer training time and higher energy consumption than identical pulse schemes. However, when identical pulse schemes are used for ferroelectric transistors, abrupt conductance changes are reported (Figure 8b, c). Also, it was confirmed that the accuracy of the neural network is significantly degraded with identical pulse schemes compared to that with incremental pulse schemes (Figure 8d). Thus, it is a challenge to develop a ferroelectric transistor compatible with an identical pulse scheme or operation method, which can decrease the training time and energy consumption.

The array structure for ferroelectric synaptic transistors and its operation method, which can decrease the training time, was demonstrated by Kim et al. Synaptic transistor array was fabricated using a low-temperature (400 °C) process by integrating a ferroelectric thin film transistor with an oxide semiconductor channel,  $InZnO_x$ , and ferroelectric gate insulator,  $HfZrO_x$  (Figure 8e). In this work, the rowand column-wise parallel programming method, in which the ferroelectric transistor in the same row and column can be programmed simultaneously, was proposed to decrease the training time of ferroelectric transistor arrays. Using the optimized parallel programming method, the conductance of the selected cell can be selectively and linearly modulated (Figure 8f). Also, the conductance of unselected cells that share the same row and column with the selected cells has remained in their states without change. Based on the electrical

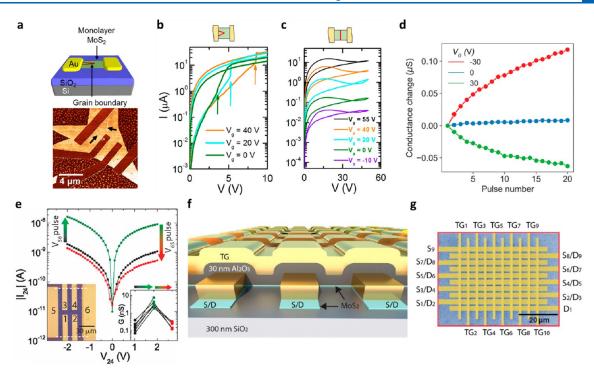

Figure 10. (a—c) Initial fundamental studies of memristive phenomena in 2D semiconducting  $MoS_2$ . (a) Schematic and atomic force microscopy image of a single-flake monolayer  $MoS_2$  device with an intersecting grain boundary. (b) Gate-tunable memristive response in an intersecting grain boundary monolayer  $MoS_2$  device. In this case, the set voltage between the high and low resistance states is controlled by the gate potential  $(V_g)$ . (c) Gate-tunable memristive response in a bisecting grain boundary monolayer  $MoS_2$  device. In this case, the current in both the high and low resistance states is modulated by the gate potential. Reprinted with permission from ref 132. Copyright 2015 Springer Nature. (d—g) Neuromorphic functionality in 2D memtransistors. (d) The unipolar synaptic response of 2D memtransistors can be tuned from potentiation to depression as a function of the gate bias  $(V_G)$ . Reprinted with permission from ref 136. Copyright 2021 American Chemical Society. (e) Multiterminal 2D memtransistors show heterosynaptic responses where the conductance state between two contacts (contacts 2 and 4) is modulated by voltage pulsing between two orthogonal contacts (contacts 5 and 6). Reprinted with permission from ref 133. Copyright 2018 Springer Nature. (f) Schematic and (g) false-colored scanning electron micrograph of a dual-gated 2D memtransistor crossbar array. Reprinted with permission from ref 137. Copyright 2020 John Wiley & Sons.

characteristics of the ferroelectric synaptic transistor and its array, the performance of convolutional neural networks with VGG-8 structure was demonstrated using the simulation method. 93 In a simulation based on the electrical characteristics of the ferroelectric synaptic transistor array, convolutional neural networks achieved an image accuracy of 90.3% on the complex image data set, CIFAR-10 (Figure 8g). This report experimentally demonstrated a neural network based on ferroelectric transistors and their convolution operations. Also, a rowand column-wise parallel programming method, which could decrease the training time, was experimentally proposed. At present, the demonstration of ferroelectric transistors for neuromorphic applications is usually done with small-density arrays or simulation methods without experimental validation of highly scaled, high-density neural networks based on ferroelectric transistors. 94-96 Further study needs to be done on the demonstration of a highly scaled transistor array for neuromorphic applications with considerations of array operations and their characteristics.

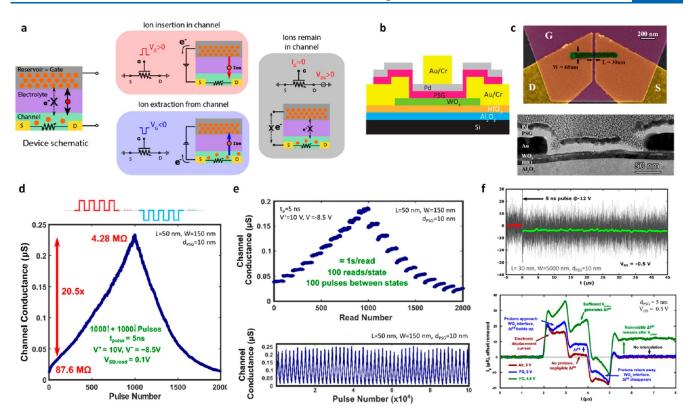

**2.4. Ion-Intercalation Programmable Resistors.** Recently, a device family of nonvolatile three-terminal programmable resistors for deep learning applications has emerged. This device class, often referred to as ECRAM (Electrochemical Random-Access Memory), ENODe (Electrochemical Neuromorphic Device), or EIS (Electrochemical Ionic Synapse), relies on controlled intercalation of dopant ions in a semiconductor channel <sup>98–111</sup> (Figure 9a). In essence, ions are shuttled back and forth between an ion reservoir (also performing the role of gate) and a channel, where the ions behave as dopants in response to the application of positive or negative voltage pulses to the reservoir with respect to the channel. In this way, the conductivity of the channel can be increased or decreased in a controlled fashion. During device programming, the ions are transferred through an electrolyte

that separates the gate from the channel while the corresponding electrons flow through the outside circuit. When the gate/reservoir is electrically left open, electrons cannot flow and the ions remain in place in the channel. Hence, the device exhibits nonvolatile characteristics.

Ion-intercalation programmable resistors have been demonstrated using Li<sup>+</sup>,  $9^{8-101}$  O<sup>2-,102-104</sup> and H<sup>+</sup>,  $10^{6-111}$  among other ions. The use of H<sup>+</sup> (protons) is particularly attractive because their small radius and light mass promise high speed and energy-efficient operation with minimum volume expansion and contraction. Also, unlike most of other ions, protons are CMOS compatible, a key consideration as deep learning accelerators will need to be constructed on a Si CMOS platform. This has implications for the nature of the ion, but also the choice of gate, channel and electrolyte materials, as well as the processing temperatures involved in device fabrication. Early protonbased device demonstrations were based on polymeric materials for the channel, reservoir and electrolyte. Organic materials are not CMOS compatible in that they cannot withstand the processing temperatures generally involved in Back-End-Of-the-Line (BEOL) CMOS fabrication. Later demonstrations used Pd as an inorganic reservoir/gate and a metal oxide (WO<sub>3</sub>) as an inorganic channel but still used polymeric Nafion as the electrolyte. 107 Proton-based devices have also been demonstrated using inorganic 2D electrolytes. 10

Recently, the use of phosphosilicate glass (PSG) as electrolyte in combination with a Pd reservoir/gate and a WO<sub>3</sub> channel has been demonstrated as the key innovation to resolve the critical limitation of protonic devices: the absence of a CMOS-compatible, solid-state material system. <sup>109–111</sup> PSG is the most suitable choice for this application. It is a well-known material in Si technology with straightforward BEOL integration capabilities; it is an excellent electrical insulator, and it also exhibits good proton conductivity at

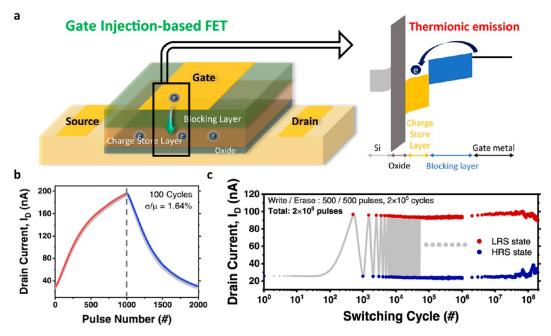

Figure 11. (a) Schematic and band diagram of GIFET. The charge is injected from or extracted to gate metal by thermionic emission. (b) Repeated LTP-LTD characteristics on a single GIFET device with 1000 potentiation - 1000 depression (5 V/-3.3 V, 500  $\mu$ s). (c) The endurance of GIFET over 2 × 10<sup>5</sup> switching cycles (2 × 10<sup>8</sup> pulses). Each switching cycle is composed of 500 write pulses with 5 V, 200  $\mu$ s and 500 erase pulses with -5 V, 200  $\mu$ s. Reprinted with permission under a Creative Commons CC BY License from ref 140. Copyright 2022 Springer Nature.

room temperature. <sup>112</sup> In fact, PSG has been used as a proton-exchange membrane in microfuel cells. <sup>113</sup> Micron-scale protonic resistors <sup>109</sup> and nanoscale active area devices <sup>110</sup> (Figure 9b, c) exhibit high operation speed (5 ns/pulse), high energy efficiency (~fJ/pulse), many (~1000) nonvolatile conductance states centered around 0.1  $\mu$ S and spanning a large dynamic range (10×), nearly linear and symmetric modulation for incremental and decremental conductance changes, good retention and high endurance (Figure 9d, e).

A detailed study of the dynamics of these devices has also been carried out by Onen et al. <sup>111</sup> They have revealed a device response that includes a transient field-effect-induced channel current that results from proton movement through the PSG during the gate voltage pulse. In effect, this device behaves as a MOSFET with a threshold voltage that shifts negative when the PSG is flooded with protons. In addition, when the magnitude of the gate voltage pulse exceeds a certain minimum, the expected nonvolatile proton intercalation induced channel current was observed. High-speed measurements reveal that in response to 5 ns gate voltage pulses, this nonvolatile conductance modulation occurs in an impulse-like fashion, without any extended equilibration period (Figure 9f).

The nonvolatile programmable protonic ion intercalation resistors described here display state-of-the-art combined material, processing, and performance properties of potential for analog deep learning applications. The operating gate voltage should be improved by engineering the PSG and Pd/PSG and PSG/WO<sub>3</sub> interfaces.

**2.5. Other Emerging Memristive Devices.** The development of memristive materials and devices including Spin-transfer Torque Magnetoresistive RAM (STT-MRAM), memtransistor, and gate-injection device can offer possibilities to improve memristive device performance and neuromorphic systems. And agnetic device has been studied for several decades, and various operation mechanisms have been reported. After predicting the Spin-transfer Torque (STT) effect without the external magnetic field by Slonczewski and Berger in 1996, STT-MRAM with magnetic tunneling junction (MTJ) has become an important memristive device in neuromorphic applications, exhibiting small device-to-device variation, fast switching speed, and excellent endurance. Provided the superior device properties of STT-MRAM, the low resistance of STT-MRAM can lead to large power consumption in a conventional crossbar array

for analogue multiply accumulate operations, which are essential operations for neuromorphic systems. To overcome this issue, Jung et al. demonstrated a 64  $\times$  64 crossbar array based on STT-MRAM cells with an architecture that includes the resistance of a field-effect transistor (FET), as every MTJ is accompanied by a FET switch.  $^{126}$  Additionally, a multistate STT-MRAM design also have been proposed for neuromorphic computing schemes as artificial synapses.  $^{127}$

The defining structural characteristic of a 2D material is its nanoscale thickness. For 2D semiconductors, this nanoscale thickness has multiple implications for electronic properties including quantum confinement effects that modulate band structure, reduced dielectric screening that results in enhanced electrostatic modulation by applied gate electric fields, and charge transport that is strongly affected by structural defects. 128 In the specific case of 2D transition metal dichalcogenides (e.g., MoS<sub>2</sub>), nanoscale thickness also implies reduced energy barriers for point defect motion, especially in polycrystalline materials where point defect motion is further enhanced along grain boundaries. 129,130 These properties of 2D transition metal dichalcogenides present opportunities for memristive materials and devices. For example, the low energy barrier for point defect motion in monolayer polycrystalline MoS<sub>2</sub> implies that the spatial doping profile and thus the charge transport properties can be reconfigured by the application of modest lateral electric fields. In this manner, memristive phenomena have been observed in monolayer polycrystalline MoS<sub>2</sub> devices. 132 By concurrently applying a vertical electric field across a gate dielectric, the memristive response can be electrostatically modulated with the details depending on the grain boundary orientation in the device channel. 132 (Figure 10a-c) Since these devices combine the nonvolatile two-terminal response of a memristor with the volatile gate modulation of a transistor, they have been dubbed memtransistors. 1

Although early work focused on devices with a small number of grain boundaries and thus were sensitive to stochastic variations in grain boundary orientation from device to device, <sup>132</sup> later work recognized that the incorporation of several grain boundaries per device leads to statistical averaging at the single device level, which substantially improves memtransistor yield and wafer-scale uniformity. <sup>133</sup> Efforts to control polycrystalline grain structure and point defect concentration <sup>134</sup>, <sup>135</sup> have also proven successful at improving memtransistor device metrics (e.g., smaller device dimensions, lower voltage

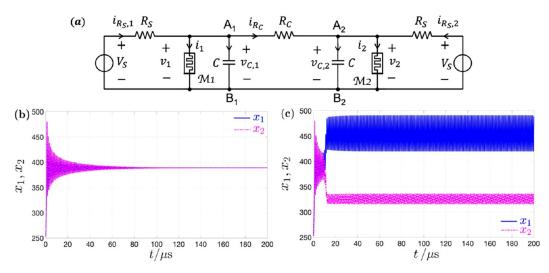

Figure 12. (a) The simplest ever-reported bioinspired circuit, 148 which reproduces the counterintuitive diffusion-driven transition from quiescence to sustained oscillatory behavior, observed by Smale in an eight-order reaction-diffusion system from cellular biology, 149 through half the number of dynamical states, encoded in two capacitors and two locally active NaMLab memristors, 146 on the proviso that the two identical memristive Pearson-Anson cells are preliminarily poised on some common Edge of Chaos operating point before the diffusion path, enabling their diffusive interaction, is activated. The four degrees of freedom of the proposed fourth-order RD-MCNN are encoded in the memristors' states  $x_1$  and  $x_2$ , and in the capacitors' voltages  $v_1$  and  $v_2$  (refer to ref 148 for details). (b, c) Diffusion-induced transition of the bioinspired array of (a) from silence to persistent oscillatory mode (all details on memristor model and cell parameters, chosen through a systematic methodology from Local Activity and Edge of Chaos Theory, are reported in ref 148). (b) Progressive approach of the states  $x_1$  and  $x_2$ of memristors M<sub>1</sub> and M<sub>2</sub> toward the same quiescent steady state, which they would independently attain, irrespective of the initial condition, in case they were let evolve in the respective uncoupled cell. Here  $R_C = 50 \Omega$ , while the initial condition for the cell I = 1(2) is arbitrarily set to  $(x_i(0), v_{C,i}(0)) = (253.15, \xi \cdot 0.1 \text{ mV})$ . (c) Formation of one of the two admissible dynamic patterns, across the homogeneous cellular medium, as determined by the choice of the initial conditions for the four RD-MCNN states, which are set as specified earlier for the simulation result in (b). Even though here  $R_C = 25 \Omega$ , reducing the coupling resistance progressively from positive infinity, first the homogeneous solution of the array loses stability, allowing the two-cell array to enter a bistability regime with static pattern formation, out of a pitchfork supercritical bifurcation, for  $R_C = R_{C,P} = 49.75 \Omega$ , and later on, due to a Hopf supercritical bifurcation, the two admissible locally stable inhomogeneous static solutions of the RD-MCNN become unstable, while concurrently two infinitesimal almost-sinusoidal locally stable oscillations, increasing in amplitude as the coupling strength is further increased, are found to develop across them, for  $R_C = R_{CH} = 28.1 \ \Omega_c^{1.53}$  Reprinted with permission from ref 148. Copyright 2022 IEEE.

operation, and reduced power consumption) in addition to enabling neuromorphic functionality such as gate-tunable potentiation and depression (Figure 10d)<sup>136</sup> and heterosynaptic responses in multi-terminal memtransistors <sup>133</sup> (Figure 10e). The 2D memtransistor channel can also be gated from above and below, which enables dual-gate memtransistors (Figure 10f) that have been incorporated into crossbar array architectures with minimal crosstalk, disturbance, or sneak currents<sup>137</sup> (Figure 10g). Since 2D memtransistors are still in their infancy, many research opportunities remain at the materials level (e.g., exploring different 2D semiconductors, dopants, contacts, and gate dielectrics) that are likely to further diversify the device and circuit possibilities both in conventional neuromorphic computing<sup>138</sup> and emerging biorealistic systems. <sup>139</sup>

A gate injection-based filed-effect transistor (GIFET) has been demonstrated by employing thermionic emission with superior synaptic characteristics (Figure 11a). 140 To achieve linearity, the authors suggest an operation method to program and erase the charges in the stored layer by thermionic emission from the gate metal (Figure 11b). The barrier height between the charge store layer (CSL,  $WO_x$ ) and blocking layer (a-Si:H) should be low to guarantee sufficient current density for a high on/off ratio and to hold electrons. The amount of charge stored in the CSL layer changes the Si channel's depletion region by field-effect, and this is the major mechanism to control synapse weight in GIFET. The LTP-LTD characteristic of the GIFET has high linearity with low asymmetric ratio, and the device also achieves robust endurance ( $\geq 2 \times 10^8$  pulses) with consecutive potentiation and depression pulses and retention properties with a data loss of 5.45% (13.6 nS) (Figure 11c). GIFET has a similar structure to the currently commercialized CTF (charge trap flash), but the engineering of the gate stack and the changing of the charge injectionextraction mechanism allow GIFET to be a promising memristive device. Based on thermionic emission mechanism, GIFET achieves excellent synaptic properties such as number of conductance states, on/off ratio, spatiotemporal variation, linearity, retention, and endurance. Moreover, all of the processes and materials for GIFET fabrication were CMOS compatible, which means it could be used as a near-future neuromorphic device. Further development to reduce programming voltage, integrate into a large array, and scale down will provide opportunities for the use of GIFET in neuromorphic hardware.

#### 3. MEMRISTOR THEORY

3.1. Edge of Chaos-Induced Bifurcations in Biomimetic Locally Active Circuits. Local Activity<sup>141</sup> refers to the capability of a physical system to act as a source of local energy upon suitable polarization. Importantly, Local Activity is a fundamental prerequisite for a system to display complex dynamical behaviors, 142 in certain occasions. Edge of Chaos 141 denotes a particularly attractive condition, in which a physical system is both locally active and asymptotically stable at some operating point. It is when a system is poised on the Edge of Chaos that emergent phenomena may appear across its physical medium out of some bifurcation.<sup>143</sup> Recurring to the universal Theory of Local Activity and Edge of Chaos is necessary to explain the mechanisms behind the appearance of complex phenomena in any physical system, which has the possibility to exchange energy with the respective environment. 144 The recent availability of memristor nanoscale physical realizations, 145,146 blessed with the capability to feature a Negative Differential

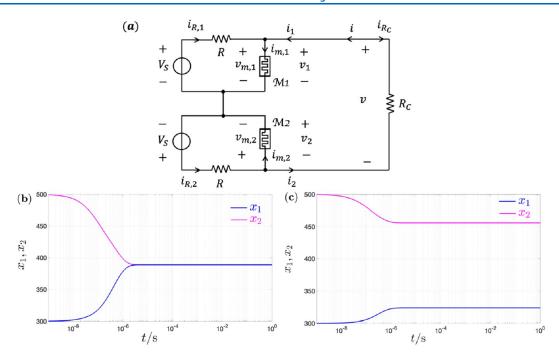

Figure 13. (a) The simplest ever-proposed reaction-diffusion system,  $^{156}$  which captures the same unexpected dissipation-induced static pattern formation, appearing, together with the destabilization of the homogeneous solution, in Turing-based models,  $^{155}$  through half the number of dynamical states, encoded in two niobium oxide-based threshold switches from NaMLab,  $^{146}$  providing its two identical memristive cells are preliminarily poised on some common locally active and asymptotically stable operating point, before the inclusion of a linear resistor of resistance  $R_C$  between the memristors' positive terminals turns the diffusion process on. (b, c) Symmetry-breaking effects in the bioinspired two-cell array of (a) (all details on memristor model and cell parameters, chosen through a systematic methodology from Local Activity and Edge of Chaos Theory, are reported in ref 156). (b) Convergence of the states  $x_1$  and  $x_2$  of memristors  $M_1$  and  $M_2$  toward the same asymptotic level, which they would independently approach, irrespective of the initial condition, if they were let evolve in the respective uncoupled cell. Here  $R_C = 100 \Omega$ , while the initial condition for the memristor  $M_1$  ( $M_2$ ) is arbitrarily set to  $x_1$ (0) = 300 ( $x_1$ (0) = 500). (c) Progressive formation across the homogeneous cellular medium of one of the two admissible Turing patterns, as dictated by the choice of the initial conditions for the two RD-MCNN states, which are set as specified earlier for the simulation result in (b). While here  $R_C = 25 \Omega$ , reducing the coupling resistance progressively from positive infinity, the homogeneous solution of the two-cell array actually loses stability, and static pattern formation first occurs, due to a supercritical pitchfork bifurcation, for  $R_C = R_{C,P} = 49.75 \Omega^{156}$  (see ref 157 for insights on static pattern formation in large RD-MCNN arrays). Reprinted with permission from ref 156. Copyright 2022 IEEE.

Resistance (NDR), <sup>147</sup> which is a signature for Local Activity, enables the design of circuits, which, once some of their constitutive units are poised on the Edge of Chaos, may reproduce complex bifurcation phenomena, occurring in biological systems, while utilizing a lower number of degrees of freedom than their original counterparts. Two major works provide proof for this claim.

In particular, Ascoli et al. 148 presented the simplest everreported bioinspired physical system, which reproduces the same counterintuitive phenomenon, reported by the American luminary Stephen Smale in 1974, 149 when, while investigating a model from cellular biology, he witnessed two identical fourthorder reaction cells, "mathematically dead" on their own, pulsing together indefinitely, upon diffusive coupling. The proposed bioinspired reaction-diffusion network, consisting of two identical and resistively coupled second-order memristive Pearson-Anson cells, features half the number of states than the corresponding biological system (the mathematical model in ref 150 also reproduces the Smale Paradox from ref 149 through a lower number of degrees of freedom, specifically 6, than the biological counterpart, but it requires two additional state variables as compared to the proposed two-cell array). As shown in Figure 12a, the neural network contains only 9 circuit elements, specifically 2 batteries, 3 linear resistors, 2 linear capacitors, and 2 volatile memristors, manufactured with

niobium oxide at the facilities of NaMLab (see ref 146 for details on the physical stack of each of the resistance switching memories, which are referred to as NaMLab memristors, in the remainder of this chapter). Employing powerful tools from the theory of Local Activity and applying methods from Nonlinear Dynamics to an accurate model of the memristor cellular unit, a comprehensive picture for its local and global behavior was drawn. This study, providing a systematic technique to choose the design parameters of the two-cell array, so as to allow diffusion-driven instabilities to appear therein, further enabled to identify the true origin for Smale's paradoxical observations: the appearance of symmetry-breaking effects, accompanied by the steady-state development of sustained oscillations, i.e. dynamic patterns, across the homogeneous cellular medium (refer to Figure 12b, c) is in fact possible if and only if the two identical reaction cells of the medium are preliminarily poised on a common Edge of Chaos (i.e., locally active and asymptotically stable) operating point, before the insertion of a dissipative path, joining the top terminals of their capacitors, let them interact diffusively. More specifically, upon a progressive decrease in the coupling resistance—refer to the circuit implementation of Figure 12a—the Reaction-Diffusion Memristor Cellular Nonlinear Network (RD-MCNN) first undergoes a supercritical pitchfork bifurcation, 151 which signals the destabilization of the homogeneous solution, with the simultaneous emergence of

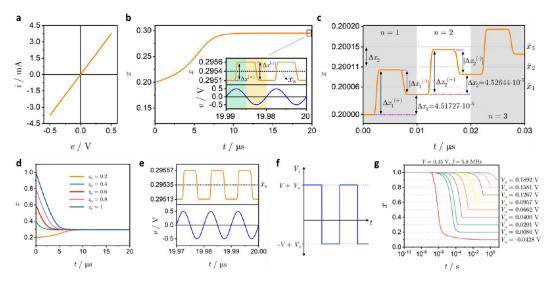

Figure 14. (a-c) Response of the  $TaO_x$ -based memristor from HP Laboratories in the high frequency limit. (a) Steady-state i-v plot of the  $TaO_x$ -based memristor model,  $^{160}$  under an AC voltage input of the form  $v=(0.5\ V)\sin\left(2\pi(100\ \text{MHz})t\right)$ . (b) Time-waveform of the device state variable x, preliminarily initialized at  $0.2\ (x_0=0.2)$ , responding to the same periodic voltage input. The inset provides a detailed view of the x vs t response over the last two input cycles of the simulated time-response. (c) Zoomed-in view of the x vs t response in (b) over the first three input cycles. Reprinted with permission from ref 158. Copyright 2022 IEEE. (d, e) Fading memory in the  $TaO_x$ -based memristor model in the high frequency limit. (d) The time-waveforms of the state variable x, for the initial conditions defined in the set  $x_0 \in \{0.2, 0.4, 0.6, 0.8, 1\}$ . Each of the depicted time-responses was induced by a zero-mean sinusoidal voltage input with amplitude  $\hat{v}=0.5\ V$  and frequency  $f=100\ MHz$ . At some finite time, all x vs t responses converge to the same steady-state oscillation, as illustrated in panel (e). (f, g)  $TaO_x$  memristor state tuning with high-frequency bipolar square-wave periodic voltage input with amplitude  $\hat{v}=V=0.45\ V$  and frequency  $f=5.8\ MHz$ , for the set of DC offset values  $V_0$  listed in the figure legend. Each  $V_0$  value was calculated by solving eq 5 with respect to  $\overline{x}_s$ , for  $\overline{x}_s \in \{0.1, 0.2, 0.3, 0.4, 0.5, 0.6, 0.7, 0.8, 0.9\}$ . The above-mentioned frequency was chosen such so as to induce an infinitesimally small periodic oscillation in the state x about  $\overline{x}_s$  in each of the simulated x vs t responses. A mathematical method for determining the frequency value that characterizes an input as a high-frequency periodic signal, based on the definition provided toward the beginning of this section, can be found in ref 158. Reprinted with permission from ref 158. Copyright 2022 IEEE.

either of two possible locally stable static inhomogeneous solutions, depending upon the initial condition, and then a supercritical Hopf bifurcation, <sup>152</sup> which endows the proposed bioinspired cellular array with the capability to support either of two locally stable dynamic inhomogeneous solutions, as established by the starting conditions for the cells' states, at the expenses of the static Turing patterns, which concurrently lose stability (consult ref 153 for more details).

In his seminal paper<sup>154</sup> Alan Turing, the Father of Artificial Intelligence, devised the model of a linear dynamical system, consisting of two identical diffusively coupled second-order reaction cells, which is subject to dissipation-driven instabilities. Due to the lack of a nonlinear saturation mechanism, the destabilization of the homogeneous solution of the array resulted here in the asymptotic divergence of its four state variables. Including a nonlinear term in a second-order Turinglike reaction cell (see ref 155, for example), the diffusion-driven symmetry-breaking phenomenon in the resulting fourth-order dynamical system may lead to the steady-state appearance of static inhomogeneous solutions. Ascoli et al. presented the simplest ever-reported two-cell neural network, 156 which, leveraging the NDR of the NaMLab memristor, is capable to support dissipation-induced static pattern formation through half the number of states than Turing-like reaction-diffusion arrays. As shown in Figure 13a, the proposed neural network is composed of just 7 one-ports, specifically 2 DC voltage sources, 3 linear resistors, and 2 niobium oxide-based volatile memristors from NaMLab. 146 In this work, they showed that complexity may emerge in a physical circuit, hosting no other dynamic

component besides the 2 locally active memristors. As reported in ref 156, an in-depth circuit- and system-theoretic analysis allowed Ascoli et al. to gain a thorough understanding of the local and global dynamics of the bioinspired reaction-diffusion network of Figure 13a, to prove that the preliminary polarization of each of its two identical constitutive units, when isolated one from the other, on some common Edge of Chaos operating point is the *conditio sine qua non* for the destabilization of the homogeneous solution of the array, later on, when a diffusion process establishes their interaction, and to enable the identification of the local supercritical pitchfork bifurcation, which spawns the birth of two locally stable inhomogeneous static solutions across the respective cellular medium under a sufficiently strong coupling condition (see Figure 13b, c).

All in all, the origin for the diffusion-induced emergent phenomena, appearing in each of the bioinspired RD-MCNNs, respectively presented in ref 148 and ref 156, is the preliminary polarization of their uncoupled reaction cells on the Edge of Chaos operating regime. Importantly, the NDR of the NaMLab memristor plays a fundamental role in biasing these cells on the Edge of Chaos. Moreover, the two studies revealed the potential of memristors with NDR to enable the reproduction of high-order dynamic phenomena in biology through lower-order electrical circuits.

# **3.2.** High-Frequency AC Response of ReRAM Cells. Depending on its switching sensitivity to input level and polarity, as well as its memory state(s), a highly nonlinear dynamical process determines the input-induced response of a real-world nonvolatile memristor. The recent research works in ref 158 and

ref 159, demonstrated how a system- and circuit-theoretic analysis of a nonlinear system, such as the memristor, enables to draw a comprehensive picture for its response to input/initial condition combinations of interest to the application at hand. In particular, the mechanisms underlying the resistance switching phenomenon that occur in a  ${\rm TaO}_x$ -based nanodevice, manufactured and modeled in Hewlett-Packard (HP) Laboratories, when stimulated with high-frequency AC periodic inputs, were elucidated on the basis of deep circuit-theoretic study. But what does a high frequency periodic input mean in terms of the memristor response? Quoting the definition provided in ref 158: "A high-frequency periodic input induces a solution waveform of the device state, which, after some finite time, becomes periodic with such a small peak-to-peak amplitude that the resulting device current—voltage locus exhibits no apparent hysteresis."

Figure 14a illustrates a seemingly nonhysteretic steady-state current—voltage locus of the  ${\rm TaO}_x$  memristor, induced by a high-frequency zero-mean sinusoidal voltage input (refer to the figure caption for further details). This device is a typical example of a first-order voltage controlled extended memristor, <sup>161</sup> whose high-level differential algebraic equation (DAE) set model reads as

$$i = G(x, v)v \tag{1}$$

$$\dot{x} = g(x, \nu) \tag{2}$$

where i denotes the current flowing through the memristor, v is the voltage across the memristor terminals, and x stands for the device only state variable, which physically represents the fraction of the oxide film, which is most conductive, due to a higher distribution of oxygen vacancies within its medium. As a result, the state x of the TaO<sub>x</sub> memristor, discussed in this section, may only assume values from the closed set [0, 1]. The functions  $G(\cdot)$  and  $g(\cdot)$  are the memristor memductance and state evolution function, respectively. Further details regarding the physical processes underlying the operation of the TaO<sub>x</sub> memristor under study, as well as the specific functional forms of eqs 1 and 2, assumed by its simulation model, can be found in ref 159. Notably, the vast majority of the real-world resistive switches reported to date can be modeled by following the mathematical formulation of extended memristors, as reported in eqs 1–2. Figure 14b plots the time-waveform of the  $TaO_x$ memristor state, x, for the same simulation settings as the ones employed in Figure 14a. The inset in Figure 14b zooms in on the last three periods of the illustrated x vs t response. Interestingly, at steady-state, x oscillates periodically with a miniscule amplitude about a mean value  $\overline{x}_s$ , i.e., at steady state,  $x(t) \approx \overline{x}_s$ (see the dotted horizontal line in the inset in Figure 14b). Figure 14c visualizes, in detail, the time-response of x over the three first cycles of the periodic input in Figure 14b, that is, for  $n \in \{1, 2, 1\}$ 3}, where *n* represents the input cycle number.  $\Delta x_n$ ,  $\Delta x_n^{(+)}$ , and  $\Delta x_n^{(-)}$ , correspond to the net change, increase, and decrease of x over the *n*-th input cycle, respectively. The dotted horizontal lines mark the running mean value  $\overline{x}_n$  of state variable x over each of the three first input cycles. It can be observed that the memristor state experiences an insignificant net change  $\Delta x_n$  over the course of each cycle *n* of a high-frequency excitation signal during the transient phase of its oscillation. According to the mathematical analyses introduced in ref 158 and ref 159, which were supported by the afore-described behavioral observations, the value of  $\overline{x}$  over each input cycle of a purely-AC periodic highfrequency voltage stimulus v(t), characterized by a very small

period T, can be related to the value of  $\Delta x$  over the same cycle through the following analytical equation:

$$\Delta x = \underbrace{\int_{0}^{T/2} g^{(+)}(\bar{x}, \nu(t)) dt}_{\Delta x^{(+)}} + \underbrace{\int_{T/2}^{T} g^{(-)}(\bar{x}, \nu(t)) dt}_{\Delta x^{(-)}}$$

(3)

The functions  $g^{(+)}(\cdot)$  and  $g^{(-)}(\cdot)$  ( $g^{(+)}(\cdot) \neq g^{(-)}(\cdot)$ ) are sign-invariant functions with opposite signs, modeling the device switching kinetics in the positive and negative stimulation cases, respectively. The moment at which transients decay to zero, the time-waveform of x becomes periodic, oscillating about  $\overline{x}_s$  with a negligible peak-to-peak amplitude (see the inset in Figure 14b). Thus,  $\Delta x = 0$  and eq 3 are simplified to the following analytical expression:

$$\underbrace{\int_{0}^{T/2} g^{(+)}(\overline{x}_{s}, \nu(t)) dt}_{\Delta x^{(+)}} + \underbrace{\int_{T/2}^{T} g^{(-)}(\overline{x}_{s}, \nu(t)) dt}_{\Delta x^{(-)}} = 0$$

(4)

The above equation allows calculation of the mean value  $\overline{x}_s$  of the steady-state periodic oscillation in the memristor state x, for a predefined high-frequency periodic voltage input v(t). Importantly, eq 4 describes the condition for the emergence of the fading memory phenomenon in memristors, 162-164 based on which the steady-state time-response of the state variable x(t), depends on the characteristics of the voltage input v(t), but not on the initial memristor state  $x_0$  (see Figure 14d, e). Through eq 4, the theoretical investigation performed in ref 158 and ref 159 provided a mathematical proof for the fading memory phenomenon in resistive switches that exhibit asymmetric switching kinetics with respect to the input polarity. The predictive power of eqs 3 and 4 was validated through a series of simulation experiments, utilizing periodic inputs with squarewave, sinusoidal, and triangle shapes. As a matter of fact, focusing in the case where the input corresponds to a highfrequency bipolar square-wave AC input, eq 4 may be simplified to a closed-form analytical formula that reads as

$$g^{(+)}(\overline{x}_s, V + V_0) + g^{(-)}(\overline{x}_s, -V + V_0) = 0$$

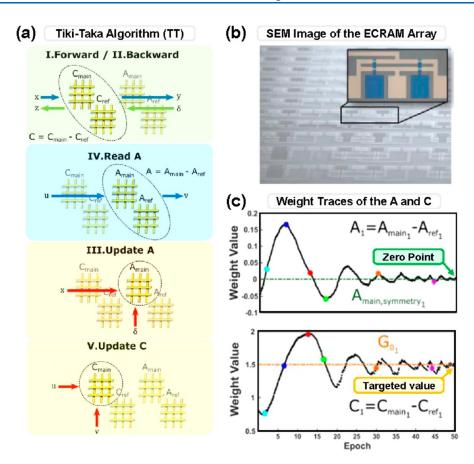

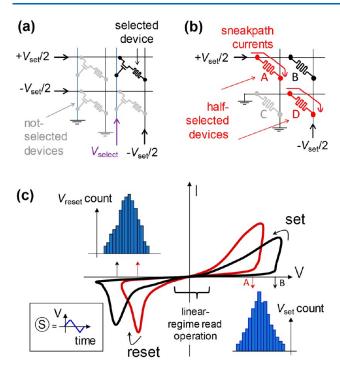

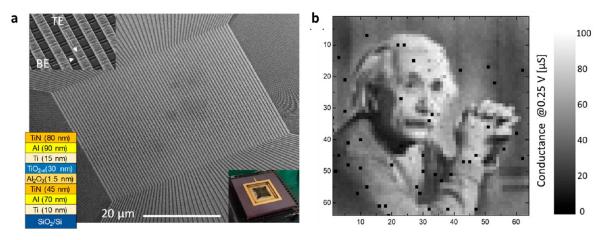

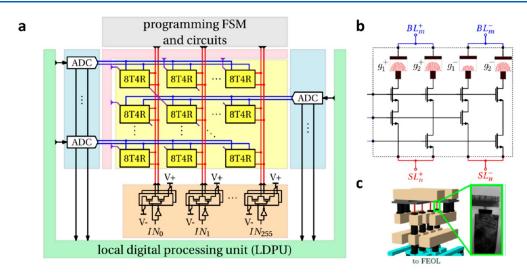

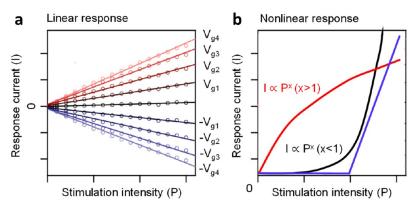

(5)