Doctoral Dissertation Doctoral Program in Electronics Engineering (35<sup>th</sup>cycle)

# Exploration of Beyond von Neumann Computing to solve the Memory-Wall issue

By

Andrea Coluccio

\*\*\*\*\*

#### Supervisor(s):

Prof. M. Graziano, Supervisor

### **Doctoral Examination Committee:**

Prof. Alberto Bosio, Full Professor, INL – Ecole Centrale de Lyon, Lyon, France Prof. Giovanni Finocchio, Associate Professor, Università degli studi di Messina, Dipartimento di Scienze matematiche e informatiche, scienze fisiche e scienze della terra, Italy

> Politecnico di Torino 2023

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Andrea Coluccio 2023

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). *I would like to dedicate this thesis to all the people who have been with me on this journey, supporting me and giving me the motivation to face the difficulties.*

### Abstract

The impressive growth in complexity of transistor technology has been the driving force behind modern electronics. Many applications (e.g., Neural Networks), which have become increasingly popular over the years, require processing enormous datasets quickly, placing stringent requirements on the hardware. Many computer architectures employed today are mainly based on a Central Processing Unit (CPU) and memories: the CPU executes the instructions composing programs, takes data from memory, and, once the processing is over, stores back the outcomes in the memory. As a result, these CPU-Memory structures, known as von Neumann architectures, require frequent data exchanges, wasting time and power. In addition, CPU and memory have not followed the same trend, resulting in an increasingly wider performance gap that requires the CPU to wait for memory constantly. This problem, known as Memory-Wall, is the most significant bottleneck preventing modern systems from keeping up with the performance demands of the latest applications. Therefore, a complete redefinition of the computing paradigms is required to overcome the limitations of von Neumann structures. A possibility lies in Beyond von Neumann Computing (BvNC), where part of the computational elements is moved close or even inside the memory, aiming to reduce the data traffic and execute tasks in parallel, achieving energy and time savings. However, developing new computing methods often requires a comprehensive rethinking of the design paradigm: for this reason, researchers have developed specialized software and CADs to assist designers with new computing paradigms or technologies. These tools generally specialize in one or more types of BvNCs and state-of-the-art architectural templates and focus either on simulations, performance estimations, or both. This thesis work presents a tool known as Design Explorer for In-Memory Architectures (DExIMA). Differently from existing tools, the idea is to define the architecture with high flexibility, going through the whole design flow up to automatic simulation, performance estimation, and comparison with von Neumann architectures. DExIMA maintains

architectural-level descriptions, so estimations can be done on any technology if implemented inside the tool. The framework allows the designer to develop BvNC architectures in a simple and guided manner by providing a schematic editor, supported implementation of algorithms and control units, Register Transfer Level (RTL) simulation, circuit performance estimation with DExIMA-Backend (an ad-hoc tool implemented in C++), and comparisons with von Neumann architectures using the Gem5 and Cacti by HP tools. At the end of the design flow, DExIMA will give an indication of the performance obtained in the BvNC case to understand how effective this type of solution is compared to a classical implementation. DExIMA also provides the architecture's RTL code that can be synthesized with classical EDA tools. Each step is guided by DExIMA, equipped with a PyQT5-based Graphical User Interface that implements all the previous routines. On the user side, the effort is significantly reduced and consists of defining the algorithm and the architecture. Different benchmarks are proposed that confirm the effectiveness of BvNC and show how, with DExIMA, the user has the possibility to control every step of the design with simplicity, considerably speeding up the whole procedure. The contributions of this work include a study of the state-of-the-art on BvNC proposals, an overview of existing EDA tools applied to BvNC, proposals of standalone BvNC architectures with demonstrated effectiveness, implementation of the DExIMA tool capable of modeling BvNC structures and estimating performance, validation of DExIMA compared to commercial EDA tools, and evaluation of the tool's versatility through the implementation of various benchmarks and analysis of their impact on von Neumann architectures.

## Contents

| List of Figures                 | xi    |

|---------------------------------|-------|

| List of Tables                  | xviii |

| I Background and previous works | 1     |

| 1 | Intr | oductio | n                                         | 4  |

|---|------|---------|-------------------------------------------|----|

|   | 1.1  | State-o | of-the-art                                | 5  |

|   |      | 1.1.1   | Beyond von Neumann concept                | 7  |

|   |      | 1.1.2   | BvNC application example: neural networks | 15 |

|   | 1.2  | Electro | onic Design Automation applied to BvNC    | 20 |

|   |      | 1.2.1   | Overview of the standard tools            | 20 |

|   |      | 1.2.2   | Tools for BvNC                            | 21 |

|   | 1.3  | Promo   | ting BvNC: results and discussions        | 23 |

|   | 1.4  | Conclu  | usions                                    | 29 |

| • | р    |         |                                           | 20 |

| 2 | Prev | lous wo | orks and architectural models             | 30 |

|   | 2.1  | Genera  | al-Purpose and Application Specific       | 30 |

|   |      | 2.1.1   | Application Specific implementations      | 31 |

|   |      | 2.1.2   | General Purpose approach                  | 50 |

|   | 2.2  | Conclu  | usions                                    | 67 |

| II | DI   | ExIMA tool for LiM design exploration     | 69  |

|----|------|-------------------------------------------|-----|

| 3  | Over | view of DExIMA software                   | 71  |

|    | 3.1  | DExIMA architectural reference structure  | 72  |

|    |      | 3.1.1 Control part and design templates   | 74  |

|    | 3.2  | DExIMA-GUI: Graphical User Interface      | 77  |

|    | 3.3  | LiM design phases                         | 80  |

|    |      | 3.3.1 Near-Memory design phase            | 82  |

|    | 3.4  | Conclusions                               | 84  |

| 4  | LiM  | design flow with DExIMA                   | 85  |

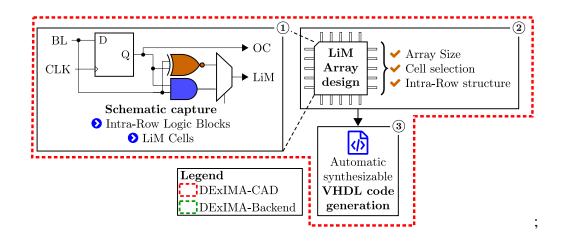

|    | 4.1  | Definition of the LiM template            | 87  |

|    | 4.2  | Definition of the LiM Cell                | 87  |

|    | 4.3  | Definition of the IRL                     | 87  |

|    | 4.4  | LiM array definition                      | 87  |

|    | 4.5  | Definition of the uRAM content            | 88  |

|    | 4.6  | Clock and default toggle rate definitions | 89  |

|    | 4.7  | Simulation                                | 90  |

|    | 4.8  | Performance estimation                    | 90  |

|    | 4.9  | Visualization of the results              | 95  |

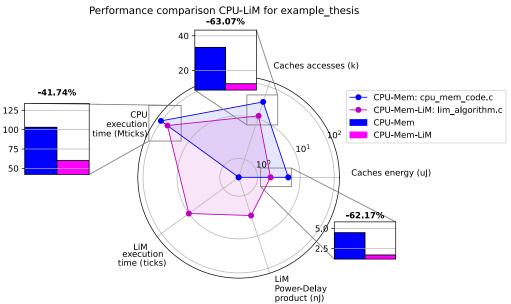

|    | 4.10 | Comparison CPU-Mem and CPU-Mem-LiM        | 97  |

|    | 4.11 | Conclusions                               | 101 |

| 5  | Fron | t-end code description: DExIMA-GUI        | 102 |

|    | 5.1  | MainWindowItems                           | 103 |

|    |      | 5.1.1 Graphical elements                  | 103 |

|    |      | 5.1.2 Functions and routines              | 111 |

|    | 5.2  | CONNECTBlocks                             | 113 |

vii

|   | 5.3  | Interco | nnections                                          | 14  |

|---|------|---------|----------------------------------------------------|-----|

|   | 5.4  | LiMTE   | EMPLATES                                           | 16  |

|   | 5.5  | MEMO    | DRYARRAYHandlers                                   | 16  |

|   | 5.6  | PERFO   | DRMANCE                                            | 17  |

|   | 5.7  | SCENI   | EElements                                          | 18  |

|   | 5.8  | SIMC    | ıfg                                                | 22  |

|   | 5.9  | TOOL    | S, VCDAnalyzer and VHDLGenerators                  | 25  |

|   |      | 5.9.1   | VCD file format                                    | 25  |

|   |      | 5.9.2   | Conversion to Wavedrom                             | 26  |

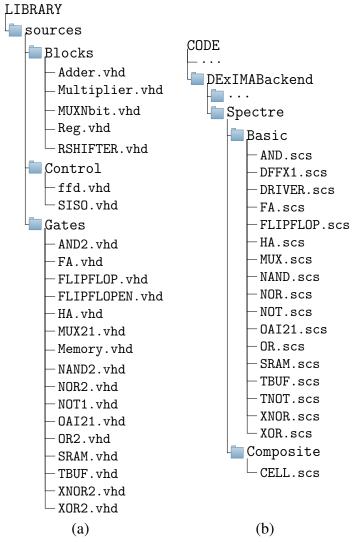

|   | 5.10 | Availab | ble blocks: LIBRARY folder and SPICE description 1 | 27  |

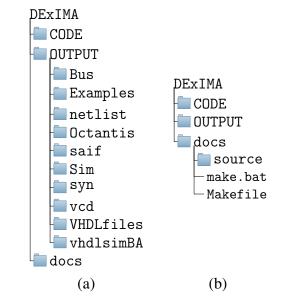

|   | 5.11 | OUTP    | UT and Documentation folders                       | 29  |

|   | 5.12 | Project | files                                              | 30  |

|   |      | 5.12.1  | Main folder                                        | 32  |

|   |      | 5.12.2  | Gem5 output directory                              | 34  |

|   | 5.13 | Conclu  | usions                                             | 37  |

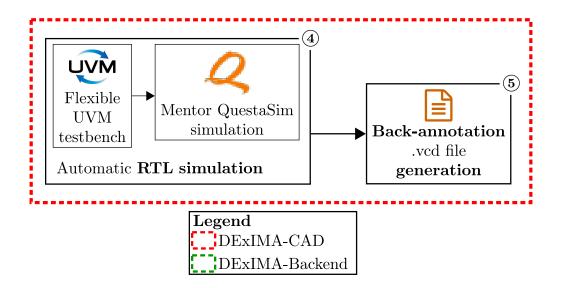

| 6 | Auto | matic F | RTL simulation 1                                   | .38 |

|   | 6.1  | Simula  | tion script                                        | 39  |

|   | 6.2  | Univer  | sal Verification Methodology testbench             | 40  |

|   | 6.3  | Interfa | ce                                                 | 41  |

|   | 6.4  | Sequer  | nce Item                                           | 42  |

|   | 6.5  | Driver  |                                                    | 43  |

|   | 6.6  | The Re  | gister Environment                                 | 46  |

|   | 6.7  | Sequer  | nces                                               | 47  |

|   |      | 6.7.1   | Reset sequence                                     | 48  |

|   |      | 6.7.2   | Write and read sequences                           | 48  |

|   |      | 6.7.3   | Set LiM operation sequence                         | 49  |

|   |     | 6.7.4  | Algorithm execution sequence                    | 149 |

|---|-----|--------|-------------------------------------------------|-----|

|   | 6.8 | The UV | VM main test                                    | 151 |

|   | 6.9 | Conclu | sions                                           | 153 |

| 7 | DEx | IMA-Ba | ackend                                          | 154 |

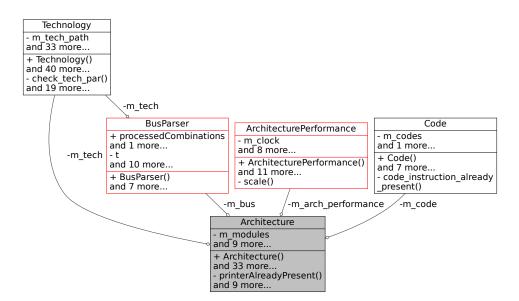

|   | 7.1 | Main c | lasses overview                                 | 156 |

|   | 7.2 | DExIM  | IA-Backend input file                           | 158 |

|   |     | 7.2.1  | The Technology class                            | 165 |

|   |     | 7.2.2  | Concept of the Printer class                    | 171 |

|   |     | 7.2.3  | The STDCell class                               | 174 |

|   |     | 7.2.4  | The CompositeGate and MultibitBlock classes     | 183 |

|   |     | 7.2.5  | The Module class                                | 188 |

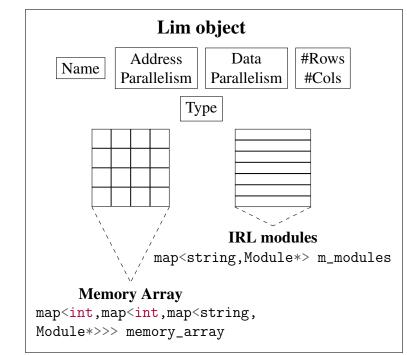

|   |     | 7.2.6  | The Lim and the Architecture classes            | 188 |

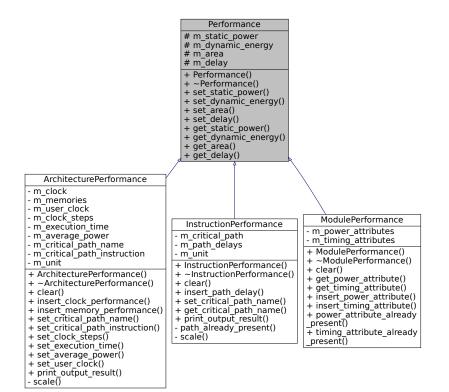

|   |     | 7.2.7  | The Performance class and its inherited classes | 189 |

|   | 7.3 | Compu  | itational model                                 | 191 |

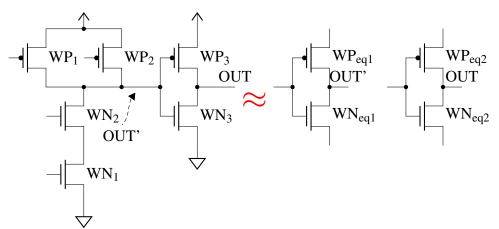

|   |     | 7.3.1  | Model for parallel and series transistors       | 191 |

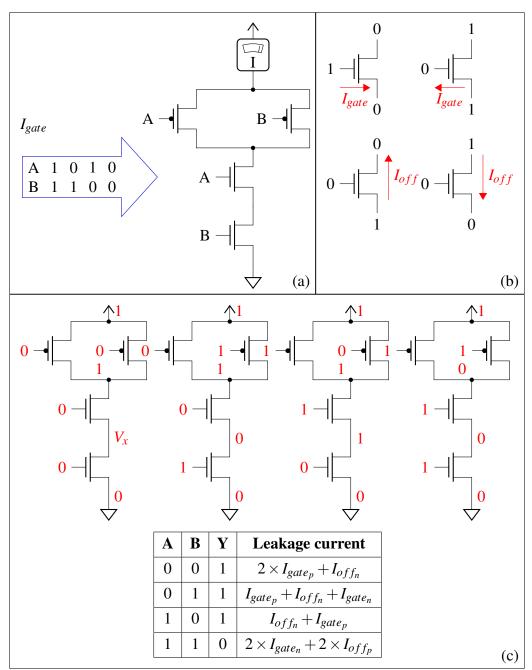

|   |     | 7.3.2  | Short circuit current                           | 192 |

|   |     | 7.3.3  | Modeling the static power                       | 197 |

|   |     | 7.3.4  | MOS capacitance model                           | 200 |

|   |     | 7.3.5  | Switching activity propagation model            | 210 |

|   |     | 7.3.6  | Dynamic energy and power models                 | 212 |

|   |     | 7.3.7  | Area model                                      | 212 |

|   |     | 7.3.8  | Delay model                                     | 213 |

|   |     | 7.3.9  | Bus model                                       | 214 |

|   |     | 7.3.10 | DExIMA output file                              | 223 |

|   | 7.4 | Conclu | isions                                          | 226 |

| 8  | Insei | rting LiM in a von Neumann system                                       | 227 |

|----|-------|-------------------------------------------------------------------------|-----|

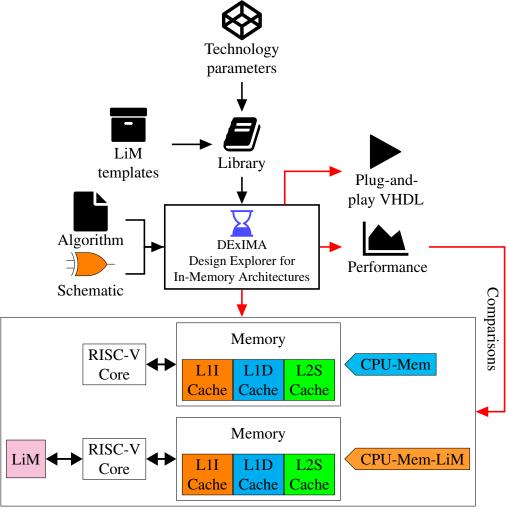

|    | 8.1   | Comparison between CPU-Mem and CPU-Mem-LiM systems                      | 227 |

|    | 8.2   | Conclusions                                                             | 232 |

| 9  | DEx   | IMA-Backend validation                                                  | 233 |

|    | 9.1   | Procedural steps for validation                                         | 234 |

|    |       | 9.1.1 Comparisons with Liberate datasheet                               | 235 |

|    |       | 9.1.2 Comparisons with Synopsys Design Compiler                         | 241 |

|    | 9.2   | Conclusions                                                             | 248 |

| 10 | Testi | ng DExIMA: benchmarking and comparisons                                 | 249 |

|    | 10.1  | XNOR-Net: a binary neural network                                       | 249 |

|    | 10.2  | Matrix-Vector Multiplication                                            | 251 |

|    | 10.3  | K-Nearest Neighbor                                                      | 253 |

|    | 10.4  | Bitmap Indexing                                                         | 255 |

|    | 10.5  | Mean-Variance                                                           | 260 |

|    | 10.6  | Results comparison                                                      | 262 |

|    | 10.7  | DExIMA-Backend vs. Synopsys Design Compiler: complex archi-             |     |

|    |       | tectures                                                                | 270 |

|    |       | 10.7.1 Investigating the worst outcomes: MVM case                       | 272 |

|    |       | 10.7.2 Investigating even more the problem: DExIMA-Backend known issues | 275 |

|    | 10.8  | SRAM vs flip-flop memories                                              | 278 |

|    | 10.9  | Evaluating the impact of the bus on CPU-Mem and CPU-Mem-LiM             | 279 |

|    | 10.10 | OConclusions                                                            | 281 |

| 11 | Conc  | clusions and future works                                               | 282 |

| Re | feren | ces                                                                     | 284 |

X

# **List of Figures**

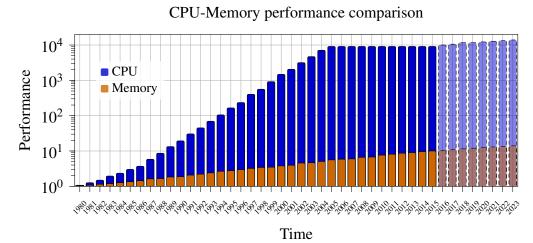

| 1.1 | CPU-memory performance comparison. Non-shaded data are taken<br>from [1]. The shaded bars are obtained through predictions and com-<br>parisons with existing qualitative graphs in the literature, particularly<br>found in the reference [2]. | 6  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

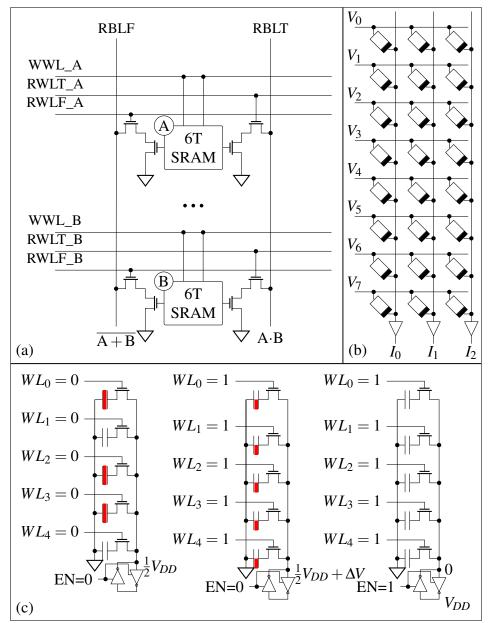

| 1.2 | Examples of Logic-in-Memory computing using (a) SRAM-based [3], (b) memristor-based [4] and (c) DRAM-based architectures [5].                                                                                                                   | 8  |

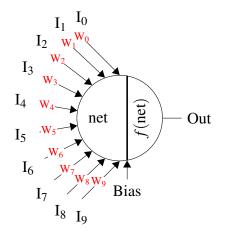

| 1.3 | Schematic of a neuron. Example with 9 inputs                                                                                                                                                                                                    | 15 |

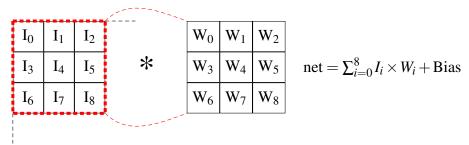

| 1.4 | Convolution computation example with a $3 \times 3$ kernel                                                                                                                                                                                      | 16 |

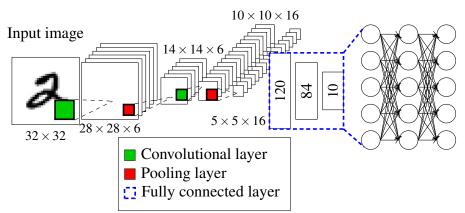

| 1.5 | Structure of LeNet 5 CNN [6], composed of 2 convolutional, 2 pooling and 3 fully connected layers and their sizes are indicated in the model.                                                                                                   | 16 |

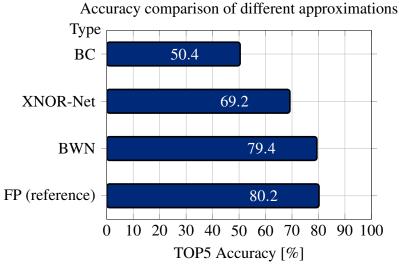

| 1.6 | TOP5 accuracy comparison between different binary approximations[7]                                                                                                                                                                             | 18 |

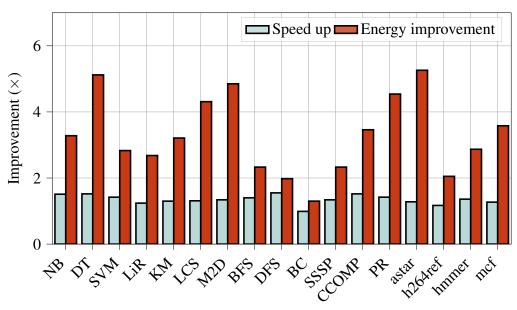

| 1.7 | Speed-up and energy improvements between non-LiM and LiM solutions. Data are taken from [8].                                                                                                                                                    | 24 |

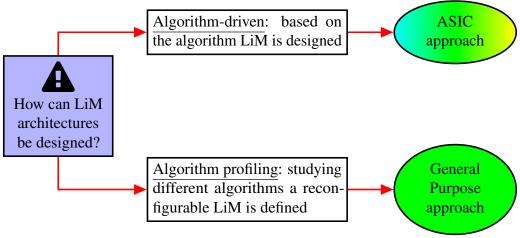

| 2.1 | LiM design approaches                                                                                                                                                                                                                           | 31 |

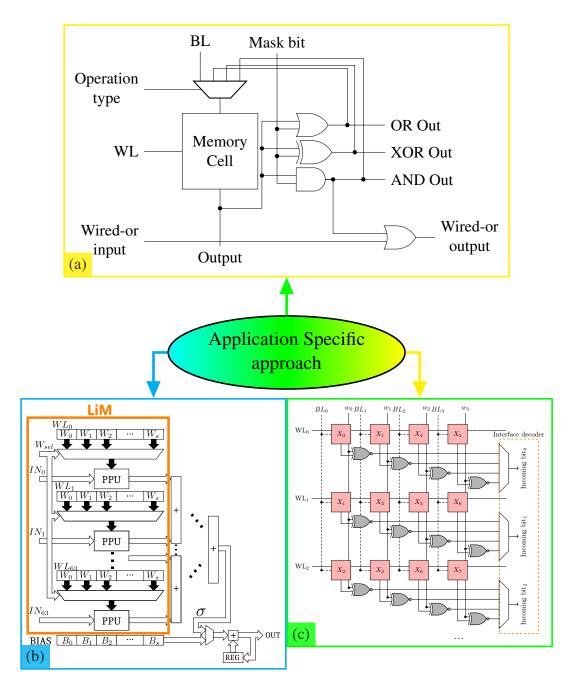

| 2.2 | Overview of the Application Specific implementations. (a) RISC-VLiM data memory. [9, 10] (b) Fixed point LiM implementation of a neural network. [11, 12] (c) XNOR-Net binary neural network implemented in LiM. [13]                           | 32 |

| 2.3 | Layout view of the LiM Cell                                                                                                                                                                                                                     | 40 |

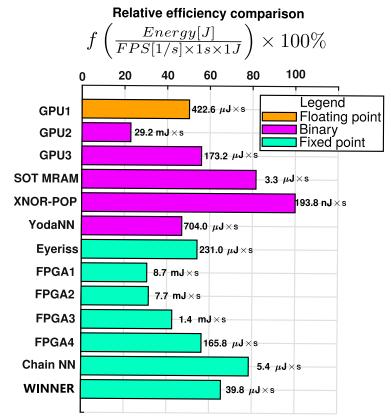

| 2.4  | Comparison of relative levels of efficiency. The numbers have been<br>rescaled in the plot to be shown in percentage form. Above each bar<br>is an indication of the value in absolute terms. In comparison to the<br>XNOR-POP, for instance, the efficiency of the WINNER algorithm               |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | is 70% [14]                                                                                                                                                                                                                                                                                        | 45 |

| 2.5  | Multiple input channels neural network design.                                                                                                                                                                                                                                                     | 47 |

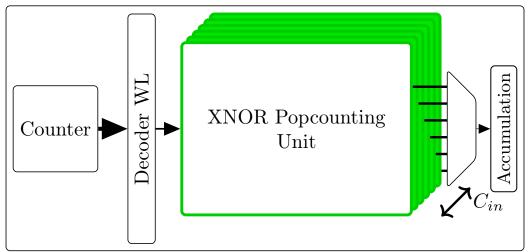

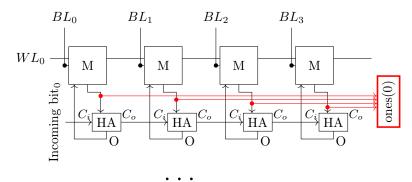

| 2.6  | Ones counter integrated in-memory.                                                                                                                                                                                                                                                                 | 48 |

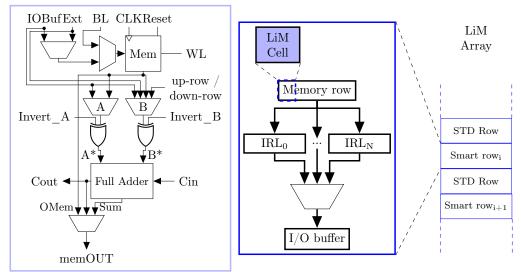

| 2.7  | Hybrid-SIMD LiM array and Cell structures.                                                                                                                                                                                                                                                         | 52 |

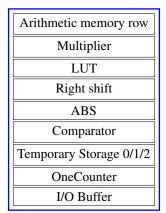

| 2.8  | Smart row structure implementing all the proposed benchmarks                                                                                                                                                                                                                                       | 58 |

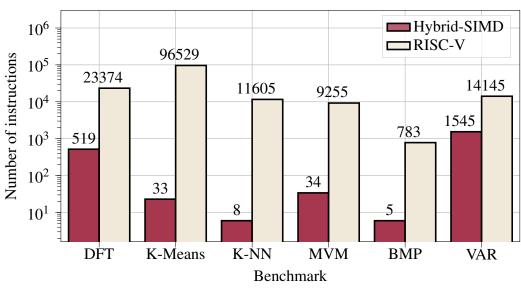

| 2.9  | Number of instructions required for RISC-V/Hybrid-SIMD architec-<br>tures                                                                                                                                                                                                                          | 59 |

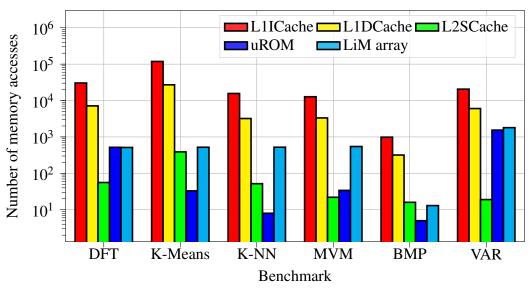

| 2.10 | Number of memory accesses for RISC-V and Hybrid-SIMD systems.                                                                                                                                                                                                                                      | 61 |

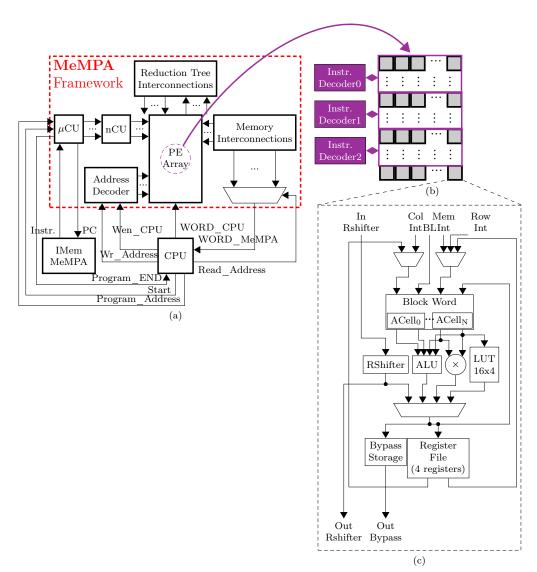

| 2.11 | MeMPA system. [15, 16] (a) MeMPA top-level view. (b) Processing<br>Matrix structure, with Standard Blocks (only memory) and Smart<br>Blocks (memory and computation), and M-SIMD implementation.<br>(c) Smart Block architecture. (d) Structure of the arithmetic cell<br>composing the Block Word | 62 |

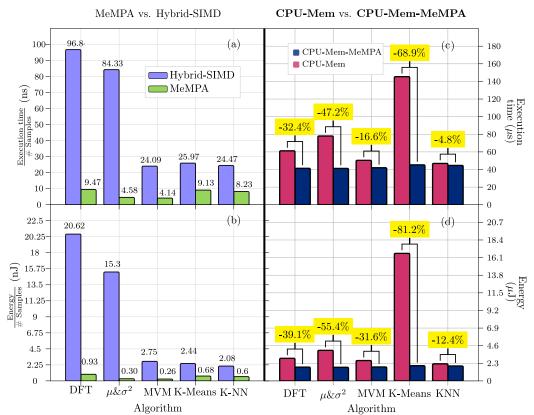

| 2.12 | MeMPA vs Hybrid-SIMD: (a) reports the Execution time/# Samples,<br>while (b) evaluates the Energy/# Samples for both structures. CPU-<br>Mem-MeMPA: Comparison of execution time (c) and energy (d)<br>between CPU-Mem and CPU-Mem-MeMPA solutions                                                 | 66 |

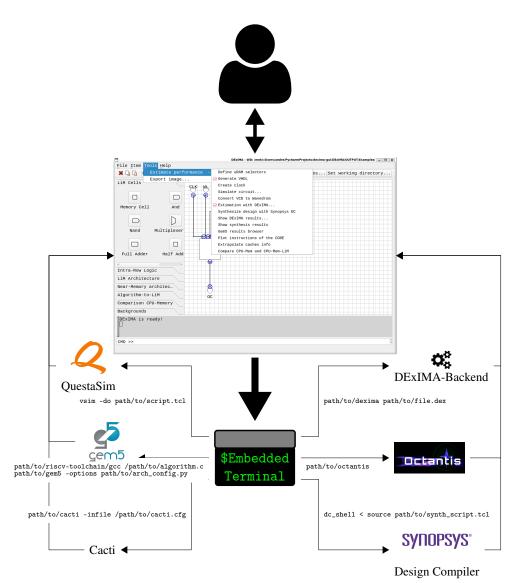

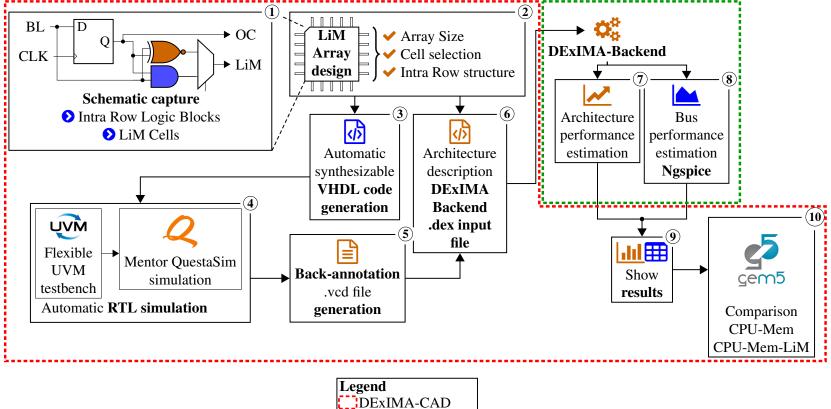

| 3.1  | Overview of the DExIMA software                                                                                                                                                                                                                                                                    | 72 |

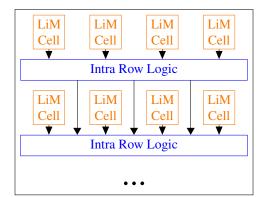

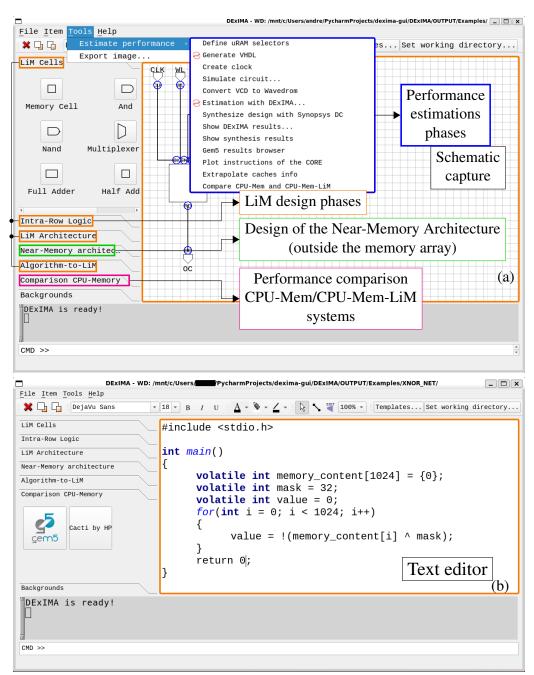

| 3.2  | Reference architectural model for the LiM Memory Array                                                                                                                                                                                                                                             | 73 |

| 3.3  | Base templates of the LiM Cell and IRL                                                                                                                                                                                                                                                             | 74 |

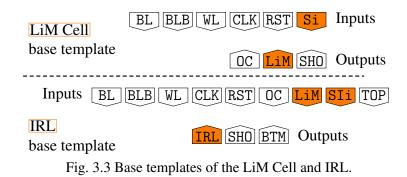

| 3.4  | Microprogrammed Control Unit implemented in DExIMA to support general and flexible driving.                                                                                                                                                                                                        | 76 |

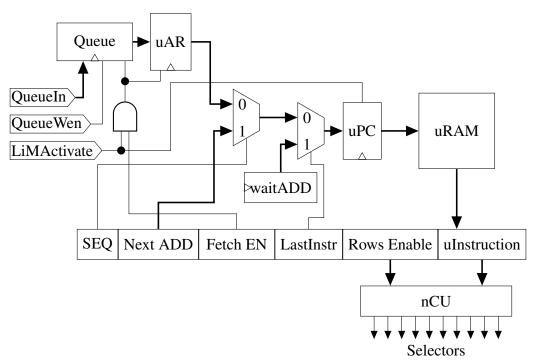

| 3.5  | Main window of the DExIMA tool. (a) Schematic capture. (b)<br>Comparison CPU-Memory and the text editor widget                                                                                                                                                                                     | 78 |

| 3.6  | High-level scheme of DExIMA software interface.                                                                                                                                                                                                                                                    | 80 |

| 3.7  | DExIMA high-level structure                                                                                                                                                                                                                                                                        | 83 |

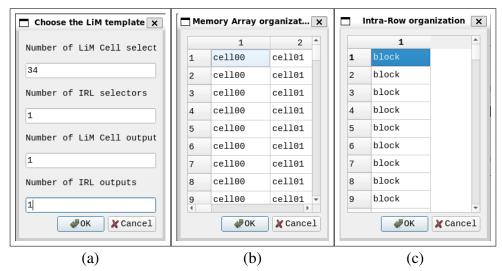

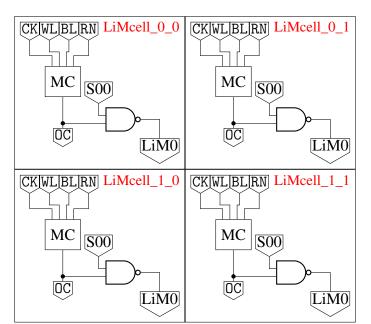

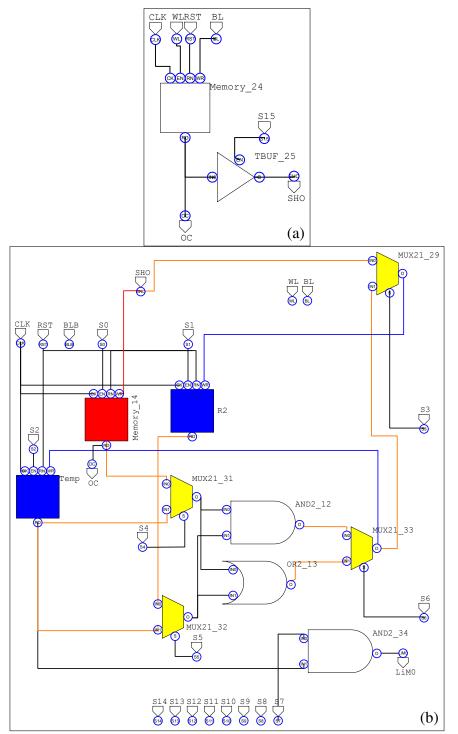

| 4.1  | (a) LiM template example. (b) LiM array cell pattern. (c) IRL organization.                                                                                                                                                                                                                            | 85  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | (a) LiM Cell and (b) IRL block examples. (c) Top-level entity scheme.                                                                                                                                                                                                                                  | 86  |

| 4.3  | Selector values defined for the LiM architecture example using the Define uRAM selectors tool.                                                                                                                                                                                                         | 89  |

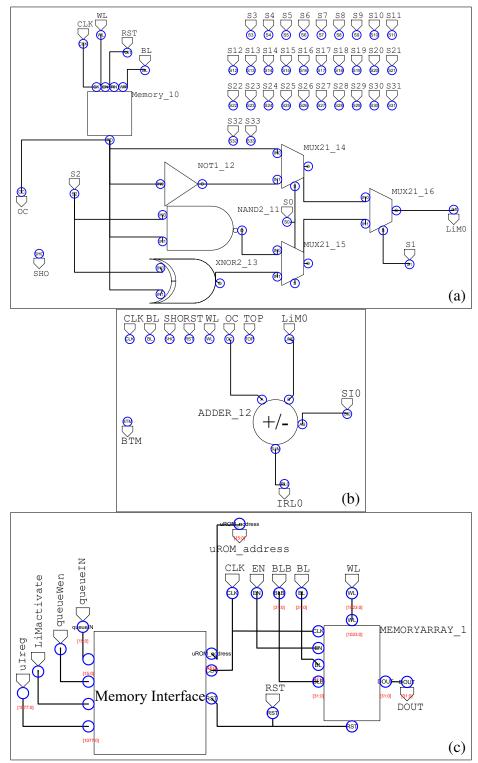

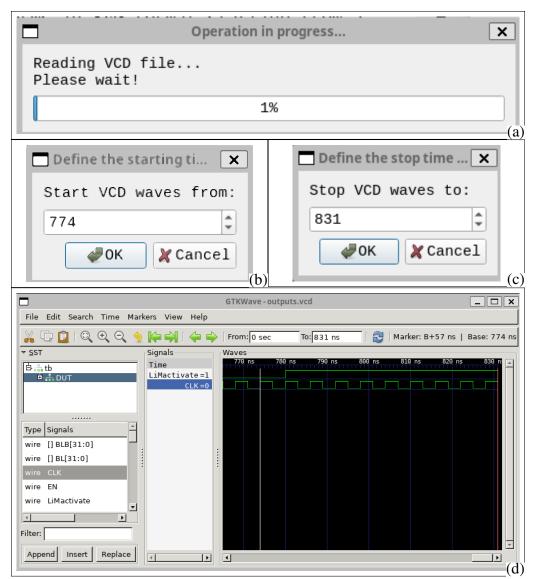

| 4.4  | (a) Schematic of the Flip-Flop-based memory cell. (b) Timing dia-<br>gram example obtained from the output <b>.vcd</b> file: LiMCELL_0_0<br>data precharging during the initial phase. (c) Top-level testbench<br>waveforms during the data precharge phase. (d) Example of the<br>computational phase | 91  |

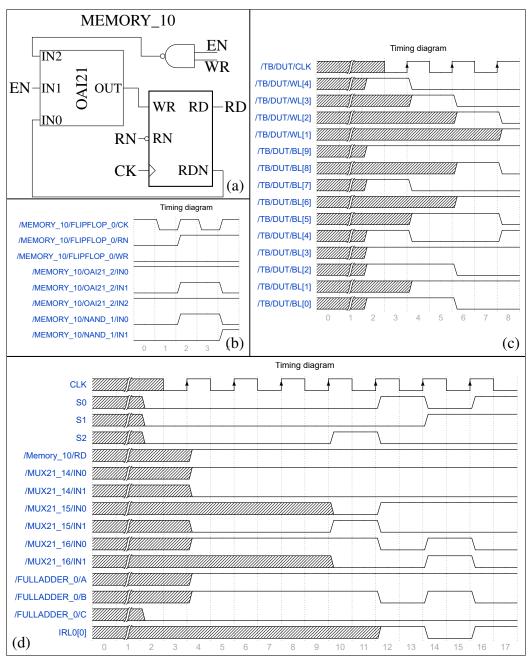

| 4.5  | <ul><li>(a) VCD parsing phase: progress bar indicating the percentage of completion of the operation. (b-c) Start-stop time instants selection dialogs. (d) Start and stop times selection for VCD parsing with GTKWave.</li></ul>                                                                     | 92  |

| 4.6  | Bus(es) selection and parameters definition.                                                                                                                                                                                                                                                           | 93  |

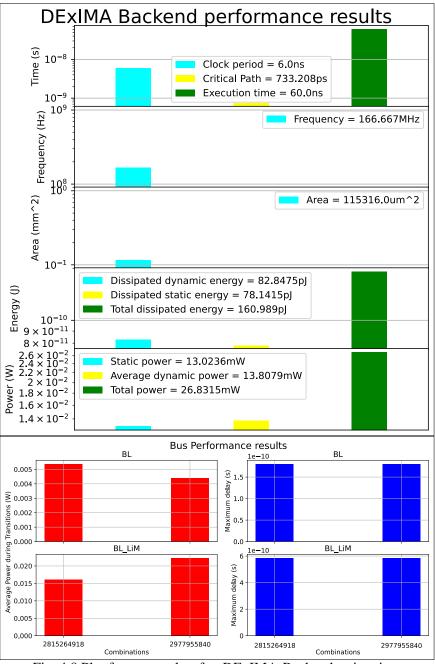

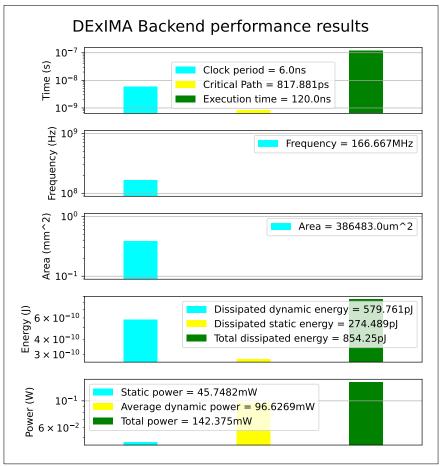

| 4.7  | Tabular format results after DExIMA-Backend estimation.                                                                                                                                                                                                                                                | 95  |

| 4.8  | Plot format results after DExIMA-Backend estimation.                                                                                                                                                                                                                                                   | 96  |

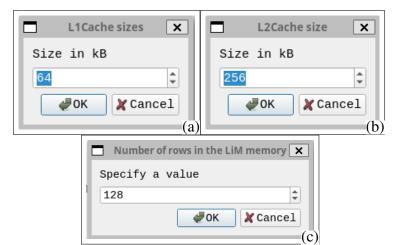

| 4.9  | Steps required for CPU-Mem and CPU-Mem-LiM comparison. (a)<br>L1 I/D cache sizes. (b) L2 shared cache size. (c) Number of LiM<br>memory rows                                                                                                                                                           | 98  |

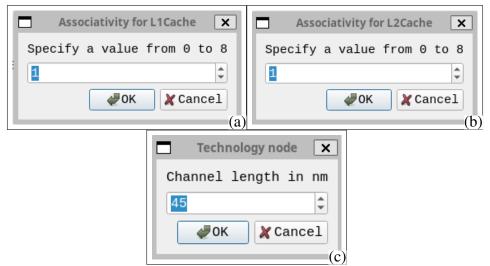

| 4.10 | Steps required for the performance of the caches. (a) L1 I/D cache associativity. (b) L2 shared cache associativity. (c) Technology node.                                                                                                                                                              | 99  |

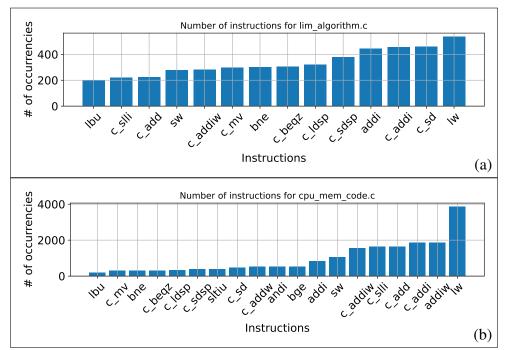

| 4.11 | Estimation of the number of instructions for both CPU-Mem-LiM (a) and CPU-Mem (b) codes                                                                                                                                                                                                                | 99  |

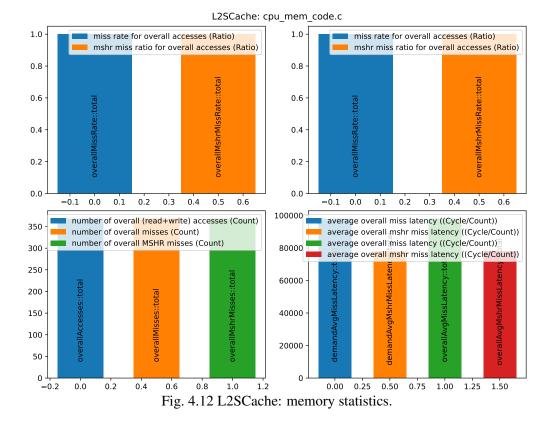

| 4.12 | L2SCache: memory statistics.                                                                                                                                                                                                                                                                           | 100 |

| 4.13 | Final comparison between CPU-Mem and CPU-Mem-LiM systems.                                                                                                                                                                                                                                              | 101 |

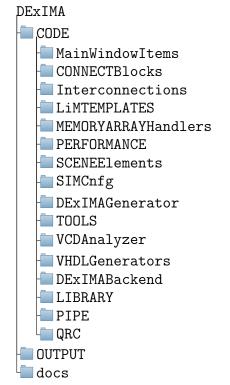

| 5.1  | Folders organizations of the DExIMA project.                                                                                                                                                                                                                                                           | 103 |

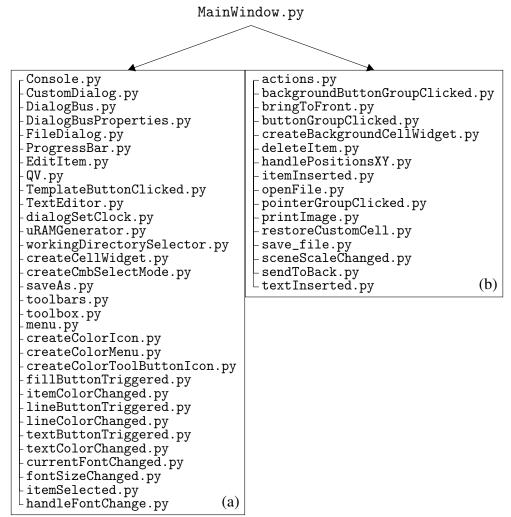

| 5.2  | Contents of the MainWindowItems folder. (a) Dialogs, progress bars,<br>and graphical widgets and elements. (b) Python files performing<br>specific routines or functions related to the graphical part                                                                                                 | 104 |

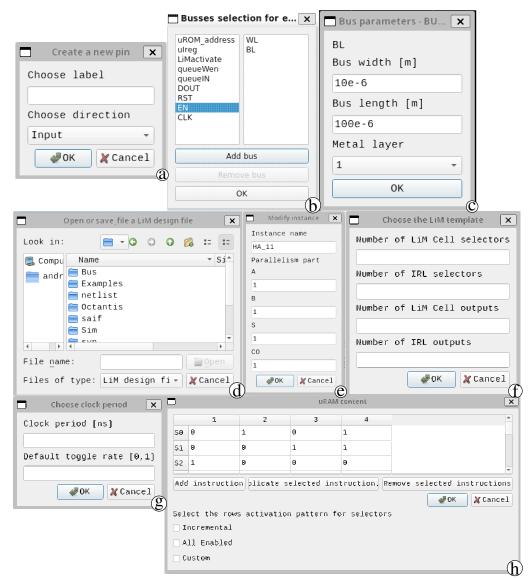

| 5. | .3  | Overview of the implemented dialogs. From left to right and top     |

|----|-----|---------------------------------------------------------------------|

|    |     | to bottom: CustomDialog, DialogBus, DialogBusProperties,            |

|    |     | FileDialog, EditItem, TemplateConfigurator, dialogSetClock          |

|    |     | and uRAMGenerator                                                   |

| 5. | .4  | Main toolbar of DExIMA software                                     |

| 5. | .5  | Top-most menu entries of DExIMA                                     |

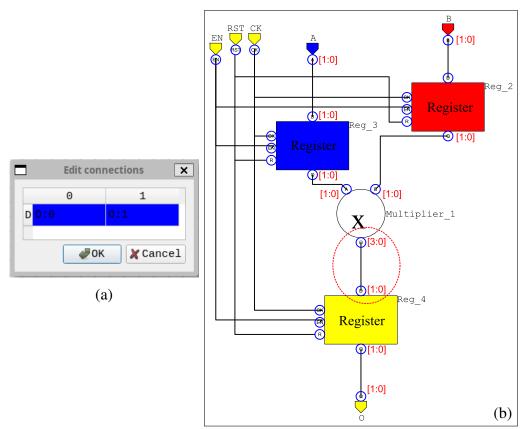

| 5. | .6  | (a) ConnectDialog window, where the user specifies, bit-per-bit,    |

|    |     | the connections between two ports having different parallelisms.    |

|    |     | (b) Example of a circuit having a connection between ports with     |

|    |     | different parallelisms                                              |

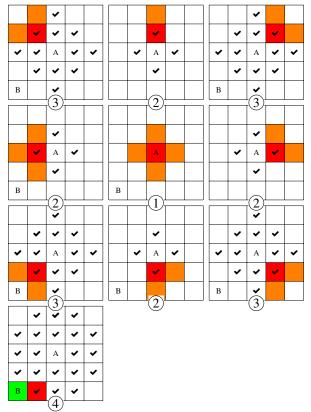

| 5. | .7  | Lee algorithm example applied to a 5x5 grid                         |

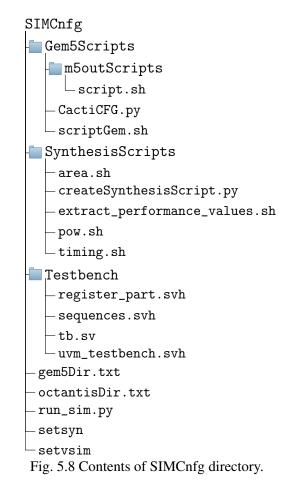

| 5. | .8  | Contents of SIMCnfg directory                                       |

| 5. | .9  | Declaration format of the signal values in a VCD file               |

| 5. | .10 | Example of a rendered waveform in Wavedrom                          |

| 5. | .11 | (a) Content of the LIBRARY folder. (b) Corresponding SPICE file     |

|    |     | descriptions of the standard cells for DExIMA-Backend 129           |

| 5. | .12 | (a) OUTPUT folder organization. (b) Documentation folder organi-    |

|    |     | zation                                                              |

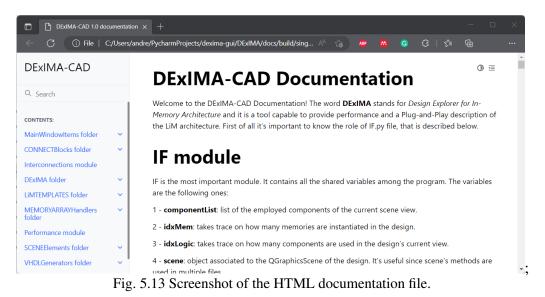

| 5. | .13 | Screenshot of the HTML documentation file                           |

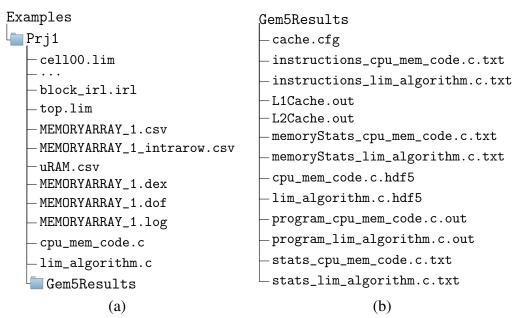

| 5. | .14 | Typical content of a DExIMA project directory. (a) Main folder. (b) |

|    |     | Gem5 results directory                                              |

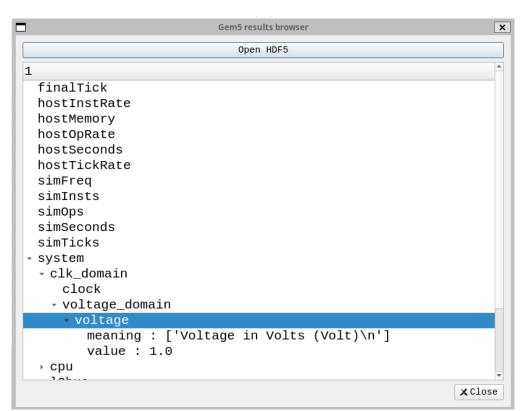

| 5. | .15 | Statistics extracted from Gem5 simulation                           |

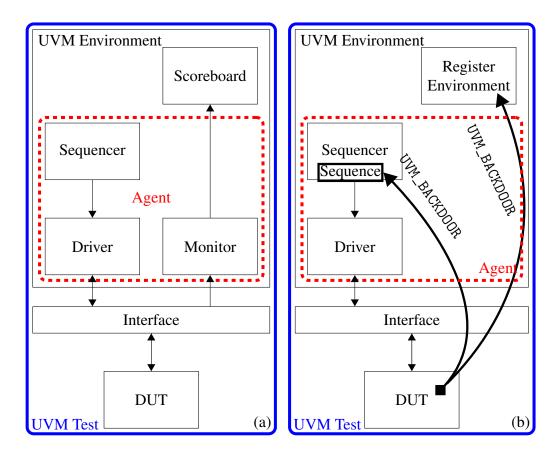

| 6  | .1  | (a) High-level scheme of a generic UVM testbench. (b) High-level    |

| 0. | • 1 | scheme of the UVM testbench employed in the DExIMA project 140      |

|    |     |                                                                     |

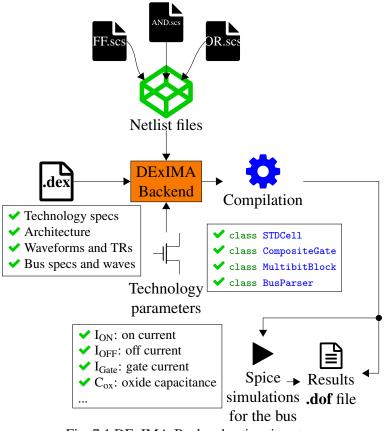

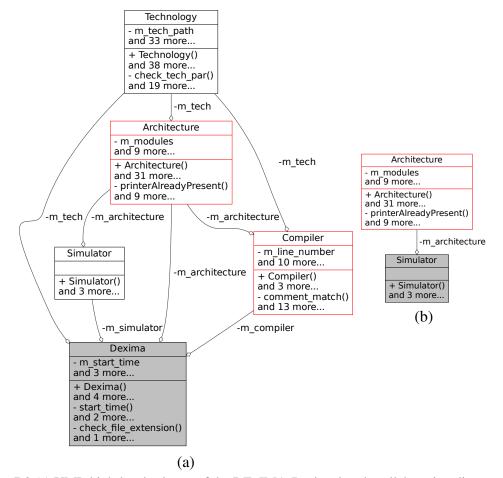

| 7. | .1  | DExIMA-Backend estimation steps                                     |

| 7. | .2  | (a) UML high-level scheme of the DExIMA-Backend tool: collab-       |

|    |     | oration diagram of Dexima class. (b) Collaboration diagram of       |

|    |     | Simulator class                                                     |

| 7.3  | Toy example of a LiM architecture and the associated DExIMA file<br>in Listing 37                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

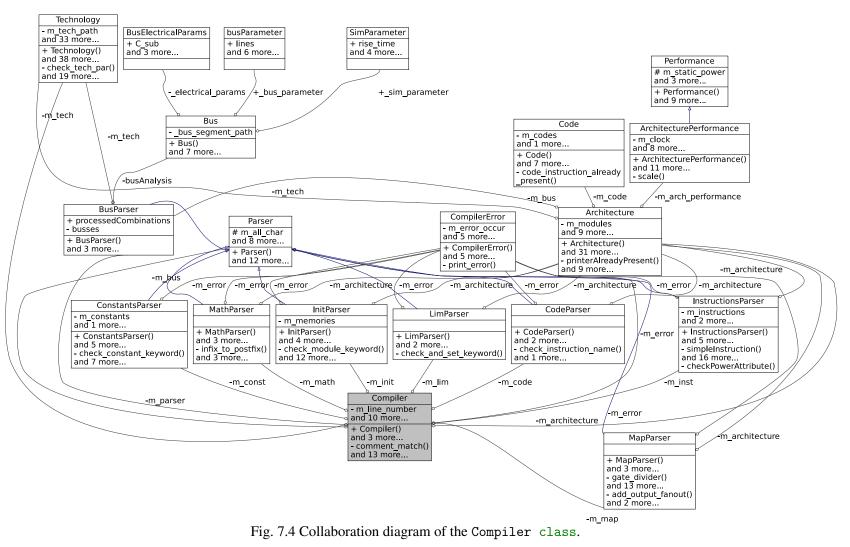

| 7.4  | Collaboration diagram of the Compiler class                                                                                                                                 |

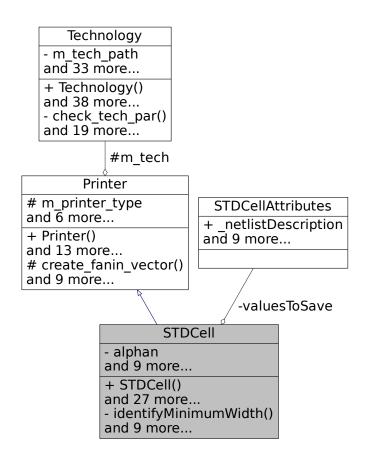

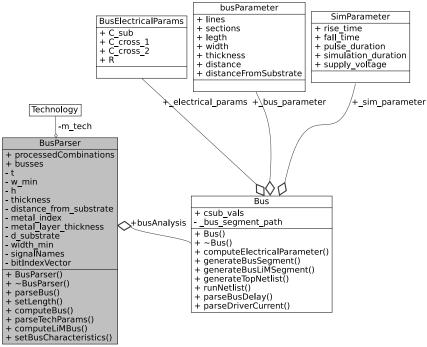

| 7.5  | UML class diagram of the Technology class                                                                                                                                   |

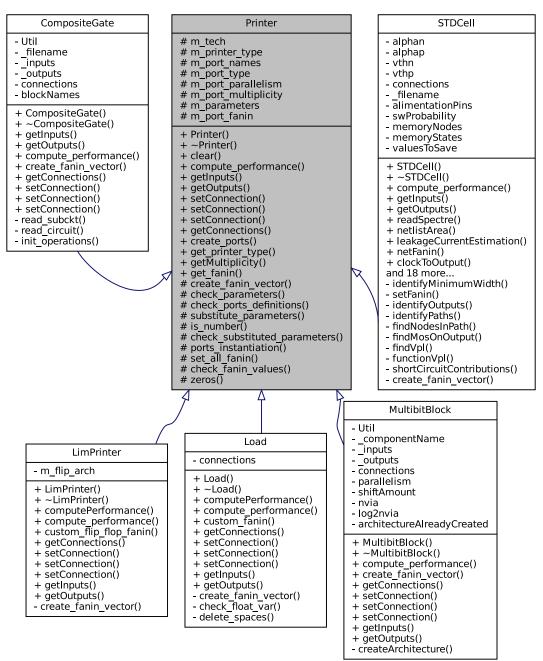

| 7.6  | Inheritance graph of the Printer class                                                                                                                                      |

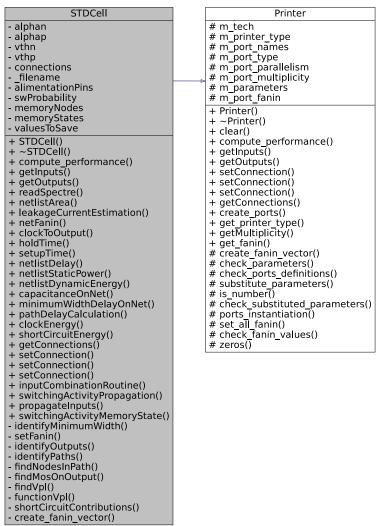

| 7.7  | UML diagram representation of the STDCell class                                                                                                                             |

| 7.8  | Related class elements of the STDCell class                                                                                                                                 |

| 7.9  | Fanout evaluation example: two inverters                                                                                                                                    |

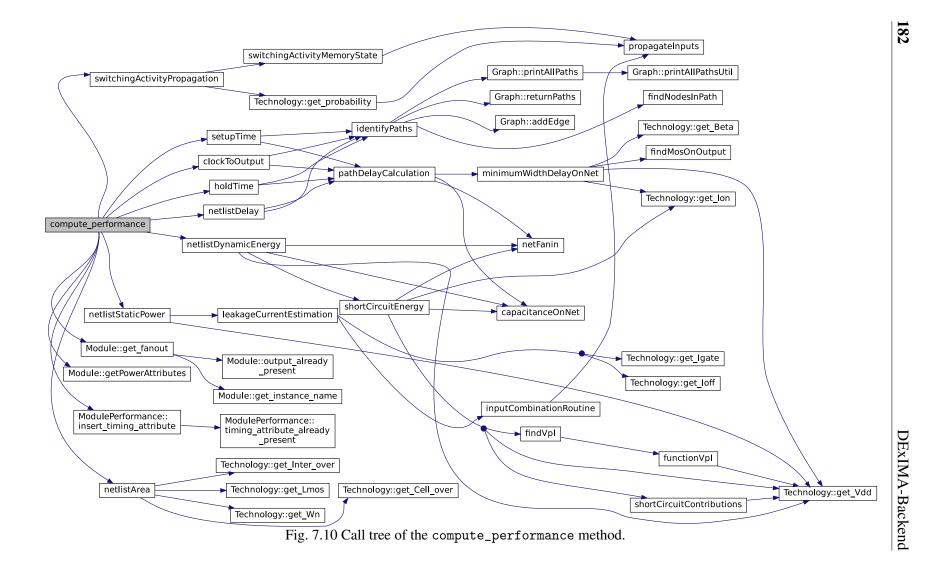

| 7.10 | Call tree of the compute_performance method                                                                                                                                 |

| 7.11 | Collaboration diagram for the CompositeGate class                                                                                                                           |

| 7.12 | Collaboration graph of the BlockUtilities class                                                                                                                             |

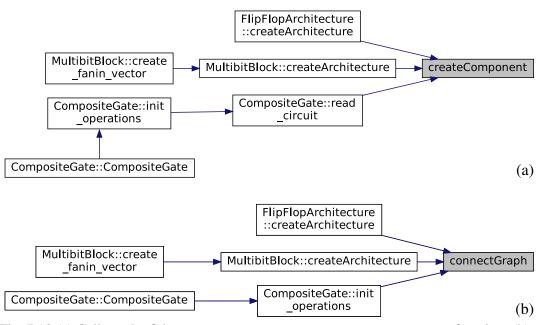

| 7.13 | (a) Call graph of the void BlockUtilities::createComponent function. (b) Call graph of the void BlockUtilities::connectGraph function                                       |

| 7.14 | Module class collaboration diagram                                                                                                                                          |

| 7.15 | Lim object: high-level scheme                                                                                                                                               |

| 7.16 | Collaboration graph of the Architecture class                                                                                                                               |

| 7.17 | Performance class inheritance graph                                                                                                                                         |

| 7.18 | AND2_X1 gate reduction example for the short circuit power com-<br>putation                                                                                                 |

| 7.19 | <ul><li>(a) Measurement of the static power for all input combinations. (b)</li><li>Leakage currents model used in DExIMA-Backend for the NMOS</li><li>transistor</li></ul> |

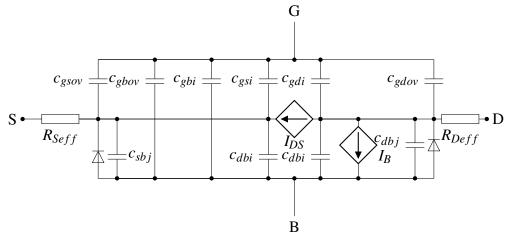

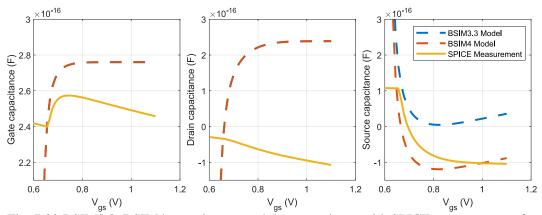

| 7.20 | MOS capacitance model used in Cadence Spectre [17] 200                                                                                                                      |

| 7.21 | Self capacitances of the MOS device                                                                                                                                         |

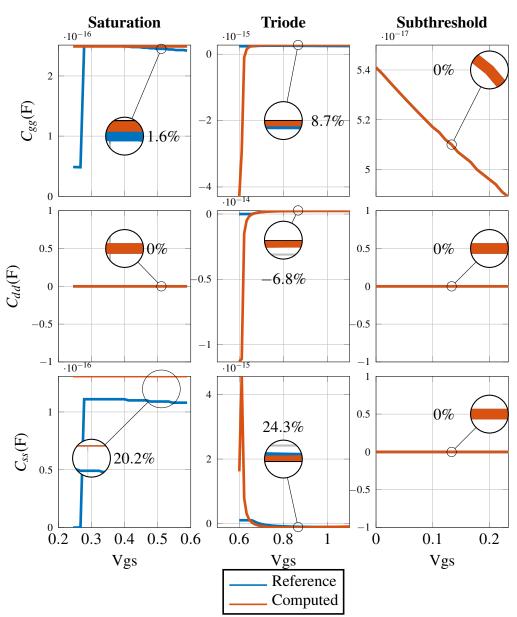

| 7.22 | BSIM3.3, BSIM4 capacitance models comparisons with SPICE                                                                                                                    |

|      | measurements for the triode region                                                                                                                                          |

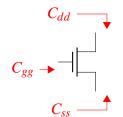

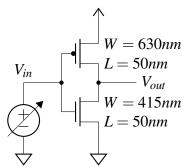

| 7.23 | Schematic of the inverter used in Cadence Virtuoso for intrinsic capacitance validation                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.24 | Comparison between reference and computed $C_{gg}$ , $C_{ss}$ and $C_{dd}$ in-<br>trinsic capacitances                                               |

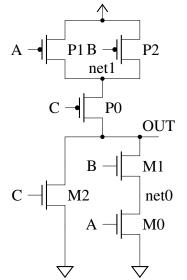

| 7.25 | Schematic of the And-Or-Invert 2-1 gate                                                                                                              |

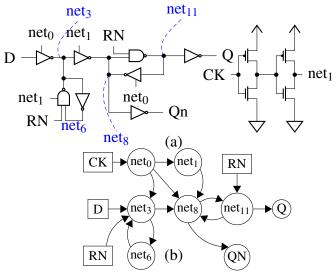

| 7.26 | (a) Schematic of a flip-flop with the equivalent logic gates. (b) Equivalent graph of the flip-flop                                                  |

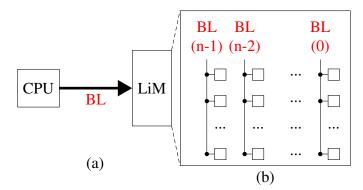

| 7.27 | Bus estimation. External (a) and internal (b) bus contributions 215                                                                                  |

| 7.28 | Simulation window in which the average transition power of a bus is computed                                                                         |

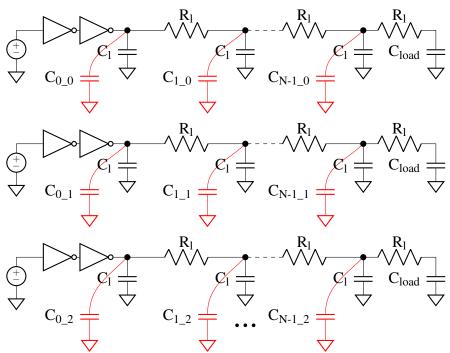

| 7.29 | Equivalent netlist of an external bus, used for the bus performance estimation. The number of lines is associated to the number of bits of the bus   |

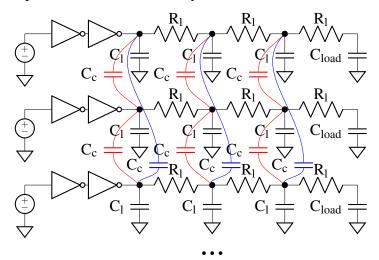

| 7.30 | LiM internal equivalent model for the bus estimation                                                                                                 |

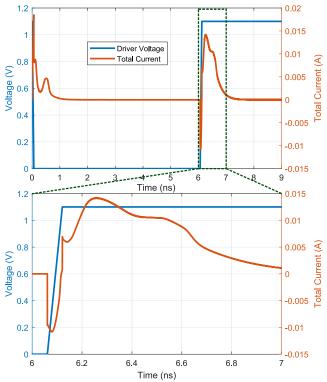

| 7.31 | Ngspice-based bus estimation waveforms. (a) Transition example<br>for the bit-0 of the BL bus. (b) Transition example for the bit-1 of<br>the BL bus |

| 7.32 | Collaboration graph of the BusParser class                                                                                                           |

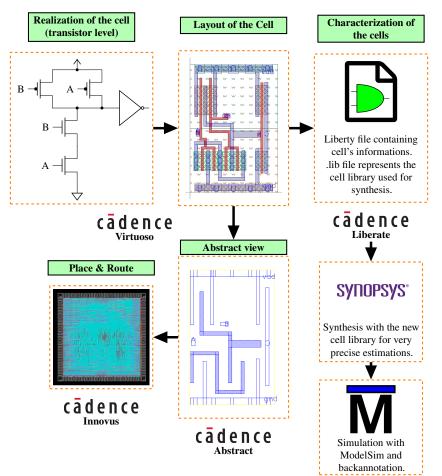

| 9.1  | Example of a typical characterization steps for a standard cell library. 237                                                                         |

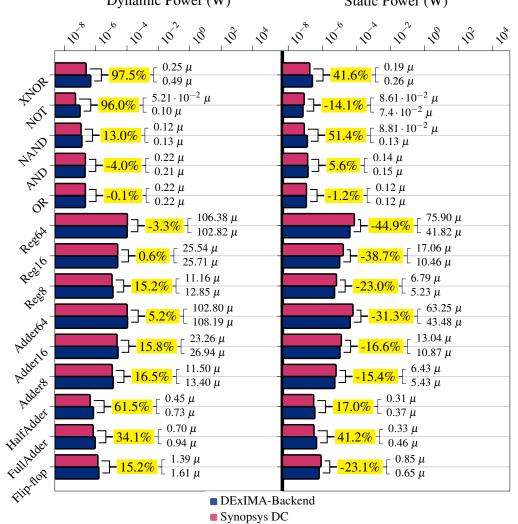

| 9.2  | Dynamic and Static powers comparisons between DExIMA and<br>Synopsys Design Compiler                                                                 |

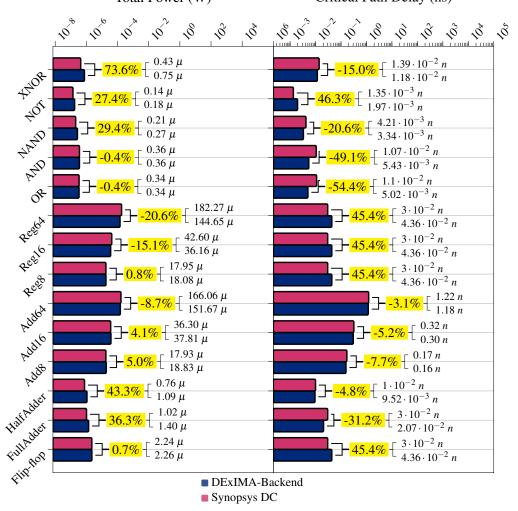

| 9.3  | Total power and critical path comparisons between DExIMA and Synopsys Design Compiler                                                                |

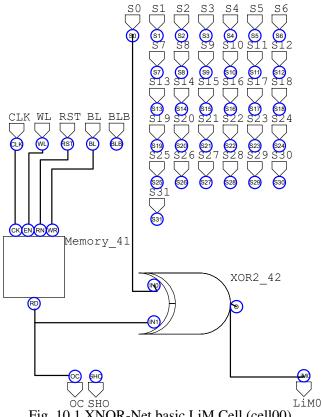

| 10.1 | XNOR-Net basic LiM Cell (cell00)                                                                                                                     |

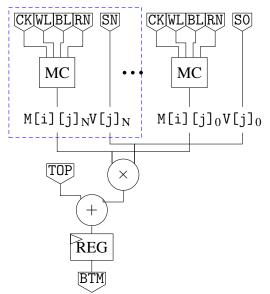

| 10.2 | LiM cell (bordered in blue) and IRL circuits for the MVM algorithm.<br>IRL contains a multiplier, an adder and a register                            |

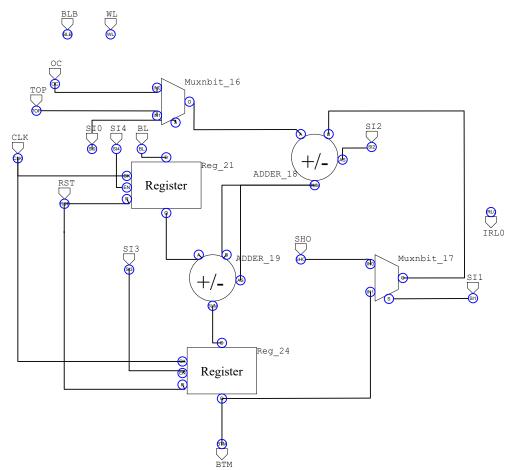

| 10.3 | IRL block implementing the K-NN computation                                                                                                          |

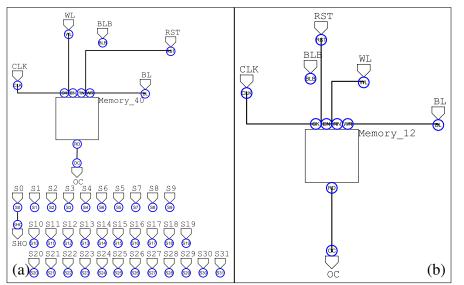

| 10.4  | LiM Cells used to implement the K-NN algorithm. (a) Cell 00, used to connect the selectors on the SHO bus. (b) Standard memory cells that simply hold data                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.5  | LiM Cells for BMP implementation. (a) Standard memory cells (st_memory_cell) and (b) LiM computational cells (compute_cell00).257                                                                                                                                                                                     |

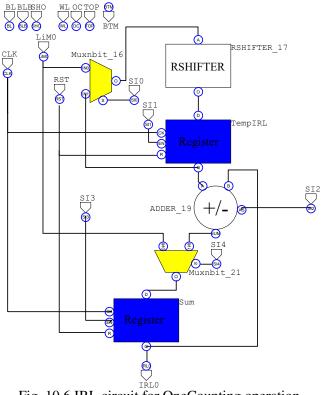

| 10.6  | IRL circuit for OneCounting operation                                                                                                                                                                                                                                                                                 |

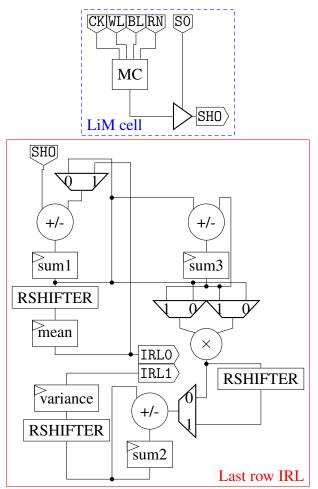

| 10.7  | Mean-Variance LiM cells and IRL circuits. Selectors pins are not shown for clarity                                                                                                                                                                                                                                    |

| 10.8  | DExIMA-Backend results for the MVM algorithm. The evaluation with back-annotation during the algorithm evaluation phase 266                                                                                                                                                                                           |

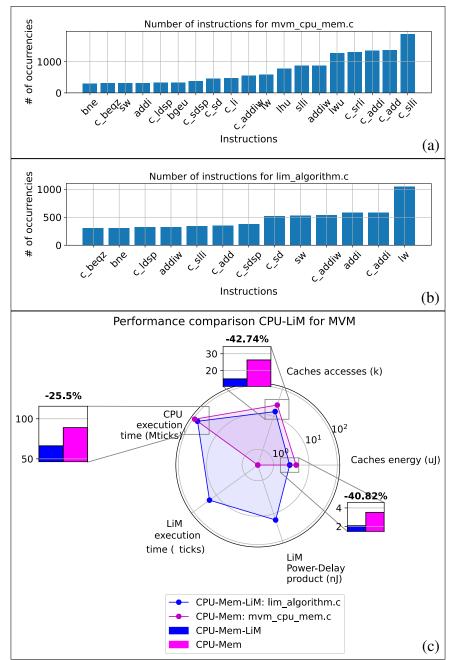

| 10.9  | Results of the MVM algorithm. The evaluation with back-annotation<br>during the algorithm evaluation phase. (a-b) Instructions profiling<br>for the MVM of the CPU-Mem and CPU-Mem-LiM architectures,<br>respectively. (c) Comparison between CPU-Mem and CPU-Mem-<br>LiM for the MVM (axes are in logarithmic scale) |

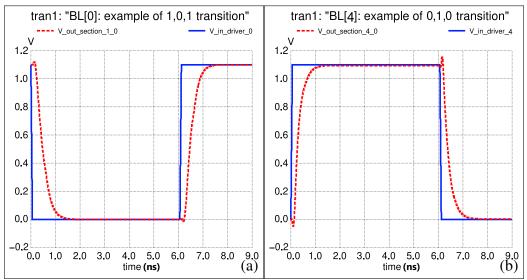

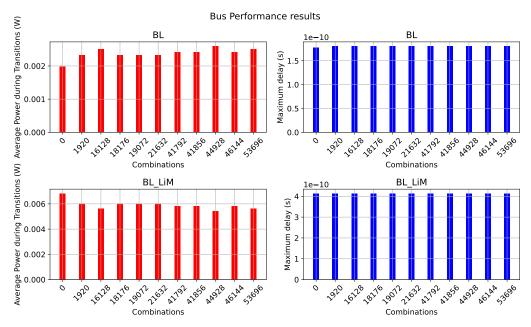

| 10.10 | OBL Bus estimation of the MVM algorithm during data precharging. 268                                                                                                                                                                                                                                                  |

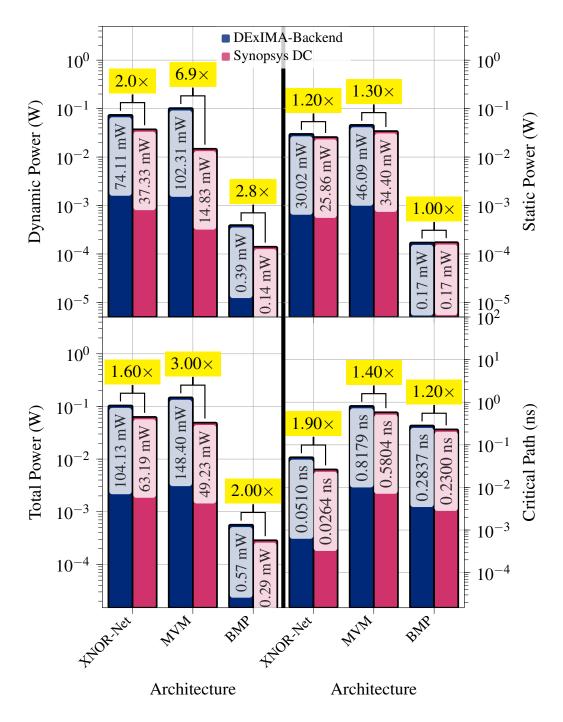

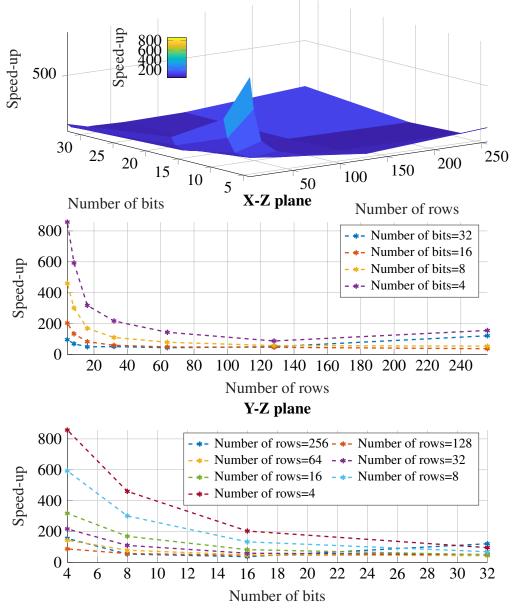

| 10.1  | Performance comparison between Synopsys Design Compiler and DExIMA-Backend for MVM, XNOR-Net and BMP                                                                                                                                                                                                                  |

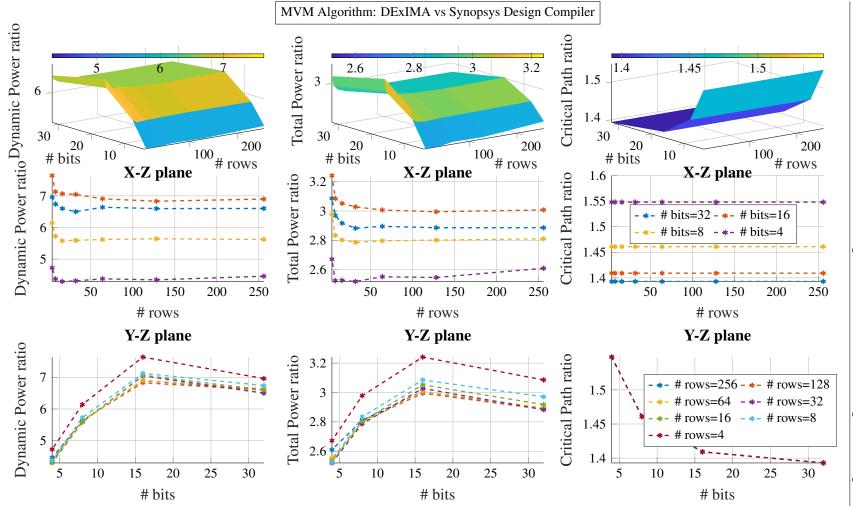

| 10.12 | 2Comparison between DExIMA-Backend and Synopsys Design Com-<br>piler performance results. The parallelism and the number of rows<br>of the LiM array are swept                                                                                                                                                        |

| 10.13 | 3DExIMA-Backend vs Synopsys Design Compiler Execution Time<br>speed-up ratio                                                                                                                                                                                                                                          |

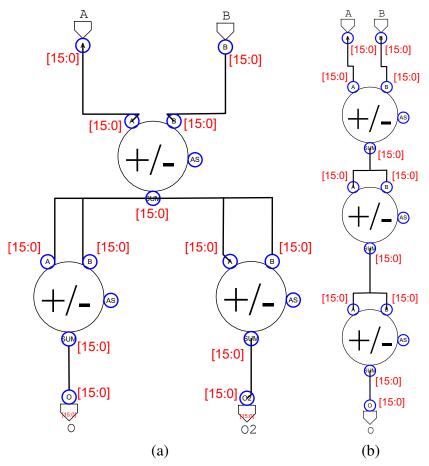

| 10.14 | 4(a) Two parallel adders circuit example. (b) Three serial adders circuit example                                                                                                                                                                                                                                     |

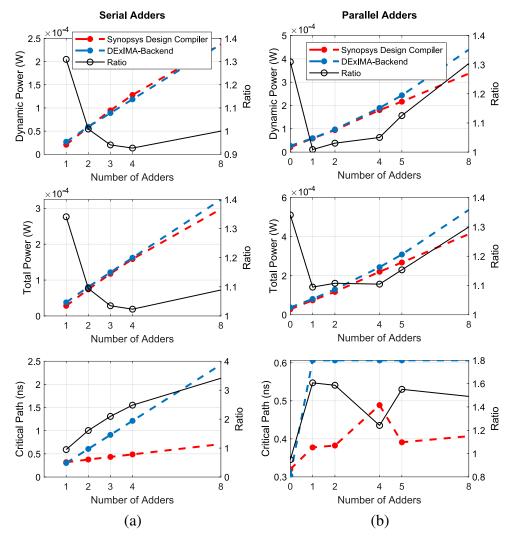

| 10.15 | 5Dynamic, Total Powers and Critical Path comparisons between<br>DExIMA-Backend and Synopsys Design Compiler. (a) Serial Adders<br>analysis. (b) Parallel Adders analysis                                                                                                                                              |

## **List of Tables**

| 1.1 | Results of execution cycles and usage percentage for BMP, MVM<br>and Linear Algebra algorithms on the architectures used in Sim <sup>2</sup> PIM.<br>The numerical values are extracted from the graph in Figure 8 on |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | page 9 of the Sim <sup>2</sup> PIM article [18]                                                                                                                                                                       | 25 |

| 2.1 | Simulation results comparison                                                                                                                                                                                         | 38 |

| 2.2 | Estimated Post Place&Route performance of the RISC-V core, stan-                                                                                                                                                      |    |

|     | dard (MEMORY), and LiM memory with a 4kB size                                                                                                                                                                         | 40 |

| 2.3 | Number of memory operations comparison between Memory and                                                                                                                                                             |    |

|     | LiM cases                                                                                                                                                                                                             | 41 |

| 2.4 | Memory energy comparisons using a clock period of 3ns                                                                                                                                                                 | 41 |

| 2.5 | AlexNet structure with the necessary number of steps for the refer-                                                                                                                                                   |    |

|     | ence architecture consisting of 64 inputs per neuron                                                                                                                                                                  | 43 |

| 2.6 | State-of-the-art performance comparison with AlexNet model. Pro-<br>cess time is rescaled to batch size equal to 1. The data of this table                                                                            |    |

|     | are partially taken from [19].                                                                                                                                                                                        | 46 |

| 2.7 | Post place&route estimation for two neural network models                                                                                                                                                             | 49 |

| 2.8 | CAM-based XNOR-Pop [20] and our LiM architectures performance                                                                                                                                                         |    |

|     | parameters comparison.                                                                                                                                                                                                | 49 |

| 2.9 | The frequency of occurrence of each instruction for SPLASH-2                                                                                                                                                          |    |

|     | benchmarks. barnes, fmm, ocean-contiguous-partitions, ocean-                                                                                                                                                          |    |

|     | non-contiguous-partitions, radiosity, water-nsquared, and water-                                                                                                                                                      |    |

|     | <b>spatial</b> are the algorithms examined                                                                                                                                                                            | 51 |

| 2.10 | Available operations performed by the LiM Cell's full adder                                                                               | 53 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | Place&Route results of the Hybrid-SIMD using CMOS 45nm tech-<br>nology [21]                                                               | 58 |

| 2.12 | Energy comparison between caches energy accesses and Hybrid-SIMD.                                                                         | 60 |

| 2.13 | Data initialization cycles, parameters, execution cycles and post-<br>Place&Route back-annotated power of each algorithm                  | 65 |

| 2.14 | Comparison of the number of L1 and L2 cache memory accesses for CPU-Mem and CPU-Mem-MeMPA.                                                | 67 |

| 7.1  | Parameter list of the 45nm CMOS technology                                                                                                | 66 |

| 7.2  | Off and gate current measured with Cadence Virtuoso for a NMOS transistor of the 45nm CMOS technology                                     | 99 |

| 7.3  | Parameters required for $A_{bulk}$ computation. Values are extracted from the NMOS model file                                             | 04 |

| 7.4  | Parameters used in the overlap capacitances calculations for the NMOS transistor                                                          | 09 |

| 9.1  | Standard cells performance comparison between Liberate and DExIMA-<br>Backend                                                             | 40 |

| 9.2  | CPU usage time comparison between DExIMA-Backend and Synopsys DC                                                                          | 48 |

| 10.1 | Performance values of each benchmark and comparison CPU-Mem<br>and CPU-Mem-LiM                                                            | 64 |

| 10.2 | Back-annotation/worst-case power estimation comparison during algorithm evaluation                                                        | 65 |

| 10.3 | Toggle rate impact evaluation in terms of dynamic and total powers.<br>Comparison between Synopsys Design Compiler and DExIMA-<br>Backend | 73 |

| 10.4 | SRAM-based and flip-flop based memory arrays performance com-<br>parisons                                                                 | 78 |

| 10.5 | BL bus performance comparison between SRAM-based and flip- |     |

|------|------------------------------------------------------------|-----|

|      | flop-based memories.                                       | 279 |

| 10.6 | Bus impact results and comparisons                         | 280 |

# Part I

# **Background and previous works**

At the end of this document, a glossasy listing acronyms and abbreviations used in this thesis can be found.

## Chapter 1

## Introduction

### Summary

This chapter introduces the concept of Beyond von Neumann Computing, a new computing approach that aims to solve the problems associated with classical architectures based on central processing units and physically separated memories. These architectures are widely used because of their extreme versatility, but they suffer from performance bottlenecks that limit their effectiveness. The section 1.1, introduces the topic and shows the limitations in von Neumann architectures, providing the rationale for why a new computation approach is needed. A study of the state of the art of these architectures is made in the subsection 1.1.1, reporting the most significant cases and providing a categorization of the Beyond von Neumann approach, which appears to be widely used and employed. The subsection 1.1.2 provides an example of an application in which Beyond von Neumann architectures, namely neural networks, with a few examples of architectural implementations provided in the literature. As will be shown in later parts, performing the design of these types of architectures can be extremely complex and tedious, so in this introductory chapter, an overview of tools developed to simplify the design procedures is given. All this is addressed in section 1.2. Finally, in section 1.3, the reason why Beyond von Neumann architectures are so important is presented. Quantitative state-of-the-art results are presented, showing the positive impact this approach has on computing architectures.

### **1.1 State-of-the-art**

Nowadays, electronic devices have rapidly spread in many aspects of human life. Computers, in particular, gained notable improvements over time, becoming fundamental devices for various applications. These applications (such as Machine Learning algorithms or neural networks) have become more and more complex over the years, requiring a massive amount of data (or datasets) to be processed in no time, imposing strict requirements on the hardware or a complete redefinition of the computing paradigms [22]. For this reason, the driving force of the architectural design has focused on integrating more transistors in a single chip by reducing their sizes, especially the channel length, or by investigating new technologies or manufacturing processes like the consolidated Fin-Field Effect Transistors (FinFET) or Gate-All-Around FETs (GAAFET) [23]. However, integrating more transistors will no longer be sufficient to stem the continuous demand for computing power in the near future because of the end of Moore's Law [24, 25]. Moore's Law states that transistors in an Integrated Circuit (IC) double every two years. Up to the present, the silicon industries have followed this trend. Transistor size reduction and technological evolution reduced power and allowed to fit more transistors in the same area. Unfortunately, this trend is about to end, probably reaching a plateau by 2025 [26, 27]. The cause is mainly due to the physical limitations of the channel length and the intrinsic difficulty in controlling the current flow in deep nanoscale transistors. Two directions are possible to overcome CMOS limitations and improve performance: exploring emerging technologies and new computing paradigms and architectures.

The most common architectures used nowadays are based on a Central Processing Unit (CPU), where most operations occur. Each program, application, or task is automatically decomposed in a series of simpler operations (or instructions), that are executed by the CPU, producing results in output. These results and instructions are saved inside memories. These CPU-memory architectures are the most diffused ones and constitute all modern computers. Two main structures are used: the von Neumann architecture [28–30], in which there is only one memory that contains instructions and data into different address spaces, and the Harvard architecture [28], in which data and instruction memories are separated. In both cases, the computational part is located in the CPU, which executes calculations extracting data from memory and saving the results again into the memory itself. This organization achieves a

Fig. 1.1 CPU-memory performance comparison. Non-shaded data are taken from [1]. The shaded bars are obtained through predictions and comparisons with existing qualitative graphs in the literature, particularly found in the reference [2].

high degree of flexibility and supports a wide variety of algorithms that can be easily written and compiled for such architectures. However, von Neumann and Harvard architectures are affected by a huge bottleneck: the Memory-Wall [31–33]. CPUs are becoming more efficient and faster, but the memories cannot follow the same trend, implying a performance reduction of the overall system [1]. This effect is confirmed in Fig. 1.1, where the performance of the CPU and the memory are reported over time. The gap between the two elements has started to grow exponentially since the 1980s. Referring to the von Neumann architectures, this effect is also called von Neumann Bottleneck [34], which is particularly evident in memory-intensive applications. Several techniques have been exploited to reduce the effects of the Memory-Wall. For example, Out-Of-Order (OOO) scheduling, concurrent instructions execution during a memory operation, caching (which consists of inserting several levels of small and very fast SRAMs close to the CPU), and prefetching [35] try to recover the latency of the main memory. However, this bottleneck still persists even in the most recent CPU-centric architectures. For this reason, in recent years, new design concepts have been born that specifically aim to reduce or solve the Memory-Wall.

#### **1.1.1 Beyond von Neumann concept**

One promising technique to solve the Memory-Wall consists of the Beyond von Neumann Computing (BvNC) [36]. The idea of the BvNC focuses on moving part of the computation inside or close to the memory, consequently reducing the data traffic. However, embedding calculations In-Memory is a challenging task and usually requires a redefinition of the existing memory design paradigms or the employment of exotic emerging technologies.

BvNC can be distinguished into two categories: if the computation is performed inside the memory array, the methodology is called Logic-in-Memory (LiM) Computing, otherwise Near-Memory Computing. LiM approaches are generally based on using different memory technologies. In standard CMOS, the most frequently adopted solutions are based on SRAM [37–41] and DRAM [5, 42] arrays. By enabling multiple wordlines (WLs) at the same time and sensing the voltage potentials on the bitlines (BLs), the BL voltages will depend on the contents of the enabled cells, so by choosing appropriate threshold voltages, the sense amplifiers' outputs will coincide with logic functions. Considering the example in Fig. 1.2 (a), proposed in [3], by precharging RBLF and RBLT to VDD and by enabling both A and B lines simultaneously, the resulting voltage on the bitlines will be proportional to the NOR and AND operation. The sense amplifiers are equipped with additional logic to perform different operations. Similarly, the BL current can also be used to perform a current-based computation. The BL current is proportional to the conductance on the path, so it depends on the state of the transistors inside the cell [43]. Moreover, SRAM-based computing is an advantageous technique exploited in [44] to empower cache memories, allowing logical computations within the array and arithmetic operations with a small Near-Memory computational unit. Content Addressable Memories (CAMs) can also be used to perform calculations since they execute the XOR (or XNOR, depending on the CAM type) operation between the search line (SL) and the cell content. The result will be written on the Match Line (ML), which is initially precharged to VDD: if there is no match, the XOR result is 0, and the ML will be discharged to 0. CAMs, as the name suggests, are addressed for data to perform search operations and are divided into two categories, namely Binary CAMs (BCAMs) and Ternary CAMs (TCAMs), which possess 10 and 16 transistors, respectively. BCAMs take care of searching for the exact word within the array, while TCAMs can also handle don't care cases [45]. In detail, the CAM functionality

Fig. 1.2 Examples of Logic-in-Memory computing using (a) SRAM-based [3], (b) memristorbased [4] and (c) DRAM-based architectures [5].

relies on several XNOR(XOR)-bitwise operations between cell contents and SLs, followed by word-level AND that produces the search result on the ML [46]: this working principle is adopted in works like [47, 48]. Moreover, taking advantage of this important feature, CAMs can also be used for other in-memory operations: in [45], a memory is constructed mimicking the functionality of CAM, but also extending its operations to AND and NOR between two or more words within

the array. Specifically, the authors propose a modified version of classical CAM memory using only 6 transistors (i.e., equivalent to SRAM) but still allowing search operations and reducing the area of the array. This memory can be dynamically reconfigured into three modes: BCAM, TCAM and SRAM, respectively. Taking advantage of different storage modes, the words can be stored by columns in the BCAM and TCAM modes, exploiting classical bitlines to perform logic operations, while they are stored by rows when using the memory in SRAM mode. In order to perform search operations, the authors divided the WLs of cells into right WL and left WL to which search line and negated search line are applied, respectively. When there is a match between the data in the cell and the value on the SL, the bitline and the bitline bar remain high. Otherwise, at least one of them is grounded. For each bitline, a modified sense amplifier is placed, which compares the voltage value with a reference voltage. Finally, each pair of sense amplifiers are ANDed to identify the match. In order to write the data in the column, the authors propose a data writing scheme based on the left and right WLs. Unlike the BCAM mode, TCAM instead needs a pair of columns to store a single word, as an additional bit is needed to represent the don't care value, thus "01" don't care, "00" and "11" for 0 and 1, respectively. In fact, the value "01" will always produce a match, whatever the value of the input search string is. Taking advantage of the BCAM mode of operation, it is also possible to perform bitwise AND operations between two or more rows; by enabling multiple right WLs, AND values can be directly obtained on sense amplifiers; similarly, a NOR operation can be obtained by enabling only left WLs. Another example of a BvNC implementation based on the CAM approach is the one presented in [46], where a methodology is developed to perform additions directly within CAM, which is implemented with different technologies: traditional SRAM and Ferroelectric FET (FeFET). The authors then propose a CAM-based architectural solution for searching within a homomorphically encrypted database, which involves the insertion of additional logic near the memory array that is responsible for computing the sum operation. Moreover, to perform the accumulation, the architecture is provided with in-place copy buffers that allow the rewriting of the sum result directly inside the memory. Another example is the work proposed in [49], where the authors propose an implementation of the Nearest Neighbor search algorithm using a CAM, which performs the computation of the hamming distance directly within the array. This time, the CAM is based on nanoelectromechanical switch technology, a new promising technology for the proposed implementation.

Regarding the DRAM-based computing, a solution is proposed in [5] and shown in Fig. 1.2 (c). The working principle is similar to the SRAM one, but this time the sensing is performed on the capacitors inside the DRAM cells. The computation starts by precharging the BL on  $\frac{VDD}{2}$ , keeping all the WLs disabled. Then, the WLs are enabled, and the capacitors inside the cells share their charges on the BL, which voltage potential results to be shifted by  $\Delta V$ , proportional to the contents of the enabled cells. Finally, the sense amplifiers are enabled, and the resulting  $\Delta V$  voltage will be translated to VDD or 0V, realizing the 5-inputs majority voting function (MAJ5). The majority voting logic can be exploited to compute the 1-bit sum by performing a MAJ3(A,B,Cin) to compute the Cout and a MAJ5(A,B,Cin,Cout,Cout). Another important LiM approach consists of the use of emerging resistive technologies, very popular in the LiM field, such that they become a promising alternative to CMOS arrays. Technologies like Magnetic Tunnel Junction (MTJ) [50-52, 36, 53], memristor [54-57] and Phase Change Memory (PCM) [36, 58, 59] are often used instead of CMOS-based memory cells. They are capable of storing data and performing computations within the array, maintaining low operating power and high efficiency simultaneously. Such devices store data through their intrinsic resistance, which can assume a high or low value depending on the applied voltage or current: high resistance  $(R_H)$  is usually associated with logic '0', while low resistance  $(R_L)$ with logic '1'. Usually, the computation is performed by exploiting Kirchhoff's current laws, similar to current-based computation in standard technologies. In the example shown in Fig. 1.2 (b) and proposed by [4], a memristor-based crossbar structure is used both as memory and computation array. The voltages are applied to one end of the memristor devices, which acts as a resistor and provides a current that is proportional to the value of the resistance. The current is sensed by the sense amplifier, which outputs the corresponding value. By enabling multiple wordlines simultaneously, the current will be proportional to the equivalent resistance on the path, performing analog multiply-and-accumulate operations that are useful in applications like neural networks.

The categories explained so far can execute simple logical or arithmetical computations in a highly parallelized fashion. More complex operations must be delegated to an external processing unit: this happens in Near-Memory computing architectures, such as Hybrid Memory Cubes (HMCs), where a processing unit is put very close to the memory. Usually, HMCs are based on DRAM memories, and the intrinsic cell structure is kept unaltered. DRAM arrays are organized in vertically stacked

layers connected utilizing Through Silicon Vias (TSVs) to a logical one [60]. Using TSVs shortens the data path and achieves a very high bandwidth. The concept of Near-Memory and In-Memory computing can also be extended to Single-Instruction-Multiple-Data (SIMD) accelerators as in [61, 47, 62], where SIMD processing units are put very close or inside a memory array. In [47], authors presented an associative processor that replaces the last level of cache, enabling both SIMD computation and storage capabilities at the same time, and [61] realizes a SIMD unit closely connected to a cache, improving parallel computations and enabling re-usability of the design. The architecture is called GP-SIMD [61], optimized to run algorithms made up of highly parallelizable functions that process a vast amount of data (e.g., Machine Learning algorithms). Apart from efficiently performing parallel workloads, GP-SIMD uses a common core to handle also sequential activities, making use of Reduction Tree Interconnections. The GP-SIMD infrastructure solves data synchronization using a regular CPU and a SIMD co-processor that shares two-dimensional memory, providing a collection of bit-serial processing units near the memory array, each associated with a different memory row. These bit-serial processing units (PUs) with In-Memory-like operations contain a full adder (FA), a logic function bit block, and four 1-bit registers. Together with a modified SRAM structure, the GP-SIMD forms a huge computational memory with SIMD capabilities. The CPU can also launch the SIMD co-processor in a non-blocking way to complete a job while performing tasks that cannot be accelerated by the GP-SIMD in an efficient manner. This co-processor has two components. The Reduction Tree Network connects all processor units directly linked to the shared memory array in the datapath and a microprogrammed sequencer, driven by the CPU, that is used to operate the SIMD array and initiate parallel processes. The CPU processes the remaining sequential sections once the sequencer finishes the requested tasks.

Summarizing, BvNC can be cathegorized in [63, 13]:

- Near-Memory: where a portion of the computing blocks is relocated in the neighborhood of memory. Belonging to this category, there are WIDE-IO2 and 3D stacked DRAM memories [64], HMCs and frameworks like GP-SIMD [61].

- 2. Logic-in-Memory (LiM): three different families belong to this category, differing essentially in the type of computation performed. (1) Computation is performed by physically inserting logic elements inside the memory cell

and LiM array. These elements carry out sparse, distributed, and parallel computation. (2) Memory arrays are themselves used as computation elements. Memory is addressed and provides the result of the computation. Look-Up Tables and CAMs belong to this family. (3) Memory arrays, through analog operations, perform computations on data. These arrays can be SRAM, DRAM, or Non-Volatile Memories (NVM) especially based on emerging resistive technology.

#### A note about MemComputing

One approach that has been gaining popularity is MemComputing (https://www. memcpu.com/). Like the approaches reported earlier, processing and storage occur in the same physical location [65]. Taking inspiration from the human brain model of computation, MemComputing-based machines are able to self-organize, building the solution pathway themselves, in fact, calculations are performed on devices that exhibit properties of temporal non-locality, thus having memory. Memristors [66] (but also Memcapacitors and Meminductors), for example, are mainly used in this type of approach because, in addition to storing data, they are capable of performing calculations that, as mentioned earlier, are based on current/voltage measurements, which can vary because of their inherent ability to reprogram their intrinsic state values (resistance, capacitance or inductance). MemComputing machines have essential differences from classical von Neumann machines, and their main characteristics are intrinsic parallelism, i.e. all the MemComputing units (or MemProcessors) work simultaneously; functional polymorphism, i.e., the ability to compute different functions without changing the network topology; and information overhead, i.e., the ability of a network of interconnected and interacting MemProcessors to store more information than the same number of non-interacting MemProcessors. Because of its computational capabilities, MemComputing can be used to solve non-polynomial (NP) problems in polynomial time. The number of MemProcessors in solving NP problems in polynomial time can increase exponentially or linearly if they take advantage of the information overhead property, as demonstrated in the article [65]. These kinds of solutions are proposed in works such as [65], which implements the algorithm of the subset sum problem, i.e., locating a subset of integers that form exactly a given sum value. The authors propose a detailed explanation and mathematical modeling of the MemComputing approach, providing an ideal implementation with a DCRAM (Dynamic Computing Random Access Memory), which is a memory composed of MemCapacitors [67], which has an infinite set of states and thus implements analog rather than digital memory cells. Computations are implemented within memory by simply taking advantage of row and column activations; by applying the activation signal to the different rows, the MemProcessors change their state according to the chosen operation, thus promoting massively parallel computations with the application of a small number of input control signals by implementing, in this specific case, sum or, similarly, data movement operations within the array. By taking advantage of these operations, the DCRAM array is able to implement the subset sum problem algorithm in n-1 iterations. However, this approach requires an exponential number of MemProcessor, as it does not exploit the information overhead. Therefore, a second solution to the subset sum problem [68] is proposed, exploiting the Discrete Fourier Transform (DFT) algorithm. Considering a subset of integers  $G = \{a1, a2, ..., an\}$  and the following formula:

$$g(x) = -1 + \prod_{j=1}^{n} \left( 1 + e^{i2\pi a_j x} \right)$$

(1.1)

And by expanding the products as  $e^{i2\pi x \sum_{j \in P} a_j}$ , the function g(x) contains all the sums of all possible subsets of G. Now applying the Fourier transform to the function g(x) as:

$$F(f_h) = \frac{1}{N} \sum_{k=1}^{N} g(x_k) e^{i2\pi f_h x_k}$$

(1.2)

The spectrum of this function will exhibit peaks at values of  $f_h$ , where  $f_h$  are the values of the sums and the amplitude of the harmonics is equal to the number of subsets of G. This type of implementation is definitely different from those presented so far, in fact it does not include the use of a memory array to implement computations, but still exploits the concept of nontemporal locality to perform NP algorithms in polynomial time. Another attractive MemComputing-based solution to an NP-Complete algorithm is the one proposed in [66], in which the authors implement a memristor-based MemComputing architecture that solves the Ant Colony problem, consisting of finding the most convenient path within a maze. The maze can be reduced to a graph, and a similar method to the one used by the ants is used to find the path. The flow of ants, in fact, can be analogized to a stream of electric current flowing through memristors that, in turn, model the physical system. If, for example, there are two paths leading from point A to a point B, where

$L_2 = 2L_1$ , the equivalent model will be two parallel branches of memristors, where in the first branch, there will be only one memristor, and in the second branch there will be two memristors in series. By applying a constant current to this circuit, the conductance of the devices, as time changes, will change by modeling the amount of pheromones within the two paths, all done in a single algorithmic step.

A nexus with classical logic MemComputing is a completely different way of performing computation based on a physical system that exploits temporal nonlocality, so it is a much broader physical concept that can also be applied in classical logic as we currently know it. As shown in [69], an OR port can be transformed into a MemComputing OR port by transforming its digital inputs into continuous variables (e.g., voltages and currents) and, along with them, also "memory variables" are associated. The OR gate, in the digital domain, has 4 different equilibrium states that are analogous to local minimum points in the analog world. By associating memory variables, it is possible to transform these local minimum points into saddle points, where MemComputing performs computations in search of equilibrium. Logic gates used in MemComputing are therefore named Self-Organized Logic Gates (SOLGs) [70], and are devices whose terminals can be either input or output, so the current can flow in both directions. Within a SOLG, Dynamic Correction Modules (DCMs) ensure the Boolean satisfiability of the logic gate. By combining multiple SOLGs, a SOLC (Self-Organized Logic Circuit) [71] can be constructed, and because of the ability of the current to flow in both directions, a SOLC can "run in reverse," solving problems that are simpler in the opposite direction (e.g., Prime Factorization). Starting with SOLCs, Self-Organized Algebraic Gates (SOAGs) [72] were developed, which are based on the same principle of operation as SOLCs. However, this time they self-organize to model algebraic expressions, aiming to solve problems such as Integer Linear Programming. In [72], the authors compared a solution implemented with SOAGs using the MemCPU solver with Gurobi 8.0, which is a commercial solver of mathematical programming problems based on classical computation, showing that the MemComputing approach was able to find much better solutions, regardless of size and structures, and, for some of these, MemCPU's convergence was extremely faster than Gurobi 8.0 (5 minutes vs. > 1 hour). The MemComputing paradigm turns out to be very efficient in solving NP problems due to the use of memory variables and the ability of the circuit to reorganize itself. This concept, however, differs from what has been covered so

far in that one does not necessarily have a memory array in which computation takes place, but instead exploits the memory that certain devices possess to perform computations: quoting the article [69], "By memory, however, I don't mean storage, but rather time nonlocality - the ability of a physical system to remember its past dynamics in order to perform necessary tasks." The concept of BvNC covered in this thesis refers to computation devices composed of memory elements or arrays connected to computation logic to keep as much data as possible thereby reducing communication with the CPU.

#### **1.1.2 BvNC application example: neural networks**

The BvNC technique is used most often in the acceleration of neural networks (NN). A NN is a computational model capable of carrying out highly difficult assignments. It is made up of "neurons," which are the fundamental building elements; by arranging these "neurons" in an interconnected network, the NN can make decisions and potentially learn from its mistakes [73].

Fig. 1.3 Schematic of a neuron. Example with 9 inputs.

The diagram shown in Fig. 1.3 provides a good illustration of an artificial neuron. It is composed of two primary components, which are *net*, which is in charge of computing the weighted sum, and f(net), which is an activation function applied to the output. In most cases, the term *net* is expressed as follows:

$$net = \sum_{i=0}^{N} I_i \times W_i + \text{Bias}$$

(1.3)

Fig. 1.4 Convolution computation example with a  $3 \times 3$  kernel.

Fig. 1.5 Structure of LeNet 5 CNN [6], composed of 2 convolutional, 2 pooling and 3 fully connected layers and their sizes are indicated in the model.

Where  $I_i$  is the input value,  $W_i$  is the corresponding weight and Bias is an additive term. Weights and biases can be adjusted to achieve the desired output with a procedure called training. Usually, the activation function is non-linear. The most important activation functions are Rectified Linear Unit (ReLU), hyperbolic tangent (tanh), and the sigmoid function [74]. NNs are made up of layers composed of a set of arranged neurons and the most common structures that can be found in the literature are Convolutional Neural Networks [6, 75] (CNNs) and Multi-Layer Perceptrons (MLP). In CNNs, convolutional layers perform the convolution operation of the input feature map (IFMAP) with a set of weights called kernels. An example of a convolution computation is depicted in Fig. 1.4: the parameters to take into account in a convolution are the weights, the input feature map to be convolved, and the stride. After the first convolution, the kernel window is moved by a step equal to stride, and a new convolution can start. As it is possible to notice by this tiny example, the convolution computation perfectly matches the equation of the neuron reported in Equation 1.3, in which usually an activation function is applied to normalize the results obtained. A real example of a CNN is the LeNet 5 [6], in which all the

convolutional layers have the same kernel size of  $5 \times 5$  pixels. The first one produces 6 output feature maps (OFMAPs), meaning that the same IFMAP is convolved with 6 different kernels. The second convolutional layer instead produces 16 OFMAPs, starting from 6 IFMAPs: for each input, 16 kernels produce 16 outputs, so 16 from the first IFMAP, 16 for the second IFMAP and so on, implying a total number of OFMAPs equal to  $6 \times 16$ . These considerations bring to the general formulation of convolution in a convolutional layer, derived from [76, 13]:

$$y_o(j,i) = Bias_o + \sum_{c_{in}=0}^{\#C_{in}-1} \sum_{k=0}^{W_y-1} \sum_{p=0}^{W_x-1} W_{o,c_{in}}(k,p) \times I_{o,c_{in}}(j \times s + k, i \times s + p)$$

(1.4)