## POLITECNICO DI TORINO Repository ISTITUZIONALE

Analysis of the impact of prototypingrelated parasitic effects in a hybrid GaN power amplifier for 5G FR1 applications

Original

Analysis of the impact of prototypingrelated parasitic effects in a hybrid GaN power amplifier for 5G FR1 applications / Bartolotti, Giulia; Zhang, Zhifan; Shi, Peiyuan; Piacibello, Anna; Camarchia, Vittorio. - In: INTERNATIONAL JOURNAL OF NUMERICAL MODELLING-ELECTRONIC NETWORKS DEVICES AND FIELDS. - ISSN 0894-3370. -ELETTRONICO. - 37:1(2024). [10.1002/jnm.3143]

Availability: This version is available at: 11583/2980183 since: 2023-07-11T06:48:16Z

*Publisher:* Wiley

Published DOI:10.1002/jnm.3143

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

DOI: 10.1002/jnm.3143

#### INVITED ARTICLE

WILEY

# Analysis of the impact of prototyping-related parasitic effects in a hybrid GaN power amplifier for 5G FR1 applications

Giulia Bartolotti | Zhifan Zhang | Peiyuan Shi | Anna Piacibello 🖻 | Vittorio Camarchia 🖻

Department of Electronics and Telecommunications, Politecnico di Torino, Torino, Italy

#### Correspondence

Anna Piacibello, Department of Electronics and Telecommunications, Politecnico di Torino, Corso Duca degli Abruzzi 24, 10129 Torino, Italy. Email: anna.piacibello@polito.it

#### Funding information

Project Programma Operativo Nazionale (PON) Ricerca e Innovazione "Tecnologie abilitanti e architetture innovative per future generazioni (6G) di trasmettitori intelligenti green", Grant/Award Number: E15F21003760001; Italian Ministry of Universities and Research (MUR)

#### Abstract

This article analyses the impact of parasitic effects encountered in the manufacturing of a Gallium Nitride power amplifier optimized for a specific trade-off of efficiency and linearity at 5G FR1 frequencies. The analysis focuses on an example based on a packaged transistor and implemented in hybrid technology, adopting a two-layer printed circuit board for passive distributed elements and surface-mount lumped components. The design is summarized, and the focus is then posed on the comparison of simulated and measured results, the main causes of inaccuracy in their agreement, and a simple way of reproducing these in simulation. The mechanical stability of the assembly and the sensitivity of the second harmonic control are identified as the main sources of performance degradation. These effects are correctly modeled at the simulation level thanks to the insertion of specific parasitic lumped elements but could not be fully eliminated at the experimental level in this specific prototype. However, post-tuning performed on the prototype, guided by the proposed analysis, still allows to reach satisfactory performance although somewhat sub-optimal compared to the one expected from simulations. At 3.5 GHz, the re-tuned PA demonstrates a measured output power in excess of 37.5 dBm at saturation, with associated gain higher than 14 dB and PAE of 60%. In a 2-tone test with 20 MHz spacing, the IMD3 remains lower than -30 dBc up to 29 dBm of output power with a corresponding PAE of the order of 32%.

#### **KEYWORDS**

5G, efficiency, gallium nitride, intermodulation distortion, linearity, power amplifier

### **1** | INTRODUCTION

The performance of transmitters in wireless communication systems is significantly influenced by that of the power amplifier (PA), and designers in this field face the constant challenge of balancing efficiency and linearity. This challenge has become increasingly crucial in recent years due to the frequency spectrum becoming more crowded, which

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

© 2023 The Authors. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields published by John Wiley & Sons Ltd.

## <sup>2 of 13</sup> WILEY-

has resulted in the adoption of very complex modulation signals to optimize the amount of information that can be carried out in a limited frequency band.

Recent modulations used in wireless communications are characterized by a high peak-to-average power ratio (PAPR), which causes the PAs to operate at an average power much lower than their maximum output power. Consequently, average efficiency is adversely affected, especially in standard amplifier architectures such as single-device amplifiers,<sup>1–4</sup> as well as balanced,<sup>5</sup> distributed,<sup>6,7</sup> and other similar PA architectures that typically attain maximum efficiency at saturation and drop rapidly away from it in output power back-off (OBO).

To address this issue, specific back-off efficiency enhancement techniques have been proposed and developed over the years. These techniques, such as load modulation<sup>8–12</sup> and supply modulation,<sup>13–16</sup> have shown great potential for improving efficiency in OBO. It is sometimes the case that these techniques are both applied to the same PA, such as in.<sup>17–19</sup> However, their implementation poses several challenges and may also complicate the inherent linearity of the PA and its ability to be linearized.

The linearity of the PA may be a more or less stringent requirement compared to other performance indicators such as output power, operating bandwidth, gain, and efficiency, depending on the targeted application.<sup>20</sup> While linearization solutions such as predistortion<sup>21-24</sup> or dual-input architectures<sup>12,25,26</sup> can enhance linearity and make it compatible with standards, they can also make PA circuit design more challenging. However, in some cases, it is essential to design a PA that is intrinsically compliant with stringent linearity requirements.

Another critical aspect is the sensitivity of the designed PA to several parameters, such as the bias voltage variations, the operating temperature,<sup>27</sup> the tolerance on the components' values, including the accuracy of the nonlinear model of the active devices,<sup>28–31</sup> and the variability that affects the manufacturing process. In general, hybrid implementations are affected by a stronger variability, related to manual manufacturing and assembly and to the adoption of off-the-shelf components, but allow for a re-tuning of the circuit after the manufacturing to correct possible shifts. Also, the spacing of the transistors and the overall larger circuit size often allow for better heat dissipation thus limiting the temperature sensitivity of the amplifier. On the contrary, the production process of monolithic integrated circuits is more repeatable, although affected by a certain amount of variability, but it allows little or no tuning after manufacturing<sup>32,33</sup> and is typically more sensitive to temperature variations due to the high power density per chip area and the more challenging heat dissipation. The complexity of the architecture, that is, the number of active devices, the presence of integrated driver stages, the spatial proximity of the active devices<sup>34,35</sup> and the presence or absence of isolating elements among them, has also an impact on its sensitivity. For instance, the single-device wideband PA of<sup>36</sup> presents a very good agreement between the target and the obtained frequency band, whereas the two-stage Doherty PA with embedded drivers presented in<sup>37</sup> is affected by a 2-GHz frequency shift. It allows however to fully cover the targeted band thanks to a specific wideband design approach.

The object of this paper is to analyze the parasitic effects related to the prototyping of a single-device class-AB PA and, once identified, to find a simple way of reproducing these effects at the circuit simulation level. The PA has been designed to maximize efficiency while satisfying stringent output power and linearity constraints around 3.5 GHz, targeting 5G applications in the FR1 frequency bands. The design targets are based on the rules imposed by the 2022 student design competition on high efficiency PAs held at the International Microwave Symposium. The PA should satisfy two main requirements, namely achieving an output power in the range 4–40 W in a single-tone test with input power lower than 24 dBm, and maximizing the PAE while maintaining all inter-modulation products below -30 dBc in a two-tone test with 20 MHz tone spacing.<sup>38</sup> The adopted design methodology is based on source and load pull simulations, at fundamental and second harmonic frequencies, aided by the identification of the parameters to which each of the targeted performance is more sensitive.

The PA has been initially fabricated with nominal component values and the experimental characterization in these conditions has evidenced the presence of a frequency shift in the small signal parameters (of about 250 MHz toward lower frequencies) and a slight degradation of the large signal performance at medium-high power. The PA has been shown to achieve, without any post-tuning, a measured output power of about 38 dBm and PAE in excess of 70% in a single-tone test at 3.25 GHz. It also achieves a 33% PAE at the -30 dBc third-order intermodulation distortion (IMD3) point in the 20 MHz two-tone test.<sup>38</sup>

A re-tuning of the parameters was carried out based on the scattering parameters of measurements, resulting in an enhancement of both small and large signal performance. However, despite these improvements, some performance discrepancies, particularly in terms of IMD3 profile at medium-high power, remain. By accurately modeling the deviations from the ideal behavior at the simulation level, we were able to identify the main sources of inaccuracy, namely the mechanical robustness of the assembly and the sub-optimal control of the second harmonic frequency. All in all,

the performed analysis leads to conclude that the design frequency was too high, and the corresponding second harmonic range too close to the reliability limits of the adopted technology and manual assembly, to allow for a fine tuning of the large signal performance that could also be robust and repeatable. These aspects will be analyzed and discussed in detail in the following Sections.

### 2 | DESIGN AND IMPLEMENTATION

The class-AB PA is designed at  $f_0 = 3.5$  GHz, for a hybrid implementation targeting 5G applications, based on the 6 W packaged gallium nitride (GaN) high-electron-mobility transistor (HEMT) (CGH40006P) from Wolfspeed. The design specifications and detailed procedure are described in Reference 38 and briefly recalled here for completeness.

The active device is stabilized in and out of the operating frequency band thanks to a parallel RC ( $R_2 \parallel C_4$ , 150  $\Omega \parallel$  1.4 pF) network on the gate and a shunt R ( $R_1$ , 120  $\Omega$ ) along the gate bias path. The stability is verified at bias conditions around class-B and deep class-AB (i.e.,  $V_{GS}$  ranging between -3.2 V and -2.9 V), since this design strongly relies on the exploitation of the IMD3 sweet spots.

Source and load terminations are optimized at fundamental and second harmonic neglecting higher-order harmonic components marginally affecting the amplifier performance. Baseband impedances are monitored and optimized as well for their impact on IMD3. More in detail, the optimization of the various parameters can be partially decoupled. The selection of the optimum load at the fundamental frequency is a trade-off between IMD3 and PAE requirements. On the other hand, the IMD3 is deeply affected by the baseband termination, which has almost no impact on the output power at the fundamental, gain, and PAE in the 1-tone test. Finally, an additional constraint in the design is represented by the minimum gain (and corresponding minimum  $P_{out,f_0}$ ) of the stage, mainly impacted by the load at the fundamental and input matching section.

The selected loads assure in simulation an IMD3 below -30 dBc, simultaneously satisfying the constraints of minimum output power with a margin of about 1 dB, to account for the passive networks losses and manufacturing inaccuracies.

Both Output (OMN) and Input (IMN) Matching Networks (MNs) are designed as a cascade of the  $2f_0$  harmonic control and of the  $f_0$  matching section. The baseband termination is optimized by tuning the DC decoupling capacitors in the supply lines. The prototype is manufactured on a Rogers 4350b substrate (3.66 relative dielectric constant, 0.762 mm substrate thickness, and 35 µm metal thickness).

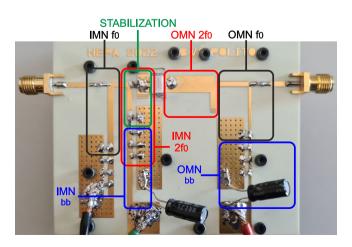

The photograph of the realized prototype is shown in Figure 1, where the structure of the MNs is highlighted.

### 3 | RESULTS

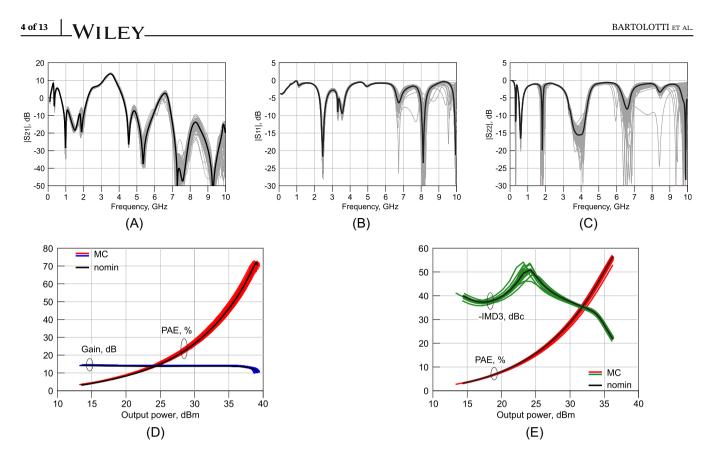

The simulated performance expected from the amplifier is reported in Figure 2, where a sensitivity analysis versus process, voltage and temperature variations is also performed. The performance clouds refer to a Monte Carlo simulation

FIGURE 1 Photograph of the manufactured PA, where the stabilization and the IMN and OMN structures are highlighted.

**FIGURE 2** Simulated small and large signal performance of the designed amplifier (circuit v0) including process variability: (A)  $S_{21}$ , (B)  $S_{11}$ , (C)  $S_{22}$ , and (D) 1-tone at 3.5 GHz and (E) 2-tone at 3.5 GHz with 20 MHz tone spacing. The solid black curves refer to the nominal performance, that is, without any statistical variability. The curves in other colors in each figure refer to the Monte Carlo simulation, labeled as MC.

with 100 iterations. The transistor and SMDs parameters vary according to the statistics provided by the manufacturer in the model library, and the transmission lines dimensions have a user-defined variation that approximately represents the accuracy of the adopted manufacturing process. The temperature and voltage variations are assumed to be limited within 20% and 5%, respectively, based on the assessment of the adopted setup. The black curves indicate the reference nominal performance when no statistical variability is considered in the simulation.

At 3.5 GHz, the designed PA can provide a saturated output power in excess of 38 dBm with an associated PAE of 70%, while maintaining the required linearity in the 2-tone test up to an output power of 35 dBm and a PAE of 50%. The simulations accounting for the parameters variability evidence that the small signal performance is most sensitive to the variations at high frequency, near the second harmonic range, which translates into a maximum PAE variation of about 8%. The 2-tone test shows a similar variability in terms of PAE and sensitivity of the IMD3 that is more marked in the low-medium power region, where the sweet spot is located. On the contrary, the -30 dBc IMD3 crossing is only slightly affected (around 1 dB variation in the output power point corresponding to the crossing).

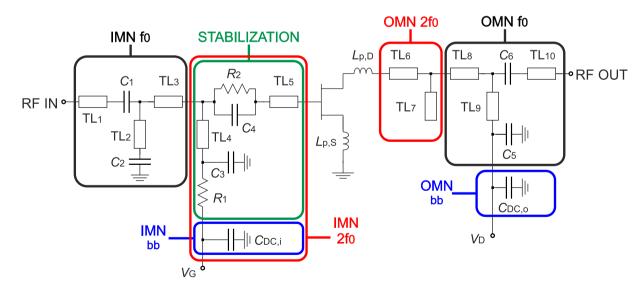

The PA has been mounted with the nominal values for transmission lines (TLs), surface-mount devices (SMDs) and edge launchers. The nominal values summarized in Table 1 refer to the equivalent circuit schematic of Figure 3, where TL<sub>i</sub> has physical width  $W_i$  and length  $L_i$  indicated in mm and the values of resistor  $R_i$  and capacitor  $C_i$  are specified in  $\Omega$  and pF, respectively. Note that the low-frequency decoupling capacitors and the input and output 50  $\Omega$  lines are omitted in the schematic. Additionally,  $L_{p,S}$  and  $L_{p,D}$ , specified in nH, represent parasitic inductive effects at the Source and Drain terminals. They are initially assumed to be null, and more details will be provided in the following.

The small signal characterization has been performed in terms of scattering parameters of the amplifier considered as a two-port double bipole, where port 1 is the input (RF IN) and port 2 is the output (RF OUT). The experimental test-bench adopts a 2-port Keysight VNA (E8361A), calibrated at the DUT planes by means of a short-open-load-thru (SOLT) calibration procedure.

The placement of the calibration planes has been considered when comparing measurements and simulations; the presence of the edge launcher amounts to a shift of approximately 20° from the PCB edge. However, this shift has a

**TABLE 1** Values of the nominal passive components relative to the schematic of Figure 3.

| Network                             | Parameter                           | Units  | <b>v0</b>   |

|-------------------------------------|-------------------------------------|--------|-------------|

| IMN, $f_0$                          | $W_1, L_1$ (TL <sub>1</sub> )       | mm, mm | 0.97, 5.7   |

| $IMN, f_0$                          | $W_2, L_2$ (TL <sub>2</sub> )       | mm, mm | 1.8, 18.6   |

| $IMN, f_0$                          | $W_3, L_3$ (TL <sub>3</sub> )       | mm, mm | 1.48, 3.68  |

| IMN, 2 <i>f</i> <sub>0</sub>        | $W_4, L_4 (\mathrm{TL}_4)$          | mm, mm | 1.63, 8.5   |

| IMN, 2 <i>f</i> <sub>0</sub>        | $W_5, L_5 (\mathrm{TL}_5)$          | mm, mm | 6.3, 4      |

| OMN, 2 <i>f</i> <sub>0</sub>        | $W_6, L_6 (\mathrm{TL}_6)$          | mm, mm | 5.27, 14.17 |

| OMN, 2 <i>f</i> <sub>0</sub>        | $W_7, L_7 (\mathrm{TL}_7)$          | mm, mm | 1.63, 4.4   |

| $OMN, f_0$                          | $W_8, L_8 (\mathrm{TL}_8)$          | mm, mm | 1.3, 9.54   |

| $OMN, f_0$                          | $W_9, L_9 (\mathrm{TL}_9)$          | mm, mm | 0.9, 16     |

| $OMN, f_0$                          | $W_{10}, L_{10} (\mathrm{TL}_{10})$ | mm, mm | 1.16, 4.68  |

| $IMN, f_0$                          | $C_1$                               | pF     | 47          |

| $IMN, f_0$                          | $C_2$                               | pF     | 2.7         |

| Stabilization                       | <i>C</i> <sub>3</sub>               | pF     | 3.3         |

| Stabilization                       | $C_4$                               | pF     | 1.4         |

| $OMN, f_0$                          | $C_5$                               | pF     | 3.3         |

| $OMN, f_0$                          | $C_6$                               | pF     | 47          |

| IMN, bb                             | $C_{ m DC,i}$                       | pF     | 33          |

| OMN, bb                             | C <sub>DC,o</sub>                   | pF     | 100         |

| Stabilization                       | $R_1$                               | Ω      | 120         |

| Stabilization                       | $R_2$                               | Ω      | 150         |

| Parasitic effect at Source terminal | $L_{\mathrm{p,S}}$                  | nH     | 0           |

| Parasitic effect at drain terminal  | $L_{\mathrm{p,D}}$                  | nH     | 0           |

FIGURE 3 Schematic of the designed PA, where the stabilization and the IMN and OMN structures are highlighted.

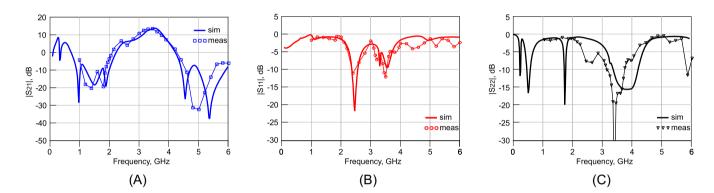

negligible effect on the simulated large signal performance. Therefore, for the sake of conciseness, only the magnitudes of the scattering parameters will be shown in the following discussion. The resulting measurements (thin lines with symbols) are compared to the simulated ones (thick solid lines) in Figure 4. Such simulation runs on the circuit v0, which illustrates the originally designed behavior. A shift toward lower frequencies in the position of the main peak of

FIGURE 4 Comparison of measured (symbols) scattering parameters and simulations on circuit v0 (solid): (A) S<sub>21</sub>, (B) S<sub>11</sub>, and (C) S<sub>22</sub>.

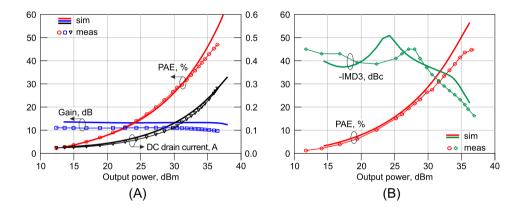

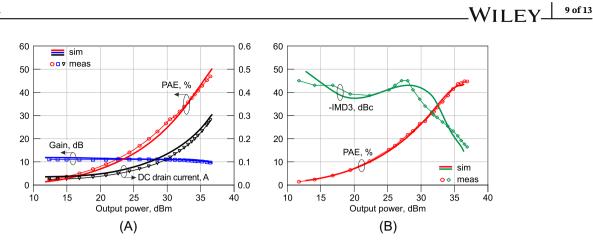

FIGURE 5 Comparison of measured (symbols) large signal performance and simulations on circuit v0 (solid): (A) 1-tone and (B) 2-tone with 20-MHz spacing.

$S_{21}$  can be observed, of about 250 MHz. Additionally, the agreement is deteriorated above 5 and 6 GHz, both in terms of gain and input/output return losses. This is partially expected, since the guaranteed operating range of both substrate and transistor only extends up to 6 GHz.

The 1-tone large signal characterization is performed on a real-time vector bench calibrated through a two-step procedure: a two-port SOLT for the relative calibration compared to a reference, followed by a SOL calibration at an extended output port connected to a power meter for the absolute power calibration. As expected, the comparison between simulations and measurements at the design frequency of 3.5 GHz does not present a very good agreement, due to the shift observed in the scattering parameters both at the input and at the output. In particular, as shown in Figure 5A the power gain is lower, and so are the saturated output power and efficiency at the similar gain compression. Note that the full PA characterization has not been performed in strong compression due to the maximum input power imposed by the design requirements.

The linearity of the stage is evaluated by measuring the IMD3 in a two-tone test with 20 MHz tone spacing.<sup>39</sup> Even if other metrics are available, such as AM-AM and AM-PM distortion<sup>40</sup> or more sophisticated system-level metrics (adjacent channel power ratio, noise-to-power ratio<sup>41</sup>), they are often adopted to benchmark the linearity of the amplifier in real field conditions, while the two-tone test is mainly adopted during the design phase as an initial estimation of the linearity.

The 2-tone large signal characterization adopts a two-locked source 4-port Keysight VNA (N5227A). Figure 5(B) reports the IMD3 (with opposite sign, for convenience) and PAE curves and highlights the similar discrepancy as observed in the 1-tone performance. The measured PAE at medium-high power is lower than predicted by simulations, and the IMD3 has a different trend altogether, across the whole power sweep. All in all, the PAE at -30 dBc IMD3 results of 30% in measurements, compared to the 48% expected from simulations. Since the IMD3 is very sensitive to  $V_{\text{GS}}$  variations, especially in deep class AB, the measurements have been repeated at several bias conditions. It has been

TABLE 2 Values of the passive components modified in the circuit versions v1 and v2.

| Parameter                                 | Units  | v0          | v1          | v2          |

|-------------------------------------------|--------|-------------|-------------|-------------|

| $\mathrm{TL}_{2}\left(W_{2},L_{2}\right)$ | mm, mm | 1.8, 18.6   | 1.8, 19.6   | 1.8, 19.60  |

| $\mathrm{TL}_4\ (W_4,L_4)$                | mm, mm | 1.63, 8.5   | 1.63, 9.5   | 1.63, 9.5   |

| $\mathrm{TL}_{5}\left(W_{5},L_{5}\right)$ | mm, mm | 6.3, 4      | 6.3, 6      | 6.3, 6      |

| $\mathrm{TL}_{6}\left(W_{6},L_{6}\right)$ | mm, mm | 5.27, 14.17 | 5.27, 17.17 | 5.27, 17.17 |

| $\mathrm{TL}_{7}\left(W_{7},L_{7}\right)$ | mm, mm | 1.63, 4.4   | 1.63, 5.4   | 0.93, 5.4   |

| $L_{\rm p,S}$                             | nH     | 0           | 0           | 0.1         |

| $L_{\rm p,D}$                             | nH     | 0           | 0           | 0.5         |

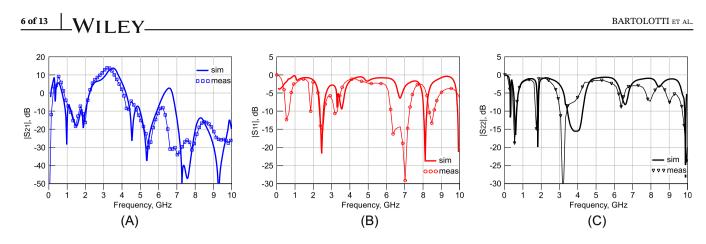

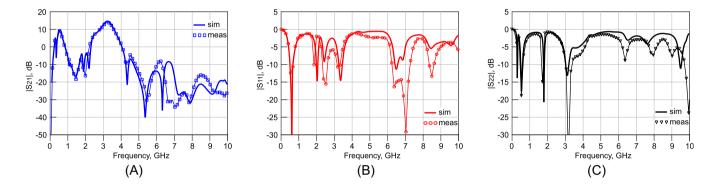

FIGURE 6 Comparison of measured (symbols) scattering parameters and simulations on circuit v1 (solid): (A) S<sub>21</sub>, (B) S<sub>11</sub>, and (C) S<sub>22</sub>.

verified that the position and depth of the sweet spot can be varied, but the performance at medium-high power remains almost unchanged.

Attempts at re-tuning have been done by modifying the size of the transmission lines and stubs, as well as the values of the SMDs of the demonstrator. The main guide adopted to evaluate improvements in the agreement during this procedure has been the scattering parameters. It has been observed that the frequency shift of the  $S_{21}$  peak can be recovered, and all the  $S_{ij}$  scattering parameters (with i, j = 1, 2) can be brought to a good agreement with simulations up to 5–6 GHz. The resulting 1-tone performance is also in good agreement, but the 2-tone one is not. However, circuit optimization and re-tuning based on 2-tone measurements are rather unpractical.

Therefore, the goal of the investigation detailed in this article is a reverse procedure, based on the modification of the circuit in simulation to reproduce the performance obtained during the measurement campaign and hence gain some insight into the sources of disagreement.

As the first step, the original circuit (v0) has been modified to get the best agreement in terms of scattering parameters (v1). The modifications to the circuit are those highlighted in Table 2. The most sensitive parts are the lines closest to the active device ( $TL_5$ ,  $TL_6$ ) and the stubs ( $TL_2$ ,  $TL_4$ , and  $TL_7$ ), especially the ones that implement the second harmonic control. The effective length of the lines toward the device may be affected by inaccurate modeling of the position of its reference planes as well as the precision of the PCB cut where the package is inserted. The main source of length shift for the capacitor-terminated stubs, instead, is the position in which the capacitor is soldered, whereas deviations of the actual capacitance away from the nominal value have a lesser impact.

The resulting scattering parameters are reported in Figure 6. It can be noted that the  $S_{21}$  behavior in the band can be perfectly captured and that all the positions of the secondary resonances of all parameters can be very well reproduced up to 9 GHz, which fully includes the second harmonic range ( $2f_0 = 7$  GHz). The agreement in terms of magnitude above 6 GHz is better for  $S_{11}$  and  $S_{22}$ , whereas the magnitude of  $S_{21}$  is still affected by a partial disagreement, which could not be recovered.

The corresponding large signal performance of circuit version v1 is shown in Figure 7. The 1-tone simulated performance (Figure 7(A)) has become more in line with the measured one in terms of gain, whereas the saturated power is still around 1.5 dB higher, with a consequent difference of 10% points in the maximum PAE. The agreement in the

7 of 13

WILEY⊥

8 of 13

FIGURE 7 Comparison of measured (symbols) large signal performance and simulations on circuit v1 (solid): (A) 1-tone, and (B) 2-tone with 20-MHz spacing.

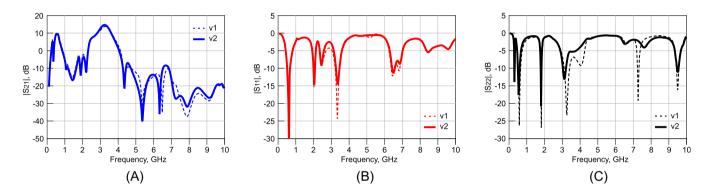

FIGURE 8 Comparison of simulated scattering parameters of circuit v2 (thick solid) and v1 (thin dashed): (A) S<sub>21</sub>, (B) S<sub>11</sub>, and (C) S<sub>22</sub>.

2-tone simulated performance (Figure 7(B)), on the other side, has significantly improved in terms of PAE, but the IMD3 curve has assumed a very different trend. Two sweet spots are now present, and the slope of the curve near saturation has become steeper. The resulting simulated PAE at -30 dBc IMD3 is now 42%.

Then, the circuit has been further modified to get the best agreement in terms of 2-tone performance (v2), while ensuring that the agreement of the scattering parameters is not compromised at least in the working band. The modifications to the circuit are highlighted in Table 2. This only required modifications to the OMN, in particular to the stub that implements the  $2f_0$  control, whereas the rest of the MNs is unchanged. The passive circuit is however modified to include parasitic effects at the source and drain of the transistor. The possible cause of these inductive parasitic effects has been identified in a circuit assembly that is not so mechanically stable. For instance, air gaps below the device package (main body and flanges) may have such effect. These inductances have proven to have a strong effect on linearity. Finally, a slight tuning of the gate bias voltage was also required, from -3.08 V to -3.03 V. A similar modification of the bias is most likely unfeasible in a real experimental setup, where the resolution of the power supply unit cannot allow this fine tuning. A possible practical implementation compatible with this range of variation would require the insertion of ad-hoc trimmers on the bias lines.

The resulting scattering parameters are reported in Figure 8, where they are compared to the ones of circuit version v1 (dashed lines). It can be noted that:

- 1.  $S_{11}$  is almost unchanged, compatibly with a modification that only affected the OMN;

- 2.  $S_{22}$  is slightly modified around the operating frequency (3–4 GHz), where the mismatch increases, and most noticeably modified around the  $2f_0$  range (6–8 GHz), where a shift in the position of a local minimum is clearly visible; and

- 3. consequently,  $S_{21}$  is mainly unchanged until 6 GHz, apart from a small difference in the gain at  $f_0$ , and varies primarily from 6 GHz to 8 GHz.

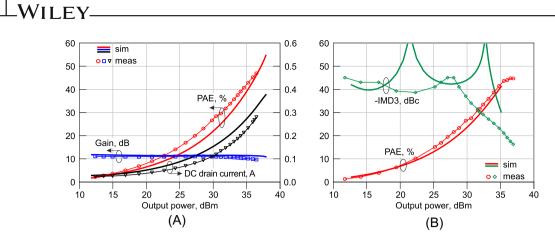

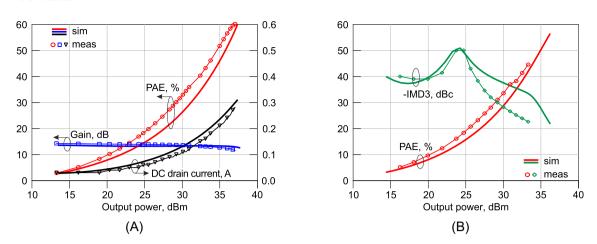

FIGURE 9 Comparison of measured (symbols) large signal performance and simulations on circuit v2 (solid): (A) 1-tone and (B) 2-tone with 20-MHz spacing.

**FIGURE 10** Comparison of re-tuned measured (symbols) scattering parameters and simulations on circuit v0 (solid): (A)  $S_{21}$ , (B)  $S_{11}$ , and (C)  $S_{22}$ .

The corresponding large signal performance of circuit v2 is shown in Figure 9. The 1-tone simulations (Figure 9A) now capture very accurately all the performance indicators of interest, namely power gain, PAE, and total DC current consumption. As a consequence, the saturated output power also correctly predicts the measured one.

The agreement in the 2-tone performance (Figure 9B), which is what the circuit modification was based on, is also very good at this stage. The PAE is perfectly captured at all power levels, and the IMD3 curve reproduces with a reasonable degree of accuracy (within 5 dB difference) the measured one, especially in terms of the position of the sweet spot and slope close to saturation. A difference in the PAE at -30 dBc still exists (34% simulated versus the 30% measured one), but this can be considered reasonable since the IMD3 measurement is the one affected by a larger error (approximately 2 dB in the adopted experimental setup) and the model of the transistor may also have some inaccuracy.

Finally, the prototype has been re-tuned based on the outcome of the previous analysis, applying the reverse modifications to the circuit elements highlighted in Table 2. However, no modification was possible to counteract the parasitic elements  $L_{p,S}$  and  $L_{p,D}$ .

The resulting prototype has been experimentally characterized, both in small and large signal conditions. The measured performance is summarized in Figure 10 and Figure 11, where it is compared to the simulations of circuit v0, that is, the expected performance of the originally designed amplifier. The frequency shift of the  $S_{21}$  peak present in the initial version of the prototype is almost fully recovered, and a very good agreement is also obtained in terms of input return loss ( $S_{11}$ ). Some discrepancies are still present in the output return loss ( $S_{22}$ ), which is somewhat expected from the previous analysis. In fact, the re-tuning allows obtaining a very good agreement in terms of large signal performance, especially under 1-tone excitation, despite some differences in the small signal parameters. Finally, the 2-tone performance has also become more in line with the predicted one, despite a difference in the IMD3 slope toward saturation.

**FIGURE 11** Comparison of re-tuned measured (symbols) large signal performance and simulations on circuit v0 (solid): (A) 1-tone and (B) 2-tone with 20-MHz spacing.

| Ref.      | Topology | Freq. (GHz) | Output power (dBm) | Efficiency (%) | Gain (dB) | IMD3 (dBc)     |

|-----------|----------|-------------|--------------------|----------------|-----------|----------------|

| 42        | Doherty  | 2.9–3.3     | 43.9               | 70             | 11        | -              |

| 43        | Class AB | 3           | 35                 | 60             | 13.5      | -30 (@ 34 dBm) |

| 44        | Doherty  | 3.5         | 40                 | 72             | 14        | -30 (@ 40 dBm) |

| 45        | Doherty  | 3-3.7       | 44.2               | 74             | 13        | -              |

| This Work | Class AB | 3.5         | 37.5               | 70             | 14        | -30 (@ 30 dBm) |

TABLE 3 Comparison of the re-tuned class-AB with similar PAs from the scientific literature.

Table 3 summarizes the measured performance of the re-tuned prototype and compares it with similar examples taken from the available scientific literature. Although the re-tuning has not completely restored the expected performance, the PA shows competitive results in line with the state of the art. Note also that the larger signal performance of the re-tuned PA at 3.5 GHz is very similar to the one that it initially showed at 3.25 GHz without any re-tuning, as mentioned in Section 1 and presented in Reference 38.

### 4 | DISCUSSION

The reverse process described in Section 3 has allowed reproducing in simulation the performance modifications observed during the experimental characterization campaign of the hybrid PA. This has been obtained by acting on three main aspects:

- 1. the physical dimensions of the distributed elements in the IMN and OMN;

- 2. the gate bias voltage; and

- 3. the parasitic effects related to the prototype assembly.

On the contrary, post-tuning on the realized prototype to recover the frequency shift based on the comparison of scattering parameters has not allowed to fully replicate in measurement of the performance expected from simulations of the original circuit (v0), although a significant improvement of the performance is observed. The remaining discrepancy can be ascribed mainly to the parasitic effects relative to the prototyping, which could be properly modeled in simulation but could not be removed in the realized hardware. Some further improvement could possibly be obtained by improving the source contact (e.g., with better mechanical control of the carrier roughness, or a more robust mounting), which was not possible to apply to the hardware presented in this work. Note also that these effects could not be taken into account by the sensitivity analysis initially performed (see Figure 2).

The process described in this work suggests that, in a case such as this, the scattering parameters are not a sufficiently good indicator of the conformity of the implemented prototype to the corresponding simulated design. The main reason, in the authors' opinion, resides in the strong effect of the second harmonic control in the specific linearityefficiency trade-off sought here, together with the fact that the second harmonic falls outside of the frequency range where the performance of the adopted transistor and substrate are guaranteed.

In fact, it has been shown that a set of circuit parameters able to perfectly match the small and large signal measurements simultaneously could not be found and that a satisfactory match of the 2-tone large signal performance can be achieved with a set of parameters that do not capture the scattering parameters at  $2f_0$ . Consequently, a post-tuning of the prototype to recover the desired performance would have been possible, if the 2-tone performance were used as a guide instead of the scattering parameters. This, however, is strongly impractical and leads to the conclusion that the proposed class-AB PA has the potential to fulfill the requirements but has a strong sensitivity to many aspects of the prototyping.

Finally, this work has provided experimental evidence that a technology pushed to its frequency limits, such as in this case, is not very robust for designs that aim at maximizing the device performance in a relatively narrow frequency range. The design would result more robust if it aimed to maintain slightly suboptimal performance on a wider frequency band, which however is not in line with the framework for the presented design. On the contrary, if a fine tuning of the termination impedances from the baseband to the second harmonic is targeted, the design frequency should be kept low enough for the whole relevant frequency range to fall well within the range where all the adopted components and their electrical models are reliable.

### 5 | CONCLUSION

The paper has presented a study of the prototyping-related parasitic effects in a single-stage class-AB GaN power amplifier designed to trade off efficiency and linearity and operate in the 5G FR1 frequency range. The analysis is based on the comparison of an initial set of measurements with different sets of simulated results, which model different sources of discrepancy between the expected results and the obtained ones. The most common one, related to the components tolerances and pcb manufacturing inaccuracies, can be successfully recovered thanks to post-tuning. However, this case study also evidences the impact of different aspects related to manufacturing, which cannot be solved a posteriori and would require a full re-design and possibly a different technological implementation. The most critical aspects are identified in the mechanical stability of the assembly and the accuracy of the second harmonic control. As a practical guideline to mitigate the effects of these inaccuracies, it appears very important to ensure good mechanical robustness of the assembly (launchers, device mounting) due to their strong impact on the performance. On the other hand, the operating frequency must be kept far enough from the maximum ratings for the transistor and substrate adopted in the selected implementation, especially if waveform engineering is adopted in the design.

#### ACKNOWLEDGEMENTS

This research was supported by the Project Programma Operativo Nazionale (PON) Ricerca e Innovazione "Tecnologie abilitanti e architetture innovative per future generazioni (6G) di trasmettitori intelligenti green" (DM 1062/21, CUP E15F21003760001) funded by the Italian Ministry of Universities and Research (MUR).

### DATA AVAILABILITY STATEMENT

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### ORCID

Anna Piacibello D https://orcid.org/0000-0001-5007-0005 Vittorio Camarchia D https://orcid.org/0000-0002-7294-6773

### REFERENCES

- 1. Woo YY, Yang Y, Kim B. Analysis and experiments for high-efficiency class-F and inverse class-F power amplifiers. *IEEE Trans Microw Theory Tech.* 2006;54(5):1969-1974. doi:10.1109/TMTT.2006.872805

- Iqbal M, Piacibello A. A 5W class-AB power amplifier based on a GaN HEMT for LTE communication band. 2016 16th Mediterranean microwave symposium (MMS). 2016; 1–4 doi: 10.1109/MMS.2016.7803827

# $\frac{12 \text{ of } 13}{13}$ WILEY-

- Zhou LH, Zhou XY, Chan WS, Sharma T, Ho D. Wideband class-F-1 power amplifier with dual-/quad-mode Bandpass response. *IEEE Trans Circ Syst I: Regul Pap.* 2020;67(7):2239-2249. doi:10.1109/TCSI.2020.2978914

- Piacibello A, Zhang Z, Camarchia V. Continuous Inverse Class-F GaN Power Amplifier with 70% Efficiency over 1.4–2 GHz Bandwidth. 2023 IEEE Topical conference on RF/microwave power amplifiers for radio and wireless applications. Las Vegas, NV, USA 22-25 January 2023; 10–12.

- 5. Lim J, Park C, Koo J, et al. A balanced power amplifier utilizing the reflected input power. 2009 IEEE international symposium on radio-frequency integration technology (RFIT); 2009: 88–91.

- Moon JS, Kang J, Brown D, et al. 100 MHz–8 GHz linear distributed GaN MMIC power amplifier with improved power-added efficiency. 2017 IEEE topical conference on RF/microwave power amplifiers for radio and wireless applications (PAWR). Phoenix, AZ, USA 15-18 January 2017: 40–43.

- Nguyen DP, Nguyen NLK, Stameroff AN, Camarchia V, Pirola M, Pham AV. A wideband highly linear distributed amplifier using intermodulation cancellation technique for stacked-HBT cell. *IEEE Trans MicrowTheory Tech.* 2020;68(7):2984-2997. doi:10.1109/TMTT.2020. 2977642

- Grebennikov A, Bulja S. High-efficiency Doherty power amplifiers: historical aspect and modern trends. *Proc IEEE*. 2012;100(12):3190-3219. doi:10.1109/JPROC.2012.2211091

- 9. Giofrè R, Piazzon L, Colantonio P, Giannini F. Being seventy-five still young: the Doherty power amplifier. *Microw J*. 2012;55(4):72-88. Cited by: 21.

- 10. Pednekar PH, Berry E, Barton TW. RF-input load modulated balanced amplifier with octave bandwidth. *IEEE Trans Microw Theory Tech*. 2017;PP(99):1-11. doi:10.1109/TMTT.2017.2748123

- 11. Shepphard DJ, Powell J, Cripps SC. A Broadband Reconfigurable Load Modulated Balanced Amplifier (LMBA). In: 2017 IEEE MTT-S International Microwave Symposium (IMS). 2017: 947–949.

- Wang W, Chen S, Cai J, Zhou X, Chan WS, Wang G. A compact outphasing power amplifier with integrated reactive compensation. *Microw Opt Technol Lett.* 2020;62(1):137-141. doi:10.1002/mop.32043

- Hanington G, Chen PF, Asbeck P, Larson L. High-efficiency power amplifier using dynamic power-supply voltage for CDMA applications. *IEEE Trans Microw Theory Tech*. 1999;47(8):1471-1476. doi:10.1109/22.780397

- 14. Popovic Z. GaN power amplifiers with supply modulation. 2015 IEEE MTT-S International microwave symposium. 2015; 1-4.

- 15. Duffy MR, Lasser G, Cappello T, Popović Z. Dual gate and drain supply modulation of an X-Band PA. In: 2019 IEEE MTT-S International microwave symposium (IMS). 2019; 979–982.

- Nogales C, Popović Z, Lasser G. A 10-W6-12GHz GaN MMIC Supply Modulated Power Amplifier. In: 2022 52nd European Microwave Conference (EuMC). 2022; 436–439.

- 17. Fishler D, Cappello T, Hallberg W, Barton TW, Popovic Z. Supply Modulation of a Linear Doherty Power Amplifier. In: 2018 48th European Microwave Conference (EuMC). 2018; 519–522.

- Preis S, Wolff N, Lenze F, et al. Load Tuning Assisted Discrete-Level Supply Modulation Using BST and GaN Devices for Highly Efficient Power Amplifiers. In: 2018 IEEE/MTT-S International Microwave Symposium –IMS. 2018; 1230–1233.

- Cappello T, Pednekar P, Florian C, Cripps S, Popovic Z, Barton TW. Supply- and load-modulated balanced amplifier for efficient broadband 5G base stations. *IEEE Trans Microw Theory Tech*. 2019;67(7):3122-3133. doi:10.1109/TMTT.2019.2915082

- Fager C, Eriksson T, Barradas F, Hausmair K, Cunha T, Pedro JC. Linearity and efficiency in 5G transmitters: new techniques for analyzing efficiency, linearity, and linearization in a 5G active antenna transmitter context. *IEEE Microw Mag.* 2019;20(5):35-49. doi:10.1109/MMM.2019.2898020

- 21. Boumaiza S, Ghannouchi F. Realistic power-amplifiers characterization with application to baseband digital predistortion for 3G base stations. *IEEE Trans Microw Theory Tech.* 2002;50(12):3016-3021. doi:10.1109/TMTT.2002.805139

- Quaglia R, Camarchia V, Guerrieri S, et al. Real-time FPGA-based baseband predistortion of W-CDMA 3GPP high-efficiency power amplifiers: Comparing GaN HEMT and Si LDMOS predistorted PA performances. European microwave conference, 2009 (EuMC 2009); Rome, Italy 29 September 2009 - 01 October 2009:342–345.

- Chen W, Lv G, Liu X, Feng Z. Energy-efficient Doherty power amplifier MMIC and beamforming-oriented digital predistortion for 5G massive MIMO application. 2017 IEEE Asia Pacific microwave conference (APMC). Kuala Lumpur, Malaysia 13-16 November 2017; 391–394.

- Haider MF, You F, He S, Rahkonen T, Aikio JP. Predistortion-based linearization for 5G and beyond millimeter-wave transceiver systems: a comprehensive survey. *IEEE Commun Surv Tut.* 2022;24(4):2029-2072. doi:10.1109/COMST.2022.3199884

- 25. Piacibello A, Quaglia R, Camarchia V, Ramella C, Pirola M. Dual-input driving strategies for performance enhancement of a Doherty power amplifier. 2018 IEEE MTT-S international wireless symposium (IWS). 2018; 1–4.

- Cahuana JC, Landin P, Gustafsson D, Fager C, Eriksson T. Linearization of dual-input Doherty power amplifiers. In: 2014 International workshop on integrated nonlinear microwave and millimetre-wave circuits (INMMiC). 2014; 1–3.

- 27. Ramella C, Pirola M, Reale A, et al. Thermal-aware GaN/Si MMIC design for space applications. In: 2019 IEEE international conference on microwaves, antennas, *Commun Electron Syst*; 2019: 1–6.

- Alvaro M, Caddemi A, Crupi G, Donato N. Temperature and bias investigation of self heating effect and threshold voltage shift in pHE-MT's. *Microelectron J* 2005; 36(8): 732–736. doi: 10.1016/j.mejo.2004.11.009

- 29. Santarelli A, Di Giacomo V, Raffo A, et al. Nonquasi-static large-signal model of GaN FETs through an equivalent voltage approach. *Int J RF and Microw Comput-Aided Eng.* 2008;18(6):507-516. doi:10.1002/mmce.20326

- Crupi G, Raffo A, Schreurs DMMP, Avolio G, Vadalà V, di Falco S, Caddemi A, Vannini G Accurate GaN HEMT nonquasi-static largesignal model including dispersive effects. *Microw Opt Technol Lett* 2011; 53(3): 692–697. doi: 10.1002/mop.25757

- Angelov I, Thorsell M, Kuylenstierna D, et al. Hybrid measurement-based extraction of consistent large-signal models for microwave FETs. In: 2013 European Microwave Conference. 2013; 267–270.

- Liu Y, Yuan JS. CMOS RF power amplifier variability and reliability resilient biasing design and analysis. *IEEE Trans Electron Dev.* 2011;58(2):540-546. doi:10.1109/TED.2010.2093141

- Azadmousavi T, Najafi AE. Adaptive body biasing circuit for reliability and variability compensation of a low power RF amplifier. *IEEE Trans Device Mater Reliab.* 2019;19(1):226-232. doi:10.1109/TDMR.2019.2899399

- Resca D, Lonac JA, Cignani R, et al. Accurate EM-based modeling of Cascode FETs. *IEEE Trans Microw Theory Tech.* 2010;58(4):719-729. doi:10.1109/TMTT.2010.2041576

- Ramella C, Piacibello A, Camarchia V, Pirola M. Electro-magnetic Crosstalk Effects in a Millimeter-wave MMIC Stacked Cell. In: 2020 International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits (INMMiC). 2020; 1–3.

- Rubio JJM, Quaglia R, Piacibello A, Camarchia V, Tasker PJ, Cripps S. 3–20-GHz GaN MMIC power amplifier design through a COUT compensation strategy. *IEEE Microw Wirel Compon Lett* 2021; 31(5): 469–472. doi: 10.1109/LMWC.2021.3066282

- Ramella C, Camarchia V, Piacibello A, Pirola M, Quaglia R. Watt-level 21–25-GHz integrated Doherty power amplifier in GaAs technology. *IEEE Microw and Wirel Compon Lett.* 2021;31(5):505-508. doi:10.1109/LMWC.2021.3069555

- Zhang Z, Piacibello A, Camarchia V. Efficiency versus linearity trade-off in an S-band class-AB power amplifier. In: 2023 IEEE topical conference on RF/microwave power amplifiers for radio and wireless applications. 2023; 26–28.

- Clark C, Silva C, Moulthrop A, Muha M. Power-amplifier characterization using a two-tone measurement technique. *IEEE Trans Microw Theory Tech.* 2002;50(6):1590-1602. doi:10.1109/TMTT.2002.1006421

- 40. Piazzon L, Giofrè R, Colantonio P, Giannini F. Investigation of the AM/pm distortion in Doherty Power Amplifiers. In: 2014 IEEE topical conference on power amplifiers for wireless and radio applications (PAWR). Newport Beach, CA, USA 19-23 January 2014; 7–9.

- Figueiredo R, Carvalho NB, Piacibello A, Camarchia V. Nonlinear dynamic RF system characterization: envelope intermodulation distortion profiles—a noise power ratio-based approach. *IEEE Trans Microw Theory Tech.* 2021;69(9):4256-4271. doi:10.1109/TMTT.2021. 3092398

- Cheng Z, Xiong G, Liu Y, Zhang T, Tian J, Guo YJ. High-efficiency Doherty power amplifier with wide OPBO range for base station systems. *IET Microw, Antenn Propa.* 2019;13(7):926-929. doi:10.1049/iet-map.2018.5617

- 43. De Falco PE, Birchall J, Smith L. Hitting the sweet spot: a single-ended power amplifier exploiting class AB sweet spots and optimized third harmonic termination. *IEEE Microw Mag.* 2017;18(1):63-70. doi:10.1109/MMM.2016.2616183

- Lyu H, Cao Y, Chen K. Linearity-enhanced and highly efficient Doherty power amplifier: 16th high efficiency power amplifier student design competition. *IEEE Microw Mag.* 2021;22(10):62-69. doi:10.1109/MMM.2021.3095979

- Nasri A, Estebsari M, Toofan S, et al. Design of a Wideband Doherty Power Amplifier with high efficiency for 5G application. *Electronics*. 2021;10(8):873. doi:10.3390/electronics10080873

**How to cite this article:** Bartolotti G, Zhang Z, Shi P, Piacibello A, Camarchia V. Analysis of the impact of prototyping-related parasitic effects in a hybrid GaN power amplifier for 5G FR1 applications. *Int J Numer Model*. 2024;37(1):e3143. doi:10.1002/jnm.3143