### POLITECNICO DI TORINO Repository ISTITUZIONALE

#### 34 dBm GaN Doherty Power Amplifier for Ka-band satellite downlink

#### Original

34 dBm GaN Doherty Power Amplifier for Ka-band satellite downlink / Piacibello, A.; Giofre, R.; Quaglia, R.; Camarchia, V.. - ELETTRONICO. - (2021), pp. 25-28. (Intervento presentato al convegno 15th European Microwave Integrated Circuits Conference, EuMIC 2020 tenutosi a Utrecht, Netherlands nel 10-15 January 2021).

Availability:

This version is available at: 11583/2979226 since: 2023-06-07T07:01:15Z

Publisher:

Institute of Electrical and Electronics Engineers Inc.

**Published**

DOI:

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

#### Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# 34 dBm GaN Doherty Power Amplifier for Ka-band satellite downlink

Abstract — This paper presents the design and experimental characterization of a Doherty power amplifier cell targeting the satellite Ka-band downlink. The foreseen application is in a combined power amplifier, where two Doherty cells are combined in parallel to achieve power levels of the order of 6 W. The measured performance of the DPA cell well compares with the present state-of-the-art for the application, with output power in excess of 34 dBm in the 17.3–20.3 GHz band, gain around 12 dB, and efficiency higher than 25% and 20%, at saturation and 6 dB output power back-off, respectively.

Keywords — Doherty, GaN, power amplifiers, satellite.

#### I. INTRODUCTION

The increasing interest of the satellite communication market for lightweight, high efficiency transmitters is pushing the research toward solid state solutions, especially for the most demanding building block of the architecture in terms of performance and cost, the power amplifier (PA). In this scenario microwave monolithic integrated circuits (MMICs) are the reference choice for the PA realization [1], [2], [3]. The output power levels targeted are still significant (between 30-40 dBm, depending on the specific transmitter architecture), while the simplicity of the transmitter architecture is a must. The adopted signals are characterised by wide bandwidth and large amplitude dynamic, posing stringent linearity requirements to the transmitter. This leads to operate the PA far from its maximum efficiency region, with a detrimental impact on the entire transmitter power consumption. To complicate the picture, digital linearisers are not suitable for these applications since most of transmitters work as active repeaters; therefore there is no availability of the baseband signal and the PA must present a good intrinsic linearity.

A strong candidate for efficient amplification with non-constant envelope modulation schemes is the Doherty PA (DPA), a very popular solution at sub-6 GHz frequencies, especially as purely RF single-input [4], because it does not require additional digital signal processing to operate, with clear advantages in terms of instantaneous channel bandwidth, but also in dual-input [5], [6] implementation.

From a technology point of view, GaAs still dominates the market of the PAs in K-band, but when output power exceeds watt level for each MMIC, GaN based solutions are starting to appear [7], [8], [3], thanks to the power density of GaN leading to smaller devices, with more favorable impedance levels leading to simpler matching networks and eventually lower cost per watt thanks to MMIC area saving. This trend is demonstrated by the present efforts from companies and agencies, such as the European Space Agency and different Departments of Defense, for the exploitation of GaN technologies.

In this work, a DPA cell is designed targeting 34.5 dBm saturated output power, over the 17.3–20.3 GHz Ka-band downlink satellite frequency range. The adopted technology is the  $100\,\mathrm{nm}$  GaN-Si process by OMMIC. The 2-stage DPA is matched on  $100\,\Omega$  in order to be used as a cell in a combined structure without the need of additional output matching, but simply with the addition of a pre-driver to achieve the required gain. The measured performance is very promising and in line with the state of the art for the present scenario [3], also considering the limitations related to the space de-rating rules and the maximum junction temperature ( $160\,^{\circ}$ C). In particular, the DPA presents a saturated power in excess of 34 dBm over the whole 3 GHz bandwidth, a gain around  $12\,\mathrm{dB}$ , and efficiency higher than 25% and 20%, at saturation and  $6\,\mathrm{dB}$  Output power Back-Off (OBO), respectively.

#### II. TECHNOLOGY ASSESSMENT AND DESIGN OF THE DPA

The D01GH technology provided by OMMIC is a GaN process on high resistivity Si substrate, suitable for high-power as well as low-noise electronic devices working in the microwave and millimetre-wave frequency range. The D01GH process provides an AlN/GaN/AlGaN active layer for Double Heterostructure Field Effect Transistors (DHFET) with gate length of 100 nm, leading to a cut-off frequency higher than 100 GHz. Two types of Metal- Insulator-Metal (MIM) capacitors are available: one to realize high capacitance values (400 pF/mm2) and the other for small values (49 pF/mm2). High resistivity Si with 100 nm thickness constitutes the substrate. An AlGaN buffer layer is interposed between Si and the GaN active layer to mitigate the lattice mismatch.

#### A. Experimental characterization of active devices

Before starting the actual DPA implementation, a source-/load-pull measurement campaign on devices with

different periphery was carried out at the centre frequency of the target bandwidth (18.8 GHz). For each periphery, output power, PAE and gain levels were measured under continuous wave (CW) stimulus by using an active load-pull system based on a vector signal analyser. The devices were biased in class AB at 60 mA/mm, with drain voltage reduced from 15 V to 11 V, in order to account for space de-rating. This preliminary activity was carried out in order to experimentally verify the power density of the process and the agreement with the nonlinear models provided by the foundry [9]. Considering the aforementioned space derating and maximum junction temperature, the process power density of 3 W/mm reduces to around 2 W/mm. Therefore, two  $8 \times 100 \,\mu m$  devices are selected for the final stage to achieve the desired output power, taking into account the losses of the passive networks. Accounting for the gain penalty of the Doherty architecture and the gain achievable by the devices at the selected frequencies, a 2-stage DPA topology with the drivers embedded into each branch [10] is selected to achieve a reasonable gain not hampering the Power Added Efficiency (PAE).

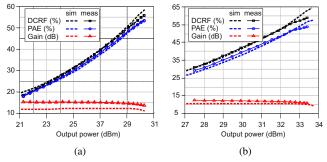

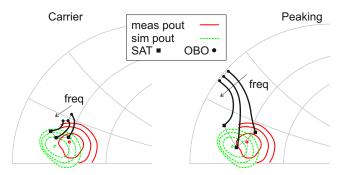

Fig 1 shows the comparison between measured and simulated performance for the  $6x50\,\mu\mathrm{m}$  and  $8x100\,\mu\mathrm{m}$  devices (driver and final stage peripheries respectively) when terminated on the optimum load at  $18.8\,\mathrm{GHz}$ . Notably, the agreement seems quite good even if the nonlinear model overestimates the output power of roughly  $1\,\mathrm{dB}$ .

Fig. 1. Comparison between measured and simulated performance of  $6x50 \mu m$  (left) and  $8x100 \mu m$  (right) devices as a function of output power at  $18.8 \, GHz$ .

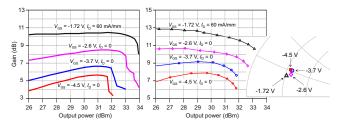

Source-/load-pull measurement were also performed in class C bias condition, considering that the Peaking devices work in that condition in a DPA. Fig.2 (left-center)shows the comparison between measured and simulated gain as a function of the output power at centre frequency for different class C bias conditions (i.e.,  $V_{\rm DD}$ =11 V &  $V_{\rm GG}$  ranging from -1.7 V to -4.5 V) for the  $8x100 \mu m$  device. Notably, there are some differences between actual and predicted results, especially for lower gate bias voltages. Similar trends have been observed on the other devices. Unfortunately, such a result is somehow expected when working with models from the foundry. Indeed, under class C operation, due to the presence of more severe gate and drain lag effects, the behaviour of the transistor can be substantially altered with respect to class AB operation. On the other hand, the Peaking device plays a key role in the implementation of a DPA. As a consequence, wrong estimation of its gate periphery and

related performance can easily hinder the active load-pulling principle on which the DPA is based, thus preventing the achievement of the specified requirements. In the same Fig. 2 (right) are reported the measured optimum loads for output power at centre frequency for the same class C bias conditions. The dependency on the gate bias voltage highlights that the tailoring of the impedance matching for the Peaking can improve the DPA performance.

Fig. 2. Load-pull results at different gate bias points for the  $8\times100\,\mu\mathrm{m}$  device. Simulated (left) and measured (center) gain vs. output power on the corresponding optimum load. Measured optimum load trajectories for output power (right).

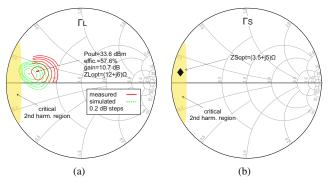

Finally, it is worth mentioning that, for some bias conditions, also the impact of the second harmonic termination was investigated by fixing the magnitude to one at both input and output side, while sweeping the phase. Results have shown the presence of a region in both input and output plane, where the device performance changes significantly. On the other hand, in the remaining region, the device performance is almost constant and still reasonably high. Fig. 3 shows output power contours of the  $8\times100\,\mu\mathrm{m}$  device in class AB with the critical region for the second harmonic highlighted, in both source and load plane. Balancing the complexity of the design with the achievable improvement by selecting the optimum harmonic terminations, in order to mitigate risks, it was decided to implement the DPA by keeping the second harmonic loads out from such a region.

Fig. 3. Output power contours level for the  $8 \times 100 \,\mu\text{m}$  device biased in class AB at 18.8 GHz with the critical region for the second harmonic highlighted (left). Optimum source impedance with the critical region for the second harmonic highlighted (right).

#### B. Design

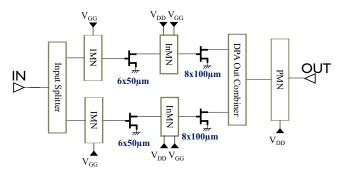

The results of the experimental characterization reported above were compared against the requirements and used to confirm the power budget computation. The synthesised loads across the devices within the DPA were monitored during all the design phases and compared against the measured contours. The proposed DPA architecture is shown in Fig. 4.

Fig. 4. Scheme of the proposed DPA.

As anticipated,  $8 \times 100 \,\mu\text{m}$  devices are selected for both Carrier and Peaking final stages. Both branches include a driver realized with a  $6\times50\mu m$  device. Small-signal unconditional stability of the devices is enforced in- and out-of-band by means of an R-C parallel network connected in series to the gate and an additional R-L series network on the gate bias line. The Doherty combiner is implemented in semi-lumped form according to the strategy described in [11], which consists in embedding the drain parasitic elements into the  $\lambda/4$  transmission line of each branch. On the Peaking path, an additional  $\lambda/4$  element is required to cancel the impedance inversion and to ensure the desired matching. This implementation requires additional real-to-real post-matching at the output, since the characteristic impedance of the Carrier's  $\lambda/4$  is determined by its  $C_{DS}$ . The post-matching network is based on [12] and matches to DPA cell to  $100\,\Omega$ in order use it in a combined structure without the need of any additional output matching. The loads synthesized

Fig. 5. Synthesised load modulation for Carrier (left) and Peaking (right) devices at 17.3, 18.8 and 20.3 GHz, compared to the simulated/measured load-pull power contours.

by the Doherty combiner at saturation are shown in Fig. 5. Given the discrepancy between simulated and measured optimum, the approach has been to target a trade-off between simulated and measured optimum load. The driver size and the inter-stage matching networks are equal in the two branches in order to maintain the signal phase alignment over the whole targeted frequency band. This represents a trade-off between performance and robustness to process variations.

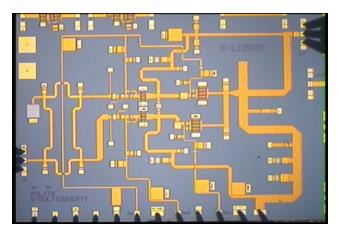

Fig. 6. Microscope photograph of the MMIC.

In fact, selecting different device peripheries and matching networks would allow to better optimize the performance over a narrow band, but ultimately results to be unfeasible over wide bands. For the same reason, the input matching networks designed according to the conjugate matching criterion are also symmetrical. The input splitter is therefore designed to provide uneven power splitting, with a Peaking/Carrier ratio of 1.25. This is again a trade-off between full turn-on of the Peaking power device, which is essential to ensure the desired OBO range, and the resulting gain penalty. The splitter is implemented as a branchline hybrid in semi-lumped form, which provides input isolation of the two branches while partially embedding the delay line needed in DPAs to ensure the proper phase alignment of the branch signals.

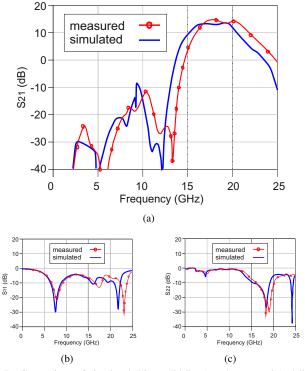

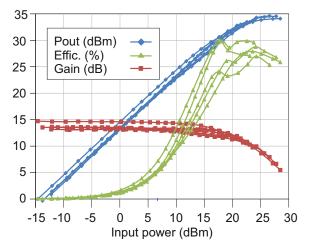

## III. FABRICATION AND EXPERIMENTAL CHARACTERIZATION

The MMIC has been fabricated, mounted on a brass carrier and measured in small- and large-signal conditions. The microscope photograph of the DPA is shown in Fig. 6. The size is 3x4 mm<sup>2</sup>. Fig. 7 reports the simulated and measured scattering parameters, measured in the 0.1-26 GHz frequency range for the nominal bias of the amplifier  $(V_{\rm DD}=11\,{\rm V},~V_{\rm GCarrierDriver}=-1.3\,{\rm V},~V_{\rm GCarrierPower}=-1.3\,{\rm V},$  $V_{\rm GPeakDriver}$ =-1.8 V,  $V_{\rm GPeakPower}$ =-2 V, They result in good agreement with the corresponding simulations except for some frequency shift toward high frequency. However, the DPA fully covers the targeted band 17.3–20.3 GHz. The measured CW performance in terms of output power, gain and efficiency versus input power is reported for 5 frequencies in the band (17.3 GHz, 18 GHz, 18.8 GHz, 19.6 GHz and 20.3 GHz) in Fig. 8 for the nominal bias condition and a load of  $100\,\Omega$ . The DPA achieves saturated output power and efficiency in excess of 34dBm and 25%, respectively on the whole band. The measured efficiency at 6 dB OBO is maintained higher than 20 % in the 3 GHz bandwidth. Compared with the present state-of-the-art the adoption of the Doherty technique somehow sacrifice the peak efficiency, but thanks to its feature of high efficiency

Fig. 7. Comparison of simulated (blue solid lines) and measured (red lines with circles) scattering parameters.

Fig. 8. Measured CW performance versus input power from 17.3 GHz to 20.3 GHz on a 100  $\Omega$  load. The curves refer to 5 frequencies in the band (17.3 GHz, 18 GHz, 18.8 GHz, 19.6 GHz and 20.3 GHz).

in back-off is foreseen as a winning solution with complex modulation schemes. The figure clearly highlights the proper Doherty behaviour of the proposed amplifier with an extended high efficiency region below saturation.

#### ACKNOWLEDGMENT

This work is funded under the ESA contract "Single-chip Ka-band Doherty amplifier" ITT: AO/1-9088/17/NL/HK Ref: Item no. 17.1ET.01. Dr. Vaclav Valenta is acknowledged for the fruitful discussions.

#### IV. CONCLUSION

A Doherty power amplifier cell for satellite Ka-Band downlink applications has been designed, fabricated and measured. The results are in line with the present state-of-the-art for this application. The PA will be adopted as a building block of a parallel combined amplifier for this application.

#### REFERENCES

- [1] R. Quaglia, V. Camarchia, M. Pirola, J. J. M. Rubio, and G. Ghione, "Linear GaN MMIC Combined Power Amplifiers for 7-GHz Microwave Backhaul," *IEEE Transactions on Microwave Theory and Techniques*, vol. 62, no. 11, pp. 2700–2710, 2014.

- [2] D. P. Nguyen, J. Curtis, and A. V. Pham, "A Doherty amplifier with modified load modulation scheme based on load-pull data," *IEEE Trans. Microw. Theory Techn.*, vol. PP, no. 99, pp. 1–10, 2017.

- [3] V. Valenta, I. Davies, N. Ayllon, S. Seyfarth, and P. Angeletti, "High-gain GaN Doherty power amplifier for Ka-band satellite communications," in IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Jan 2018, pp. 29–31.

- [4] R. Giofré, L. Piazzon, P. Colantonio, and F. Giannini, "An Ultra-Broadband GaN Doherty Amplifier with 83% of Fractional Bandwidth," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 11, pp. 775–777, Nov. 2014.

- [5] A. Piacibello, R. Quaglia, V. Camarchia, C. Ramella, and M. Pirola, "Dual-input driving strategies for performance enhancement of a Doherty power amplifier," in 2018 IEEE MTT-S International Wireless Symposium (IWS), 2018, pp. 1–4.

- [6] A. Piacibello, M. Pirola, V. Camarchia, C. Ramella, R. Quaglia, X. Zhou, and W. S. Chan, "Comparison of S-Band Analog and Dual-Input Digital Doherty Power Amplifiers," in 2018 48th European Microwave Conference (EuMC), Sep. 2018, pp. 1237–1240.

- [7] C. Campbell, C. Lee, V. Williams, M.-Y. Kao, H.-Q. Tserng, P. Saunier, and T. Balisteri, "A Wideband Power Amplifier MMIC Utilizing GaN on SiC HEMT Technology," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2640 –2647, Oct. 2009.

- [8] R. Giofrè, A. Del Gaudio, and E. Limiti, "A 28 GHz MMIC Doherty Power Amplifier in GaN on Si Technology for 5G Applications," in 2019 IEEE MTT-S International Microwave Symposium (IMS), June 2019, pp. 611–613

- [9] R. Quaglia, A. Piacibello, F. Costanzo, R. Giofre, M. Casbon, R. Leblanc, V. Valenta, and V. Camarchia, "Source/Load-Pull Characterisation of GaN on Si HEMTs with Data Analysis Targeting Doherty Design," in 2020 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Jan 2020, pp. 1–3.

- [10] R. Quaglia, V. Camarchia, T. Jiang, M. Pirola, S. Donati Guerrieri, and B. Loran, "K-Band GaAs MMIC Doherty Power Amplifier for Microwave Radio With Optimized Driver," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 11, pp. 2518–2525, Nov 2014.

- [11] R. Quaglia, V. Camarchia, J. J. Moreno Rubio, M. Pirola, and G. Ghione, "A 4-W Doherty Power Amplifier in GaN MMIC Technology for 15-GHz Applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 4, pp. 365–367, April 2017.

- [12] C. Monzon, "A small dual-frequency transformer in two sections," *IEEE Trans. Microw. Theory Techn.*, vol. 51, no. 4, pp. 1157 1161, Apr. 2003.