Doctoral Dissertation Doctoral Program in Electrical, Electronics and Communications Engineering (XXXIV cycle)

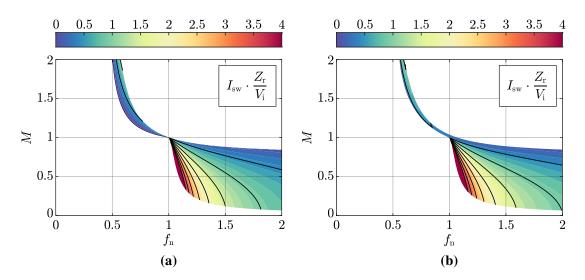

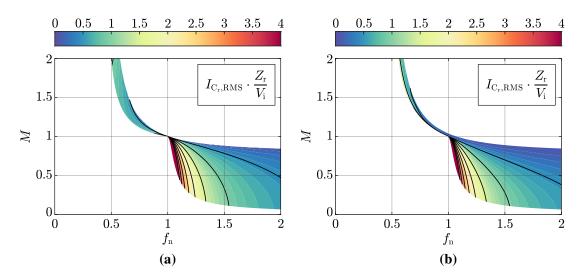

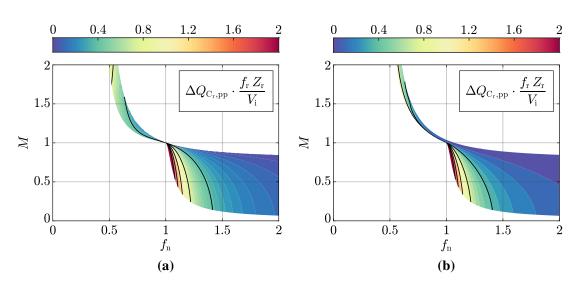

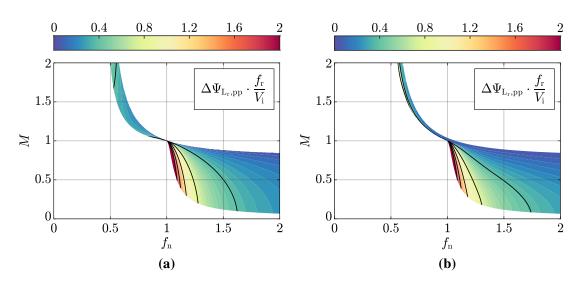

# Analysis, Design and Control of a Modular Full-Si Converter Concept for Electric Vehicle Ultra-Fast Charging

**Davide Cittanti**

Supervisor:

Prof. Radu Bojoi

**Doctoral Examination Committee:**

Prof. Marco Liserre, *Referee* Prof. Luca Solero, *Referee* Prof. Gabriele Grandi Prof. Paolo Mattavelli Prof. Johann W. Kolar

> Politecnico di Torino June 30, 2022

# Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Davide Cittanti June 30, 2022

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

# Acknowledgements

First and foremost, I would like to thank my supervisor Prof. Radu Bojoi for his technical guidance and for giving me the opportunity to undertake my Ph.D. in his research group within the Power Electronics Innovation Center (PEIC). Our activities have gone much beyond academic research, involving several industry projects and a ton of laboratory experience. Also, I have learned a lot from him during these years, especially from his tireless working attitude and his strive for excellence. Thank you Radu, "failure is not an option"!

Despite not being my official co-supervisor, special thanks go to Prof. Eric Armando, who has always supported me with unbelievable technical experience and has alleviated the work pressure of the whole group with his playful attitude and his funny jokes. Grazie Eric!

Huge thanks go to my friends and workmates Fabio, Matteo, Stefano, Sandro, Enrico, Vincenzo, Fausto, Simone and Paolo, who were always there when I needed them and have all contributed to my research activities. Thank you guys for having made this experience more enjoyable with our coffee breaks, water breaks, ice-cream breaks, kebab breaks (we clearly did a lot of breaks...)!

A sincere acknowledgement goes to the people of the ETH Power Electronic Systems Laboratory (PES). In particular, I would like to thank Prof. Johann W. Kolar, who has given me the opportunity of spending almost an entire year at PES. His brilliant insights, his rock-solid knowledge and his dedicated working attitude have inspired me greatly. Furthermore, a special thanks goes to my supervisors Mattia and Jonas, who have continuously overseen my activities and have made possible the outcomes of our research. Also, a big thank you goes to all guys and girls at PES, for the great discussions during lunch-time, coffee/cake breaks, mountain hikes and looong waiting times during calorimetric measurements!

My deepest thanks go to my parents and my sister, for their continuous support over the years. None of my studies and achievements could have been possible without them.

Last but not least, I would like to thank my wife Mimma for her love and understanding during the tough period of my studies. She has always supported me in the moments of need and she has most of all contributed to lead me where I am now.

Thank you! Grazie! Davide

# Abstract

The transportation sector is one of the major contributors to the global greenhouse gas generation and is thus subject to considerable political attention. In view of the increasing concerns on the long-term effects of  $CO_2$  emissions in the atmosphere and the worsening air quality in most urban areas, a worldwide shift towards vehicle electrification is currently underway. Government policies are pushing for the phase-out of internal combustion engine vehicles (ICEVs), i.e. no longer able to satisfy the increasingly strict emission requirements, meanwhile supporting the adoption of electric vehicles (EVs).

Even though EVs provide several advantages with respect to ICEVs, such as better performance, no local pollution, reduced maintenance and cost of ownership, limited noise emissions and the option of charging at home and/or at work, there are still significant challenges that impair their widespread adoption. In particular, potential EV customers are typically discouraged by the higher price with respect to comparable ICEVs and fear "range anxiety", due to the limited range (i.e., typically 200-500 km), the long charging times (i.e., usually exceeding 30 min for a full charge) and the general lack of charging stations. To ensure a broader EV adoption, the key technical challenges to be overcome are related to improving current battery technology (i.e., in terms of cost, energy density, charge rate, lifetime degradation, etc.), enhancing the performance of EV powertrain components (i.e., in terms of efficiency, size, weight, etc.) and scaling up dramatically the charging infrastructure (i.e., in terms of charging power, number of stations, number of stalls, etc.).

In this context, this thesis deals with the converter-level challenges related to the development of high-power EV battery chargers, which represent a key enabler to mainstream EV adoption as they address one of the major customer concerns, i.e. the charging time. In particular, the focus is on ultra-fast battery charging technology, which aims to achieve a stop-and-go EV refueling experience similar to the one of an ICEV, targeting  $\approx 200$  km of added range in 5 min. The main goal of this dissertation is to analyze, design, control and assess experimentally a modular converter concept for EV ultra-fast charging, addressing the challenging requirements set by the application. The performed research activity has resulted in several contributions, mainly related to the converter analysis and modeling, the converter design and the converter control.

# Abbreviations

| 1D      | One-Dimensional                   |

|---------|-----------------------------------|

| 2D      | Two-Dimensional                   |

| 2LSVPWM | Two-Level Space Vector PWM        |

| 3LDPWMA | Three-Level Discontinuous PWM A   |

| 3LDPWMB | Three-Level Discontinuous PWM B   |

| 3LSVPWM | Three-Level Space Vector PWM      |

| BCM     | Boundary Conduction Mode          |

| BMS     | Battery Management System         |

| CC      | Constant-Current                  |

| ССМ     | Continuous Conduction Mode        |

| CV      | Constant-Voltage                  |

| DAB     | Dual Active Bridge                |

| DAC     | Digital-to-Analog Converter       |

| DCM     | Discontinuous Conduction Mode     |

| DPF     | Displacement Power Factor         |

| DPS     | Double Phase-Shift                |

| DSO     | Distribution System Operator      |

| DSP     | Digital Signal Processor          |

| EDF     | Extended Describing Function      |

| EMI     | ElectroMagnetic Interference      |

| EV      | Electric Vehicle                  |

| FHA     | First Harmonic Approximation      |

| GaN     | Gallium Nitride                   |

| HEMT    | High Electron Mobility Transistor |

|         |                                   |

| ICEV    | Internal Combustion Engine Vehicle                |

|---------|---------------------------------------------------|

| ISR     | Interrupt Service Routine                         |

| MAF     | Moving Average Filter                             |

| MCU     | MicroController Unit                              |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor |

| PCB     | Printed Circuit Board                             |

| PCC     | Point of Common Coupling                          |

| PI      | Proportional-Integral                             |

| PLL     | Phase-Locked Loop                                 |

| PSFB    | Phase-Shift Full Bridge                           |

| PWM     | Pulse-Width Modulation                            |

| RMS     | Root Mean Square                                  |

| Si      | Silicon                                           |

| SiC     | Silicon Carbide                                   |

| SPS     | Single Phase-Shift                                |

| SPWM    | Sinusoidal PWM                                    |

| TDA     | Time Domain Analysis                              |

| THD     | Total Harmonic Distortion                         |

| THIPWM  | Third Harmonic Injection PWM                      |

| TIM     | Thermal Interface Material                        |

| TPS     | Triple Phase-Shift                                |

| VCO     | Voltage-Controlled Oscillator                     |

| WBG     | Wide BandGap                                      |

| ZCS     | Zero Current Switching                            |

| ZMPCPWM | Zero Mid-Point Current PWM                        |

| ZOH     | Zero-Order Hold                                   |

| ZVS     | Zero Voltage Switching                            |

|         |                                                   |

# Contents

| Ac | know   | ledgements                           | iii |

|----|--------|--------------------------------------|-----|

| Ał | ostrac | t                                    | iv  |

| Ał | obrevi | iations                              | v   |

| 1  | Intr   | oduction                             | 1   |

|    | 1.1    | Electric Vehicle Ultra-Fast Charging | 2   |

|    |        | 1.1.1 Requirements and Challenges    | 2   |

|    |        | 1.1.2 State-of-the-Art               | 4   |

|    | 1.2    | Goals and Research Contributions     | 6   |

|    | 1.3    | Specifications and Architecture      | 8   |

|    | 1.4    | Outline of the Thesis                | 10  |

|    | 1.5    | List of Publications                 | 12  |

| 2  | AC/    | DC Converter – Analysis              | 18  |

|    | 2.1    | Introduction                         | 18  |

|    |        | 2.1.1 Converter Topologies           | 19  |

|    |        | 2.1.2 Key Challenges                 | 22  |

|    | 2.2    | Operating Principle and Limits       | 23  |

|    |        | 2.2.1 Basics of Operation            | 24  |

|    |        | 2.2.2 Zero-Sequence Voltage Limits   | 28  |

|   |     | 2.2.3   | Modulation Index Limits                | 29 |

|---|-----|---------|----------------------------------------|----|

|   |     | 2.2.4   | Power Factor Angle Limits              | 30 |

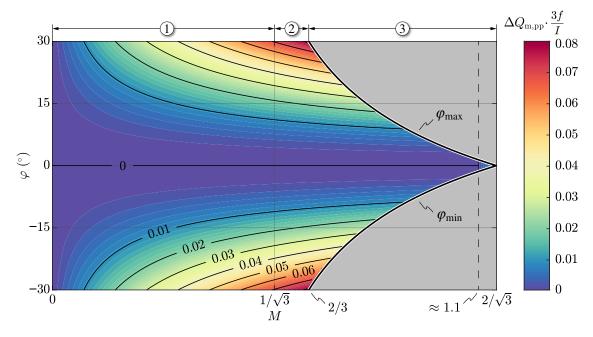

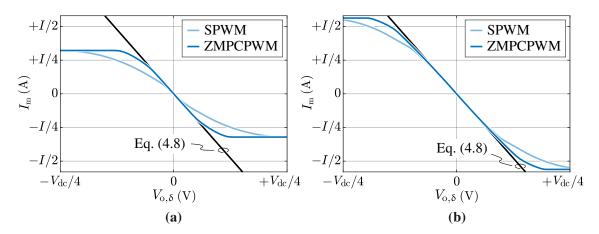

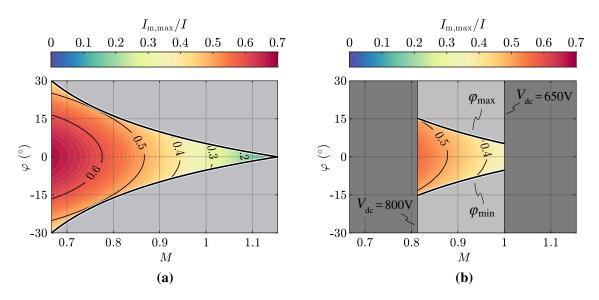

|   |     | 2.2.5   | Mid-Point Current Limits               | 31 |

|   | 2.3 | Modul   | ation Strategies                       | 36 |

|   |     | 2.3.1   | Modulator                              | 37 |

|   |     | 2.3.2   | Zero-Sequence Voltage Injection        | 37 |

|   |     | 2.3.3   | Zero-Sequence Voltage Saturation       | 42 |

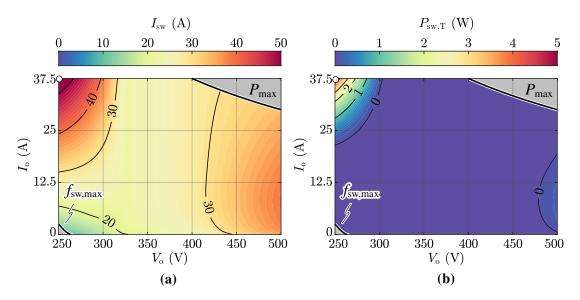

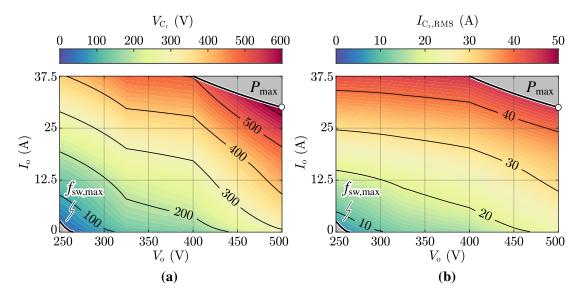

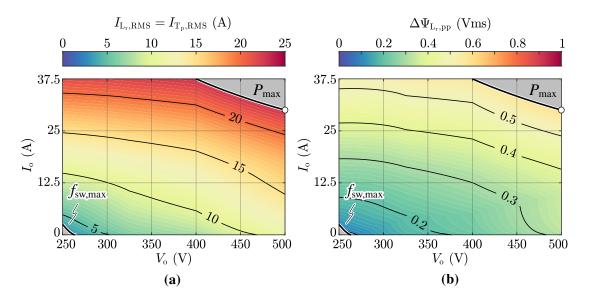

|   | 2.4 | Compo   | onent Stresses                         | 42 |

|   |     | 2.4.1   | Semiconductor Devices                  | 43 |

|   |     | 2.4.2   | DC-Link Capacitors                     | 48 |

|   |     | 2.4.3   | AC-Side Inductors                      | 54 |

|   | 2.5 | Summ    | ary                                    | 60 |

| 3 |     |         | werter – Design                        | 61 |

| 3 |     |         | C                                      | -  |

|   | 3.1 |         |                                        | 61 |

|   |     | 3.1.1   | Specifications and Performance Targets | 62 |

|   | 3.2 | Compo   | onent Design/Selection                 | 64 |

|   |     | 3.2.1   | Semiconductor Devices                  | 64 |

|   |     | 3.2.2   | DC-Link Capacitors                     | 68 |

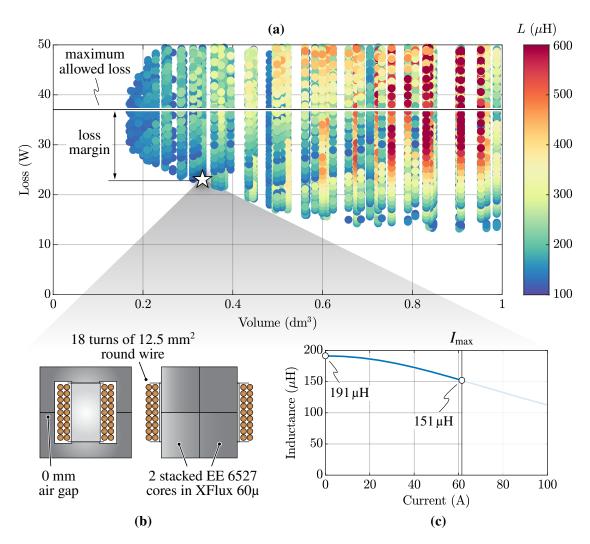

|   |     | 3.2.3   | AC-Side Inductors                      | 69 |

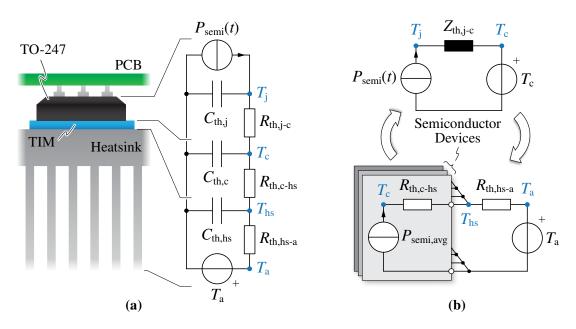

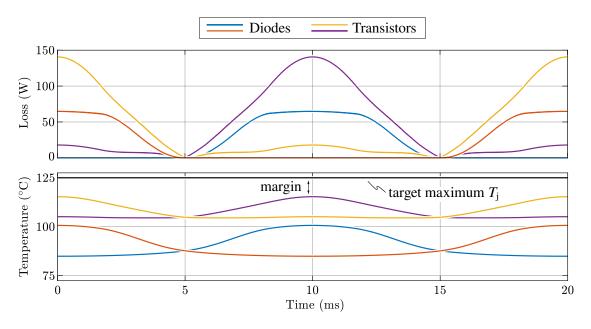

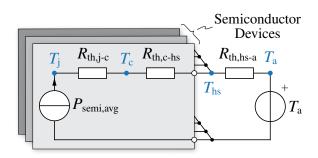

|   |     | 3.2.4   | Heat Dissipation System                | 74 |

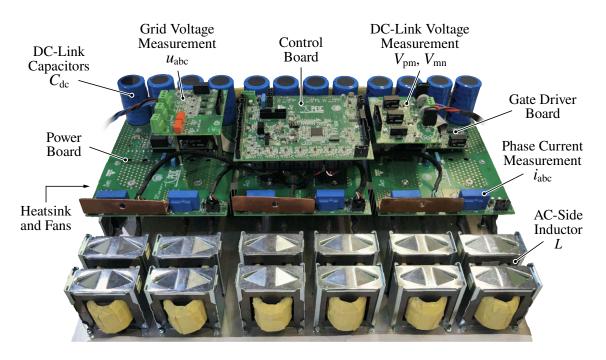

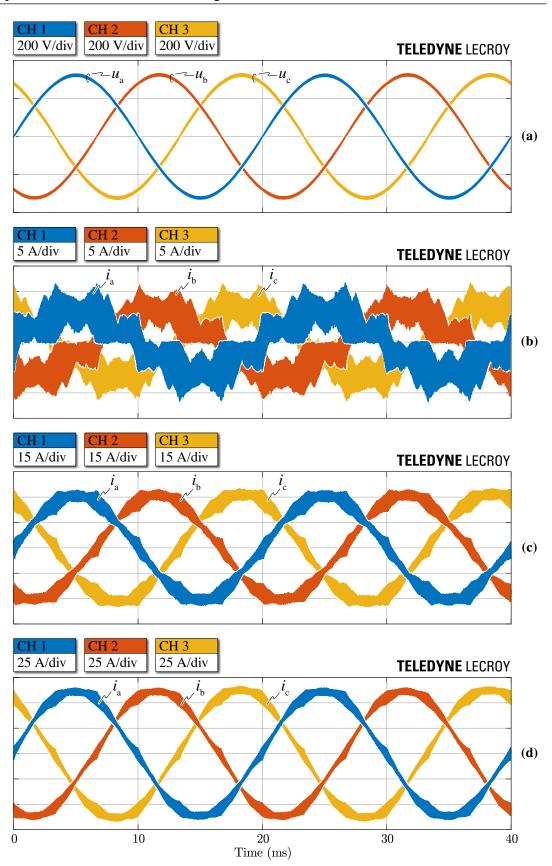

|   | 3.3 | Experi  | mental Results                         | 77 |

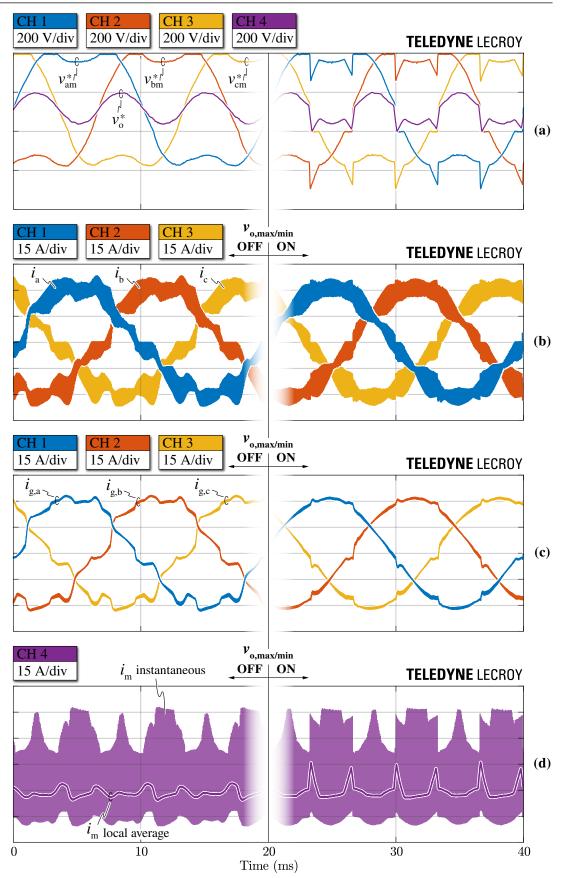

|   |     | 3.3.1   | AC-Side Inductor Currents              | 79 |

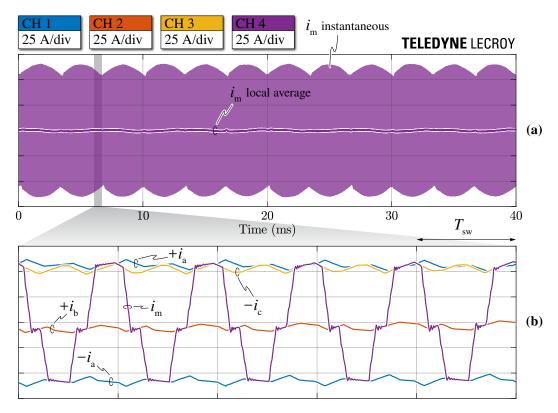

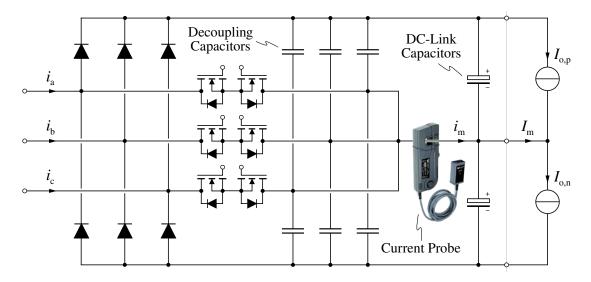

|   |     | 3.3.2   | DC-Link Mid-Point Current              | 79 |

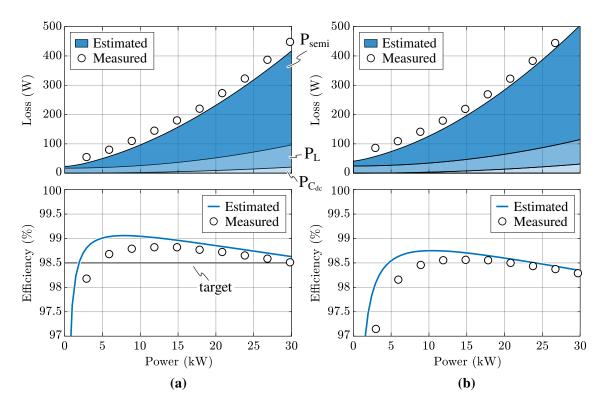

|   |     | 3.3.3   | Loss and Efficiency                    | 82 |

|   | 3.4 | Summ    | ary                                    | 83 |

| 4 |     |         | verter – Control                       | 84 |

| - |     |         |                                        |    |

|   | 4.1 | Introdu | uction                                 | 85 |

|   | 4.2 | System | n Small-Signal Model                     |

|---|-----|--------|------------------------------------------|

|   | 4.3 | Contro | oller Design                             |

|   |     | 4.3.1  | dq Current Control Loops                 |

|   |     | 4.3.2  | DC-Link Voltage Control Loop             |

|   |     | 4.3.3  | DC-Link Mid-Point Voltage Balancing Loop |

|   | 4.4 | Simula | ation Results                            |

|   | 4.5 | Experi | imental Results                          |

|   |     | 4.5.1  | Steady-State Operation                   |

|   |     | 4.5.2  | Dynamical Operation                      |

|   | 4.6 | Summ   | ary                                      |

| 5 | DC/ |        | nverter – Analysis 114                   |

| 5 | 5.1 |        | uction                                   |

|   | 5.1 | 5.1.1  |                                          |

|   |     | 5.1.2  | Converter Topologies                     |

|   | 5.2 |        | Key Challenges                           |

|   | 5.2 | -      | ting Principle $\dots$ 119               |

|   |     | 5.2.1  | First Harmonic Approximation (FHA)       |

|   |     | 5.2.2  | Operating Limits                         |

|   |     | 5.2.3  | Modes of Operation                       |

|   |     | 5.2.4  | Soft-Switching Mechanisms                |

|   | 5.3 | Comp   | onent Stresses                           |

|   |     | 5.3.1  | Semiconductor Devices                    |

|   |     | 5.3.2  | Resonant Capacitor                       |

|   |     | 5.3.3  | Resonant Inductor                        |

|   |     | 5.3.4  | Transformer                              |

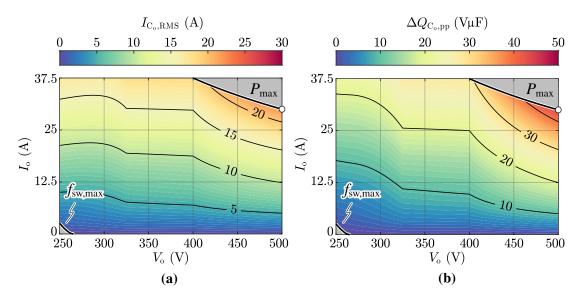

|   |     | 5.3.5  | Input Filter Capacitor                   |

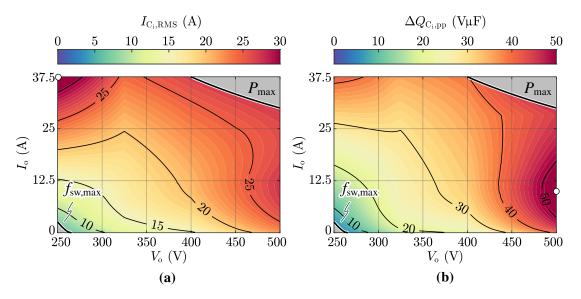

|   |     | 5.3.6  | Output Filter Capacitor                  |

|   | 5.4 | Summ   | ary                                      |

| 6 | DC/ | DC Cor  | nverter – Design                                 | 146 |

|---|-----|---------|--------------------------------------------------|-----|

|   | 6.1 | Introdu | uction                                           | 146 |

|   |     | 6.1.1   | Specifications and Performance Targets           | 148 |

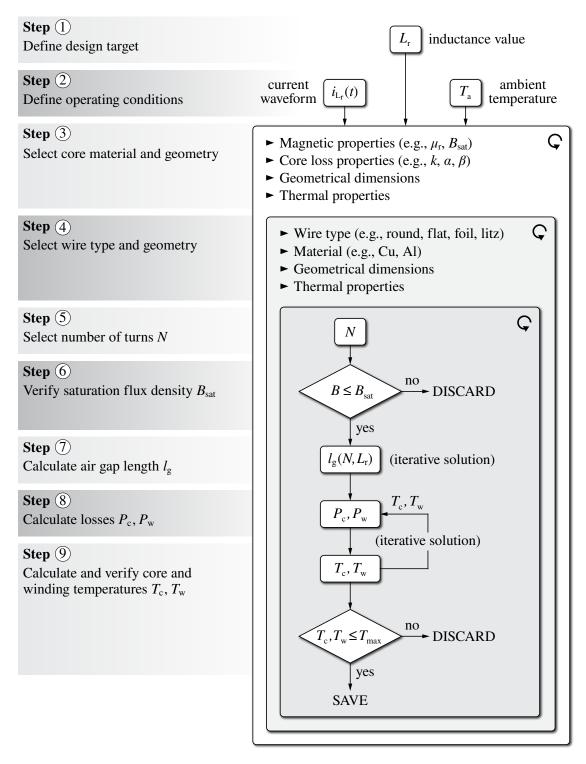

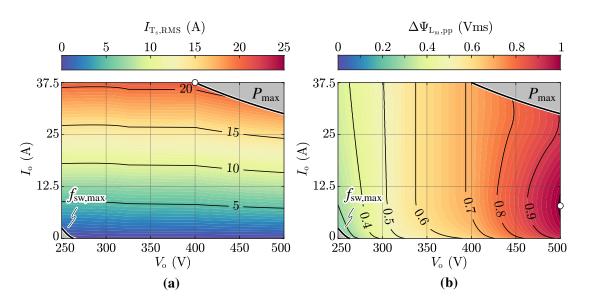

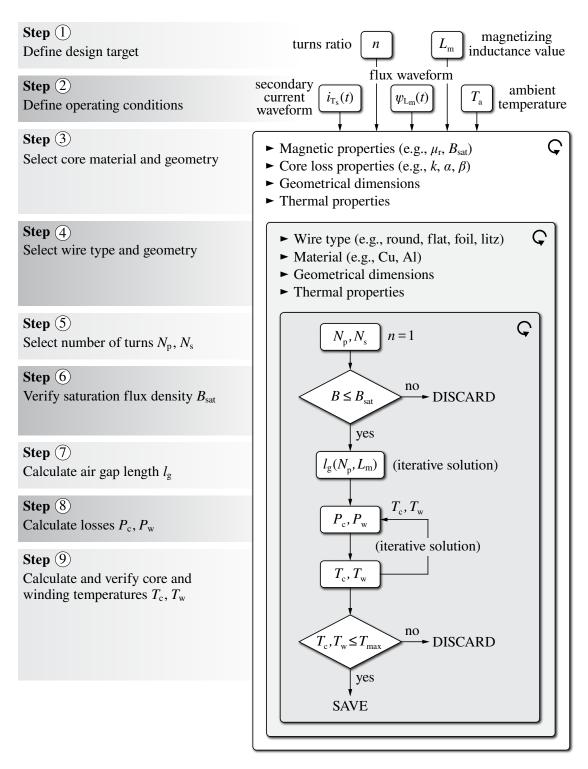

|   | 6.2 | Design  | Procedure                                        | 150 |

|   | 6.3 | Compo   | onent Design/Selection                           | 156 |

|   |     | 6.3.1   | Semiconductor Devices                            | 156 |

|   |     | 6.3.2   | Resonant Capacitor                               | 160 |

|   |     | 6.3.3   | Resonant Inductor                                | 161 |

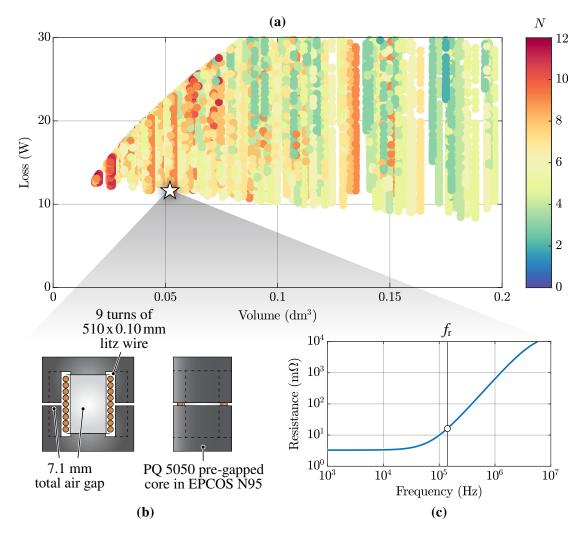

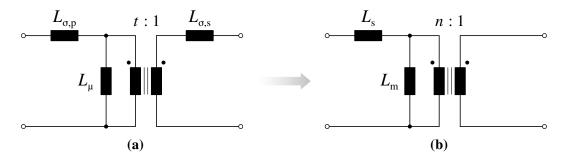

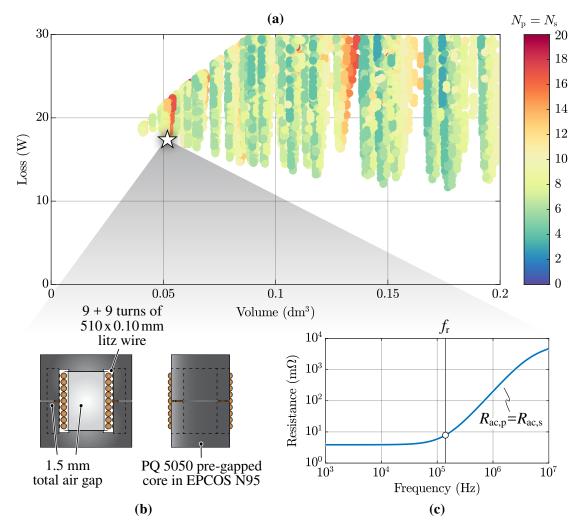

|   |     | 6.3.4   | Transformer                                      | 164 |

|   |     | 6.3.5   | Input Filter Capacitor                           | 168 |

|   |     | 6.3.6   | Output Filter Capacitor                          | 169 |

|   |     | 6.3.7   | Heat Dissipation System                          | 170 |

|   | 6.4 | Experi  | mental Results                                   | 172 |

|   |     | 6.4.1   | Resonant Tank Impedance                          | 174 |

|   |     | 6.4.2   | Steady-State Waveforms                           | 174 |

|   |     | 6.4.3   | Loss and Efficiency                              | 177 |

|   | 6.5 | Summ    | ary                                              | 178 |

| _ |     |         |                                                  |     |

| 7 |     |         | iverter – Control                                | 179 |

|   | 7.1 |         | uction                                           |     |

|   | 7.2 | System  | n Small-Signal Model                             | 182 |

|   |     | 7.2.1   | Full 7 <sup>th</sup> Order System Model          | 183 |

|   |     | 7.2.2   | Reduced 3 <sup>rd</sup> Order System Model       | 189 |

|   |     | 7.2.3   | Proposed Dual 1 <sup>st</sup> Order System Model | 191 |

|   | 7.3 | Contro  | oller Design                                     | 198 |

|   |     | 7.3.1   | Output Current Control Loop                      | 199 |

|   |     | 7.3.2   | Output Voltage Control Loop                      | 205 |

|   | 7.4 | Simula  | ation Results                                    | 206 |

|   | 7.5 | Experi  | mental Results                                   | 209 |

|     |        | 7.5.1     | Look-Up Table (LUT) Extraction              | 211 |

|-----|--------|-----------|---------------------------------------------|-----|

|     |        | 7.5.2     | Steady-State Operation                      | 213 |

|     |        | 7.5.3     | Dynamical Operation                         | 215 |

|     | 7.6    | Summa     | ary                                         | 221 |

|     | Appe   | endix 7.  | A Linearized State-Space Model Coefficients | 221 |

|     | Appe   | endix 7.1 | B LUT Interpolation and Derivative          | 227 |

| 8   | Con    | clusions  | and Outlook                                 | 229 |

|     | 8.1    | Results   | s and Summary                               | 229 |

|     | 8.2    | Future    | Developments                                | 233 |

| Bil | oliogr | aphy      |                                             | 234 |

# Chapter 1

# Introduction

As a result of increasing concerns on the long-term effects of  $CO_2$  emissions in the atmosphere caused by the combustion of fossil fuels, a worldwide shift towards renewable energy generation and domestic/industrial electrification is currently underway.

The transportation sector accounts for  $\approx 23\%$  of the global CO<sub>2</sub> emissions (as of 2021 [1]) and is therefore subject to considerable political attention. Because of government regulations aiming to limit greenhouse gas emissions, internal combustion engine vehicles (ICEVs) are being phased out, as they are no longer able to satisfy the increasingly strict emission requirements. At the same time, the adoption of electric vehicles (EVs) is increasing rapidly [2], in view of their better performance, absence of local pollution, government incentives (when present), reduced maintenance and cost of ownership, limited noise emissions and the option of charging at home and/or at work. Although EV sales already accounted for  $\approx 10\%$  of the global car market in 2021 [2] (i.e., including battery EVs and plug-in hybrid EVs), they still represent only  $\approx 1.5\%$  of the global car stock and several challenges have yet to be overcome. In particular, potential EV customers are typically discouraged by the higher price with respect to comparable ICEVs and fear "range anxiety", due to the limited range (i.e., typically 200 – 500 km), the long charging stations.

From a technical standpoint, the key challenges for a broader EV adoption are related to improving current battery technology (i.e., in terms of cost, energy density, charge rate, lifetime degradation, etc.), enhancing the performance of EV powertrain components (i.e., in terms of efficiency, size, weight, etc.) and scaling up dramatically the charging infrastructure (i.e., in terms of charging power, number of stations, number of stalls, etc.). In this context, this work deals with the technical challenges related to the development of high-power EV battery chargers, which allow to tackle one of the major obstacles to EV adoption, i.e. the charging time.

# 1.1 Electric Vehicle Ultra-Fast Charging

Off-board DC fast chargers are a key enabling technology for the widespread adoption of EVs, since they allow to dramatically decrease the EV charging time with respect to built-in on-board AC chargers (cf. **Fig. 1.1**) [3, 4]. Furthermore, a widespread DC charging infrastructure would address the customer fear for range anxiety and simultaneously enable the advent of EVs with smaller battery packs and thus lower cost, addressing a much larger part of the market.

Ultra-fast charging (or extreme fast charging) refers to the ability of achieving a stopand-go EV refueling experience similar to the one of an ICEV [5], targeting  $\approx 200 \text{ km}$  of added range in 5 min. Considering that the typical passenger vehicle energy consumption ranges between 150 - 250 Wh/km [6], this target translates in a required charging power of  $\approx 300 - 500 \text{ kW}$ . The high power to be processed, together with several other requirements, poses several technical challenges in the realization of an ultra-fast battery charger. In this section, the key requirements of ultra-fast battery chargers are described and the main challenges related to their design and operation are discussed. Moreover, an overview of the state-of-the-art of ultra-fast chargers is provided.

#### **1.1.1 Requirements and Challenges**

The main requirements of an EV ultra-fast battery charger can be summarized in:

- high conversion efficiency, to maximize the energy transferred to the vehicle and minimize the heat dissipation;

- ▶ high power density, to minimize the volume and thus the footprint of the system;

- high reliability, to maximize the mean time between failures and therefore maximize the charging station availability;

| On-Board | AC Charger | Off-Board DC | C Charger  |

|----------|------------|--------------|------------|

| Level 1  | Level 2    | Level (3)    | Level ④    |

|          |            |              |            |

| 3 kW     | 10 kW      | 50 kW        | 150-350 kW |

| (10 h)   | (3 h)      | (35 min)     | (5-12 min) |

|          |            |              |            |

| Slow     | Medium     | Fast         | Ultra-Fast |

**Fig. 1.1:** Simplified overview of the existing charging levels [7, 8], the related charging power and the estimated time to charge 30 kWh (i.e., 200 km of range at 150 Wh/km).

- cost effectiveness, as the initial investment cost is charged to the final user and must ensure a competitive price per kWh;

- galvanic isolation between the main distribution grid and the vehicle battery according to safety standards [9];

- wide output voltage range, to provide a universal supply capable of charging all commercially available EVs;

- sinusoidal grid-side currents with low distortion and harmonics according to gridcode standards [10, 11];

- ▶ low battery-side current ripple, to limit the premature aging of the battery itself.

The simultaneous achievement of all aforementioned requirements poses significant technical challenges.

In particular, achieving at the same time high efficiency, high power density, high reliability, cost effectiveness, galvanic isolation and wide output voltage range leads to an extremely challenging converter design. For instance, the high amount of transferred power together with the limited converter volume require an adequate heat dissipation system (e.g., a 95 % efficiency at 300 kW translates in 15 kW of heat to be dissipated).

Furthermore, ensuring clean sinusoidal grid currents and low battery charging current ripple lead to a challenging converter control, which may be addressed with advanced control strategies implemented by digital means.

Another significant challenge is related to the impact of ultra-fast battery chargers on the distribution grid [12–14]. In fact, conventional DC fast charging stations represent a high-power, unpredictable and discontinuous load for the electrical system. The large scale diffusion of this kind of stations is increasing the utility daily peak load, directly causing transformer overload and accelerated aging, meanwhile increasing system power losses [12]. Moreover, their lack of flexibility leads to high peak power charges for the station operator, which are then reflected on the charging price for the final users, and poses serious challenges to the power distribution system, affecting its stability and decreasing the power quality [15]. Most of the issues mentioned above can be addressed either by directly connecting the charger to the medium-voltage grid [16–19] or by having local energy storage at disposal, e.g. leveraging the EV batteries (i.e., known as vehicle-to-grid operation) or installing separate storage to the station [20–22]. In particular, a correct sizing of the storage unit provides great flexibility to the charging station, allowing to reduce its peak power demand and the size of the protection equipment, thus leading to both lower operational costs and initial investment [22, 23]. Moreover, the availability

of stored energy opens up the possibility of providing grid ancillary services, such as active power injection/absorption for grid frequency regulation, reactive power support for voltage regulation, grid harmonic reduction and fault current generation during voltage dips/swells [13]. These features can directly support the power distribution system, effectively turning around the drawbacks of conventional ultra-fast charging stations, meanwhile allowing for an additional revenue stream for the station operator [24].

It is worth noting that this work only focuses on the converter-level challenges of low-voltage ultra-fast chargers, therefore medium-voltage converter architectures and the integration of fast-charging stations into the grid are not discussed here.

#### 1.1.2 State-of-the-Art

DC fast chargers directly deliver DC current to the vehicle battery pack, meanwhile ensuring galvanic isolation from the mains (i.e., for safety reasons in case of fault). As of today, most commercially available DC fast chargers are rated between 50 kW and 150 kW [5], nevertheless a new generation of ultra-fast chargers rated at 350 kW and above is starting to be deployed [16, 17, 39–41]. The technical specifications of several state-of-the-art ultra-fast chargers currently available on the market are summarized in **Table 1.1**. These

| Manufacturer<br>and Model     | Nominal<br>Power | Input<br>Voltage      | Output<br>Voltage   | Output<br>Current | Nominal<br>Efficiency |

|-------------------------------|------------------|-----------------------|---------------------|-------------------|-----------------------|

| Blink RT 175-S [25]           | 175 kW           | 480 V <sub>RMS</sub>  | 200-920 V           | 350 A             | >94.5%                |

| BTC Power HPCT-200 [26]       | 200 kW           | $480\mathrm{V_{RMS}}$ | 50-950V             | 500 A             | >92%                  |

| Delta UFC 200 [27]            | 200 kW           | $400V_{RMS}$          | 200 - 1000  V       | 500 A             | _                     |

| Tesla Supercharger V3 [28]    | 250 kW           | $480\mathrm{V_{RMS}}$ | $50-500\ V$         | 631 A             | _                     |

| Alpitronic HYC 300 [29]       | 300 kW           | $400\mathrm{V_{RMS}}$ | 150 - 1000  V       | 500 A             | >94%                  |

| Siemens SICHARGE D [30]       | 300 kW           | $400\mathrm{V_{RMS}}$ | 150 - 1000  V       | 500 A             | >95.5%                |

| ABB Terra HP350 [31]          | 350 kW           | $400\mathrm{V_{RMS}}$ | $150-920\mathrm{V}$ | 500 A             | >94%                  |

| ENERCON E-Charger 600 [32]    | 350 kW           | $400\mathrm{V_{RMS}}$ | $200-920\mathrm{V}$ | 500 A             | >94%                  |

| EVBox Ultroniq [33]           | 350 kW           | $480\mathrm{V_{RMS}}$ | 50-950V             | 500 A             | _                     |

| SIGNET DP350K [34]            | 350 kW           | $480\mathrm{V_{RMS}}$ | $150-920\mathrm{V}$ | 500 A             | _                     |

| PHIHONG DO 360 [35]           | 360 kW           | $480\mathrm{V_{RMS}}$ | $150-950\mathrm{V}$ | 500 A             | >94%                  |

| EVTEC ristretto&charge [36]   | 384 kW           | $400\mathrm{V_{RMS}}$ | $150-920\mathrm{V}$ | 500 A             | >94.5%                |

| ChargePoint Express Plus [37] | 400 kW           | $400\mathrm{V_{RMS}}$ | 200 - 1000  V       | 500 A             | >95%                  |

| Ingeteam RAPID ST [38]        | 400 kW           | $400\mathrm{V_{RMS}}$ | 50 - 1000  V        | 500 A             | _                     |

Tab. 1.1: Technical specifications of several commercially available ultra-fast chargers.

chargers are all designed to be connected to the low-voltage grid and typically consist of several paralleled units with a reduced power rating (i.e., 10-30 kW). Notably, the modularity allows to benefit from economies-of-scale, ensures an upgradable system, enables the disconnection of some units at light load to preserve efficiency and allows to reconfigure the connections between units to achieve a wider output voltage/load range.

All commercially available ultra-fast chargers support one or more of the five existing DC fast-charging standards reported in **Table 1.2**, namely CHAdeMO (global), CCS Type 1 (US), CCS Type 2 (EU), GB/T (China), and the Tesla proprietary supercharger system (global). It is worth noting that the ultimate limit to the charging power is set by the voltage/current capability of the connector (and cable). For this reason, liquid cooled cables and connectors are typically adopted when the charging current exceeds 350 A. Although the standards differ on several technical aspects (e.g., the connector, the communication protocol, etc.), the charging process follows similar steps, starting with a signal handshake, the isolation verification and the exchange of fundamental information, such as the vehicle charging limits. Once these steps are completed, the vehicle DC relay is closed and the charging session begins. During the charging process, the vehicle battery management system (BMS) communicates to the charger the desired current and/or voltage reference. Finally, once the desired state-of-charge is met, the vehicle disconnects itself by opening its DC relay.

As mentioned earlier, all state-of-the-art EV ultra-fast chargers are designed to be connected to the three-phase low-voltage grid, mainly to leverage the existing industrial power electronics knowledge and availability [4, 5, 17, 42]. According to safety standards [9], the charging station must ensure the galvanic isolation (i.e., with isolation monitoring) between the main distribution network and the vehicle battery, such that the

|                 | CHAdeMO | CCS Type 1 | CCS Type 2 | GB/T   | Tesla |

|-----------------|---------|------------|------------|--------|-------|

|                 |         |            |            |        | 9     |

|                 |         |            |            |        |       |

| Maximum Voltage | 1000 V  | 1000 V     | 1000 V     | 950 V  | _     |

| Maximum Current | 400 A   | 500 A      | 500 A      | 400 A  | _     |

| Maximum Power*  | 400 kW  | 500 kW     | 500 kW     | 380 kW | -     |

Tab. 1.2: Overview of the five DC fast-charging standards (adapted from [39]).

\*based on maximum voltage and current ratings.

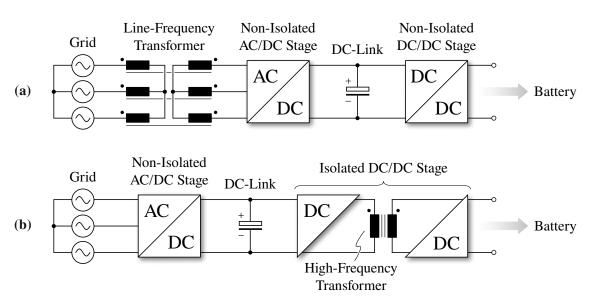

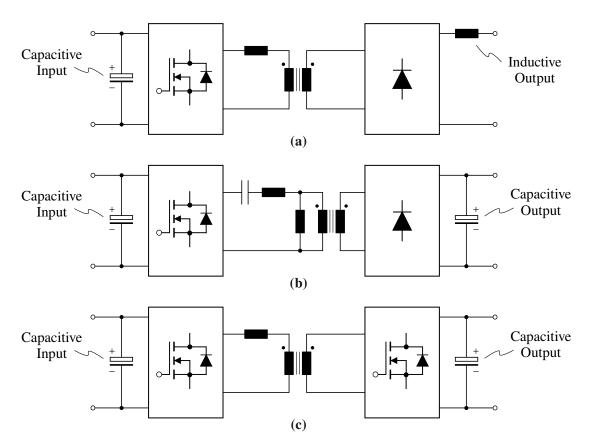

**Fig. 1.2:** Equivalent circuit schematic of the two most adopted ultra-fast charger architectures, addressing the galvanic isolation requirement (**a**) with a line-frequency transformer connected to the grid and (**b**) with a high-frequency transformer located within the DC/DC stage.

system acts as an unearthed IT power supply system, allowing the driver to safely touch the car in the presence of one isolation fault. This requirement can be approached in two different ways, which lead to two different charger architectures [5]. The first architecture is shown in **Fig. 1.2(a)** and provides the galvanic isolation by means of a conventional line-frequency transformer connected to the grid, followed by a rectifier (i.e., AC/DC) stage and a non-isolated DC/DC stage to address the wide output voltage range. The second architecture, reported in **Fig. 1.2(b)**, features an AC/DC stage directly connected to the grid and implements the galvanic isolation within the DC/DC converter stage by means of a high-frequency transformer, allowing to significantly reduce the overall system volume. For this reason, the second architecture is the most adopted in practice and is the one considered herein.

## **1.2 Goals and Research Contributions**

The main goal of this dissertation is to analyze, design, control and assess experimentally a modular converter concept for EV ultra-fast charging, addressing all requirements and challenges reported in **Section 1.1.1**. In particular, in view of the strict requirements in terms of reliability and cost-effectiveness, only silicon (Si) semiconductor devices are considered, aiming to quantify the performance achievable by a full-Si ultra-fast charger implementation with state-of-the-art Si technology.

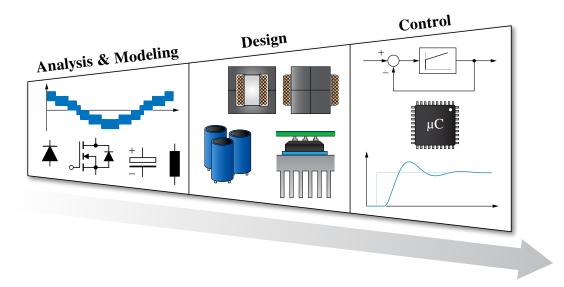

The research contributions of this thesis can be organized under three main categories, as illustrated in **Fig. 1.3**:

- ► Converter analysis and modeling. The stresses on all active and passive components (i.e., semiconductors, capacitors, inductors, transformers) are analyzed in detail and several approximate analytical expressions, useful for the converter design and assessment, are obtained for the first time. Furthermore, approximate small-signal models of both the AC/DC and the DC/DC converter stages are derived, providing straightforward tools for the design and tuning of the closed-loop controllers. In particular, a novel simplified dual first-order small-signal model for LLC resonant converter is proposed.

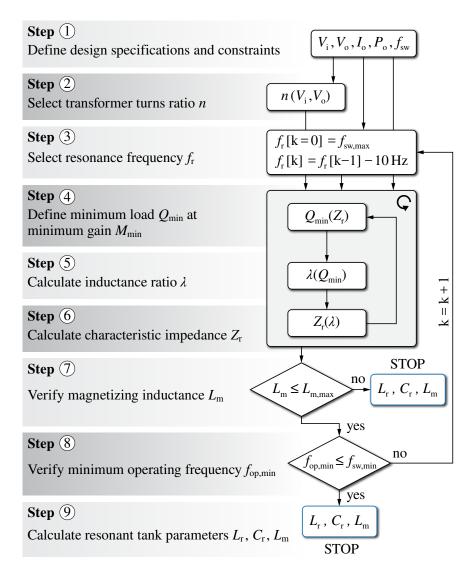

- ► *Converter design.* A complete step-by-step design procedure of both converter stages is provided, including the selection of the semiconductor devices, the sizing of the capacitors, the multi-objective optimization of the magnetic components and the sizing of the heat dissipation system. In particular, a novel iterative design procedure for LLC resonant converters is proposed, aimed at identifying the optimal parameter values that minimize the converter conduction losses.

- Converter control. High-performance digital multi-loop control strategies are proposed for both the AC/DC and the DC/DC converter stages, aiming to maximize the control dynamics and disturbance rejection capabilities. Furthermore, the derived small-signal models are exploited to provide straightforward design/tuning procedures for all control loops.

**Fig. 1.3:** Overview of the three main subjects of this dissertation: converter analysis and modeling, converter design, converter control. All research contributions belong to one of these categories.

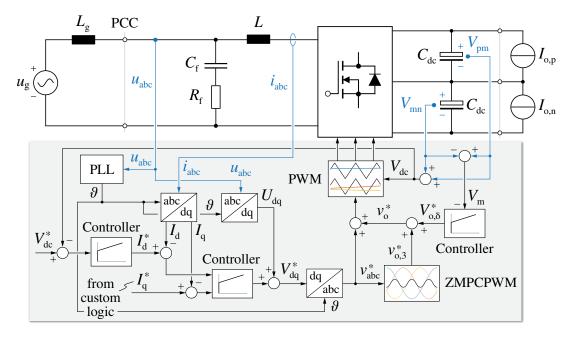

## **1.3** Specifications and Architecture

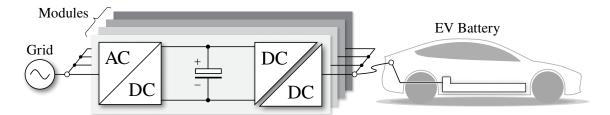

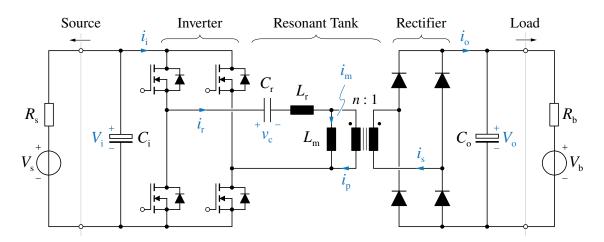

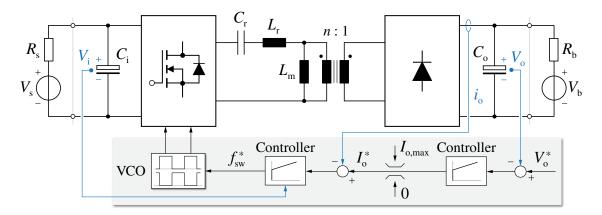

The considered ultra-fast charger architecture consists of two converter stages, as shown in **Fig. 1.4** (cf. **Fig. 1.2(b)**). The first stage is a three-phase grid-connected AC/DC converter with unity power factor correction capabilities. The role of this stage is to absorb the total amount of charging power from the grid, meanwhile ensuring sinusoidal input currents (i.e., with low distortion and harmonics). The second stage is a high-frequency DC/DC converter, which provides the galvanic isolation from the main distribution grid and regulates the charging process by controlling the output current.

In view of the high target nominal power of ultra-fast chargers (cf. Section 2.1.1), the full power is typically addressed with a modular approach, i.e. paralleling multiple converter units rated at a fraction of the total power. The modularity provides several advantages [43], as it allows to benefit from economies-of-scale, increases the total converter reliability, improves the thermal management, ensures an upgradable system and enables the disconnection of some units at light load to preserve efficiency. On the other hand, the use of multiple paralleled units increases the overall system complexity, particularly at the control level. For instance, the DC/DC units cannot be controlled independently when operating in constant-voltage (CV) charging, as only one unit must control the output voltage (i.e., behaving as a voltage source) and send the output current references to the others (i.e., behaving as current sources) [44, 45]. Nonetheless, this issue can be addressed by adopting a master/slave control hierarchy.

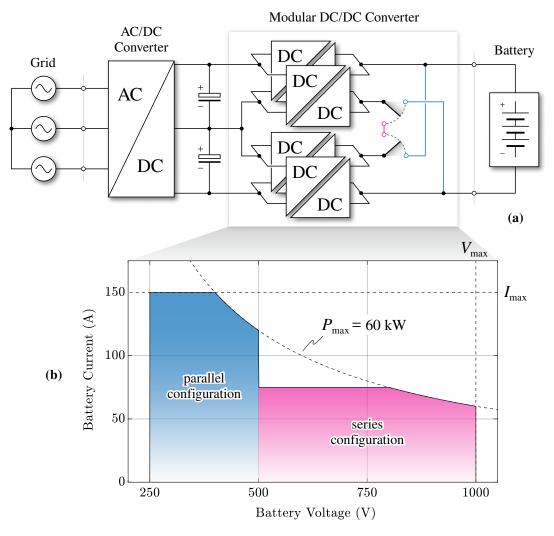

Besides having to employ only Si semiconductor devices (i.e., due to their high maturity, reliability and cost-effectiveness), the considered converter module must comply with the target specifications and operating conditions summarized in **Table 1.3**. In particular, considering the relatively high power rating (i.e., 60 kW) and the wide output voltage range (i.e., 250-1000 V), and leveraging the split DC-link provided by the three-level AC/DC stage (cf. **Chapter 2**), the DC/DC converter stage is split into 4x15 kW units with reconfigurable series/parallel outputs, as schematically represented in **Fig. 1.5(a)**. This architecture is already adopted in industry [32] and allows to reduce by a factor of two the output voltage range to be addressed by the single unit (i.e., from 250-1000 V to

Fig. 1.4: Typical EV ultra-fast charger architecture, consisting of several converter modules in parallel.

| Nominal | Input     | Input          | Input                 | Output     | Output  | Nominal    |

|---------|-----------|----------------|-----------------------|------------|---------|------------|

| Power   | Frequency | Voltage        | Current               | Voltage    | Current | Efficiency |

| 60 kW   | 50 Hz     | $400  V_{RMS}$ | 86.5 A <sub>RMS</sub> | 250-1000 V | 150 A   | >95.5%     |

Tab. 1.3: Specifications and operating conditions of the considered ultra-fast charger module.

**Fig. 1.5:** (a) equivalent circuit schematic of the architecture of the considered 60 kW DC fast charger module and (b) highlight of the output voltage/current feasible operating region assuming reconfigurable (i.e., series/parallel) DC/DC converter outputs.

250-500 V), significantly improving the achievable converter performance. Furthermore, the power split allows to simplify the realization of the magnetic components, to employ discrete semiconductor devices without the need of hard-paralleling and to turn-off one or more modules at light load operation, ensuring higher efficiency over the complete charging range (cf. **Chapter 6**). The feasible operating region of the 60 kW converter module is shown in **Fig. 1.5(b)**, where the maximum converter output current  $I_{max}$ , voltage

$V_{\text{max}}$  and power  $P_{\text{max}}$  limits are indicated. The two output voltage intervals corresponding to the two different DC/DC converter configurations are highlighted.

It is worth noting that a nominal efficiency > 95.5% is targeted, aiming to outperform all commercially available EV ultra-fast chargers (cf. **Table 1.1**). Since the considered converter module consists of two stages, an efficiency target of 98.5\% is set for the AC/DC stage and, consequently, a minimum efficiency target of 97\% is obtained for the DC/DC stage.

## **1.4 Outline of the Thesis**

This thesis consists of two parts (with three chapters each) and a conclusive chapter. The content of each chapter is summarized here.

## PART I: AC/DC Converter

#### Chapter 2: Analysis

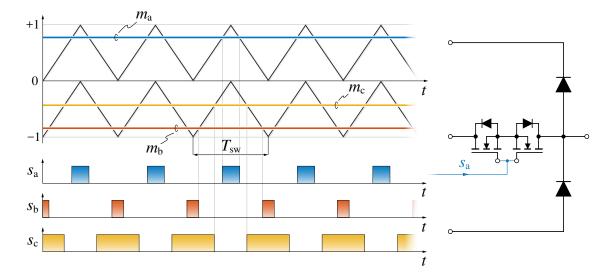

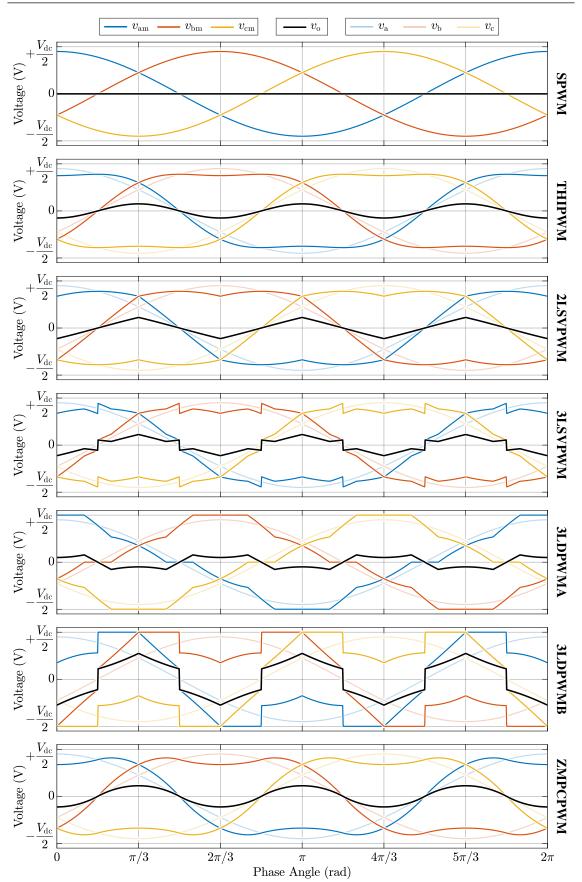

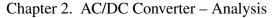

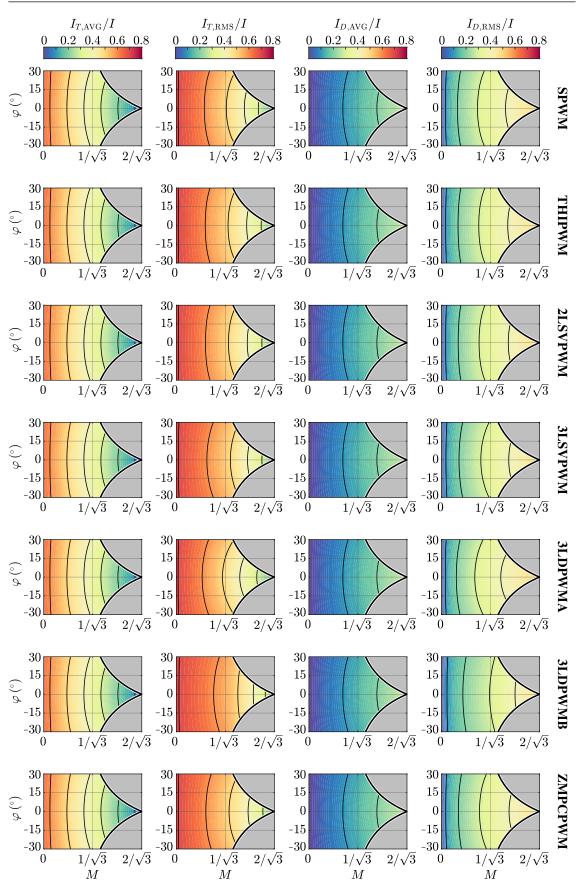

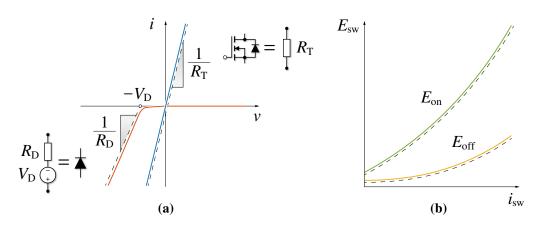

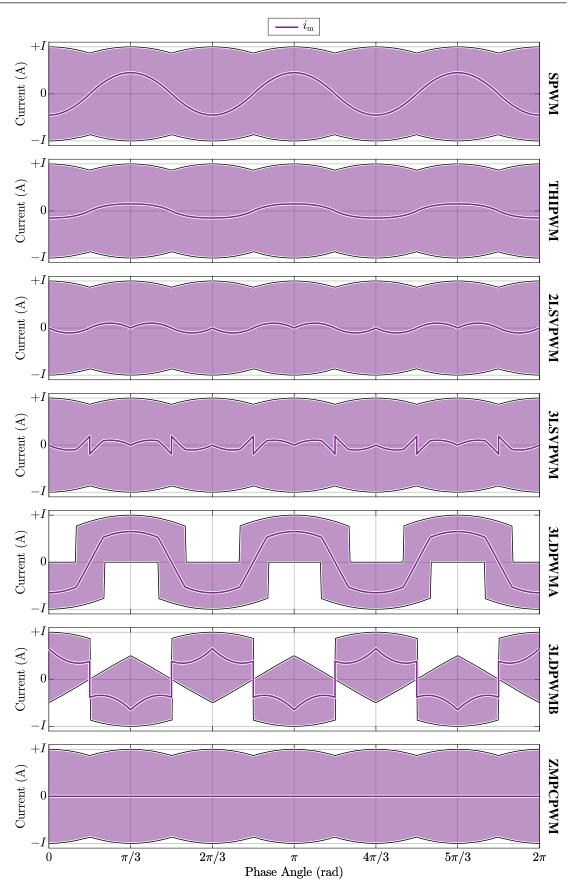

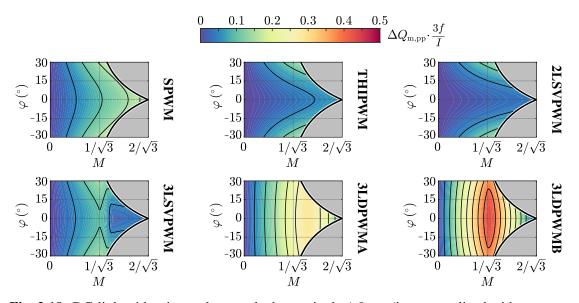

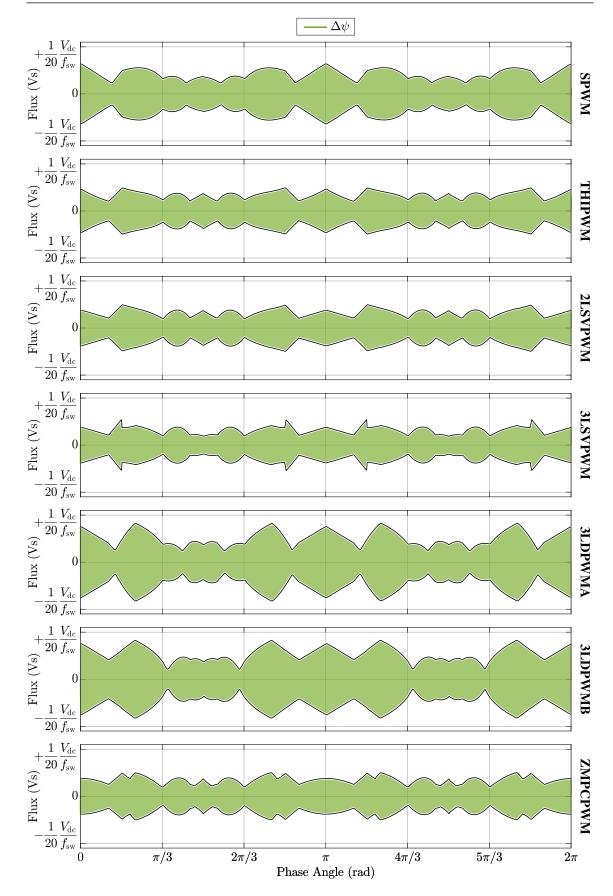

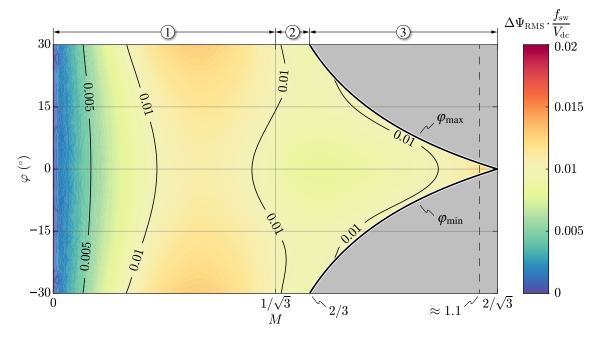

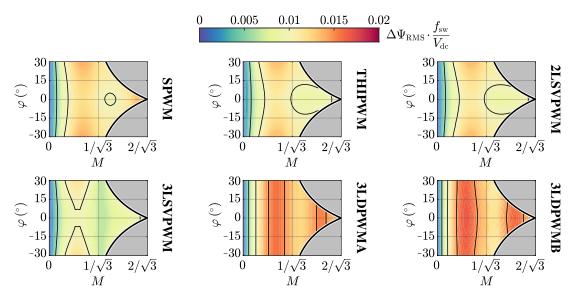

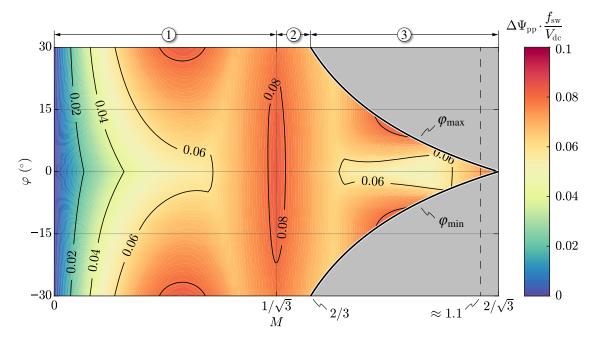

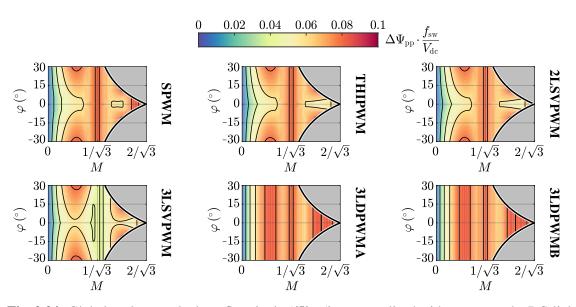

The requirements of the AC/DC stage are introduced and an overview of the existing three-phase pulse-width modulated (PWM) converter topologies for general active rectification is provided, leading to the selection of a unidirectional three-level T-type structure. Therefore, the operational basics of three-level rectifiers are described, including a detailed analysis of the converter operating limits. Moreover, the converter modulation process is explained and seven different modulation strategies are introduced. Finally, the stresses on the converter active and passive components (i.e., semiconductor losses, DC-link RMS current and charge ripple, AC-side inductor RMS and peak-to-peak flux ripple) are estimated analytically and/or numerically for all modulation strategies, providing straightforward tools for the converter design and preliminary assessment.

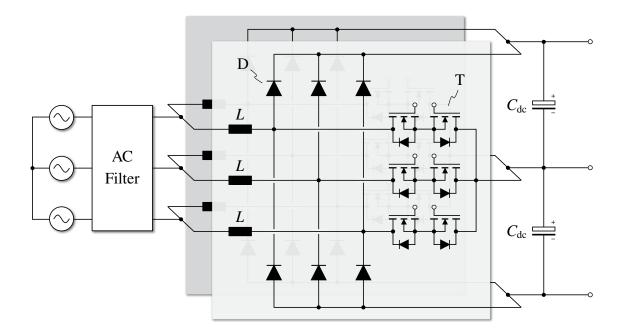

#### Chapter 3: Design

The complete design methodology of the considered 60 kW three-level unidirectional T-type rectifier is outlined. In view of the high target nominal power, a dual three-phase converter structure is adopted, halving the current rating of each bridge-leg and thus allowing for the adoption of discrete Si semiconductor devices. Therefore, the step-by-step converter design procedure is described, including the selection, sizing and/or optimization of all main converter active and passive components, i.e. the semiconductor devices, the DC-link capacitors, the AC-side inductors and the heat dissipation system (i.e., heatsink and fans). Finally, a converter prototype is built and its performance in terms of loss and efficiency is assessed experimentally.

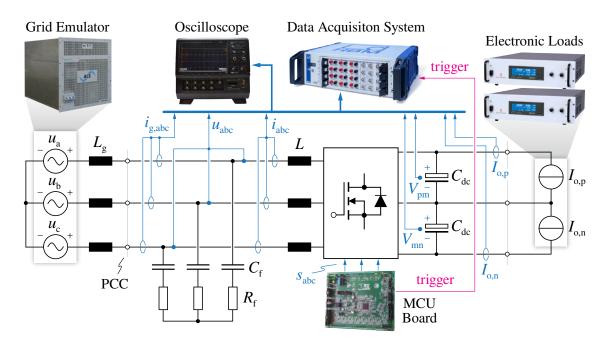

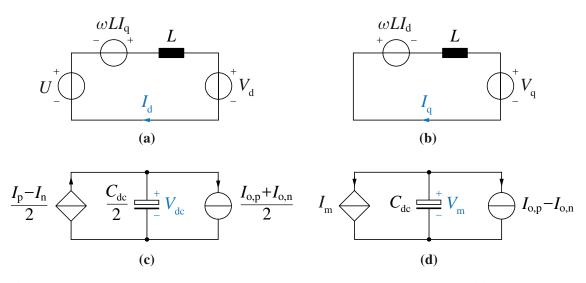

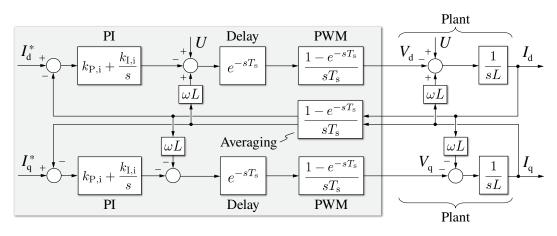

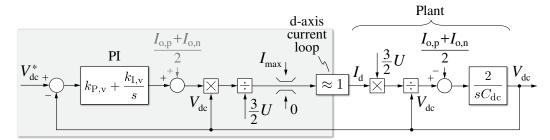

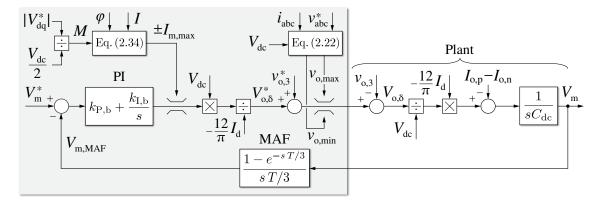

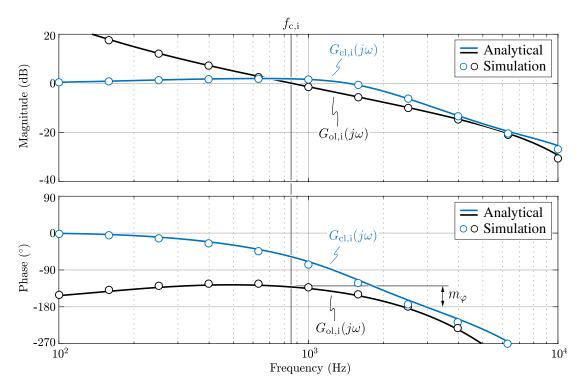

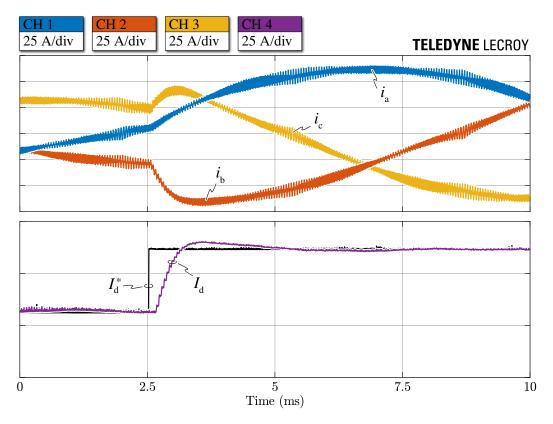

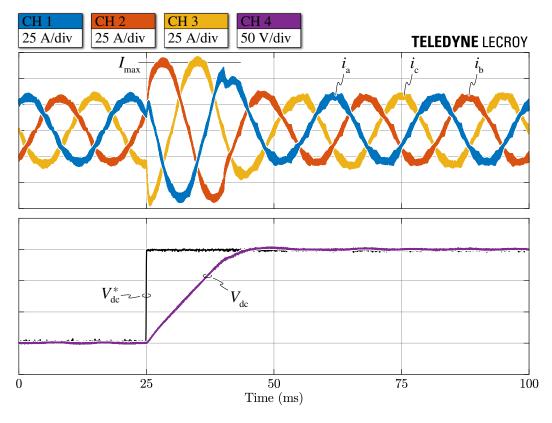

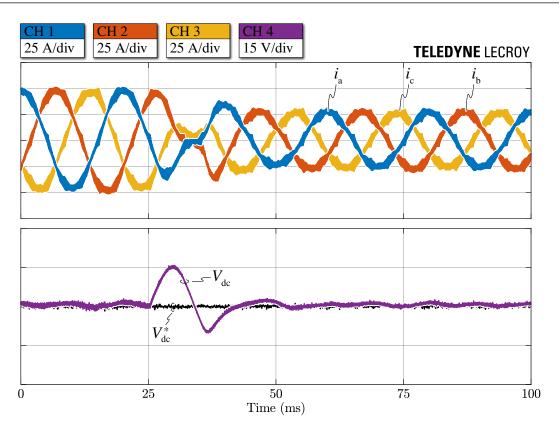

#### Chapter 4: Control

This chapter focuses on the design, tuning and experimental assessment of a highperformance digital multi-loop control strategy for the considered three-level unidirectional T-type rectifier, aiming at minimum phase current distortion under all operating conditions (e.g., non-unity power factor, unbalanced split DC-link loading), fast response dynamics and strong disturbance rejection. To accurately design the four control loops (i.e., dq-currents, DC-link voltage, DC-link mid-point voltage deviation), the system state-space equations are described and the small-signal model of the three-level rectifier is derived. The controllers are then tuned leveraging analytical expressions, taking into account the delays and the discretization introduced by the digital control implementation. Finally, the steady-state and dynamical performance of the proposed multi-loop control strategy is verified in circuit simulation and experimentally on the T-type rectifier prototype, adopting a general purpose microcontroller unit (MCU) for the digital control implementation.

#### PART II: DC/DC Converter

#### ► Chapter 5: Analysis

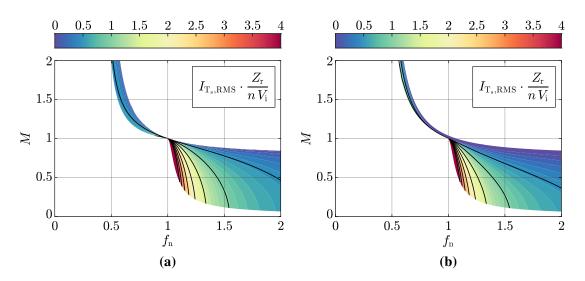

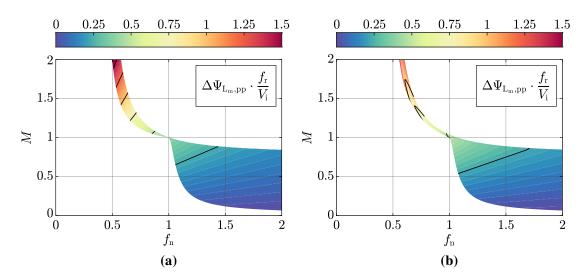

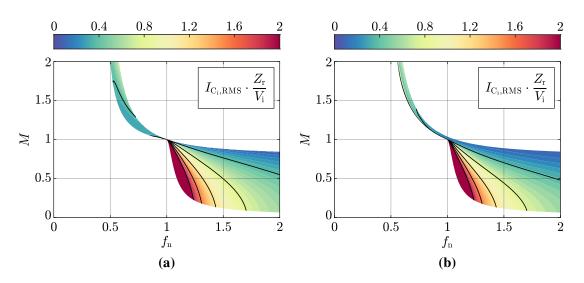

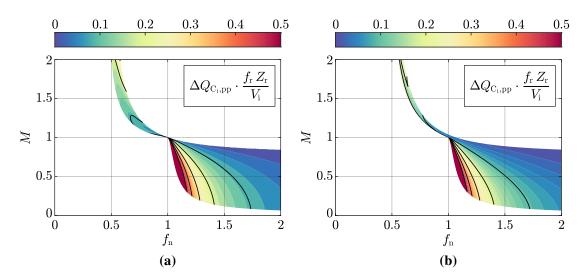

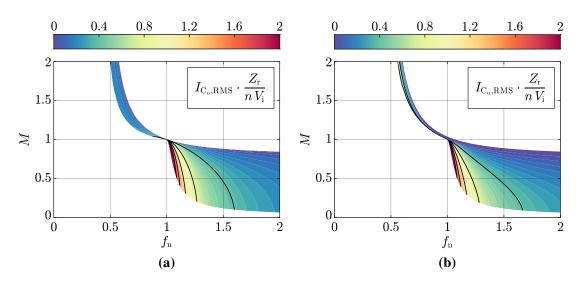

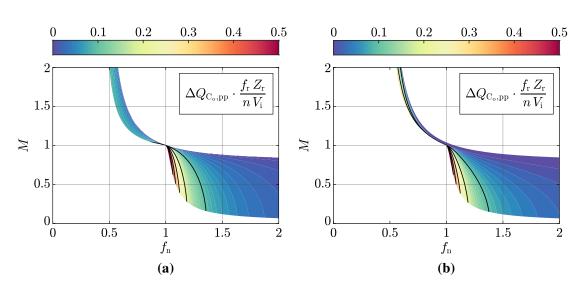

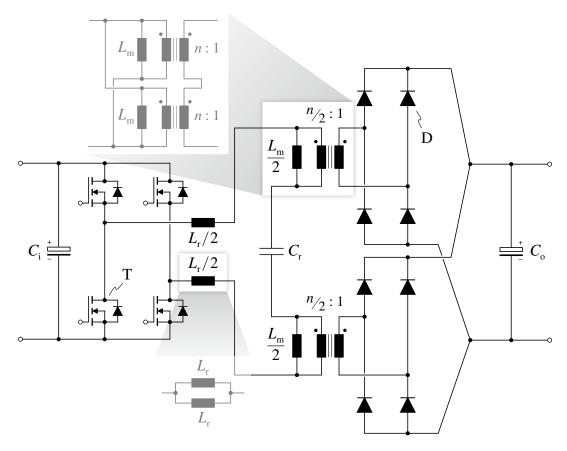

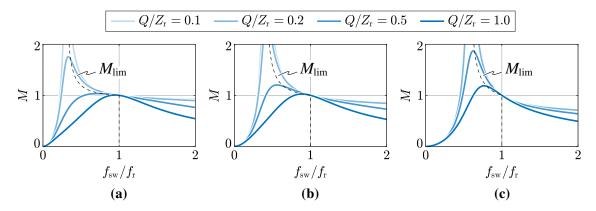

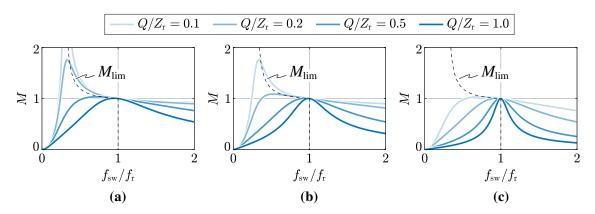

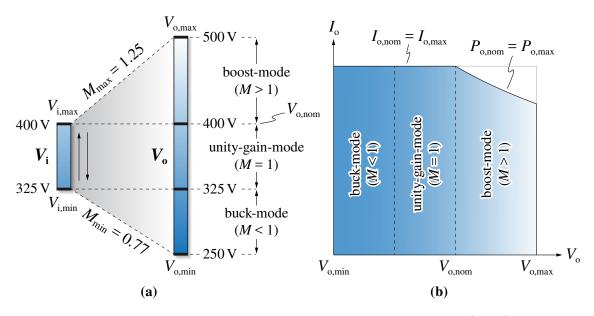

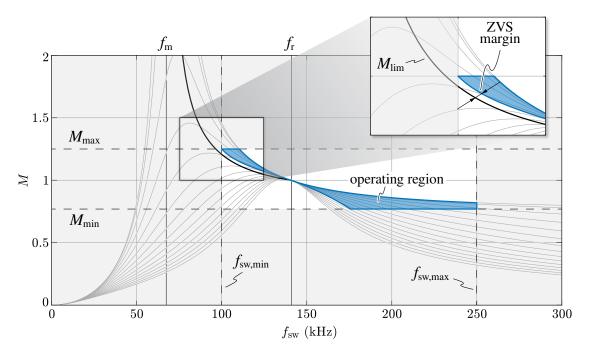

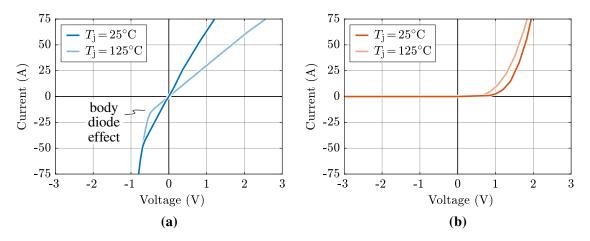

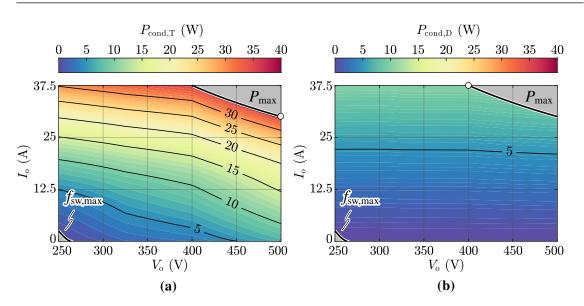

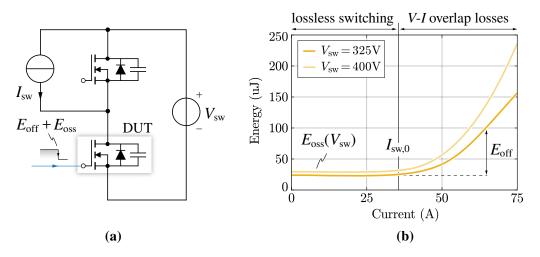

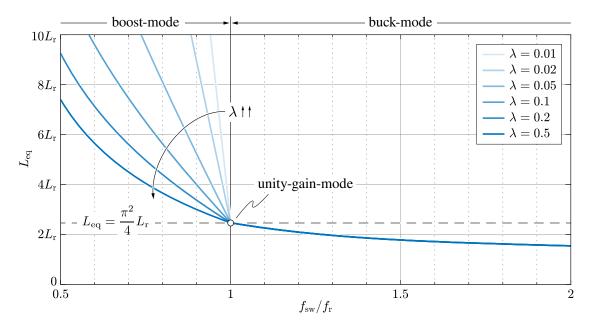

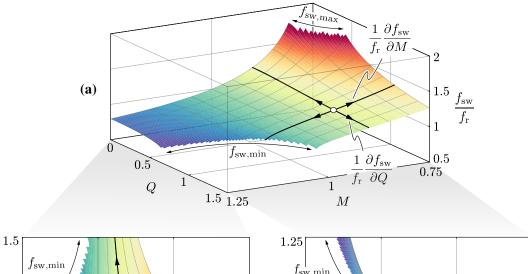

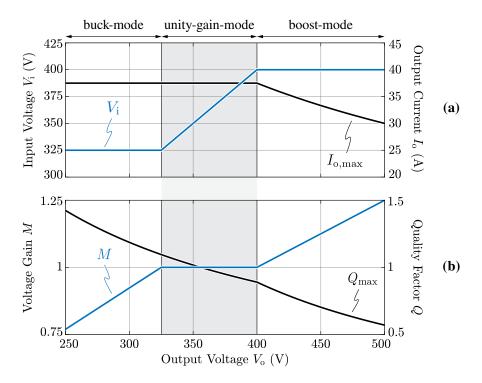

An overview of the most adopted topologies for EV battery charging is provided and a resonant LLC converter is selected for the present 4x15 kW application, due to its unmatched efficiency and wide output load/voltage regulation capability. The operating principle of the LLC converter is described, leveraging the first harmonic approximation (FHA) method to identify the converter operating limits in terms of switching frequency, input/output voltage gain and output load. Furthermore, the three typical modes of operation of the LLC converter (i.e., boost-mode, unity-gain-mode, buck-mode) are described in detail and the soft-switching mechanisms of the primary-side transistors and secondary-side diodes are explained. Finally, the stresses on the converter active and passive components (i.e., semiconductor devices, resonant capacitor, resonant inductor, transformer, input/output filter capacitors) are assessed both analytically with FHA and numerically with the more accurate time-domain analysis (TDA), providing straightforward tools for the converter design and/or assessment.

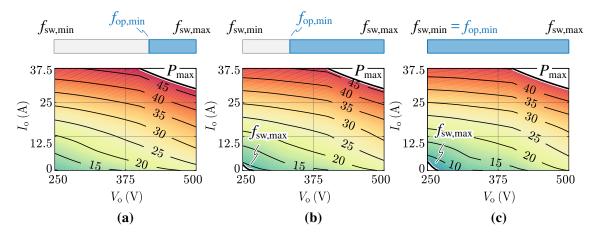

#### Chapter 6: Design

A novel iterative design procedure for resonant LLC converters is proposed and applied to the considered modular 4x15 kW application, aiming to minimize the total converter conduction losses. In view of the high target nominal power, an unconventional LLC circuit structure is adopted to split the current/voltage ratings of the magnetic components (i.e., resonant inductors, transformers) and the current rating of the output rectifier diodes (i.e., allowing for the adoption of discrete Si

semiconductor devices). Once the main converter parameters are determined by the proposed design procedure, the selection, sizing and/or optimization of all main converter active and passive components is carried out, including the semiconductor devices, the resonant capacitor, the resonant inductors, the isolation transformers, the input/output filter capacitors and the heat dissipation system (i.e., heatsink and fans). Finally, a 15 kW LLC converter prototype is built and its performance in terms of loss and efficiency is assessed experimentally.

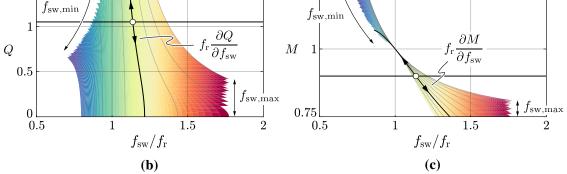

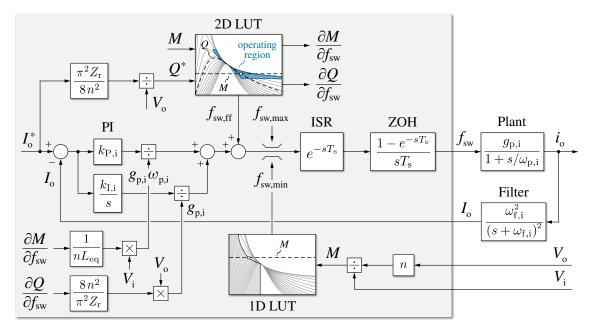

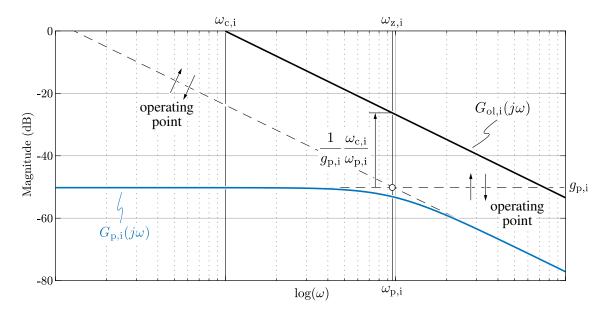

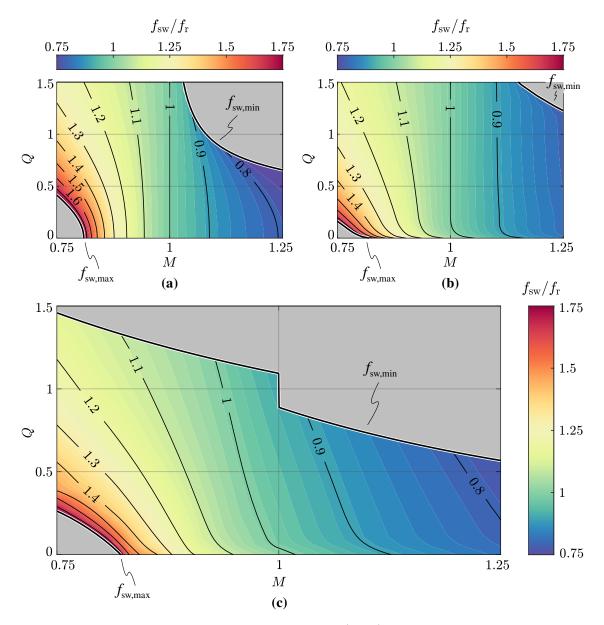

#### Chapter 7: Control

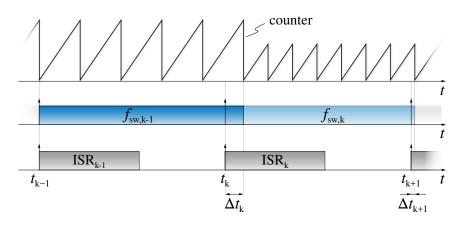

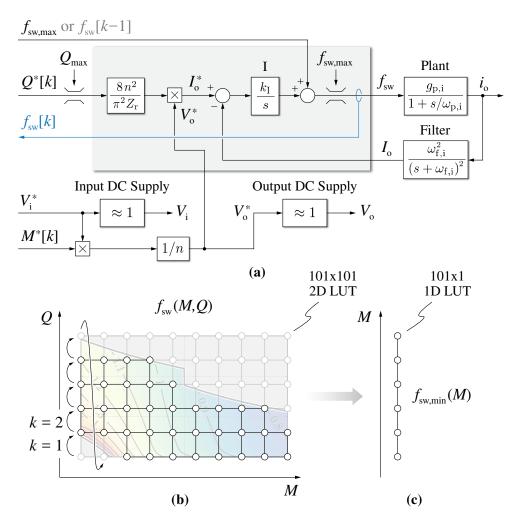

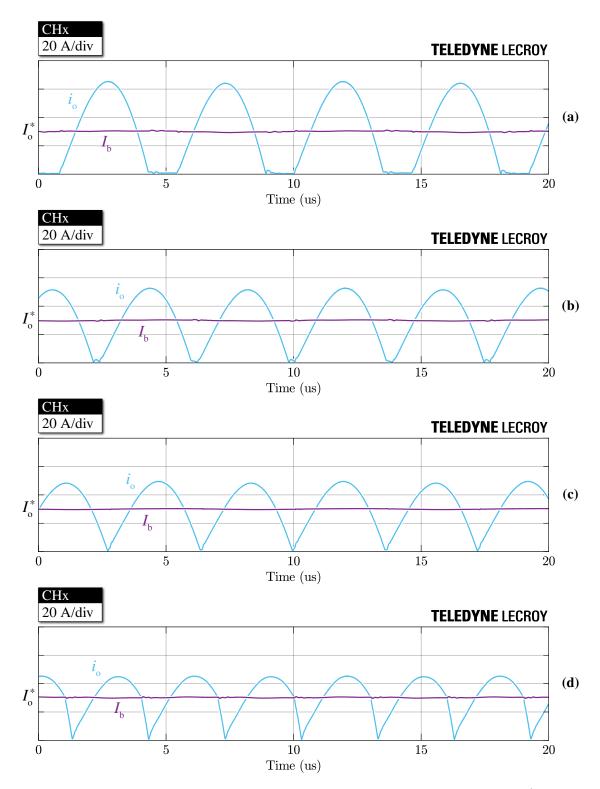

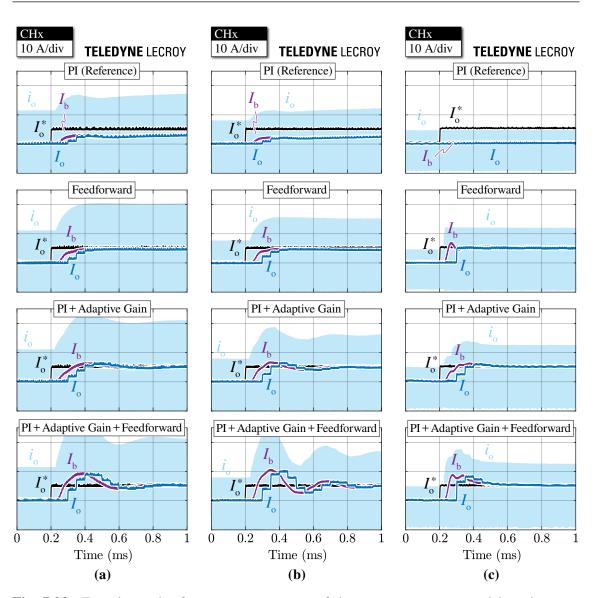

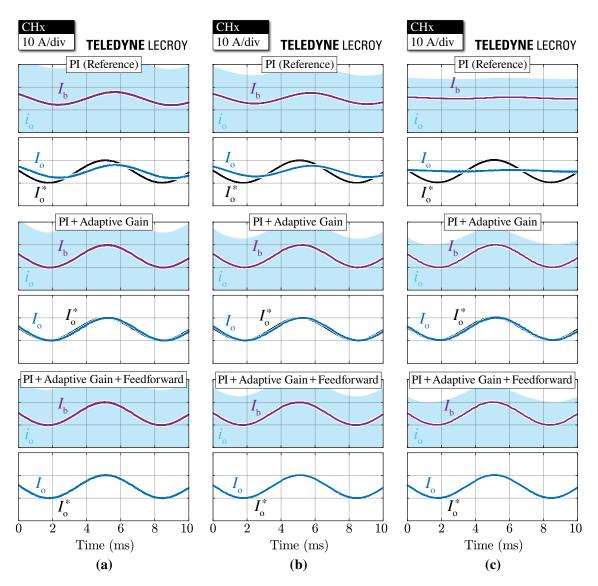

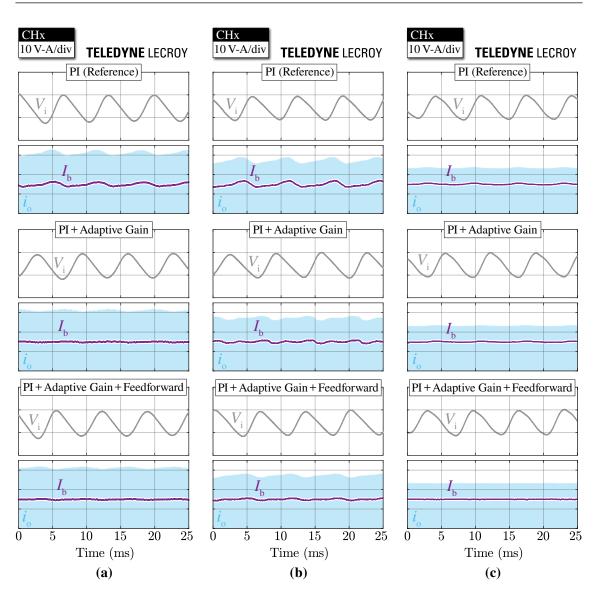

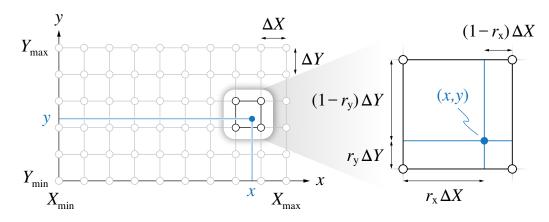

This chapter focuses on the design, tuning and experimental assessment of a highperformance digital multi-loop control strategy for the considered LLC resonant converter, aiming at constant closed-loop bandwidth, fast response dynamics and strong disturbance rejection across the complete converter operating region. The control scheme consists of two cascaded voltage and current loops. To design and tune these controllers, a novel simplified LLC dual first order small-signal model is proposed. The system non-linear behavior affecting the current control loop is counteracted by a real-time controller gain adaptation process, which ensures constant control bandwidth. In particular, the adaptive gain values are provided by a static switching frequency look-up table (LUT) obtained experimentally. Moreover, the steady state switching frequency value is fed forward at the output of the current loop regulator, providing a further dynamical performance enhancement. Finally, the steady-state and dynamical performance of the current control loop are verified both in circuit simulation and experimentally on the LLC converter prototype, adopting a general purpose MCU for the digital control implementation.

#### **Conclusion and Outlook**

Chapter 8

The content of this thesis is summarized in this chapter, highlighting the most significant findings and research contributions. Furthermore, an outlook on potential improvements and future developments is provided.

## **1.5 List of Publications**

The publications developed during this Ph.D. (i.e., 10 journal articles, 16 conference papers, 3 patent applications) have been the result of different projects and activities, either related or unrelated to the thesis core topic. In the following, the publications are reported in reverse chronological order.

## **Journal Articles**

*Related* to the thesis core topic:

- ▶ D. Cittanti, M. Gregorio, E. Vico, F. Mandrile, E. Armando, and R. Bojoi, "High Performance Digital Multi-Loop Control of LLC Resonant Converters for EV Fast Charging with LUT-Based Feedforward and Adaptive Gain", *Transactions on Industry Applications (Early Access)*, May 2022, DOI: 10.1109/TIA.2022.3178394.

- D. Cittanti, M. Gregorio, E. Bossotto, F. Mandrile, and R. Bojoi, "Three-Level Unidirectional Rectifiers under Non-Unity Power Factor Operation and Unbalanced Split DC-Link Loading: Analytical and Experimental Assessment", *Energies*, vol. 14, no. 17, p. 5280, Aug. 2021, DOI: 10.3390/EN14175280.

- D. Cittanti, M. Gregorio, E. Bossotto, F. Mandrile, and R. Bojoi, "Full Digital Control and Multi-Loop Tuning of a Three-Level T-Type Rectifier for Electric Vehicle Ultra-Fast Battery Chargers", *Electronics*, vol. 10, no. 12, p. 1453, Jun. 2021, DOI: 10.3390/ELECTRONICS10121453.

- D. Cittanti, F. Mandrile, M. Gregorio, and R. Bojoi, "Design Space Optimization of a Three-Phase LCL Filter for Electric Vehicle Ultra-Fast Battery Charging", *Energies*, vol. 14, no. 5, p. 1303, Feb. 2021, DOI: 10.3390/EN14051303.

- ▶ F. Mandrile, **D. Cittanti**, V. Mallemaci, and R. Bojoi, "Electric Vehicle Ultra-Fast Battery Chargers: A Boost for Power System Stability?", *World Electric Vehicle Journal*, vol. 12, no. 1, p. 16, Jan. 2021, DOI: 10.3390/WEVJ12010016.

Unrelated to the thesis core topic:

- D. Cittanti, C. Gammeter, J. Huber, R. Bojoi, and J. W. Kolar, "A Simplified Hard-Switching Loss Model for Fast-Switching Three-Level T-Type SiC Bridge-Legs", *Electronics*, vol. 11, no. 11, p. 1686, May 2022, DOI: 10.3390/ELECTRONICS111 11686.

- D. Cittanti, E. Vico, and R. Bojoi, "New FOM-Based Performance Evaluation of 600/650 V SiC and GaN Semiconductors for Next-Generation EV Drives", *IEEE* Access, vol. 10, pp. 51693-51707, May 2022, DOI: 10.1109/ACCESS.2022.3174777.

- D. Cittanti, M. Guacci, S. Mirić, R. Bojoi, and J. W. Kolar, "Analysis and Performance Evaluation of a Three-Phase Sparse Neutral Point Clamped Converter for Industrial Variable Speed Drives", *Electrical Engineering*, vol. 104, no. 2, pp. 623–642, Apr. 2022, DOI: 10.1007/S00202-021-01290-W.

- D. Cittanti, M. Gregorio, F. Mandrile, and R. Bojoi, "Full Digital Control of an All-Si On-Board Charger Operating in Discontinuous Conduction Mode", *Electronics*, vol. 10, no. 2, p. 203, Jan. 2021, DOI: 10.3390/ELECTRONICS10020203.

- S. Rubino, R. Bojoi, D. Cittanti, and L. Zarri, "Decoupled and Modular Torque Control of Multi-Three-Phase Induction Motor Drives", *IEEE Transactions on Industry Applications*, vol. 56, no. 4, pp. 3831–3845, Jul. 2020, DOI: 10.1109/TIA. 2020.2991122.

## **Conference Papers**

*Related* to the thesis core topic:

- D. Cittanti, E. Vico, M. Gregorio, and R. Bojoi, "Design and Experimental Assessment of a 60 kW All-Si Three-Phase Six-Leg T-Type Rectifier for Electric Vehicle Ultra-Fast Charging", in *Proc. of the International Conference on Electrical, Computer, Communications and Mechatronics Engineering (ICECCME)*, Mauritius, Oct. 2021, DOI: 10.1109/ICECCME52200.2021.9590926.

- D. Cittanti and R. Bojoi, "Modulation Strategy Assessment for 3-Level Unidirectional Rectifiers in Electric Vehicle Ultra-Fast Charging Applications", in *Proc. of the AEIT International Conference of Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE)*, Torino, Italy, Nov. 2020, DOI: 10.23919/AEIT AUTOMOTIVE50086.2020.9307416.

- D. Cittanti, E. Vico, M. Gregorio, F. Mandrile, and R. Bojoi, "Iterative Design of a 60 kW All-Si Modular LLC Converter for Electric Vehicle Ultra-Fast Charging", in *Proc. of the AEIT International Conference of Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE)*, Torino, Italy, Nov. 2020, DOI: 10.23919/AE ITAUTOMOTIVE50086.2020.9307381.

- D. Cittanti, M. Gregorio, E. Armando, and R. Bojoi, "Digital Multi-Loop Control of an LLC Resonant Converter for Electric Vehicle DC Fast Charging", in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE)*, Detroit, MI, USA, Oct. 2020, DOI: 10.1109/ECCE44975.2020.9236177.

- D. Cittanti, F. Mandrile, and R. Bojoi, "Optimal Design of Grid-Side LCL Filters for Electric Vehicle Ultra-Fast Battery Chargers", in *Proc. of the International Universities Power Engineering Conference (UPEC)*, Torino, Italy, Sep. 2020, DOI: 10.1109/UPEC49904.2020.9209771.

D. Cittanti, M. Gregorio, and R. Bojoi, "Digital Multi-Loop Control of a 3-Level Rectifier for Electric Vehicle Ultra-Fast Battery Chargers", in *Proc. of the AEIT International Annual Conference (AEIT)*, Catania, Italy, Sep. 2020, DOI: 10.23919/ AEIT50178.2020.9241196.

*Unrelated* to the thesis core topic:

- ▶ **D. Cittanti**, E. Vico, F. Mandrile, E. Armando, and R. Bojoi, "Analysis and Conceptualization of a Single-Phase Buck-Boost Integrated EV On-Board Charger Based on a Double Bridge Inverter Drive System", in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE)*, Detroit, MI, USA, Oct. 2022 (accepted for publication).

- ▶ F. Stella, E. Vico, **D. Cittanti**, C. Liu, T. Wu, L. Xiong, and R. Bojoi, "Design and Testing of an Automotive Compliant 800 V 550 kVA SiC Traction Inverter with Full-Ceramic DC-Link and EMI Filter", in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE)*, Detroit, MI, USA, Oct. 2022 (accepted for publication).

- D. Cittanti, E. Vico, E. Armando, and R. Bojoi, "Analysis and Conceptualization of a 400 V 100 kVA Full-GaN Double Bridge Inverter for Next-Generation Electric Vehicle Drives", in *Proc. of the IEEE Transportation Electrification Conference and Exhibition (ITEC)*, Anaheim, CA, USA, Jun. 2022, DOI: 10.1109/ITEC53557.2022. 9813847.

- ▶ D. Cittanti, F. Stella, E. Vico, C. Liu, J. Shen, G. Xiu, and R. Bojoi, "Analysis and Design of a High Power Density Full-Ceramic 900 V DC-Link Capacitor for a 550 kVA Electric Vehicle Drive Inverter", in *Proc. of the International Power Electronics Conference (IPEC ECCE Asia)*, Himeji, Japan, May 2022, DOI: 10.23 919/IPEC-HIMEJI2022-ECCE53331.2022.9807220.

- D. Cittanti, E. Vico, E. Armando, and R. Bojoi, "Analysis and Conceptualization of a 800 V 100 kVA Full-GaN Three-Level Flying Capacitor Inverter for Next-Generation Electric Vehicle Drives", in *Proc. of the International Power Electronics Conference* (*IPEC – ECCE Asia*), Himeji, Japan, May 2022, DOI: 10.23919/IPEC-HIMEJI2022-ECCE53331.2022.9807091.

- D. Cittanti, V. Mallemaci, F. Mandrile, S. Rubino, R. Bojoi, and A. Boglietti, "PWM-Induced Losses in Electrical Machines: An Impedance-Based Estimation Method", in *Proc. of the International Conference on Electrical Machines and Systems (ICEMS)*, Gyeongju, Korea, Oct. 2021, DOI: 10.23919/ICEMS52562.2021. 9634438.

- J. W. Kolar, J. A. Anderson, S. Mirić, M. Haider, M. Guacci, M. Antivachis, G. Zulauf, D. Menzi, P. S. Niklaus, J. Miniböck, P. Papamanolis, G. Rohner, N. Nain, D. Cittanti, and D. Bortis, "Application of WBG Power Devices in Future 3-Φ Variable Speed Drive Inverter Systems: How to Handle a Double-Edged Sword", in *Proc. of the IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, Dec. 2020, DOI: 10.1109/IEDM13553.2020.9372022.

- D. Cittanti, M. Guacci, S. Mirić, R. Bojoi, and J. W. Kolar, "Comparative Evaluation of 800 V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives", in *Proc. of the International Conference on Electrical Machines and Systems (ICEMS)*, Hamamatsu, Japan, Nov. 2020, DOI: 10. 23919/ICEMS50442.2020.9291123.

- S. Rubino, R. Bojoi, D. Cittanti, and L. Zarri, "Decoupled Torque Control of Multiple Three-Phase Induction Motor Drives", in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE)*, Baltimore, MD, USA, Sep. 2019, DOI: 10.1109/ ECCE.2019.8912502.

- S. Borlo, D. Cittanti, M. Gregorio, F. Mandrile, and S. Musumeci, "Comparative CCM-DCM Design Evaluation of Power Inductors in Interleaved PFC Stage for Electric Vehicle Battery Chargers", in *Proc. of the International Conference on Clean Electrical Power (ICCEP)*, Otranto, Italy, Jul. 2019, DOI: 10.1109/ICCEP.20 19.8890112.

### Patents

- D. Cittanti, F. Mandrile, E. Vico, E. Armando, and R. Bojoi, "Caricabatterie Integrato per Veicoli Elettrici basato su Topologia a Doppio Ponte Trifase e Metodo di Controllo", IT Patent, 2022 (application in process).

- F. Stella, E. Vico, D. Cittanti, C. Liu, J. Shen, G. Xiu, and R. Bojoi, "Adaptive Desaturation Detection for Precise Overcurrent Protection of Power Semiconductors", CN Patent, 2021 (application in process).

- F. Stella, E. Vico, D. Cittanti, C. Liu, J. Shen, G. Xiu, and R. Bojoi, "Integrated Common and Differential Mode Filter Inductor with Dual Material Magnetic Core", CN Patent, 2021 (application in process).

# PART I AC/DC Converter

# Chapter 2

# AC/DC Converter – Analysis

#### - Abstract

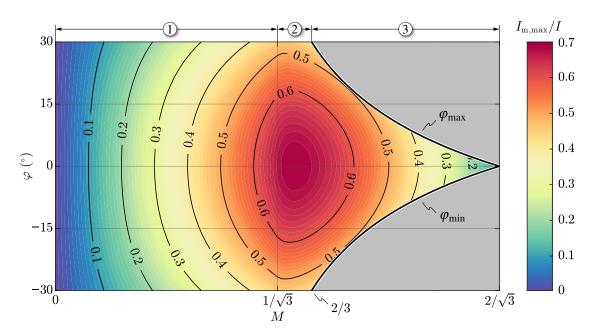

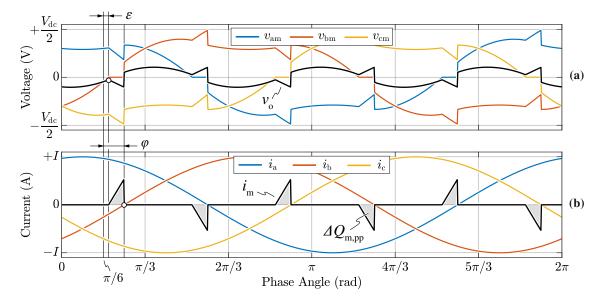

The AC/DC conversion stage of an electric vehicle (EV) ultra-fast battery charger must absorb the total charging power from the grid, meanwhile ensuring sinusoidal input current shaping with low harmonic content. Due to the strict conversion efficiency and power density targets set by the application, pulse-width modulated (PWM) active rectifiers are the most suitable converter candidates, ensuring lower current distortion, wider regulation capability and higher overall performance with respect to passive and/or hybrid rectification solutions. In this chapter, an overview of the existing three-phase PWM converter topologies for general active rectification is provided and a unidirectional three-level T-type structure is selected for the present 60 kW application. The operational basics of three-level unidirectional rectifiers are described, including a detailed analysis of the converter operating limits in terms of e.g., modulation index (i.e., voltage range), power factor angle (i.e., reactive power capability) and DC-link mid-point current (i.e., operation under unbalanced split DC-link loading). Moreover, the converter modulation process is explained and seven different modulation strategies are introduced. Finally, the stresses on the converter active and passive components (i.e., semiconductor losses, DC-link RMS current and charge ripple, AC-side inductor RMS and peak-to-peak flux ripple) are assessed analytically and/or numerically for all modulation strategies, providing straightforward tools for the converter design.

## 2.1 Introduction

The grid-tied AC/DC converter of an EV ultra-fast battery charger has the fundamental role of supplying the subsequent DC/DC conversion stage with the total amount of charging power. In doing so, the AC/DC converter must ensure:

- regulated output (i.e., DC-link) voltage, as this should not be affected by the variation of the grid voltage and/or the charging power;

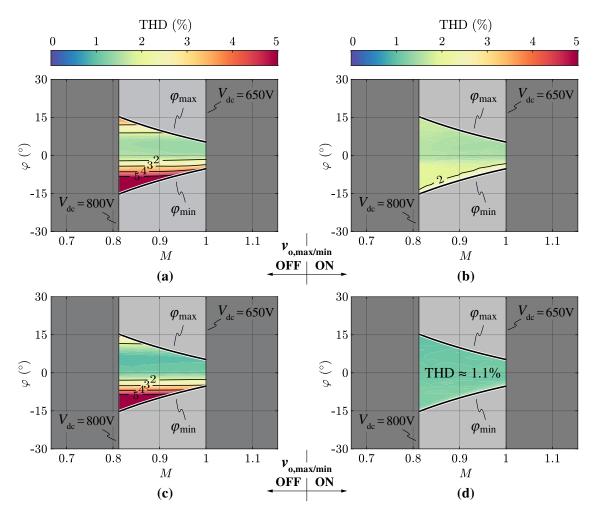

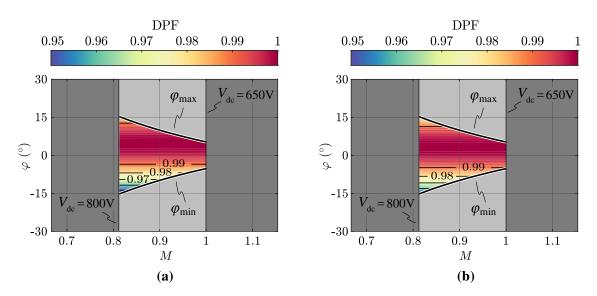

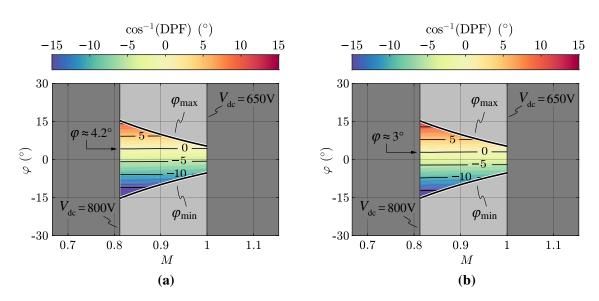

- ▶ sinusoidal input current with limited harmonics (i.e., according to IEEE 519 [10, 11]) and a total harmonic distortion (THD) lower than 5 %;

- ohmic-equivalent grid behavior with a displacement power factor (DPF) higher than 0.99;

- ▶ high conversion efficiency and power density.

These requirements directly exclude both passive rectification solutions (e.g., diode rectifiers with inductive/capacitive smoothing, multi-pulse rectifiers, etc.) and hybrid rectification solutions (e.g., combinations of diode rectifiers and DC/DC converters, third-harmonic injection systems, etc.), since these systems either fail to comply with the AC-side or DC-side requirements or may not achieve a sufficient trade-off between conversion efficiency and overall converter volume (i.e., including the filtering components) [46, 47]. Therefore, only pulse-width modulated (PWM) active rectifiers, also known as active front-ends (AFEs) or power factor correctors (PFCs), feature the necessary characteristics and performance for the present application.

#### 2.1.1 Converter Topologies

Among three-phase active rectification solutions, a major distinction must be made between voltage-source boost-type rectifiers (i.e., inductive AC-side, capacitive DC-side) and current-source buck-type rectifiers (i.e., capacitive AC-side, inductive DC-side). In particular, boost-type rectifiers can only regulate the output voltage to be higher than the grid line-to-line peak voltage (i.e.,  $V_{\rm II}$ ), whereas buck-type rectifiers can only operate with an output voltage below  $\sqrt{3}/2V_{\rm II}$ . In the present case, only voltage-source boost-type converters are considered, as they typically feature lower complexity, lower semiconductor count and higher efficiency than current-source buck-type solutions, especially considering the practical realization of the bipolar switches required by current-source converters. It is worth noting that the buck-boost functionality of the complete battery charger is ensured by the combination of the DC/DC stage (i.e., featuring a buck-boost characteristic) and the modular, reconfigurable structure of the charging module outlined in **Section 1.3**.

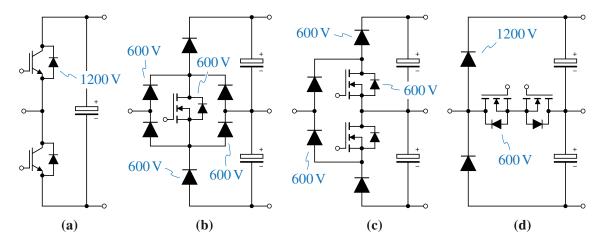

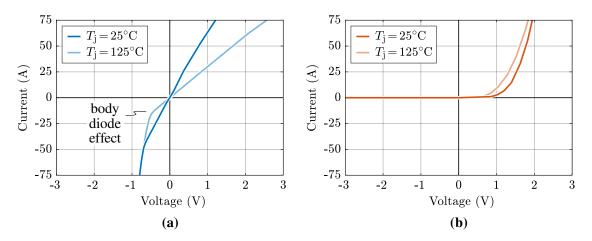

At present, the most widespread topology for three-phase active rectification is the twolevel six-switch rectifier/inverter (cf. **Fig. 2.1(a)**), being simple, well-understood, reliable and intrinsically bidirectional. However, the performance achievable by this converter topology in terms of efficiency/power density trade-off is significantly limited by its two-level output voltage waveform (i.e., requiring large AC-side filtering elements) and by the high voltage rating of the semiconductor devices (i.e., featuring relatively poor conduction and switching characteristics) [48–50]. In particular, assuming a full-Si AC/DC converter realization with a maximum DC-link voltage of 800 V (cf. **Chapter 3**), the two-level bridge-leg structure requires the adoption of 1200 V IGBTs with 1200 V antiparallel diodes, as shown in **Fig. 2.1(a)**. Due to the bipolar nature of IGBTs/diodes (i.e., featuring tail-current and reverse-recovery phenomena) and the high switched voltage, Si-based two-level converters feature poor switching performance and are thus not suited for the present application.

The most effective approach to enhance the overall performance of the rectifier is by adopting multi-level topologies, which simultaneously reduce the stress on the AC-side filter components and allow to employ semiconductor devices with lower voltage rating and thus better figures-of-merit [51]. Nonetheless, as the total count of semiconductor devices and driving circuits scales with the number of introduced levels, the increase in complexity and control effort rapidly counteracts the performance benefits of multi-level topologies, thus limiting the number of practically useful levels in low-voltage applications. Since DC fast chargers typically require unidirectional power flow from the grid to the vehicle, three-level rectifiers represent an attractive alternative to the two-level inverter, trading higher efficiency and power density for a slight complexity increase [46, 47, 52, 53]. In fact, these converter topologies are able to generate a three-level output voltage waveform employing a low number of active switches (i.e., equal or lower with respect to the two-level inverter) and ensuring minimum modulation complexity, as no switching dead-times need to be provided (i.e., each bridge-leg features only one bidirectional bipolar switch that cannot short-circuit the DC-link). Additionally, in three-level rectifiers the active

**Fig. 2.1:** Bridge-leg equivalent circuit schematics of (**a**) the two-level rectifier, (**b**) the three-level VIENNA-type rectifier, (**c**) the three-level NPC-type rectifier, and (**d**) the three-level T-type rectifier. A maximum DC-link voltage of 800 V is assumed and Si IGBTs, MOSFETs and diodes are considered.

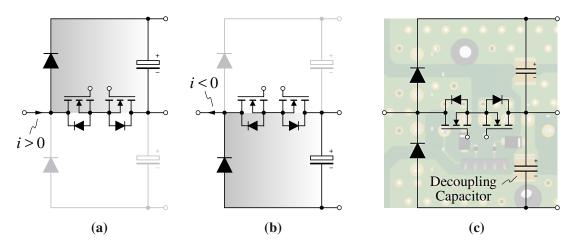

devices must only switch half of the DC-link voltage (i.e., 400 V), allowing for a significant reduction of the switching losses and enabling the adoption of 600 V Si MOSFETs, which feature far better switching characteristics than 1200 V IGBTs. Therefore, the combination of increased switching frequency and multi-level output voltage waveform allows to dramatically reduce size of the passive components (i.e., dominating the converter volume) and thus significantly improve power density at constant efficiency or vice-versa.

There are three main variants of the unidirectional three-level rectifier:

- ► VIENNA-type (cf. Fig. 2.1(b)); each bridge-leg employs one 600 V transistor, four 600 V line-frequency diodes (i.e., commutating with the grid frequency, featuring low cost and relatively low on-state voltage drop) and two 600 V fast-recovery diodes (i.e., commutating with the switching frequency, featuring relatively high cost and high on-state voltage drop). The transistor, together with the four line-frequency diodes connected around it, forms a bipolar bidirectional (i.e., four-quadrant, 4Q) switch. The main advantages of this topology are the reduced voltage rating (i.e., 600 V) of all semiconductor devices and the requirement of only three transistors (and gate drivers) for the whole converter. Conversely, the disadvantages are the high total part count (i.e., seven semiconductor devices per bridge-leg), the relatively large conduction losses (i.e., due to the presence of two diodes or two diodes and one transistor in the conduction path) and the unfavorable switching frequency commutation loop (i.e., which includes the parasitic inductance of three elements).

- ▶ NPC-type (cf. **Fig. 2.1(c)**); each bridge-leg consists of two 600 V transistors, two 600 V line-frequency diodes and two 600 V fast-recovery diodes. By modifying the structure of the 4Q switch with respect to the VIENNA-type implementation (i.e., adding one transistor and eliminating two line-frequency diodes), the neutral point clamped (NPC) rectifier achieves reduced conduction losses by having only one transistor and one diode in the conduction path when the AC node is connected to the DC-link mid-point. Furthermore, the NPC topology benefits from a low switching frequency commutation loop inductance (i.e., involving only two elements), thus allowing for enhanced switching performance and simple layout. Nonetheless, each NPC bridge-leg still features a high component count (i.e., six semiconductor devices and two gate drivers) and relatively large conduction losses.

- ► T-type (cf. Fig. 2.1(d)); each bridge-leg employs two 600 V transistors in anti-series connection (i.e., forming the 4Q switch) and two 1200 V fast-recovery diodes. The T-type bridge-leg structure allows to minimize conduction losses, as the conduction path is either through a single diode or two transistors. Therefore, despite adopting 1200 V diodes (i.e., featuring relatively high reverse-recovery charge) and having three

elements within a switching frequency commutation loop (i.e., leading to high parasitic inductance), the T-type rectifier provides considerable advantages with respect to the other three-level topologies, namely reduced component count (i.e., four semiconductor devices and only one gate driver per bridge-leg) and low conduction losses.

Overall, the three-phase three-level unidirectional T-type rectifier provides the most promising converter-level performance, combining the advantages of the two-level inverter (i.e., low semiconductor and gate driver count, low conduction loss) and the three-level VIENNA-type and NPC-type rectifiers (i.e., transistors with reduced voltage rating and high switching performance, three-level output voltage waveform). For these reasons, the T-type topology is considered for the AC/DC conversion stage of the 60 kW ultra-fast battery charging converter module.

#### 2.1.2 Key Challenges

Despite achieving an excellent compromise among cost, complexity and overall performance, three-level rectifiers feature unique challenges. For instance, one key issue of unidirectional rectifiers is the discontinuous conduction mode (DCM) operation around the current zero-crossings, which, if not correctly addressed, can lead to unacceptable phase current distortion in light load conditions [54]. Furthermore, besides having to ensure sinusoidal input current shaping, regulated output voltage, ohmic grid behavior and high efficiency/power density, three-level rectifiers must also control the DC-link mid-point voltage deviation (i.e., the voltage balancing between the two DC-link capacitors), as this increases the voltage stress on the semiconductor devices and negatively affects the AC-side current quality [55]. In particular, the voltage balancing feature must be ensured also when a split DC-link load unbalance occurs, which may be the case when separate DC/DC converters are connected to the split DC-link outputs (cf. Section 1.3).

Other desirable features (i.e., which are not strictly required) include the minimization of the DC-link mid-point low-frequency voltage oscillation [56, 57], which directly affects the size of the DC-link capacitors and may be hard to reject by the DC/DC conversion stage (cf. **Chapter 7**), and the operation under non-unity power factor, to support the reactive energy flows in distribution grids [13]. Both features are quite challenging to achieve, since the unidirectional nature of three-level rectifiers limits the maximum converter-side displacement power factor (DPF) and affects the DC-link mid-point generation process, limiting the converter ability to compensate the mid-point voltage oscillation.

Part of the content of this chapter has been published in [58] and [59].

# 2.2 Operating Principle and Limits

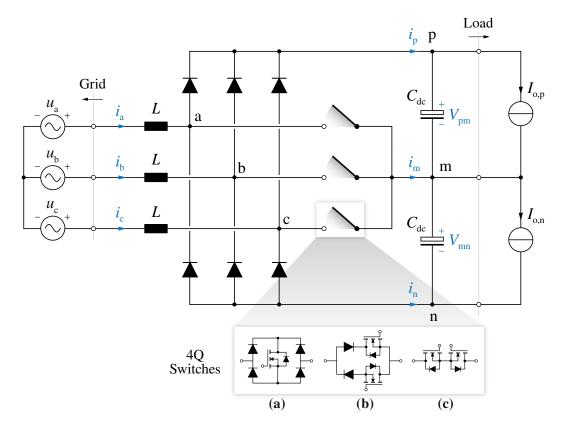

Even though the 60 kW rectifier is divided in two paralleled 30 kW converter units, these are assumed to be operated with synchronized and in-phase PWM carriers (cf. Section 3.1.1). Therefore, the considered six-leg T-type converter can be analyzed as a generic unidirectional three-phase three-level rectifier, shown in Fig. 2.2.

Each converter bridge-leg features two diodes that provide a passive connection between the AC input and the upper/lower DC-link rails (i.e., depending on the current direction), and a bipolar, bidirectional four-quadrant (4Q) switch, which actively connects the AC input to the DC-link mid-point. Notably, the 4Q switch types shown in **Fig. 2.2(a)** and **Fig. 2.2(b)** are typically integrated inside the input diode bridge (cf. **Fig. 2.1(b)**, (c)), allowing for the use of diodes with halved voltage rating. To simplify the following analysis and achieve compact analytical expressions (i.e., useful for the converter design and control), the DC-side loads connected to the upper and lower DC-link halves are assumed as ideal current-sources, whereas no inner grid impedance and no AC-side filter are considered.

**Fig. 2.2:** Equivalent circuit schematic of a generic grid-connected three-phase three-level unidirectional rectifier. The mid-point switches are bipolar and bidirectional, i.e., four-quadrant (4Q). A highlight of the possible 4Q switch topologies is provided, namely (**a**) the VIENNA-type, (**b**) the NPC-type, and (**c**) the T-type: switches (**a**) and (**b**) are typically integrated inside the input diode bridge (cf. **Fig. 2.1(b**), (**c**)), allowing for the use of diodes with halved voltage rating.

#### 2.2.1 Basics of Operation

The system state variables defining the converter operation are the AC-side inductor currents  $i_a$ ,  $i_b$ ,  $i_c$  and the DC-link capacitor voltages  $V_{pm}$ ,  $V_{mn}$  (cf. **Fig. 2.2**). Due to the three-phase three-wire nature of the system

$$i_{a} + i_{b} + i_{c} = 0,$$

(2.1)

therefore only two currents are independent and the total number of state variables is reduced to four. Moreover, the DC-link capacitor voltages  $V_{pm}$  and  $V_{mn}$  can be rearranged to define the DC-link voltage  $V_{dc}$  and the mid-point voltage deviation  $V_m$ , respectively

$$V_{\rm dc} = V_{\rm pm} + V_{\rm mn}, \qquad (2.2)$$

$$V_{\rm m} = V_{\rm pm} - V_{\rm mn}. \tag{2.3}$$

Notably, in normal operating conditions  $V_{\rm m} = 0$  assuming balanced split DC-link voltages  $V_{\rm pm} = V_{\rm mn} = V_{\rm dc}/2$ .

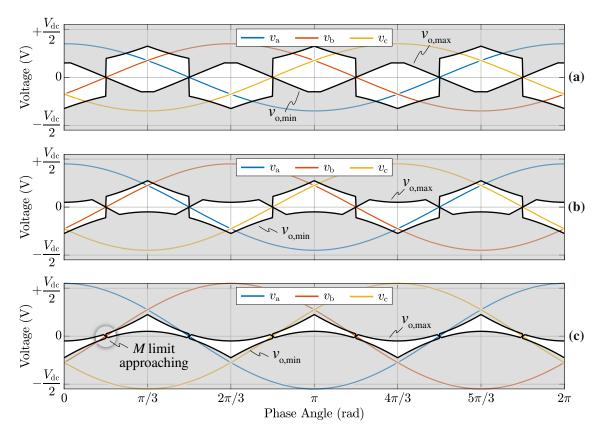

Disregarding the voltage drop at fundamental frequency across the AC-side inductance L (i.e., negligible for converters with high switching-to-fundamental frequency ratios [57]), the phase voltage local averages applied by the rectifier can be expressed as

$$\begin{cases} v_{a} = M \frac{V_{dc}}{2} \cos(\vartheta) \\ v_{b} = M \frac{V_{dc}}{2} \cos(\vartheta - \frac{2}{3}\pi) \\ v_{c} = M \frac{V_{dc}}{2} \cos(\vartheta - \frac{4}{3}\pi) \end{cases}$$

(2.4)

where  $\vartheta = \omega t = 2\pi f t$  is the phase angle, f is the grid frequency,  $M = 2V/V_{dc}$  is the modulation index of the rectifier and  $V \approx U$  is the phase voltage peak value. For the sake of completeness, the phase voltages  $v_a$ ,  $v_b$ ,  $v_c$  can be represented with a space vector approach as

$$\vec{V} = \frac{2}{3} \left( v_{\rm a} e^{j0} + v_{\rm b} e^{j2\pi/3} + v_{\rm c} e^{j4\pi/3} \right), \qquad (2.5)$$

where j is the imaginary operator.

Neglecting the switching ripple, the controlled phase currents are sinusoidal and are therefore expressed by

$$\begin{aligned}

i_{a} &= I \cos(\vartheta - \varphi) \\

i_{b} &= I \cos(\vartheta - \frac{2}{3}\pi - \varphi) \\

i_{c} &= I \cos(\vartheta - \frac{4}{3}\pi - \varphi)

\end{aligned}$$

(2.6)

where *I* is the phase current peak value and  $\varphi$  is the converter-side power factor angle (i.e.,  $\varphi = \angle v_x - \angle i_x$  with x = a, b, c). Similarly to the phase voltages,  $i_a, i_b, i_c$  can be expressed with an equivalent space vector representation as

$$\vec{I} = \frac{2}{3} \left( i_{\rm a} e^{j0} + i_{\rm b} e^{j2\pi/3} + i_{\rm c} e^{j4\pi/3} \right).$$

(2.7)

Due to the structure of a three-level unidirectional rectifier, the AC terminal of each bridge-leg may be actively connected to the DC-link mid-point (switch in the ON state) or, depending on the phase current direction, passively connected to either the positive or negative DC-link rails (switch in the OFF state). Consequently, the voltage applied by each bridge-leg with respect to the DC-link mid-point can assume three different values, namely  $0, +V_{dc}/2$  and  $-V_{dc}/2$ , which correspond to three separate switching states.

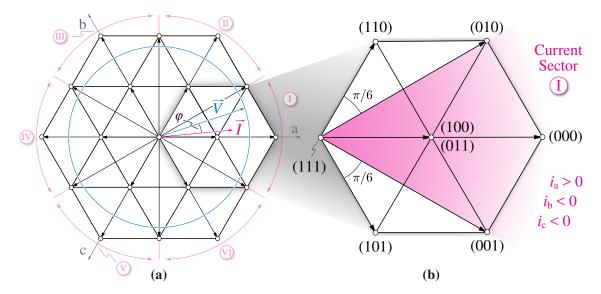

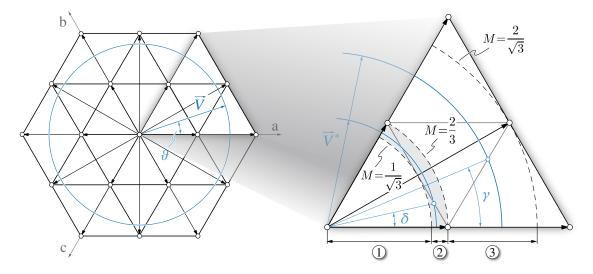

The total number of switching state combinations of a three-phase three-level rectifier is theoretically  $3^3 = 27$ ; however all three bridge-legs cannot be connected to the positive or negative DC-link rails at the same time due to the bridge diodes (i.e.,  $i_a + i_b + i_c = 0$ ), therefore the total number of states is reduced to 25. The overall number of space vectors can be derived by observing that six space vectors are redundant, leading to total space vector number of 25 - 6 = 19. An overview of the space vector diagram of a three-level rectifier is provided in **Fig. 2.3(a)**.

**Fig. 2.3:** Complete space vector diagram of a unidirectional three-phase three-level rectifier. An overview of the 19 available space vectors, the 6 separate current sectors, the phase voltage vector  $\vec{V}$ , the phase current vector  $\vec{I}$  and the converter-side power factor angle  $\varphi$  is shown in (**a**). A focus on the voltage space vector hexagon available when  $\vec{I}$  is transiting inside current sector ① is provided in (**b**): the switching states are defined by the combination of the 4Q switch signals  $s_x$ , i.e., 0 when the 4Q switch is OFF and 1 when the 4Q switch is ON.

Due to their unidirectional nature, three-level rectifiers cannot apply all 19 space vectors at any given time, as the feasible bridge-leg voltage values depend on the direction of the phase currents. The 6 different phase current direction combinations (i.e.,  $2^3 - 2$ , being  $i_a + i_b + i_c = 0$ ) define 6 separate regions in the space vector diagram, referred to as current sectors in the following. When the current vector  $\vec{I}$  transits through these regions, each bridge-leg can only apply two out of the three possible states, leading to a total of  $2^3 = 8$  switching combinations. Therefore, the total number of allowed space vectors becomes 7, being 1 switching combination redundant. The 7 available voltage space vectors when  $\vec{I}$  is located within current sector  $\mathbf{①}$  (i.e.,  $i_a > 0$ ,  $i_b < 0$ ,  $i_c < 0$ ) are illustrated in **Fig. 2.3(b)**. The highlighted hexagon indicates that whatever voltage space vector  $\vec{V}$  located inside the hexagon itself may be generated with a suitable combination of the 7 available space vectors.

### **AC-Side Voltage Generation**

The local average of the bridge-leg voltages applied by the rectifier  $(v_{xm})$  can be expressed as the sum of two contributions, namely the phase voltage component  $v_x$  and the zerosequence voltage component  $v_o$ , as

$$v_{\rm xm} = v_{\rm x} + v_{\rm o}$$

$x = a, b, c.$  (2.8)

The phase voltages  $v_a$ ,  $v_b$ ,  $v_c$  are controlled to regulate the converter input currents  $i_a$ ,  $i_b$ ,  $i_c$  according to their reference sinusoidal values, being

$$\frac{\mathrm{d}i_{\mathrm{x}}}{\mathrm{d}t} = \frac{u_{\mathrm{x}} - v_{\mathrm{x}}}{L} \quad \mathrm{x} = \mathrm{a}, \mathrm{b}, \mathrm{c}.$$

(2.9)

As previously explained, because of the relatively low value of *L* in systems with high switching-to-fundamental frequency ratios, the low-frequency voltage drop across the AC-side inductors can typically be neglected [57], such that  $v_x \approx u_x$ .

The zero-sequence component  $v_0$  is defined as the average of the three bridge-leg voltages, i.e.,

$$v_{\rm o} = \frac{v_{\rm am} + v_{\rm bm} + v_{\rm cm}}{3}.$$

(2.10)

Even though  $v_0$  has no effects on the phase current generation process in a three-phase three-wire system, it defines the modulation strategy of the rectifier (cf. Section 2.3), affecting the high-frequency stresses on the AC-side inductors and DC-link capacitors (cf. Section 2.4), and may be leveraged to regulate the DC-link mid-point current, as shown in the following.

### **DC-Side Current Generation**

The three DC-link rail currents  $i_p$ ,  $i_m$ ,  $i_n$  indicated in **Fig. 2.2** are bounded by the following relation:

$$i_{\rm p} + i_{\rm m} + i_{\rm n} = 0,$$

(2.11)

due to the three-wire DC-link structure.

In particular,  $i_p$  and  $i_n$  are linked to the total power transfer of the rectifier, being

$$P = v_{a}i_{a} + v_{b}i_{b} + v_{c}i_{c} = V_{pm}i_{p} - V_{mn}i_{n} \approx \frac{1}{2}V_{dc}(i_{p} - i_{n}), \qquad (2.12)$$

where balanced split DC-link voltages (i.e.,  $V_{pm} = V_{mn} = V_{dc}/2$ ) are assumed.

The generation process of the DC-link mid-point current  $i_m$  is slightly more complicated and has been investigated in several papers [55, 56, 60]. The main driver of  $i_m$  is the zerosequence voltage component  $v_0$  injected by the converter. Even though this component does not affect the phase currents, it modifies the duty cycles (i.e., relative ON-times)  $\tau_a$ ,  $\tau_b$ ,  $\tau_c$  of the mid-point 4Q switches, which in turn affect the mid-point current local average value, namely

$$i_{\rm m} = \tau_{\rm a} i_{\rm a} + \tau_{\rm b} i_{\rm b} + \tau_{\rm c} i_{\rm c}.$$

(2.13)

The values of  $\tau_a$ ,  $\tau_b$ ,  $\tau_c$  are determined by the ratio between their respective reference bridge-leg voltages  $v_{xm}$  and the DC-link voltage  $V_{dc}$  as

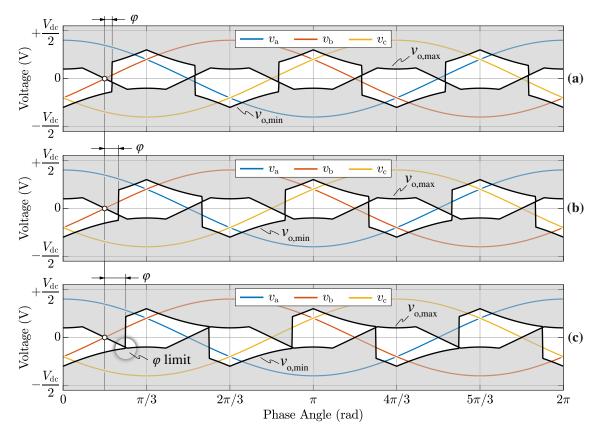

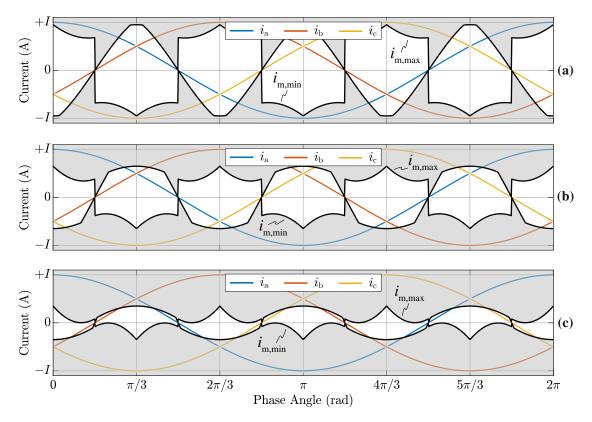

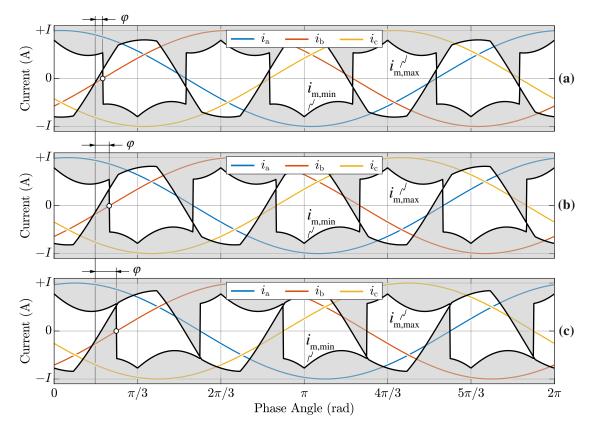

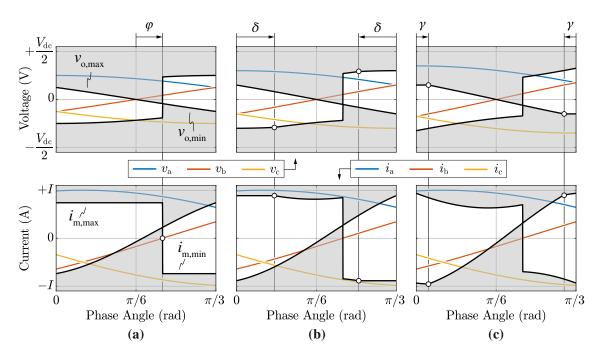

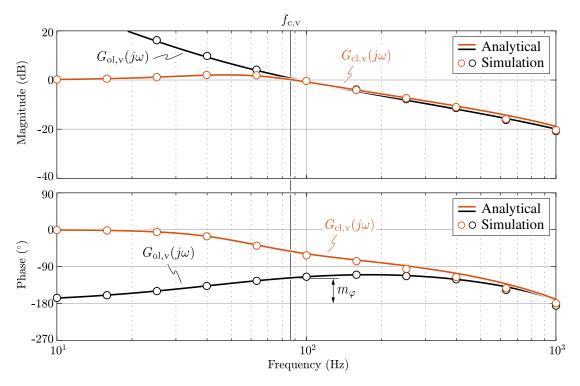

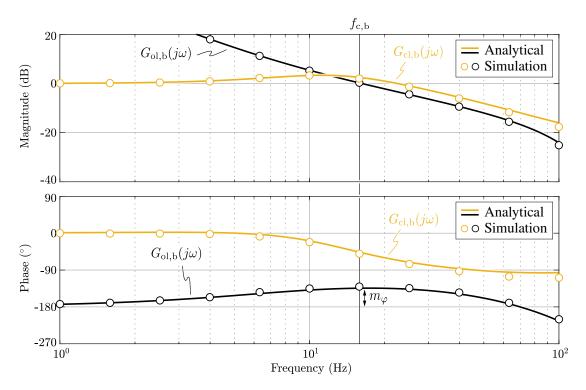

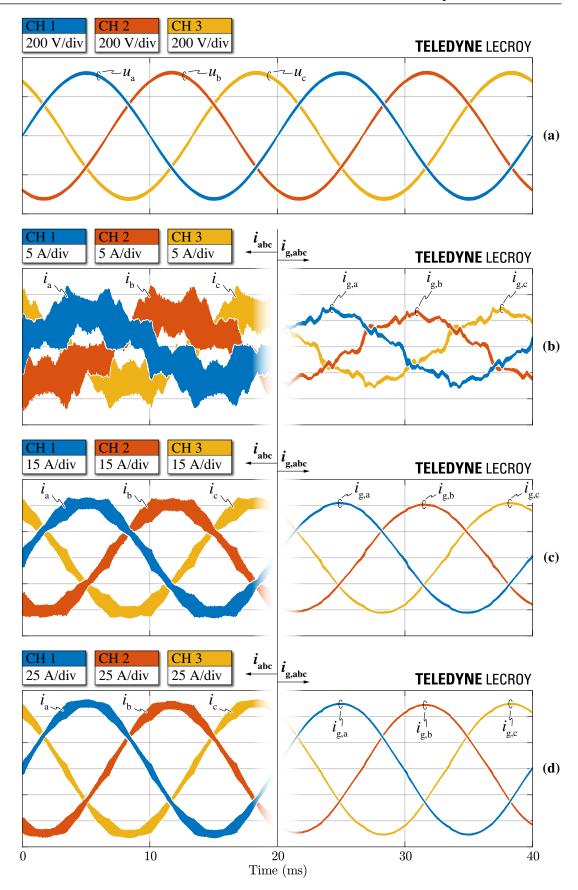

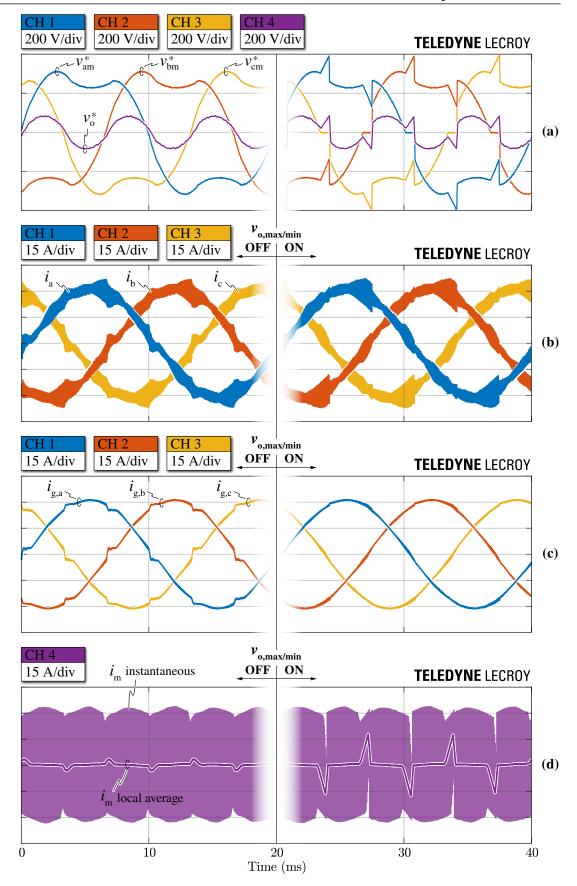

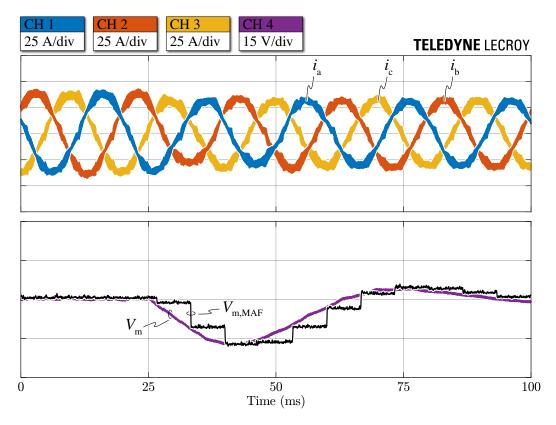

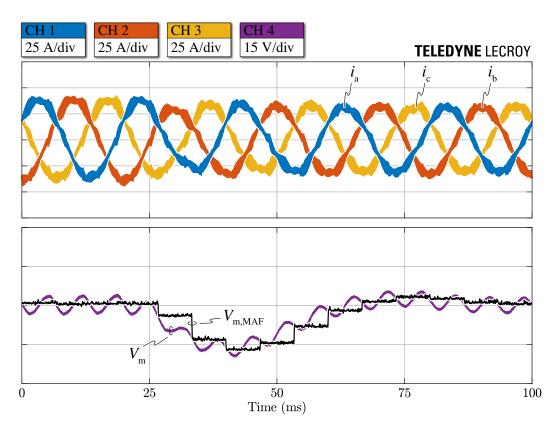

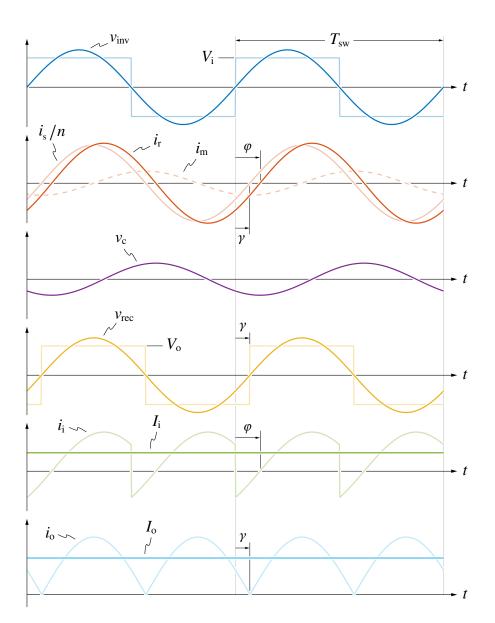

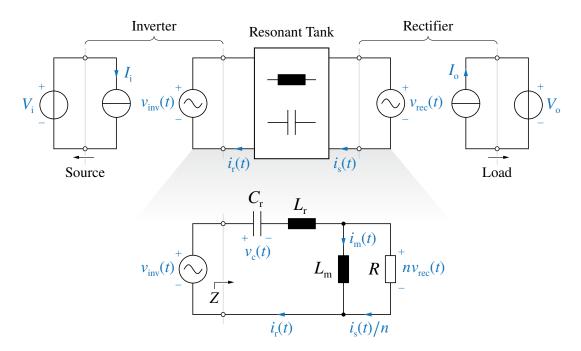

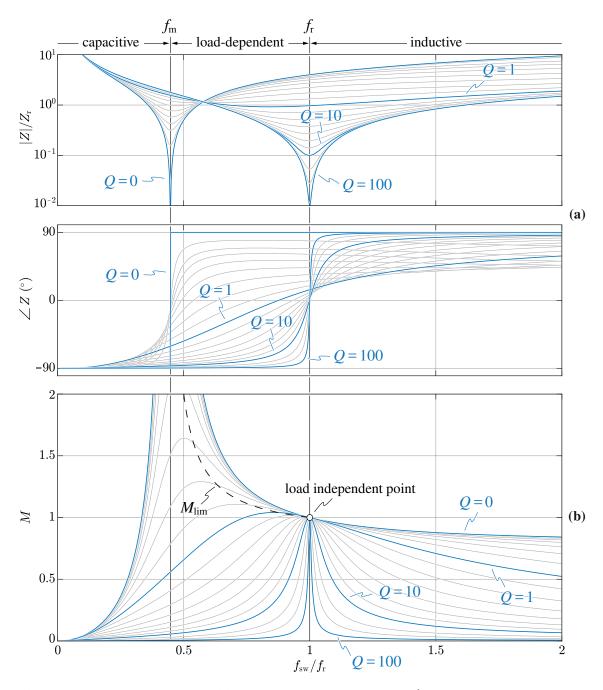

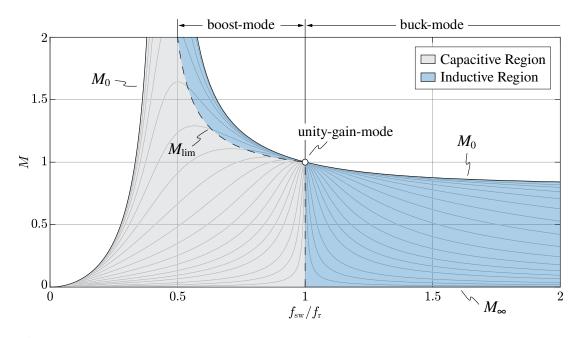

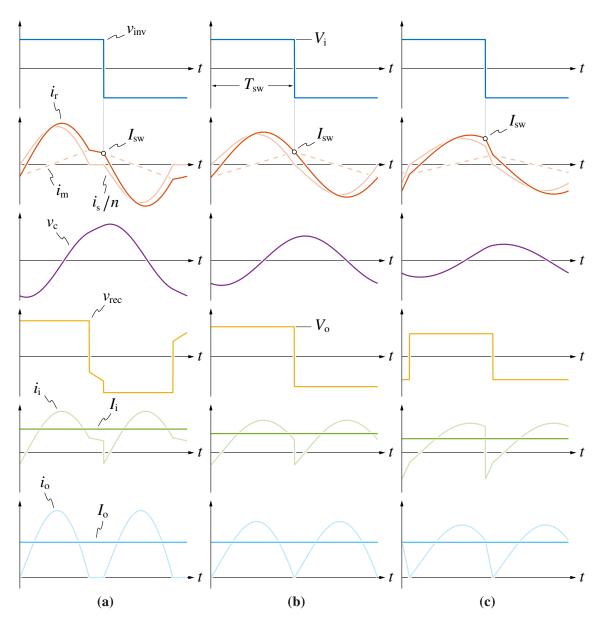

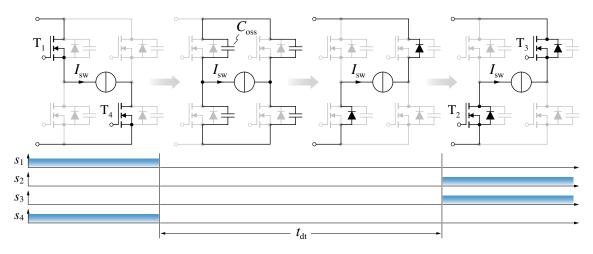

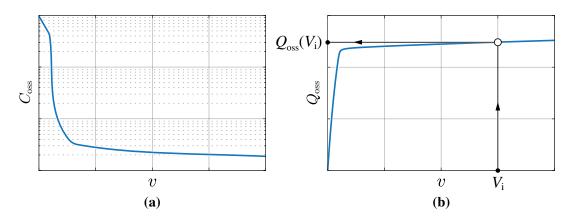

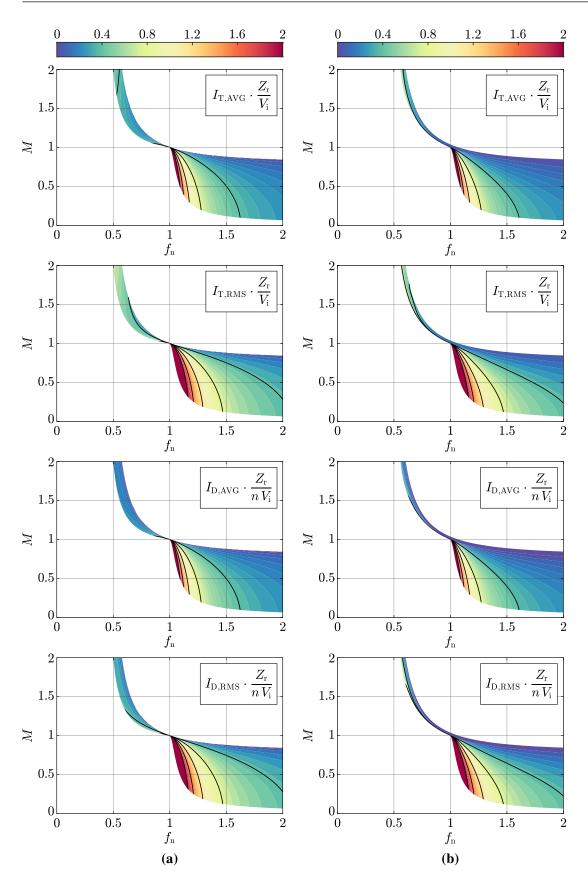

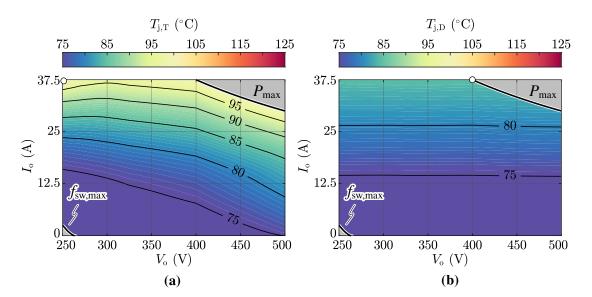

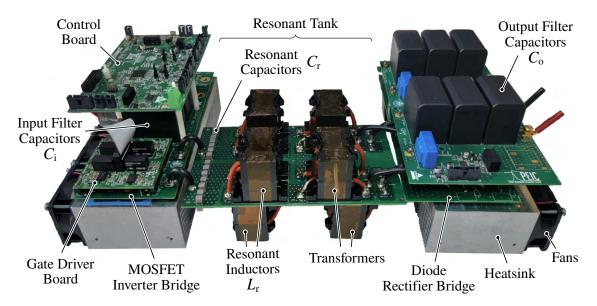

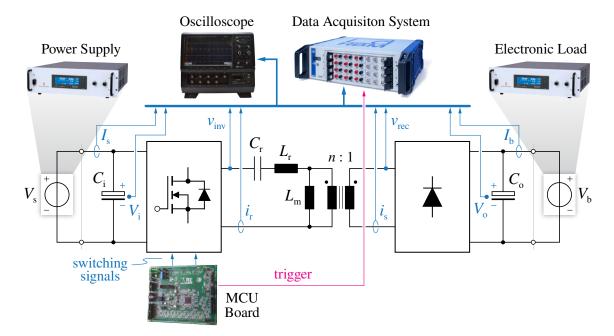

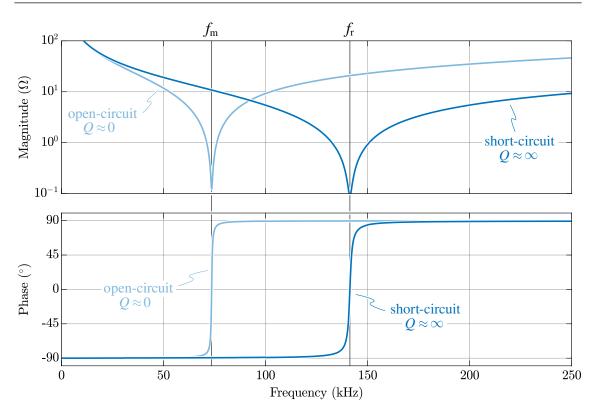

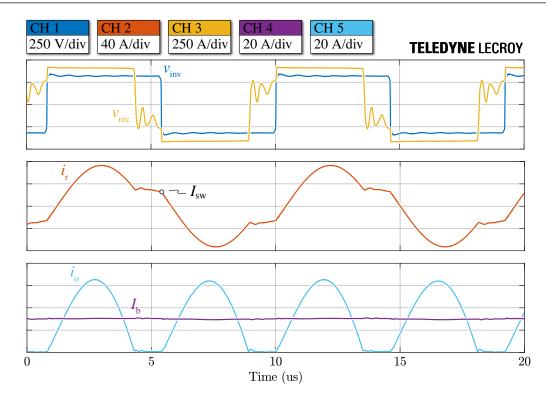

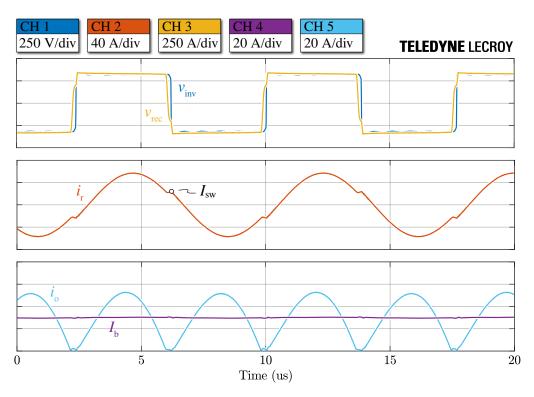

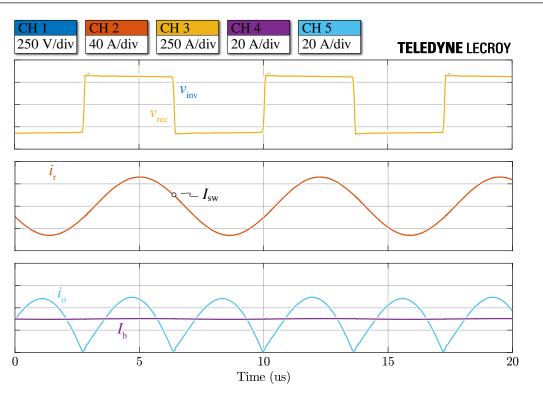

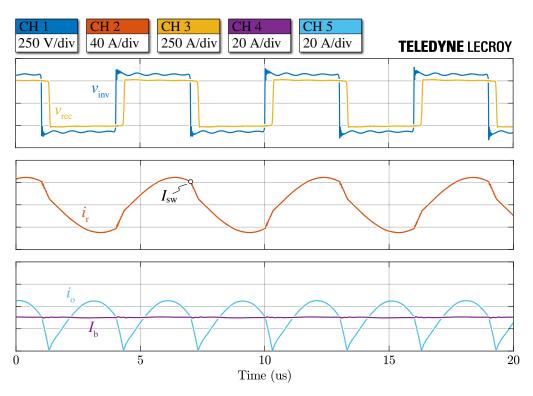

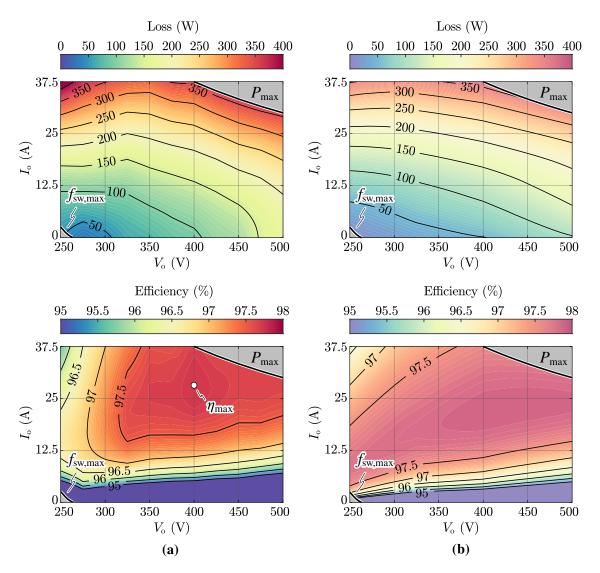

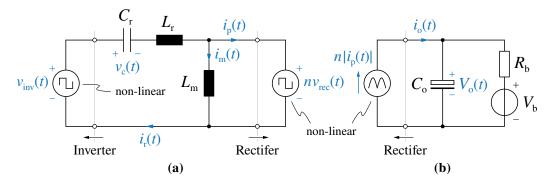

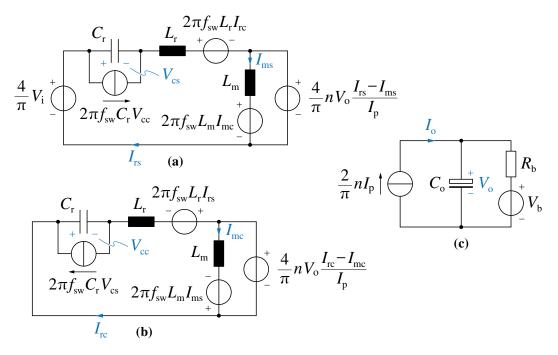

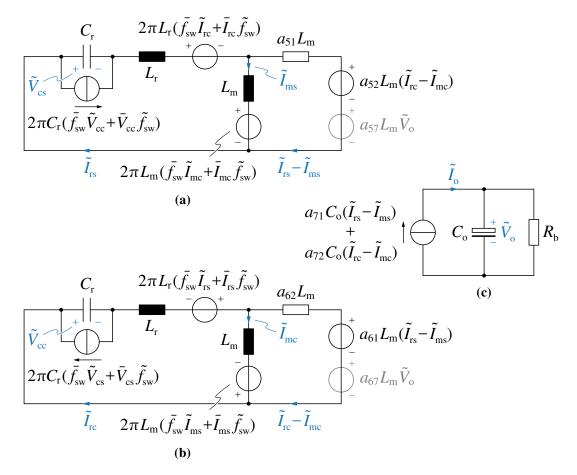

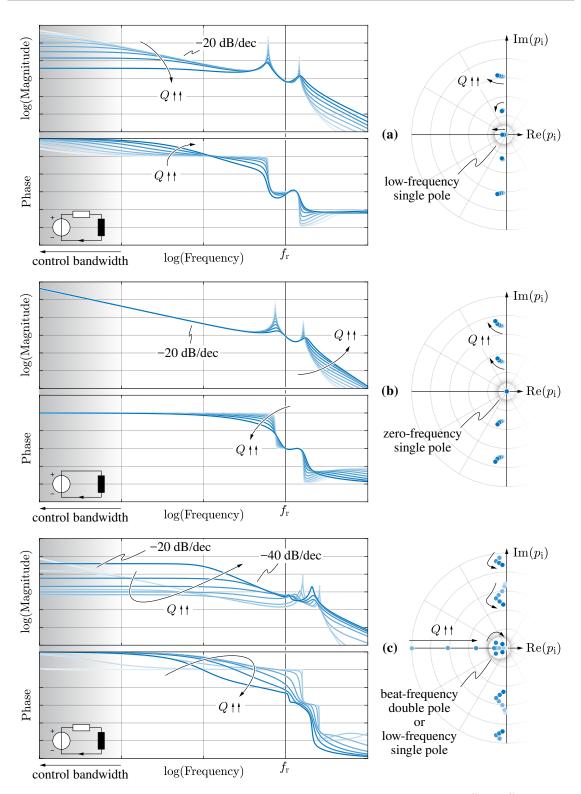

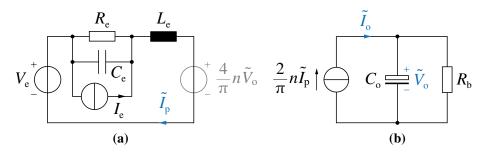

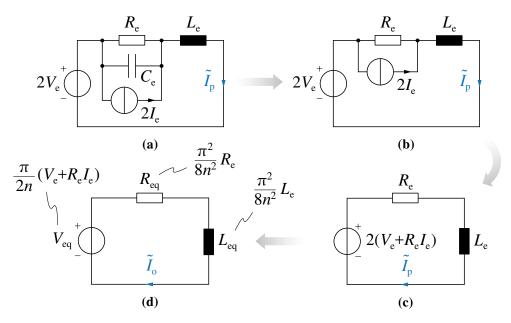

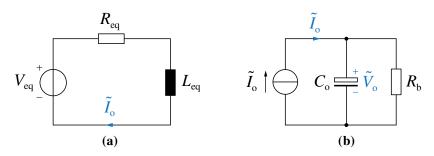

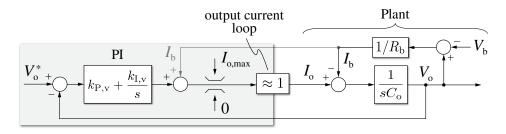

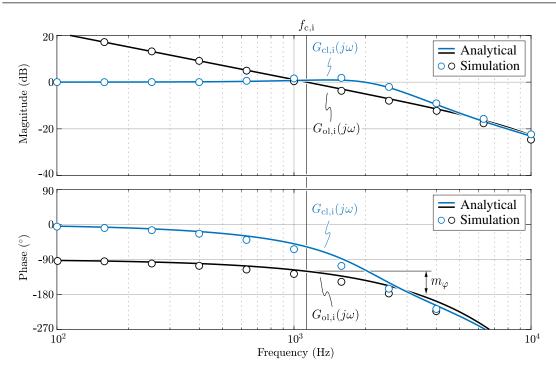

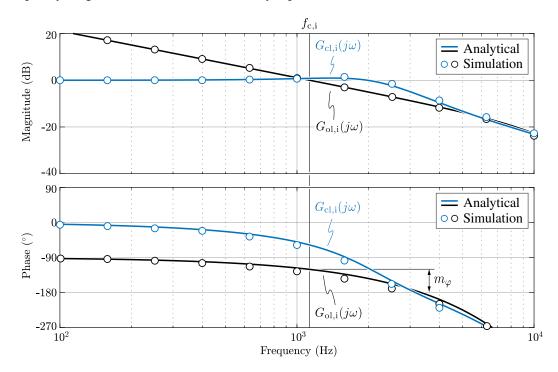

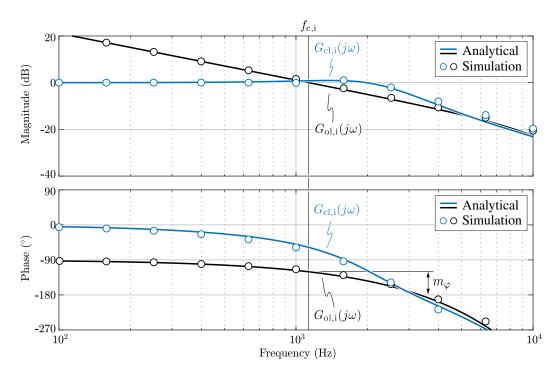

$$\tau_{\rm x} = 1 - \frac{2}{V_{\rm dc}} |v_{\rm xm}| = 1 - \frac{2}{V_{\rm dc}} |v_{\rm x} + v_{\rm o}| \qquad {\rm x} = {\rm a, \, b, \, c.} \tag{2.14}$$