# POLITECNICO DI TORINO Repository ISTITUZIONALE

A 0.01mm2, 0.4V-VDD, 4.5nW-Power DC-Coupled Digital Acquisition Front-End Based on Time-Multiplexed Digital Differential Amplification

Original

A 0.01mm2, 0.4V-VDD, 4.5nW-Power DC-Coupled Digital Acquisition Front-End Based on Time-Multiplexed Digital Differential Amplification / Crovetti, PAOLO STEFANO; Rubino, Roberto; Pedro, Toledo; Musolino, Francesco; Klimach, Hamilton; Chen, Yong; Richelli, Anna. - ELETTRONICO. - (2022). (Intervento presentato al convegno ESSCIRC 2022-IEEE 48th European Solid State Circuits Conference (ESSCIRC) tenutosi a Milan (Italy) nel 19-22 September 2022) [10.1109/ESSCIRC55480.2022.9911357].

Availability:

This version is available at: 11583/2972539 since: 2022-10-23T09:11:04Z

Publisher: IEEE

Published DOI:10.1109/ESSCIRC55480.2022.9911357

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# A $0.01 \text{mm}^2$ , $0.4 \text{V}\text{-}V_{\text{DD}}$ , 4.5 nW-Power DC-Coupled Digital Acquisition Front-End Based on Time-Multiplexed Digital Differential Amplification

Paolo Crovetti<sup>1</sup>, Roberto Rubino<sup>1</sup>, Pedro Toledo<sup>1</sup>, Francesco Musolino<sup>1</sup>, Hamilton Klimach<sup>2</sup>, Yong Chen<sup>3</sup>, Anna Richelli<sup>4</sup>

<sup>1</sup>Dept. of Electronics and Telecommunications (DET), Politecnico di Torino, Torino, Italy

<sup>2</sup>Electr. Eng. Dept., Graduate Program in Microelectronics, Fed. Univ. of Rio Grande do Sul, Porto Alegre, Brazil

<sup>3</sup>State-Key Laboratory of Analog and Mixed-Signal VLSI and IME/ECE-FST, University of Macau, Macao, China

<sup>4</sup>Department of Information Engineering, University of Brescia, Brescia, Italy

e-mail: paolo.crovetti@polito.it

Abstract—A reconfigurable, high-impedance, DC-coupled lowfrequency digital acquisition front-end (DAFE) suitable to operate under a power supply voltage ranging from 0.2 to 1V down to 600 pW power is presented in this paper. Matchingindifferent DC accuracy over a rail-to-rail input range is uniquely achieved by the new time-multiplexed digital differential amplification technique at ultra-low area and without chopping and auto-zeroing. A 180 nm testchip of the proposed DAFE occupies 0.00945 mm<sup>2</sup> and draws 4.5 nW at a 0.4 V supply, has a 120 Hz gain-bandwidth product, with an in-band input noise of 11.3  $\mu$ Vrms, a 137  $\mu$ V input offset voltage standard deviation, 65.7 dB CMRR, 63.8 dB PSRR, and provides a 46.5 dB-SFDR, 6.9 bit-ENOB digitized output at -12 dBFS.

*Index Terms*—DC-coupled digital acquisition front-end (DAFE), time-multiplexed digital differential amplification (TMD<sup>2</sup>A), CMOS, ECG, IoT.

### I. INTRODUCTION

Ultra-compact, energy-quality scalable sensor interfaces operating from a low, extremely variable supply under a < 10 nW power budget are required to enable next-generation sub-millimeter remotely-powered implantable biosensors [1] and energy-autonomous IoT nodes [2]. In this scenario, AC-coupled acquisition front-ends (AFEs) with < 10 nW power [3], [4], [5] and 0.01-mm<sup>2</sup>-scale area [6], [7] have been demonstrated for ECG, EEG and audio signal acquisition.

DC-coupled AFEs, needed e.g. in electrochemical and temperature sensors acquisition, pose further challenges, and DC accuracy (i.e. low DC offset/drifts, high DC CMRR and PSRR) is achieved by chopping [8], [6] and/or auto-zeroing [9], at the cost of much increased power, area and lower input impedance.

In this paper, a scalable, DC-coupled, biosignal digital AFE (DAFE) with inherent DC offset and drift suppression and direct digitization is demonstrated in 180nm CMOS aiming to simultaneously achieve order-of-nanowatt power, area-efficiency and decent DC accuracy over a wide supply range.

## II. TIME-MULTIPLEXED DIGITAL DIFFERENTIAL AMPLIFICATION (TMD<sup>2</sup>A)

The proposed DAFE entails inherently offset- and drift-free, differential-mode amplification without relying on matching,

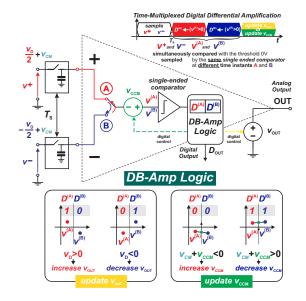

Fig. 1. Concept diagram of the Time-Multiplexed Digital Differential Amplification principle.

chopping or auto-zeroing, thanks to the new time-multiplexed digital differential amplification (TMD<sup>2</sup>A) approach illustrated in Fig.1. Here, the same single-ended comparator is multiplexed in time to compare the non-inverting  $(v^+)$  and the inverting  $(v^-)$  differential analog inputs against the same threshold (assumed to be 0 V in the following), and differential-mode signal amplification is achieved as in a Digital-Based Amplifier (DB-Amp) [10].

In details, after  $v^+$  and  $v^-$  are simultaneously sampled, the switch in Fig.1 is operated in A, so that  $v^+$  is in series to the common-mode (CM) compensating floating voltage source (CM-FVS)  $v_{\rm CCM}$ , and the input voltage

$$v^{(A)} = v^+ + v_{CCM} = \frac{v_D}{2} + v_{CM} + v_{CCM}$$

is applied to the comparator. The comparator digital output is 1 if  $v^{(A)} > 0$  and 0 otherwise, and is stored in  $D^{(A)}$ . Then,

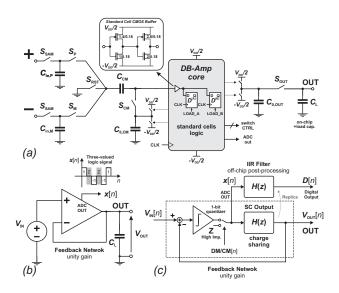

Fig. 2. Proposed SC TMD<sup>2</sup>A DAFE: (a) schematic, (b) unity-gain configuration considered for input signal digitization, (c) equivalent block diagram of the configuration in (b).

the switch is operated in B, the comparator input is

$$v^{(B)} = v^- + v_{CCM} = -\frac{v_D}{2} + v_{CM} + v_{CCM}$$

and the corresponding comparator output is stored in  $D^{(B)}$ .

Based on  $D^{(A)}$  and  $D^{(\bar{B})}$ , either  $v_{OUT}$  or  $v_{CCM}$  are updated as in a DB-Amp [10], i.e. if  $(D^{(A)}, D^{(B)}) = (1,0)$   $((D^{(A)}, D^{(B)}) = (0,1))$ , which implies that  $v_D > 0$  ( $v_D < 0$ ),  $v_{OUT}$  is increased (decreased) by a minimum step, and  $v_{CCM}$  is kept unchanged. On the contrary, if  $(D^{(A)}, D^{(B)}) = (1,1)$   $((D^{(A)}, D^{(B)}) = (0,0))$ ,  $v_{CCM}$  is decreased (increased) by a minimum step so that to track  $v_{CM}$ , aiming to enforce  $|v_{CM} + v_{CCM}| < |v_D/2|$ , as required to detect the sign of  $v_D$  in the next cycles, while  $v_{OUT}$  is hold.

### A. Transistor-Level Design

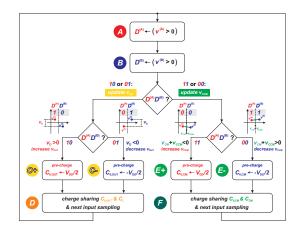

In the proposed DAFE, TMD<sup>2</sup>A is realized in 180nm CMOS by switched capacitor (SC) techniques [see schematic in Fig. 2(a)]. A small standard cell CMOS digital buffer [transistor level details in Fig. 2(a)] is used as a single-ended comparator, while the input sampling capacitors, the CM-FVS and the output voltage source are implemented by pF-range Metal-insulator-Metal (MiM) capacitors, and the floating switches are designed by CMOS pass gates operated at boot-strapped voltage. The DB-Amp core is a finite state machine (FSM) automatically synthesized in standard-cell logic, whose state transition graph is shown in Fig. 3.

### B. Circuit Operation

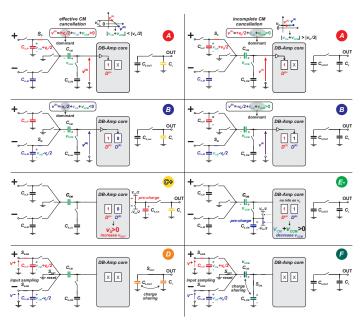

In state A (B), the input capacitor  $C_{\text{in},\text{P}}$  ( $C_{\text{in},\text{M}}$ ), charged at the non-inverting (inverting) input voltage  $v^+$  ( $v^-$ ) sampled at the previous cycle (see below), is connected in series to  $C_{\text{CM}}$  at the buffer input (Fig.4, states A-B in the left and right column) and its digital output is stored in the D-Flip Flop  $D^{(A)}$ ( $D^{(B)}$ ) at the next clock edge. Depending on ( $D^{(A)}, D^{(B)}$ ), the FSM evolves to states C+/C-, to update the output voltage (left

Fig. 3. State transition graph of the DB-Amp control unit.

Fig. 4. Sequence of switch configurations corresponding to the states in Fig.3: for  $|v_{\rm CM} + v_{\rm CCM}| < |v_{\rm D}/2|$ , i.e. dominant differential component (left) and for  $|v_{\rm CM} + v_{\rm CCM}| > |v_{\rm D}/2|$ , i.e. dominant CM component (right).

column in Fig.4), or to states E+/E-(right column in Fig.4), to update the voltage  $v_{\rm CCM}$  across  $C_{\rm CM}$ .

In order to increase (decrease) the output voltage, the fF-range capacitor  $C_{0,\text{OUT}}$  is first pre-charged to  $V_{\text{DD}}/2$  ( $-V_{\text{DD}}/2$ ) in state C+ (C-), and then connected in parallel to  $C_{\text{L}}$  in state D, so that  $v_{\text{OUT}}$  is increased (decreased) by:

$$\Delta v_{\rm OUT} = \frac{C_{0,\rm OUT}}{C_{\rm L} + C_{0,\rm OUT}} \left( {}^+_{(-)} \frac{V_{\rm DD}}{2} - v_{\rm OUT} \right).$$

In the same state D,  $v^+$  and  $v^-$  are simultaneously sampled on  $C_{\rm in,P}$  and  $C_{\rm in,M}$ . In a similar fashion, in E+ (E-), the fFrange capacitor  $C_{0,CM}$  is pre-charged to  $V_{\rm DD}/2$  ( $-V_{\rm DD}/2$ ) and then connected in parallel to  $C_{\rm CM}$  in the next state F, to update  $v_{\rm CCM}$  as demanded to compensate the CM input component, as well as drifts and process, voltage and temperature (PVT)related variations in the CMOS buffer logic threshold. In the

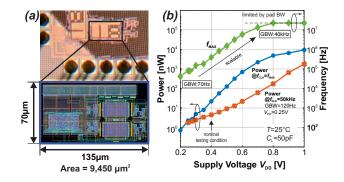

Fig. 5. Test chip micrograph (a) and (b) maximum clock frequency  $f_{\rm max}$  and power (@ $f_{\rm clk} = f_{\rm max}$  and @ $f_{\rm clk} = 50 \,\rm kHz$ ) versus supply voltage  $V_{\rm DD}$ .

TABLE I Measured DC Performance of Six Dice at  $25^{\circ}\,{\rm C},\,V_{\rm DD}=0.4\,{\rm V}$

|              | Unit    | #1   | #2   | #3   | #4   | #5   | #6   | $\mu$ | $\sigma$ |

|--------------|---------|------|------|------|------|------|------|-------|----------|

| Input Offset | $\mu V$ | +83  | +19  | +54  | +230 | -20  | -188 | +30   | 137      |

| DC Gain      | dB      | 40.8 | 39.9 | 39.6 | 38.0 | 42.7 | 36.3 | 39.6  | 2.2      |

| CMRR         | dB      | 68.0 | 74.0 | 68.5 | 60.4 | 60.0 | 63.4 | 65.7  | 5.4      |

| PSRR         | dB      | 83.9 | 55.3 | 54.0 | 60.6 | 69.0 | 60.1 | 63.8  | 11.1     |

same state F,  $v^+$  and  $v^-$  are also sampled, as in D. Either state D or state F conclude an operating cycle, and are followed by state A in the next cycle.

As in [10], [11], the circuit operates as an analog differential amplifier with a gain-bandwidth (GBW) product proportional to the clock frequency. When connected in negative feedback under fixed capacitive load [e.g. in the unity-gain configuration as in Fig. 2(b)], the circuit operates as a delta modulator [6], [7] [see Fig. 2(c)], and a digitized version of the output can be retrieved in post-processing from the sequence of the DB-Amp FSM states by infinite impulse response (IIR) digital filtering.

### **III. EXPERIMENTAL RESULTS**

A CMOS test-chip of the proposed DAFE has been fabricated in 180 nm and occupies merely 0.00945 mm<sup>2</sup> [micrograph in Fig. 5(a)]. When tested at 25°C in unity-gain feedback configuration [Fig. 2(b)] with  $C_{\rm L} = 50 {\rm pF}$ , the DAFE operates under a 0.2-1 V supply voltage range with a rail-to-rail input/output swing, at a maximum clock frequency  $f_{\rm max}$  ranging from 28 kHz to 15 MHz (upper-limited by the analog pads), corresponding to a scalable GBW from 70 Hz to 40 kHz. From Fig.5b, the power consumption varies from 600 pW at 0.2 V to 9.58  $\mu$ W at 1 V (from 2.0 nW at 0.25 V to 1.77  $\mu$ W at 1 V) under  $f_{\rm clk} = f_{\rm max}$  ( $f_{\rm clk} = 50$  kHz). At 0.4 V supply ( $V_{\rm DD}$ ) and  $f_{\rm clk} = 50$  kHz, considered hereafter in the DAFE characterization, the power is 4.5 nW.

Based on the DC characterization at 25°C, 0.4 V  $V_{\rm DD}$ ,  $C_{\rm L} = 50 {\rm pF}$  and  $f_{\rm CLK} = 50 {\rm \, kHz}$  (see Tab. I), the input offset voltage of six dice ranges from -188 to  $+230 \, \mu {\rm V}$ , the open-loop DC gain from 36.3 to 42.7 dB, the CMRR from 60.0 to 74.0 dB and the PSRR from 54.0 to 83.9 dB. These results prove the reasonable DC accuracy of the proposed DAFE. Moreover, the DC input resistance of all dice is above  $1G\Omega$ .

The time-domain analog output of sample #2 in unitygain feedback [ $v_{OUT}$  in Fig. 2(b)] under 0.1 Hz, 360 mV<sub>pk-pk</sub>

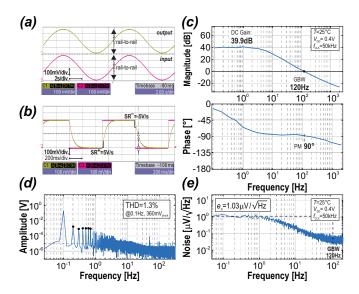

Fig. 6. Analog output testing: time-domain response in unity-gain closed-loop configuration for rail-to-rail sine (a) and square wave (b) input; (c) open-loop differential gain frequency response (magnitude and phase); (d) output voltage spectrum (test conditions as in (a)), (e) input noise spectrum (from output noise spectrum measured with  $v^+ = v^- = 0$ , considering 39.9 dB DC gain).

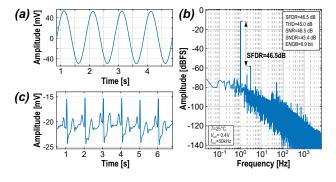

Fig. 7. ADC output testing: time-domain waveform reconstructed from the ADC output stream [Figs. 2(b)-(c)] under 1 Hz,  $50 \text{ mV}_{pk}$  (-12 dBFS) sine input (b) spectrum of the reconstructed output in (a) and ADC dynamic performance; (c) reconstructed ECG waveform (ECG-20 mV electrode offset).

sine-wave input, and under a rail-to-rail square-wave input are shown in Figs. 6(a)-(b). The spectrum of the signal in Fig. 6(a) is shown in Fig. 6(c) and reveals a THD of 1.3%. Based on the open-loop frequency response reported in Fig. 6(c), the DC gain is 39.9 dB and the GBW is 120 Hz. The openloop input-referred noise spectrum in Fig. 6(e) reveals an in-band noise power spectral density of  $1.03 \,\mu V / \sqrt{Hz}$  and an effective suppression of 1/f noise. The integrated input noise in the 0.05-1 Hz (0.05-120 Hz) bandwidth is  $1.03 \,\mu V_{\rm rms}$ (11.3  $\mu V_{\rm rms}$ ).

In Figs. 7(a)-(b), the time-domain waveform and the spectrum of a 50 mV<sub>pk</sub> (i.e. -12 dBFS), 1 Hz sine-wave reconstructed from the digital output stream of the DAFE postprocessed off-chip by an IIR filter as in [6] is shown. The results reveal 46.5 dB SFDR, 45.0 dB THD and 43.4 dB SNDR, corresponding to 6.9 ENOB, and demonstrate the operation of the DAFE as an ADC. An ECG signal reconstructed from the digital output is shown in Fig. 7(c) and confirms the suitability of the DAFE to biosignal acquisition.

| -                |                     |                |               | 20MI AKI30I |             | -           |           |              |               |                |

|------------------|---------------------|----------------|---------------|-------------|-------------|-------------|-----------|--------------|---------------|----------------|

| Reference        | Unit                | [6]            | [12]          | [3]         | [5]         | [8]         | [9]       | [13]         | [7]           | This Work      |

| Architecture     |                     | AFE            | ATC           | AFE         | AFE         | CCIA        | Buffer    | LNA          | $\Delta$ -ADC | DAFE           |

| Coupled          |                     | DC             | DC            | AC          | AC          | DC          | DC        | DC           | DC            | DC             |

| Technology       | nm                  | 40             | 65            | 65          | 180         | 65          | 180       | 180          | 180           | 180            |

| Area             | $\mathrm{mm}^2$     | 0.015          | 0.006         | 0.200       | 0.75        | 0.100       | 1.4       | 1            | 0.011         | 0.00945        |

| Normalized Area  | $10^6 \cdot F^2$    | 9.37           | 1.42          | 47.3        | 23.1        | 23.7        | 43.2      | 30.9         | 0.65          | 0.291          |

| Supply Voltage   | V                   | 0.6            | 0.5           | 0.6         | 1.2/0.6     | 1           | 1.8       | 0.2/0.8      | 0.6/1.2/3.3   | 0.4            |

| Supply Range     | V                   | N/A            | N/A           | 0.5-0.7     | N/A         | N/A         | N/A       | N/A          | N/A           | 0.2-1          |

| Input Range      | $\% V_{\rm DD}$     | 50             | 0.8           | N/A         | N/A         | N/A         | N/A       | N/A          | 91            | 90             |

| Power            | nW                  | 3,300          | 1,275         | 3           | $8.3^{(e)}$ | 1,800       | 378,000   | 790          | 990           | 4.5            |

| Bandwidth        | Hz                  | 150            | 11,000        | 1.5-370     | 470         | 0.5-100     | 1,450,000 | 670          | 500           | $120^{(i)}$    |

| Input Resistance | $G\Omega$           | 0.05           | $0.031^{(f)}$ | N/A         | N/A         | $0.8^{(f)}$ | (g)       | $0.01^{(f)}$ | 2.96          | > 1            |

| DC Gain          | dB                  | N/A            | N/A           | 32          | 31-59       | 40          | 0         | 57.8         | N/A           | $39.6^{(i,k)}$ |

| Input Offset     | $\mu V$             | N/A            | N/A           | N/A         | N/A         | 1           | 0.4       | N/A          | N/A           | $137^{(j)}$    |

| In-band Noise    | $\mu V_{rms}$       | $20^{(c)}$     | 3.8           | 26          | 17          | $6.7^{(d)}$ | N/A       | 0.94         | $2.6^{(c)}$   | $11.3^{(c,h)}$ |

| (noise BW)       | (Hz)                | (1-150)        |               | (1.5-370)   |             | (0.5-100)   |           | 1-500        |               | (0.05-120)     |

| Noise PSD        | $\mu V / \sqrt{Hz}$ | N/A            | 0.036         | N/A         | N/A         | 0.021       | 0.02      | 0.036        | N/A           | 1.03           |

| $NEF^{(a)}$      |                     | $147^{(c)}$    | 2.2           | 2.1         | 2           | 3.3         | 7.3       | 1.6          | $3.5^{(c)}$   | $4.1^{(c)}$    |

| $PEF^{(b)}$      |                     | $13,012^{(c)}$ | 2.4           | 2.6         | 4.8         | 10.9        | 96        | 2.1          | $15.2^{(c)}$  | $6.7^{(c)}$    |

| THD              | %                   | 1              | 0.2           | N/A         | N/A         | 1.5         | N/A       | N/A          | N/A           | $1.3^{(l)}$    |

| CMRR             | dB                  | 60             | 60            | 60          | N/A         | 134         | N/A       | 85           | > 78          | $65.7^{(i)}$   |

| PSRR             | dB                  | N/A            | N/A           | 63          | N/A         | 120         | 125       | 80/75        | N/A           | $63.8^{(i)}$   |

| SFDR             | dB                  | 56             | 60            | N/A         | N/A         | N/A         | N/A       | N/A          | N/A           | 46.5           |

| ENOB             | bit                 | N/A            | N/A           | 9.2         | 7.7         | N/A         | N/A       | N/A          | 9.7           | 6.9            |

TABLE II

Perfomance Summary and Comparison with Low Frequency Sensor Interfaces

<sup>(a)</sup>  $NEF = V_{n,rms} \sqrt{\frac{2I_B}{4\pi kT V_T BW}}$ , where  $V_{n,rms}$  is the rms input noise,  $I_B$  is the supply current and BW is the bandwidth; <sup>(b)</sup>  $PEF = V_{DD} \cdot NEF^2$ ; <sup>(c)</sup> includes ADC quantization noise (and ADC current for NEF/PEF), <sup>(d)</sup> with DC servo loop, <sup>(e)</sup> LNA+ADC power considered, <sup>(f)</sup> estimated. <sup>(g)</sup> <1pA total input current; <sup>(h)</sup> Input rms noise in the 0.05-120 Hz BW estimated from the measured open-loop input-referred noise spectral density  $e_n$  in Fig.6(e) as  $e_n \cdot \sqrt{BW}$ ; <sup>(i)</sup> Average of 6 samples; <sup>(j)</sup>Std. Dev. of 6 samples; <sup>(k)</sup> Open-loop gain; <sup>(l)</sup> Under 0.1 Hz, 90% rail-to-rail input; Best in **bold**.

### IV. COMPARISON AND CONCLUSIONS

Compared with the state of the art of low-frequency AFEs in Table II, the proposed DAFE occupies the lowest normalized area (2.2X less than [7]) and works at the minimum voltage and over the widest supply range (4X wider than [3]) with rail-to-rail input/output swing, uniquely offering power-quality scalability. At 0.4 V, the power is comparable with AC-coupled AFEs [3], [5] (1.5X more than [3], in 65 nm, and 1.8X less than [5], also in 180nm), which have 3.1X-3.9X larger bandwidth and 2.3X-1.5X more in-band rms noise.

Compared to DC-coupled AFEs with similar bandwidth [6]– [8], [13], the DAFE has an inherently high input resistance (> 1 G $\Omega$ ), consumes 1.2X-106X less area and 175X-733X less power, while providing a digitized output as [6], [7]. The offset, although 137X-342X larger than [8], [9], is the only reported in sub- $\mu$ W AFEs. The in-band rms noise is 1.8X less than [6] and 4X more than [7], which inherently include quantization noise as the DAFE, while it is 12X more than the best [13]. The noise efficiency factor (NEF)/power efficiency factor (PEF) metrics, defined in Table II, are 1.2X worse/2.3X better than [7] and 36X/1,942X better than [6], while they are 2.6X/3.2X worse than [13], the best in Table II. The digitized output of the DAFE is slightly worse in terms of effective resolution (-0.8/-2.8 bit ENOB) compared to [3], [5], [7].

The measured results confirm that the performance of the DAFE are suitable to DC-coupled sensor interfaces for nextgeneration microscale biosensing and energy-autonomous IoT nodes.

### REFERENCES

- S. Carrara, "Body Dust: Well beyond wearable and implantable sensors," *IEEE Sensors Journal*, pp. 1–1, 2020.

- [2] M. Alioto, "From less batteries to battery-less alert systems with wide power adaptation down to nWs" *IEEE Design Test*, vol. 38, no. 5, pp. 90–133, 2021.

- [3] P. Harpe et al., "A 0.20 mm<sup>2</sup>, 3 nW signal acquisition IC for miniature sensor nodes in 65 nm CMOS," *IEEE Journ. of Solid-State Circ.*, vol. 51, no. 1, pp. 240–248, 2016.

- [4] H. Wang et al., "A 5.5 nW battery-powered wireless ion sensing system," in ESSCIRC 2017, 2017, pp. 364–367.

- [5] S. Jeong, et al., "Always-on 12-nW acoustic sensing and object recognition microsystem for unattended ground sensor nodes," *IEEE Journ.* of Solid-State Circ., vol. 53, no. 1, pp. 261–274, 2018.

- [6] R. Mohan, et al., "A 0.6-V, 0.015-mm<sup>2</sup>, time-based ECG readout for ambulatory applications in 40-nm CMOS," *IEEE Journ. of Solid-State Circ.*, vol. 52, no. 1, pp. 298–308, 2017.

- [7] M. R. Pazhouhandeh et al. "Opamp-less sub-µW/channel Δ-modulated neural-ADC with super-GΩ input impedance," *IEEE Journ. of Solid-State Circ.*, vol. 56, no. 5, pp. 1565–1575, 2021.

- [8] Q. Fan et al., "A 1.8 μW 60 nV/√Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE Journ. of Solid-State Circ.*, vol. 46, no. 7, pp. 1534–1543, 2011.

- [9] T. Rooijers, J. H. Huijsing, and K. A. A. Makinwa, "An auto-zerostabilized voltage buffer with a quiet chopping scheme and constant sub-pA input current," *IEEE Journ. of Solid-State Circ.*, pp. 1–1, 2021.

- [10] P. S. Crovetti, "A digital-based analog differential circuit," *IEEE Trans.* on Circ. and Syst. I: Reg. Papers, vol. 60, no. 12, pp. 3107–3116, 2013.

- [11] P. Toledo, et al. "Fully digital rail-to-rail OTA with sub-1000-µm<sup>2</sup> area, 250-mV minimum supply, and nW power at 150-pF load in 180 nm," *IEEE Solid-State Circ. Lett.*, vol. 3, pp. 474–477, 2020.

- [12] L. B. Leene and T. G. Constandinou, "A 0.006 mm<sup>2</sup> 1.2 μW analog-totime converter for asynchronous bio-sensors," *IEEE Journ. of Solid-State Circ.*, vol. 53, no. 9, pp. 2604–2613, 2018.

- [13] F. M. Yaul and A. P. Chandrakasan, "A sub-μW 36nV/√Hz chopper amplifier for sensors using a noise-efficient inverter-based 0.2V-supply input stage," in *ISSCC 2016*, 2016, pp. 94–95.