## POLITECNICO DI TORINO Repository ISTITUZIONALE

### Direct Digital Sensing Potentiostat targeting Body-Dust

Original

Direct Digital Sensing Potentiostat targeting Body-Dust / Rubino, Roberto; Carrara, Sandro; Crovetti, Paolo. -ELETTRONICO. - (2022). (Intervento presentato al convegno 2022 IEEE Biomedical Circuits and Systems Conference (BioCAS2022) tenutosi a Taipei (Taiwan) nel 13-15 October 2022) [10.1109/BioCAS54905.2022.9948649].

Availability: This version is available at: 11583/2972538 since: 2022-10-23T09:00:17Z

Publisher: IEEE

Published DOI:10.1109/BioCAS54905.2022.9948649

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# Direct Digital Sensing Potentiostat targeting Body-Dust

Roberto Rubino DET Politecnico di Torino Torino, Italy roberto\_rubino@polito.it Sandro Carrara Integrated Circuits Laboratory École Polytechnique Fédérale de Lausanne Lausanne, Switzerland sandro.carrara@epfl.ch Paolo Crovetti DET Politecnico di Torino Torino, Italy paolo.crovetti@polito.it

Abstract—In this paper, an innovative Direct Digital Sensing Potentiostat integrated circuit for enzymeless blood glucose sensing and direct digitization is proposed to address the requirements of Body Dust. The circuit occupies a silicon area of 460  $\mu m^2$  in 180nm CMOS and operates down to 0.4 V power supply voltage with 4.7 nW power consumption. The functionality of the proposed circuit and its performance under typical conditions and under process and temperature variations is tested by post-layout simulations.

Index Terms—Body Dust, potentiostat, glucose sensing, Digital-Based Amplifier (DB-Amp)

#### I. INTRODUCTION

The concept of Body Dust (BD) [1] envisions the integration of micrometer-scale sensors embedded in bio-compatible, wirelessly powered CMOS integrated circuits (ICs), with a size comparable to human blood cells (  $< 100\mu$ m diameter), small enough to ubiquitously circulate in tissues and blood as swarms of particles and able to exchange data from within the human body to the outside world for diagnosis and healthmonitoring purposes.

Turning BD into reality demands analog CMOS ICs with micrometer-scale dimensions and nanowatt power [1], which are hard to be designed by traditional techniques. In this context, digital-based analog design, which has recently been proposed to address the requirements of Internet of Things (IoT) applications [3], [4], is more and more emerging as a viable option to meet the area and power requirements of BD applications. Even though quasi-digital potentiostats have been proposed in [2], fully digital potentiostats have never been presented so far. In this paper, a Direct Digital Sensing Potentiostat (DDSP) for the enzymeless detection of species in a physiological solution is presented, aiming to glucose detection within the framework of the Body Dust research.

The paper is structured as follows: in Section II, a model of the micrometer-scale electrode interface for the enzymeless glucose detection is devised, extrapolating electrode parameters from literature-derived measured characterizations. In Section III, the DDSP electronic architecture is presented, and its working principle is explained, focusing on its direct digital acquisition capability. Section IV follows, in which the performance of the DDSP is tested by post-layout simulations, both under nominal conditions and in the presence of process

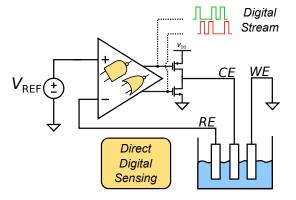

Fig. 1. Direct Digital sensing Potentiostat.

and temperature variations, and compared with the state-ofthe-art. Some conclusions are finally drawn in Section V.

#### II. ELECTROCHEMICAL SENSOR

The Direct Digital Sensing Potentiostat (DDSP) performs non-enzymatic glucose detection employing a potentiostatbased current sensing topology, as in Fig.1, fixing the potential of the solution at the reference (RE) electrode while measuring the reduction or oxidation current flowing between the counter (CE) and working (WE) electrodes. The chronoamperometric (CA) method is considered from now on.

#### A. Sensor design and modeling

To electrically simulate the sensing architecture, a model of the electrochemical interface is developed. A square WE with platinum-nanospheres nanostructures as in [5] is considered, having a sensitivity

$$S_0 = 4\mu A / (mM \cdot cm^2) \tag{1}$$

in enzymeless detection of glucose [6].

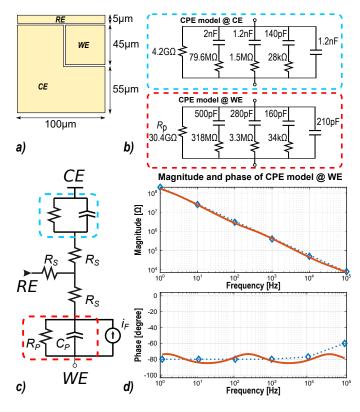

The WE geometry is chosen to be  $45\mu$ m-side platinum square as in Fig.2a, suitable to BD particles in the order of  $100\mu$ m lateral size. The sensitivity of the WE faradaic current with respect to glucose concentration, denormalised with respect to the electrode area is, from (1)

$$S = \frac{4\mu A}{cm^2 \cdot mM} \cdot (0.0045 cm)^2 = 0.081 \frac{nA}{mM}.$$

(2)

Fig. 2. Considered electrodes geometry (a), WE and CE electrical CPE model (b), high-level electrical model of the sensor (c), magnitude and phase of the CPE impedance at the WE (d).

Taking into account the usual glucose physiological range being in between 3mM and 8mM, a full-range current of 0.8nA (up to 10mM) is expected.

Along with the faradaic current, which is conveniently modelled by a concentration-driven current generator ( $i_{\rm F}$  at the WE) the Randles circuit model of each electrode is extracted as in Fig.2c, including the solution resistance  $R_{\rm S}$ , a constant phase element (CPE) and the charge transfer resistance  $R_{\rm P}$ . Focusing of preliminary *in vitro* testing, the value of  $R_{\rm S}$  is set considering the conductivity of a commercially available 0.01 M phosphate buffer saline (PBS) solution, being  $\sigma_{\rm PBS} =$  $12 \,{\rm mS}/{\rm cm}$ .

A cubic volume of solution of  $45\mu$ m side has been considered to estimate the solution resistance. The value of  $R_{\rm S}$  is thus derived:

$$R_{\rm S} = \left(\sigma_{\rm PBS} \cdot \frac{A}{d}\right)^{-1} \simeq 18.5 \,\mathrm{k\Omega} \tag{3}$$

where  $A = (45 \,\mu\text{m})^2$  and  $d = 45 \,\mu\text{m}$ . The charge transfer resistance  $R_{\rm P}$  and the CPE  $C_{\rm P}$  electrical models (highlighted in dashed boxes in Fig.2c) for the WE and CE are extrapolated from the magnitude and phase impedance characterization of platinum electrodes reported in [7].

The reference magnitude and phase curves chosen to model the WE (blue diamonds curve in Fig.2d) are fit with the parallel RC model in Fig.2d, according to the algorithm

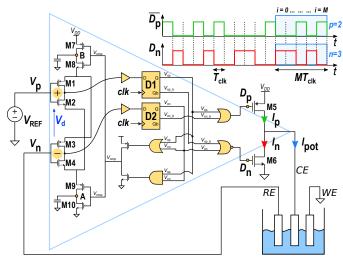

Fig. 3. Proposed digital-based potentiostat schematic and digital acquisition pulses.

presented in [8], resulting in the WE model in Fig.2b (dashed red box).

An analogous procedure is employed to model the CE, resulting in the RC model in Fig.2b (dashed blue box) while just the solution resistance is considered for the RE, being its current negligible thanks to the potentiostat high input impedance.

#### **III. DIRECT DIGITAL SENSING POTENTIOSTAT**

The proposed DDSP takes advantage of the digital-based amplifier (DB-Amp) principe [3], [9], [10] for potentiostat readout, as schematically depicted in Fig.1. The schematic of the DB-Amp adopted in this work is reported in Fig.3. Compared to [10] and [3], [9], where a resistive summing network, and a Muller C element are used for the input common-mode (CM) compensation, floating inverters [11] are employed in the input stage of the DB-Amp proposed in this work to further enhance energy efficiency.

The non-inverting  $(v_p)$  and inverting  $(v_n)$  analog input signals of the DB-Amp in the DDSP, to be connected to  $V_{REF}$ and to the RE, respectively, are applied to the inputs of the CMOS floating inverters M1-M2 and M3-M4, which do not draw any DC current. The digital outputs of such inverters are sampled by the D Flip-Flops D1 and D2, respectively, on the active clock edge.

As in [10], when D1=0 and D2=1 (D1=1 and D2=0), which implies that  $v_{\rm d} = v_{\rm p} - v_{\rm n} > 0$  ( $v_{\rm d} \le 0$ ), the output stage M5-M6 is operated to increase (decrease) the output voltage, i.e. the pMOS device M5 (the nMOS device M6) is turned on for one clock cycle  $T_{\rm clk}$ , thus sourcing (sinking) a nearly constant current  $I_{\rm P}$  ( $I_{\rm N}$ ) in the CE capacitance, corresponding to a positive (negative) charge packet  $I_{\rm P}T_{\rm clk}$  ( $I_{\rm N}T_{\rm clk}$ ).

When D1 and D2 have the same logical value, the sign of  $v_d$  cannot be detected and the output stage M5-M6 is kept in high impedance. Moreover, when D1=0 and D2=0 (D1=1 and D2=1) the negative (positive) supply of the input inverters is

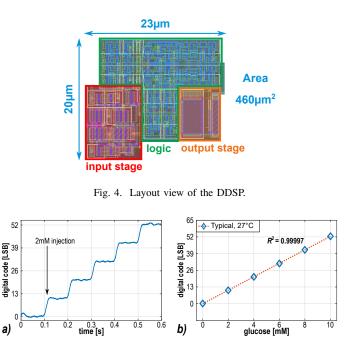

Fig. 5. Digital acquisition under staircase concentration increase of 2mM (a) and the corresponding calibration curve (b).

a)

tied by M9 to node A (by M8 to node B), which was predischarged to 0 V via M10 (pre-charged to  $V_{\rm DD}$  via M7) in the previous cycle. Such reconfiguration provides the input inverters with a dynamic bias, as required to asymmetrically discharge (charge) their output and to detect the sign of  $v_{\rm d}$ , resulting in D1=0 and D2=1 or D1=0 and D2=1 in the next cycle(s).

Thanks to negative feedback and to the filtering effect of the CE capacitance, the RE potential is forced by the DB-Amp to the non-inverting input voltage  $V_{\text{REF}}$  (ripple below 2.3mV rms) by injecting discrete charge packets in the CE. Since the charge in each packet is nearly constant, the time average of the CE current  $I_{pot}$ , which turns out to be equal to the faradaic current  $I_{\rm F}$ , is directly estimated counting the number of the positive (negative) digital pulses p(n) over the last M clock cycles as follows:

$$I_{\rm F} = \frac{pI_{\rm P} - nI_{\rm N}}{M} \tag{4}$$

Based on (4), a digitized version of  $I_{\rm F}$  is directly obtained post-processing the digital streams  $D_{\rm p}$  and  $D_{\rm n}$  driving the gates of M5 and M6 in Fig.3, thus suppressing the analog to digital converter (ADC) which is needed in conventional implementations.

#### IV. POST-LAYOUT SIMULATIONS AND COMPARISON

The proposed DDSP has been designed in 180nm CMOS and tested by post-layout simulations, performed connecting the DDSP to the electrochemical cell equivalent circuit described in Sec.II, fixing the WE potential at  $-V_{\text{REF}} = -0.2 \text{ V}$ , which corresponds to the first oxidation peak of the glucose in [5].

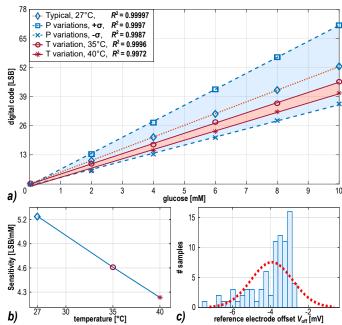

Fig. 6. Calibration curve spread against process  $(\pm \sigma)$  and temperature  $(35^{\circ}C)$ to 40°C) variations(a), sensitivity variation with temperature (b) and reference electrode offset variation with mismatch (c).

The layout of the DDSP cell, reported in Fig.4, occupies merely  $460 \,\mu \text{m}^2$ . Based on post-layout simulations at  $27^{\circ}\text{C}$ under 0.4 V supply, 50 kHz clock, and typical process conditions, the power consumption of the DDSP is 4.7 nW, the input current ranges from -22 nA to +33 nA, and the total input-referred noise, averaging DDSP binary streams over M=3,600 clock cycles, is  $65\,\mathrm{pA}_\mathrm{rms}$  including quantization noise, resulting in a 58 dB dynamic range.

The simulated chronoamperogram and digital code/concentration curve under а staircase glucose concentration increase of 2 mM steps are reported in Fig.5a and Fig.5b respectively, and reveal a sensitivity of 5.2 LSB/mM and a high linearity  $R^2 = 0.99997$ .

Based on Monte Carlo simulations under process variations, the standard deviation of the DDSP sensitivity is  $\sigma = 1.8 \, \mathrm{LSB/mM}$ , as shown in Fig.6a. The digital code/concentration curves of simulated samples at  $\pm \sigma$  sensitivity reported in Fig.6a reveal a linearity degradation from  $R^2 = 0.99997$  to  $R^2 = 0.9987$ . The simulated sensitivity versus temperature is reported in Fig.6b in the range 27°C-40°C and the simulated calibration curves at the extreme temperatures are shown in Fig.6a. A worst-case linearity degradation from  $R^2 = 0.99997$  to  $R^2 = 0.9972$  is observed at 40°C with respect to 27°C. These results reveal how process and temperature variations can be effectively compensated by linear calibration.

The distribution of the RE potential offset due to device mismatch has been obtained by Monte Carlo simulations and is reported in Fig.6c. The offset mean value and standard deviations are  $V_{\text{off}} = 3.9 \,\text{mV}$  and  $\sigma_{V_{\text{off}}} = 1.1 \,\text{mV}$ , respectively.

Compared to potentiostat front-ends proposed over the last

|               | Units      | [12]                   | [13]    | [14]     | [15]          | [16]      | This Work            |

|---------------|------------|------------------------|---------|----------|---------------|-----------|----------------------|

| Method        | -          | CV,CA,EIS <sup>†</sup> | CA,CV   | CA,CV    | CA,CV         | CA,CV     | СА                   |

| Measured      | -          | yes                    | yes     | yes      | yes           | yes       | no                   |

| Current Range | μA         | $\pm 0.2$              | $\pm 5$ | $\pm 15$ | $\{-7, +10\}$ | $\pm 1.5$ | $\{-0.022, +0.033\}$ |

| Dyn. Range    | dB         | 104                    | 108     | 73       | 58            | 105       | 58                   |

| Linearity     | $R^2$      | -                      | 0.998   | -        | 0.999         | 0.9990    | 0.99997              |

| Current Noise | pA (rms)   | 7.76                   | 41      | -        | 25000         | -         | 65                   |

| Bandwidth     | Hz         | 10,000                 | -       | 200      | 50,000        | 1         | 7*                   |

| Technology    | nm         | 180                    | 180     | 180      | 180           | 65        | 180                  |

| Area          | $\rm mm^2$ | 0.208                  | 0.78    | 2.25     | 3.17          | 0.07      | 0.00046              |

| Supply        | V          | 1.8                    | > 1.1   | 1.8      | 1.2           | 1.2       | 0.4                  |

| Power         | $\mu W$    | 311.4                  | 16      | 73.9     | 19            | 25        | 0.0047               |

| Digital out   | -          | no                     | yes     | yes      | yes           | yes       | yes                  |

TABLE I POTENTIOSTAT PERFORMANCE COMPARISON

<sup>†</sup>EIS: electrochemical impedance spectroscopy.

$\star$  Limited by M, traded with noise.

years for chronoamperometry and cyclic voltammetry, whose performance is summed up in Tab.I, the proposed DDSP operates at the lowest supply voltage ( $3 \times$  less than [15] and [16]) while dissipating the smallest power ( $3,400 \times$  less than [13]) at the smallest area ( $150 \times$  less than [16], which is though fabricated in a more scaled technology).

The DDSP reports the best linearity  $R^2 = 0.99997$ , with an rms current noise of  $65 \,\mathrm{pA_{rms}}$  (more than the  $41 \,\mathrm{pA_{rms}}$ of [13]) while showing a smaller dynamic range of  $58 \,\mathrm{dB}$ (comparable to [15]).

These results are establishing the DDSP as a promising solution for Body Dust applications, thanks to its ultra low power and area, low supply voltage and robustness against process, temperature and mismatch variations.

#### V. CONCLUSION

In this paper, an original fully digital potentiostat designed in 180nm CMOS technology has been presented as an acquisition front-end for chronoamperometric electrochemical detection of glucose.

Based on post-layout simulations, the digital potentiostat operates down to 0.4 V power supply voltage (3× less than [15] and [16]) having 58 dB dynamic range, with a significant advantage in terms of power (4.7 nW,  $3,400 \times$  less than [13]) and area ( $460 \,\mu\text{m}^2$ ,  $150 \times$  less than [16]) compared to recent alternatives, thus meeting the requirements of Body Dust applications.

#### REFERENCES

- S. Carrara, "Body Dust: Well Beyond Wearable and Implantable Sensors," in *IEEE Sensors Journal*, vol. 21, no. 11, pp. 12398-12406, Jun. 2021

- [2] S. Aiassa, F. Stradolini, A. Tuoheti, S. Carrara and D. Demarchi, "Quasi-Digital Biosensor-Interface for a Portable Pen to Monitor Anaesthetics Delivery," 2019 15th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), 2019, pp. 265-268

- [3] Toledo, P., Rubino, R., Musolino, F., and Crovetti, P., "Re-thinking analog integrated circuits in digital terms: A new design concept for the IoT era," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 68, no. 3, pp. 816-822, Mar. 2021

- [4] P. Toledo, P. S. Crovetti, H. D. Klimach, F. Musolino and S. Bampi, "Low-Voltage, Low-Area, nW-Power CMOS Digital-Based Biosignal Amplifier," in IEEE Access, vol. 10, pp. 44106-44115, 2022.

- [5] Taurino, I., Sanzó, G., Mazzei, F. et al. "Fast synthesis of platinum nanopetals and nanospheres for highly-sensitive non-enzymatic detection of glucose and selective sensing of ions," *Sci. Rep.* vol.5, no.15277, 2015

- [6] Dhara, K., Mahapatra, D.R. "Electrochemical nonenzymatic sensing of glucose using advanced nanomaterials," *Microchim. Acta* vol.185, no.49, 2018

- [7] Adam Wang, Doohwan Jung, Dongwon Lee, and Hua Wang "Impedance Characterization and Modeling of Subcellular to Micro-sized Electrodes with Varying Materials and PEDOT:PSS Coating for Bioelectrical Interfaces," ACS Applied Electronic Materials vol. 3 n. 12, p.5226-5239, 2021

- [8] Valsa, J.; Vlach, J. "RC models of a constant phase element," Int. J. Circuit Theory Appl, vol. 41, pp. 59–67, 2013.

- [9] Toledo, P., Crovetti, P., Aiello, O., and Alioto, M., "Fully digital rail-torail OTA with sub-1000-μm<sup>2</sup> area, 250-mV minimum supply, and nW power at 150-pF load in 180 nm," *IEEE Solid-State Circuits Letters*, vol. 3, pp. 474–477, 2020.

- [10] Crovetti, P. S., "A digital-based analog differential circuit," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 12, pp. 3107–3116, 2013.

- [11] X. Tang, B. Kasap, L. Shen, X. Yang, W. Shi and N. Sun, "An Energy-Efficient Comparator with Dynamic Floating Inverter Pre-Amplifier," 2019 Symposium on VLSI Circuits, (2019) pp. C140-C141.

- [12] B. Shen and M. L. Johnston, "DC-100 kHz Tunable Readout IC for Impedance Spectroscopy and Amperometric Measurement of Electrochemical Sensors," 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), 2020, pp. 651-654

- [13] Y. -C. Chen, S. -Y. Lu and Y. -T. Liao, "A Microwatt Dual-Mode Electrochemical Sensing Current Readout With Current-Reducer Ramp Waveform Generation," in *IEEE Transactions on Biomedical Circuits* and Systems, vol. 13, no. 6, pp. 1163-1174, Dec. 2019

- [14] H. -Y. Lee, P. -W. Huang, D. -S. Ciou, Z. -X. Liao and S. -Y. Lee, "A Power-Efficient Current Readout Circuit with VCO-Based 2nd-Order CT  $\Delta\Sigma$  ADC for Electrochemistry Acquisition," 2020 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2020, pp. 1-2.

- [15] Lu SY, Liao YT. "A 19 uW, 50 kS/s, 0.008-400 V/s Cyclic Voltammetry Readout Interface With a Current Feedback Loop and On-Chip Pattern Generation." *IEEE Trans. Biomed. Circ. Syst.*, vol.12, no.2, pp. 190–198, 2021

- [16] J. Aymerich et al., "A 15-uW 105-dB 1.8-Vpp Potentiostatic Delta-Sigma Modulator for Wearable Electrochemical Transducers in 65-nm CMOS Technology," in IEEE Access, vol. 8, pp. 62127-62136, 2020.