## POLITECNICO DI TORINO Repository ISTITUZIONALE

Foundry-Enabled Scalable All-to-All Optical Interconnects Using Silicon Nitride Arrayed Waveguide Router Interposers and Silicon Photonic Transceivers

Original

Foundry-Enabled Scalable All-to-All Optical Interconnects Using Silicon Nitride Arrayed Waveguide Router Interposers and Silicon Photonic Transceivers / Zhang, Y; Xiao, X; Zhang, K; Li, S; Samanta, A; Zhang, Y; Shang, K; Proietti, R; Okamoto, K; Yoo, S. J. B.. - In: IEEE JOURNAL OF SELECTED TOPICS IN QUANTUM ELECTRONICS. - ISSN 1077-260X. - STAMPA. - 25:5(2019), pp. 1-9. [10.1109/JSTQE.2019.2910415]

Availability: This version is available at: 11583/2972259 since: 2022-10-12T13:22:44Z

*Publisher:* IEEE / Institute of Electrical and Electronics Engineers

Published DOI:10.1109/JSTQE.2019.2910415

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <</p>

# Foundry-Enabled Scalable All-to-All Optical Interconnects using Silicon Nitride Arrayed Waveguide Router Interposers and Silicon Photonic Transceivers

Yu Zhang, Xian Xiao, Kaiqi Zhang, Siwei Li, Anirban Samanta, Yichi Zhang, Kuanping Shang, Roberto Proietti, Katsunari Okamoto, *Fellow, IEEE* and S. J. Ben Yoo, *Fellow, IEEE*

Abstract-This paper summarizes our latest results of integrated all-to-all optical interconnect systems using compact, low-loss silicon nitride (SiN) arrayed waveguide grating router (AWGR) through AIM photonics' multiple-project-wafer (MPW) services. In particular, we have designed, taped out and initially characterized a chip-scale silicon photonic low-latency interconnect optical network switch (Si-LIONS) system with an 8×8 200GHz spacing cyclic SiN AWGR, 64 microdisk modulators and 64 on-chip germanium photodector (PD). The 8×8 SiN AWGR in design has a measured insertion loss of 1.8 dB and a crosstalk of -13 dB, with a footprint of 1.3 mm  $\times$  0.9 mm. We measured an error-free performance of the microdisk modulator at 10 Gb/s upon 1Vpp voltage swing. We demonstrated wavelength routing with error-free data transmission using the on-chip modulator, SiN AWGR and an external PD. We have designed and taped out the optical interposer version of the all-to-all system using SiN waveguides and low-loss chip-to-interposer couplers. Lastly, we illustrate our preliminary designs and results of 16×16 and 32×32 SiN AWGRs, and discuss the possibility of scaling beyond 1024×1024 all-to-all interconnections with reduced number of wavelengths (e.g. 64) using the Thin-CLOS architecture.

*Index Terms*—Photonic integrated circuits, silicon photonics, arrayed waveguide grating router, optical interposer, electronic-photonic integration.

#### I. INTRODUCTION

As high-performance computing (HPC) platforms with multi-core processors are being deployed to sustain the ever-growing data demands, optical interconnects are attracting applications in networks on chips (NoC) systems owing to their superior performance in terms of low latency, high throughput, and high energy efficiency [1-3]. Arrayed waveguide grating router (AWGR)-based all-to-all optical interconnects [4, 5] are particularly attractive among many existing optical switching and routing solutions [6, 7] as they enable contentionless nonblocking interconnects with a simple interconnection topology [8].

1

Integrated photonics, particularly silicon photonics [9-15], offers an attractive platform for such AWGR-based all-to-all interconnect systems with advantages of: (1) significant reductions in size, weight, and power (SWaP) compared to the standalone devices with fiber connections [16]; (2) and facilitating high-radix all-to-all interconnections. Recent demonstrations showed silicon photonic AWGRs with up to 512×512 [17] and a 8×8 Silicon Photonic Low-Latency Interconnect Optical Network Switch (Si-LIONS) with an integrated silicon photonic AWGR and silicon photonic (SiPh) transceivers [18]. Si-LIONS will also allow close integration with silicon photonic (SiPh) transceivers [18], Complementary-Metal-Oxide-Semiconductor (CMOS) ICs and [19], nanoelectronics [20].

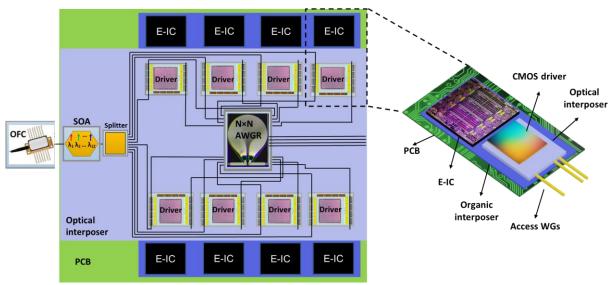

Silicon nitride (SiN)/SiO2 waveguides, compared to silicon/SiO<sub>2</sub> waveguides, offer lower index contrast and lower thermo-optical coefficient [21]. Therefore, they are less sensitive to fabrication imperfections and environmental temperature variations, thus they are more desirable for lowloss [22, 23] and high port count AWGRs. Fig. 1 schematically illustrates [8] an all-to-all optically interconnected network involving multi-socket compute nodes where the compute nodes including the electronic IC cores integrated with silicon photonic transceivers and an optical interposer including a SiN AWGR. An optical frequency comb (OFC) laser will feed in N number of wavelengths from the edge of the optical interposer. Laser inputs will then be amplified by a semiconductor optical amplifier (SOA) and equally split into SiPh transmitters on Ncomputing nodes. Modulated signals then are transmitted to the desired node through the wavelength routing by SiN AWGR and detected by the wavelength selective filter and on-chip PDs. The expanded view of Fig. 1 illustrates an integration scheme

dyuzhang@ucdavis.edu,

xxian@ucdavis.edu,

zkq@ucdavis.edu,

swli@ucdavis.edu,

asamanta@ucdavis.edu,

nszhang@ucdavis.edu,

kshang@ucdavis.edu,

rproietti@ucdavis.edu,

sbyoo@ucdavis.edu).

K. Okamoto is with the Aidi Corporation, 305-0032 Ibaraki, Japan (e-mail: katsu@okamoto-lab.com).

This paragraph of the first footnote will contain the date on which you submitted your paper for review This work was supported with funding from the American Institute of Manufacturing Photonics under contract numbers 201503002, 201704070 and 201700658.

Y. Zhang, X. Xian, K. Zhang, S. Li, A. Samanta, Y. Zhang, K. Shang, R. Proietti and S. J. B. Yoo are with the Electronic and Computer Engineering Department, University of California, Davis, CA 95616 USA (e-mail:

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Fig. 1 Schematic of an all-to-all optical interconnected electronic ICs using SiN AWGR

of the electronic ICs and silicon photonics, and Sec. III B will discuss details of this later.

In this paper, we design and tape-out a Si-LIONS chip which monolithically integrates a low-crosstalk  $8 \times 8$  200-GHz cyclic silicon nitride (SiN) AWGR, SiPh transmitters, and receivers. We further experimentally demonstrate 10 Gb/s OOK transmission between different input and output ports of the Si-LIONS chip. The remainder of the paper is organized as follows. Section II details the design and characterization of our chipscale Si-LIONS system using an  $8 \times 8$  200 GHz spacing cyclic SiN AWGR and on-chip modulators and PDs. Section III shows our design and integration plan of the SiN AWGR, SiPh transceiver modules, and electronic driver ICs on an optical interposer. Sect IV presents our initial designs and results on  $16 \times 16$  and  $32 \times 32$  SiN AWGRs and discuss the scalability

### towards large port count. Section V concludes the paper.

#### II. CHIP-SCALE INTEGRATED SI-LIONS SYSTEM USING 8×8 SIN AWGR

2

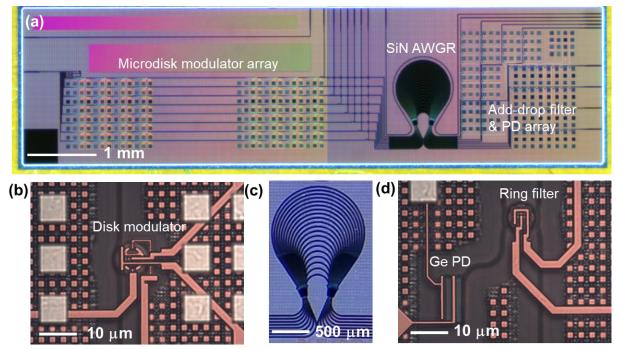

Here we detail our design of a chip version Si-LIONS system, characterization of individual components, and demonstration of error-free wavelength routing. Fig. 2 (a) shows the microscope image of the 8×8 Si-LIONS chip which was laid out using AIM Photonic process developed kit (PDK) 2.0 and fabricated through an AIM Photonic multi-project-wafer (MPW) run. An eight-wavelength laser emission was coupled into the chip through an edge coupler from the left side of the chip and then split equally into the 8 input waveguides. For each input ports of the 8×8 SiN AWGR, there is an array of

Fig. 2. (a) Optical microscope picture of the 8 x 8 Si-LIONS system with SiN AWGR and SiPh transmitters and receivers. Zoom-in pictures of (b) a silicon microdisk modulator, (c) the 8 x 8 SiN AWGR and (d) a silicon microring filter and Ge photodector pair.

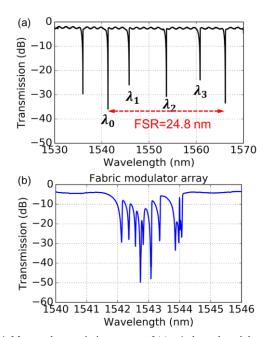

Fig. 3. Measured transmission spectra of the 8 x 8 SiN from (a) central waveguide input (input waveguide 5) and (b) side waveguide input (input waveguide 1).

8 microdisk modulators as SiPh transmitters and at each output ports, there is an array of 8 microring add-drop filters and photodetectors as the SiPh receiver. The microdisk modulator array and add-drop filters array are designed to have the highspeed metal pads arrangement and spacing to be compatible with a 65nm technology node electronic driver ICs [24]. A 90:10 coupler is used to monitor the resonance alignment of the modulators at each of the AWGR's input ports.

Figs. 2 (b) – (d) show the zoom-in photographs of a silicon microdisk modulator, the 8×8 SiN AWGR and a silicon microring filer and Ge PD pair. The microdisk modulator has a diameter less than 10  $\mu$ m. Therefore, the capacitance is only a few *fF*, which helps to reduce the power consumption. The designed 8×8 SiN AWGR has a footprint of 1.3 mm × 0.9 mm. The channel spacing is designed to be 200 GHz and FSR is designed to 1.6 THz for cyclic wavelength routing performance. The add-drop filter and Ge PD pair works as a wavelength selective receiver.

#### A. SiN AWGR Characterization

We measured the transmission spectra of the SiN AWGR after diced off 1-to-8 splitters and modulator arrays. The input port end facets are polished after the dicing. Figs. 3 (a) and (b) show the measured transmission spectra of the 8×8 SiN AWGR from central input and side input. Measured spectra are normalized to the wrapped around waveguide with similar length. We extract a 1.8dB insertion loss and a -13dB crosstalk for the central input. There is an additional ~1dB loss for the side input. We attribute the relatively high crosstalk to the unoptimized SiN AWGR design. In our previous design with narrower input/output waveguide spacing, we were able to achieve -18 dB crosstalk [25]. The sharp dips in the measured spectra originate from the add-drop filters at the output ports.

3

Fig. 4. Measured transmission spectra of (a) a 4-channel modulator array with different resonance wavelength and (b) a 9-channel modulator array with same resonance wavelength.

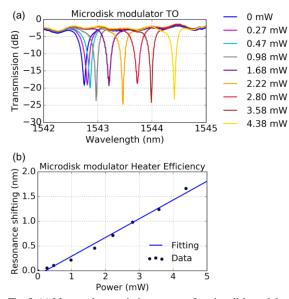

Fig. 5. (a) Measured transmission spectra of a microdisk modulator upon different heating power and (b) Measured and fitted heater.

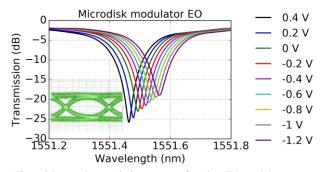

Fig. 6. Measured transmission spectra of a microdisk modulator upon different bias voltage. Inset: 10 Gb/s eye diagram of a modulator upon 1Vpp swing.

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Fig. 7. Experimental setup for the routing demonstration on the fabricated chip.

#### B. Microdisk Modulator Characterization

As shown in Fig. 2 (a), every four modulators in the modulator array are grouped together to be driven by a 65nm 4channel electronic IC. Fig. 4 (a) shows the measured transmission spectra of such modulator groups from the test structure. The resonance wavelengths are designed to have 800 GHz spacing. We studied the resonance wavelength uniformity on a single die using a cascaded nine microdisk modulator structure. All nine modulators are designed to have the same resonance wavelength. Fig. 4 (b) shows the measured transmission spectra from the nine-modulator array. We observed a maximum wavelength deviation of  $\pm 1$  nm (125 GHz). Therefore, resonance wavelength with the SiN AWGR channel passband.

The modulator element from the AIM photonic foundry's PDK has a built-in thermal tuner. Fig. 5 (a) shows the resonance red-shift upon different heating power. We extract a tuning efficiency of 0.38 nm/mW (Fig. 5 (b)), corresponds to 65 mW for tuning across a full free-spectral-range (FSR). Further reductions in this thermo-optical tuning power consumption can rise from selectively etching the oxide layer underneath [26].

Fig. 6 shows the measured electro-optical response of the modulator upon different bias voltage on the *p-n* diode. With 1V swing (-0.6 V to 0.4 V), the modulator reveals an extinction ratio (ER) > 20 dB with an insertion loss < 3 dB. The inset shows the 10 Gb/s eye diagram from the modulator with 1Vpp. Current modulation speed is limited by our pattern generator and according to the PDK performance [27], it can operate at a data rate up to 40 Gb/s.

#### C. Routing Experiments

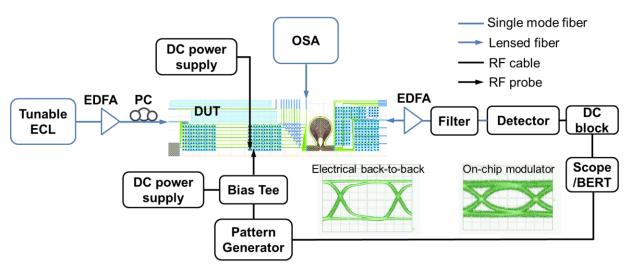

We demonstrated proof-of-concept wavelength routing interconnects using a setup shown in Fig. 7. A polarization controller (PC) is used to ensure TE polarization input and a pair of lensed fibers are used for coupling light into and out of the Si-LIONS chip. The input light of the chip is modulated by one of the on-chip microdisk modulator and routed by the AWGR. The optical signals at the AWGR output is amplified by another EDFA and detected by an external PD. In this

4

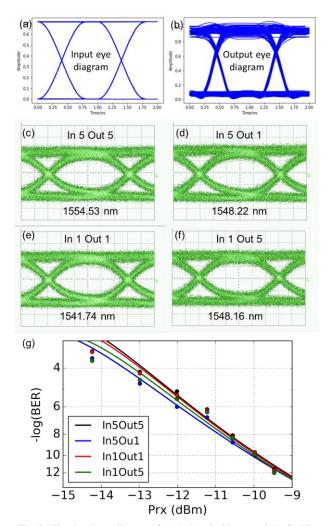

Fig. 8. Simulated eye diagrams for (a) electrical input and (b) Ge PD output. Measured eye diagrams for (c) input 5 to output 5, (d) input 5 to output 1, (e) input 1 to output 1 and (f) input 1 to output 5. (g) Measured BER curves as a function of received power.

experiment we did not use the on-chip Ge PD due to the lack of external transimpedance amplifier (TIA). Our new electronic driver ICs with on-chip TIAs will become available in early January 2019, their integration 2.5D and 3D integration of such driver ICs and SiPh PICs are in progress for all-to-all interconnect demonstrations. An RF probe array is used to provide DC signals to the heaters of the microdisk for resonance alignment and inject RF signals to the diodes of the microdisk for modulation. Resonance alignment is monitored through the top 90/10 coupler coupled to an optical spectrum analyzer (OSA). The eye diagram is measured by using an oscilloscope.

Figs. 8 (a) and (b) shows the simulated eye-diagram from the electrical input and from on-chip Ge PD using our Verilog-A based models [28]. The output eye diagram is mainly deteriorated by the coherent crosstalk from the AWGR passband. Figs. 8 (c) - (f) show the eye diagrams of 10 Gb/s OOK transmission from input port 5 to output port 5, input port 5 to output port 1, input port 1 to output port 1 and input port 1 to output port 5. The modulation signal is a  $2^{31}$ -1 PRBS produced by a pattern generator. The bias voltage is optimized to 0.9 V and the peak-to-peak voltage is set as 1V. Fig. 8 (e) shows the measured BER curves of all four paths. Error-free operations are achieved with received power larger than -10 dBm. BER curves from the on-chip Ge PD will be measured after driver ICs integration.

#### III. 2.5D INTEGRATION ON AN OPTICAL INTERPOSER

As shown in Fig. 1, an optical interposer is necessary to further extend chip-to-chip optical communications to all-to-all interconnects. In this section, we reveal our efforts on low-loss, alignment tolerant SiPh transceiver chip-to-interposer optical coupling, initial tapeout through AIM photonic passive interposer MPW run and future integration schemes using active optical interposer.

#### A. SiPh Transceiver Dies-to-interposer Optical Coupling

Conventional electrical packaging using flip-chip bonding typically has a placement error of  $\pm 0.5 \ \mu m$  [29], comparable to a typical silicon waveguide width, and misalignment could significantly increase after the annealing. Optical coupling could be deteriorated with such misalignment; therefore, it is critical to develop a low-loss, alignment-tolerant coupling method between the SiPh transceiver chip. Following our

5

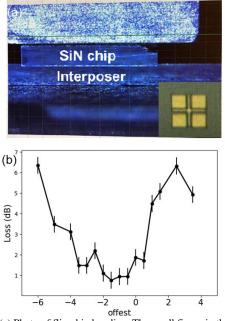

Fig. 9. (a) Photo of flip-chip bonding. The small figure in the right bottom illustrates the alignment of flip-chip bonding. (b) Experimental results of SiN to SiN inter-chip coupler.

previous work [30], we have designed and fabricated SiN-based evanescent coupler with an overlapping length of 500  $\mu$ m and a taper width of 250 nm (limited by the lithography tool).

We fabricated a simple straight waveguide structures with trenches to extract the coupling loss from interposer to SiPh chip. We then performed an Au-to-Au flip-chip bonding for the SiPh chip to interposer packaging (Fig. 9 (a)). Fig. 9 (b) shows measured coupling loss of the evanescent coupler upon different misalignment. We observed a minimum 0.41 dB loss from the coupler with 3dB tolerance to be  $\sim \pm 3 \ \mu m$  [31]. We attribute the loss variation within the tolerance band to the unwanted dust in the coupler region. Such low-loss and misalignment tolerant coupling methods developed here can be transferred to a foundry to enable efficient coupling from the SiPh die to optical interposer in a manufacturing environment.

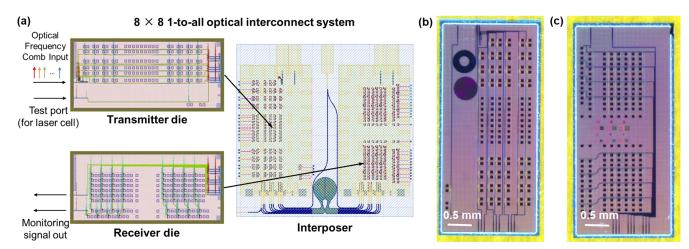

Fig. 10. (a) Schematic of the 8 × 8 SiN AWGR-based all-to-all system demonstrator on an optical interposer submitted to AIM photonics 2018 June MPW run. Optical microscope pictures of a SiPh (b) transmitter die and (c) receiver die to be bonded on the optical interposer.

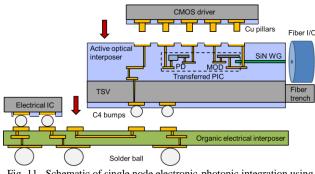

Fig. 11. Schematic of single node electronic-photonic integration using an active optical interposer

#### *B.* Initial Foundry Tapeout for Optical Interposer Based Allto-all Interconnects Demonstration and Future Integration on Active Optical Interposer

As a first step for optical interposer and SiN AWGR enabled all-to-all interconnection demonstration, we have taped-out an  $8 \times 8$  system demonstrator using AIM photonic passive optical interposer and full SiPh MPW run. Fig. 10 shows the layout layout of the optical interposer comprising an  $8 \times 8$  SiN AWGR integrated with SiPh transmitter and receiver dies. The transmitter die contains total 64 modulators on 8 input waveguides and the receiver die contains total 64 filter and Ge PD pair on 8 output waveguides. They will be both bonded on top of the optical interposer. The OFC laser signal will be fed into the transmitter chip from the fiber trench on top of the interposer. Given the footprint constraint, transmitter and receiver CMOS driver ICs will not be on the interposer. They will be wire-bonded from the left and right edges of the interposer to drive total 8 modulators and 8 PDs for a 1-to-all interconnection demonstration. We estimate the power efficiency of the entire system to be 3.2 pJ/bit, which can be decomposed into a laser power consumption of 2.4 pJ/bit, a Tx IC (including the modulator heating) power consumption of 0.4pJ/bit and a Rx IC (including the drop filter heating) power consumption of 0.4 pJ/bit.

The planned release of active silicon photonic optical interposer from AIM photonics in 2019 will greatly reduce the complexity and footprint needed for packaging and integration with CMOS driver and electrical ICs (e.g. GPU dies) to be interconnected. Fig. 11 illustrates a potential scheme for such integration. With the active SiPh components embedded in the optical interposer, CMOS drivers can directly connect to the modulators and PDs. This reduces the length of high-speed traces to below 10  $\mu$ m [32], far shorter than the passive optical interposer case. The optical interposer can then be integrated with the electrical ICs/dies to be interconnected through an organic interposer using the backside C4 bumps. Powering of the whole system will be provided from the PCB underneath.

#### IV. SCALING TO LARGE PORT COUNTS

For HPC applications, massive parallelism is preferred to connect thousands of GPUs, CPUs, FPGAs and etc. in flexible and scalable architectures. This requires a large port count possibly exceeding  $1000 \times 1000$ . In this session, we present our

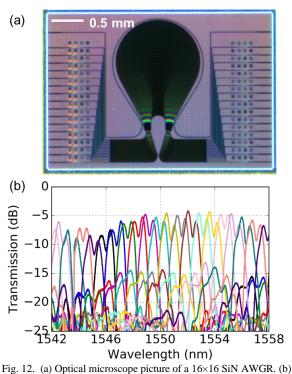

Fig. 12. (a) Optical microscope picture of a 16×16 SiN AWGR. (b) Measured transmission spectra of a 16×16 SiN AWGR from central input.

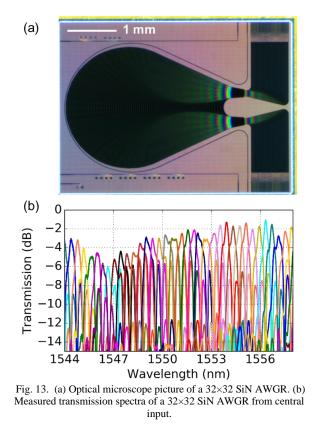

initial design and characterization results of  $16 \times 16$  and  $32 \times 32$  SiN AWGRs and discuss the port count scalability using the thin-CLOS architecture.

> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

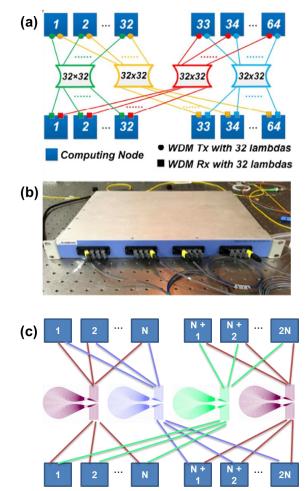

Fig. 14. (a) Schematic of a 64×64 all-to-all interconnect using four 32×32 silica AWGR in Thin-CLOS architecture. (b) Picture of the Thin-CLOS system in 1U rack. (c) Integrated Thin-CLOS architecture achieved with three layers of SiN.

#### A. Initial Designs and Results on 16×16 and 32×32 SiN AWGR

In the same MPW run, we have taped-out  $16 \times 16$  and  $32 \times 32$ SiN AWGR to explore the scalability of our AWGR devices. Fig. 12 (a) and Fig. 13 (a) shows the optical microscope images of the  $16 \times 16$  and  $32 \times 32$  SiN AWGR with a footprint of 2.4 mm × 1.6 mm and 4.6 mm × 2.9 mm. Fig. 12 (b) and Fig. 13 (b) shows the measured transmission spectra of the  $16 \times 16$  and  $32 \times 32$  SiN AWGR. We extracted an insertion loss of 5 dB and a crosstalk of -10 dB for the  $16 \times 16$  SiN AWGR and an insertion loss of 2 dB and a crosstalk of -10 dB for the  $32 \times 32$  SiN AWGR. We attribute the relatively high crosstalk partly due to the phase error induced from the fabrication imperfections (sidewall roughness, film thickness variation) in the relatively large device region. We believe this can be reduced using improved lithography method from foundry [33].

#### B. Thin-CLOS Architecture for Port Count Scaling

There are multiple limiting factors prevent our single SiN AWGR system from being practically deployed in a large scale ( $\geq$  32). Other than the fabrication imperfection induced the crosstalk discussed above, such imperfection also affects the

channel spacing and passband of the fabricated SiN AWGR devices. Second, As the total number of wavelength channel grows, coherent in-band crosstalk increases significantly [34]. This can deteriorate the BER of the optical links. Third, using the same spectral range with increased number of wavelengths would require a narrow channel spacing. This increases the total AWGR size and demands more complex OFC laser sources. To achieve large port count, it would be desirable to use many smaller port count AWGRs and combined them to provide the same interconnectivity offered by a single larger AWGR, with a price of increased waveguide routings to connect between the small AWGRs [16].

7

In our previous work [16], we have demonstrated a  $64\times64$  all-to-all interconnect systems in Thin-CLOS architecture using four standalone  $32\times32$  silica AWGRs (Fig. 14 (a)). The system is packed in 1U rack (Fig. 14 (b)) with a power consumption of 10W. It is possible to build a miniature system on-chip with 100× reduction in size and weight using the SiN AWGRs and multilayer SiN waveguides [25] for routing, as shown in Fig. 14 (c). The overall size of that chip can fit into a 22 mm × 22 mm area, given a  $32\times32$  SiN AWGR size of 4.6 mm × 2.9 mm. With recent developments, such multilayer SiN process offerings have become available in multiple foundries [27, 35], and foundry-based manufacturing based Thin-CLOS based large-scale optical interconnects can become possible.

#### V. SUMMARY

In this paper, we present and discuss our SiN AWGR-based integrated all-to-all optical interconnect systems through AIM Photonics foundry's active SiPh and passive optical interposer MPW runs. We have designed, taped-out and characterized a chip-scale Si-LIONS system with an 8×8 200GHz spacing cyclic SiN AWGR and SiPh modulators and PDs. We demonstrated wavelength routing with error-free data transmission using the on-chip modulator, the on-chip SiN AWGR, an off-chip laser, and an off-chip PD. New CMOS driver IC tape-out is complete and 2.5D and 3D integration of the electronic ICs with the silicon photonic transceivers are in We have designed and taped-out the optical progress. interposer version of the all-to-all system using SiN AWGRs and low-loss chip-to-interposer couplers. Here, we have designed and characterized a 16×16 and 32×32 SiN AWGRs. Utilizing such AWGRs, scaling to a high-radix all-to-all interconnect interposer is possible using the Thin-CLOS architecture and multilayer SiN waveguides.

#### ACKNOWLEDGMENT

The authors thank Prof. Sam Palermo, Dr. Kunzhi Yu and Dr. Po-Hsuan Chang for the CMOS driver ICs design and tapeout, and useful discussion for the electronic-photonic integration. Active silicon device and optical interposer chip were fabricated by AIM photonic MPW runs. Interposer test chip fabrication took place at the Marvell Nanolab Facility (Berkeley, CA) and at the Center for Nano-Micro Manufacturing (Davis, CA).

This research was developed with funding from American Institute of Manufacturing Photonics under contract numbers 201503002, 201704070 and 201700658.

The final version of record is available at http://dx.doi.org/10.1109/JSTQE.2019.2910415

#### > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

#### REFERENCES

- M. A. Taubenblatt, "Optical Interconnects for Large Scale Computing Systems: Trends and Challenges," in Advanced Photonics 2018 (BGPP, IPR, NP, NOMA, Sensors, Networks, SPPCom, SOF), Zurich, 2018, p. NeTh3F.2: Optical Society of America.

- M. A. Taubenblatt, "Optical Interconnects for High-Performance Computing," *Journal of Lightwave Technology*, vol. 30, no. 4, pp. 448-457, 2012.

- [3] A. Benner, "Optical interconnect opportunities in supercomputers and high end computing," in *OFC/NFOEC*, 2012, pp. 1-60.

- [4] S. Kamei, M. Ishii, M. Itoh, I. Shibata, Y. Inoue, and T. Kitagawa, "64 /spl times/ 64-channel uniform-loss and cyclic-frequency arrayed-waveguide grating router module," *Electronics Letters*, vol. 39, no. 1, pp. 83-84, 2003.

- [5] B. Glance, I. P. Kaminow, and R. W. Wilson, "Applications of the integrated waveguide grating router," *Journal of Lightwave Technology*, vol. 12, no. 6, pp. 957-962, 1994.

- [6] K. Chen, A. Singla, A. Singh, K. Ramachandran, L.Xu, Y. Zhang, X. Wen, and Y. Chen, "OSA: An Optical Switching Architecture for Data Center Networks With Unprecedented Flexibility," *IEEE/ACM Transactions on Networking*, vol. 22, no. 2, pp. 498-511, 2014.

- [7] R. Hemenway, R. Grzybowski, C. Minkenberg, and R. Luijten, "Optical-packet-switched interconnect for supercomputer applications[Invited]," *Journal of Optical Networking*, vol. 3, no. 12, pp. 900-913, 2004/12/03 2004.

- [8] P. Grani, R. Proietti, S. Cheung, and S. J. B. Yoo, "Flat-Topology High-Throughput Compute Node With AWGR-Based Optical-Interconnects," *Journal of Lightwave Technology*, vol. 34, no. 12, pp. 2959-2968, 2016.

- [9] R. Soref, "The Past, Present, and Future of Silicon Photonics," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 12, no. 6, pp. 1678-1687, 2006.

- [10] S. Feng, T. Lei, H. Chen, H. Cai, X. Luo, and A. W. Poon, "Silicon photonics: from a microresonator perspective," *Laser & Photonics Reviews*, vol. 6, no. 2, pp. 145-177, 2012/04/01 2012.

- [11] G. T. Reed, G. Mashanovich, F. Y. Gardes, and D. J. Thomson, "Silicon optical modulators," *Nature Photonics*, Review Article vol. 4, p. 518, 07/30/online 2010.

- [12] D. Feng, S. Liao, P. Dong, N. Feng, H. Liang, D. Zhang, C. Kung, J. Fong, R. Shafiiha, J. Cunningham, A. V. Krishnamoorthy, and M. Asghari, "High-speed Ge photodetector monolithically integrated with large cross-section silicon-on-insulator waveguide," *Applied Physics Letters*, vol. 95, no. 26, p. 261105, 2009/12/28 2009.

- [13] E. Timurdogan, C. M. Sorace-Agaskar, J. Sun, E. Shah Hosseini, A. Biberman, and M. R. Watts, "An ultralow power athermal silicon modulator," *Nature Communications*, Article vol. 5, p. 4008, 06/11/online 2014.

- [14] J. Wang, Z. Sheng, L. Li, A. Pang, A. Wu, W. Li, X. Wang, S. Zou, M. Qi, and F. Gan, "Low-loss and low-crosstalk 8 × 8 silicon nanowire AWG routers fabricated with CMOS technology," *Optics Express*, vol. 22, no. 8, pp. 9395-9403, 2014/04/21 2014.

- [15] M. J. R. Heck, H. Chen, A. W. Fang, B. R. Koch, D. Liang, H. Park, M. N. Sysak, and J. E. Bowers, "Hybrid Silicon Photonics for Optical Interconnects," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 17, no. 2, pp. 333-346, 2011.

- [16] R. Proietti, X. Xiao, K. Zhang, G. Liu, H. Lu, P. Fotouhi, J. Messig, and S. J. B. Yoo, "Experimental Demonstration of a 64-Port Wavelength Routing Thin-CLOS System for Data Center Switching Architectures," *Journal of Optical Communications and Networking*, vol. 10, no. 7, pp. B49-B57, 2018/07/01 2018.

- [17] S. Cheung, T. Su, K. Okamoto, and S. J. B. Yoo, "Ultra-Compact Silicon Photonic 512 × 512 25 GHz Arrayed Waveguide Grating Router," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 20, no. 4, pp. 310-316, 2014.

- [18] R. Yu, S. Cheung, Y. Li, K. Okamoto, R. Proietti, Y, Yin, and S. J. B. Yoo, "A scalable silicon photonic chip-scale optical switch for high performance computing systems," *Optics Express*, vol. 21, no. 26, pp. 32655-32667, 2013/12/30 2013.

- [19] A. H. Atabaki, S. Moazeni, F. Pavanello, H. Gevorgyan, J. Notaros, L. Alloatti, M. T. Wade, C. Sun, S. A. Kruger, H. Meng, K. Al Qubasisi, I. Wang, B. Zhang, C. V. Baiocco, M. A. Popovic, V. M. Stojanovic, and R. J. Ram, "Integrating photonics with silicon

nanoelectronics for the next generation of systems on a chip," *Nature*, vol. 556, no. 7701, pp. 349-354, 2018/04/01 2018.

8

- [20] L. Carroll, J. Lee, C. Scarcella, K. Gradkowski, M. Duperron, H. Lu, Y. Zhao, C. Eason, P. Morrissey, M. Rensing, S. Collins. Y. H. Hwang, and P. O'Brien, "Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices," *Applied Sciences*, vol. 6, no. 12, 2016.

- [21] A. Arbabi and L. L. Goddard, "Measurements of the refractive indices and thermo-optic coefficients of Si3N4 and SiOx using microring resonances," *Optics Letters*, vol. 38, no. 19, pp. 3878-3881, 2013/10/01 2013.

- [22] D. Dai, J. Bauters, and J. E. Bowers, "Passive technologies for future large-scale photonic integrated circuits on silicon: polarization handling, light non-reciprocity and loss reduction," *Light: Science* &*Amp; Applications,* Review vol. 1, p. e1, 03/29/online 2012.

- [23] K. Shang, S. Pathak, C. Qin, and S. J. B. Yoo, "Low-Loss Compact Silicon Nitride Arrayed Waveguide Gratings for Photonic Integrated Circuits," *IEEE Photonics Journal*, vol. 9, no. 5, pp. 1-5, 2017.

- [24] K. Yu, C. Chen, C. Li, H. Li, A. Titriku, B. Wang, A. Shafik, Z. Wang, M. Fiorentino, P. Y. Chiang, and S. Palermo, "25Gb/s hybrid-integrated silicon photonic receiver with microring wavelength stabilization," in 2015 Optical Fiber Communications Conference and Exhibition (OFC), 2015, pp. 1-3.

- [25] X. Xiao, Y. Zhang, R. Proietti, and S. J. B. Yoo, "Scalable AWGRbased All-to-All Optical Interconnects with 2.5D/3D Integrated Optical Interposers," in 2018 IEEE Photonics Society Summer Topical Meeting Series (SUM), 2018, pp. 161-162.

- [26] P. Dong, W. Qian, H. Liang, R. Shafiiha, D. Feng, G. Li, J. E. Cunningham, A. V. Krishnamoorthy, and M. Asghari, "Thermally tunable silicon racetrack resonators with ultralow tuning power," *Optics Express*, vol. 18, no. 19, pp. 20298-20304, 2010/09/13 2010.

- [27] AIM\_Photonics. (2018). Available: <u>http://www.aimphotonics.com/</u>

- [28] K. Zhang, X. Xiao, Y. Zhang, and S. J. B. Yoo, "Verilog-A Compact Modeling and Simulation of AWGR based All-to-All Optical Interconnects," in 2018 Conference on Lasers and Electro-Optics (CLEO), 2018, pp. 1-2.

- [29] M. J. Wale, "Self aligned, flip chip assembly of photonic devices with electrical and optical connections," in 40th Conference Proceedings on Electronic Components and Technology, 1990, pp. 34-41 vol.1.

- [30] K. P. Shang, S. Pathak, B. B. Guan, G. Y. Liu, and S. J. B. Yoo, "Low-loss compact multilayer silicon nitride platform for 3D photonic integrated circuits," (in English), *Optics Express*, vol. 23, no. 16, pp. 21334-21342, Aug 10 2015.

- [31] Y. Zhang, K. Shang, Y. Zhang, and S. J. B. Yoo, "Low-Loss Wafer-Scale Silicon Photonic Interposer Utilizing Inverse-Taper Coupler," in 2018 IEEE Photonics Conference (IPC), 2018, pp. 1-2.

- [32] C. McDonough, D. La Tulipe, D. Pascual, P. Tariello, J. Mucci, M. Smalley, A. Nguyen, T. Vo, C. Johnson, P. Nguyen, J. Corbet, G. Leake, E. Timurdogan, V. Stojanovic, M. R. Watts, and D. Coolbaugh, "Heterogeneous Integration of a 300mm Silicon Photonics-CMOS Wafer Stack by Direct Oxide Bonding and Vialast 3D Interconnection," *International Symposium on Microelectronics*, vol. 2015, no. 1, pp. 000621-000626, 2015/10/03 2015.

- [33] T. Horikawa, D. Shimura, H. Okayama, S. Jeong, H. Takahashi, J. Ushida, Y. Sobu, A. Shiina, M. Tokushima, K. Kinoshita, and T. Mogami, "A 300-mm Silicon Photonics Platform for Large-Scale Device Integration," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 24, no. 4, pp. 1-15, 2018.

- [34] E. L. Goldstein, L. Eskildsen, and A. F. Elrefaie, "Performance implications of component crosstalk in transparent lightwave networks," *IEEE Photonics Technology Letters*, vol. 6, no. 5, pp. 657-660, 1994.

- [35] W. D. Sacher, Y. Huang, G. Lo, and J. K. S. Poon, "Multilayer Silicon Nitride-on-Silicon Integrated Photonic Platforms and Devices," *Journal of Lightwave Technology*, vol. 33, no. 4, pp. 901-910, 2015.

**Yu Zhang** received his B. S. degree of Optoelectronics from Huazhong University of Science and Technology, Wuhan, China, in 2010 and the Ph.D. degree in Electronic and Computer Engineering from The Hong Kong University of Science and Technology, Hong Kong, in 2016. He is now an assistant project scientist in electrical and computer engineering at the University of California, Davis, CA.

His current research interest focuses on 3D integrated silicon photonic optical phased array, hybrid silicon laser, amplifier and phase modulators and silicon photonic integrated circuit enabled all-to-all interconnection for scalable highperformance computing systems.

Xian Xiao received the B.S. and M.S. degrees from Tsinghua University, Beijing, China, in 2012 and 2015. He has been working toward the Ph.D. degree in electrical and computer engineering at the University of California, Davis, CA, USA, since 2015.

He was a research intern with Nokia Bell Labs in the summer of 2016 and 2017, with Lawrence Berkeley National Laboratory from 2017 to 2018, and with Hewlett-Packard Labs in the summer of 2018.

His current research interest includes silicon photonics, optical interconnects, and 2.5D/3D photonic integration.

**Kaiqi Zhang** received the B.S. degree from Tsinghua University, Beijing, China, in 2016. He has been working toward the Ph.D. degree in electrical and computer engineering at the University of California, Davis, CA, USA, since 2016.

**Siwei Li** received the B.S. and M.S. degrees from Tsinghua University, Beijing, China, in 2012 and 2015. He has been working toward the Ph.D. degree in electrical and computer engineering at the University of California, Davis, CA, USA, since 2015.

Anirban Samanta received his B.E. degree in Electronics and Communications Engineering from Birla Institue of Technology, Mesra, India in 2012 and his M.S. degree from University of California, Irvine, USA in 2014. He is currently pursuing his Ph.D. degree in Electrical and Computer Engineering at the University of California, Davis, USA. He has previously worked with the ARIANNA neutrino detector group at Irvine, developing sensor systems for neutrino detection.

His current research interest focuses on Electronic-Photonic co-simulation, co-design and integration with applications in high performance computing and data centers.

**Yichi Zhang** was born in Lingbei, Shenyang, Liaoning, China in 1993. He received the B.S. degrees in electrical engineering from Nanjing University, in 2016.

From 2013 to 2016, he was a Research Assistant with the Jiangsu Provincial Key Laboratory of Advanced Manipulating Technique of Electromagnetic wave. Since 2016, he has been a Research Assistant with the Next Generation Networking Systems Laboratory, the University of California, Davis.

**Kuanping Shang** received the B.S. degree in physics with a second Bachelor degree in economics from Peking University,

China in 2011 and the Ph.D. degree in Electronic and Computer Engineering from The University of California, Davis, CA in 2017. He is now working at Intel.

From June 2009 to June 2010, he was a Research Assistant in the Institute of Modern Optics, Peking University. From June 2010 to June 2011, he was a Research Assistant in the State Key Lab for Mesoscopic Physics, China.

received degree Roberto Proietti the M.S. in telecommunications engineering from the University of Pisa, Pisa, Italy, in 2004, and the Ph.D. degree in electrical engineering from Scuola Superiore Sant Anna, Pisa, in 2009. He is a Project Scientist with the Next Generation Networking Systems Laboratory, University of California, Davis. His research interests include optical switching technologies and architectures for supercomputing and data center applications, high-spectral-efficiency coherent transmission systems, and elastic optical networking.

Katsunari Okamoto [M'85, SM'98, F'03] was born in Hiroshima, Japan, on October 19, 1949. He received the B.S., M.S., and Ph.D. degrees in electronics engineering from the University of Tokyo, Tokyo, Japan, in 1972, 1974, and 1977, respectively. In 1977, he was with Ibaraki Electrical Communication Laboratory, Nippon Telegraph and Telephone Corporation (NTT), Ibaraki, Japan, and was engaged in research on transmission characteristics of multimode, dispersion-flattened single-mode single polarization (PANDA) fibers, and fiber-optic components. He proposed for the first time the dispersion-flattened fiber (DFF) and succeeded in the fabrication of DFF that had chromatic dispersion less than  $\pm 1$ ps/km/nm over a wide spectral range. From September 1982 to September 1983, he was a Guest Researcher with the Optical Fiber Group, Southampton University, Southampton, U.K., where he was engaged in research on birefringent optical fibers. From October 1987 to October 1988, he was an Associate Professor with the Research Center for Advanced Science and Technology (RCAST), University of Tokyo, with Dr. E. A. J. Marcatili from AT&T Bell Laboratories. He was a Guest Professor of the endowed chair at RCAST. They studied the influence of nonlinear optical effects on propagation characteristics of optical fibers. Along with research activities, they taught electromagnetic theory, optoelectronics, and fiber optics at the Electronics and Applied Physics Department. Since 1990, he has been working on the analysis and the synthesis of guided-wave devices and the computer-aideddesign (CAD) and fabrication of silica-based planar lightwave circuits (PLCs) at Ibaraki R&D Center, NTT Photonics Laboratories. He developed a CAD tool based on the beam propagation method and a FEM waveguide and stress analyses. The design tool for arrayed waveguide grating (AWG) filter is widely utilized in the NTT Photonics Laboratory and its subsidiary company (NEL). He has developed a  $256 \times 256$  star coupler, various kinds of AWGs, ranging from eight-channel 300nm spacing AWGs to 128-channel 25-GHz AWGs, flat spectral response AWGs, and integrated-optic reconfigurable add/drop multiplexers. Two hundred to fifty gigahertz-spacing AWGs are now widely used in commercial WDM systems. In 2003, he started Okamoto Laboratory Ltd. Okamoto Laboratory is an R&D consulting company that deals with the custom

design of optical fibers and functional planar lightwave circuits. Since July 2006, he has been a Professor of electrical and computer engineering at the University of California, Davis (UC Davis). He has published more than 220 papers in technical journals and international conferences. He authored and coauthored eight books including Fundamentals of Optical Waveguides. His research interests include passive and active photonics devices for high-performance all-optical networks. He is a member of the Optical Society of America and the Institute of Electronics, Information, and Communication Engineers of Japan.

S. J. Ben Yoo [S'82, M'84, SM'97, F'07] currently serves as a distinguished professor of electrical engineering at UC Davis. His research at UC Davis includes 2D/3D photonic integration for future computing, communication, imaging, and navigation systems, micro/nano systems integration, and the future Internet. Prior to joining UC Davis in 1999, he was a Senior Research Scientist at Bellcore, leading technical efforts in integrated photonics, optical networking, and systems integration. His research activities at Bellcore included the next-generation Internet, reconfigurable multiwavelength optical networks (MONET), wavelength interchanging cross connects, wavelength converters, vertical-cavity lasers, and high-speed modulators. He led the MONET testbed experimentation efforts, and participated in ATD/MONET systems integration and a number of standardization activities. Prior to joining Bellcore in 1991, he conducted research on nonlinear optical processes in quantum wells, a four-wavemixing study of relaxation mechanisms in dye molecules, and ultrafast diffusion-driven photodetectors at Stanford University. Prof. Yoo received his B.S. degree in electrical engineering with distinction, his M.S. degree in electrical engineering, and his Ph.D. degree in electrical engineering with a minor in physics, all from Stanford University, California, in 1984, 1986, and 1991, respectively. He is Fellow of IEEE, OSA, NIAC and a recipient of the DARPA Award for Sustained Excellence (1997), the Bellcore CEO Award (1998), the Mid-Career Research Faculty Award (2004 UC Davis), and the Senior Research Faculty Award (2011 UC Davis).