## Doctoral Dissertation Doctoral Program in Computer and Control Engineering (34<sup>th</sup>cycle)

## Reliability and Security Assessment of Modern Embedded Devices

By

## Annachiara Ruospo

\*\*\*\*\*

#### **Supervisor:**

Prof. Ernesto Sanchez

#### **Doctoral Examination Committee:**

Prof. Letícia Maria Bolzani Poehls, IDS RWTH Aachen University, Germany

Prof. Alberto Bosio, École Centrale De Lyon, INSA Lyon, CNRS, INL, France

Prof. Giorgio Di Natale, Referee, Université Grenoble-Alpes, TIMA, CNRS, France

Prof. Luca Sterpone, Politecnico di Torino, DAUIN, Italy

Prof. Haralampos Stratigopoulos, Referee, Sorbonne Université, CNRS, LIP6,

France

Politecnico di Torino 2022

## **Declaration**

Annachiara Ruospo 2022

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

| Dedico tutto questo alla mia famiglia, da sempre e per sempre al mio fianco. |

|------------------------------------------------------------------------------|

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

## Acknowledgements

And I would like to acknowledge all the people who have shared this journey with me, providing me with incessant support and help, in different forms.

Firstly, I would like to thank my tutor, Prof. Ernesto Sanchez, for guiding me, advising me, helping me over the years of my Ph.D. I will be forever grateful to you for giving me this opportunity. It has been a journey not only professional, but of life. Thank you. I would like to thank Prof. Matteo Sonza Reorda for giving me his trust, in every situation, and for always being attentive to my professional growth. I would also sincerely like to thank Prof. Alberto Bosio for his constant support, for giving me interesting opportunities, and for introducing me to this stimulating and exciting research world.

Then, I would like to acknowledge all the professors in CAD & Reliability Group, and my colleagues for encouraging me to conduct my research in an enjoyable environment. A special thank goes to Professors Paolo Bernardi, Luca Sterpone, and Giovanni Squillero for our very interesting collaborations. Then, to Davide Piumatti, Andrea Floridia, Aleksa Damljanovick, Esteban Rodriguez, and Riccardo Cantoro for sharing with me my best and worst moments, and to all my current colleagues in LAB3+7. Thanks, Gabriele Gavarini for entering our exciting "TheNNReliable" team, thank you for your very valid support and for sharing with me the last important moments of my Ph.D. Next, I would like to thank Professor Luigi Dilillo, Lucas Matana Luza, and Marcello Traiola for our very interesting path together.

Last but not least, special thanks go to my lovely family, to Kevin, and to my friends for their constant and warm presence and, most importantly, for the energy they give me and encourage me every day. My family with unmeasurable love have always protected, supported, and encouraged me. Without them, none of this would have been possible. Thank you dad, mom, Ilaria, grandpa. Thank you, Kevin, for being exactly as you are. Thank you for sharing this journey with me.

To conclude, I would like to thank all the people I have met over these long years, who in different ways and intensities have given me the courage to achieve this goal.

#### **Abstract**

The complexity of modern embedded systems has increased rapidly over the past few decades. The integration of many various technologies as well as the adoption of more sophisticated algorithms pose significant challenges in ensuring the robustness and the reliability of these systems. Indeed, together with the shrinking of technology nodes, even more systems leverage artificial intelligence based algorithms to cope with their ever-growing computing requirements. In this light, worthy of note is the emerging trend toward the adoption of brain-inspired artificial models, i.e., Artificial Neural Networks, in different fields, like automotive, robotic, avionic, etc. If from one side this results to be a very interesting solution, given their outstanding and near-human computational capabilities; from the other side this could be dangerous from the safety point of view. Actually, outsourcing important decisions to them (like deciding whether the car should stop to let a pedestrian pass), can be threatening for the following reason. As a matter of fact, being predictive model, they are not 100% accurate: even in fault-free scenarios, they can provide a wrong answer. Then, despite their very interesting capabilities which are appealing for both industry and academic, it is necessary to deeply investigate the reliability and the behaviours of those systems in faulty scenarios, especially because it has been demonstrated that with the shrinking of the technology, emerging devices are more prone to physical defects.

This manuscript is organized in two parts. The primary focus of this Ph.D. thesis is on artificial intelligence-based systems and on the assessment and the improvement of their reliability. This topic has been addressed comprehensively at very different abstraction levels and from different perspectives. Firstly, a characterization of the existing fault models is provided together with the identification of the possible vulnerabilities in ANN-based systems. Then, a key contribution of these research activities is the proposals of different fault injection tools and methodologies to easy and support the reliability assessment process. Specifically, this is done at

different levels: by addressing only the ANN model, or by considering the entire system entailing both the ANN software running on a target hardware system. The advantages and disadvantages of the different categories are detailed in the manuscript. At this level, the principal novelties are the identification of the critical bits in different data type representations, the establishment of critical neurons depending on the importance of a neuron as a class- and as a network-dependent entity; trade-offs analysis on data type representations based on two aspects, i.e., the memory footprint of the application and their reliability. In the end, relying on these analysis and results, strategies to mitigate the effect of faults have been proposed. The first proposed technique aims at redistributing neuronal computations on an AI-based SoC by leveraging integer linear programming. The second mitigation technique is an on-line testing solution based on the adoption of Software Test Libraries coexisting with the requirements of ANN algorithms.

Together with the reliability assessment of neural networks, this Ph.D. thesis covers also a further important topic: the hardware security of modern embedded systems. The complexity of emerging hardware systems led the industry to pursue new development processes: to build a SoC, a recent trend is to rely on third-party IP blocks to keep the cost low and to meet the deadlines. This outsourcing poses increasing concerns regarding the security of modern embedded devices. As an example, these IP blocks might come with malicious circuitry intentionally added by adversaries, namely Hardware Trojans. They are hidden inside the design and become active under certain rare conditions (such as input sequences). Otherwise, they can be always active since the power on of their host device. Their malicious functionalities can vary from leaking secret information, degrading the circuit's performance, creating backdoors for attackers, and many others. In the literature, new advances and progress have been done in this field, especially in proposing specific detection methodologies to discover hidden Trojans inside a given design. However, the existing gap lies in the HT benchmarks used to validate state-of-the-art methodologies. Indeed, they are obsolete and very simple, unable to represent the complexity of current designs and architectures. For example, they are injected on small 8-bit 8051 microprocessors, or simple cryptographic circuits. In this context, one of the main contributions of this Ph.D. thesis is the release of a set of Hardware Trojans benchmarks at the Register Transfer Level for an open-source pipelined RISC core. They have been designed by following the guidelines for creating hardto-detect Trojans. Furthermore, the second contribution in this field is a pre-silicon detection methodology for detecting RTL Hardware Trojans. This is build on a deep learning analysis of the dynamic and static properties extracted from the design RTL model. Experimental results show that the proposed technique is highly accurate in highlighting suspicious code sections. By carefully inspecting them, it is possible to unfold all the hardware trojans.

## **Contents**

| Li | ist of Figures x |               |                                                         |     |

|----|------------------|---------------|---------------------------------------------------------|-----|

| Li | st of T          | <b>Tables</b> |                                                         | xvi |

| In | trodu            | ction         |                                                         | 1   |

| Ι  | Art              | tificial      | Neural Networks Reliability                             | 6   |

| 1  | Bac              | kground       | d and Related Works                                     | 8   |

|    | 1.1              | Fault I       | Models in ANNs                                          | 8   |

|    |                  | 1.1.1         | Fault Propagation                                       | 12  |

|    | 1.2              | Relate        | d Works                                                 | 13  |

|    |                  | 1.2.1         | Fault Injection Tools and Frameworks                    | 13  |

|    |                  | 1.2.2         | Advantages and Disadvantages of Fault Injection Method- |     |

|    |                  |               | ologies                                                 | 19  |

|    |                  | 1.2.3         | Related Studies on ANN Weights and Neurons              | 22  |

|    |                  | 1.2.4         | Related Studies on Mitigation Strategies                | 25  |

|    |                  | 1.2.5         | Software Test Library                                   | 26  |

| 2  | Mai              | n Conti       | ributions                                               | 28  |

| 3  | Reli             | ability A     | Assessment at the Software Level                        | 32  |

x Contents

|   | 3.1         | Static                                      | Parameters in Artificial Neural Networks |                                     |           |

|---|-------------|---------------------------------------------|------------------------------------------|-------------------------------------|-----------|

|   |             | 3.1.1                                       |                                          |                                     |           |

|   |             |                                             | 3.1.1.1                                  | Proposed Approach                   |           |

|   |             |                                             | 3.1.1.2                                  | Experimental Results                |           |

|   |             | 3.1.2                                       | Reduced                                  | Precision ANN Weights               |           |

|   |             |                                             | 3.1.2.1                                  | Proposed Approach                   |           |

|   |             |                                             | 3.1.2.2                                  | Experimental Results                |           |

|   | 3.2         | Dynan                                       |                                          | eters in Artificial Neural Networks |           |

|   | 3 <b>.2</b> | 3.2.1                                       |                                          | I Approach                          |           |

|   |             | 3.2.2                                       |                                          | ental Results                       |           |

|   | 3.3         |                                             |                                          | у                                   |           |

|   | 3.3         | Спири                                       | a Summu                                  | <i>y</i>                            | , 0       |

| 4 | Reli        | ability A                                   | Assessmen                                | nt at the Architectural Level       | <b>79</b> |

|   | 4.1         | Propos                                      | sed Approa                               | ach                                 | 79        |

|   | 4.2         | Experi                                      | mental Re                                | sults                               | 82        |

|   | 4.3         | Chapte                                      | er Summar                                | у                                   | 85        |

| _ | D 11        | 1 914                                       |                                          |                                     | 0.0       |

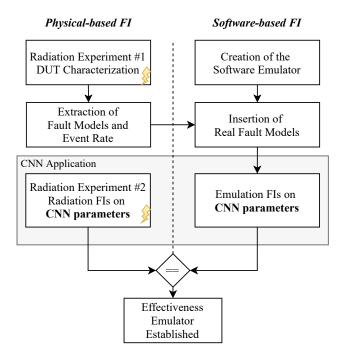

| 5 |             | eliability Assessment at the Physical Level |                                          | •                                   | 86        |

|   | 5.1         | Propos                                      | sed Approa                               | ach                                 | 86        |

|   |             | 5.1.1                                       | Radiation                                | n Experiments                       | 88        |

|   |             |                                             | 5.1.1.1                                  | DUT Characterization                | 88        |

|   |             |                                             | 5.1.1.2                                  | Radiation Tests on CNNs             | 89        |

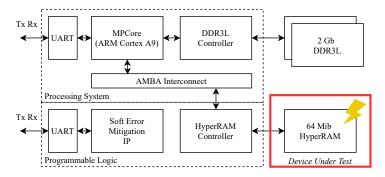

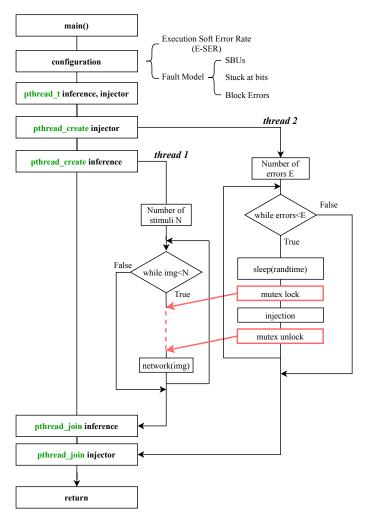

|   |             | 5.1.2                                       | Software                                 | Emulator                            | 92        |

|   | 5.2         | Experi                                      | mental Re                                | sults                               | 94        |

|   |             | 5.2.1                                       | Radiation                                | n Tests Results                     | 94        |

|   |             | 5.2.2                                       | Software                                 | Emulator Results                    | 96        |

|   | 5.3         | Chapte                                      | er Summar                                | у                                   | 104       |

Contents xi

| 6  | Miti                                              | gation                               | Strategies                                           | 106   |

|----|---------------------------------------------------|--------------------------------------|------------------------------------------------------|-------|

|    | 6.1 Neurons Redistributions on AI-oriented MPSoCs |                                      |                                                      |       |

|    |                                                   | 6.1.1                                | Proposed Approach                                    | . 108 |

|    |                                                   |                                      | 6.1.1.1 Integer Linear Programming based Methodology | . 109 |

|    |                                                   | 6.1.2                                | Experimental Results                                 | . 111 |

|    | 6.2                                               | 5.2 Software Test Libraries for ANNs |                                                      |       |

|    |                                                   | 6.2.1                                | Proposed Approach                                    | . 117 |

|    |                                                   | 6.2.2                                | Experimental Results                                 | . 120 |

|    | 6.3                                               | Chapte                               | er Summary                                           | . 126 |

| II | Se                                                | curity                               | of modern devices                                    | 128   |

| 7  | Bacl                                              | kground                              | d and Related Works                                  | 130   |

| 8  | Mai                                               | n Conti                              | ributions                                            | 134   |

| 9  | Har                                               | dware T                              | Гrojans                                              | 135   |

|    | 9.1                                               | Propos                               | sed Benchmarks                                       | . 135 |

|    |                                                   | 9.1.1                                | Experimental Analysis and Implementation             | . 137 |

|    | 9.2                                               | Pre-sil                              | icon Detection methodology                           | . 141 |

|    |                                                   | 9.2.1                                | Proposed Methodology                                 | . 141 |

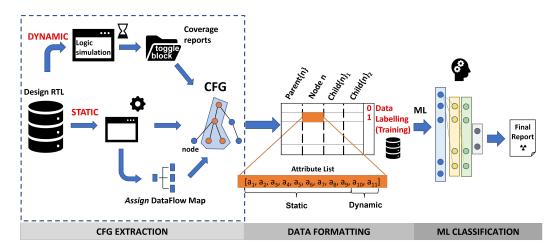

|    |                                                   |                                      | 9.2.1.1 Control Flow Graph Extraction                | . 143 |

|    |                                                   |                                      | 9.2.1.2 Data Formatting                              | . 145 |

|    |                                                   |                                      | 9.2.1.3 Classification                               | . 146 |

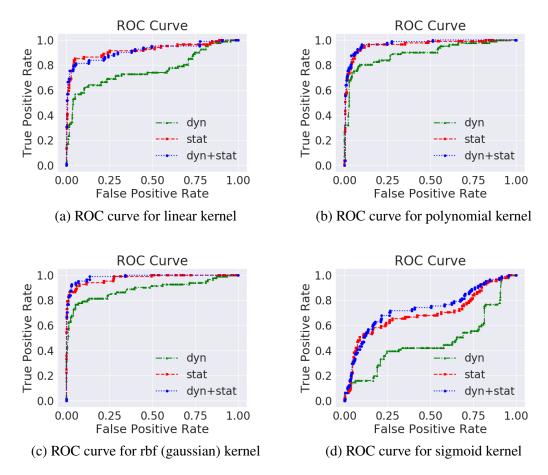

|    |                                                   | 9.2.2                                | Experimental Results                                 | . 147 |

|    | 9.3                                               | Chapte                               | er Summary                                           | . 153 |

| 10 | Con                                               | clusions                             | s and Achievements                                   | 156   |

| xii                    | Contents |

|------------------------|----------|

| 10.1 Future Directions |          |

| Bibliography           | 162      |

## **List of Figures**

| 1.1 | The fundamental concepts of fault, error, and failure applied to an ANN-based system.                                                                                                                                   | 10 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Fault Propagation in a full system [1]                                                                                                                                                                                  | 12 |

| 1.3 | Schematic of Fault Injection approaches for Deep Neural Networks.                                                                                                                                                       | 14 |

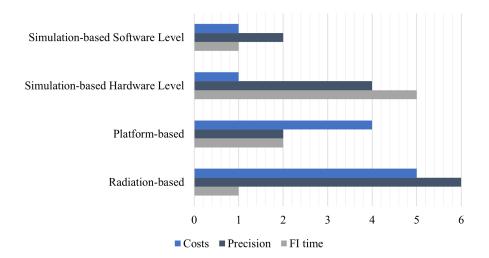

| 1.4 | Comparing different Fault Injection Techniques. The x-axis reports the specific level: 1-Low, 2-Medium-Low, 3-Medium, 4-High-Medium, 5-High, 6-Very High                                                                | 20 |

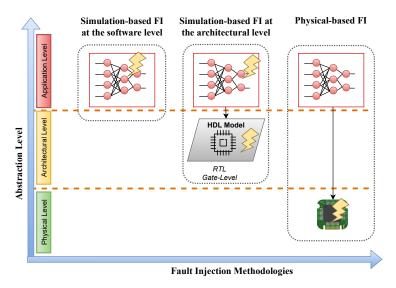

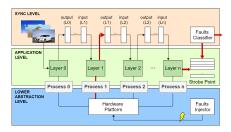

| 2.1 | Fault injection approaches for assessing the reliability of ANNs and ANN-based systems at different abstraction levels. In each situation, the lightning bolt icon illustrates where errors or faults can be introduced | 29 |

| 3.1 | Single Precision IEEE 754 Floating-Point Standard                                                                                                                                                                       | 34 |

| 3.2 | LeNet Masked Faults                                                                                                                                                                                                     | 38 |

| 3.3 | LeNet Safe Observed Faults                                                                                                                                                                                              | 38 |

| 3.4 | LeNet Unsafe Observed Faults                                                                                                                                                                                            | 39 |

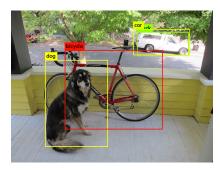

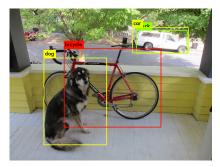

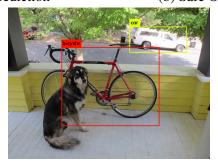

| 3.5 | Example of YOLO Predictions                                                                                                                                                                                             | 40 |

| 3.6 | Tiny YOLO Masked Faults                                                                                                                                                                                                 | 41 |

| 3.7 | Tiny YOLO Unsafe Observed Faults                                                                                                                                                                                        | 41 |

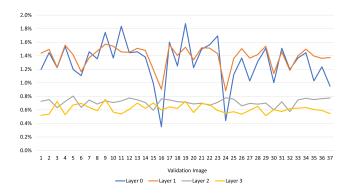

| 3.8 | YOLO Workload #4                                                                                                                                                                                                        | 42 |

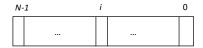

| 3.9 | Custom Data Type                                                                                                                                                                                                        | 43 |

**xiv** List of Figures

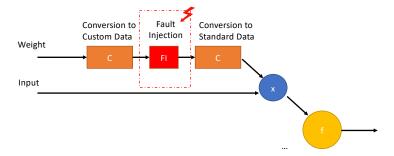

| 3.10 | On-line Weights Conversions                                                                                                                                                                                                                                           | 44 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.11 | Fault Injection Scenario [2]                                                                                                                                                                                                                                          | 46 |

| 3.12 | Critical Bits                                                                                                                                                                                                                                                         | 49 |

| 3.13 | LeNet-5 pre-trained weights distribution                                                                                                                                                                                                                              | 49 |

| 3.14 | YOLO pre-trained weights distribution                                                                                                                                                                                                                                 | 55 |

| 3.15 | Basic Scheme for a neuronal computation                                                                                                                                                                                                                               | 63 |

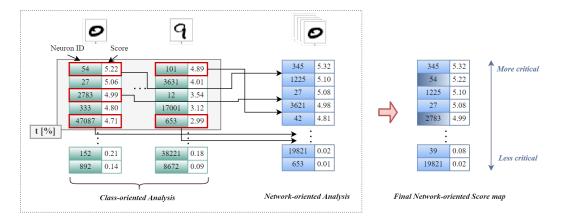

| 3.16 | The critical neuron identification process: a practical example with the MNIST dataset                                                                                                                                                                                | 66 |

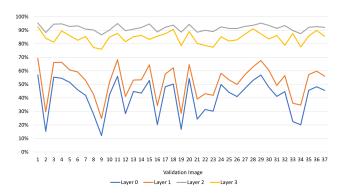

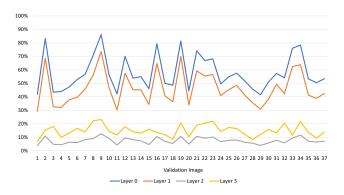

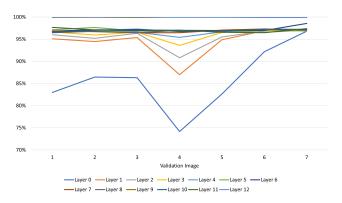

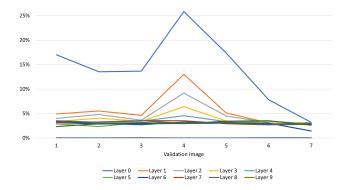

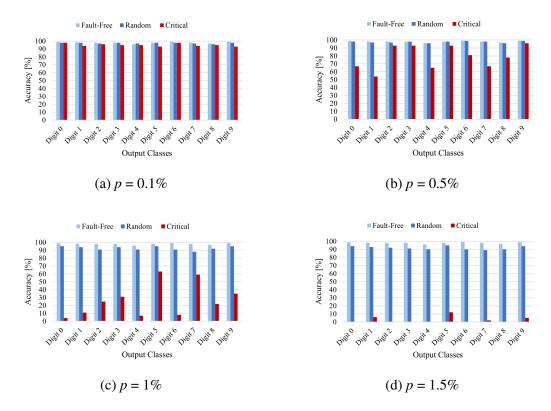

| 3.17 | MNIST LeNet: software fault injection campaigns on <i>random</i> and <i>critical</i> neurons                                                                                                                                                                          | 70 |

| 3.18 | SVHN ConvNet: software fault injection campaigns on <i>random</i> and <i>critical</i> neurons                                                                                                                                                                         | 71 |

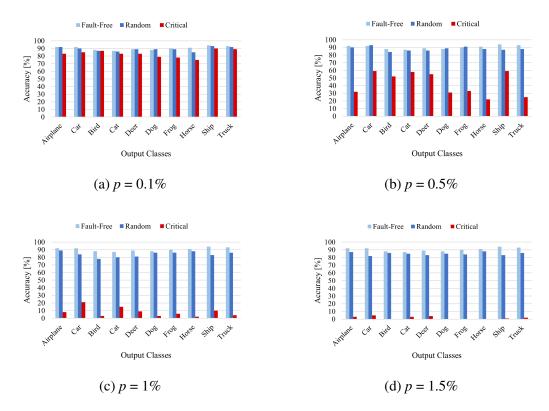

| 3.19 | CIFAR-10 All-CNN: Software fault injection campaigns on <i>random</i> and <i>critical</i> neurons                                                                                                                                                                     | 72 |

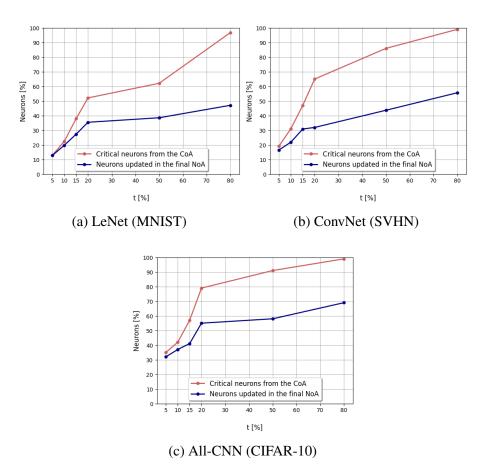

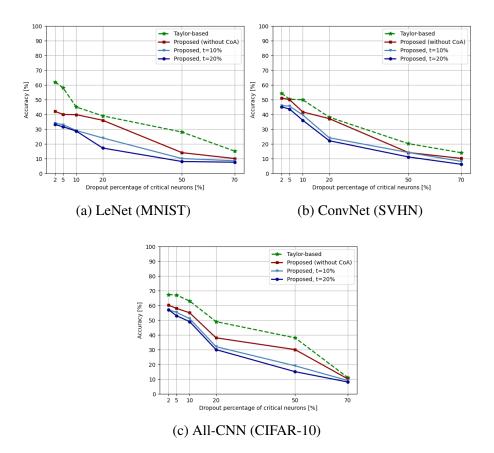

| 3.20 | Network-oriented Analysis with a growing t percentage of critical neurons from the CoA                                                                                                                                                                                | 74 |

| 3.21 | Showing the robustness of the proposed approach based on the contribution of the CoA and the NoA (blue lines). Its effectiveness is compared against [3] (green line) and our proposed methodology without the contribution of the class-oriented analysis (red line) | 75 |

| 3.22 | Intersection between the critical neuron ranking obtained using the test set and the rankings obtained using subsets of the validation set. The figure shows how, for ResNet-32, the intersection remains stable for different values of <i>pNeu</i>                  | 78 |

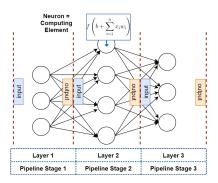

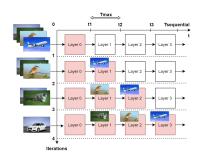

| 4.1  | Exploiting the pipeline technique to reduce the DNN simulation time.                                                                                                                                                                                                  | 81 |

| 4.2  | Proposed Pipelined Multi-Level Fault Injector Tool                                                                                                                                                                                                                    | 81 |

| 5.1  | Diagram of the Proposed Approach                                                                                                                                                                                                                                      | 87 |

| 5.2  | Top-level diagram of the system. The DUT is highlighted                                                                                                                                                                                                               | 91 |

List of Figures xv

| 5.3 | A diagram of the proposed emulator                                                                                                                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

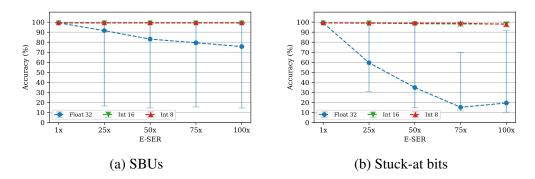

| 5.4 | Accuracy variation based on the increase of the E-SER with SBUs or stuck-at faults for the three CNNs                                                                                                    |

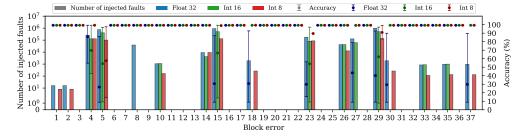

| 5.5 | Number of injected stuck-at faults for each single BE for each CNN application (y-axis on the left). Average accuracy value for each single BE affecting a run at a random time (y-axis on the right) 99 |

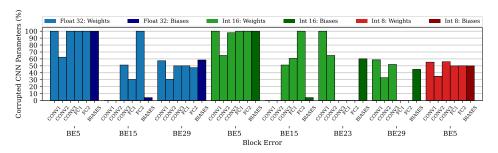

| 5.6 | The incidence of the most critical BEs on CNNs weights and biases. 101                                                                                                                                   |

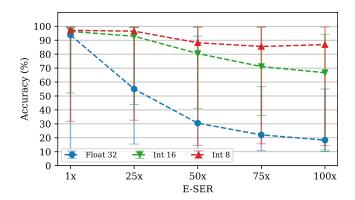

| 5.7 | Multiple block errors affecting the three CNNs under assessment 103                                                                                                                                      |

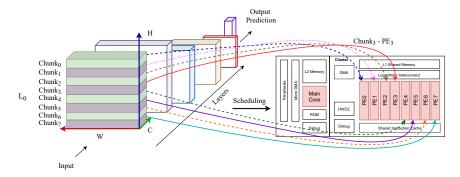

| 6.1 | Neurons assignment in a AI-oriented SoC exploiting the SIMD configuration                                                                                                                                |

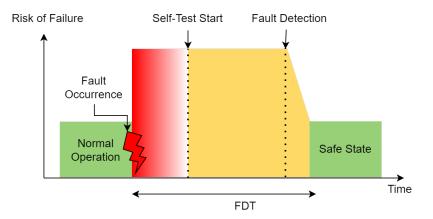

| 6.2 | Fault Detection Time                                                                                                                                                                                     |

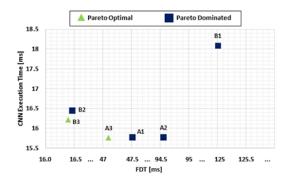

| 6.3 | CNN performance versus FDT                                                                                                                                                                               |

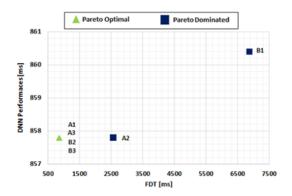

| 6.4 | Resnet-18 performance versus FDT                                                                                                                                                                         |

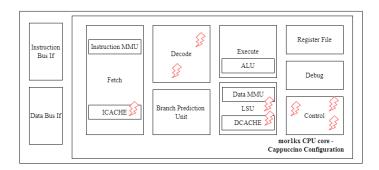

| 9.1 | RTL Hardware Trojans benchmarks inserted in the mor1kx CPU 138                                                                                                                                           |

| 9.2 | Flow of the proposed methodology                                                                                                                                                                         |

| 9.3 | ROC curves for 4 different kernels including different set of extracted attributes (farther from the 45-diagonal, i.e., closer to the upper-left corner, the better)                                     |

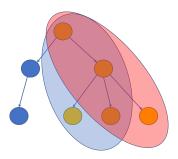

| 9.4 | Set of nodes belonging to Hardware Trojans as TP and FN 153                                                                                                                                              |

## **List of Tables**

| 3.1  | LeNet [4]                                                                                | 36 |

|------|------------------------------------------------------------------------------------------|----|

| 3.2  | Tiny YOLO [5]                                                                            | 37 |

| 3.3  | LeNet-5 Data Type Accuracy Loss [%]                                                      | 50 |

| 3.4  | LeNet-5 Fault List for Fault Injection Campaigns                                         | 50 |

| 3.5  | LeNet-5 Fault Injection outcomes with respect to the <b>Golden Standard</b> version      | 53 |

| 3.6  | LeNet-5 Fault Injection outcomes with respect to the <b>Golden Custom</b> version        | 54 |

| 3.7  | YOLO Data Type Accuracy Loss [%]                                                         | 55 |

| 3.8  | YOLO Fault List for Fault Injection Campaigns                                            | 56 |

| 3.9  | YOLO Fault Injection outcomes with respect to the <b>Golden Standard</b> version         | 58 |

| 3.10 | YOLO Fault Injection outcomes with respect to the <b>Golden Custom</b>                   | 61 |

| 3.11 | ANN Benchmarks                                                                           | 68 |

| 4.1  | Pipelined Fault Injector timing details                                                  | 83 |

| 4.2  | A comparison between the performances of the sequential fault injector wrt the pipelined | 83 |

| 4.3  | Fault Injection Results                                                                  | 84 |

| 4.4  | Sequential Framework vs Pipelined Multi-Level Framework                                  | 85 |

List of Tables xvii

| 5.1 | Estimated event rate for both test scenarios                                                                                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Summary of the runs that return a faulty accuracy at the end of the radiation tests on CNNs                                                                  |

| 5.3 | Details of SBUs and stuck-at bits injection for the <i>Float 32</i> , <i>Int 16</i> , <i>Int 8</i> CNNs with an increasing E-SER: 1x, 25x, 50x, 75x, 100x 97 |

| 5.4 | BE Injection Details                                                                                                                                         |

| 5.5 | Details of block error injections for the CNNs <i>Float 32</i> , <i>Int 16</i> , <i>Int 8</i> with an increasing E-SER: 1x, 25x, 50x, 75x, 100x 103          |

| 6.1 | Figures of variance when the chunks of neurons are assigned following a static scheduling                                                                    |

| 6.2 | Figures of variance when the chunks of neurons are assigned following the proposed ILP and Variance-based optimal scheduling 113                             |

| 6.3 | RTL Fault Injection Results                                                                                                                                  |

| 6.4 | CNN timing details                                                                                                                                           |

| 6.5 | Software Test Library Details                                                                                                                                |

| 6.6 | RI5CY stuck at faults details and test coverage                                                                                                              |

| 7.1 | RTL Hardware Trojan benchmarks available on Trust-Hub [6, 7] 132                                                                                             |

| 9.1 | Hardware Trojan Benchmarks Description                                                                                                                       |

| 9.2 | Synthesis Results                                                                                                                                            |

| 9.3 | Experimental results of the four SVM classifiers                                                                                                             |

| 9.4 | Experimental results of the Neural Network                                                                                                                   |

| 9.5 | Meaning of the confusion matrix in context of HT detection 153                                                                                               |

Nowadays, safety and security assessments for modern embedded systems are challenging tasks. Indeed, they have become increasingly complex and sophisticated due to the ever-growing computing requirements and capabilities. As a matter of fact, the growing complexity of emerging computing systems has called for enhanced computing paradigms. Among all the existing possibilities, Artificial Intelligence (AI)-based solutions and, specifically, brain-inspired computing models, have gained large interest in the industry and academia for their outstanding and near-human computational capabilities. Inspired by the human brain where billions of neurons process information in parallel [8], researchers have developed artificial models, named Artificial Neural Networks (ANNs) which mimic the functioning of the human brain [9]. The neural network history has its roots in 1943 with the seminar paper by Warren S. McCulloch and Walter Pitts [10]. For the first time, they described a formal neuron with capabilities similar to that of a Turing machine, and created a machine able to implement logical reasoning. The idea of exploring logic in terms of manifestations of a mental process forms the basis for the artificial intelligence world. From that historical time on, a large amount of studies made progress in improving the theory behind brain-inspired computations to build highly complex artificial models. For their superior qualities, they represent now one of the most used solutions for addressing complex computational problems.

AI-based systems surround our daily life, and, among other countless applications, they power our virtual assistants, transcribe our voice messages, recognize people in our phone, or, in our car. Moreover, they have found successful applications in several safety-critical domains, like automotive, robotic, avionic. Their adoption in human environments raises many concerns. For these reasons, assessing their reliability has become a crucial requirement, and, due to their complexity, there is a growing need to develop even more sophisticated methodologies to accomplish

this scope. It is also worth adding that neural networks are notorious for producing inaccurate inference results. They are not 100% accurate due to their nature as predictive models, which provides an essential aspect that must be considered when addressing the reliability of these systems. Adoption in road cars, for example, may lead to the violation of functional safety requirements (e.g., ISO 26262 [11]). As a consequence, recently, the research community has become even more interested in determining aspects such as the reliability and trustworthiness of AI-based systems.

It is worth saying that, ANNs are traditionally considered intrinsically faulttolerant and tightly robust, being brain-inspired models. Indeed, our brain is known as the best information processing system, with its 10 billion nerve cells (i.e., biological neurons) and about 10,000 synapses for each connection starting from a neuron. Because of its plastic capacity to renew, repair, and reconfigure its neuronal activities, it can withstand synapses or neuron errors while still operating correctly [12]. Clearly, this fascinating plastic property can not be extended to artificial neurons, which being mathematical models, are not capable of self-repairing from errors. On the other hand, it is necessary to specify why it is claimed that they can be considered inherently robust and fault-tolerant models. Firstly, they own a certain degree of robustness because of their redundancy. In fact, such artificial models are composed of more neurons than they really need. This property is known as *over-provisioning* and constitutes a very key principle in neural networks fields [13]. Due to this excessive neurons budget, it has been demonstrated that over-provisioning leads to robustness [14]. In other words, this characteristic means that ANNs can accept a finite number of neurons failing without affecting the computation's outcome; beyond that number, accuracy declines gradually [15]. The second reason behind the claim of the intrinsic robustness is related to their distributed and parallel architecture. In those systems, the unit of failure is one single neuron or synapse. Examples are reported by IBM teams which recently presented neuromorphic implementations of convolutional neural networks where neurons can fail independently [16].

Under these assumptions, i.e., (i) the over provisioning and (ii) the single neuron-s/synapse as units of failures, artificial neural networks can be considered having an intrinsic robustness and reliability.

However, in the real world this is not totally true, because they are not used as pure mathematical models, but they are deployed on silicon. The first examples of digital architectures devised for neural networks have been systolic array structures,

very suitable to express their recurrence and parallelism [17, 18]. In that particular architecture, an individual processing element implemented the function of an associated neuron while the weights were stored in a circular memory. For another perspective, it means that a single physical fault affecting the hardware corrupted a single neuronal computation. Therefore, the single neurons as unit of failure was preserved in that case. Currently, neural networks are typically executed on high-performance GPUs or optimized custom ASIC designs, where a single hardware unit implements many neuronal computations. As a consequence, a single physical fault affects many neurons, tearing down the theory of the intrinsic fault tolerance.

A growing number of AI-based systems are built on ASIC design implementations, especially those exploited on the Internet of Things (IoT) world and for the edge computing (e.g., [19, 20]). The reason lies in their flexibility, which makes them suitable for a wide range of applications requiring low-power and low-cost resource-constrained embedded devices. On a final note, regardless the used architecture (e.g., GPUs, FPGAs, ASICs), new emerging devices at nanoscale dimensions are more prone to manufacturing defects and transient faults [21]. In other words, the probability that parts of the hardware fail due to the occurrence of physical faults increases as the shrinking of semiconductor technologies continues.

In light of these considerations, it starts to be crucial to evaluate the reliability of systems based on artificial neural networks and, generally, artificial intelligence algorithms. This is further motivated by the following considerations:

- Being predictive models, they are not 100% accurate. Even in fault-free scenarios, they can provide a wrong result.

- In many contexts and applications, they make choices for us.

- There is a growing push from the industry to deploy them on safety-critical systems (e.g., self-driving cars).

**Part I** of the manuscript addresses this topic and describes the principal contribution of my Ph.D. thesis in this field. The primary focus is on the reliability assessment of artificial neural networks and AI-based hardware systems. First, an in-depth investigation has been done to understand the main vulnerabilities of those systems; then, tools and methodologies have been proposed to perform reliability assessments, and then, mitigation solutions are proposed to improve their reliability.

In this manuscript, a detailed background in the area is given in Chapter 1: the principal vulnerabilities and fault models are addressed, and a specific section on related works is provided. The novelties and the main contributions are illustrated in Chapter 2. Next, Chapters 3, 4, and 5 detail the main research works that have been done to assess the reliability of ANNs at very different abstraction levels: respectively, at the software by considering only the neural network model, at the hardware by presenting the architecture of a RTL fault injector, at the physical by describing the architecture of a software emulator which is capable of injecting real faults retrieved from radiation test campaigns. Finally, leveraging the outcomes coming from the previously described assessment phase, mitigation strategies are proposed in Chapter 6 to improve the reliability of ANNs running on hardware embedded systems. An Integer Linear Programming (ILP)-based method is proposed to redistribute neuronal computations on a resource-constrained AI-oriented ASIC device to improve its reliability. Finally, the adoptions of Software Test Libraries (STLs) for the on-line testing and their coexistence with the requirements of artificial neural networks are investigated in a study.

ANNs Reliability is not the only issue covered in this manuscript. Part of the research in these years focused also on the security of modern embedded devices. In the last years, the growing complexity of modern devices and the fabrication costs led the Integrated Circuit (IC) industry to pursue a new global business model. In that regard, even more companies around the world are deeply involved in all phases of the IC supply chain. The outsourcing of part of the process to untrusted third-party entities raises growing concerns about the hardware security of the final products. Particularly, Hardware Trojans (HTs) are gaining worldwide attention not only from academia and industries, but also from government bodies [22]. Hardware Trojans are malicious and intended alteration of a circuit, that endangers the trustworthiness and the security of the hardware, leading to unwanted behaviour. As an example, a HT may leak secret information, change the circuit functionality or degrade the performance. In the literature, the vast majority of the existing detection techniques are applied at gate-level [23][24]. However, a growing examples of HTs inserted at the RTL are coming out, due to the flexibility for implementing various malicious functions. Hence, more RTL HTs detection techniques are needed.

**Part II** of the manuscript deals with this issue: the security of modern embedded systems. Chapter 7 provides background knowledge in the field together with an accurate analysis of state-of-the-art research works. Chapter 8 introduces the main

novelties in the field. Then, in Chapter 9, the two main contributions in this topic are described: first, the description of newly released RTL Hardware Trojan benchmarks for pipelined RISC microprocessor cores. Second, a machine learning-based strategy to detect RTL Hardware Trojans at the pre-silicon phase of the supply chain. The analysis is based on dynamic and static properties extracted from the RTL model of the design under assessment.

To conclude, Chapter 10 includes a summary of this research, together with useful information on future research directions and recommendations.

# Part I Artificial Neural Networks Reliability

## **Chapter 1**

## **Background and Related Works**

The origin of Artificial Neural Networks (ANNs) dates back to 1943 with the work published by W. Pitt and W. McCulloch [25], where the concept of a neuron as a computing unit was formalized for the first time. They are computing models composed of computing nodes, i.e., neurons, connected to one another through communication links, i.e., synapses. The role of an ANN is essentially to mimic the behaviour of a function. For this purpose, ANNs are first trained by observing the function input-output correspondence. Then, they can reproduce the learned function behaviour by propagating the computed values from the input neuron(s) to the output neuron(s) [9]. The propagation is regulated by weights and biases parameters, which are specific to each synapse and neuron, respectively. Neurons are arranged in layers, at least one input layer, one intermediate (or hidden), and one output layer and multiple hidden layers, is named a *deep* neural network.

The intent of this chapter is to provide the reader with basic definitions and concepts in the field. Section 1.1 overviews the different fault models existing in ANNs. In Section 1.2, related works in the topic are described.

#### 1.1 Fault Models in ANNs

It is known that Artificial Neural Networks have built-in fault-tolerance properties due to their distributed and parallel structure, as well as for their redundancy due to over-provisioning [13]. However, the evaluation of their fault tolerance is not a trivial task because there are no common systematic methods or tools for the assessment [21]. The intent of this section is to introduce and clarify basic definitions related to fault types and fault models in ANNs and ANN-based systems.

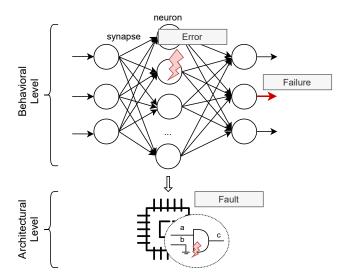

Fault Injections (FIs) have long been acknowledged as appealing techniques for assessing the dependability of systems under test among all available testing approaches. Such procedure consists of introducing faults/errors into the system under test and checking its behaviour in response to them. To address reliability issues in ANNs, it is first necessary to clarify where faults can be injected and at which abstraction level. Dealing with different abstraction levels, before delving into the distinct reliability assessment approaches, it is worth reminding the fundamental concepts of defect, fault, error, and failure [26]. A defect in an electronic system is the difference between the intended design and the implemented hardware. Typical defects are due to the process, the material, the age of the device, and the package. The representation of a defect is a *fault*, an anomalous physical condition that may lead to an error. An error is the exhibition of a fault in a system that might not or might be propagated and, in this last case, give rise to failures. An example of their application to the neural network field is reported in Figure 1.1, where the two principal levels are illustrated: the architectural and the behavioural one. The former includes the target hardware device, the latter the artificial neural network application. If the injections are performed at the behavioural level, we can talk about errors and failures, whereas if they address the physical abstraction level, also referred to as architectural, we will refer to faults. For the system represented in Figure 1.1, the defect is the short circuit to the ground, while the fault is the signal b stuck-at logic 0.

In this light, reliability assessments in the neural network domain can focus on: (i) the neural network model as a technology-independent software application, (ii) the system comprising both the neural network model and the final hardware architecture running it. In the first case (i), a designer might be interested in evaluating the robustness of the neural network, regardless of the target device on which it will be deployed. As a consequence, a fault injection process can target only the entities belonging to the ANN model, i.e., neurons and synapses. According to [15], each neuron must be considered as a single entity that can fail independently of the failure of any other. This is also true for synapses. In line with the classification proposed in [21], errors in artificial neural networks may occur in the following elements:

- **Communication channels**: The communication link between two neuron cells can be broken due to faulty interconnections or noise.

- **Synaptic weights**: Weights represent the strength of the connection between two neuron cells.

- **Neuron body**: It constitutes the core of the neuron cell and includes both the summation and the activation function. An error affecting the neuron body can be distinguished in two categories: *crash* and *byzantine*. In the first, the neuron completely stops its activities and saturates to positive/negative values. In the second, it transmits arbitrary values.

Figure 1.1 The fundamental concepts of fault, error, and failure applied to an ANN-based system.

Therefore, a FI campaign can mimic the occurrence of such error types. When running the FI campaigns, all these sources of errors can be considered to assess the ANN resilience. Other similar fault model classifications for ANNs are proposed by Sequin and Clay in [27], Chandra and Singh in [28], and Bolt in [29]. Specifically, in [29], the author presents a method for developing fault models at the abstract level by taking into account several characteristics, such as the fault location and the time of occurrence. In practice, having the high-level model of the ANN under test, these errors can be injected in the following faulty locations: weights, biases, communication links, and input or output neurons.

As regards the second case (ii), a designer might be interested in evaluating the robustness of the entire system before deploying a given ANN on a final device. Therefore, together with the error types affecting the ANN software model, all the physical faults affecting the hardware model should be taken into account. Faults affecting electronic devices can be classified for their temporal characteristics as permanent or transient. The former is stable with time and represents irreversible physical damage. The latter is active only for a short period of time and arises as a result of external disturbance or abnormal conditions or events (e.g., particle strikes). Starting from this broad fault types classification, the following fault models have been proposed over the years as abstractions of physical defects in electronics devices:

- 1. **Stuck-at**: Individual elements of the electronic device are tied to a state. For example, in a memory array, the bit can be stuck at a logical '1' or '0', and regardless of the operation, the read result will be the same.

- 2. **Bit-Flip**: Individual memory elements of the electronic device had their logical state changed. This change in the logical state can be recoverable by resetting the value on the element.

The stuck-at fault is a very common fault model. Indeed, it has been shown that many transistor and interconnection defects can be modelled with fair accuracy as permanent defects at the logic level. On the other hand, a random bit-flip model can represent the occurrence of transient faults, usually affecting registers or memory regions. Transient faults (i.e., soft errors) may be caused by different sources of interference phenomena such as electrical noise, electromagnetic interference and impinging ionizing particles. However, it is fair to say that today these two fault models are not able to cover the newer fault mechanisms of the deep-submicrometer technologies: new fault models are needed to deal with delays, stuck-opens, open-lines, bridgings, and transient pulses.

Nevertheless, it has been demonstrated that the stuck-at and bit-flip models allow a good investigation of the fault tolerance also at behavioural level [21] and, for this reason, they have been widely used for reliability studies. For instance, an error affecting the communication channels of a neural network can be modelled as a single or multiple stuck-at-0 or stuck-at-1 faults affecting one or more bits of the channel. Similarly, an error in the synaptic weights can be represented with a stuck-at

fault (o bit-flip) impacting one or more bits of the weight parameter. For example, if adopting a 32-bit floating-point representation, an error in a weight means that one or more bits of the 32 can be faulty. The same reasoning can be applied for representing a crash or byzantine neuron. A neuron can be considered dead if it is no longer transmitting values: this error can be modelled with a stuck-at-0 at its output. Contrarily, a Byzantine neuron can be modelled as a stuck-at-value.

Figure 1.2 Fault Propagation in a full system [1].

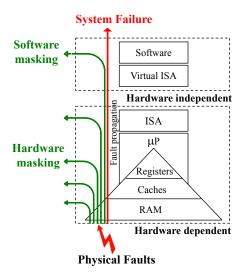

#### 1.1.1 Fault Propagation

So far, all the possible fault models existing in neural network based systems have been detailed. Nevertheless, it is worthy of note to discuss *how* hardware faults can be propagated in a system. The hardware system can be affected by faults due to physical manufacturing defects. As shown in Figure 1.2, faults can propagate through the various hardware structures that encompasses the entire system. However, it is likely that they will be masked during the propagation, either at the technological or at the architectural level [1]. When a hardware fault reaches the software layer, it might damage data, instructions, or control flow. These errors can cause incorrect program execution, resulting in erroneous results, or they might block the application from running, resulting in unexpected termination or application hangs. At the same time, the software stack can hide mistakes, avoiding failures at the output of the application. These phenomena are both inherently crucial for system reliability

1.2 Related Works

and a difficult challenge for engineers who must verify the safety of their systems. Additionally, it must be said that the scenario illustrated in Figure 1.2 is valid for *every* kind of application. It has been pointed out for an interesting reason: apart from the above-described system (hardware or software) masking ability, neural network applications possess an intrinsic masking ability, by their own. It is therefore very interesting to understand how these properties coexist and combine.

#### 1.2 Related Works

In the literature, several research studies have been done in this field. As stated, the research community has been even more interested in understanding the reliability of artificial neural networks and systems based on them. This section first cover the principal fault injection techniques and tools proposed at very different levels, and discusses their main advantages and disadvantages (Sections 1.2.1 and 1.2.2). Next, it presents related works in the literature: techniques to study the resilience of weights and neurons in neural networks are presented in Section 1.2.3, and to improve their robustness in Section 1.2.4. Finally, an overview of the Sofware Test Libraries (STLs) is given in Section 1.2.5.

#### 1.2.1 Fault Injection Tools and Frameworks

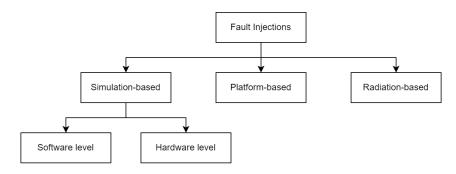

In [30], we propose a preliminary classification for classifying the state-of-the-art FI methodologies for the assessment of ANNs reliability. Depending on the abstraction level, they can be ranked in the following way.

- **Simulation-based:** The injection process is carried out without relying on the physical device finally running the ANN. Moreover, depending on the abstraction level, they can be further ranked.

- Software Level: The injections are performed on a high-level model of the ANN, not considering any details of the actual hardware architecture.

- Hardware Level: The injections are performed on a more accurate model of the ANN that simulates the target hardware architecture. This can be described at the register transfer level (RTL) or gate level, for example.

- **Platform-based:** The measurements and the analyses are performed directly on a physical device that emulates the final implementation of a design using FPGAs or on physical platforms running the ANN under assessment, e.g., CPUs and GPUs.

- Radiation-based: The reliability assessment is performed in the actual platform running the ANN under assessment by means of external electromagnetic interference, such as ionizing particle incidence through accelerated radiation test campaigns.

A schematic illustration is given in Figure 1.3.

Figure 1.3 Schematic of Fault Injection approaches for Deep Neural Networks.

The great majority of published works in this topic consists in **simulation-based software-level** methodologies: they are the most frequently used for having lower costs, for being faster, more controllable, and easier to deploy. To investigate the weaknesses of the neural network, and to be independent of any potential hardware architecture, a Fault Injection (FI) framework is typically developed to inject errors in a high-level model of the DNN under assessment. Two principal ones are publicly available to run neural network applications: TensorFlow [31] and PyTorch [32]. They are open-source machine learning frameworks for DNN-based applications that in the last years enjoyed enormous popularity among engineers and developers. Clearly, these represent the most popular solutions, but many others are available in the research community: N2D2 [33], Darknet [34], or even custom tools have been created for the purpose. In [35], Chen *et al.* present TensorFl, a high-level FI framework for DNN. It is a flexible tool that can be used to inject faults at the TensorFlow graph level, particularly at the output of the TensorFlow operators. NN models are represented as a sequence of operations (nodes) in TensorFlow, which

1.2 Related Works 15

are connected in a computational graph. It means that faults can be injected at the TensorFlow graph level (in the high-level programming logic) by corrupting the outputs of the most common operators (e.g., Add, Sub, Mul, ReLU, Conv2D). Since TensorFlow does not expose the operators and most of the execution occurs "behind the scenes", TensorFI is created by duplicating the original TensorFlow graph. Then, at inference time, it is possible to choose between the golden operators and the faulty ones. Only transient faults are injected in one of the following formats: by flipping a single bit in one (or all) the data item(s) of the target operator; by shuffling one (or all) the data item(s) of the target operator into random values; by changing the output of the target operator into all zeros. A further TensorFlow-based software-level FI framework is described in [36]. It is written in Python and, similarly to TensorFI, it uses the TensorFlow graph to inject errors into the most common mathematical operations Add, Sub, and Mul. Three types of errors are introduced at the output of the faulty operator: a single bit-flip, a random value instead of the computed one, all zeros. On the base of [35], an efficient fault injector for finding the safety-critical bits in DNN-based application is proposed in [37], namely BinFI. The goal of the framework is to identify the safety-critical bits that are most vulnerable to hardware transient faults (soft errors) and protect them at low cost. Since the purpose is to pinpoint all the safety-critical bits of the program to measure its overall resilience, a random FI based on statistical sampling would not have covered all the cases, and thus, was not suited for the scope. An exhaustive FI would have resulted in substantial performance overheads. Indeed, depending on the number of bits in the program, the time would have been directly proportional. Therefore, a binary search FI approach (BinFI) was used by exploiting the monotonicity feature of the functions used in ML applications, which is extremely useful to prune the FI space and efficiently detect the safety-critical bits. The framework is built on the top of TensorFI. To identify the critical bits of the DNN, faults are injected in the processor datapath (pipeline registers and ALU) and propagates to the software level (the ML application). Note that they consider faults that are not masked before reaching the software layer (as described in Section 1.1.1, as masked faults do not affect the execution of the application. It is assumed that the main memory, cache and register file are protected by error correction code (ECC) or parity, and thus, not considered as faulty locations. In line with prior works [35, 36] and studies on how hardware faults lead to erroneous values (instruction-level errors in [38]), errors in BinFI are injected directly into the output value of TensorFlow operators.

On the other side, based on PyTorch, Mahmoud *et al.* propose in [39] a runtime perturbation tool for DNNs, named PyTorchFI. It allows performing FIs in weights and/or neurons in convolutional operations. Perturbations in weights are performed offline by modifying the weight tensor, while neuron values are modified during the forward pass of a computational model by exploiting the hook functionality. Even though PyTorchFI operates at the application level of DNNs, it can also model lower level faults (such as register-level) by mapping them to single or multiple bit-flips in single or multiple neurons. FI campaigns are performed to study the reliability of six neural networks adopting an INT8 quantization: AlexNet, GoogleNet, ResNet-50, ShuffleNet, SqueezeNet, VGG-19. Moreover, interestingly, they show that PytorchFI runs at the native speed of silicon, as it requires no code instrumentation for error modeling. The emulations on both CPUs and GPUs show that all the inferences (with and without PyTorchFI) typically take less than 0.2 seconds.

Software methodologies are relevant for assessing the DNN resilience to errors and, in particular, for characterizing the criticality of the layers and the various DNN topologies. However, these analyses might not be complete to represent the real behaviour when deployed on a physical hardware device. It is evident that software-level simulations and theoretical analyses may lack the information of the underlying hardware platform and are relatively less accurate [40]. As outlined in the introduction, the choice of the hardware architecture hosting the DNN plays a key role in the final reliability of the system. Therefore, it might be needed to study the overall system resilience to faults *before* reaching the fabrication phase. Working at the software level allows the injection of errors only on neural networks parameters (such as synaptic weights, activations values) or on high-level programming logic representing the basic operations of DNN models. On the other hand, simulations at the hardware-level enable a wider spectrum of possibilities. The lower the abstraction level, the higher the degree of freedom. For these reasons, it is required to run the fault injections on a more accurate Hardware Description Level (HDL) model of the target hardware architecture running the DNN. HDL models give the opportunity to perform such studies comprehensively with accuracy and exactness close to the real hardware. However, it is also worth saying that the lower the abstraction level, the higher the simulation time.

A good compromise between a pure software approach and a pure hardware one is presented in [41], where a software technique meets the precision and accuracy of the hardware abstraction level. Fldelity [41] is a resilience analysis framework that

1.2 Related Works 17

has been developed to study the behaviour of hardware errors in DL accelerators. The framework is able to model a class of hardware errors (transient) in software with high fidelity, only leveraging on high-level design information obtained from architectural descriptions. Indeed, using just the information coming from design plans, block diagrams, architectural descriptions, and estimated values, FIdelity is able to generate accurate software fault models without the need to access the RTL description or the presence of a RTL description at all. Note that RTL is not likely to be available during the early phases of the design process. By defining a Reuse Factor Analysis, they are able to obtain the set of faulty output neurons, i.e., output neurons that are affected by a specific hardware fault. According to the hardware-level faults derived from the architectural analysis, random bit-flips are injected at specific input values, weights, output neurons of the DNN under assessment. To demonstrate that FIdelity software fault models are accurate, the authors use NVDLA [42], an open-source accelerator provided by NVIDIA. RTL injections are performed to compare the software fault models generated using the Reuse Factor Analysis with the information obtained from the RTL simulations. FIdelity is built on TensorFlow, and the DNN models used for its validation are: Inception, ResNet-50, and MobileNet which are trained on ImageNet and Cifar-10; Transformer trained on IWSLT14, a dataset containing about 160K sentence pairs, english-german and german-english; YOLO, trained on COCO dataset. Interestingly, this paper also analyses the effects of the quantization to 16- and 8-bit integers (INT16-INT8) as well as the half-precision floating-point (16-bit FP), thanks to the TensorFlow support for playing with reduced-precision data representations.

Driven by analogous motivation of [41], Li *et al.* [43] propose a framework for studying the propagation of transient faults (i.e., soft errors) in DNN-based systems. The study addressed the reliability of DNN accelerators, in particular a recently proposed one, Eyeriss [44]. Due to the lack of the RTL implementation, they modified an open-source DNN simulator framework, Tiny-CNN, to map each line of code in the simulator to the corresponding hardware component of the DNN accelerators under assessment. In this way, they are able to randomly inject faults into the data-path of accelerators and into the buffers of the Eyeriss DNN accelerator. The error propagation behaviours are classified according to the structure of the neural networks, the data types, the position of layers, and the types of layers. Four DNNs are investigated: AlexNet, CaffeNet, NiN, and ConvNet.

Salami et al. in [40] present a simulation-based hardware-level FI framework for performing an in-depth vulnerability analysis of a hardware accelerator described at the RTL. The assessment is performed by considering both the applicationlevel specifications (the DNN weights, inputs, and the intermediate values) and the architectural-level ones (the specific data representation and the amount of computational resources, i.e., the PEs). In this paper, they propose an HLS approach to characterize the effects of both permanent and transient faults. Faults are injected during the inference cycles on a sub-set of registers: those that are in charge to store the neural network parameters, i.e., the weights, input values, and intermediate ones. To assess the sensitivity of the neural network layers, permanent and transient faults are also placed in the layer registers (individually). Also, the activation values are studied, particularly in two state-of-the-art activation functions: positive saturating linear and logarithmic sigmoid. So far, a similarity could be found with the injections made at the software level. However, having the HDL model running the DNN under assessment, Salami et al. performed also architectural-level analyses. First, they played with the architecture of the accelerator to study how the amount of processing elements can impact the fault propagation behaviour. FIs are performed for different numbers of PEs, i.e., 64, 256, 1024, revealing a direct proportionality between the number of PEs and the reliability of the accelerator against permanent and transient faults. Second, they studied the sensitivity of sign, digit, and fraction sections of the FxP data representation.

Next, some reliability assessment methodologies are performed by running FIs directly on an **emulation platform**. In [45], the authors present Ares, a framework for quantifying the resilience of DNNs. It enables the DNNs execution directly on the GPUs and targets permanent faults occurring in the memory, which is the unit hosting the weights. At the application level, errors are injected in the weights, the activations and the hidden states through bit-flips. Particularly, they are injected at construction time (static) and evaluation time (dynamic). The former are injected off-line, before the inference is executed. The latter are injected during the inference phase, introducing a minimum performance overhead. Ares is built on the top of Keras [46], which takes high-level DNN descriptions specified in Python and executes them using either Theano [47] or TensorFlow back ends.

Concerning the emulation on FPGAs, several tools for the reliability assessment of DNNs have been introduced. De Sio *et al.* proposed FireNN [48]: an emulation platform for evaluating the reliability of DNNs. The methodology exploits the

1.2 Related Works 19

reconfigurability of FPGAs to mimic faults affecting the hardware running DNNs (e.g., stuck-at faults, delays, conflicting connections, and others). Particularly, the framework emulates the effects of single event upsets with random bit-flip injections in the configuration memory of the programmable logic of Zynq All Programmable SoC, running specific layers of the targeted DNN. The FI framework combines software and hardware levels through the extension of PyTorch and PyNQ[49] frameworks and exploits Vivado HLS to develop a custom IP core for performing convolutional operations. In the paper, the evaluation is performed on the fifth convolutional layer of the AlexNet network.

The **radiation-based** FI category relies on the exposure of the system to an accelerated radiation source, e.g., atmospheric-like neutrons. Being radiation a source of perturbations in electronics devices, in the literature, several radiationbased approaches have been proposed. For example, in [50], the authors evaluated the impact of neutron-induced SEUs on a CNN (LeNet-5) implemented with three different levels of approximation on the data representation. In this study, the target hardware is the memory device that hosts the network parameters and input images. A similar approach is presented in [51], where a 2- and 3-D Flash memory storing the weights of an ANN is exposed to X-ray irradiation. Also, in [52], three different NVIDIA GPU architectures are exposed to a neutron beam targeting the study of error propagation in computing resources. Finally, targeting an FPGA-based architecture, Libano et al. in [53] analyse the SEUs influence on three versions of a MNIST CNN implemented in an SRAM-based FPGA. Most of the works that assess the reliability of ANN applications via radiation-based approaches use atmospheric-like neutrons as a radiation source. However, as mentioned above, for a specific environment, specific radiation sources like protons, heavy-ions, electrons, among others, should be considered.

## 1.2.2 Advantages and Disadvantages of Fault Injection Methodologies

We introduce three different metrics for presenting the trade-offs between the state-of-the-art fault injection approaches:

• **Costs:** It refers to the costs needed to carry out the reliability assessment, including both resources and time.

Figure 1.4 Comparing different Fault Injection Techniques. The x-axis reports the specific level: 1-Low, 2-Medium-Low, 3-Medium, 4-High-Medium, 5-High, 6-Very High.

- Precision: It means how much the FI procedure is close to reality, and the

obtained results are accurate and realistic.

- **Fault Injection Time:** The amount of time that the injection process takes to complete a single injection cycle.

In Figure 1.4, we assign a specific level to these metrics and grade them as *Low* (1), *Medium-Low* (2), *Medium* (3), *High-Medium* (4), *High* (5), and *Very High* (6). As for the costs, because simulation-based approaches do not need the development and purchase of specific electronic devices to conduct the assessments, they are the most cost-effective. Moreover, when the HDL model is available, the costs are low and, anyhow, reduced compared to other FI techniques. When working with platform-based techniques, economic costs increase since they rely on the purchase and usage of specific validation or emulation devices (e.g., GPUs, CPUs, and FPGAs). A further benefit is also due to the fact that (i) they can be utilized again once the FI campaigns are completed, and (ii) they can be parallelized to increase the performance. The radiation-based procedures are the most expensive ones for three principal reasons: access to an irradiation facility, hardware setup development, and the low possibility of reusing the irradiated devices.

The precision with which the four FI procedures provide findings varies and is dependent on how well these approaches simulate the incidence of realistic system 1.2 Related Works 21

faults and how near they are to real. Radiation-based FI techniques achieve the maximum level of precision, as radiation-induced faults directly impact the silicon implementation of the device under test. This enables the DNN model to be accurately characterized. On the other hand, simulation-based hardware-level FIs have a good level of precision. Due to the adoption of the HDL model (either RTL or gate-level), their injection procedure can be considered close to the actual silicon implementation. For this reason, they are credited with a medium-high precision level. Contrarily, platform-based and simulation-based software-level FIs both have a low-medium precision level for the following reasons. The incidence of realistic hardware faults is mimicked using sophisticated software fault models, where errors are injected at the software or algorithmic level. Specifically, when a DNN model is written in C or C++, it can be compiled and executed directly on a physical hardware device; hence, the injected software errors can be close to the faults they attempt to reproduce. In higher-level programming languages or tools, such as Python, PyTorch, and TensorFlow, FI frameworks introducing errors at the algorithmic level are exposed to a more elaborate compilation chain. Consequently, the lower the programming language level adopted for the DNN application, the higher the precision. One of the advantages of conducting simulation-based reliability assessments at the software level is the possibility of characterizing the vulnerability of neural networks independently of the target hardware device and, in particular, driving analyses on layers, data types, weights, and network's parameters.

However, when a more thorough reliability evaluation is necessary, the injection campaigns should additionally encompass the target hardware that will ultimately execute the DNN under test, clearly when the device's HDL model, whether RTL or gate-level, is provided. In this second scenario (such as in [30, 40]), hardware-level FIs can achieve better accuracy of the results, closer to the silicon implementation.

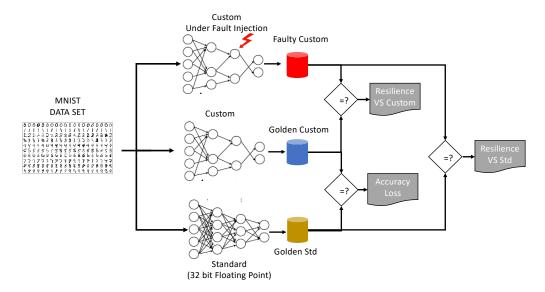

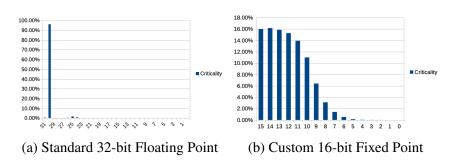

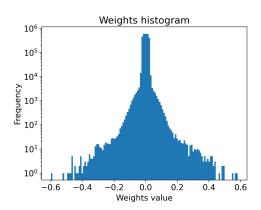

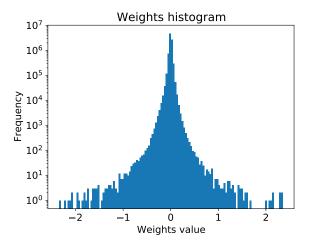

In a recent paper [54], we propose using realistic fault models (retrieved from radiation test campaigns) to inject at the software level in a CNN application, with the aim of enhancing the precision level of simulation-based FIs at the software level. The methodology is presented in Chapter 5.