# POLITECNICO DI TORINO Repository ISTITUZIONALE

Analysis and Design of a High Power Density Full-Ceramic 900 V DC-Link Capacitor for a 550 kVA Electric Vehicle Drive Inverter

#### Original

Analysis and Design of a High Power Density Full-Ceramic 900 V DC-Link Capacitor for a 550 kVA Electric Vehicle Drive Inverter / Cittanti, Davide; Stella, Fausto; Vico, Enrico; Liu, Chaohui; Shen, Jinliang; Xiu, Guidong; Bojoi, Radu. - ELETTRONICO. - (2022), pp. 1144-1151. (Intervento presentato al convegno 2022 International Power Electronics Conference (IPEC-Himeji 2022- ECCE Asia) tenutosi a Himeji, Japan nel 15-19 May 2022) [10.23919/IPEC-Himeji2022-ECCE53331.2022.9807220].

Availability:

This version is available at: 11583/2969288 since: 2022-07-28T07:27:28Z

Publisher:

**IEEE**

Published

DOI:10.23919/IPEC-Himeji2022-ECCE53331.2022.9807220

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

## Analysis and Design of a High Power Density Full-Ceramic 900 V DC-Link Capacitor for a 550 kVA Electric Vehicle Drive Inverter

Davide Cittanti\*, Fausto Stella\*, Enrico Vico\*, Chaohui Liu<sup>†</sup>, Jinliang Shen<sup>†</sup>, Guidong Xiu<sup>†</sup> and Radu Bojoi\*

\*Dipartimento Energia "G. Ferraris", Politecnico di Torino, Italy

†National New Energy Vehicle Technology Innovation Center, China

\*Corresponding Author: Davide Cittanti (davide.cittanti@polito.it)

Abstract—The drive inverter is a crucial component of an electric vehicle (EV) powertrain, being responsible for the DC/AC power conversion between the battery and the electric motor. The increasing demand for lower weight and higher conversion efficiency is opening new challenges, encouraging the adoption of new technologies (e.g., wide bandgap semiconductor devices). In particular, the DC-link capacitor typically represents the bulkiest inverter component and poses a strict limitation to the achievable converter power density, therefore it is subject to strong pressure for improvement. In this context, novel ceramic capacitor technologies promise superior performance with respect to well established film-based solutions, featuring both higher specific capacitance and higher RMS current capability. Therefore, this paper focuses on the analysis, sizing and design of a full-ceramic 900 V DClink capacitor for next-generation EV drive inverters, including a comparative assessment with a state-of-the-art film-based solution. For verification purposes, a DC-link prototype for a SiC MOSFET 550 kVA 25 kHz drive inverter is realized, demonstrating superior power density (i.e.,  $\approx$  6.6 times smaller and  $\approx$  3.6 times lighter than a corresponding film-based solution). Furthermore, electrical and thermal measurements are performed on a ceramic capacitor sample, successfully supporting the DC-link sizing and design.

Index Terms—two-level inverter; DC-link capacitor; ceramic capacitors; film capacitors; traction drive; electric vehicles (EVs)

#### I. INTRODUCTION

During the last decade, as a result of both government policies and consumer demand, electric vehicles (EVs) have rapidly become more and more attractive with respect to traditional internal combustion engine (ICE) vehicles. At present, the automotive industry is increasingly pushing for lighter and more efficient EV powertrains, leading to considerable technological challenges [1].

An EV drive train normally consists of a battery system, a drive inverter and an electric motor, as shown in Fig. 1. Being responsible for the full DC/AC power conversion between the battery and the electrical machine, the drive inverter is a crucial component

Fig. 1. Schematic overview of an electric vehicle (EV) drive train, including the battery, the DC-link capacitor, the drive inverter and the electric motor.

and is thus subject to great pressure for improvement [1]–[3]. The main requirements of an automotive-grade inverter can be summarized in high power density (both volumetric and gravimetric), high conversion efficiency over a wide load range [4], high voltage operation (due to the ongoing shift to 800 V battery architectures [5]), high temperature capability, and high switching frequency (to provide sufficient control margin and reduce PWM-induced losses in high-speed, low-inductance machines with several pole pairs typically adopted in automotive [4], [6]–[8]).

While all mentioned requirements are currently being tackled with the adoption of modern wide bandgap (WBG) semiconductor devices, such as silicon carbide (SiC) MOSFETs and gallium nitride (GaN) HEMTs [9]–[11], and the adoption of multi-level inverter topologies [5], [11], [12], an upper limitation to the drive inverter power density is enforced by the DC-link capacitor. In fact, the sizing of state-of-the-art film-based DC-link capacitors is mostly unaffected by the higher switching frequencies enabled by WBG devices, as the limiting design criterion is typically the RMS current stress (i.e., unaffected by the switching frequency). Moreover, multi-level inverter topologies leave unaltered both DC-link RMS current and voltage ripple with respect to traditional two-level inverters [12], therefore being unable to reduce the DC-link capacitor size.

In this context, high-voltage ceramic capacitor technology (e.g., CeraLink® from TDK [13]) promises superior performance with respect to film-based solutions, featuring higher specific capacitance, higher RMS current capability, higher maximum temperature operation, lower equivalent series inductance (due to the smaller package), and decreasing resistance with frequency (i.e., effectively benefiting from higher frequency operation). Although highly disregarded until recently [14], ceramic technology represents a key enabler for next-generation EV drive inverters, theoretically allowing for a significant performance leap in terms of gravimetric and volumetric power density.

While several works describing the sizing and design of three-phase inverter DC-link capacitors have already been reported in literature [15]–[17], only few papers focus on ceramic-based solutions [18] and, to the best of the authors' knowledge, none of them highlights the performance benefits unlocked by ceramic technology. In particular, even though [14] provides a comparative performance assessment of different capacitor technologies suitable for EVs, the analysis is not validated with a DC-link capacitor design.

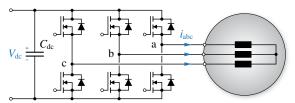

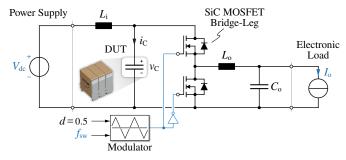

Fig. 2. Schematic overview of the considered two-level drive inverter system.

Therefore, the main goal of this paper is to analyze, size and design a 900 V full-ceramic DC-link capacitor for a two-level EV drive inverter (cf. Fig. 2), meanwhile providing a comparison with a traditional state-of-the-art film-based solution. In particular, the main contributions of this work can be summarized in (1) a quantitative performance evaluation of automotive-grade film and ceramic capacitor technologies, (2) a straightforward extension of the traditional sizing procedure of a two-level inverter DC-link capacitor, taking into account the frequency-dependent RMS current capability of ceramic capacitors, (3) the conceptualization and realization of a high power density full-ceramic 900 V DC-link capacitor, and (4) the experimental assessment of the electrical and thermal performance of a ceramic capacitor sample under large-signal excitation.

This paper is structured as follows. In Section II the most suitable DC-link capacitor technologies for automotive application are described and a quantitative performance comparison among them is carried out. In Section III the stresses and the sizing criteria for a two-level inverter DC-link capacitor are briefly recalled, and the adopted DC-link design procedure is outlined. In Section IV a DC-link capacitor prototype for a SiC MOSFET 550 kVA 25 kHz EV drive inverter is designed and realized for verification purposes. Furthermore, electrical and thermal measurement results are provided in Section V, where a ceramic capacitor sample is tested under large-signal excitation. Finally, Section VI summarizes and concludes this work.

#### II. AUTOMOTIVE DC-LINK CAPACITOR TECHNOLOGIES

Automotive DC-link capacitors require high RMS current capability (i.e., low equivalent series resistance and high thermal conductivity), high specific capacitance, high maximum temperature operation, high self-resonance frequency (i.e., low equivalent series inductance), and high reliability (i.e., long mean time between failures). While electrolytic capacitors excel in terms of specific capacitance (i.e., energy density), they do not achieve acceptable performance in terms of the remaining criteria [19], therefore they are typically not adopted in high-voltage automotive drive inverters.

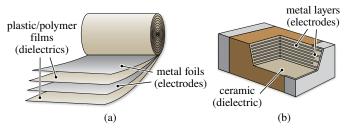

Fig. 3. Overview of the typical internal structure of (a) film capacitors and (b) multi-layer ceramic capacitors (MLCCs).

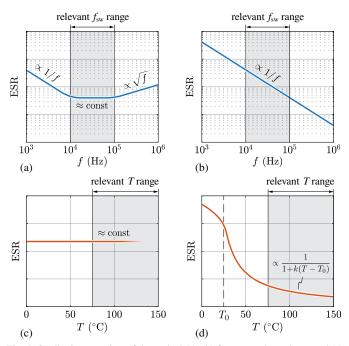

Fig. 4. Qualitative overview of the typical (a)–(b) frequency dependence and (c)–(d) temperature dependence of the equivalent series resistance (ESR) for (a),(c) film capacitors and (b),(d) PLZT ceramic capacitors. The relevant switching frequency and operating temperature ranges for automotive inverter DC-link applications (i.e.,  $10-100\,\mathrm{kHz}$ ,  $75-150\,^\circ\mathrm{C}$ ) are highlighted.

This section discusses the main features of film and ceramic capacitors for automotive DC-link application, providing a quantitative performance benchmark for both technologies.

#### A. Film Capacitors

Film capacitors are typically realized by interleaving plastic/polymer films (dielectrics) with metal foils (electrodes) [20], as illustrated in Fig. 3(a). The employed dielectric materials are non-polar and have low relative permittivity ( $\varepsilon_{\rm r} \approx 2-3$ ), leading to lower capacitance density with respect to electrolytic capacitors. Nevertheless, they show little temperature dependence and are thus suited for high temperature operation, typically up to 100–125 °C. Additionally, the self-healing properties of film capacitors substantially improve their reliability, making them a desirable choice in automotive applications. On the negative side, the equivalent series resistance (ESR) of film capacitors tends to be approximately constant with frequency in the 10-100 kHz range (cf. Fig 4(a)), after which the ESR starts increasing  $\propto \sqrt{f}$  due to AC skin effect (i.e., depending on the thickness of metal foils and contacts) [20]. Therefore, the power losses and the RMS current capability of film-based DC-link capacitors are typically either unaltered or negatively affected by an inverter switching frequency increase. Further drawbacks of film capacitors in traction drive applications can be identified in their relatively high equivalent series inductance (i.e., due to the large physical size of high-power DC-link capacitors), which leads to low self-resonance frequencies and thus limits the frequency operating range of the capacitor itself, and their limited allowed self-heating temperature rise (i.e.,  $\approx 10-20$  °C) [20], which hinders their RMS current capability and potentially requires an active thermal management.

#### B. Ceramic Capacitors

The typical structure of a ceramic capacitor is illustrated in Fig. 3(b), where ceramic dielectric layers with large relative permittivity (i.e.,  $\varepsilon_{\rm r}$  up to 10 000) are alternated with metal electrodes. Due to their structure, these capacitors are also known as multilayer ceramic capacitors (MLCCs), and can be classified into three main categories: class I, class II, and lead-lanthanum-zirconate-titanate (PLZT) capacitors [1]. In general, all ceramic capacitors feature higher specific RMS current capability than film capacitors and can operate at higher temperatures (i.e., up to 150 °C) [14]. Moreover, due to their inherent small size (i.e., the brittleness of the dielectric material limits the package dimensions) ceramic capacitors are characterized by low equivalent series inductance and are thus more suited for high-frequency applications. On the other hand, the upper limitation to the capacitor size requires the paralleling of tens/hundreds of units to achieve the required DClink capacitance in traction inverter applications, posing substantial design and realization challenges to ensure symmetrical current sharing and to minimize the overall stray inductance.

Class I ceramic capacitors (e.g., C0G) employ a linear dielectric material with relatively low permittivity (i.e.,  $\varepsilon_{\rm r}\approx 20$ –40) and feature low temperature and DC voltage bias dependencies, trading excellent capacitance stability for a low capacitance/energy density. These characteristics make class I capacitors most suited for power electronics applications where constant capacitance is required, such as filters and/or resonant converters.

On the contrary, class II ceramic capacitors (e.g., X7R, X6R) can achieve much higher capacitance densities (i.e., suitable for DC-link applications), however they are characterized by a significant capacitance drop with increasing DC voltage bias and operating temperature, due to the employed non-linear ferroelectric dielectric materials. Furthermore, mainly due to the rigidity of the ceramic dielectric material, these capacitors can easily crack when they are subject to sufficient mechanical and thermal stresses, leading to possible short circuits between terminals. This aspect significantly affects the overall reliability of these components in harsh and vibrating environments, such as automotive applications, therefore they are not well suited for EV traction drive DC-links.

PLZT capacitors (e.g., CeraLink® from TDK [13]) represent emerging and promising candidates for automotive DC-link applications, since they employ an antiferroelectric dielectric material characterized by a permittivity increase with the DC voltage bias. In particular, this feature allows to store a higher amount of energy in nominal operating conditions (i.e., at rated voltage) with respect to class II capacitors. Moreover, the PLZT dielectric withstands and favours high temperature operation (i.e., up to 150 °C, with ESR decreasing approximately linearly with temperature, cf. Fig. 4(d)) and the copper electrodes provide enhanced electrical and thermal dissipation performance, enabling an unparalleled specific RMS current capability. Additionally, the ESR of PLZT capacitors approximately decreases  $\propto 1/f$ , as shown in Fig. 4(b), allowing for a further RMS current capability increase with increasing inverter switching frequency (i.e.,  $I_{\rm RMS} \propto \sqrt{f_{\rm sw}}$ ), as opposed to film capacitors. Concerning reliability, the internal structure of PLZT capacitors consists in the equivalent series connection of two MLCCs [13] and enables the capacitor operation in case of a

first crack (i.e., short circuit) in the dielectric, thus achieving higher reliability levels than other ceramic capacitor technologies. It is also worth noting that, even though the ESR of PLZT capacitors decreases with temperature (cf. Fig. 4(d)), above 75 °C the capacitance value shows a negative temperature coefficient, allowing for the natural balancing of the current among paralleled capacitors and thus avoiding thermal runaway [14]. All together, these features clearly indicate that PLZT capacitors represent the most suited ceramic-based candidates for EV traction drive DC-links. Therefore, CeraLink® technology from TDK will be considered as ceramic capacitor benchmark in the following sections.

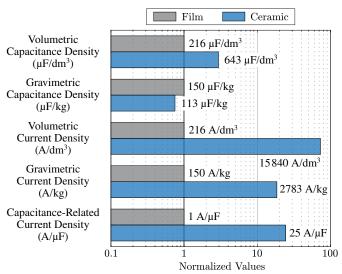

#### C. Performance Comparison

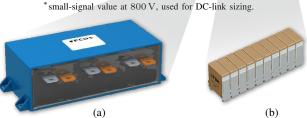

In order to provide a quantitative comparative analysis between automotive film and ceramic DC-link capacitors, two commercially available high-performance 900 V solutions are considered as technology benchmarks, as reported in Table I and Fig. 5. Due to the very different parameter absolute values of the two capacitor models, the capacitance and RMS current values are expressed in relative terms to provide useful specific performance indicators, which are illustrated in Fig. 6. Remarkably, the small-signal capacitance value is considered for the PLZT ceramic capacitor, as it represents a worst-case (i.e., minimum) capacitance value for DC-link applications, where a relatively small voltage ripple is superimposed to a comparatively large DC bias voltage [13].

It is observed that the PLZT ceramic solution strongly outperforms the film one according to all specific performance indicators except for the gravimetric capacitance density, which results comparable. In particular, the ceramic solution excels in terms of RMS current carrying capability, which typically represents the limiting design criterion for film-based automotive DC-link capacitors. Therefore, it is evident that PLZT ceramic technology has the potential to significantly enhance the performance of automotive inverter DC-links.

TABLE I. Specifications of the considered benchmark capacitors.

|                     | Film                    | Ceramic                 |

|---------------------|-------------------------|-------------------------|

| Manufacturer        | EPCOS (TDK)             | TDK                     |

| Part Number         | B25655P9127K151         | CeraLink® FA10          |

| Rated Voltage       | $900\mathrm{V}$         | $900\mathrm{V}$         |

| Rated Capacitance   | $120\mu\mathrm{F}$      | $1.3\mu\mathrm{F}^*$    |

| Rated RMS Current   | $120\mathrm{A}$         | $32\mathrm{A}$          |

| Maximum Temperature | $105^{\circ}\mathrm{C}$ | $150^{\circ}\mathrm{C}$ |

| Volume              | $554.4\mathrm{cm}^3$    | $2.0\mathrm{cm}^3$      |

| Weight              | 800 g                   | 11.5 g                  |

Fig. 5. Highlight of the considered  $900\,V$  benchmark capacitors (not to scale): (a) EPCOS B25655P9127K151 [21], (b) TDK CeraLink® FA10 [22].

Fig. 6. Specific performance comparison between the selected benchmark film and PLZT ceramic capacitors. The specific performance indicators are normalized with respect to the film capacitor value and are shown in logarithmic scale.

#### III. DC-LINK CAPACITOR SIZING

The DC-link capacitor of a three-phase two-level inverter must simultaneously satisfy two main design criteria [16]: it must comply with the maximum RMS current stress dictated by the application, which generates losses and affects the capacitor temperature rise, and it must ensure a predefined maximum peak-to-peak voltage ripple, which increases the peak voltage applied to the semiconductor devices and alters the ideal operation of the converter (i.e., the AC-side applied voltages).

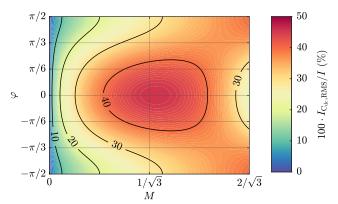

Disregarding the AC-side switching frequency current ripple, the RMS current flowing into the DC-link capacitor can be expressed analytically as [23]

$$I_{\text{C}_{\text{dc}},\text{RMS}} = I \sqrt{M \left[ \frac{\sqrt{3}}{4\pi} + \cos^2 \varphi \left( \frac{\sqrt{3}}{\pi} - \frac{9}{16} M \right) \right]},$$

(1)

where I is the peak phase current value,  $M=2V/V_{\rm dc}$  is the inverter modulation index (i.e.,  $0 \leq M \leq 2/\sqrt{3}$  in linearity),  $\varphi$  is the load power factor angle, V is the reference peak phase voltage value and  $V_{\rm dc}$  is the DC-link voltage. Remarkably, (1) is not affected by the inverter pulse-width modulation (PWM) strategy [23].  $I_{\rm C_{dc},RMS}$  is illustrated in normalized form (i.e., divided by the peak phase

Fig. 7. Normalized DC-link capacitor RMS current  $I_{\mathrm{C_{dc},RMS}}$  as function of the inverter modulation index M and the load power factor angle  $\varphi$ . The normalization factor is the peak phase current I.

current I) in Fig. 7 as function of M and  $\varphi$ . The worst-case value of (1) is found for  $\varphi=0$  and  $M={}^{10\sqrt{3}}/{}9\pi$ , obtaining:

$$I_{\rm C_{dc},RMS,max} = \frac{5}{2\sqrt{3}\pi} I \approx 0.46 I.$$

(2)

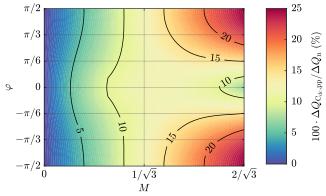

The DC-link capacitor peak-to-peak charge ripple  $\Delta Q_{\rm C_{dc},pp}$  (i.e., the high-frequency current-time area) is directly proportional to the voltage ripple  $\Delta V_{\rm dc,pp}$  and provides a straightforward relation to size the DC-link capacitance value  $C_{\rm dc}$  through its definition:

$$\Delta Q_{\rm C_{dc},pp} = C_{\rm dc} \, \Delta V_{\rm dc,pp}. \tag{3}$$

Unfortunately, a general analytical expression of  $\Delta Q_{\rm C_{dc},pp}$  valid for all operating conditions cannot be derived, as the maximum peak-to-peak value of the charge ripple within a fundamental period depends on  $M, \varphi$  and the selected modulation strategy, changing expression abruptly [24]. Therefore,  $\Delta Q_{\rm C_{dc},pp}$  is calculated numerically considering space vector modulation (SVPWM) [25] and is illustrated in Fig. 8, where it is normalized with respect to  $\Delta Q_{\rm n} = I/f_{\rm sw}$ . The worst-case value of  $\Delta Q_{\rm C_{dc},pp}$  is found for  $M=2/\sqrt{3}$  and  $\varphi=\pm\pi/2$ , obtaining [24]

$$\Delta Q_{\rm C_{dc},pp,max} = \frac{1}{4} \frac{I}{f_{\rm sw}}.$$

(4)

The DC-link capacitance  $C_{\rm dc}$  required by the application is obtained as the value that satisfies both the RMS current and peak-to-peak voltage ripple constraints, as:

$$C_{\rm dc} = \max \left[ C_{\rm dc, I_{RMS}}, C_{\rm dc, \Delta V_{pp}} \right].$$

(5)

The expression of  $C_{

m dc,\Delta V_{pp}}$  can be directly derived from (3) and (4) assuming a specified value of  $\Delta V_{

m dc,pp,max}$ , as

$$C_{\rm dc,\Delta V_{\rm pp}} = \frac{\Delta Q_{\rm C_{\rm dc},pp,max}}{\Delta V_{\rm dc,pp,max}} = \frac{1}{4} \frac{I}{f_{\rm sw} \, \Delta V_{\rm dc,pp,max}}, \quad (6)$$

whereas the expression of  $C_{

m dc,I_{RMS}}$  requires additional definitions and specific assumptions, which are provided in Appendix A. Therefore, considering the maximum RMS current stress  $I_{

m C_{dc},RMS,max}$  and assuming as a worst-case (i.e., conservative) scenario that the total RMS current stress takes place at  $f=f_{

m sw}$ , the expression of  $C_{

m dc,I_{RMS}}$  is obtained by manipulating (14):

$$C_{\rm dc,I_{RMS}} = C^* \frac{I_{\rm C_{dc},RMS,max}}{I_{\rm RMS}^*} \left(\frac{f^*}{f_{\rm sw}}\right)^{\alpha/2} \sqrt{\frac{T_{\rm max} - T_{\rm a}^*}{T_{\rm max} - T_{\rm a}^*}},$$

(7)

Fig. 8. Normalized DC-link capacitor peak-to-peak charge ripple  $\Delta Q_{\mathrm{C_{dc},pp}}$  as function of the inverter modulation index M and the load power factor angle  $\varphi$  assuming SVPWM. The normalization factor is  $\Delta Q_{\mathrm{n}} = I/f_{\mathrm{sw}}$ .

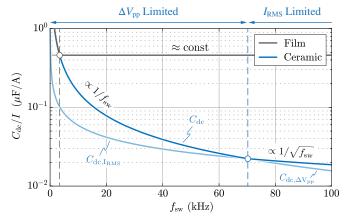

Fig. 9. DC-link capacitance  $C_{\rm dc}$  requirement normalized with respect to the peak phase current I as function of the inverter switching frequency  $f_{\rm sw}$  and the capacitor technology (i.e., film and PLZT ceramic, cf. Fig. 5), assuming  $V_{\rm dc}=800\,{\rm V}$ ,  $\Delta V_{\rm dc,pp,max}=20\,\%\,V_{\rm dc}$  and  $T_{\rm a}=85\,^{\circ}{\rm C}$ . The two regions where the DC-link capacitor sizing is respectively dominated by  $C_{\rm dc,\Delta V_{pp}}$  ( $\Delta V_{\rm pp}$  limited) and by  $C_{\rm dc,I_{RMS}}$  ( $I_{\rm RMS}$  limited) are highlighted for the ceramic technology.

where  $C^*$ ,  $I^*_{\rm RMS}$ ,  $f^*$  and  $T^*_{\rm a}$  are respectively the capacitance, the RMS current capability, the test frequency and the ambient temperature values provided in the manufacturer's datasheet,  $T_{\rm max}$  is the maximum capacitor operating temperature (i.e.,  $T=T^*=T_{\rm max}$ ),  $T_{\rm a}$  is the considered ambient temperature, and  $\alpha\approx 0$  for film capacitors (i.e., ESR approximately independent of  $f_{\rm sw}$  in the considered frequency range, cf. Fig. 4), whereas  $\alpha\approx 1$  for CeraLink® capacitors (cf. Fig. 4).

The normalized DC-link capacitance requirement for the considered film and PLZT ceramic technologies is shown in Fig. 9 (i.e., divided by the peak phase current I) as function of the inverter switching frequency  $f_{\rm sw}$ , assuming  $V_{\rm dc} = 800\,{\rm V}$ ,  $\Delta V_{\rm dc,pp,max} = 20 \% V_{\rm dc}$  and  $T_{\rm a} = 85 \, ^{\circ}{\rm C}$ . It is observed that, depending on the value of  $f_{sw}$ , the main factor limiting the DC-link sizing is either the voltage ripple requirement (at low frequency) or the RMS current stress (at high frequency). Moreover, while for film capacitors the RMS current criterion tends to dominate the sizing for  $f_{\rm sw} > 4 \, \rm kHz$ , CeraLink<sup>®</sup> technology allows for a large capacitance reduction if higher switching frequency values can be exploited. It is also worth highlighting that for both technologies, once the RMS current limit is reached, the DC-link capacitance decreasing trend either stops (in the film case) or slows down substantially (in the ceramic case). In particular, due to the reduction of ESR  $\propto 1/f$  in CeraLink® capacitors, a non negligible DC-link reduction can still be obtained for higher switching frequencies.

#### IV. DESIGN CASE STUDY: 550 KVA INVERTER

In this section, the capacitor sizing approach described in Section III is applied to a specific case study and a full-ceramic DC-link prototype is designed and realized. The target specifications and nominal operating conditions of the considered three-phase two-level drive inverter are reported in Table II.

TABLE II. INVERTER SPECIFICATIONS AND NOMINAL OPERATING CONDITIONS.

| Parameter   | Description         | Value            |

|-------------|---------------------|------------------|

| S           | Apparent Power      | 550 kVA          |

| I           | Peak Phase Current  | $795\mathrm{A}$  |

| $V_{ m dc}$ | DC-Link Voltage     | $800\mathrm{V}$  |

| $f_{ m sw}$ | Switching Frequency | $25\mathrm{kHz}$ |

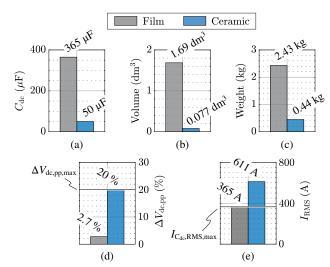

Fig. 10. Film vs. ceramic DC-link capacitor sizing according to the procedure outlined in Section III, assuming  $\Delta V_{\rm dc,pp,max} = 20\,\%\,V_{\rm dc},\,T_{\rm a} = 85\,^{\circ}{\rm C}$  and the inverter specifications reported in Table II. (a) DC-link capacitance  $C_{\rm dc},$  (b) volume, (c) weight, (d) normalized peak-to-peak voltage ripple  $\Delta V_{\rm dc,pp},$  (e) RMS current capability  $I_{\rm RMS}$ . The film capacitor size is determined by the RMS current stress ( $I_{\rm RMS}$  limited), whereas the ceramic capacitor size is dictated by the required peak-to-peak voltage ripple ( $\Delta V_{\rm DD}$  limited).

#### A. DC-Link Sizing

A film-based and a PLZT ceramic-based DC-link solutions are sized according to the procedure outlined in Section III, considering the inverter specifications reported in Table II and assuming a target maximum peak-to-peak voltage ripple  $\Delta V_{\rm dc,pp,max} = 20\,\%\,V_{\rm dc} = 160\,\mathrm{V}$  and an ambient temperature  $T_{\rm a} = 85\,^{\circ}\mathrm{C}$ . Leveraging expressions (5), (6) and (7), the results in terms of capacitance, volume, weight, peak-to-peak voltage ripple and RMS current capability are reported in Fig. 10.

It is observed that the CeraLink® solution achieves superior theoretical performance with respect to the film-based solution, in terms of both DC-link volume and weight. Remarkably, the large reduction in weight and volume is to be mainly attributed to the high specific RMS current capability of PLZT ceramic technology, and not to its high volumetric/gravimetric capacitance density. In fact, since the RMS current limit is not encountered up to very high  $f_{\rm sw}$  values (cf. Fig. 9), the inverter switching frequency increase allows to significantly reduce the total capacitance requirement. This is not the case for the film-based solution, which encounters the RMS current limit at relatively low frequency (i.e.,  $\approx 4\,\mathrm{kHz}$ , cf. Fig. 9).

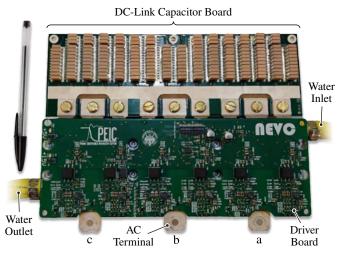

#### B. DC-Link Realization

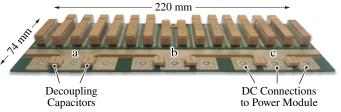

A custom designed full-ceramic DC-link prototype is realized and is shown in Fig. 11. It consists of a double-side  $800\,\mu\mathrm{m}$  thick copper PCB, housing several  $900\,\mathrm{V}$  CeraLink® capacitors in different formats to reach the total required capacitance of

Fig. 11. Bottom view of the realized 900 V full-ceramic DC-link board.

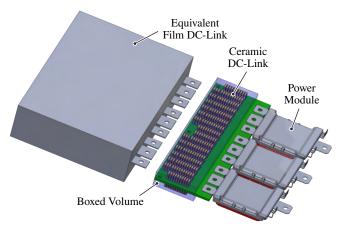

Fig. 12. 3D overview of the proposed 900 V full-ceramic DC-link capacitor and comparison with the equivalent film-based solution.

50 μF (i.e., small-signal value), namely 32 FA10 [22] (1.3 μF each) and 24 FA3 [22] (0.39 µF each). Additionally, 6 LP [26] capacitors (0.13 µF each) are placed between the DC terminals of the power modules, allowing to minimize the commutation loop inductance and thus the SiC MOSFET switching voltage overshoot. Remarkably, the capacitors are mounted on both PCB sides to optimize the available PCB footprint. The total weight of the DC-link board is 0.676 kg, including the CeraLink® capacitors and the thick PCB copper traces, while its total boxed volume is  $0.254\,\mathrm{dm^3}$ . It can be noticed that these weight and volume values are well above the ones achievable theoretically (cf. Fig. 10), respectively by  $\approx 1.5$  times and  $\approx 3.3$  times. While the weight increment is directly associated with the addition of the thick-copper PCB (i.e., not considered in the analysis), the volume increment can be mostly attributed to the clearance requirements (i.e., the physical distance between devices): the latter in particular could be significantly reduced with proper manufacturing techniques.

Nevertheless, despite the inefficient space usage, the realized solution is  $\approx 6.6$  times smaller and  $\approx 3.6$  times lighter than its film-based counterpart (i.e.,  $1.69\,\mathrm{dm^3}$ ,  $2.43\,\mathrm{kg}$ ). A visual comparison between the two solutions is provided in Fig. 12.

A picture of the complete three-phase drive inverter prototype is shown in Fig. 13. This system employs three separate half-

Fig. 13. Top view of the realized 550 kVA drive inverter system.

bridge 1200 V SiC MOSFET automotive power modules from Danfoss (i.e., DP660B1200T105606). It is worth mentioning that the realized inverter prototype has been designed to be tested on an electric vehicle, therefore it includes other components (e.g., EMI filter, control board, enclosing aluminum case) that are out of the scope of this paper and are thus not shown.

#### V. EXPERIMENTAL RESULTS

To assess the validity of the DC-link capacitor sizing/design reported in Section III and Section IV, electrical and thermal measurements are performed on a 900 V CeraLink® FA3 capacitor sample (i.e., 900 V, 0.39  $\mu F$ ) [22], for reasons of testing simplicity. Fig. 14 shows the schematic of the adopted experimental setup. The device under test (DUT) is used as the DC-link of a SiC MOSFET synchronous buck converter operated at constant duty cycle (i.e., d=0.5) and is completely decoupled from the DC power supply by means of a large inductance, such that the AC component of the current switched by the buck converter entirely flows through the DUT. Therefore, the capacitor is subject to a symmetric square wave current with amplitude  $I_{\rm o}/2$  and frequency  $f_{\rm sw}$ , leading to the following stress expressions:

$$I_{\rm RMS} = \frac{I_{\rm o}}{2}, \ \Delta Q_{\rm pp} = \frac{1}{4} \frac{I_{\rm o}}{f_{\rm sw}}.$$

(8)

Remarkably, all three degrees of freedom of the realized experimental setup (i.e., the DC voltage bias  $V_{\rm dc}$ , the output load current  $I_{\rm o}$  and the switching frequency  $f_{\rm sw}$ , cf. Fig. 14) are exploited to perform a wide range of tests and assess the performance of the selected capacitor under small- and large-signal excitation.

#### A. Peak-to-Peak Voltage Ripple

The equivalent capacitance value of CeraLink® capacitors changes with the amplitude of the excitation (i.e., voltage ripple) [13], due to the hysteretic behaviour of the utilized antiferroelectric PLZT dielectric. Therefore, the first experimental tests aim at assessing the peak-to-peak voltage ripple performance of the DUT as function of the imposed charge ripple (i.e., varying the output current according to (8)). Notably, no such results are provided by the manufacturer and/or are available in literature at the time of writing.

Fig. 14. Equivalent circuit schematic of the adopted experimental setup for the performance assessment of a CeraLink® FA3 capacitor (i.e., 900 V,  $0.39\,\mu\text{F})$  [22]. The bridge-leg employs Wolfspeed C3M0032120K SiC MOSFETs (1200 V,  $32\,\text{m}\Omega)$  and the values of the filtering elements are  $L_{\rm i}=L_{\rm o}=64\,\text{mH}$ ,  $C_{\rm o}=66\,\mu\text{F}$ . The operating conditions of the device under test (DUT) can be changed by varying  $V_{\rm dc}$ ,  $I_{\rm o}$  and  $f_{\rm sw}$  (highlighted in blue).

Fig. 15. Experimental (a) peak-to-peak voltage ripple  $\Delta V_{\rm pp}$  and (b) equivalent capacitance  $C_{\rm eq}=\Delta Q_{\rm pp}/\Delta V_{\rm pp}$  as functions of the peak-to-peak charge ripple  $\Delta Q_{\rm pp}=I_{\rm o}/4f_{\rm sw}$  at  $f_{\rm sw}=25\,{\rm kHz}$ ,  $T_{\rm a}=23\,{\rm ^{\circ}C}$  and variable DC bias voltage  $V_{\rm dc}$ .  $C_{\rm eq}$  is also illustrated in (c) as function of  $\Delta V_{\rm pp}$ : the maximum peak-to-peak voltage ripple defined by the application is highlighted (i.e.,  $\Delta V_{\rm dc,pp,max}=20\,{\rm \%}\,V_{\rm dc}=160\,{\rm V}$ ), showing that  $C_{\rm eq}$  is  $9\,{\rm \%}$  higher than the rated small-signal capacitance value  $C^*=390\,{\rm nF}$  [22].

Fig. 15(a) and Fig. 15(b) show the peak-to-peak voltage ripple  $\Delta V_{\rm pp}$  and the equivalent capacitance  $C_{\rm eq}=\Delta Q_{\rm pp}/\Delta V_{\rm pp}$  obtained experimentally as functions of the peak-to-peak charge ripple  $\Delta Q_{\rm pp}$  and the DC voltage bias  $V_{\rm dc}$ . The tests are carried out by performing short switching burst periods at the target design switching frequency  $f_{\rm sw}=25\,{\rm kHz}$ , in order not to heat up the DUT during the measurements and keep its temperature approximately constant (i.e.,  $T\approx T_{\rm a}=23\,{\rm ^{\circ}C}$ ). It is observed that the voltage ripple does not rise linearly with the charge ripple excitation, leading to an increase in  $C_{\rm eq}$  for higher ripple amplitudes. Furthermore, the significantly positive effect of the DC bias voltage increase on the  $C_{\rm eq}$  value is clearly seen, highlighting the antiferroelectric behaviour of the DUT.

By expressing  $C_{\rm eq}$  as function of  $\Delta V_{\rm pp}$ , Fig. 15(c) is obtained. Remarkably, this figure provides fundamental information for the correct design of a PLZT-based DC-link capacitor, which is not available in the manufacturer's datasheet. Focusing on the curve obtained at  $V_{\rm dc}=800\,\rm V$ , it is observed that for low values of  $\Delta V_{\rm pp}$  the measured equivalent capacitance is below the rated small-signal capacitance value  $C^*=390\,\rm nF$  (i.e., however still within the  $\pm20\,\%$  tolerance band declared in the datasheet). Nevertheless, due to the capacitance increase with the amplitude of the excitation,  $C_{\rm eq}$  exceeds  $C^*$  in the selected design point (i.e.,  $\Delta V_{\rm dc,pp,max}=20\,\%\,V_{\rm dc}=160\,\rm V)$ , providing a  $\approx9\,\%$  design margin to the realized DC-link. It is worth highlighting that, to effectively assess the average performance of the selected capacitor technology, a higher number of capacitor samples would need to be tested.

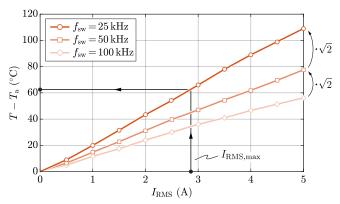

Fig. 16. Experimental capacitor temperature rise as function of the RMS current stress  $I_{\rm RMS}$  at  $V_{\rm dc}=800\,{\rm V}$ ,  $T_{\rm a}=23\,{\rm ^{\circ}C}$  and variable switching frequency  $f_{\rm sw}$ . The maximum current stress defined by the application is highlighted (i.e.,  $I_{\rm RMS,max}=I_{C_{\rm dc},{\rm RMS,max}}\,{}^{C^*}/C_{\rm dc}\approx 2.85\,{\rm A}$ ), leading to a temperature rise of  $\approx 62\,{}^{\circ}{\rm C}$ .

#### B. RMS Current Capability

To verify the current scaling laws introduced in Appendix A and used to derive (7), thermal measurements are performed at  $V_{\rm dc}=800\,{\rm V}$  to assess the DUT temperature rise as function of the RMS current stress  $I_{\rm RMS}$  and the switching frequency  $f_{\rm sw}$ . A thermal camera is employed to monitor the capacitor temperature rise with respect to the ambient (i.e.,  $T_{\rm a}=23\,{\rm ^{\circ}C}$ ). The results are reported in Fig. 16. It is immediately observed that the temperature rises approximately  $\propto I_{\rm RMS}$  (i.e., instead of  $\propto I_{\rm RMS}^2$ ), suggesting that the capacitor ESR decreases linearly with the temperature rise. This can be easily inferred by simplifying the temperature dependence expression of the ceramic capacitor (cf. Fig. 4(d)), under the assumption of high values of k or T, such that k ( $T-T_0$ )  $\gg 1$ :

$$\frac{R_{\rm ESR}(T)}{R_{\rm ESR}(T_0)} = \frac{1}{1 + k(T - T_0)} \approx \frac{1}{k(T - T_0)}.$$

(9)

Furthermore, it is observed that halving the switching frequency leads to a  $\approx \sqrt{2}$  increase of the temperature rise (i.e., capacitor losses). Since the capacitor ESR (and losses) decrease linearly with the temperature rise according to (9) (i.e.,  $1/\sqrt{2}$ ), it is straightforward to derive that the switching frequency halving leads to the doubling of the ESR, successfully verifying the  $R_{\rm ESR} \propto 1/f$  trend (cf. Section II) for large-signal excitation levels. According to Fig. 16, the maximum current stress defined by the application leads to a temperature rise of  $\approx 62\,^{\circ}{\rm C}$ , however this value does not reflect the real operating conditions (i.e.,  $T_{\rm a}=85\,^{\circ}{\rm C}$ ), which would lead to a much lower loss and temperature rise due to (9).

#### VI. CONCLUSION

This paper has proposed the analysis, sizing and design of a  $900\,\mathrm{V}$  full-ceramic DC-link capacitor for a  $550\,\mathrm{kVA}$   $25\,\mathrm{kHz}$  two-level EV drive inverter. It has been demonstrated that the use of PLZT ceramic capacitors allows to significantly reduce both volume (by  $\approx 6.6$  times) and weight (by  $\approx 3.6$  times) with respect to a state-of-the-art film-based solution, enabling a performance leap in the drive inverter power density. Furthermore, experimental tests have assessed for the first time the large-signal performance of PLZT capacitors, both in terms of peak-to-peak voltage ripple (i.e., equivalent capacitance) and RMS current capability (i.e., temperature rise).

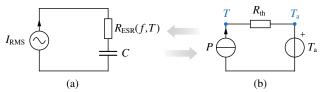

Fig. 17. Simplified (a) electrical equivalent circuit and (b) thermal equivalent circuit of a generic capacitor.

### APPENDIX A CAPACITOR RMS CURRENT SCALING

The RMS current capability of a capacitor is defined by different factors (e.g., physical size, ESR, number of paralleled units, operating frequency, temperature), which can affect the capacitor thermal dissipation capability, the generated losses, or both.

A simplified electrical equivalent circuit of a generic capacitor is illustrated in Fig. 17(a), which indicates that the capacitor power losses can be expressed as

$$P = R_{\rm ESR}(f, T) I_{\rm RMS}^2, \tag{10}$$

where  $R_{\rm ESR}(f,T)$  is the frequency/temperature-dependent ESR and  $I_{\rm RMS}$  is the RMS current flowing through the capacitor itself. For simplicity of the analysis, a sinusoidal current with frequency f is assumed.

The capacitor losses must then be dissipated towards the ambient, according to the simplified steady-state thermal equivalent circuit in Fig. 17(b). The heat flow leads to a rise of the capacitor temperature T with respect to the ambient temperature  $T_a$ , expressed as

$$T - T_{\rm a} = P R_{\rm th}, \tag{11}$$

where  $R_{\rm th}$  is the thermal resistance of the capacitor towards the ambient. Therefore, the RMS current capability of the capacitor is obtained by substituting (10) into (11):

$$I_{\rm RMS} = \sqrt{\frac{T - T_{\rm a}}{R_{\rm th} R_{\rm ESR}(f, T)}}.$$

(12)

Assuming to parallel N capacitor units (i.e.,  $N=C/C^*$ ) and considering general frequency and temperature dependencies of the capacitor ESR (i.e.,  $R_{\rm ESR} \propto 1/f^{\alpha}$ ,  $R_{\rm ESR} \propto 1/[1+k(T-T_0)]^{\beta}$ , cf. Section II), the following scaling laws are obtained:

$$\begin{cases}

R_{\text{ESR}}(f,T) = R_{\text{ESR}}^*(f^*,T^*) \frac{C^*}{C} \left(\frac{f^*}{f}\right)^{\alpha} \left(\frac{1+k(T^*-T_0)}{1+k(T-T_0)}\right)^{\beta} \\

R_{\text{th}} = R_{\text{th}}^* \frac{C^*}{C}

\end{cases} (13)$$

where \* indicates the values related to a single capacitor unit operating in the conditions specified in the manufacturer's datasheet,  $\alpha \approx \beta \approx 0$  for film capacitors and  $\alpha \approx \beta \approx 1$  for PLZT ceramic capacitors.

Therefore, a comprehensive scaling law for the capacitor RMS current capability is obtained from (12) and (13), as

$$I_{\rm RMS} = I_{\rm RMS}^* \frac{C}{C^*} \left(\frac{f}{f^*}\right)^{\alpha/2} \left(\frac{1 + k(T - T_0)}{1 + k(T^* - T_0)}\right)^{\beta/2} \sqrt{\frac{T - T_a}{T^* - T_a^*}}.$$

(14)

#### REFERENCES

- I. Husain et al., "Electric Drive Technology Trends, Challenges, and Opportunities for Future Electric Vehicles," Proceedings of the IEEE, vol. 109, no. 6, pp. 1039–1059, Jun. 2021.

- [2] T. M. Jahns and H. Dai, "The Past, Present, and Future of Power Electronics Integration Technology in Motor Drives," CPSS Transactions on Power Electronics and Applications, vol. 2, no. 3, pp. 197–216, Sep. 2017.

- [3] J. Reimers, L. Dorn-Gomba, C. Mak, and A. Emadi, "Automotive Traction Inverters: Current Status and Future Trends," *IEEE Transactions on Vehicular Technology*, vol. 68, no. 4, pp. 3337–3350, Apr. 2019.

- [4] A. K. Morya et al., "Wide Bandgap Devices in AC Electric Drives: Opportunities and Challenges," *IEEE Transactions on Transportation Electrification*, vol. 5, no. 1, pp. 3–20, Mar. 2019.

- [5] A. Poorfakhraei, M. Narimani, and A. Emadi, "A Review of Multilevel Inverter Topologies in Electric Vehicles: Current Status and Future Trends," *IEEE Open Journal of Power Electronics*, pp. 155–170, 2021.

- [6] D. Gerada et al., "High-Speed Electrical Machines: Technologies, Trends, and Developments," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 6, pp. 2946–2959, Jun. 2014.

- [7] F. Savi, D. Barater, M. D. Nardo, M. Degano, C. Gerada, P. Wheeler, and G. Buticchi, "High-Speed Electric Drives: A Step Towards System Design," *IEEE Open Journal of the Industrial Electronics Society*, vol. 1, pp. 10–21, 2020.

- [8] D. Cittanti, V. Mallemaci, F. Mandrile, S. Rubino, R. Bojoi, and A. Boglietti, "PWM-Induced Losses in Electrical Machines: An Impedance-Based Estimation Method," in *International Conference on Electrical Machines and Systems (ICEMS)*, Oct. 2021, pp. 548–553.

- [9] J. Millán et al., "A Survey of Wide Bandgap Power Semiconductor Devices," *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2155–2163, May 2014.

- [10] A. Bindra, "Wide-Bandgap-Based Power Devices: Reshaping the Power Electronics Landscape," *IEEE Power Electronics Magazine*, vol. 2, no. 1, pp. 42–47, Mar. 2015.

- [11] J. W. Kolar *et al.*, "Application of WBG Power Devices in Future 3-Φ Variable Speed Drive Inverter Systems "How to Handle a Double-Edged Sword"," in *IEEE International Electron Devices Meeting (IEDM)*, Dec. 2020, pp. 27.7.1–27.7.4.

- [12] D. Cittanti, M. Guacci, S. Mirić, R. Bojoi, and J. W. Kolar, "Comparative Evaluation of 800V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives," in *International Conference on Electrical Machines and Systems (ICEMS)*, Nov. 2020, pp. 1699–1704

- [13] TDK, "CeraLink® Capacitors: Technical Guide," 2021.

- [14] S. Chowdhury, E. Gurpinar, and B. Ozpineci, "High-Energy Density Capacitors for Electric Vehicle Traction Inverters," in *IEEE Transportation Electrification Conference Expo (ITEC)*, Jun. 2020, pp. 644–650.

- [15] M. Salcone and J. Bond, "Selecting Film Bus Link Capacitors for High Performance Inverter Applications," in *IEEE International Electric Machines and Drives Conference (IEMDC)*, May 2009, pp. 1692–1699.

- [16] H. Wen, W. Xiao, X. Wen, and P. Armstrong, "Analysis and Evaluation of DC-Link Capacitors for High-Power-Density Electric Vehicle Drive Systems," *IEEE Transactions on Vehicular Technology*, vol. 61, no. 7, pp. 2950–2964, Sep. 2012.

- [17] M. Uğur and O. Keysan, "DC Link Capacitor Optimization for Integrated Modular Motor Drives," in *IEEE International Symposium on Industrial Electronics (ISIE)*, Jun. 2017, pp. 263–270.

- [18] R. Alizadeh et al., "Busbar Design for Distributed DC-Link Capacitor Banks for Traction Applications," in *IEEE Energy Conversion Congress* and Exposition (ECCE), Sep. 2018, pp. 4810–4815.

- [19] J. Schnack, S. Brückner, H. Süncksen, U. Schümann, and R. Mallwitz, "Analysis and Optimization of Electrolytic Capacitor Technology for High-Frequency Integrated Inverter," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 11, no. 6, pp. 999–1011, Jun. 2021

- [20] TDK, "Film Capacitors: General Technical Information," 2018.

- [21] EPCOS, "PCC for Infineon HybridPack Drive (HP Drive)," 2016.

- [22] TDK, "CeraLink® Flex Assembly (FA) Series," 2019.

- [23] J. Kolar, H. Ertl, and F. C. Zach, "Calculation of the Passive and Active Component Stress of Three-Phase PWM Converter Systems with High Pulse Rate," in *European Conference on Power Electronics and Applications*, vol. 3, Oct. 1989, pp. 1303–1311.

- [24] M. Vujacic, M. Hammami, M. Srndovic, and G. Grandi, "Analysis of DC-Link Voltage Switching Ripple in Three-Phase PWM Inverters," *Energies*, vol. 11, no. 2, p. 471, Feb. 2018.

- [25] A. Hava, R. Kerkman, and T. Lipo, "Simple Analytical and Graphical Methods for Carrier-Based PWM-VSI Drives," *IEEE Transactions on Power Electronics*, vol. 14, no. 1, pp. 49–61, Jan. 1999.

- [26] TDK, "CeraLink® Low Profile (LP) Series," 2019.