# **Research on Reliability of Nanoscale System on Chips**

A dissertation submitted to Xi'an Jiaotong University and Politecnico di Torino in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> Weitao Yang Supervisor: Prof. Chaohui He Prof. Luca Sterpone Nuclear Science and Technology March 2022

## 摘要

纳米级系统芯片具有诸多优势,如体积小,重量轻,功耗低,集成度高等,使其在 多种应用中不断受到青睐,如航空航天,高能物理等。不过,对于应用于航空航天,高 能物理等环境下的电子系统,其所要面临的一个重要挑战是高能粒子入射电子系统诱 发的可靠性问题。尤其是随着半导体制造工艺的不断提升,各种高能粒子入射造成的 电子系统单粒子效应问题愈发显著。

为了探究纳米级系统芯片在不同粒子辐射环境下的可靠性问题,首先选取了两款 纳米级系统芯片: Xilinx Zyng-7000 All Programmable System on Chip (Xilinx 28nm CMOS SoC)和 Xilinx Ultrascale+ Multi-Processor Programmable System on Chip (Xilinx 16nm FinFET MPSoC)为研究对象。其中,前者为 28nm 互补金属氧化物制造工艺(CMOS), 后者为 16nm FinFET 制造工艺。针对两款芯片,采用多种手段对高能粒子诱发单粒子 效应问题开展了研究。研究手段主要包括加速器辐照实验,GEANT4 蒙特卡洛模拟仿 真,软件故障注入和概率安全分析等。对于 Xilinx 28nm CMOS SoC, 主要进行了质子, 大气中子和重离子的单粒子效应加速器辐照测试以及蒙特卡洛模拟。其中,质子辐照 中,利用 70 和 90 MeV 质子对非加固和加固状态下的片上存储器模块进行了单粒子效 应辐照测试,指出了70和90MeV质子诱发单粒子效应能力较为接近的原因,验证了 基于非对称双核模式下的单粒子效应加固能力。大气中子辐照中,通过对比分析不同 能量段中子造成的单粒子效应情况,指出 1-10 MeV 中子对于 Xilinx 28nm CMOS SoC 单粒子效应贡献不能忽略,热中子导致的单粒子效应亦需要考虑。在重离子加速器辐 照测试中,对于不同处理器模式下的单粒子效应进行了测试,指出处理器模式对单粒 子翻转效应无影响,发现了高线性能量转移值(LET)离子会诱发 Xilinx Zynq-7000 SoC 供电接口电流阶梯上升。

对于 Xilinx 16nm FinFET MPSoC,以多种图像应用处理算法为例,主要涉及图像 拉伸、边沿处理和深度神经网络(DNN)处理等,开发了不同的单粒子效应测试以及 软件故障注入系统。设计了基于软错误缓解(SEM)IP 核,动态部分重配置(DPR) 和动态重配置(DR)的故障注入系统,并且针对不同图像应用处理算法进行了故障注 入。结合概率安全分析方法,采用故障树分析方法对 SEM IP 故障注入结果进行了分 析,指出其敏感模块。采用失效模式和效应分析方法对 DPR 故障注入结果进行了分析, 指出了不同模块和错误对系统的可靠性造成威胁的严酷性程度。此外,通过 DNN 故障 注入,提出了一种提升 SRAM FPGA 上 DNN 识别精度的方法。

通过对两组系统级芯片单粒子效应进行测试,对不同应用环境下的可靠性问题进行了评估,为该系列芯片在强辐射环境下的应用提供了参考和支持。

Ι

关键词:系统芯片;单粒子效应;可靠性;加速器;蒙特卡洛模拟;故障注入 论文类型:应用基础

# ABSTRACT

Nanoscale system on chip (SoC) has many advantages, such as small size, light weight, low power consumption, high integration, etc., making them increasingly popular in a variety of applications, such as aerospace, high-energy physics, etc. However, electronic systems used in aerospace, high-energy physics, and other environments must face an important challenge: the reliability problem under strong radiation environments. Smaller technology suffers more seriously.

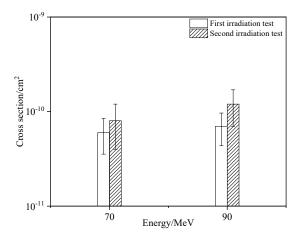

In order to explore the reliability of nanoscale SoCs in different particle radiation environments, two SoCs: Xilinx Zynq-7000 All Programmable SoC (Xilinx 28nm CMOS SoC) and Xilinx Ultrascale+ Multi-Processor Programmable SoC (Xilinx 16nm FinFET MPSoC) are used as devices under tests (DUTs). The former is a 28nm complementary metal oxide manufacturing process (CMOS) product, and the latter is manufactured with 16nm FinFET technology. For the two SoCs, various methods were employed to evaluate the single event effects (SEEs). The research methods include accelerator irradiation, GEANT4 Monte Carlo simulation, software fault injection, and probabilistic safety analysis. For SEE on Xilinx 28nm CMOS SoC, the accelerator irradiations and Monte Carlo simulations for protons, atmospheric neutrons, and heavy ions were carried out. In proton irradiation, 70 and 90 MeV protons were used to perform SEE irradiation tests on the on-chip memory (OCM) block under the nonhardening and hardening conditions. It was pointed out why the 70 and 90 MeV protons were more similar in inducing SEE. Meanwhile, the SEE hardening capability of the design based on asymmetric dual-core mode was verified. During atmospheric neutron irradiation tests, SEEs caused by neutrons in different energy ranges were investigated. The results indicated that the contribution of neutrons from 1 to 10 MeV to SEE of Xilinx 28nm CMOS SoC can not be ignored, and the SEE caused by thermal neutrons should be considered. SEE under different processor modes was tested in the heavy ion accelerator irradiation test. It was pointed out that the processor mode did not affect the single event upset (SEU). It was found that high linear energy transfer (LET) particles can induce Xilinx 28nm CMOS SoC power supply interface step-up current.

Aiming at the Xilinx 16nm FinFET MPSoC, a variety of image application processing algorithms are applied as test objects, mainly involving image stretching, edge processing, and deep neural network (DNN) processing. For different algorithms, various SEE tests and software fault injection (FI) systems have been developed. Specifically, the FI systems involved soft error mitigation (SEM) IP, dynamic partial reconfiguration (DPR), and dynamic reconfiguration (DR). Different FI results were analyzed, taking advantage of the diverse probability safety analysis methods. For instance, the fault tree analysis (FTA) method was used to analyze the SEM IP FI results, and the modules' sensitivity was investigated. The

failure modes and effects analysis (FMEA) method was employed to analyze the DPR fault injection results. The severity of the threat to the system reliability caused by different modules and errors was observed. In addition, through FI on DNN implementation on SRAM-based FPGA, a method was proposed to improve the accuracy of DNN identification.

By assessing SEEs on two SoCs, reliability issues in different application environments were evaluated, which provided reference and support for the applications in the strong irradiation environments.

**KEY WORDS**: System on chip; Single event effect; Reliability; Accelerator; Monte carlo simulation; Fault injection

TYPE OF DISSERTATION: Application Fundamentals

# CONTENTS

| ABSTRACT (Chinese)                                |    |

|---------------------------------------------------|----|

| ABSTRACT (English)                                |    |

| 1 Preface                                         |    |

| 1.1 Research Background                           |    |

| 1.1.1 SoC Development and Application             |    |

| 1.1.2 Radiation Environment                       |    |

| 1.1.3 Radiation Effects                           |    |

| 1.2 Research Status of Nanoscale SoC SEE          |    |

| 1.2.1 SEE Research on Xilinx 28nm CMOS SoC        | .7 |

| 1.2.2 SEE Research on Xilinx 16nm FinFET MPSoC    | .8 |

| 1.3 Layout of the Dissertation                    | .9 |

| 2 SEE Evaluation on SoCs                          | 11 |

| 2.1 SEE Evaluation on Xilinx 28nm CMOS SoC        | 11 |

| 2.1.1 Xilinx Zynq-7000 SoC                        | 11 |

| 2.1.2 Tested Block                                | 12 |

| 2.1.3 Test System1                                | 2  |

| 2.1.4 SEE Test Facilities in China                | 3  |

| 2.1.5 Monte Carlo Simulation                      | 3  |

| 2.1.6 SEE Hardening                               | 4  |

| 2.2 SEE Evaluation on Xilinx 16nm FinFET MPSoC    | 6  |

| 2.2.1 Test Benchmarks                             | 17 |

| 2.2.2 Fault Injection Implementations             | 17 |

| 2.2.3 PSA Analysis                                | 20 |

| 2.3 Summary                                       | 21 |

| 3 Proton SEE on Xilinx 28nm CMOS SoC              | 22 |

| 3.1 SEE Induced by Proton                         | 22 |

| 3.2 Proton Irradiation Setup                      | 22 |

| 3.2.1 Proton Beam Terminal                        | 22 |

| 3.2.2 Test Layout                                 | 23 |

| 3.2.3 Test Implementation                         | 23 |

| 3.3 Irradiation Results and Analysis              | 24 |

| 3.3.1 Proton Irradiation Results                  |    |

| 3.3.2 Monte Carlo Simulation Analysis             |    |

| 3.4 Summary                                       |    |

| 4 Atmospheric Neutron SEE on Xilinx 28nm CMOS SoC |    |

| 4.1 Atmospheric Neutron SEE                       |    |

| 4.2 Irradiation Examination                           | 32 |

|-------------------------------------------------------|----|

| 4.2.1 CSNS Spectrum                                   | 32 |

| 4.2.2 Test Implementation                             | 32 |

| 4.3 Irradiation Results                               |    |

| 4.4 Test Results Analysis                             |    |

| 4.4.1 E>1 and E>10 MeV Neutron Contribution           |    |

| 4.4.2 Mono-energy Neutron Geant4 Simulation           | 35 |

| 4.5 Thermal Neutron Influence Evaluation              | 37 |

| 4.5.1 BL09-2 Irradiation Results                      |    |

| 4.5.2 Thermal Neutron Contribution                    |    |

| 4.5.3 Elements Interaction                            | 40 |

| 4.6 Equivalence with Medium-energy Proton             | 42 |

| 4.7 Summary                                           | 43 |

| 5 Multi Patterns SEE on Xilinx 28nm CMOS SoC          | 44 |

| 5.1 Patterns Examination and Irradiation Setup        | 44 |

| 5.1.1 Patterns Examination                            | 44 |

| 5.1.2 Irradiation Setup                               | 44 |

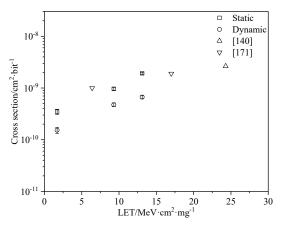

| 5.2 Irradiation Results                               | 46 |

| 5.2.1 SEE of HI-13 Irradiation                        | 46 |

| 5.2.2 SEE of HIRFL Irradiation                        | 47 |

| 5.3 Different Test Modes Influence                    | 49 |

| 5.4 Summary                                           | 51 |

| 6 Single Event Effect Hardening by Multi-Layer Design | 53 |

| 6.1 System-Level SEE Hardening                        | 53 |

| 6.1.1 Redundancy                                      | 53 |

| 6.1.2 Watchdog                                        | 53 |

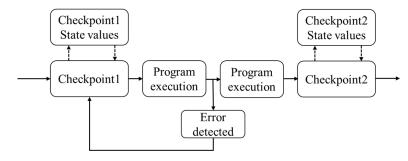

| 6.1.3 Checkpoint Rollback Recovery                    | 53 |

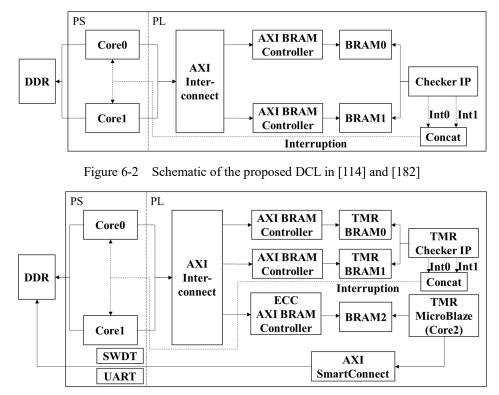

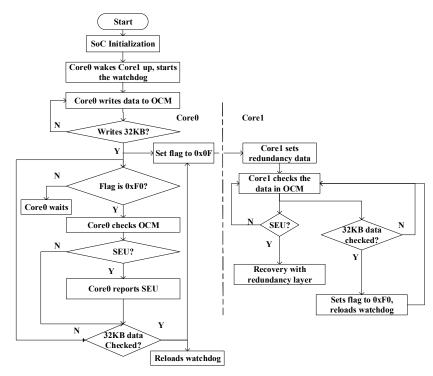

| 6.2 Multi-Layer Hardening Design                      | 55 |

| 6.2.1 Redundancy Layer                                | 55 |

| 6.2.2 Watchdog Monitor Layer                          | 55 |

| 6.2.3 AMP Layer                                       | 56 |

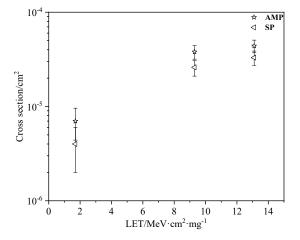

| 6.3 Irradiation Tests                                 | 57 |

| 6.3.1 Test Setup                                      | 57 |

| 6.3.2 Proton Beam                                     | 57 |

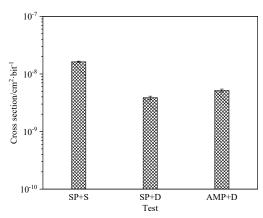

| 6.4 Irradiation Results and Discussions               | 58 |

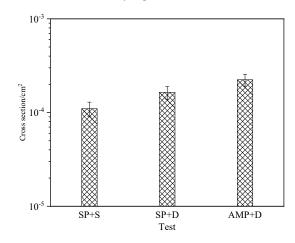

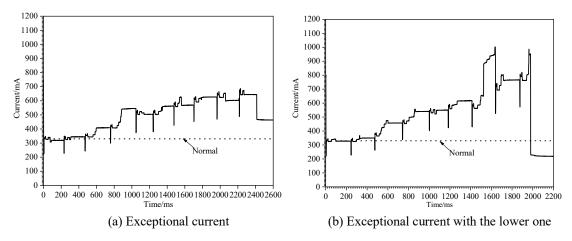

| 6.4.1 Irradiation Results                             | 58 |

| 6.4.2 Results Analysis                                | 59 |

| 6.5 Summary                                           | 61 |

| 7 SEM-based FI and FTA on Xilinx 16nm FinFET MPSoC    | 62 |

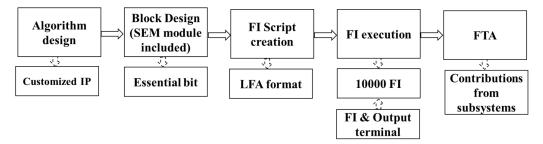

| 7.1 Overall Framework of SEM-based FI                 | 62 |

| 7.2 FI Design                                         | 63 |

| 7.2.1 Test Design in SEM-based FI                   | 63  |

|-----------------------------------------------------|-----|

| 7.2.2 FI and Outcome Terminal Design                | 64  |

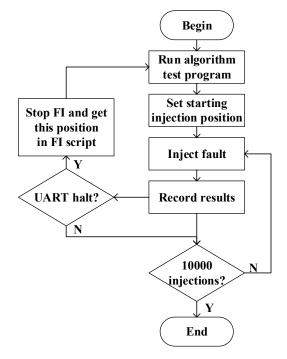

| 7.3 FI Implementation                               | 65  |

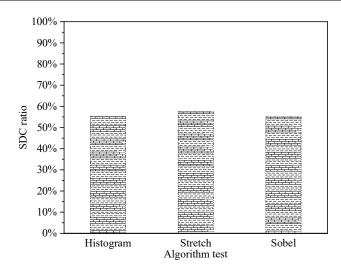

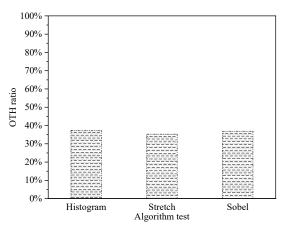

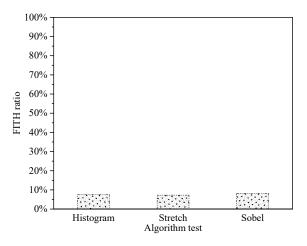

| 7.4 Detected FI Results                             | 68  |

| 7.5 FTA on the Detected Errors                      | 70  |

| 7.5.1 Events in Fault Trees                         | 70  |

| 7.5.2 Failure Rates of Events                       | 71  |

| 7.6 Summary                                         | 73  |

| 8 DPR-based FI and FMEA on Xilinx 16nm FinFET MPSoC | 74  |

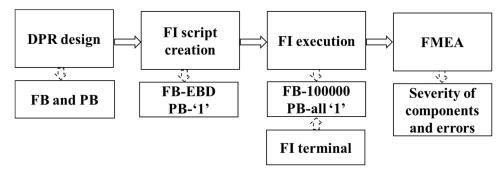

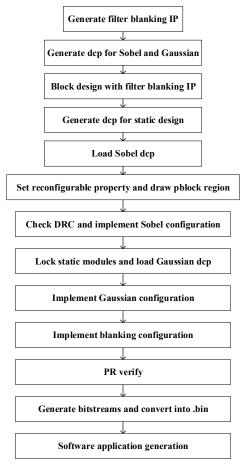

| 8.1 DPR-based FI Overall Structure                  | 74  |

| 8.2 DPR Design                                      | 75  |

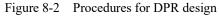

| 8.3 FI in DPR                                       | 77  |

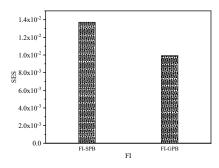

| 8.4 Detected Errors in FB and PB injections         | 79  |

| 8.4.1 Detected Errors                               | 79  |

| 8.4.2 SES of Errors                                 | 80  |

| 8.5 FMEA on the FI results                          | 81  |

| 8.5.1 FMEA Construction                             |     |

| 8.5.2 System Risk Assessment                        |     |

| 8.6 Summary                                         |     |

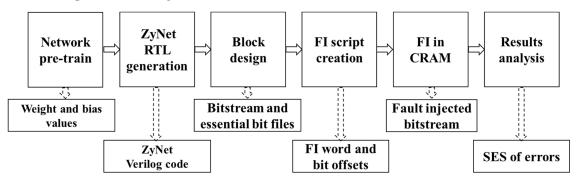

| 9 DR-based FI on DNN in Xilinx 16nm FinFET MPSoC    | 85  |

| 9.1 DR-based FI on DNN Realization Diagram          | 85  |

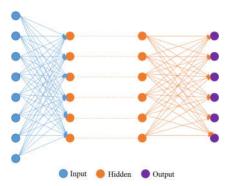

| 9.2 ZyNet DNN Implementation on Ultrascale+ MPSoC   |     |

| 9.2.1 Tested DNN                                    |     |

| 9.2.2 DNN Training and Implementation on MPSoC      |     |

| 9.3 FI on DNN                                       |     |

| 9.4 DNN FI Results                                  | 91  |

| 9.4.1 EIA on DNN                                    | 93  |

| 9.4.2 Optimal EIA on DNN                            | 94  |

| 9.5 DNN enhancement based on DR                     | 95  |

| 9.6 Summary                                         | 96  |

| 10 Conclusions and Suggestions                      | 97  |

| 10.1 Conclusions                                    | 97  |

| 10.2 Innovations                                    |     |

| 10.3 Suggestions                                    |     |

| Acknowledgments                                     |     |

| References                                          |     |

| Achievements                                        | 127 |

|                                                     |     |

# Abbreviation

| AXI         | Advanced extensible interface                             |

|-------------|-----------------------------------------------------------|

| APU         | Application process unit                                  |

| AMP         | Asymmetric multiprocessing                                |

| BL          | Beamline                                                  |

| BLF         | Bitstream load failure                                    |

| BRAM        | Block random access memory                                |

| BPSG        | Boro-phospho-silicate glass                               |

| CRE         | Calculation-result error                                  |

| CPU         | Central processing unit                                   |

| CY CIAE-100 | China institute of atomic energy 100 MeV proton cyclotron |

| CSNS        | China spallation neutron source                           |

| COTS        | Commercial-off-the-shelf                                  |

| CMOS        | Complementary metal oxide semiconductor                   |

| CLB         | Configuration logic block                                 |

| CRAM        | Configuration random access memory                        |

| CSU         | Configuration security unit                               |

| CRC         | Cyclic redundancy check                                   |

| DPHM        | Decoupled and poisoned hydrogen moderator                 |

| DNN         | Deep neural network                                       |

| DIA         | Degradation of the identification accuracy                |

| DCP         | Design checkpoints                                        |

| DRC         | Design rule check                                         |

| DUT         | Device under test                                         |

| DSP         | Digital signal processor                                  |

| DMA         | Direct memory access                                      |

| DD          | Displacement damage                                       |

| DFI         | DMA failed at initialization                              |

| DDR         | Double data read                                          |

| DCL         | Dual-core lockstep                                        |

| DPR         | Dynamic partial reconfiguration                           |

| DR          | Dynamic reconfiguration                                   |

| EIAS        | EIA sensitivity                                           |

| ERI         | Electronics resurgence initiative                         |

| EDF         | Energy-depletion film                                     |

| EIA         | Enhancement of the identification accuracy                |

| EDC         | Error detection and correction                            |

| ECC         | Error-correcting code                                     |

|             |                                                           |

| EBC    | Essential bits configuration                        |

|--------|-----------------------------------------------------|

| EBD    | Essential bits data                                 |

| ETA    | Event tree analysis                                 |

| FIT    | Failure in time                                     |

| FITH   | Fault injection terminal hang                       |

| FMEA   | Failure mode and effect analysis                    |

| FT     | Faraday tube                                        |

| FI     | Fault injection                                     |

| FTA    | Fault tree analysis                                 |

| FPGA   | Field-programmable gate array                       |

| FinFET | Fin field effect transistor                         |

| FF     | Flip flop                                           |

| FB     | Full bitstream                                      |

| BFUG   | Global clock buffer                                 |

| HI-13  | Heavy ion 13                                        |

| HIRFL  | Heavy ion research facility in lanzhou              |

| HKMG   | High-k metal gate                                   |

| IAC    | Identification accuracy changed                     |

| IO     | Input and output ports                              |

| ICAP   | Internal configuration access port                  |

| IRDS   | International roadmap for devices and systems       |

| IOB    | IO block                                            |

| JTAG   | Joint test action group                             |

| LGAA   | Lateral gate all around                             |

| LET    | Linear energy transfer                              |

| LFA    | Linear frame addresses                              |

| LUT    | Look up table                                       |

| MN     | Misidentification numbers                           |

| MBU    | Multi-bit upset                                     |

| MCU    | Multi-cell upset                                    |

| MP     | Multi-processor                                     |

| MPSoC  | Multi-processor system on chip                      |

| NICRA  | National innovation center of radiation application |

| OCM    | On chip memory                                      |

| OEIA   | Optimal EIA                                         |

| OTH    | Outcome terminal hang                               |

| PB     | Partial bitstream                                   |

| PSA    | Probability safety analysis                         |

| PS     | Processing system                                   |

| PCAP   | Processor configuration access port                 |

| PL     | Programmable logic                                  |

|        |                                                     |

| RHBP    | Radiation hardening by process                 |

|---------|------------------------------------------------|

| RAM     | Random access memory                           |

| ROM     | Read-only memory                               |

| RM      | Reconfiguration modules                        |

| ReLU    | Rectified linear unit                          |

| RISC    | Reduced instruction set computer               |

| RR      | Reprogrammable region                          |

| RPN     | Risk priority number                           |

| SEEM    | Secondary-electron emission monitor            |

| SD      | Secure digital                                 |

| SDC     | Silent data corruption                         |

| SBU     | Single bit upset                               |

| SEB     | Single event burnout                           |

| SEE     | Single event effect                            |

| SEFI    | Single event functional interruption           |

| SEGR    | Single event functional metruption             |

| SHE     | Single event fard error                        |

| SEL     | Single event latch-up                          |

| SET     | Single event transient                         |

| SEU     | Single event upset                             |

| SCU     | Snoop control unit                             |

| SEM     | Soft error mitigation                          |

| SER     | Soft error rate                                |

| SES     | Soft error sensitivity                         |

| SEP     | Solar energetic particle                       |

| SP      | Sole-processor                                 |

| SAA     | South atlantic anomaly                         |

| SRIM    | Stopping and range of ions in matter           |

| SB      | Switch box                                     |

| SMP     | Symmetric multiprocessing                      |

| SH      | System halt                                    |

| SoC     | System on chip                                 |

| SVT     | System validation tool                         |

| TID     | Total ionization dose                          |

| TMR     | Triple modular redundancy                      |

| TCL     | Triple-core lockstep                           |

| UART    | Universal asynchronous receiver-transmitter    |

| USB     | Universal serial bus                           |

| $N_b$   | Total tested bits                              |

| Ni      | Number of injected faults                      |

| $SER_b$ | Soft error rate of Mbit/FIT·Mbit <sup>-1</sup> |

|         |                                                |

## ABBREVIATION

| $SER_d$        | Soft error rate of device/FIT                                               |

|----------------|-----------------------------------------------------------------------------|

| ξ              | Error                                                                       |

| $\sigma_b$     | Bit cross section/cm <sup>2</sup> ·bit <sup>-1</sup>                        |

| $\sigma_d$     | Device cross section/cm <sup>2</sup>                                        |

| $\sigma_{sat}$ | Stature cross section/cm <sup>2</sup> or cm <sup>2</sup> ·bit <sup>-1</sup> |

| $L_{th}$       | LET threshold/MeV·cm <sup>2</sup> ·mg <sup>-1</sup>                         |

| Ø              | Cumulative fluence/cm <sup>-2</sup>                                         |

|                |                                                                             |

# 1 Preface

The system on chip (SoC) is a chip that integrates various electronic components. As a highly integrated advanced electronic system, the SoC rapidly has wider and wider applications. However, when the SoC is adopted in a hazardous environment, radiation effects, such as single event effect (SEE) caused by energetic particles, can not be ignored. This chapter briefly introduces the commercial-off-the-shelf (COTS) SoC development and application, harsh environment and radiation effects, and SEE research status on nanoscale SoCs.

## 1.1 Research Background

## 1.1.1 SoC Development and Application

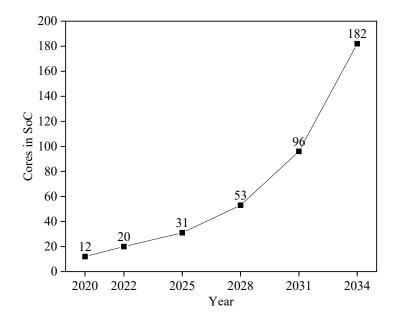

The International Roadmap for Devices and Systems (IRDS) 2020 released the next generations' logic core device technology roadmap <sup>[1]</sup>. Table 1-1 and Figure 1-1 are extracted from the report. They indicate the future trend of semiconductor technology and nanoscale COTS SoC integration. And it also declares the advanced COTS SoC will be continually and prosperously applied in the future. At the same time, it evidences the necessity and urgency of constantly studying relative issues, such as reliability, on the advanced processes COTS SoC.

| finFET: fin field-effect transistor, LGAA: lateral gate-all-around device |        |        |       |       |          |          |  |

|---------------------------------------------------------------------------|--------|--------|-------|-------|----------|----------|--|

| Year                                                                      | 2020   | 2022   | 2025  | 2028  | 2031     | 2034     |  |

| "Node<br>range"/nm                                                        | "5"    | "3"    | "2.1" | "1.5" | "1.0 eq" | "0.7 eq" |  |

| -                                                                         | finFET | finFET | LGAA  | LGAA  | LGAA-3D  | LGAA-3D  |  |

| Mainstream<br>device                                                      | Oxide  | Oxide  | Oxide | Oxde  | Oxide    | Oxide    |  |

| Vdd/V                                                                     | 0.70   | 0.70   | 0.65  | 0.65  | 0.60     | 0.60     |  |

| Gate<br>length/nm                                                         | 18     | 16     | 14    | 12    | 12       | 12       |  |

Table 1-1 IRDS 2020 logic core device technology roadmap <sup>[1]</sup>,

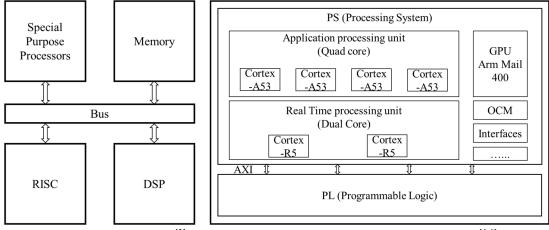

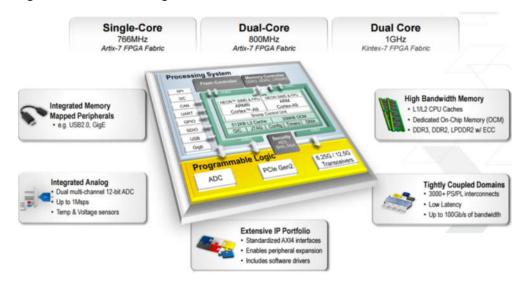

As a highly integrated electronic system, the COTS SoC keeps pace with the advanced and updated technology all the time since it was first released in the 1970s<sup>[2]</sup>. Especially since it enters the ultra-deep sub-micron technology, paradigms of the SoC rapidly shift and constantly update <sup>[3]</sup>. Nowadays, the old generation micron technology, which integrated reduced instruction set computer (RISC) processors, digital signal processor (DSP), and others, has developed into the nanoscale technology hybrid all programmable multi-processor (MP) SoCs. Figure 1-2 (a) and 1-2 (b) present the schematics of the traditional SoC and newer COTS FinFET Ultrascale+ MPSoC, respectively.

Figure 1-1 Core in SoC reported in IRDS 2020<sup>[1]</sup>

(b) Newer FinFET Ultrascale+ MPSoC [4-6]

Figure 1-2 Schematics of the micron SoC and FinFET Ultrascale+ MPSoC

Nanoscale COTS SoC always enjoys excellent performance in manufacturing, integration, and power dissipation. That's why different nanoscale COTS SoCs continuously gain much attention and are widely applied in various applications. Besides the conventional applications, such as multimedia processing, communication, biomedical, the nanoscale COTS SoC applications currently also involve aerospace vehicles, artificial intelligence, self-driving, high energy physics equipment, and so on <sup>[7-15]</sup>. Moreover, the nanoscale COTS SoC also gains popularity in the radiation community compared to similar rad-hard parts considering the trade-off between the cost and the performance, especially when it comes to the Cubesats and Nanosats <sup>[16]</sup>. The electronics resurgence initiative (ERI) (2017) takes the nanoscale COTS 3DSoC as the partial 2025-2030 research plan, and the flight avionics hardware roadmap (2014) regards nanoscale avionics COTS SoC spanning 2017 to 2026 <sup>[17-18]</sup>. These facts signify the development and applications of nanoscale COTS SoC and

demonstrate the urgency and necessity of reliability research.

However, when the nanoscale COTS SoC is employed in these platforms and scenes, it will encounter different radiation environments.

### 1.1.2 Radiation Environment

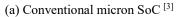

The spacecraft electronics may suffer from energetic particles, i.e., protons, heavy ions, and electrons, from outer space. In detail, they come from the Van Allen belt, solar cosmic rays, or galactic cosmic rays <sup>[19-21]</sup>. Figure 1-3 shows the diagram of the earth's radiation environment <sup>[22]</sup>.

Figure 1-3 The diagram of the earth's radiation environment <sup>[22]</sup>

## 1) Van Allen Radiation Belt

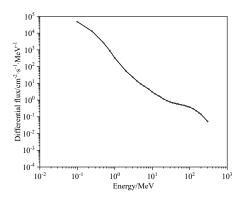

In 1958, the Van Allen radiation belts were discovered <sup>[23]</sup>. The belts are dynamic regions where the earth's magnetic field traps charged particles. They are composed of two belts. One is the inner belt, and the other is the outer one. The former location is about 1.2R to 2R (R is the earth radius), and energetic protons dominate it. The energy of the proton is up to 100s MeV. However, the region of the outer belt is about 3R to 10R, and the majority of the particle is the electron. The maximum energy of the electron is about 7 MeV <sup>[24-25]</sup>. In the inner belt, a region is named South Atlantic Anomaly (SAA), where the magnetic is reduced, and the proton's flux is rather higher than the same altitude regions <sup>[26]</sup>. Figure 1-4 presents the trapped proton differential flux spectrum of the AP8 max model in OMERE <sup>[27]</sup>.

Figure 1-4 The differential flux of trapped proton for AP8 max model at 800km altitude and 98° inclination <sup>[27]</sup>

2) Solar Cosmic Rays

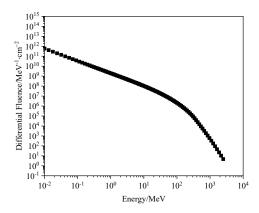

Solar cosmic rays are also called solar energetic particles (SEPs). It was first reported in the 1940s <sup>[28]</sup>. The rays are associated with solar flares. Most of the particle is protons, and the energy is up to GeV. Alpha particles, heavy ions, and electrons make up a small part of the rays. SEPs are episodic, and their cycle is about 11 years. That contains four low solar years and seven high solar years. Especially in the high years, solar flare frequency skyrockets and pose serious risks to various space and terrestrial electronic systems. Figure 1-5 draws the SEP differential fluence spectra for the 1989/10 Tylka model <sup>[29]</sup>.

Figure 1-5 SEP differential fluence spectra for the 1989/10 Tylka model <sup>[29]</sup>

## 3) Galactic Cosmic Rays

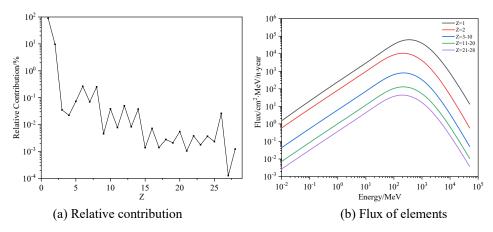

The galactic cosmic rays originate from the outside of the solar system <sup>[30]</sup>. However, it is an inverse correlation with solar activity. That means the galactic cosmic rays are intensive at a solar minimum <sup>[31]</sup>. The galactic cosmic rays are mainly composed of protons, which account for about 87%. The proton energy ranges from MeV to GeV. What's more, alpha particles and heavy ions take up approximately 12% and 1%, respectively <sup>[31]</sup>. Figure 1-6 (a) and (b) show the relative contribution and flux of different elements in galactic cosmic rays (Z=1 to Z=28), respectively.

Besides that, as the leap scaling of the nanoscale electronics, SEEs induced by atmospheric neutron also become significant to the terrestrial electronics system <sup>[32-34]</sup>. Simultaneously, SEEs caused by high energy electrons are gaining attention <sup>[35]</sup>.

Figure 1-6 Relative contribution and flux of different elements in galactic cosmic rays (Z=1 to Z=28)

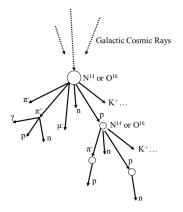

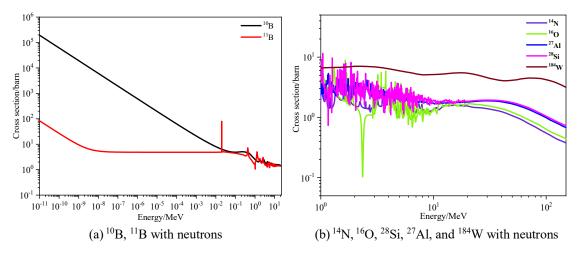

The cosmic rays can interact with the atoms, such as <sup>14</sup>N or <sup>16</sup>O, in the atmosphere. And these processes will generate plenty of secondary particles. The majority of the generated particles are neutrons, and atmospheric neutrons' flux correlates with the altitude, latitude, and other factors <sup>[36]</sup>. Proton, electron, muon, pion, and others are also generated in the processes. Figure 1-7 displays the schematic of the atmospheric neutron environment.

Figure 1-7 Schematic of the atmospheric neutron environment<sup>[36]</sup>

From aerospace to terrestrial, different energetic particles appear in different environments, and their incidents in nanoscale COTS SoCs may influence their reliabilities and cause various radiation effects.

## 1.1.3 Radiation Effects

The transient and cumulative radiation effects occur in electronics due to energetic particles hitting. The cumulative effect is the result of long-term irradiation. It includes total ionization dose (TID) and displacement damage (DD) <sup>[37-40]</sup>. And The transient effect is the single event effect (SEE) induced by a single energetic particle <sup>[41-43]</sup>.

#### 1) TID

The TID effect comes from the energy deposited by ionizing particles <sup>[44]</sup>. It leads to electron-hole pairs, resulting in trapped charges in the oxides and the interfaces in semiconductor devices. The following steps are summarized for TID <sup>[45-46]</sup>.

--Generation electron-hole pairs

- --Partial electron-hole pairs recombination

- --Carriers transport in the oxide

--Traps formation

2) DD

DD is the non-ionizing effect caused by energetic particles. Atoms are dislodged by the collision of the hitting particles. The collided atom is displaced from its original position, resulting in vacancy defects and interstitial defects. These defects can form cluster defects further <sup>[39]</sup>.

As semiconductors scale down, the oxide dielectric layers continuously shrink, the complementary-metal-oxide-semiconductor (CMOS) technologies turn more resilient to cumulative effects. Contrarily, reliability problems caused by SEE become more rigorous <sup>[47]</sup>.

3) SEE

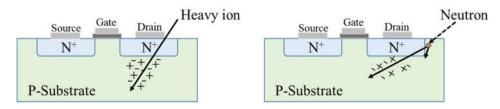

An energetic particle passes through the semiconductor, and it can directly or indirectly deposit energy and generate electron-hole pairs along its trajectory <sup>[48]</sup>. For example, Figure 1-8 depicts an energetic particle's direct and indirect mechanisms generating electron-hole pairs in a MOS by heavy ion and neutron, respectively.

(a) Direct generating by heavy ion (b) Indirect generating by a neutron

Figure 1-8 The mechanisms of direct and indirect generate electron-hole pairs

Following processes, such as recombination, drift, and diffusion, carriers drift, or diffuse to opposite polarity under the intense electric-filed, the charge collection and a pulse current appear at the node. SEE emerges if the collected charge exceeds the critical charge, which is the minimum amount charge forcing node state change <sup>[49]</sup>.

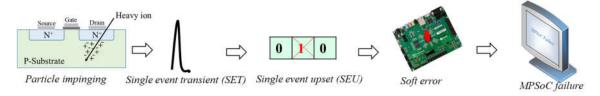

Figure 1-9 shows a brief schematic of SEE in a complicated SoC. When an energetic particle strikes the cell nodes, it can deposit energy along the trajectory. It can also generate electron-hole pairs along the track and cause a glitch at the node, namely a single event transient (SET). Then, if the pulse of the glitch is wide enough or captured by a memory cell, it possibly leads to datum change. Under this case, the single event upset occurs. Subsequently, if the processor uses the changed datum, it can cause results to error even SoC function fails.

Figure 1-9 Schematic of SEE in MPSoC

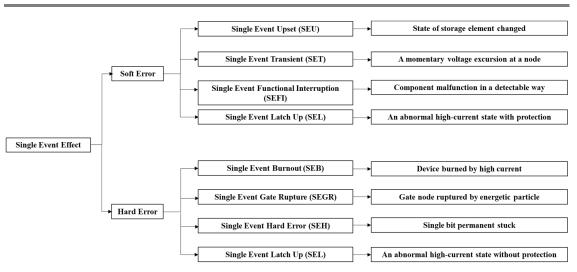

SEE may be non-destructive or destructive to the target electronics. The non-destructive and destructive effects are also named soft and hard errors. The soft errors are transient ones and can be recovered or processed. In comparison, the hard errors are permanent and result in the device being unavailable. Figure 1-10 describes the detail of different kinds of SEEs. For example, the SEU and single event functional interruption (SEFI) are soft errors, while the single event burnout (SEB) and single event gate rupture (SEGR) are hard errors.

For the SEU, according to the upset bit information, it can be the single bit upset (SBU), multi-bit upset (MBU), or multi-cell upset (MCU). What's more important is the MBU and MCU are turned out to be more serious as the semiconductor technology scaled down.

This work is dedicated to nanoscale COTS SoCs SEEs' reliability evaluations. To date, some efforts have also been conducted on this issue by other researchers.

Figure 1-10 Details of different kinds of SEEs [50]

## 1.2 Research Status of Nanoscale SoC SEE

It was a tremendous evolution that nanoscale SoC integrates the field-programmable gate array (FPGA) and ARM processor <sup>[51]</sup>. This evolution attracts industrial and academic interest, especially from the harsh environment applications, since the related products are released <sup>[52]</sup>. That's why the SEEs reliability assessment on the newer Xilinx COTS 28nm CMOS SoC and 16nm FinFET MPSoC continuously updates to now.

## 1.2.1 SEE Research on Xilinx 28nm CMOS SoC

For the SEE evaluations on Xilinx 28nm CMOS SoC, the effort involves SEE tests and mitigation techniques.

Austin set out to quantify the soft error rate (SER) of a COTS multi-core microprocessor SoC produced by Xilinx for the first time. And a 64MeV proton beam was used to measure the SEU susceptibility of the Xilinx Zynq processor sub-system <sup>[53]</sup>. It laid the foundation for the later SEE tests on nanoscale COTS SoCs. Giovanni discussed the temperature influence on atmospheric neutron inducing SER on Xilinx Zynq programmable logic sub-system <sup>[54]</sup>. Regarding SEE on Xilinx 28nm Zyng-7000 SoC, other researchers also conducted various tests and analyses. For example, Lucas performed multiple SEE tests based on various particles and designs [55-57]. Specifically, heavy ions and protons were adopted to examine SEE sensitivity under the condition of supply voltage and temperature variations <sup>[55]</sup>. Different memory organizations' SEE sensitivity was compared [56]. Trade-offs among different HLSbased designs' performance and reliability were analyzed <sup>[57]</sup>. Gennaro presented an analysis of traditional fault tolerance on parallel and Linux systems <sup>[58]</sup>. The reliability of a convolutional neural network implementation was discussed in [59]. Fault injections on 13 benchmarks were executed on Gem5<sup>[60]</sup>. Mehran measured heavy ion inducing multiple blocks SEE cross sections <sup>[61]</sup>. Libano proposed to distinguish critical and tolerable errors in artificial neural networks <sup>[62]</sup>. Mostafa investigated the delay changes of a routing network in heavy ion irradiation [63]. Vasileios characterized SEE vulnerability using very/ultra highenergy heavy ions <sup>[64]</sup>. David estimated the space SER based on the proton irradiation <sup>[65]</sup>.

Eduardo proposed software-implemented hardware fault tolerance techniques, simulation and heavy ion radiations were applied to verify the performance <sup>[66]</sup>. A generic model was presented to compute an implementation SEU sensitivity in [67]. A compiler-assisted software fault tolerance tool was developed, and the hardening performance was also examined <sup>[68-69]</sup>. A hybrid scrubber was built-in software to scrub configurations in [70]. Adria applied a dualcore lockstep design to mitigate soft errors <sup>[71]</sup>. Igor updated the bitstream-based SEU emulators and proposed a mathematical model <sup>[72-73]</sup>. Aaron presented a novel form of high speed internal processor configuration access port (PCAP) configuration port scrubbing strategy <sup>[74]</sup>. Farah designed a lightweight and fully testable SEU mitigation system to repair flips in configuration <sup>[75]</sup>. Ludovica reported a self rerouting and dynamically reconfiguration technique <sup>[76]</sup>.

Apart from Xilinx 28nm CMOS SoC, SEEs on similar devices from other vendors are also be examined. For instance, SEEs on Microsemi SoC were evaluated in neutron beam <sup>[77]</sup>. In [78], the authors investigated how the configuration of the processing system influences the reliability of the SmartFusion2' SoC.

Concerning studies of SEE on Xilinx 28nm CMOS SoC in China, efforts have also been made. Besides the alpha, proton radiation tests, Du analyzed the SoC reliability in the probability safety analysis (PSA) method, too <sup>[79-82]</sup>. In [79], seven hardware blocks' SEE susceptibilities of the SoC were investigated. In [80], low-energy proton beams were utilized to measure blocks' SEE vulnerability. At the same, fault injection and PSA were also applied in SoC sensitivity analysis based on the obtained irradiation results <sup>[81-82]</sup>. Liu observed the SEE sensitivity based on laser irradiation <sup>[83]</sup>. Microbeam irradiation was applied to investigate SEE sensitivity locations in [84]. Wu analyzed the SEE vulnerability using Soft Error Mitigation (SEM) IP <sup>[85]</sup>. Cui hardened SEU through dual-core mutual-check and recovery mechanisms <sup>[86]</sup>. A direct memory access (DMA) channel-redundant hardening method was proposed to enhance the reliability of DMA against soft errors <sup>[87]</sup>.

In general, these researches include five categories. The first one is the SEE sensitivity test on blocks or elements of the SoC directly in normal conditions using different accelerator irradiation. While the second is the SEE test in different operation conditions, for example, in different supply voltages or temperatures. The third examines SEE vulnerability in different application workloads, such as convolutional neural networks. And the fourth is software-based fault injections. Meanwhile, the last one is different SEE mitigating techniques relying on various strategies. Even though these efforts get some results, they are not comprehensive. For example, the particle energy is limited in the SEE test. Some proposed measures are only examined using the software. It's necessary to do further system-level SEE research on 28nm CMOS SoC.

#### 1.2.2 SEE Research on Xilinx 16nm FinFET MPSoC

Compared with the Xilinx 28nm CMOS SoC, the 16nm FinFET MPSoC integrates more components and enjoys a higher performance. The FinFET process is different from the CMOS, and researchers are also interested in how the SEE vulnerability is different from that

of the 28nm SoC.

In [88], the 1<sup>st</sup> Xilinx 16nm FinFET processor SEE results were presented, and SEEs were examined with neutrons, 64 MeV protons, and thermal neutrons. In addition. Christian implemented a fault-tolerant MPSoC for small satellites <sup>[89]</sup>. In [90], SEU reliability of neural networks was investigated with mitigation techniques against upsets for two case studies. Oscar presented a methodology to quantify multi metrics to SEE <sup>[91]</sup>. Additionally, three neutron beam tests were performed to characterize the SEE in [92]. David investigated SEE cross sections in proton beams and estimated the SER in space radiation <sup>[93]</sup>. Heavy-ion and neutron induced single event latch-up and SEU events were investigated in [94]. Maximilien observed the SEU induced by ultra-high energy heavy ion irradiation <sup>[95]</sup>. Pierre presented a test methodology using the Xilinx system validation tool (SVT) design suite to characterize SEE <sup>[96]</sup>. Philip examined the SEL and SEU susceptibility in proton irradiation <sup>[97]</sup>. The SEU response to SEM IP was investigated using 64MeV mono-energetic proton irradiation <sup>[98]</sup>.

The nanoscale COTS SoCs are rather complicated, and they can be applied in diverse circumstances and encounter various SEEs. Although some studies have been performed about SEEs, many questions are still not solved, and efforts need to be done further.

This study mainly focuses on SEE evaluations on two nanoscale COTS SoCs: the Xilinx 28nm CMOS SoC and 16nm FinFET Ultrascale+ MPSoC. Various irradiation tests, software simulations, fault injections, and analysis methods are adopted.

## 1.3 Layout of the Dissertation

This dissertation takes two nanoscale COTS SoCs as the study objects based on the introduction and efforts aforementioned. It presents SEE evaluations on them taking advantage of various solutions. According to the research objects and assessment methods, this dissertation is divided into ten chapters, and the main research contents of each chapter are as follows:

The 1<sup>st</sup> chapter is the preface. It introduces the COTS SoC development and application, harsh environment and radiation effects, and SEE research status on nanoscale SoCs.

The 2<sup>nd</sup> chapter is the SoC SEE test methodology. It briefs the two target nanoscale COTS SoCs and the used test methodologies in this article. For the SEE on Xilinx 28nm CMOS SoC, the adopted study methodologies are mainly irradiation tests and Monte Carlo simulations. While for the SEE on Xilinx 16nm FinFET MPSoC, the research methods are primarily involved fault injections and probability safety analyses.

The 3<sup>rd</sup> chapter is the proton SEE on Xilinx 28nm CMOS SoC. It introduces the 70 and 90 MeV proton beams' SEE irradiation tests and the Monte Carlo simulations on the chip.

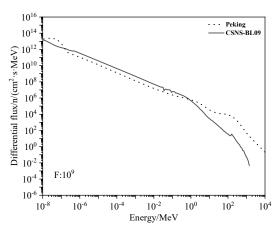

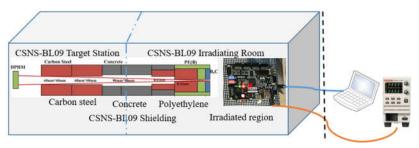

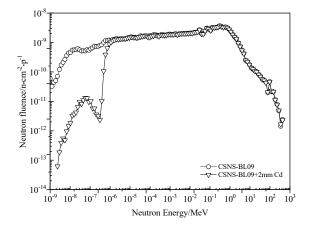

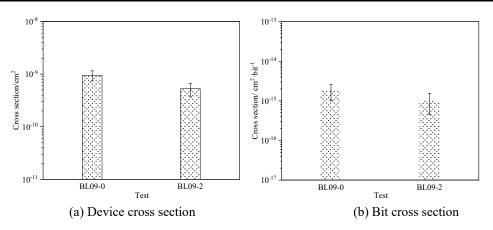

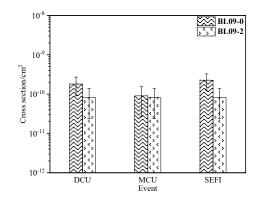

The 4<sup>th</sup> chapter is the atmospheric neutron SEE on Xilinx 28nm CMOS SoC. It describes multi SEE irradiation tests on the SoC using the China spallation neutron source and points out the SEE contributions from different energy range neutrons, especially the contribution from 1MeV and thermal neutrons.

The 5<sup>th</sup> chapter is the multi patterns SEE on Xilinx 28nm CMOS SoC. It implements multi patterns in the SoC and examines the SEE sensitivities of different patterns using heavy

ion irradiations.

The 6<sup>th</sup> chapter is the single event effect hardening by multi-layer design. It proposes the multi-layer design to immune SEE on the Xilinx 28nm CMOS SoC and verifies the performance of the design taking advantage of proton irradiations.

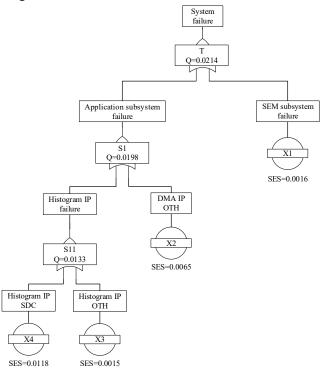

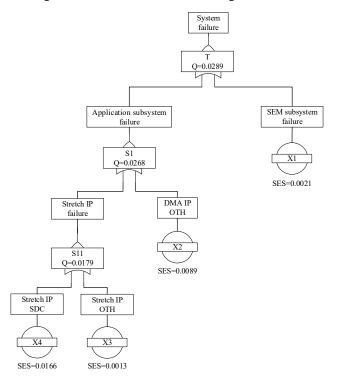

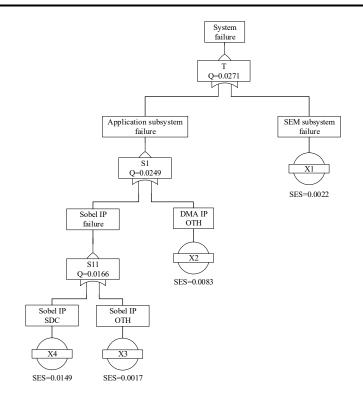

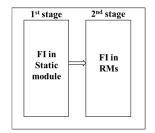

The 7<sup>th</sup> chapter is the SEM-based FI and FTA on Xilinx 16nm FinFET MPSoC. It involves the fault injections on the MPSoC based on SEM IP. Meanwhile, it analyzes the fault injection results using fault tree analysis (FTA) and figures out the SEE sensitivity of each tested algorithm and SEM subsystem.

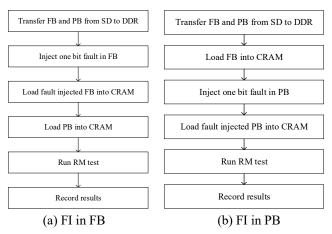

The 8<sup>th</sup> chapter is the DPR-based FI and FMEA on Xilinx 16nm FinFET MPSoC. It implements two DPR designs on the MPSoC and performs fault injections in the full and partial bitstreams. At the same time, the failure modes and effects analysis (FMEA) method is employed to analyze the obtained fault injection results in DPR fault injection, too. The SEE severity series of modules and errors are analyzed.

The 9<sup>th</sup> chapter is the DR-based FI on DNN in Xilinx 16nm FinFET MPSoC. It implants an open-source DNN on the MPSoC. Then, fault injection based on DR is executed to observe the performance of the DNN. And a solution is proposed in improving the DNN performance implemented on SRAM-based MPSoCs.

The 10<sup>th</sup> chapter is the conclusions and suggestions. It concludes the research findings of this dissertation and provides some suggestions for future studies.

# 2 SEE Evaluation on SoCs

As mentioned above, two typical nanoscale COTS SoCs were tested in this study. One is manufactured with 28nm CMOS technology, and the other is the 16 nm FinFET technology. Aiming at SEEs on the two SoCs, various irradiation tests, hardening designs, fault injections, and analysis methodologies are executed and verified.

# 2.1 SEE Evaluation on Xilinx 28nm CMOS SoC

## 2.1.1 Xilinx Zynq-7000 SoC

Xilinx Zynq-7000 SoC is an all programmable architecture SoC. It is built on state-ofthe-art, low power, high performance, 28nm, high-k metal gate (HKMG), and CMOS technology. This series of products embed a dual-core ARM® Cortex<sup>TM</sup>-A9 processor based processing system (PS) and programmable logic (PL) parts in a single die. Besides the heart processors, PS also includes the on-chip memory (OCM), Data/Instruction Cache, other memory interfaces, and plenty of peripherals. What's more, a flexible and scalable FPGA locates in the PL. Between the PS and PL, various buses provide communication. This SoC can serve the following applications: automotive driving, industrial control, smart camera, medical imaging, and others <sup>[99]</sup>.

Figure 2-1 draws the diagram of the Xilinx 28nm CMOS SoC [100].

Figure 2-1 Diagram of the Xilinx 28nm CMOS SoC<sup>[100]</sup>

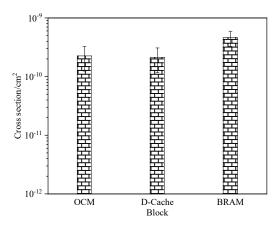

Memory blocks, for example, the OCM and Cache in PS, and the block random access memory (BRAM) in the PL, are critical components of the SoC. Their vulnerabilities in different radiation environments significantly influence the reliability of the SoC. For the Xilinx 28nm CMOS SoC, SEEs on memory blocks were evaluated and analyzed in multiple irradiation sources.

## 2.1.2 Tested Block

SEE on OCM, D-Cache, BRAM, and other memory blocks were studied in different conditions. In other blocks' tests, D-Cache is disabled. In some irradiations, several blocks are tested using one irradiation source. But, limited by the accelerator hours, a separate block is tested only in some irradiation tests.

1) OCM Block

The OCM block contains 256 KB random access memory (RAM) and 128 KB read-only memory (ROM) (BootROM). It supports two advanced extensible interface (AXI) slave ports (64-bit). One is dedicated to the central processing unit (CPU) access through the application process unit (APU) snoop control unit (SCU), and the other is shared by other masters within the PS and PL. The boot process uses the BootROM memory and is not visible to users <sup>[99]</sup>.

During the irradiation, SEU examination on OCM is executed with the following operations. Firstly, a data pattern, for instance, 0xA5A5A5A5, 0x5A5A5A5A, 0xFFFFFFF, or others, is written into the target range, and then data are read back. Finally, the processor compares the read-back with the expected to determine SEU occurrence.

#### 2) D-Cache Block

Each of the Cortex-A9 processors has a separate 32 KB L1 instruction and data Cache. And the L1 data Cache (D-Cache) plays the role of holding data that the Cortex-A9 processor uses. Key features of the L1 D-Cache are the following, for example, physically indexed and tagged, supporting two 32-byte line-fill buffers and one 32-byte eviction buffer <sup>[99]</sup>.

The data pattern, for instance, 0xA5A5A5A5, 0x5A5A5A5A, 0xFFFFFFFF, or others, is written into the target range of D-Cache. After the operations, such as flushing, writing, and invalidating the corresponding ranges, the host determines whether SEEs emerge during the irradiation.

## 3) BRAM Block

The BRAM is an important part of the PL. It locates in the PL, storing up to 36 KB of data. It can be configured as either two independent 18 KB RAMs or a sole 36 KB RAM. The writing and reading are synchronous operations for BRAM <sup>[99]</sup>.

PS is responsible for writing and reading BRAM data via the AXI interface. During the irradiation, the data pattern, for instance, 0xA5A5A5A5, 0x5A5A5A5A, 0xFFFFFFFF, or others, is written into the target range, and then data are read back. Finally, the processor compares the read back one with the expected to determine SEU.

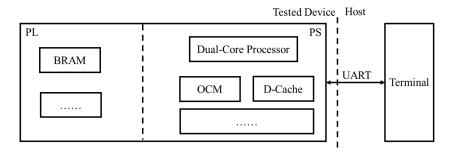

#### 2.1.3 Test System

The test system is composed of the host and tested device. The host is in charge of sending instructions and recording messages in real-time in a terminal. The tested device is the Xilinx 28nm CMOS SoC. The SoC is irradiated by particles during irradiation, and messages displayed on the terminal indicate the SEE occurrences on the SoC. The fiber universal serial bus (USB) cable provides communication between the host and SoC through the device's UART interface. Usually, the following information is required for the universal asynchronous receiver-transmitter (UART) communication. They include the communication port, baud rate,

parity bit, data with, and stop bit. Figure 2-2 shows the simplified architecture of the test system.

Figure 2-2 The architecture of the test system. Tested blocks are visible in the device block

## 2.1.4 SEE Test Facilities in China

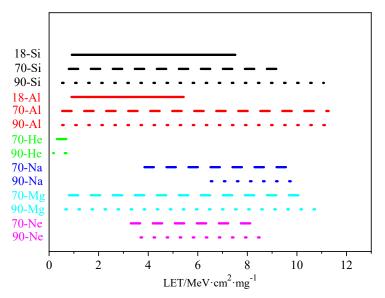

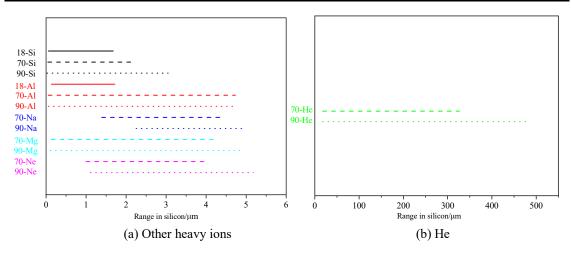

The irradiation test is highly effective in checking the SoC's SEE vulnerabilities. To date, diverse advanced particle accelerators are available in China. They involve beams of heavy ion, proton, atmospheric neutron, and electron. Among them, some have served in electronic systems irradiation tests for decades. For example, the heavy ion 13 (HI-13) accelerator in the National Innovation Center of Radiation Application (NICRA), China Institution Atomic Energy (CIAE), was commissioned in the 1980s <sup>[101]</sup>. Several particle parameters of the HI-13 are shown in Table 2-1. The Heavy Ion Research Facility in Lanzhou (HIRFL) was another crucial accelerator in the same period <sup>[102]</sup>. In addition, some are put into application in the latest years, such as the China Spallation Neutron Source (CSNS) and the China Institute of Atomic Energy 100 MeV proton cyclotron (CY CIAE-100) <sup>[103-104]</sup>. These facilities provide accelerator beams in SEE tests in China, and these accelerators are utilized in the Xilinx 28nm CMOS SoC SEE evaluations.

| Particle           | Energy/MeV | Surface LET<br>/MeV·cm <sup>2</sup> ·mg <sup>-1</sup> | Ranges in silicon/µm |  |

|--------------------|------------|-------------------------------------------------------|----------------------|--|

| $^{1}\mathrm{H}$   | 23         | 0.018                                                 | 3060                 |  |

| $^{12}C$           | 80         | 1.73                                                  | 127.1                |  |

| <sup>16</sup> O    | 104        | 3.03                                                  | 100.8                |  |

| <sup>19</sup> F    | 104        | 4.33                                                  | 76.6                 |  |

| <sup>28</sup> Si   | 126        | 9.6                                                   | 46.6                 |  |

| <sup>35</sup> Cl   | 138        | 13.9                                                  | 38.9                 |  |

| <sup>48</sup> Ti   | 149        | 22.6                                                  | 30.8                 |  |

| <sup>63</sup> Cu   | 161        | 33.4                                                  | 26.4                 |  |

| <sup>79</sup> Br   | 210        | 42                                                    | 29.4                 |  |

| $^{127}\mathrm{I}$ | 238        | 62.8                                                  | 27                   |  |

Table 2-1 The frequently used particles in the HI-13<sup>[105]</sup>

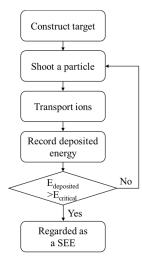

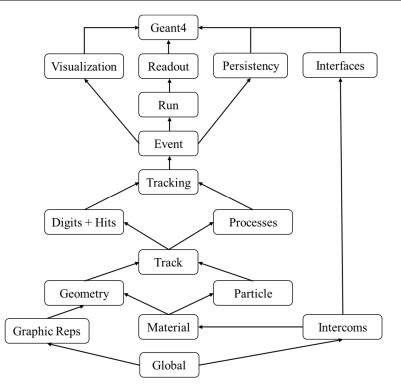

## 2.1.5 Monte Carlo Simulation

The Monte Carlo simulation helps to further analyze the investigated SEEs during irradiation tests. Especially, the physics-based Monte Carlo simulation tools gain much interest

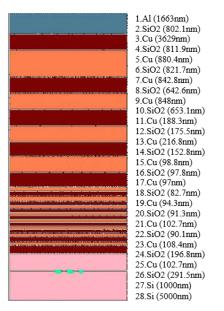

and popularity in radiation effects simulation. Currently, software tools, such as Geant4, CREME96, and others, are widely used in devices' SEE simulations and evaluations. These simulations usually involve the devices' sensitive volumes and critical charges <sup>[106-108]</sup>. Figure 2-3 shows the SEE simulation workflow in these tools.

Figure 2-3 Monte Carlo simulation workflow

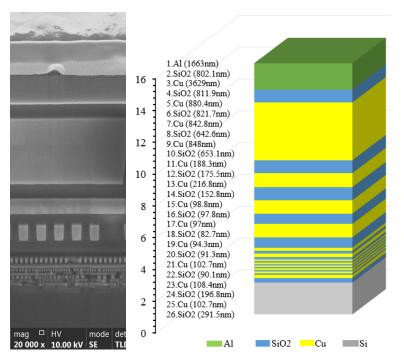

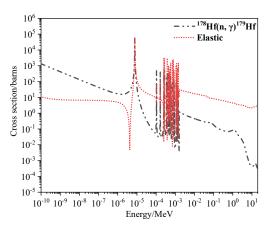

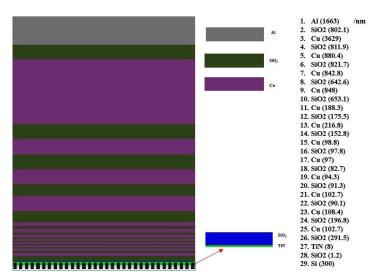

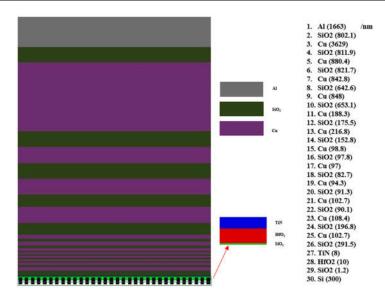

The vertical structure information of the Xilinx 28nm CMOS SoC is extracted to construct the simulation model. Figure 2-4 displays a cut-in photo of its vertical structure and the detail of each layer.

Figure 2-4 Photo of the extracted vertical cut-in of the Xilinx Zynq-7000 SoC

## 2.1.6 SEE Hardening

The SEE vulnerability of each tested block is investigated from the irradiation tests. In

some missions, the raw device's reliability cannot meet requirements, and the SEE hardening is necessary according to the mission duration and operation environment. For the established nanoscale COTS SoC, it's unfeasible to immune SEE via radiation hardening by process (RHBP) <sup>[109]</sup>. And that's why more efforts focus on system-level hardening techniques regarding SoC SEEs.

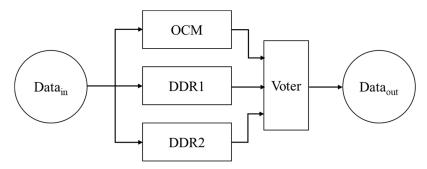

SEE hardening usually depends on the concept of redundancy, and redundancy can be achieved in hardware, software, information, or time <sup>[110]</sup>. Hardware redundancy incorporates replicated hardware or designs. Software redundancy is reached via checkpoint and recovery or other techniques. Information redundancy is executed by operations, such as error detection and correction (EDAC), cyclic redundancy check (CRC), etc. Time redundancy is repeating the same program execution <sup>[111]</sup>. Figure 2-5 presents the common triple modular redundancy (TMR), which takes the OCM in the SoC as an example. The TMR technique costs a large number of resources. So, some optimal TMR designs are also introduced. In [112], Luis proposed the automated design flow in implementing TMR. The author designed the partial TMR in [113].

Figure 2-5 The architecture of the triple modular redundancy implementation on OCM

The Xilinx 28nm CMOS SoC integrates the dual-ARM cores and FPGA inner the chip, and this characteristic provides more solutions for SoC hardening. For example, the hardening solutions depend on dual-core lockstep (DCLS), symmetric or asymmetric multiprocessing (SMP or AMP) mode. In [114], the DCLS was applied in the SoC, and the heavy ions' irradiation and fault injection were conducted to check the hardening performance. In [115], a novel triple-core lockstep (TCLS) approach was presented, incorporating the software level mitigation measures.

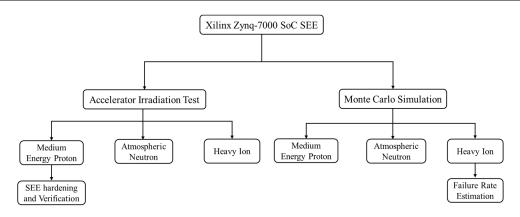

In general, in the current dissertation, multi irradiation tests involving proton, neutron, and heavy ion, are performed on the Xilinx 28nm CMOS SoC to evaluate SEEs in different radiation environments. Then, Monte Carlo simulations provide more detail to analyze the investigated phenomenon in irradiations. In addition, an AMP-based hardening solution is proposed and verified. Figure 2-6 outlines the research contents of SEE studies on Xilinx 28nm CMOS SoC in this work. It can be seen for each kind of particle, accelerator irradiation test and Monte Carlo simulation are performed. Moreover, SEE hardening performance is also examined using medium energy proton irradiation. The failure rate in space is also estimated, relying on the heavy ion irradiation results.

Figure 2-6 The SEE study schematic of this work on Xilinx 28nm CMOS SoC

Unlike the SEE evaluation on Xilinx 28nm CMOS SoC, the effort mainly focuses on the PS part and irradiation test. For the Xilinx 16nm FinFET MPSoC, SEEs are evaluated and analyzed on several specific applications primarily implemented in the PL section taking advantage of fault injection and probability safety analysis methods.

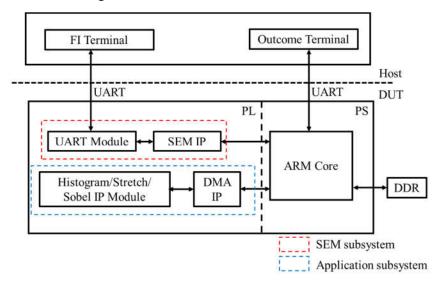

## 2.2 SEE Evaluation on Xilinx 16nm FinFET MPSoC

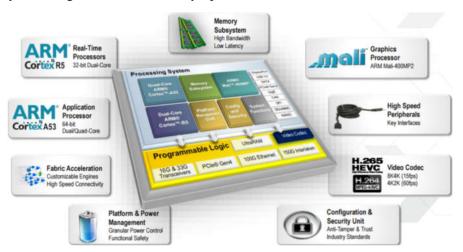

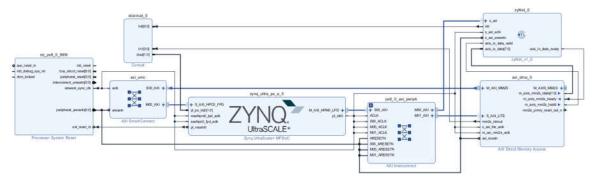

The Xilinx Zynq Ultrascale+ MPSoC is the first application-specific integrated circuit class programmable architecture. That enables multi-hundred gigabit per second levels of system performance with smart processing while efficiently routing and processing data on a chip <sup>[116]</sup>. The MPSoC is manufactured with the high-performance 16nm FinFET+ technology. The device retains a 2X increment compared with the planar device's watt and performance <sup>[117]</sup>. Moreover, the Xilinx 16nm FinFET MPSoC extends the processor scalability from 32 to 64 bits. And a 64-bit quad-core ARM® Cortex®-A53 processor, a 32-bit dual-core ARM Cortex-R5 real-time processor, and an ARM® Mali<sup>TM</sup>-400MP are integrated inner the processing system. It strongly supports hardware virtualization, graphics acceleration, video processing, waveform and packet processing, advanced power management, etc. <sup>[117]</sup>. Figure 2-7 displays the diagram of the Xilinx Zynq Ultrascale+ MPSoC.

Figure 2-7 Diagram of the Xilinx 16nm FinFET MPSoC<sup>[100]</sup>

## 2.2.1 Test Benchmarks

The image processing algorithms, such as edge processing and deep neural network (DNN), are prosperously extended in advanced SoC applications <sup>[118-120]</sup>. Their reliabilities are critical in some applications, for instance, self-driving. To explore SEE sensitivities on the Xilinx 16nm FinFET MPSoC in these applications, multiple image processing test benchmarks are designed, and fault injections are performed.

The image processing involves multiple algorithms, such as Histogram, Stretch, Sobel, Gaussian, etc. The DNN algorithm achieves handwritten digit identification. All of them are implemented in the PL parts in the Xilinx 16nm FinFET MPSoC. These algorithm designs can be implemented as an IP introduced in the block design. Or, they can be directly added to the block design as a separate block. The Vivado and Vitis 2019.2 software are employed in the designs <sup>[121]</sup>.

In Vivado 2019.2, the block design is built firstly. After the operations, such as synthesis, implementation, bitstream files are generated. The bitstreams and related files are the basements of fault injections. In Vitis 2019.2, programs are created, and necessary settings must also be done. For instance, in the SEM-based fault injection, the PL configuration logic interface should be transferred to the internal configuration access port (ICAP), and it's achieved via clearing the configuration security unit (CSU) pcap ctrl register.

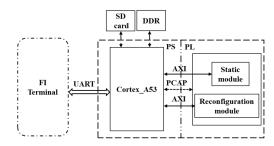

## 2.2.2 Fault Injection Implementations

Fault injection (FI) is an effective and feasible way to explore MPSoC's reliability. The FI platforms can be reached in several ways, spanning hardware-based to software-based <sup>[122]</sup>. It should be pointed out the vulnerability analysis of designs is prior to the expensive accelerator particle striking in SEE assessments and checking the hardening solutions' performance.

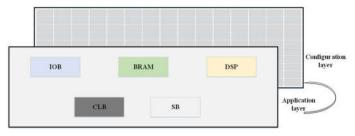

The application and configuration layers are two abstractions in FPGA. Figure 2-8 displays the abstracted layers in FPGA. The IO block (IOB), BRAM, DSP, configuration logic block (CLB), switch box (SB), and others are the hardware resources in the applications layer <sup>[122]</sup>. The configuration layer contains the configuration memory, in which different frames correspond to different hardware resources. If the bitstream in configuration memory encounters an energetic particle, the bit information may be flipped, and the function of the design may fail. Via modifying the bit information in the configuration random access memory (CRAM), it mimics the SEE in the bitstream and can investigate the consequences of SEE in CRAM.

Figure 2-8 Abstracted layers in FPGA, including the application and configuration layers

Bitstream lengths for different series devices vary, table 2-2 lists several devices' CRAM configuration parameters. It can be seen the least bitstream length is 44,549,344 bits, which means that FI on the entire bitstreams is extremely time-consuming. Therefore, the fault injection is usually randomly executed.

| Device | Configuration<br>Bitstream Length/bit | Configuration<br>Frames | Words per Frame |

|--------|---------------------------------------|-------------------------|-----------------|

| XCZU2  | 44,549,344                            | 14,964                  | 93              |

| XCZU3  | 44,549,344                            | 14,964                  | 93              |

| XCZU4  | 61,269,888                            | 20,956                  | 93              |

| XCZU5  | 61,269,888                            | 20,956                  | 93              |

| XCZU6  | 212,086,240                           | 71,260                  | 93              |

| XCZU7  | 154,488,736                           | 51,906                  | 93              |

| XCZU9  | 212,086,240                           | 71,260                  | 93              |

Table 2-2 Configuration bitstream parameters of different devices [123]

To keep the efficiency of random fault injection, the essential bit of the target design is necessary. Essential bit is the bits that are essential to the proper operation of any specific design loaded into the device <sup>[124]</sup>. However, if an energetic particle corrupts an essential bit, the FPGA may be malfunction. The essential bit files can be generated using the following property setting in Vivado design <sup>[124]</sup>.

set\_property bitstream.seu.essentialbits yes [current\_design]

The essential bits data (EBD) and essential bits configuration (EBC) files are created with the above proper setting, and they are the files related to the essential bit. The '1' in the EBD file signifies the corresponding location is essential, and this location's bit in EBC is the essential bit information. The fault injection script can be created based on the EBD file in different solutions. For the target device in this work, the pad word length is 118 words for the EBD and EBC files except for the header messages. Figure 2-9 (a) and (b) show the EBD and EBC file screenshot for a design.

| 📄 xx | . ebd🗵                                  | 🗎 xx | .ebc×                                   |

|------|-----------------------------------------|------|-----------------------------------------|

| 206  | 010010001010010000000000000000000000000 | 206  | 000000000000000000000000000000000000000 |

| 207  | 000000100001000000000000000000000000000 | 207  | 000000000000000000000000000000000000000 |

| 208  | 000000000010000100100010100100          | 208  | 000000000000000000000000000000000000000 |

| 209  | 010010001010010000000000000000000000000 | 209  | 000000000000000000000000000000000000000 |

| 210  | 000000100001000000000000000000000000000 | 210  | 000000000000000000000000000000000000000 |

| 211  | 0000000000100000100100010100100         | 211  | 000000000000000000000000000000000000000 |

| 212  | 000000000000000000000000000000000000000 | 212  | 000000000000000000000000000000000000000 |

| 213  | 000000000000000000000000000000000000000 | 213  | 000000000000000000000000000000000000000 |

| 214  | 000000000000000000000000000000000000000 | 214  | 000000000000000000000000000000000000000 |

| 215  | 10001000001001000010001100001000        | 215  | 000000000100000000000000000000000000000 |

| 216  | 10100011001010000000010000000000        | 216  | 000000000000000000000000000000000000000 |

| 217  | 00000100001000101000100000101100        | 217  | 000000000000000000000000000000000000000 |

|      | (a) EBD file screenshot                 |      | (b) EBC file screenshot                 |

Figure 2-9 Screenshot from the EBD and EBC file

The SEM controller and dynamic partial reconfiguration (DPR) are two solutions among various injection ways. They are employed in this study to execute FI on Xilinx 16nm FinFET MPSoC.

a) SEM-based Fault Injection

Fault injection using SEM IP is a common approach. SEM IP provided by Xilinx is

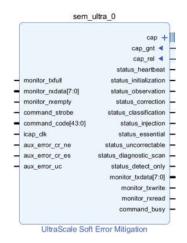

capable of injecting and mitigating errors in bitstreams <sup>[125]</sup>. Figure 2-10 depicts the picture of the SEM block in Vivado. Based on the essential bit script, SEM IP can inject one or more bits error in the frame via ICAP. What's more, it can mitigate SEE cooperating with the techniques such as error-correcting code (ECC) or CRC. The SEM controller can execute the following six modes, totally <sup>[124]</sup>. In the current study, injection and mitigation are required, so the chosen mode is mitigation and testing.

- Mitigation and Testing

- · Mitigation only

- Detect and Testing

- Detect only

- Emulation

- · Monitoring only

Figure 2-10 The SEM block in Vivado

During SEM fault injection, the essential bits are transferred into the frame, the smallest addressable cell in the bitstream, with the linear frame addresses (LFA). The length of LFA is 44 bits for the target devices, whose format is shown in Table 2-3.

|                                         | 18 | able $2-3$ | The format of LFA in Xilinx Zynq Ultrascale+ MPSoC |   |                    |            |           |  |

|-----------------------------------------|----|------------|----------------------------------------------------|---|--------------------|------------|-----------|--|

| #Bit 43-40 39-36 35-32 31-30 29-12 11-5 |    |            |                                                    |   | 11-5               | 4-0        |           |  |

| Content                                 | С  | 0          | 0                                                  | 0 | Linear frame index | Word index | Bit index |  |

Table 2-3

The format of LFA in Xilinx Zyng Ultrascale+ MPSoC

Even though the SEM IP is a low-cost solution to emulate and mitigate SEE in design, it fails if the fault is injected into the SEM corresponding frame. Hence, other ways are also adopted in fault injection, for instance, the DPR, DR.

b) DPR-based Fault Injection

The SRAM-based FPGA can be reprogrammed fully or partially many times, especially a region inner the FPGA can be flexibly reconfigured without disturbing other rest designs' operations in DPR <sup>[126-127]</sup>. It provides a way for fault injection based on DPR.

In DPR, a reconfigure block is designed in a reprogrammable region (RR), the full and partial bitstreams are generated finally. Then, the generated bitstreams are restored in secure

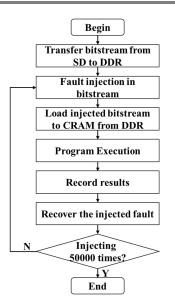

digital (SD) card and transmitted to double data read (DDR), via PCAP, they are loaded into CRAM implementing functions. Before loading the bitstreams from DDR to CRAM, fault can be injected by modifying the target bit.

It's different from the SEM-based fault injection, DPR fault injection doesn't require an extra block design. What's more important is it can indicate failures caused by full or partial bitstream upset. Moreover, Xilinx provides the library functions for PCAP transmitting bitstreams.

Compared with DPR, DR doesn't need to create the RR and generate partial bitstreams. It resembles a part of procedures in DPR. And the fault injection based on DR is similar to making fault injection in the full bitstream in DPR.

## 2.2.3 PSA Analysis

The fault injection campaign is capable of investigating SEEs while the CRAM bit flips. The injected bit may lead to SEM or customized design failure in SEM-based fault injection. And in the DPR-based fault injection, the effects from full or partial bitstreams' injections can be observed. Similarly, for the DR-based fault injection, SEE influences on the design can be viewed directly. In order to analyze the obtained results further, PSA is adopted in some fault injections.

Probabilistic safety analysis is an effective approach to evaluate the reliability and safety of complex systems. It's extensively applied in nuclear power plants and spacecraft <sup>[128-129]</sup>. The analysis modes, i. e. event tree analysis (ETA), FMEA, and FTA, are several standard commonly employed modules in PSA <sup>[130]</sup>. In this work, some modules are utilized to analyze the obtained results, for example, FTA and FMEA.

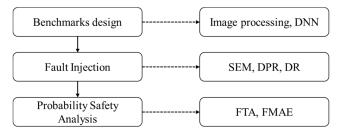

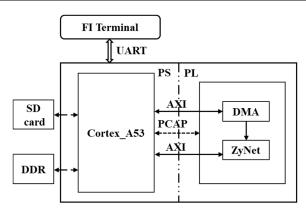

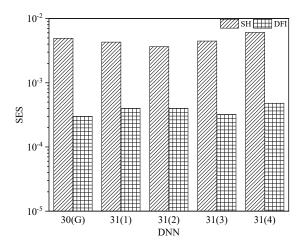

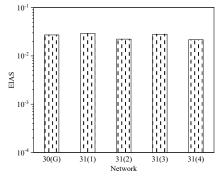

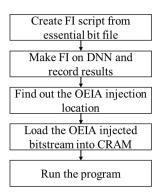

Regarding the Xilinx 16nm FinFET MPSoC, in this work, several test benchmarks are designed. Then, fault injection is executed depending on SEM, DPR, and DR, respectively. Last but not least, the probability safety analysis method is applied to analyze some investigated results in fault injections. Meanwhile, a solution to improve DNN performance based on DR fault injection is proposed, too. Figure 2-11 presents the research architecture on Xilinx 16nm FinFET MPSoC.

Figure 2-11 The research architecture on Xilinx 16nm FinFET MPSoC

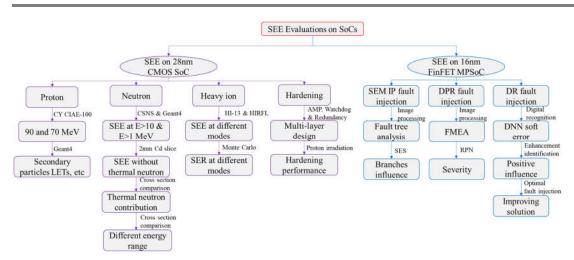

On the whole, this study focuses SEE assessments on the Xilinx 28nm CMOS SoC and 16nm FinFET MPSoC. The proton, neutron, and heavy ion irradiations as well as different kinds of fault injections are employed to evaluate SEE vulnerability under different conditions. Figure 2-12 describes the key research roadmap furthermore of the dissertation.

#### 2 SEE Evaluation on SoCs

Figure 2-12 The key research roadmap of the dissertation

# 2.3 Summary

It briefly introduced the research sketch of SEE evaluation on two series of SoCs: Xilinx Zynq-7000 SoC (28nm CMOS SoC) and Xilinx Zynq Ultrascale+ MPSoC (16nm FinFET MPSoC). For each SoC, the utilized test and evaluation methodologies are introduced. The SEE evaluations for Xilinx 28nm CMOS SoC are mainly about irradiation tests and Monte Carlo simulation. While for the Xilinx 16nm FinFET MPSoC, the SEE evaluations primarily involve fault injection and PSA analysis.

# 3 Proton SEE on Xilinx 28nm CMOS SoC

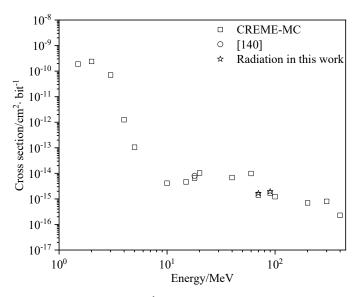

Energetic protons dominate the cosmic rays. As the semiconductor technology scales, it's inevitable to suffer SEE caused by energetic protons for nanoscale aerospace electronic systems. Therefore, SEE evaluations induced by energetic protons becomes extremely necessary. This chapter investigates 70 and 90 MeV protons inducing SEEs on Xilinx 28nm CMOS SoC at the CY CIAE-100 platform, the first medium energy proton SEE test terminal in China <sup>[104]</sup>. At the same time, the Geant4 and CREME-MC Monte Carlo simulations are also employed to analyze the mechanisms further of the investigated SEE.

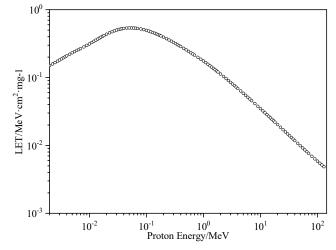

## 3.1 SEE Induced by Proton

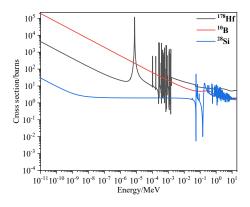

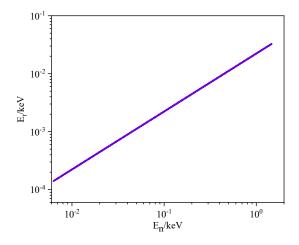

SEE induced by proton comes from two mechanisms. One is the direct ionization, and the other is the nuclear reaction. Recent research indicated low energy protons could induce SEE in nanoscale devices by direct ionization <sup>[131-134]</sup>, as the linear energy transfer (LET) of low-energy protons is greater than the devices' LET thresholds. The LET of the proton is shown in Figure 3-1 from stopping and range of ions in matter (SRIM) <sup>[135]</sup>. It can be seen in Figure 3-1, the LET of medium energy (20-100 MeV) proton is less than that of the low energy approximately two orders of magnitudes. It means the medium energy proton is impossible to lead to SEE through direct ionizing, only depending on the nuclear reaction.

Figure 3-1 The LET of different energy protons

## 3.2 Proton Irradiation Setup

## 3.2.1 Proton Beam Terminal

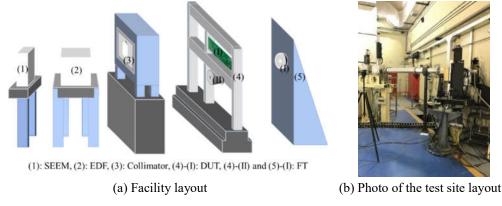

The proton beam is produced by the cyclotron accelerator. Then, the beam is extracted from the tube. Before hitting the device under test (DUT), the particle energy is adjusted by the energy-depletion film (EDF). At the same time, the collimator is utilized to regulate the beam collimation and spot area. The proton flux is monitored by the secondary-electron emission monitor (SEEM) and faraday tube (FT). Figure 3-2 (a) shows the terminal layout of the CY CIAE-100 platform <sup>[104]</sup>. And Figure 3-2 (b) is the photo of the test site layout.

Figure 3-2 Terminal layout of the CY CIAE-100 platform

The DUT is mounted on the platform sample holder, and the holder can move in different directions: up, down, left, and right. During irradiation, different regions of the DUT can be irradiated by moving the holder directly without disturbing the beam spot. The available beam size spans from  $1 \times 1$  to  $10 \times 10$  cm<sup>2</sup>. The proton energy varies from 30 to 100 MeV, and the flux is adjustable in the range of  $10^5$  to  $10^{12}$  p·cm<sup>-2</sup>·s<sup>-1</sup>.

## 3.2.2 Test Layout

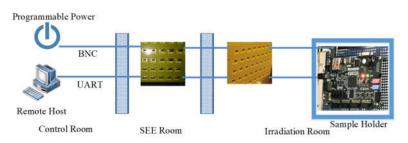

The irradiation campaign involves three rooms, including the control room, the SEE room, and the irradiation room. The programmable power remotely supplies the voltage of the test board in the control room, meanwhile, the current on the tested board is visible through the power. And the host computer in the control room also remotely communicates with the DUT. The platform holding the DUT stands in the irradiation room. Between them, the SEE room provides the transit connection. Figure 3-3 presents the schematic of the test layout in irradiation.

Figure 3-3 The schematic of the irradiation connection

## 3.2.3 Test Implementation

The DUT is the Xilinx 28nm CMOS SoC. The tested block is the OCM block. The chip size is about 1.8 cm×1.8 cm, and the beam covers the chip during the irradiation. Two test boards are mounted on the holder. One is irradiated with the 90 MeV proton, and the 70 MeV proton beam strikes another. 64 KB OCM were tested dynamically with the check pattern of 0xA5A5A5A5. Information including flipped addresses and bits are recorded in real-time once

| Table 3-1         | The parameters of two irradiations       |                            |

|-------------------|------------------------------------------|----------------------------|

| Proton Energy/MeV | Flux/p·cm <sup>-2</sup> ·s <sup>-1</sup> | Fluence/p·cm <sup>-2</sup> |

| 90                | $1.3 \times 10^{8}$                      | $1.0 \times 10^{11}$       |

| 70                | $2.3 \times 10^{8}$                      | 1.0×10 <sup>11</sup>       |

a SEE event is investigated.

Table 3-1 lists the flux and fluence of both irradiations. It can be seen the cumulative fluence  $1.0 \times 10^{11}$  cm<sup>-2</sup> in two irradiations. And which is the same in the two tests, although a little discrepancy exists in the fluxes.

## 3.3 Irradiation Results and Analysis

#### 3.3.1 Proton Irradiation Results

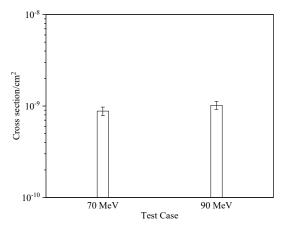

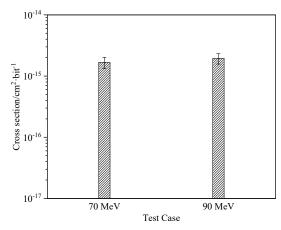

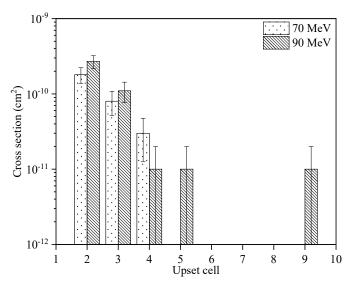

During both irradiations, SEU and SEFI events are detected. In the 90 MeV irradiation test, 143 SEU and 7 SEFI events are observed. And 118 SEU and 6 SEFI events were observed during the 70 MeV irradiation test. The SEUs contain SBU, DCU, and MCU (number of upset cells more than 2) events.

Besides the detected SBU and DCU events, the MCUs include 3, 4, 5, and 9 cell upsets in the 90 MeV irradiation test. Table 3-2 presents the details of SEE. It can be seen SBU dominates the events. Although the MCU number is once for 4, 5, and 9 cells upset, the fact, especially the detected nine-cell upsets, illustrates the device is vulnerable to medium energy proton.

|       | Ta  | ble 3-2 | Upset events in t | he 90 MeV proto | n irradiation |               |

|-------|-----|---------|-------------------|-----------------|---------------|---------------|

|       | SBU | DCU     | 3 cell upsets     | 4 cell upsets   | 5 cell upsets | 9 cell upsets |

| Total | 102 | 27      | 11                | 1               | 1             | 1             |

| 0→1   | 54  | 12      | 4                 | 0               | 1             | 1             |

| 1→0   | 48  | 15      | 7                 | 1               | 0             | 0             |

T11 22 II ( (1 00 M M ( ) ) )

SEEs of the 70 MeV irradiation test are shown in Table 3-3. It can be seen the majority of the event is SBU, too. It's different from the MCU in the 90 MeV irradiation test, the maximum MCU is the 4 cell upsets in the 70 MeV irradiation test while it occurs not once only.

Table 3-3

SEE in the 70 MeV proton irradiation

|       |     |     | / · · · · · · · · · · · · · · · · · |               |

|-------|-----|-----|-------------------------------------|---------------|

|       | SBU | DCU | 3 cell upsets                       | 4 cell upsets |

| Total | 88  | 18  | 8                                   | 3             |

| 0→1   | 46  | 10  | 4                                   | 1             |

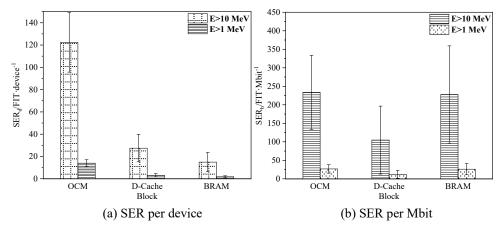

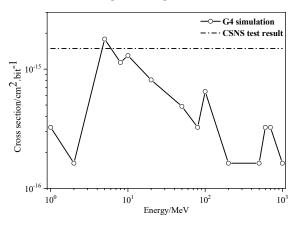

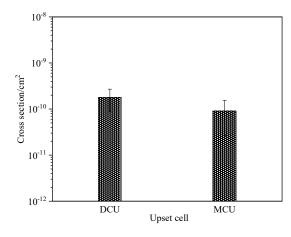

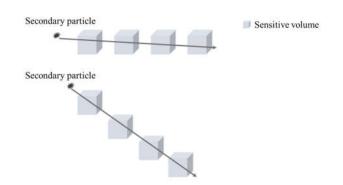

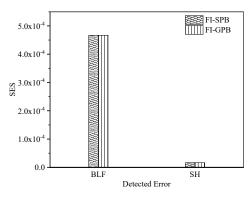

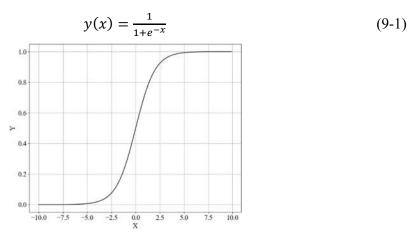

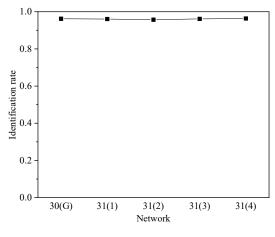

| 1→0   | 42  | 8   | 4                                   | 2             |