# POLITECNICO DI TORINO Repository ISTITUZIONALE

A Simplified Hard-Switching Loss Model for Fast-Switching Three-Level T-Type SiC Bridge-Legs

| Original A Simplified Hard-Switching Loss Model for Fast-Switching Three-Level T-Type SiC Bridge-Legs / Cittanti, Davide; Gammeter, Cristoph; Huber, Jonas; Bojoi, IUSTIN RADU; Kolar, Johann W In: ELECTRONICS ISSN 2079-9292 ELETTRONICO 11:11(2022), p. 1686. [10.3390/electronics11111686] |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Availability: This version is available at: 11583/2964760 since: 2022-05-26T18:09:43Z                                                                                                                                                                                                          |  |

| Publisher: MDPI                                                                                                                                                                                                                                                                                |  |

| Published DOI:10.3390/electronics11111686                                                                                                                                                                                                                                                      |  |

| Terms of use:                                                                                                                                                                                                                                                                                  |  |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                        |  |

|                                                                                                                                                                                                                                                                                                |  |

| Publisher copyright                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                |  |

(Article begins on next page)

Communication

# A Simplified Hard-Switching Loss Model for Fast-Switching Three-Level T-Type SiC Bridge-Legs

Davide Cittanti <sup>1</sup>, Cristoph Gammeter <sup>2</sup>, Jonas Huber <sup>2</sup>, Radu Bojoi <sup>1</sup> and Johann W. Kolar <sup>2</sup>

- Dipartimento Energia "Galileo Ferraris", Politecnico di Torino, 10129 Torino, Italy; davide.cittanti@polito.it (D.C.); radu.bojoi@polito.it (R.B.)

- Power Electronic Systems Laboratory (PES), ETH Zürich, 8092 Zürich, Switzerland; christoph.gammeter@celeroton.com (C.G.); kolar@lem.ee.ethz.ch (J.W.K.)

- \* Correspondence: huber@lem.ee.ethz.ch

Abstract: Hard-switching losses in three-level T-type (3LTT) bridge-legs cannot be directly estimated from datasheet energy loss curves, which are given for symmetric two-level half-bridge configurations only. The commutations in a 3LTT bridge-leg occur between semiconductors with different blocking voltages and/or current ratings, and involve a third semiconductor device in the switching transition, which contributes additional capacitive losses. This paper, therefore, describes a simplified approach to estimate a lower bound for the hard-switching losses of 3LTT bridge-legs (note that the approach is applicable to other three-level topolgies as well). In view of the very fast switching speeds of wide-bandgap semiconductors, the model neglects voltage/current overlap losses and considers only the dominating charge-related loss contributions (semiconductor output capacitances, body diode reverse-recovery charge), thus requiring minimal information from datasheets. A direct experimental verification with an 800 V DC-link 3LTT bridge-leg (1200 V and 650 V SiC MOSFETs) operating with output currents up to 25 A confirms the good accuracy of the simplified switching-loss model.

Keywords: switching losses; three-level converters; wide-bandgap semiconductors; SiC MOSFETs

Citation: Cittanti, D.; Gammeter, C.; Huber, J.; Bojoi, R.; Kolar, J.W. A Simplified Hard-Switching Loss Model for Fast-Switching Three-Level T-Type SiC Bridge-Legs. *Electronics* 2022, 11, 1686. https://doi.org/10.3390/ electronics11111686

Academic Editors: Ayan Mallik and Irfan Ahmad Khan

Received: 2 May 2022 Accepted: 23 May 2022 Published: 25 May 2022

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

Three-level converter topologies, especially in combination with wide-bandgap (WBG) power semiconductors such as SiC MOSFETs, are enabling ever more compact and more efficient power electronic converter systems [1-4], and are therefore of key importance to next-generation PFC rectifiers for battery charging, datacenter power supply modules, and inverter systems for variable-speed drives used in industry automation and electrified transport. In particular, the three-level T-type (3LTT) converter (cf., Figure 1), originally proposed in the 1970s [5], achieves very promising performance for 800 V DC-link applications, especially if modern WBG power semiconductors are employed [3,6]. Essentially, a two-level bridge-leg (with 1200 V SiC MOSFETs) is extended by a four-quadrant switch that allows the connection of the AC output terminal to the DC-link midpoint, i.e., enables three output voltage levels. The four-quadrant midpoint switch can advantageously be realized with two 650 V SiC MOSFETs connected in anti-series. Compared to other three-level topologies, such as the neutral-point-clamped (NPC) converter [7,8], or its sibling with active switches instead of clamping diodes (active NPC, ANPC) [9], the 3LTT requires, thus, fewer power semiconductors and, especially, fewer gate-drive power supplies (if the midpoint switch employs a common-source configuration); i.e., the 3LTT shows a favorable trade-off between functionality and complexity [10].

To perform a first-step comparative evaluation of different power semiconductors for a given application, there is a need to quickly estimate switching losses. Whereas datasheets usually directly provide turn-on and turn-off energy losses as a function of voltage and current for symmetric two-level bridge-legs, the situation is more complicated for 3LTT bridge-legs [6,11]. First, any commutation between two semiconductor devices

Electronics **2022**, 11, 1686 2 of 10

also changes the blocking voltage across a third device connected to the common switching node, causing additional capacitive losses. Second, the commutations occur between semiconductors with different blocking voltage and/or current ratings (i.e., for the example mentioned above, between a 1200 V SiC MOSFET and a 650 V SiC MOSFET used as the midpoint switch). For these reasons, it is not possible to use the switching loss data available in typical semiconductor datasheets directly for estimating the switching losses of a certain device combination in a 3LTT bridge-leg.

Therefore, this paper provides a simplified approach to estimate the minimum hard-switching losses of SiC-MOSFET-based 3LTT bridge-legs by considering only charge-related losses (i.e., capacitive and reverse-recovery losses), which effectively dominate the hard-switching energy loss for fast-switching power semiconductors [12]. This paper consolidates existing contributions to semiconductor output capacitance charge/discharge loss modeling for three-level bridge-legs [6,11,13], as well as to the simplified estimation of diode reverse-recovery losses [6,11], into a compact, straightforward loss modeling approach.

In contrast to the interesting switching loss estimation method developed in [13], which requires double-pulse test loss measurement results, the loss model proposed herein can be parametrized with datasheet information on the devices' output capacitances,  $C_{\rm oss}$ , and reverse-recovery charge,  $Q_{\rm rr}$ , only. Additionally, targeting GaN devices, the modeling approach outlined in [13] does not account for reverse-recovery losses, i.e., it is not directly applicable to 3LTT bridge-legs with SiC MOSFETs. The switching-loss model in [13] has only been verified indirectly at the converter level by measuring the total converter losses of a 3LTT undiriectional rectifier adopting 650 V GaN HEMTs and 1200 V SiC Schottky diodes.

In this paper, a dedicated experimental verification of the proposed loss model is performed on an 800 V DC-link 3LTT bridge-leg prototype (using 1200 V and 650 V SiC MOSFETs) through accurate calorimetric loss measurements. The experimental results confirm an almost perfect prediction of capacitive charge/discharge losses and show that the proposed model, including diode reverse-recovery, achieves a maximum hard-switching loss underestimation error of 18% (i.e., due to neglecting overlap losses [12]). It is worth highlighting that even though this work focuses on the 3LTT converter topology (for reasons of clarity and conciseness), the proposed hard-switching-loss model can be applied to arbitrary three-level bridge-legs (e.g., NPC, ANPC, etc.), as explained in [6].

The paper is organized as follows. First, Section 2 discusses the modeling of capacitive losses in a 3LTT bridge-leg, clarifying also the impact of the third device connected to the switching node but not actively involved in the commutation. In Section 3, a simplified model for the estimation of the bridge-leg losses in hard-switching operation is described, taking into account both capacitive and reverse-recovery loss contributions. Section 4 provides a direct experimental verification of the proposed models, using highly accurate calorimetric measurements of the semiconductor losses. Finally, Section 5 concludes the paper and gives an outlook on future developments, highlighting the importance of comprehensive reverse-recovery information in device datasheets.

Electronics **2022**, 11, 1686 3 of 10

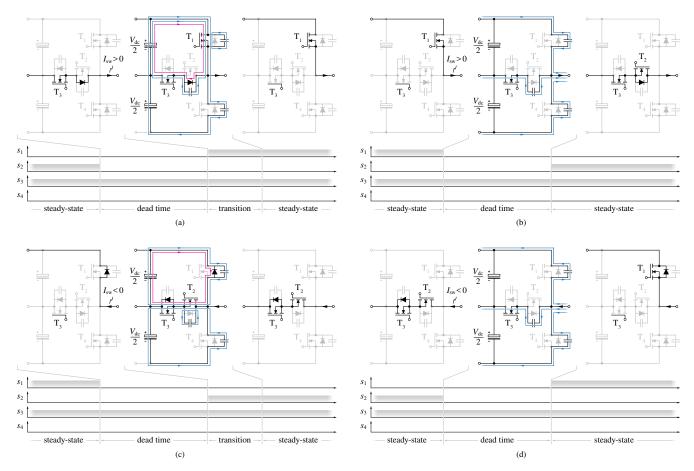

**Figure 1.** Three-level T-type (3LTT) bridge-leg switching transitions involving  $T_1$  and  $T_2$ . Four different events are identified, depending on the switching sequence  $T_1 \leftrightarrow T_2$  and the direction of the bridge-leg output current  $I_{sw}$ . (a)  $T_1 \leftarrow T_2$ ,  $I_{sw} > 0$  (hard-switching event), (b)  $T_1 \rightarrow T_2$ ,  $I_{sw} > 0$  (soft-switching event), (c)  $T_1 \rightarrow T_2$ ,  $I_{sw} < 0$  (hard-switching event), (d)  $T_1 \leftarrow T_2$ ,  $I_{sw} < 0$  (soft-switching event). Blue lines represent the charge/discharge current paths of the semiconductor output capacitances, whereas pink lines indicate the diode reverse-recovery current path. The gate signals of  $T_1$ ,  $T_2$ ,  $T_3$ , and  $T_4$  are qualitatively shown as  $s_1$ ,  $s_2$ ,  $s_3$ , and  $s_4$ , respectively, and the steady-state, dead time, and transition intervals are indicated.

#### 2. Three-Level T-Type Capacitive Loss Analysis

This section provides a detailed analysis of the losses related to the charging/discharging of the semiconductor output capacitances in a 3LTT bridge-leg, as shown in Figure 1. In particular, this analysis focuses only on the upper half of the bridge-leg (i.e.,  $T_1 \leftrightarrow T_2$  switching transitions, cf., Figure 1), since all results can be extended directly to the other bridge-leg half for reasons of symmetry. According to Figure 1, four different switching events can occur, depending on the commutation sequence (i.e.,  $T_1 \to T_2$  or  $T_2 \to T_1$ ) and the direction of the bridge-leg output current  $I_{\rm sw}$ . For each situation, the respective figure shows the steady state before the transition or the dead time interval, the transition interval (only for hard-switching events), and the steady state after the transition.

For example, Figure 1a shows a transition from  $T_2$  to  $T_1$  ( $T_1 \leftarrow T_2$ ) with  $I_{sw} > 0$ . In the initial steady state (not shown), the switching node is connected to the DC-link midpoint via  $T_2$  and  $T_3$ . The dead time interval starts when  $T_2$  turns off. During this interval, the switching node voltage does not change, as the load current flows in  $T_2$ 's body diode until  $T_1$  turns on. This turn-on process dissipates the energy  $E_{oss,T1}$  stored in the output capacitance of  $T_1$ , and causes the indicated current flows to charge the output capacitance of  $T_2$  to  $V_{dc}/2$  and to charge  $T_4$ 's output capacitance from  $V_{dc}/2$  to  $V_{dc}$ . The turn-on process of  $T_1$  also initiates the reverse-recovery process of  $T_2$ 's body diode, which is discussed in

Electronics **2022**, 11, 1686 4 of 10

Section 3. Finally, in the new steady state, the switching node is connected to the positive DC-link rail via  $T_1$ . Since a certain amount of energy is always dissipated during the switching transition (e.g.,  $E_{\text{oss},T1}$ ), this is considered a hard-switching event. Similarly, Figure 1b shows the transition in the opposite direction, i.e., from  $T_1$  to  $T_2$  ( $T_1 \rightarrow T_2$ ) with  $I_{\text{sw}} > 0$ . Once  $T_1$  turns off, the load current charges/discharges the involved output capacitances until the switching node is finally connected to the DC-link midpoint via  $T_3$  and  $T_2$ 's body diode. The turn-on of  $T_2$  at the end of the dead time interval is, thus, lossless, and accordingly, this transition is a soft-switching event. The transitions in Figure 1c,d follow analogous steps.

The indicated charging/discharging currents give rise to losses. To quantify these capacitive switching losses, all four switching events shown in Figure 1 are analyzed using the method reported in [14], which is based on the energy balance expression

$$E_{\text{loss,cap}} = E_{\text{initial}} + E_{\text{source}} - E_{\text{final}} - E_{\text{load}}, \tag{1}$$

where  $E_{\rm initial}$  and  $E_{\rm final}$  are the total stored energies in all device capacitances before and after the commutation, respectively, while  $E_{\rm source}$  and  $E_{\rm load}$  are the energies provided by the DC-link and absorbed by the output load during the transition, respectively. Note that instantaneous switching transitions are assumed (i.e., no *V-I* overlap across the MOSFET channel); hence, no energy is transferred to the load during the hard-switching events (a) and (c) (i.e.,  $E_{\rm load} = 0$ ), whereas no loss is generated during the soft-switching events (b) and (d) (i.e.,  $E_{\rm loss,cap} = 0$ , assuming a sufficient dead time to complete the voltage transition [14]). Therefore, the energy balance terms for the two hard-switching events (a) and (c) are derived as

$$I_{\text{sw}} > 0 : \begin{cases} E_{\text{initial}} = E_{\text{oss,T}_{1}}(V_{\text{dc}}/2) + E_{\text{oss,T}_{4}}(V_{\text{dc}}/2) \\ E_{\text{final}} = E_{\text{oss,T}_{2}}(V_{\text{dc}}/2) + E_{\text{oss,T}_{4}}(V_{\text{dc}}) \\ E_{\text{source}} = Q_{\text{oss,T}_{2}}(V_{\text{dc}}/2) \frac{V_{\text{dc}}}{2} + \left[ Q_{\text{oss,T}_{4}}(V_{\text{dc}}) - Q_{\text{oss,T}_{4}}(V_{\text{dc}}/2) \right] V_{\text{dc}} \end{cases}$$

(2)

$$I_{\text{sw}} < 0 : \begin{cases} E_{\text{initial}} = E_{\text{oss,T}_2}(V_{\text{dc}}/2) + E_{\text{oss,T}_4}(V_{\text{dc}}) \\ E_{\text{final}} = E_{\text{oss,T}_1}(V_{\text{dc}}/2) + E_{\text{oss,T}_4}(V_{\text{dc}}/2) \\ E_{\text{source}} = Q_{\text{oss,T}_1}(V_{\text{dc}}/2) \frac{V_{\text{dc}}}{2} - \left[ Q_{\text{oss,T}_4}(V_{\text{dc}}) - Q_{\text{oss,T}_4}(V_{\text{dc}}/2) \right] \frac{V_{\text{dc}}}{2} \end{cases}$$

(3)

where  $Q_{oss}$  and  $E_{oss}$  refer to the charge and the energy stored in the semiconductor output capacitance  $C_{oss}$ , respectively:

$$Q_{\text{oss}} = \int_{0}^{V_{\text{DS}}} C_{\text{oss}}(v) \, dv, \quad E_{\text{oss}} = \int_{0}^{V_{\text{DS}}} C_{\text{oss}}(v) \, v \, dv.$$

(4)

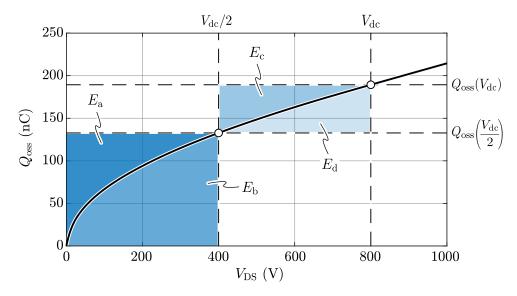

For reasons of clarity and compactness, we define the energy terms

$$E_{\rm a} = E_{\rm oss}(V_{\rm dc}/2),\tag{5}$$

$$E_{\rm b} = Q_{\rm oss}(V_{\rm dc}/2)\frac{V_{\rm dc}}{2} - E_{\rm oss}(V_{\rm dc}/2),$$

(6)

$$E_{\rm c} = [E_{\rm oss}(v_{\rm dc}) - E_{\rm oss}(v_{\rm dc}/2)] - [Q_{\rm oss}(v_{\rm dc}) - Q_{\rm oss}(v_{\rm dc}/2)] \frac{V_{\rm dc}}{2}, \tag{7}$$

$$E_{\rm d} = [Q_{\rm oss}(V_{\rm dc}) - Q_{\rm oss}(V_{\rm dc}/2)]V_{\rm dc} - [E_{\rm oss}(V_{\rm dc}) - E_{\rm oss}(V_{\rm dc}/2)], \tag{8}$$

Electronics **2022**, 11, 1686 5 of 10

which are graphically illustrated in Figure 2 for a Wolfspeed  $1200 \,\mathrm{V}$   $32 \,\mathrm{m}\Omega$  SiC MOS-FET and  $V_{\mathrm{dc}} = 800 \,\mathrm{V}$ . By inserting Equations (2) and (3) in Equation (1) and leveraging Equations (5)–(8), straightforward capacitive loss expressions are obtained:

$$E_{\text{loss,cap}}(I_{\text{sw}} > 0) = E_{\text{a,T}_1} + E_{\text{b,T}_2} + E_{\text{d,T}_4}, \tag{9}$$

$$E_{\text{loss,cap}}(I_{\text{sw}} < 0) = E_{\text{a,T}_2} + E_{\text{b,T}_1} + E_{\text{c,T}_4}. \tag{10}$$

Note that different expressions are obtained for  $I_{\rm sw}>0$  and  $I_{\rm sw}<0$ , as the power semiconductors involved in the respective commutations are different (i.e.,  $T_1 \neq T_2$ ; for example, in a bridge-leg with 800 V DC-link voltage,  $T_1$  is typically a 1200 V MOSFET, whereas  $T_2$  is typically a 650 V MOSFET) and the charging/discharging of  $C_{\rm oss,T_4}$  (i.e., the output capacitance of the third power semiconductor not actively involved in the commutation) is affected by the current direction, as it is *charged* from  $V_{\rm dc}/2$  to  $V_{\rm dc}$  in the hard-switching transition with  $I_{\rm sw}>0$ , shown in Figure 1a, but *discharged* from  $V_{\rm dc}$  to  $V_{\rm dc}/2$  in the hard-switching transition with  $I_{\rm sw}<0$ , shown in Figure 1c.

**Figure 2.** Output charge  $Q_{\rm oss}$  dependence on the drain-source voltage  $V_{\rm DS}$  of the Wolfspeed C3M0032120K 1200 V 32 m $\Omega$  SiC MOSFET, with highlighted capacitive energy components  $E_{\rm a}$ ,  $E_{\rm b}$ ,  $E_{\rm c}$ , and  $E_{\rm d}$ , assuming  $V_{\rm dc} = 800$  V.

# 3. Simplified Hard-Switching Loss Model

The total losses generated by a hard-switching commutation in an arbitrary SiC MOSFET bridge-leg can be expressed as [12]

$$E_{\rm sw} = E_{\rm loss,cap}(V_{\rm sw}, I_{\rm sw}) + Q_{\rm rr}(I_{\rm sw})V_{\rm sw} + \frac{1}{2}\frac{V_{\rm sw}^2}{\frac{\mathrm{d}v}{\mathrm{d}t}}I_{\rm sw} + \frac{1}{2}\frac{I_{\rm sw}^2}{\frac{\mathrm{d}i}{\mathrm{d}t}}V_{\rm sw}, \tag{11}$$

where  $V_{\rm sw}$  and  $I_{\rm sw}$  are the switched voltage and current, respectively,  $E_{\rm loss,cap}$  is the capacitive loss contribution (depending on the switched voltage and the direction of the switched current, cf., Equations (9) and (10) in Section 2, and  $Q_{\rm rr}$  is the reverse-recovery charge of the MOSFET body diode involved in the commutation process (e.g., the body diode of  $T_2$  in Figure 1a and the body diode of  $T_1$  in Figure 1c). The last two terms of Equation (11) represent the V-I overlap losses and depend on the voltage and current time derivatives during the overlap time. It is worth noting that Equation (11) only represents turn-on losses, as the switching losses during the turn-off transition can typically be neglected if the MOSFET is assumed to be turned off fast enough [12].

A simplified switching-loss model, only accounting for the unavoidable charge-related losses [6,11], can be obtained by assuming infinitely fast transitions, such that the *V-I*

Electronics 2022, 11, 1686 6 of 10

overlap loss contributions in Equation (11) can be neglected. This assumption also allows to express the diode reverse-recovery charge as a linear function of the switched current [15]: infinitely fast current transitions force the complete diode forward bias injected charge (which is proportional to the conducted current) to be swept away as  $Q_{\rm rr}$ , because no time is left for charge recombination to take place. Thus, we obtain

$$Q_{\rm rr} \approx \tau |I_{\rm sw}|,$$

(12)

where  $\tau$  is the charge carrier recombination lifetime. Therefore, a simplified linear switching-loss model with respect to the switched current is obtained from Equation (11) as

$$E_{\rm sw} \approx E_{\rm loss,cap}(V_{\rm sw}, I_{\rm sw}) + \tau |I_{\rm sw}| V_{\rm sw}, \tag{13}$$

which represents a theoretical lower limit (as overlap losses are neglected) for hard-switching losses in arbitrary SiC MOSFET bridge-legs.

Remarkably, Equation (13) solely depends on typically available manufacturer datasheet information, since  $E_{\rm loss,cap}$  can be extracted from the  $C_{\rm oss}(v)$  curve (cf., Section 2), and  $\tau$  can be obtained from the reverse-recovery charge data (i.e.,  $Q_{\rm rr}$ ,  $I_{\rm sw}$ ) by inverting Equation (12). In particular, with  $\tau$  being approximately linearly dependent on the semiconductor junction temperature  $T_{\rm j}$  [16], two  $Q_{\rm rr}$  values at different temperatures are sufficient to roughly estimate the reverse-recovery losses for an arbitrary  $T_{\rm j}$ . It is worth noting that datasheet values for  $Q_{\rm rr}$  typically include the semiconductor's  $Q_{\rm oss}(V_{\rm sw})$ , as the bipolar and capacitive charge components are indistinguishable during reverse-recovery charge measurements [17]. Therefore,  $Q_{\rm oss}$  must be first subtracted from datasheet  $Q_{\rm rr}$  values before using them in Equation (12).

#### 4. Experimental Validation

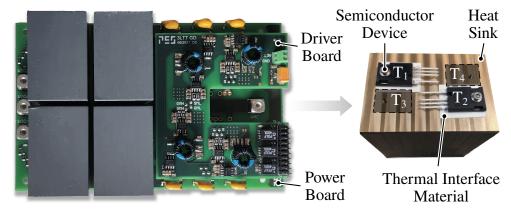

This section aims to validate and assess the accuracy first of the capacitive loss analysis described in Section 2, and then its combination with the simplified hard-switching-loss model proposed in Section 3. We use the 3LTT bridge-leg prototype shown in Figure 3, which employs third-generation  $1200\,V$   $32\,m\Omega$  (for  $T_1,T_4$ ) and  $650\,V$   $25\,m\Omega$  (for  $T_2,T_3$ ) SiC MOSFETs from Wolfspeed in four-pin TO-247-4 packages (i.e., featuring a Kelvin source pin for faster switching). To obtain accurate switching loss results, we employ a transient calorimetric measurement method [18], specifically, the variant presented and validated in [19]. With this approach, the semiconductor devices are mechanically connected and thermally coupled to a brass block acting as a heat sink. By measuring the time required for the brass block temperature to increase by a defined amount (i.e., by  $10\,^{\circ}$ C in the present case), and by subtracting the estimated conduction losses (the on-state resistance of the devices under test is measured for different temperatures during the calibration phase of the calorimetric measurement setup), the semiconductor switching losses can be extracted.

**Figure 3.** Overview of the 3LTTC bridge-leg test board and brass heat sink used for calorimetric loss measurements.

Electronics **2022**, 11, 1686 7 of 10

### 4.1. No-Load Operation ( $I_{sw} = 0$ )

To verify the capacitive loss model described in Section 2, loss measurements at zero output current (i.e., no-load) are performed for different switched voltages (i.e., different DC-link voltages). The no-load operation allows to avoid all current-dependent terms in Equation (11), and thus, to accurately determine the 3LTT bridge-leg capacitive losses, which are defined by the sum of Equations (9) and (10) as

$$E_{\rm sw}(I_{\rm sw}=0) = Q_{\rm oss,T_1}(V_{\rm dc}/2)\frac{V_{\rm dc}}{2} + Q_{\rm oss,T_2}(V_{\rm dc}/2)\frac{V_{\rm dc}}{2} + E_{\rm c,T_4} + E_{\rm d,T_4}.$$

(14)

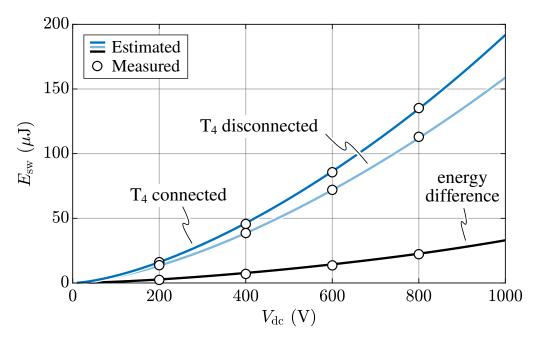

Figure 4 compares the calorimetrically measured no-load losses and the datasheet-based estimations using the proposed capacitive switching-loss model. To quantify the additional capacitive energy contribution  $E_{c,T_4} + E_{d,T_4}$  coming from the presence of a third switch that is not actively involved in the commutation (i.e.,  $T_4$  for the case at hand), two sets of measurements are performed, with  $T_4$  electrically connected or disconnected to the circuit. The results show excellent correspondence between measurements and estimations, supporting the validity of the described capacitive loss model.

**Figure 4.** Comparison between estimated and measured zero output current losses in the 3LTT bridge-leg ( $T_1 = T_4$ : C3M0032120K,  $T_2 = T_3$ : C3M0025065K) as a function of the DC-link voltage  $V_{\rm dc}$ . The results are obtained by switching  $T_1 \leftrightarrow T_2$ : the additional energy loss related to the charging/discharging of  $C_{\rm oss,T_4}$  (i.e.,  $E_{\rm c,T_4} + E_{\rm d,T_4}$ ) is indicated in black. The estimated energy losses take into account the measured parasitic capacitance  $C_\sigma \approx 35\,{\rm pF}$  between the switching node and the DC-link as  $E_\sigma = 2 \cdot 1/2\,C_\sigma V_{\rm sw}^2$ .

## 4.2. Operation under Load ( $I_{sw} > 0$ , $I_{sw} < 0$ )

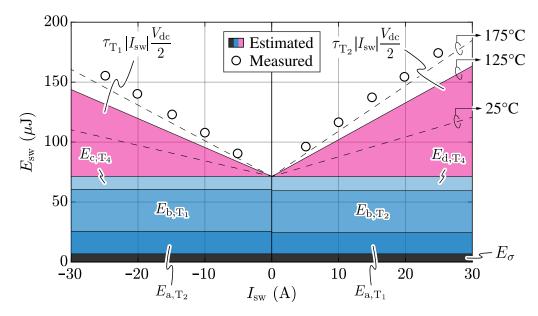

To assess the accuracy of the simplified hard-switching-loss model proposed in Section 3, loss measurements for positive and negative bridge-leg output currents ( $I_{\rm sw}$ , cf., Figure 1) are performed. Due to the temperature dependency of the reverse-recovery time constant  $\tau$ , the bridge-leg duty cycle and switching frequency are adjusted to always achieve an estimated semiconductor junction temperature of around 125 °C ( $\pm 10$  °C). The switching losses are estimated according to the simplified loss model in Equation (13), i.e.,

$$E_{\rm sw}(I_{\rm sw} > 0) = E_{\rm a,T_1} + E_{\rm b,T_2} + E_{\rm d,T_4} + \tau_{\rm T_2} |I_{\rm sw}| \frac{V_{\rm dc}}{2}, \tag{15}$$

Electronics 2022, 11, 1686 8 of 10

$$E_{\rm sw}(I_{\rm sw} < 0) = E_{\rm a,T_2} + E_{\rm b,T_1} + E_{\rm c,T_4} + \tau_{\rm T_1} |I_{\rm sw}| \frac{V_{\rm dc}}{2}.$$

(16)

As the  $Q_{\rm rr}$  information of both the 1200 V and 650 V MOSFETs is only provided at  $T_{\rm j}=175\,^{\circ}{\rm C}$ ; the datasheets belonging to the same semiconductor devices in a different, surface-mount TO-263-7L package are used to extract  $\tau$  at  $T_{\rm j}=25\,^{\circ}{\rm C}$ , enabling a linear interpolation between the  $\tau(T_{\rm j})$  values.

Figure 5 and Table 1 compare the experimental results and the estimations obtained with the proposed datasheet-based switching-loss model for the 3LTTC, whereby Figure 5 also provides a breakdown of the the capacitive loss contributions from Equations (9) or (10), respectively, and of the reverse-recovery losses. Considering its simplicity, the model predicts the measured hard-switching losses well, achieving a maximum underestimation error of 18% in the considered load current range. The model accuracy reduces with increasing  $|I_{\rm Sw}|$ , as the unaccounted-for V-I overlap (caused by the finite dv/dt and di/dt values) increasingly affects the overall losses. The deviation between the measured and estimated losses is, in fact, well reflected by the approximate evaluation of the V-I overlap losses with Equation (11), assuming reasonable values of  $dv/dt \approx 100 \, V/ns$  and  $di/dt \approx 10 \, A/ns$  (i.e., according to measurements and datasheet information). As the switching speeds of next-generation WBG power transistors are expected to show an increasing tendency, driven by the trend towards further integration of power electronic converters and, especially, by integrated gate-drive circuits [20], the accuracy of the proposed loss model is expected to improve further.

**Figure 5.** Comparison between estimated and measured hard-switching losses in the 3LTT bridgeleg ( $T_1 = T_4$ : C3M0032120K,  $T_2 = T_3$ : C3M0025065K) as a function of the switched current  $I_{\rm sw}$  at  $V_{\rm dc} = 800\,{\rm V}$  and  $T_{\rm j} \approx 125\,{\rm ^{\circ}C}$ . The estimated energy losses take into account the measured parasitic capacitance  $C_{\sigma} \approx 35\,{\rm pF} + 50\,{\rm pF}$  (between the switching node and the DC-link, and the winding capacitance of the load inductor), as  $E_{\sigma} = 1/2\,C_{\sigma}V_{\rm sw}^2$ . The estimated losses for  $T_{\rm j} = 25\,{\rm ^{\circ}C}$  and  $T_{\rm j} = 175\,{\rm ^{\circ}C}$  are indicated with dashed lines.

Electronics **2022**, 11, 1686 9 of 10

**Table 1.** Comparison between estimated and measured hard-switching losses in the 3LTT bridge-leg as a function of the switched current  $I_{\rm sw}$  at  $V_{\rm dc}=800\,{\rm V}$  and  $T_{\rm j}\approx125\,{\rm ^{\circ}C}$ . The losses are estimated with (15) for  $I_{\rm sw}>0$  and with (16) for  $I_{\rm sw}<0$ .

| Switched Current | Measured Loss | <b>Estimated Loss</b> | Error  |

|------------------|---------------|-----------------------|--------|

| $-25\mathrm{A}$  | 155.4 μJ      | 128.3 µJ              | -17.5% |

| $-20\mathrm{A}$  | 140.3 µJ      | 116.9 µJ              | -16.7% |

| $-15\mathrm{A}$  | 123.0 µJ      | 105.5 μJ              | -14.2% |

| $-10\mathrm{A}$  | 107.9 μJ      | 94.1 µJ               | -12.7% |

| $-5\mathrm{A}$   | 90.6 μJ       | 82.7 μJ               | -8.6%  |

| +5 A             | 96.3 μJ       | 85.8 μJ               | -10.9% |

| $+10\mathrm{A}$  | 116.6 μJ      | 100.2 μJ              | -14.0% |

| $+15\mathrm{A}$  | 137.3 μJ      | 114.7 μJ              | -16.5% |

| $+20{\rm A}$     | 154.5 μJ      | 129.2 μJ              | -16.4% |

| +25 A            | 174.3 µJ      | 143.6 µJ              | -17.6% |

#### 5. Conclusions

This paper describes a simplified method to estimate the hard-switching losses in SiC-based three-level T-type (3LTT) bridge-legs. Remarkably, the proposed method is applicable to other three-level topologies as well. Neglecting voltage/current overlap losses and considering only charge-related loss components, the proposed approach requires minimal information from datasheets. It can not only account for the capacitive charge/discharge loss caused by the third semiconductor device that is subject to the voltage transient during hard-switching events, but it is also especially applicable to commutations between semiconductor devices with different blocking voltage and/or current ratings. The proposed loss model is verified experimentally by calorimetrically measuring the switching losses of an 800 V DC-link 3LTT bridge-leg prototype employing 1200 V and 650 V SiC MOSFETs. The results show that, with the proposed model, the basic semiconductor information provided in the datasheet are sufficient to predict the switching losses of the 3LTT with reasonable accuracy, resulting in a maximum underestimation error of 18% with respect to calorimetric measurements.

Whereas a certain loss underestimation must be expected due to not considering the overlap losses (whose importance reduces with increasing switching speeds enabled by future integrated gate drivers), it is worth highlighting that the estimation accuracy strongly depends on the quality of the  $Q_{\rm rr}$  information provided by the semiconductor device manufacturers in their datasheets. Unfortunately, this information is often unreliable (e.g., possibly including unwanted high-frequency ringing effects [17]) and/or is only provided for one operating point (i.e., a single combination of  $I_{\rm sw}$ ,  $T_{\rm j}$ ,  $^{\rm di}/_{\rm dt}$ ). Therefore, better  $Q_{\rm rr}$  data quality, considering, for instance, the measurement procedure proposed in [17], and the availability of more data points in datasheets could further improve the accuracy of the proposed straightforward modeling approach for hard-switching losses in 3LTT (and other three-level) bridge-legs.

**Author Contributions:** Conceptualization, D.C., C.G., J.H. and J.W.K.; methodology, D.C. and C.G.; software, D.C.; validation, D.C. and J.H.; formal analysis, D.C. and C.G.; investigation, D.C. and J.H.; resources, J.H. and J.W.K.; data curation, D.C. and J.H.; writing—original draft preparation, D.C. and J.H.; writing—review and editing, D.C., C.G., J.H., R.B. and J.W.K.; visualization, D.C.; supervision, J.H. and J.W.K.; project administration, J.H. and J.W.K.; funding acquisition, R.B. and J.W.K. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

**Conflicts of Interest:** The authors declare no conflict of interest.

Electronics **2022**, 11, 1686

#### References

1. Teichmann, R.; Bernet, S. A Comparison of Three-Level Converters Versus Two-Level Converters for Low-Voltage Drives, Traction, and Utility Applications. *IEEE Trans. Ind. Appl.* **2005**, *41*, 855–865. [CrossRef]

- 2. Schweizer, M.; Friedli, T.; Kolar, J.W. Comparative Evaluation of Advanced Three-Phase Three-Level Inverter/Converter Topologies against Two-Level Systems. *IEEE Trans. Ind. Electron.* **2013**, *60*, 5515–5527. [CrossRef]

- 3. Gurpinar, E.; Castellazzi, A. Single-Phase T-Type Inverter Performance Benchmark Using Si IGBTs, SiC MOSFETs, and GaN HEMTs. *IEEE Trans. Power Electron.* **2016**, *31*, 7148–7160. [CrossRef]

- 4. Satpathy, S.; Bhattacharya, S.; Veliadis, V. Comprehensive Loss Analysis of Two-level and Three-Level Inverter for Electric Vehicle Using Drive Cycle Models. In Proceedings of the IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 2017–2024. [CrossRef]

- 5. Holtz, J. Selbstgeführter Wechselrichter. German Patent 2 339 034 C2, 5 January 1983. (In German)

- Cittanti, D.; Guacci, M.; Mirić, S.; Bojoi, R.; Kolar, J.W. Comparative Evaluation of 800V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives. In Proceedings of the 2020 23rd International Conference on Electrical Machines and Systems (ICEMS), Hamamatsu, Japan, 24–27 November 2020; pp. 1699–1704. [CrossRef]

- 7. Baker, R.H. Bridge Converter Circuit. U.S. Patent 4270 163 A, 26 May 1981.

- 8. Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. *IEEE Trans. Ind. Appl.* **1981**, *IA-17*, 518–523. [CrossRef]

- Bruckner, T.; Bemet, S. Loss Balancing in Three-Level Voltage Source Inverters Applying Active NPC Switches. In Proceedings of the 2001 IEEE 32nd Annual Power Electronics Specialists Conference (IEEE Cat. No. 01CH37230), Vancouver, BC, Canada, 17–21 June 2001; Volume 2, pp. 1135–1140. [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [CrossRef]

- 11. Gammeter, C. Multi-Objective Optimization of Power Electronics and Generators of Airborne Wind Turbines. Ph.D. Thesis, ETH Zurich, Zurich, Switzerland, 2017. [CrossRef]

- 12. Deboy, G.; Haeberlen, O.; Treu, M. Perspective of Loss Mechanisms for Silicon and Wide Band-Gap Power Devices. *CPSS Trans. Power Electron. Appl.* **2017**, 2, 89–100. [CrossRef]

- 13. Liu, B.; Ren, R.; Jones, E.A.; Gui, H.; Zhang, Z.; Chen, R.; Wang, F.; Costinett, D. Effects of Junction Capacitances and Commutation Loops Associated With Line-Frequency Devices in Three-Level AC/DC Converters. *IEEE Trans. Power Electron.* **2019**, 34, 6155–6170. [CrossRef]

- 14. Kasper, M.; Burkart, R.M.; Deboy, G.; Kolar, J.W. ZVS of Power MOSFETs Revisited. *IEEE Trans. Power Electron.* **2016**, 31, 8063–8067. [CrossRef]

- 15. Lauritzen, P.; Ma, C. A Simple Diode Model with Reverse Recovery. IEEE Trans. Power Electron. 1991, 6, 188–191. [CrossRef]

- 16. Nayak, D.; Yakala, R.K.; Kumar, M.; Pramanick, S. Temperature Dependent Reverse Recovery Characterization of SiC MOSFETs Body Diode for Switching Loss Estimation In a Half-Bridge. *IEEE Trans. Power Electron.* **2022**, *37*, 5574–5582. [CrossRef]

- 17. Sochor, P.; Huerner, A.; Hell, M.; Elpelt, R. Understanding the Turn-off Behavior of SiC MOSFET Body Diodes in Fast Switching Applications. In Proceedings of the PCIM Europe digital days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Online, 3–7 May 2021; pp. 290–297.

- Hoffmann, L.; Gautier, C.; Lefebvre, S.; Costa, F. Optimization of the Driver of GaN Power Transistors Through Measurement of Their Thermal Behavior. IEEE Trans. Power Electron. 2014, 29, 2359–2366. [CrossRef]

- Rothmund, D.; Bortis, D.; Kolar, J.W. Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10-kV SiC MOSFETs and Diodes. IEEE Trans. Power Electron. 2018, 33, 5240–5250. [CrossRef]

- Mantooth, H.A.; Glover, M.D.; Shepherd, P. Wide Bandgap Technologies and Their Implications on Miniaturizing Power Electronic Systems. IEEE Trans. Emerg. Sel. Top. Power Electron. 2014, 2, 374

–385. [CrossRef]