Doctoral Dissertation Doctoral Program in Electronics and Telecommunications engineering (34<sup>th</sup>cycle)

# FPGA Acceleration of Domain-specific Kernels via High-Level Synthesis

By

### Mohammad Amir Mansoori

\*\*\*\*\*

#### Supervisor(s):

Prof. Mario R. Casu

**Doctoral Examination Committee:** Prof. Christian Pilato , Referee, Politecnico di Milano Prof. Ioannis Sourdis, Referee, Chalmers University of Technology

> Politecnico di Torino 2022

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Mohammad Amir Mansoori 2022

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my niece, Gandom, who is 4 years old at this time. I do so to show my endless love to her and to see her happiness and smiley face.

### Acknowledgements

And I would like to thank my supervisor, Prof. Mario R. Casu, for his continuous support, guidance, and patience throughout my PhD project. I would also like to acknowledge the support from Prof. Luciano Lavagno for all his invaluable advice. In addition, I acknowledge the financial support provided by the EMERALD project (Grant Agreement No. 764479) and Prof. Francesca Vipiana as the project coordinator.

#### Abstract

Compute-demanding algorithms in today's applications need to achieve high performance, which is becoming more difficult in general-purpose processors due to the decline of the Moore's law. Domain-specific hardware accelerators can assist general-purpose processors in improving the performance and efficiency while preserving the flexibility. They can accelerate a *domain* of applications rather than a single application making it possible to use the efficient specialized hardware acceleration techniques in a broad range of applications.

In this thesis, we focus on the development of Domain-Specific Accelerators (DSAs) for a broad domain of applications consisting of *biomedical microwave algorithms* and *Machine Learning (ML) techniques*. Although the initial purpose of this research was the development of a biomedical Microwave Imaging (MI) system, The hardware acceleration methods introduced in this thesis are not limited to MI only. We analyzed the recurrent algorithms that are used in these applications to extract their compute-intensive parts that are termed *kernels*. Then we proposed efficient accelerators for these domain-specific kernels to achieve high performance.

The main computational kernels that are considered in this work are *Finite Difference Time Domain (FDTD)*, *Principal Component Analysis (PCA)*, *Support Vector Machine (SVM)*, and *Artificial Neural Networks (ANNs)* including *Multi-Layer Perceptron (MLP)* and *Convolutional Neural Networks (CNNs)*. For each kernel, we proposed highly efficient hardware accelerators to obtain an optimal performance by considering several factors such as processing time, resource usage, and power consumption. The target hardware platform is Field Programmable Gate Arrays (FPGAs) and the hardware design approach is High Level Synthesis (HLS) which is used to convert a software code written in C or C++ into its corresponding hardware description language. Although several FPGA accelerators have already been presented for the above-mentioned kernels, they have some drawbacks and

limitations. Our proposed design methodologies try to address and overcome these limitations.

The proposed hardware accelerator for 3D FDTD considers the impact of polarization currents in dispersive materials, and models the absorbing boundary conditions as Convolutional Perfectly Matched Layers (CPML) in all directions, as opposed to the conventional FDTD accelerators. We use spatial blocking to store a partial block of data while processing the previous block. Local storage of FDTD coefficients and boundary elements, function inlining, and merging the parallel loops are among the other optimization techniques.

The PCA hardware accelerator considered in this work is implemented in FPGA and is designed entirely in HLS. A new block-streaming method is introduced to make the internal PCA computations more efficient. The flexibility of our design allows us to use it for different FPGA targets, with flexible input data dimensions, and it also lets us easily switch from a more accurate floating-point implementation to a higher speed fixed-point solution.

To implement a fast and accurate Support Vector Machine (SVM) classifiers in embedded systems, we propose a flexible FPGA-based SVM accelerator highly optimized through a dataflow architecture. Thanks to HLS and the dataflow method, our design is scalable and can be used for large data dimensions when there is limited on-chip memory. The hardware parallelism is adjustable and can be specified according to the available FPGA resources. The performance of different SVM kernels is evaluated in hardware. In addition, an efficient fixed-point implementation is proposed to improve the speed.

The last computational kernel considered in this thesis is related to the Neural Networks. Although there are some tools available to generate a hardware design from a high level description of the network (like hls4ml), the selection of network parameters and hardware configurations at the same time is not a trivial task. Although several works have recently addressed the problem of performance co-optimization for hardware and network training, most of them considered either a fixed network or a given hardware architecture. In this work, we propose a new framework for joint optimization of network architecture and hardware configurations, which is based on Bayesian Optimization (BO) on top of HLS. We evaluate our methodology on a network optimized for an FPGA target and show the efficiency of the Pareto set obtained by the proposed joint-optimization approach.

## Contents

| Li | st of l | Figures |                                                         | xi  |

|----|---------|---------|---------------------------------------------------------|-----|

| Li | st of [ | Fables  |                                                         | xvi |

| 1  | Intr    | oductio | n                                                       | 1   |

|    | 1.1     | Motiva  | ation and Problem Statement                             | 3   |

|    | 1.2     | Comp    | ute-Intensive Kernels                                   | 3   |

|    |         | 1.2.1   | 3D FDTD                                                 | 4   |

|    |         | 1.2.2   | PCA using SVD/EVD                                       | 5   |

|    |         | 1.2.3   | SVM                                                     | 6   |

|    |         | 1.2.4   | Neural Networks                                         | 6   |

|    | 1.3     | Challe  | enges in Designing Domain-Specific Accelerators         | 7   |

|    | 1.4     | Scope   | and Outline                                             | 9   |

| 2  | Bac     | kgroun  | d                                                       | 12  |

|    | 2.1     | Perfor  | mance Analysis of Domain-Specific Accelerators          | 12  |

|    | 2.2     | High I  | Level Synthesis for the Design of Hardware Accelerators | 14  |

|    |         | 2.2.1   | Design Optimizations in HLS                             | 15  |

|    |         | 2.2.2   | HLS Design Trends in Selected Domains                   | 17  |

|    | 2.3     | Applic  | cations of Domain-Specific Accelerators                 | 17  |

|    |         | 2.3.1   | Biomedical Microwave Techniques                         | 18  |

|   |     | 2.3.2  | Machine Learning (ML)                                        | 21 |

|---|-----|--------|--------------------------------------------------------------|----|

|   | 2.4 | Microv | wave Imaging Algorithms                                      | 24 |

|   |     | 2.4.1  | Inverse Scattering Problem                                   | 24 |

|   |     | 2.4.2  | Qualitative Imaging                                          | 27 |

|   |     | 2.4.3  | Quantitative Imaging                                         | 27 |

|   | 2.5 | Machi  | ne Learning Algorithms                                       | 28 |

|   |     | 2.5.1  | Preprocessing                                                | 29 |

|   |     | 2.5.2  | Feature Extraction                                           | 29 |

|   |     | 2.5.3  | Classification                                               | 29 |

| 3 | FPG | A Acce | leration of 3D FDTD for Microwave Imaging using HLS          | 31 |

|   | 3.1 | Relate | d Work                                                       | 34 |

|   | 3.2 | FDTD   | in Microwave Imaging                                         | 36 |

|   |     | 3.2.1  | Background                                                   | 36 |

|   |     | 3.2.2  | Boundary Conditions: CPML                                    | 37 |

|   |     | 3.2.3  | FDTD Pseudo-Code                                             | 38 |

|   | 3.3 | FPGA   | Design of an FDTD Compute Unit                               | 40 |

|   |     | 3.3.1  | Two Architectures: Large and Small                           | 42 |

|   |     | 3.3.2  | Blocking Method and Merging of $J_P$ Update Equations        | 44 |

|   |     | 3.3.3  | Loop Merge and Local Storage for Boundaries                  | 46 |

|   |     | 3.3.4  | Loop Pipeline, Function Inline, and Storage for Coefficients | 48 |

|   | 3.4 | Multi- | FPGA Implementation                                          | 49 |

|   | 3.5 | Result | S                                                            | 51 |

|   |     | 3.5.1  | Impact of HLS Optimizations on Performance                   | 52 |

|   |     | 3.5.2  | FDTD Performance on a Single FPGA                            | 54 |

|   |     | 3.5.3  | FDTD Performance on Multiple FPGAs                           | 60 |

|   | 3.6 | Discus | sion                                                         | 65 |

|   | 3.7  | Conclu  | usions                                                                 | 67       |

|---|------|---------|------------------------------------------------------------------------|----------|

| 4 | Higl | h Level | Design of a Flexible PCA Hardware Accelerator                          | 69       |

|   | 4.1  | PCA A   | Algorithm Description                                                  | 72       |

|   | 4.2  | Hyper   | spectral Imaging                                                       | 74       |

|   | 4.3  | PCA H   | Hardware Accelerator Design                                            | 74       |

|   |      | 4.3.1   | Block-Streaming for Covariance Computation                             | 76       |

|   |      | 4.3.2   | High Level Synthesis Optimizations                                     | 79       |

|   |      | 4.3.3   | Fixed-Point Design of the Accelerator                                  | 84       |

|   |      | 4.3.4   | Hardware Prototype for PCA Accelerator Assessment with the HI Data Set | 85       |

|   | 4.4  | Result  | s                                                                      | 87       |

|   |      | 4.4.1   | Number of Blocks, Bands, and Pixels                                    | 88       |

|   |      | 4.4.2   | Fixed-Point and Floating-Point Comparison                              | 90       |

|   |      | 4.4.3   | Evaluation on Hyperspectral Images                                     | 92       |

|   |      | 4.4.4   | Evaluation on Microwave Data                                           | 98       |

|   | 4.5  | Conclu  | usions                                                                 | 98       |

| 5 | HLS  |         | Dataflow Hardware Architecture for Support Vector Ma                   | -<br>100 |

|   | 5.1  | SVM ]   | Background                                                             | 102      |

|   | 5.2  | Propos  | sed SVM Accelerator                                                    | 103      |

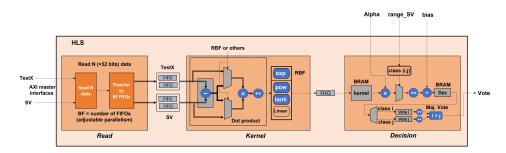

|   |      | 5.2.1   | Read SVM Inputs                                                        |          |

|   |      | 5.2.2   | Kernel Computation                                                     |          |

|   |      | 5.2.3   | Decision Function                                                      | 107      |

|   |      | 5.2.4   | Fixed-Point Implementation                                             |          |

|   | 5.3  | Result  | s                                                                      |          |

|   |      | 5.3.1   | Microwave Data Set                                                     |          |

|    | 5.4         | Conclu   | usions                                                       | . 111      |

|----|-------------|----------|--------------------------------------------------------------|------------|

| 6  | Har<br>erat |          | Design and Optimization of Neural Networks and ML Acce       | el-<br>112 |

|    | 6.1         | Relate   | d Work                                                       | . 113      |

|    | 6.2         | Multi-   | objective Framework for Training and Hardware Co-optimizatio | n115       |

|    |             | 6.2.1    | Multi-Objective BO with Constraints (MOBOC)                  | . 115      |

|    |             | 6.2.2    | Search Space                                                 | . 116      |

|    |             | 6.2.3    | Function Evaluations                                         | . 117      |

|    |             | 6.2.4    | Objectives and Constraints Extraction                        | . 117      |

|    |             | 6.2.5    | Update Bayesian model                                        | . 117      |

|    | 6.3         | Evalua   | tion on Neural Networks                                      | . 117      |

|    |             | 6.3.1    | Multi-Layer Perceptron (MLP)                                 | . 117      |

|    |             | 6.3.2    | Convolutional Neural Networks (CNN)                          | . 119      |

|    |             | 6.3.3    | MLP in Microwave Data Set                                    | . 122      |

|    | 6.4         | Conclu   | usions                                                       | . 124      |

| 7  | Con         | clusions | s and Future Work                                            | 125        |

|    | 7.1         | Conclu   | usions                                                       | . 125      |

|    |             | 7.1.1    | List of Published Papers                                     | . 128      |

|    | 7.2         | Future   | Work                                                         | . 129      |

| Re | feren       | ces      |                                                              | 132        |

| Ар | pend        | ix A L   | ist of Acronyms                                              | 145        |

X

# **List of Figures**

| 1.1  | Propagation of electromagnetic fields and the impact of variations in electric and magnetic fields.                                                            | 4  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | PCA for dimensionality reduction to remove redundant information.                                                                                              | 5  |

| 1.3  | SVM for binary classification finds the decision boundary with max-<br>imum margin between two classes (L2).                                                   | 6  |

| 1.4  | Network structure for a) MLP and b) CNN                                                                                                                        | 7  |

| 2.1  | Various design metrics in the implementation of a hardware accelerator                                                                                         | 14 |

| 2.2  | Hardware design flow in Vivado                                                                                                                                 | 15 |

| 2.3  | Hardware optimization directives                                                                                                                               | 16 |

| 2.4  | General diagram of a Microwave Imaging system                                                                                                                  | 19 |

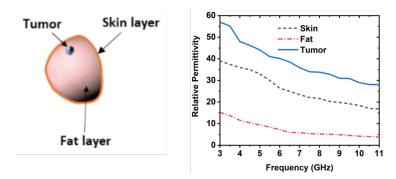

| 2.5  | Dielectric properties of breast tissues                                                                                                                        | 20 |

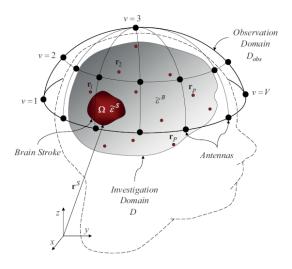

| 2.6  | Brain stroke detection with MI system containing V antennas and P candidate locations for the stroke positions $(r_1 \text{ to } r_P) \dots \dots \dots \dots$ | 21 |

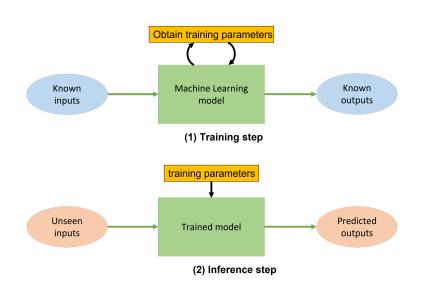

| 2.7  | Machine Learning training and inference steps.                                                                                                                 | 22 |

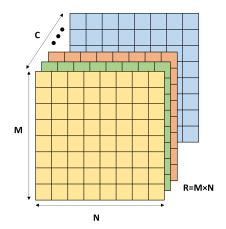

| 2.8  | Hyper-spectral Images (HI) with <i>C</i> bands. Each band has $R = M \times N$ pixels.                                                                         | 23 |

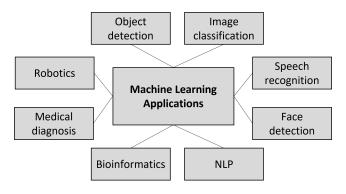

| 2.9  | Machine Learning Applications.                                                                                                                                 | 23 |

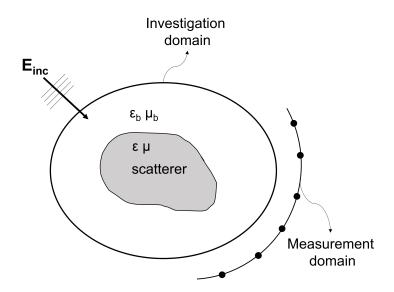

| 2.10 | Microwave Imaging setup. Inverse scattering is the problem of find-<br>ing $\varepsilon$ and $\mu$ from the microwave measurements in the measurement          | 25 |

|      | domain                                                                                                                                                         | 25 |

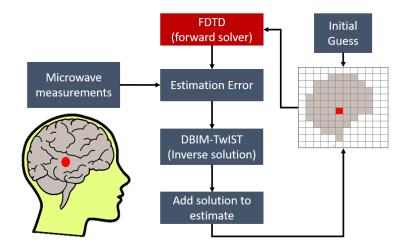

| 2.11 | General diagram of a non-linear image reconstruction iterative algo-<br>rithm in MI, with the compute-intensive FDTD step.                                                                                                                                   | 28 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

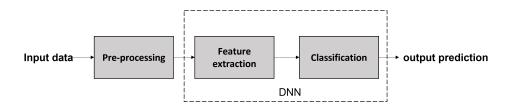

| 2.12 | Three data processing steps in Machine Learning. Note that in DNNs, feature extraction and classification are implemented in different layers of the network.                                                                                                | 29 |

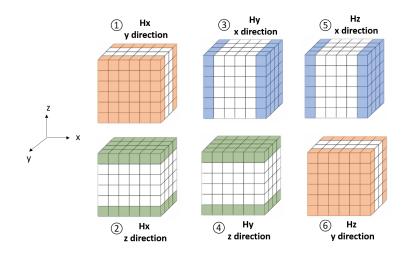

| 3.1  | Boundary regions for <i>H</i> field in 3D FDTD                                                                                                                                                                                                               | 38 |

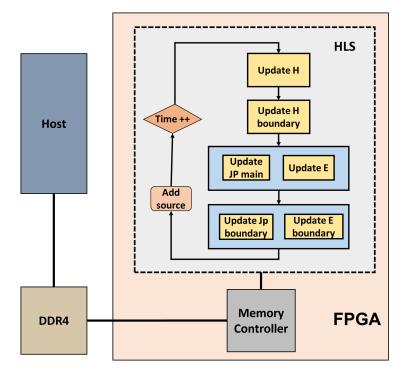

| 3.2  | FDTD CU design in HLS for a single FPGA.                                                                                                                                                                                                                     | 41 |

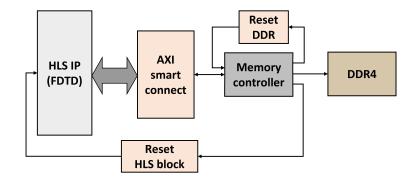

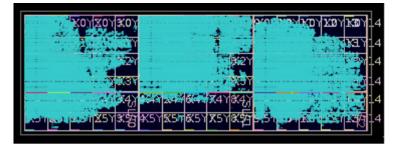

| 3.3  | Detailed view of the CU design in Vivado                                                                                                                                                                                                                     | 42 |

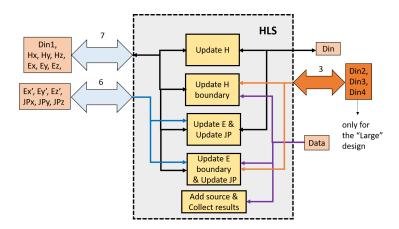

| 3.4  | Details of the interfaces of the CU for Small and Large designs                                                                                                                                                                                              | 43 |

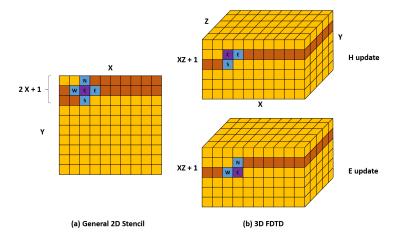

| 3.5  | Blocking method for FDTD and its difference with a general stencil                                                                                                                                                                                           | 45 |

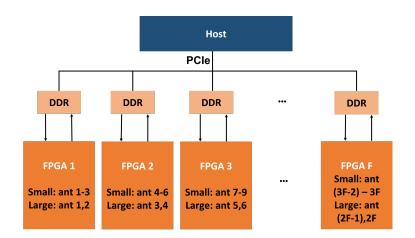

| 3.6  | Multi-FPGA platform with $F$ FPGAs for 3D FDTD acceleration                                                                                                                                                                                                  | 50 |

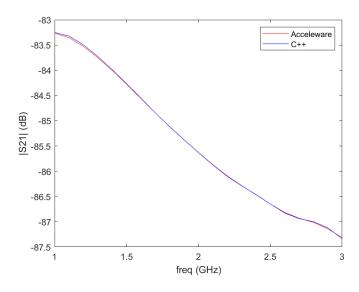

| 3.7  | Accuracy comparison: Acceleware design versus our C++ code                                                                                                                                                                                                   | 51 |

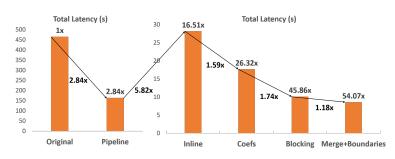

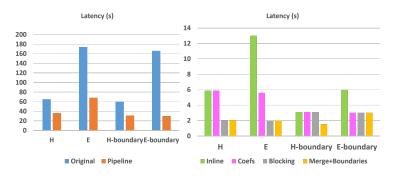

| 3.8  | Impact of different HLS optimization methods on the total latency.<br>(numbers on top of the bars show the improvement compared to the<br>original code, and numbers bellow the arrows show the improvement<br>compared to the previous optimization method) | 52 |

| 3.9  | Impact of different HLS optimization methods on the latency of eachFDTD function.                                                                                                                                                                            | 53 |

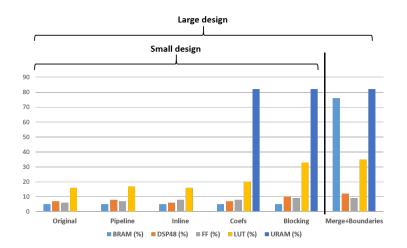

| 3.10 | Impact of HLS optimization methods on resource usage per SLR.                                                                                                                                                                                                | 54 |

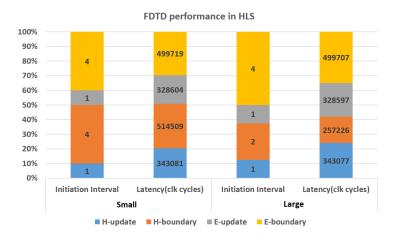

| 3.11 | The performance of the main FDTD loops in Small and Large design in HLS.                                                                                                                                                                                     | 55 |

| 3.12 | Device view in a) Small and b) Large design after place-and-route (it contains 3 SLRs in the left, middle and right side of the FPGA).                                                                                                                       | 57 |

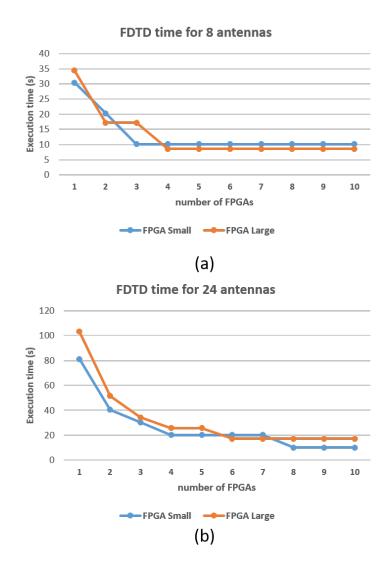

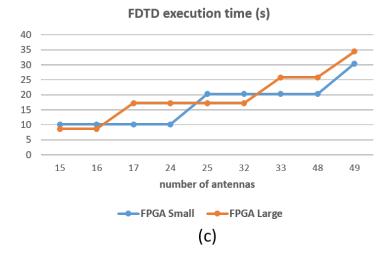

| 3.13 | FDTD execution time for different number of FPGAs, (a) 8 antennas, (b) 24 antennas.                                                                                                                                                                          | 62 |

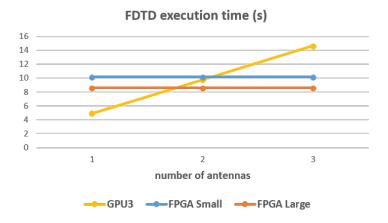

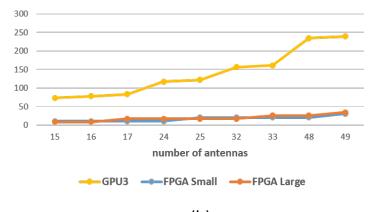

| 3.14 | FDTD execution time for 8 FPGAs and different number of antennas,<br>(a) from one antenna up to the maximum number in a single FPGA<br>(3 for Small design), (b) Comparison of the single GPU in this work<br>(GPU3, highly optimized for one antenna) and multi-FPGA design<br>for multiple antennas, (c) more detailed view of multi-FPGA design |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | results                                                                                                                                                                                                                                                                                                                                            | 64 |

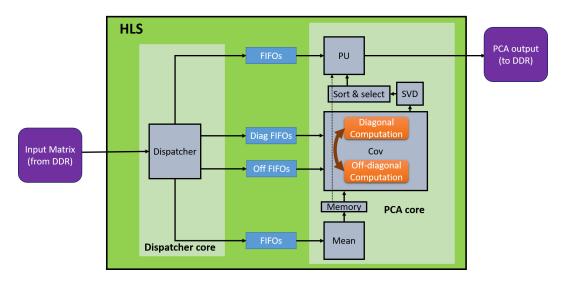

| 4.1  | Architecture of the proposed hardware accelerator for Principal<br>Component Analysis (PCA) in Field-Programmable Gate Arrays<br>(FPGA).                                                                                                                                                                                                           | 75 |

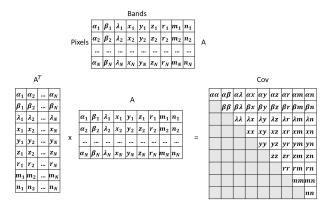

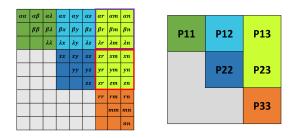

| 4.2  | Example of covariance computation with 9 bands and N pixels, $PQ = \Sigma_{i=1}^{N} P_i \times Q_i$ , where $P, Q$ are the symbols of bands ( $\alpha$ to $n$ )                                                                                                                                                                                    | 76 |

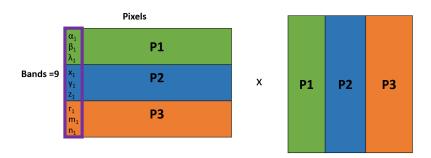

| 4.3  | Example of partitioning of input data into blocks. The total number of bands is $B = 9$ and the block size is $B_{max} = 3$                                                                                                                                                                                                                        | 77 |

| 4.4  | Illustration of an example of covariance computation using the block-<br>streaming method with 3 blocks ( $B = 9, B_{max} = 3$ )                                                                                                                                                                                                                   | 77 |

| 4.5  | Block-streaming method with 4 blocks $(B/B_{max} = 4)$                                                                                                                                                                                                                                                                                             | 78 |

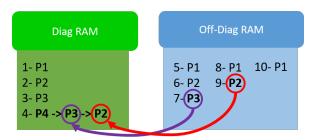

| 4.6  | Order of data storage in the Diagonal and Off-diagonal RAMs inside the Cov unit.                                                                                                                                                                                                                                                                   | 79 |

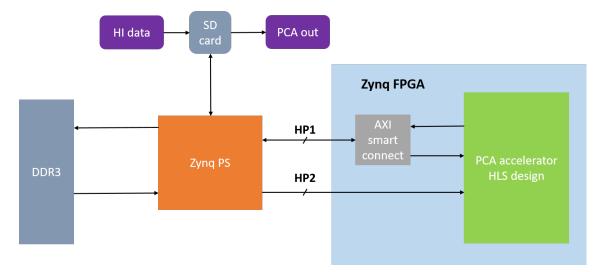

| 4.7  | PCA accelerator design in Zedboard                                                                                                                                                                                                                                                                                                                 | 86 |

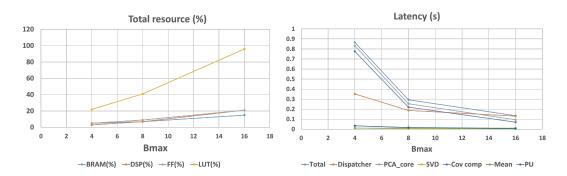

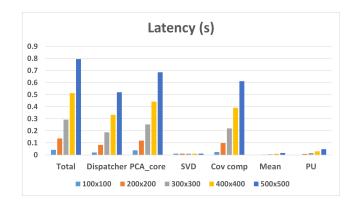

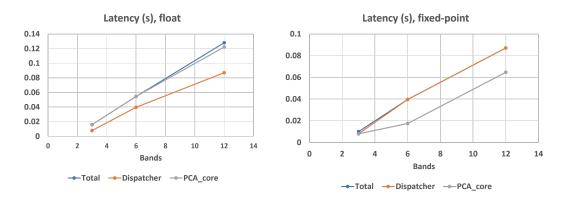

| 4.8  | Impact of block size $(B_{max})$ on the resource usage and latency for the Virtex7, bands = 48, pixels = $300 \times 300$ , floating-point design.                                                                                                                                                                                                 | 88 |

| 4.9  | Impact of the number of pixels on the latency for Virtex7, bands=48,<br>$B_{max} = 8$ , floating-point design                                                                                                                                                                                                                                      | 89 |

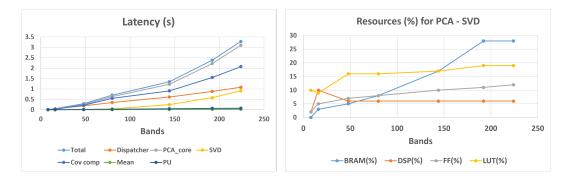

| 4.10 | Latency and resource usage for Virtex7 with a fixed block size $(B_{max} = 8)$ , floating-point design                                                                                                                                                                                                                                             | 89 |

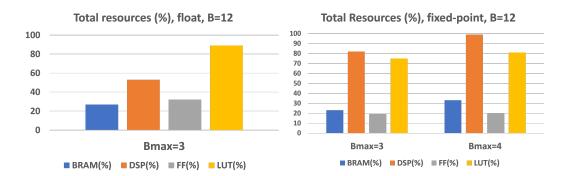

| 4.11 | Resource usage for Zedboard for fixed- and floating-point design, $B = 12$ , pixels = $300 \times 300$ .                                                                                                                                                                                                                                           | 90 |

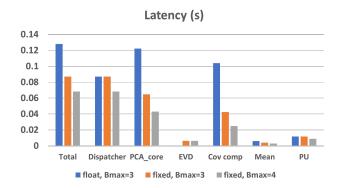

| 4.12 | Comparison of the latency of the fixed- and floating-point design for Zedboard, $B = 12$ , pixels = $300 \times 300$                                                                                                                                                                                                                               | 91 |

| 4.13 | Latency for Zynq7000 with a fixed block size ( $B_{max} = 3$ ), pixels = $300 \times 30092$                                                                                                                                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.14 | Resource usage for Zynq7000 with a fixed block size ( $B_{max} = 3$ ),<br>pixels=300 × 300                                                                                                                                           |

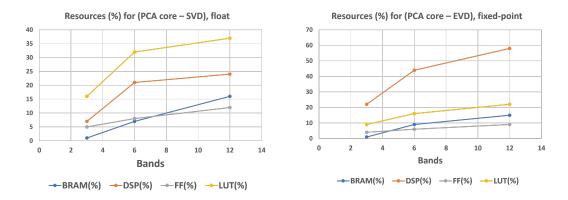

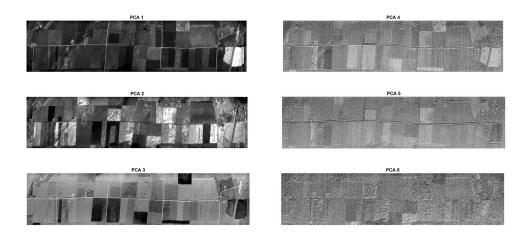

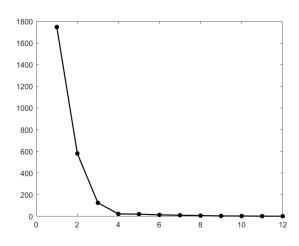

| 4.15 | The first 6 principal components of the HI data set. Our PCA accelerator in Zedboard produces the first 3 outputs (PCA1 to PCA3) 95                                                                                                  |

| 4.16 | Energy distribution of the eigenvalues for the Hyperspectral Imaging (HI) data set                                                                                                                                                   |

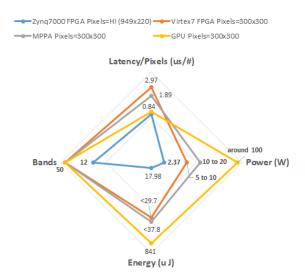

| 4.17 | Comparison of different hardware platforms between latency per pixel, power consumption, input size (bands) and energy 97                                                                                                            |

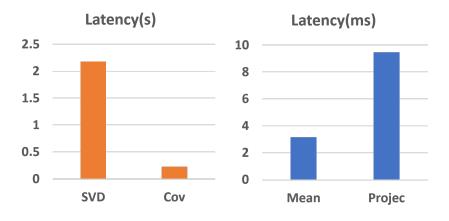

| 4.18 | Processing time for PCA compute units in FPGA with Microwave dataset                                                                                                                                                                 |

| 5.1  | SVM classification with linear kernel                                                                                                                                                                                                |

| 5.2  | Proposed SVM accelerator in HLS                                                                                                                                                                                                      |

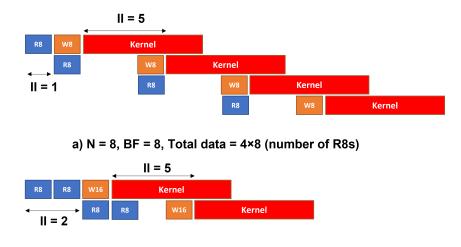

| 5.3  | Impact of the number of FIFO channels ( <i>BF</i> ) with a total of $4 \times 8 =$ 32 data, (a) $BF = N$ , (b) $BF = 2N$ , overall latency is reduced 105                                                                            |

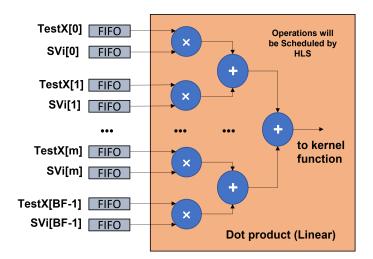

| 5.4  | Manual unrolling for kernel computation                                                                                                                                                                                              |

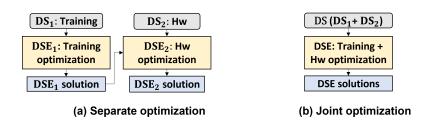

| 6.1  | Optimization of training hyper-parameters and hardware configura-<br>tions: (a) traditional separate DSE, (b) more efficient joint DSE. $DS_1$<br>and $DS_2$ stand for Design Space of training and hardware design,<br>respectively |

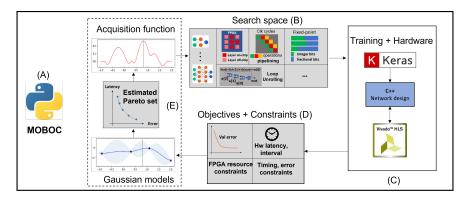

| 6.2  | Proposed methodology for training and hardware co-optimization in FPGA devices                                                                                                                                                       |

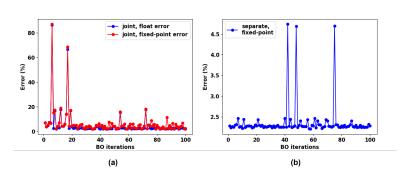

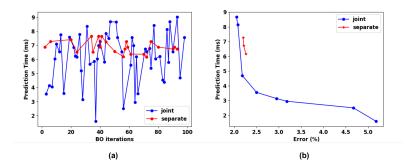

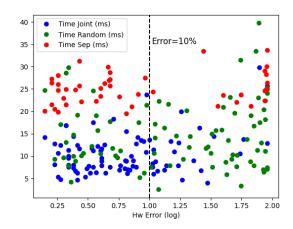

| 6.3  | Percentage of training error (float error) and hardware error (fixed-<br>point error) in each BO iteration, (a) proposed joint optimization, (b)<br>separate optimization                                                            |

| 6.4  | Comparison of (a) prediction time and (b) Pareto fronts                                                                                                                                                                              |

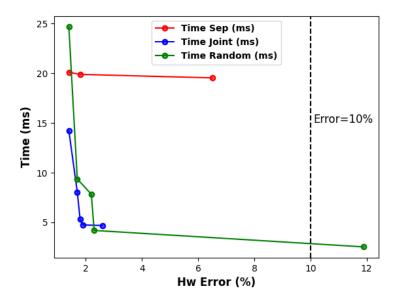

| 6.5 | Pareto-points found by the joint approach, random search, and con-    |

|-----|-----------------------------------------------------------------------|

|     | ventional separate method in the space of prediction error (Hw error) |

|     | and execution latency (Time). Total number of iterations is 100 for   |

|     | all methods                                                           |

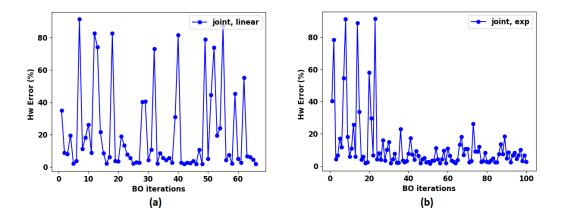

| 6.6 | Hardware error in our joint method in each BO iteration with (a)      |

|     | linear and (b) exponential error function                             |

| 6.7 | Total points suggested by the joint, separate, and random search      |

|     | methods; note the concentration of the joint method on low errors     |

|     | (< 10%)                                                               |

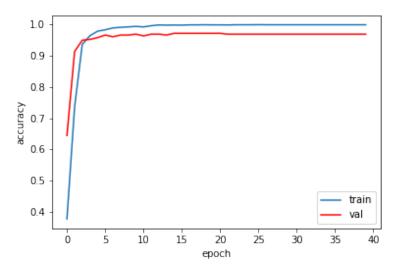

| 6.8 | Accuracy of MLP during training by MI dataset                         |

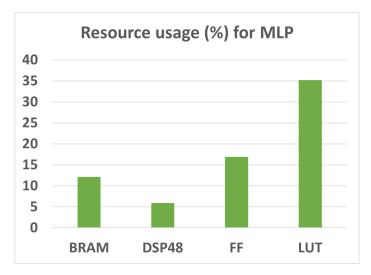

| 6.9 | Resource usage for MLP in Zynq FPGA                                   |

## **List of Tables**

| 1.1 | Domain-specific kernels (rows) and their applications (columns)                                                                                                                               | 4  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | HLS hardware optimization strategies for a FDTD CU                                                                                                                                            | 41 |

| 3.2 | Description of AXI interfaces.                                                                                                                                                                | 44 |

| 3.3 | Resource usage for the Small design: HLS estimation and Vivado implementation results                                                                                                         | 58 |

| 3.4 | Resource usage for the Large design: HLS estimation and Vivado implementation results                                                                                                         | 59 |

| 3.5 | Performance comparison: CPU = Intel Xeon, GPU1 = Tesla K20C<br>GPU2 = Tesla P40, GPU3 = GPU1 CUDA implementation, and<br>FPGA (UltraScale+). TDP = Thermal Design Power, Energy =<br>TDP×Time | 61 |

| 3.6 | Performance comparison between our single Small FPGA design and other FPGA implementations.                                                                                                   | 61 |

| 3.7 | Dimensions of FDTD coefficients.                                                                                                                                                              | 63 |

| 4.1 | Resource usage obtained from HLS for HI data set on Zedboard,<br>bands = 12                                                                                                                   | 93 |

| 4.2 | Latency (ms) for Zedboard, HI data set, bands = 12                                                                                                                                            | 93 |

| 4.3 | Vivado implementation of PCA accelerator on Zedboard for HI data,<br>bands=12, accuracy is compared with MATLAB.                                                                              | 94 |

| 4.4 | Comparison of our PCA accelerator with other conventional methods.<br>The input data dimensions are set to $30 \times 16$ for all designs                                                     | 95 |

| 4.5 | Comparison of the proposed PCA hardware design with other High Level Synthesis (HLS)-based accelerators. The dimensions of a spectral image data set $(640 \times 480 \times 12)$ is selected for all of the |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | designs                                                                                                                                                                                                      |

| 4.6 | Execution time (ms) for the PCA implementation on GPU, Massively<br>Parallel Processing Array (MPPA), and FPGA (our work) 97                                                                                 |

| 5.1 | Kernel functions in SVM                                                                                                                                                                                      |

| 5.2 | MNIST dataset: performance and resource usage                                                                                                                                                                |

| 5.3 | Comparison of different SVM kernels                                                                                                                                                                          |

| 5.4 | Comparison of the proposed accelerator with different SVs and same number of features ( $N_f = 27$ ) in the same FPGA (model1 and model2 use different pre-processing methods on training data) 109          |

| 5.5 | Performance comparison with two manual RTL designs 109                                                                                                                                                       |

| 5.6 | Performance analysis of SVM accelerator for medical microwave data set using floating-point data precision ( $N_{SV} = 2009, N_{features} = 110, N_{samples} = 900$ )                                        |

| 5.7 | Performance analysis of SVM accelerator for medical microwave data set using fixed-point data precision ( $N_{SV} = 2009, N_{features} = 110, N_{samples} = 900$ )                                           |

| 6.1 | Ranges of parameters for the joint training/hardware optimization method.                                                                                                                                    |

| 6.2 | Search space featuring network architecture and hardware configura-<br>tions (UF:Unroll Factor)                                                                                                              |

| 6.3 | Pareto points obtained by three methods                                                                                                                                                                      |

| 6.4 | Evaluation of MLP performance in microwave anomaly detection.<br>Fixed-point precision is selected in hardware with total and integer<br>widths of 16 and 10, respectively                                   |

## Chapter 1

## Introduction

Today's increasing demand for compute-intensive applications calls for efficient approaches to achieve the desired performance. Most of the computations in a variety of applications usually take place in general purpose processors, or CPUs. To keep up with the increasing computations in new applications, one could easily wait for the new technology which, according to the Moore's law, could make it possible to run the application faster. However, the end of Moore's law prevents to continue scaling of the performance and efficiency. Therefore, we need to look for other alternatives to speed up the computations in current and future applications. One of the few alternatives is "*Domain-Specific hardware Accelerators (DSAs)*".

Domain-specific accelerators are subset of hardware accelerators that can be used for a specific domain of applications. There are different applications in which the domain-specific accelerators have been already used with considerable improvement in performance compared to general-purpose computers. These applications include deep learning, bioinformatics, image processing, and many more fields. Designing an accelerator requires considerable effort to acquire an efficient hardware performance, which can be achieved by a combination of the following methodologies: Parallelism, efficient memory systems, specialized operations, and overhead reduction techniques. The reason of recent trend in using DSAs is their potential as one of the few techniques to improve the efficiency and performance of the accelerators even with the decline of Moore's law benefits [1].

DSAs can be used in embedded systems which are computing platforms containing all the hardware and software components embedded in the system to execute an application-specific program. A high-performance embedded platform very often consists of one or more general purpose processors, together with a number of specialized *hardware accelerators* (DSAs). These can be either on the same electronic board, or integrated in the same System-on-Chip (SoC). One of the popular approaches in recent years to design such accelerators is to use Field Programmable Gate Arrays (FPGAs). Nowadays, advanced SoC FPGAs have a variety of programmable features as well as hardwired functions providing flexibility for the hardware designers. One example is the usage of soft processors or hard processors in these systems. The former uses the internal programmable logic and resources of an FPGA to design a processor, while the latter is a fixed hardware outside the programmable logic of the FPGA and communicates with it via dedicated peripherals in the same SoC. The flexibility comes from large amount of hardware resources available in today's FPGAs, including massive arrays of programmable logic units and their interconnections, large on-chip memories, custom data paths, high speed I/O, and microprocessor cores all co-located on the same chip [2].

Designing a hardware accelerator faces the designers with several challenges. Firstly, design goals and requirements for different applications can vary significantly. In some application such as video encoding and streaming, a high throughput is required while in others accuracy is more important than throughput, such as bio-sensing data acquisition systems. Some applications tend to be inherently computation-limited, in the sense that their performance is determined by the number of computational resources working in parallel, while others tend to be inherently memory-limited, because their performance is bounded by the memory bandwidth. There are finally cases in which depending on the details of the implementation (e.g., on the internal parallelism), an application can transition from a computation- to a memory-bound performance region (this is typical for Deep Learning workloads). Depending on the application, the hardware design goals and technique have to change. Secondly, achieving the optimal performance in hardware accelerators requires a trade off between different design goals, which is clarified in more detail in the next section. Thirdly, in today's high-performance computing applications, one of the important factors is the design and development time, which tends to be very high if the traditional approaches to the hardware design are used. Therefore, it is important to utilize the capabilities of recent design tools to obtain an efficient hardware design, a subject that will be introduced and discussed in more detail in section 2.2.

In the remainder of this chapter, we first introduce the main motivation behind this work and discuss the problem statement. In Section 1.2, the domain-specific computational kernels that are considered in this thesis are briefly introduced. The challenges of designing hardware accelerators for these compute-intensive kernels are described in Section 1.3. Finally, in Section 1.4, an overview of this thesis, with scope and goal, is given.

## **1.1 Motivation and Problem Statement**

The main objective of this thesis is to design efficient hardware accelerators for compute-intensive kernels that are used in two main application areas: *Biomedical Microwave techniques* and *Machine Learning algorithms*. Although the initial motivation of this work was the development of a medical microwave imaging device in the EMERALD project<sup>1</sup>, we considered a broader range of applications that is not restricted to Microwave Imaging only and includes Machine Learning methods as well.

There are several algorithms that are used in these application areas which contain computationally-expensive kernels. General purpose processors cannot offer high performance when they are used for these kernels. An alternative is using domain-specific accelerators which provide higher efficiency.

Therefore, the main problem that is addressed in this thesis can be divided into two parts: (1) Analysis of the recurrent algorithms in biomedical microwave imaging and Machine Learning to find the compute-intensive kernels, (2) Designing the domain-specific accelerators for these kernels in an efficient way.

### **1.2 Compute-Intensive Kernels**

In this section, we briefly introduce the compute-intensive kernels inside the algorithms that are used in different application areas. This broad *domain of applications* include "medical microwave techniques" (which contains "Analysis of antennas and electromagnetic wave simulation"), and Machine Learning (which contains "Hyperspectral imaging", "Feature extraction", and "Classification").

<sup>&</sup>lt;sup>1</sup>www.msca-emerald.eu

Table 1.1 shows the domain-specific kernels considered in this thesis (rows of the table) and their potential application areas (columns of the table). All the kernels in Table 1.1 can be used in the "Biomedical Microwave Techniques" application area. However, we consider a broader domain of applications in which the kernels in this thesis can be used. In the next chapters, the methodologies to design efficient hardware accelerators for these kernels will be presented in order to optimize and enhance the performance of these kernels in FPGAs.

|         | Biomedical           | Antennas | Hyperspectral | Machine Learning   |                |

|---------|----------------------|----------|---------------|--------------------|----------------|

|         | Microwave techniques | analysis | Imaging       | Feature extraction | Classification |

| FDTD    | +                    | +        | -             | -                  | -              |

| SVD/EVD | +                    | -        | -             | +                  | -              |

| PCA     | +                    | -        | +             | +                  | -              |

| SVM     | +                    | -        | +             | -                  | +              |

| MLP     | +                    | -        | +             | +                  | +              |

| CNN     | +                    | -        | +             | +                  | +              |

Table 1.1 Domain-specific kernels (rows) and their applications (columns).

#### 1.2.1 3D FDTD

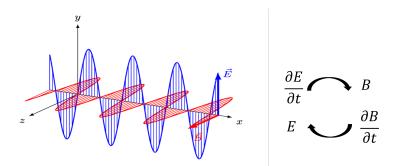

Finite Difference Time Domain (FDTD) is a numerical analysis technique to simulate the propagation of electromagnetic fields in different materials. Based on Maxwell equations, any variation in the electric fields will cause a magnetic field and vice versa, as shown in Fig. 1.1.

Fig. 1.1 Propagation of electromagnetic fields and the impact of variations in electric and magnetic fields.

As will be stated in Section 2.4.3, FDTD is the critical computational part of one of the non-linear iterative microwave image reconstruction algorithms. Due to the need for higher resolution in MI recent years, three dimensional FDTD has become

more popular. Therefore, hardware acceleration of 3D FDTD can significantly improve the performance of embedded MI systems which use FDTD in their internal algorithms. In Chapter 3 the details of proposed methodology for 3D FDTD hardware accelerator in FPGA is presented.

#### 1.2.2 PCA using SVD/EVD

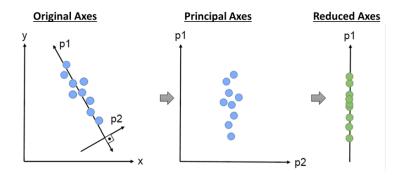

Principal Component Analysis (PCA) is a feature extraction technique in ML and can be used to remove redundant information in data. An illustrative example is shown in Fig. 1.2 in which the redundant information in the horizontal axis can be removed by transforming original data into its corresponding principal components and ignoring the axis with low variations. PCA is extremely useful when we have large data dimensions and it is difficult to process the entire data, hence reducing the dimensions of data.

As we will see later, PCA consists of several components. These components can be considered as other compute-intensive kernels. For example, Singular Value Decomposition (SVD) and Eigenvalue Decomposition (EVD), can be used not only in PCA, but also in other inverse scattering solutions in MI. Therefore, by hardware implementation of PCA, we can accelerate the execution of several compute-intensive kernels, such as SVD and EVD. We explain the proposed methodology for the hardware acceleration of PCA in Chapter 4.

Fig. 1.2 PCA for dimensionality reduction to remove redundant information.

#### 1.2.3 SVM

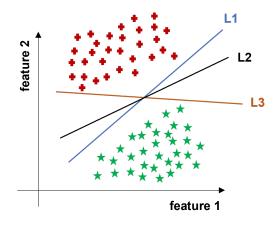

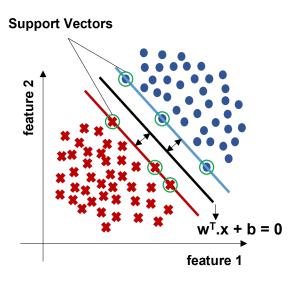

Support Vector Machine (SVM) is a powerful classification (and regression) algorithm in ML. SVM for binary classification finds a separating line (or hyper-plane) between data points of two classes which can best separate the classes. As shown in Fig. 1.3, SVM obtains the separating line by maximizing the margin between the classes. Although there are infinite number of separating lines (e.g. L1 to L3 in Fig. 1.3), only one line is optimal (L2) which can be generalized to the new data points that might appear in the future. In Chapter 5, more details about the theory of SVM together with its corresponding hardware accelerator design are explained thoroughly.

Fig. 1.3 SVM for binary classification finds the decision boundary with maximum margin between two classes (L2).

#### **1.2.4** Neural Networks

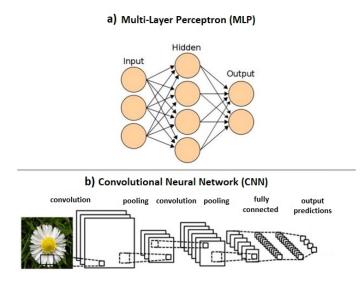

Neural Networks (NNs), also called Artificial NNs (ANNs) are a subset of ML and at the heart of Deep Learning (DL) algorithms. Their structure is inspired from the human brain and from the way that biological neurons signal to each other. ANNs comprise of input layers, multiple hidden layers, and output layers, and each layer consists of several compute nodes. These nodes receive and process the inputs and weights from the previous layer to produce the outputs.

There are different types of architectures for NNs. In Multi-Layer Perceptrons (MLPs), network layers are fully connected to each other, meaning that each node in one layer is connected to all the nodes in the next layer, as shown in Fig. 1.4 (a). In

Convolutional Neural Networks (CNNs) each layer consists of multiple filters that are *convolved* with the input data, as shown in Fig. 1.4 (b). Other types of ANNs can be found in [3]. In Chapter 6, more details about hardware acceleration of ANNs will be presented. In addition, we will propose a new framework for co-optimization of training hyper-parameters and hardware configurations to achieve the optimum performance in embedded accelerators design for ML algorithms, including ANNs.

Fig. 1.4 Network structure for a) MLP and b) CNN [4]

## **1.3 Challenges in Designing Domain-Specific Acceler**ators

There are several challenges in designing hardware accelerators for the domainspecific kernels introduced in previous section. In the following, we briefly explain these challenges and then, we explain the methodologies that we proposed to overcome these challenges:

In **3D FDTD** kernel, one of the main challenges is the **access to a large volume** of data from external memory. Although several methodologies have been proposed to address this issue, they are not effective in Microwave Imaging (MI) where we need to add more details in FDTD equations. Specifically, previous works did not consider the **impact of polarization current** and dispersive materials in FDTD equations. In addition, the **boundary conditions** used in the majority of the previous works oversimplify the FDTD algorithm. Considering these details in FDTD equations makes the design of the hardware accelerator more challenging which we address in this thesis.

- 2. In PCA kernel, the large data dimension and computational complexity of PCA algorithm create several challenges. Due to the large amount of data in PCA computations, most of the previous works could not implement all the computational units in hardware, so they left some essential parts (like covariance computation) to be executed off-line in software. In addition, conventional PCA accelerators use RTL approach for the hardware design which increases the design and development time. Flexibility and efficiency are other challenges in PCA accelerator design. Supporting different data dimensions and data types is not trivial in a full PCA hardware accelerator design which is considered in this thesis.

- 3. In **SVM** kernel, the main challenge that is usually ignored in previous works is **scalability**, which means that we can use the same design for larger data dimensions. In addition, most of the previous SVM accelerators only focused on binary classification or simple kernel functions. Multi-class classification in SVM is more challenging because it requires more computations. We addressed these challenges for SVM accelerator design in our thesis.

- 4. In ANNs, the main challenge in designing efficient hardware accelerators is the co-optimization of training hyper-parameters and hardware configurations. Despite the recent efforts in designing co-optimization frameworks, there are still so much opportunities for further enhancement. Specifically, a *truly* **multi-objective optimization** framework in the context of *multiple hardware configurations* has not been fully explored in the domain of HLS-based FPGA acceleration of ANNs. We elaborate further on this issue when introducing the proposed framework.

### **1.4 Scope and Outline**

In this thesis, we focus on the design of domain-specific hardware accelerators to enhance the performance of recurrent algorithms used in a broad domain of applications. Machine Learning and biomedical Microwave Imaging are two main target applications. Although all the proposed accelerators can be used in the biomedical microwave application (as the main target), they have a broader range of applications and are useful in a variety of Machine Learning techniques. The main goal is to use specific hardware accelerators to improve the performance of these recurrent algorithms under various constraints (e.g., latency, power, resource usage). Designing such hardware accelerators requires the analysis of each algorithm and usage of specific hardware optimization techniques to accelerate the execution of the compute-intensive parts. For the hardware design and implementation, we use High Level Synthesis (HLS) and the target application. In addition, obtaining the best performance in ML algorithms requires the optimization of training hyper-parameters and hardware configurations, which is also considered in this work.

In the following, the main contributions of this thesis and the methodologies to overcome the above-mentioned challenges are described:

- 1. Evaluation of widely-used algorithms in a broad domain of applications, including MI and ML.

- 2. FPGA acceleration of **3D FDTD** for multi-antennas microwave imaging (**Chapter 3**):

- We proposed a spatial blocking approach to overcome the problem of memory access time.

- To deal with the challenge of the additional polarization current, we could use HLS capabilities to efficiently process the extra computations by merging the corresponding loops on the polarization currents with the loops on the electric fields update.

- We presented two versions of our FDTD accelerator: Small and Large designs with different resource usage and number of interfaces to meet memory bandwidth requirements and increase the flexibility.

- For the complex boundary conditions in our FDTD accelerator we merged the parallel loops in the boundary regions and used local memories whenever possible to store the required data. We implemented the computations of boundary equations in HLS by considering *CPML* conditions *in all directions*.

- Our single FPGA accelerator for FDTD could achieve 1.44× lower execution time per antenna compared to the best GPU design of the same algorithm. In our multi-FPGA design with 8 FPGAs and a typical number of 24 antennas, a 11.5x reduction of execution time can be achieved compared to the best GPU design. In addition, our design is more energy efficient than the conventional methods.

- 3. High level design of a flexible FPGA accelerator for Principal Component Analysis (**PCA**) (**Chapter 4**):

- We presented an efficient block-streaming methodology to overcome the issue of large data dimensions and memory access time in PCA.

- In contrast to most of the previous works, the covariance computation is included in our PCA accelerator design for large data dimensions.

- Our proposed PCA accelerator is flexible because it can be used for different input sizes and FPGA targets.

- We presented a more accurate floating-point and a faster fixed-point implementation to improve flexibility and efficiency.

- Compared to a similar FPGA implementation of PCA using VHDL, our HLS design has a 2.3× improvement in the processing time, and a significant reduction of the resource usage. Compared to other HLSbased approaches, our design has a maximum of 2.5× speedup.

- 4. A new dataflow hardware architecture for Support Vector Machine (SVM) (Chapter 5):

- We proposed a scalable hardware accelerator for SVM algorithm in FPGAs that can support different data dimensions while guaranteeing a high throughput.

- Multi-class classification with recurrent SVM kernels are supported in our proposed accelerator.

- The level of hardware parallelism in our accelerator is adjustable thanks to the HLS-based configurations.

- In addition to the floating-point precision, we presented efficient implementation of fixed-point design for the SVM accelerator.

- A minimum of 10× latency improvement compared to similar HLSbased and 4.4× improvement compared to RTL-based designs can be achieved by our dataflow hardware architecture for SVM accelerator.

- 5. High level implementation and optimization of conventional **Neural Networks** in FPGAs (**Chapter 6**):

- We introduced a new framework for the co-optimization of ML training and hardware design.

- We used Multi-objective Bayesian Optimization on top of High Level Synthesis as a new approach for the co-optimization problem.

- Instead of using a fixed hardware architecture, our framework supports adjustable HLS-based hardware configurations.

- The Pareto set achieved with our framework outperforms those obtained with the other methods, with 1.7× and 1.4× improvement in execution time for the minimum error compared to *random* and *separate* methods, respectively.

- 6. Boosting the performance by using HLS-based hardware optimization techniques

- 7. Evaluation of each accelerator on a dataset obtained by microwave measurements to assess the feasibility of the proposed solutions for biomedical microwave applications.

In the next chapter, we introduce a background about the design of domainspecific hardware accelerators and their applications. In the following chapters, we explain hardware design methodologies for the domain-specific kernels that were introduced in Sec. 1.2 and compare them with the state-of-the-art related works. In addition, in Chapter 6, the co-optimization methodology for hardware and training is explained. The last chapter is dedicated to the conclusions, future works, and outputs of thesis and the publications.

## Chapter 2

## Background

## 2.1 Performance Analysis of Domain-Specific Accelerators

For the best design of an accelerator, the broadest possible range of applications must be covered, which makes it possible to accelerate more than one single application. Domain-specific instructions can be added to programmable processors to provide efficiency while preserving flexibility. In addition, we can build a parallel computer from domain-specific accelerators in order to expand the domain of applications.

To design a domain-specific accelerator, the designer must always find a trade-off between efficiency and generality. If the accelerator is designed for only one specific application, it results in the best possible efficiency, but with a limited range of use. On the other hand, designing a general-purpose processor, although is flexible, results in a weak efficiency. The best approach is to increase the range of applications as much as possible to keep the flexibility and not to lose the efficiency of a single specialized accelerator [1].

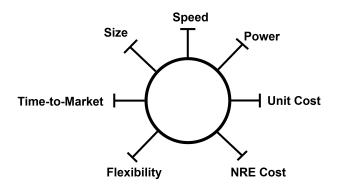

In another view, high-performance computing systems with DSAs must be carefully designed to meet stringent requirements. They require not only lots of computations as well as correct functional behaviour, but also must meet several quantifiable and often contradictory design metrics, which must be optimized simultaneously to achieve an efficient implementation. A design metric is a measurable feature of the system's implementation which can be interpreted in several ways. In the following, different design metrics in the implementation of hardware accelerators are explained.

One of the most important design metrics is *performance* which can be further specified to capture one peculiar aspect of speed. For example, Execution time (or Latency), and Throughput (the rate at which a system can process data and receive new input<sup>1</sup>) are two representations of system performance. Another design metric is Power consumption which, if combined with execution time and considered in its average form, determines the lifetime of a battery, or when considered in its peak form it affects the cooling requirements of a chip. The size of computing devices is also important because the physical space and geometry required by the system must be as small as possible to fit on a given area, ranging from the silicon area of single-chip implementation to the form-factor of a board for a multi-chip design. A crucial design metric in the accelerators design is *Cost* which can be divided into  $NRE^2$  cost (the cost of designing the system, after which any number of units of the system can be manufactured without incurring additional design cost) and Unit cost (the cost of manufacturing each copy of the system excluding the NRE cost). Designing a high-performance system usually requires a complex and long design procedure (hence, large NRE) and leads to using a large amount of hardware resources (hence, a high unit cost). Flexibility, as another design metric, is defined as the ability to change the functionality of the system without incurring heavy NRE cost. Finally, *Time to market* determines the amount of time required to design and manufacture the system to the point that the system can be sold to customers. Other design metrics can be found in [5].

The above-mentioned metrics are usually in contrast, and improving one of them leads to the degradation of the others. Fig. 2.1 shows an illustration of different design metrics which can be considered as a wheel with different pins. Pushing one pin will cause others to pop out [5]. A hardware designer must be able to optimize these metrics under various constraints.

<sup>&</sup>lt;sup>1</sup>A more precise definition will be presented in the next chapters.

<sup>&</sup>lt;sup>2</sup>Non-Recurrent Engineering

Fig. 2.1 Various design metrics in the implementation of a hardware accelerator

## 2.2 High Level Synthesis for the Design of Hardware Accelerators

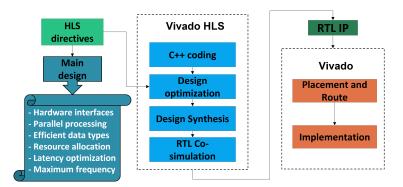

To design a hardware accelerator in an FPGA, the traditional approach uses Hardware Description Languages (HDL) like VHDL or Verilog. Although this approach is still the predominant design methodology, it impacts the development time and the design effort. As hardware computing systems become more and more complex, designing an efficient hardware in RTL requires significant effort, which makes it difficult to find the best hardware architecture. In fact, the advances in chip integration capabilities have increased the complexity of embedded systems to such a level that their development time sometimes exceeds even their product lifetime. An alternative solution that is becoming more and more popular in recent years is the High Level Synthesis (HLS) approach. HLS raises the design abstraction level by using software programming languages like C or C++. Through the processes of scheduling, binding, and allocation, HLS converts a software code into its corresponding RTL description. The main advantage of HLS over HDL is that it enables designers to explore the design space more quickly, thus reducing the total development time with a quality of results comparable and often better than RTL design.

To understand the main steps in designing a hardware accelerator with Xinlinx FPGAs based on HLS, we introduce the hardware design flow in Fig. 2.2. Starting from a software code written in C or C++ in Vivado HLS tool, we design our hardware by applying efficient HLS *directives* to optimize our design. In the synthesis step,

the optimized code is compiled and translated into a netlist. In the last step in Vivado HLS, it is possible to run the C/RTL co-simulation to check if the generated RTL is functionally identical to the C++ code. Finally, an RTL IP could be generated that can be used in Vivado tool. The final steps in Vivado are Placement, route, implementation and generation of the bit-stream.

Fig. 2.2 Hardware design flow in Vivado

#### 2.2.1 Design Optimizations in HLS

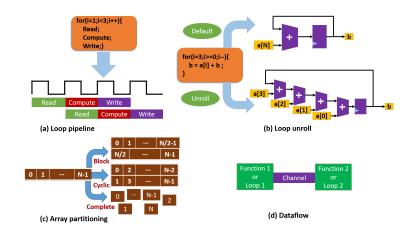

To introduce the principles behind the HLS-based hardware optimization techniques, a more abstract description of the high-level directives is presented in this part. In Figure 2.3 the most widely used optimization directives are illustrated with their corresponding hardware implementation. These directives include *Loop Pipelining, Loop Unrolling, Array Partitioning,* and *Dataflow.* These directives can be used to reduce the latency, increase the throughput, and make the best use of the hardware resources. Note that latency is the time required to produce the output of a computation starting from when the corresponding input is received. Throughput is the rate at which the outputs are produced (or the inputs are consumed) and is measured as the reciprocal of the time difference between the arrival of two consecutive outputs (or inputs). In the following, these HLS optimization directives are briefly introduced:

- Loop *Pipelining* allows multiple operations of a loop to be executed concurrently on different hardware resources, while those resources are used repeatedly over the various iterations of the loop.

- Loop *Unrolling*, instead, creates multiple instances of the hardware for the loop body, which allows some or all of the loop iterations to occur in parallel.

- By using *Array Partitioning* we can split an array, which is implemented in RTL by default as a single block RAM resource, into multiple smaller arrays that are mapped to multiple block RAMs. This increases the number of memory ports providing more bandwidth to access data.

- The *Dataflow* directive allows multiple functions or loops to operate concurrently. This is achieved by creating channels (FIFOs or Ping-Pong buffers) in the design, which enables the operations in a function or loop to start before the previous function or loop completes all of its operations. The Dataflow directive is mainly used to improve the overall latency and throughput of a design.

- Arbitrary Precision (AP) data types make it possible to use efficient number of bits for the data types. As opposed to the software C++ codes in general purpose processors which support fixed number of bits, using AP data types in HLS-based designs can reduce the resource usage and increase the performance.

- *Loop merging* provides the opportunity to execute the multiple loops in parallel which results in reducing the design latency.

- By using *Resource Allocation* directive, it is possible to allocate specific hardware resources for individual computational operations.

Fig. 2.3 Hardware optimization directives

#### 2.2.2 HLS Design Trends in Selected Domains

Although there are several tools to design HLS-based hardware accelerators that are developed either commercially or by academia [6], we focus on *Vivado HLS*, a commercial tool that is used for Xilinx FPGAs.

There have been a growing interest in recent years in using HLS tools to design domain-specific accelerators. In this subsection, we introduce some of the relevant works as examples that used HLS for their hardware accelerator design. We will highlight the advantages of our accelerators compared to these works in the related chapters. For broader analysis of the literature, including both HLS-based and RTL-based designs, please refer to the corresponding chapter.

In the design of FDTD accelerators, the authors in [7] use an HLS tool called MaxCompiler to optimize their design. However, they used simplified boundary conditions. In [8], memory and power performance of FPGA accelerators for general *stencil* algorithms including FDTD have been investigated by using MaxCompiler tool. For the PCA hardware design, an HLS-based design was introduced in [9]. Schellhorn et al., presented another PCA implementation on FPGA in [10] by using HLS. However, the EVD part could not be implemented in hardware due to the limited available resources. In [11], an HLS design for SVM acceleration is proposed and is extended in [12, 13]. Due to the local storage of SVM coefficients, these works could be tested on small-scale problems. Finally, there are numerous works for the design of ANNs in hardware using HLS, one of which is hls4ml ([14]). However, the efficient co-design of ANNs training and hardware configurations has not been fully explored.

### 2.3 Applications of Domain-Specific Accelerators

In this section we introduce some of the applications that are relevant for this thesis in which domain-specific accelerators can be used. It is important to understand the main objectives of each application to obtain the specifications and requirements of the accelerators used in these applications. We focus on two research areas as examples of domain-specific applications, which are *biomedical microwave techniques* and *Machine Learning (ML)*. Note that ML is a general research field and has a wide range of applications one of which could be biomedical microwave applications.

#### 2.3.1 Biomedical Microwave Techniques

Microwave Imaging (MI) is a technique to observe the internal structure of an object by using electromagnetic fields at microwave frequencies. It has received considerable attention in medical applications due to the fast diagnosis and high safety for the patient [15]. Unlike other medical imaging modalities, such as CT-scan or X-ray, MI has the advantage of using non-ionizing radiations. This is because microwave radiations are electromagnetic waves at frequencies between 300MHz and 300GHz, which is between radio and infrared frequency ranges. Although ultraviolet, X-ray, and gamma-ray are commonly used in medical imaging, they have much higher frequencies compared to microwaves, which makes them ionizing radiations causing several health risks in the medical imaging devices (as opposed to nonionizing microwave radiations). Having lower frequencies, microwave radiations have low penetration depth, and it is more challenging to use them for medical diagnosis. Although Magnetic Resonance Imaging (MRI) does not use any radiation either, the MRI instruments are bulky and very expensive and can be used only inside the hospitals. The low-cost, small-scale, portable, and non-invasive characteristics of an MI device make it one of the most promising medical imaging techniques [16].

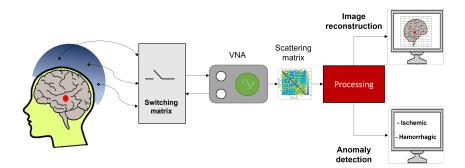

A Microwave Imaging system uses microwave radiations emitted from a set of antennas arranged in a proper geometry around a given body part. The reflections of these radiations, which are created at the interface between tissues exhibiting different dielectric properties—i.e., a so called *dielectric contrast*—are captured and converted to an output image according to a specific algorithm to highlight, for example, an anomaly within a body part.

The development of an MI device requires collaboration between researchers working on different parts of the device. This is the main goal of the EMERALD project (www.msca-emerald.eu), an MSCA training network funded by the European Commission under the H2020 program. The research work at the basis of this thesis has been done in the framework of this project, in which the various MI techniques used by researchers very often require hardware acceleration, as it will be explained later. Before delving deeper into the various accelerators required by the MI techniques, let us introduce the main components of an MI device.

An MI system consists of several components that are depicted in Fig. 2.4 for the particular case of brain stroke monitoring. A similar figure can be depicted for other

MI applications such as breast cancer detection. The first component of the system is a set of antennas that are arranged around the body part under consideration (i.e. head or breast). These antennas are connected to a switching matrix, which controls which pairs of antennas are active during the measurements. A Vector Network Analyzer (VNA) is connected to the switching matrix and measures the microwave radiations in the form of a scattering matrix. Each element (i, j) of the scattering matrix describes the relation between the wave emitted by the *i*th antenna and the wave received by the *j*th antenna. Therefore, if the number of antennas is *N*, the scattering matrix is a symmetric matrix with  $N \times N$  elements showing the relative transferred energy between each pair of antennas. The last component of the device is a processing system that is used to convert the microwave measurements into the image pixels (image reconstruction), or to analyze the microwave measurements to detect anomalies for medical diagnosis (anomaly detection). Precisely the algorithms used in such processing system may require acceleration.

Fig. 2.4 General diagram of a Microwave Imaging system.

When the microwave electromagnetic fields are radiated to the body, the reflected waves are scattered due to the difference between the dielectric properties of the body tissues. This phenomena is termed *scattering*. Related to the scattering phenomena are two heavy computing problems that are implemented in the processing system, especially in iterative algorithms. One is termed *forward scattering* and consists in computing the scattered field via electromagnetic simulations starting from an electromagnetic model of the objects (i.e. the body tissues), which have to be completely known with their dielectric properties. The second one is termed *inverse scattering*, in which the goal is instead to retrieve the properties of an unknown object from the known scattered field. Often forward and inverse scattering are combined in iterative optimization problems in a way that inverse scattering invokes

repeatedly the forward step until convergence, but it is also possible that inverse scattering uses a different technique than forward scattering to obtain the unknown parameters. Medical MI suggests therefore different algorithms to solve the problem of inverse scattering, which will be briefly discussed in Section 2.4.

#### **Microwave Imaging in Breast Cancer Detection**

Breast cancer is the most common type of cancer and the leading cause of death in women worldwide [17]. MI is a trending technology in biomedical research community for breast cancer detection. Although mammography is the standard imaging modality in the diagnosis of breast cancer, its ionizing radiations calls for safer imaging techniques. The higher dielectric contrast of the tumor tissues compared to normal breast tissues allows for the breast tumor detection in an MI system, as shown in Fig. 2.5.

Fig. 2.5 Dielectric properties of breast tissues. Difference in relative permittivity allows for tumor detection in MI ([18]).

There have been several works in recent years concentrating on the development of an MI system in the application of breast cancer diagnosis [19–22, 18, 23].

#### Microwave Imaging in Brain Stroke Monitoring

Brain stroke is a cerebrovascular disease affecting a large percentage of people worldwide, which can lead to permanent disabilities or even death. Early diagnosis of brain stroke, either ischemic or hemorrhagic, helps in finding the right treatment. Recently, there has been a growing interest in using MI technology for brain stroke monitoring [24–29]. In Fig. 2.6, the setup of a recent MI device is shown, which

consists of a set of antennas that are placed around the head and P positions are considered for the locations of the stroke. The exact location of the stroke can be detected by using an MI inverse scattering solution.

Fig. 2.6 Brain stroke detection with MI system containing V antennas and P candidate locations for the stroke positions  $(r_1 \text{ to } r_P)$  ([29]).

## **2.3.2** Machine Learning (ML)

Machine Learning algorithms are applicable to a variety of applications including MI. Due to the extensive range of applications of ML, we consider a general framework for ML algorithms which is not limited only to microwave imaging. There are two steps in any ML model that are shown in Fig. 2.7 which shows how the training and inference of an ML model is performed. Any ML model contains a set of training parameters that are obtained during the training step. The training parameters depend on the type of ML approach, including weights and biases for a Neural Network, coefficients for linear regression models, or support vectors for Support Vector Machines (SVMs). Once these training parameters are obtained, they can be used in the inference step to predict the outputs of the model for the new input data. Estimation of the mapping between inputs and outputs are termed classification (for discrete outputs) or regression (for continuous outputs). In Sec. 2.5, different ML models are explained in more detail. Note that using data *pre-processing* and *feature extraction* techniques before the training step leads to higher accuracy and, most of the times, these steps are also required and can be considered part of an ML pipeline.

Fig. 2.7 Machine Learning training and inference steps.