## POLITECNICO DI TORINO Repository ISTITUZIONALE

### From 0.18µm to 28nm CMOS Down-scaling for Data Links in Body Dust Applications

Original

From 0.18µm to 28nm CMOS Down-scaling for Data Links in Body Dust Applications / Barbruni, Gian Luca; Carrara, Sandro; Ros, Paolo Motto; Demarchi, Danilo. - ELETTRONICO. - (2021), pp. 1-4. (Intervento presentato al convegno 2021 IEEE Sensors tenutosi a Sydney, Australia nel 31 Oct.-3 Nov. 2021) [10.1109/SENSORS47087.2021.9639639].

Availability: This version is available at: 11583/2947878 since: 2021-12-27T15:35:16Z

Publisher: IEEE

Published DOI:10.1109/SENSORS47087.2021.9639639

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# From 0.18µm to 28nm CMOS Down-scaling for Data Links in Body Dust Applications

Gian Luca Barbruni, Sandro Carrara Integrated Circuits Laboratory École polytechnique fédérale de Lausanne Neuchâtel, Switzerland gianluca.barbruni,sandro.carrara@epfl.ch

Abstract-In this work, we study the effect of transistor downscaling in a wireless communication circuit for Body Dust application. The system requires a chip lateral size smaller than 10 µm miming the typical size of a red blood cell and so, supporting free circulation in human tissues. Moreover, an ultralow-power architecture is needed since the system is battery-less and wirelessly powered via acoustic power transfer. The aim of this paper is to present a data communication system for Body Dust systems, which works from the multiplexed sensor read-out front-end to the transmitter back-end taking account diagnostic information on different metabolite concentrations in human body. This work shows that scaling the architecture from a 0.18-µm to 28-nm CMOS processes, it is possible to improve both size and power consumption. The improvement is about 40 times in size (2000  $\mu$ m<sup>2</sup> down to 50  $\mu$ m<sup>2</sup>) and two order of magnitude in average power consumption (10 µW to cents of nW).

*Index Terms*—Body Dust; ULP CMOS design; Transistor downscaling; Active Biosensors; sub-10 µm CMOS Architectures; OOK modulation.

#### I. INTRODUCTION

"Body Dust" research is a huge worldwide effort [1], [2] with the goal of developing new highly innovative solutions for precision medicine applications, obtaining a more efficient monitoring, for example in oncology. Among the wireless power transfer methods toward miniaturised implants [3], Body Dust system is ideated to be powered via UltraSounds (US). An external array of US transmitters are used to wirelessly supply drinkable and ingestible micro-active sensingchip, which are able to communicate through backscattering [4]. The CMOS Body Dust cube is ideated to include: (i) a bio-sensing front-end with five nano-biosensors mounted on the top metal layer; (ii) a potentiostat; (iii) a current-tofrequency (I-to-f) converter to convert the sensed current from the front-end to a frequency-modulated signal; (iv) a multiplexed layer with sub-Hz oscillation to read in series the five nano-biosensors' outputs [5]; (v) a power management unit; and (vi) a communication circuit to modulate and transmit the diagnostic information to the external base station, as validated in [6], [7]. The challenging in the Body Dust system is the miniaturisation toward a sub-10- µm-size, being area consumption the first critical point of the system. The second big challenge remains the power consumption since rectifying Paolo Motto Ros, Danilo Demarchi DET Politecnico di Torino Turin, Italy paolo.mottoros,danilo.demarchi@polito.it

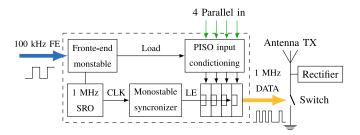

Fig. 1: System block diagram.

the US incoming signal, only few µW are exploitable for the functioning of the entire system [8]. In this paper, we present a sub-10-µm-size CMOS transmitter able to communicate with the external environment exploiting the On-Off Keying (OOK) modulation through backscattering. This transmission approach has been used for Neural Dust sensing system [9]. In that case, the architecture was composed by three different nodes (an external and a sub-dural transmitter and the proper neural dusts) while in our system the external base station and the body dust tags are only expected. Moreover, in that architecture any communication circuit was implemented (the impedance modulation was made through a switching MOSFET only). To this end, we based our design following the event-driven digital architecture implemented in UMC 0.18 µm CMOS technology [10], that has shown very promising results [11]. In this regard, the study of transistor downscaling is an interesting aspect that has been largely investigated in the recent years [12]. Moreover, planar technologies, such as Fully Depleted Silicon On Insulator (FDSOI), provides improved speed, simplified manufacturing and reduced power compared to bulk silicon technologies. Therefore, in this paper we investigated the possibility to scale the nodes from the UMC 0.18 µm to the FD-SOI 28 nm CMOS technologies for data links in sub-10-µm-size Body Dust systems.

#### **II. PROPOSED ARCHITECTURE**

The proposed communication circuit is constituted by: a 1 MHz Starved Ring Oscillator (SRO), a Front-End (FE) monostable, a monostable synchronizer, a four-inputs Parallel-Input Serial-Output (PISO) register and a modulator switch (Fig. 1). The FE input signal comes from the sensor front-end layer, as in [2]. In particular, the biological signal is extracted by a potentiostat, followed by a I-to-f converter with a sensitivity of 7 kHz/nA [2]. For currents in the range of 1-5 nA and a sensor sensitivity of almost  $1.8 \cdot 10^{-7} A/(mmol \cdot mm)$ ), the maximum frequency of the FE input pulse is almost 100 kHz. This quasidigital signal will be used to trigger an event-driven wireless transmitter, as the impulse radio proposed in [13]. However, a unique 3-bit address is taken from the multiplexer of the Body Dust chip, used to distinguish among five different quasidigital signals extracted by different sensor front-end. All the blocks will be now discussed as regard its implementation in UMC 0.18 µm CMOS technology.

#### A. The Starved Ring Oscillator

The function of the ring oscillator is to synchronize the shifting register in order to create a serial 1 MHz data. The oscillation frequency is approximated by (1):

$$f = \frac{I}{N \cdot C_{tot} \cdot V_{dd}} \tag{1}$$

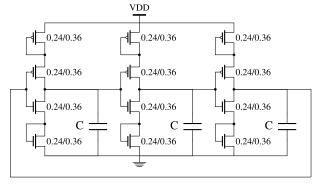

in which I is the current flowing through the ring, N is the number of stages,  $C_{tot}$  is the total capacitance and  $V_{dd}$  is the supply voltage (e.g. 1.8 V). We designed a three-stages-starved-ring oscillator (Fig. 2). Capacitances and MOSFETs' size have been designed following the trade-off between the desired oscillation frequency of 1 MHz with the overall size of the component (in particular C=200 fF). As a matter of fact, the total capacitance can be decreased operating on the length of the transistors. As a result, the total area improvement is less than 10% at the cost of a reduced SRO performance reliability and an highly dependence on parasitics. Post-layout simulations also show a 1 % frequency variation among a temperature sweep from 27°C to 47°C (reasonable ranges for biomedical application). Table I compares the SRO performance with two frequency to voltage converters [14], [15].

#### B. The PISO register

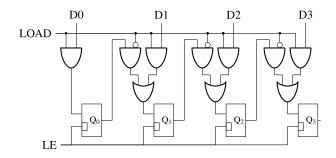

We designed a 4-inputs PISO register through four Dlatches, which are triggered by a Latch Enable (LE) signal driven by the monostable synchronizer (Fig. 3). With respect to a PISO made by Positive Edge Triggered (PET)-D Flip

Fig. 2: Three stages Starved Ring Oscillator (SRO).

TABLE I: SRO features comparison.

|                         | [14]       | [15]  | This work |

|-------------------------|------------|-------|-----------|

| CMOS nodes              | 130nm      | 130nm | 180nm     |

| Voltage supply (V)      | 3.3        | 3.3   | 1.8       |

| External component      | Yes        | No    | No        |

| Frequency (MHz)         | 22.5-360   | 1     | 1         |

| Power (µW)              | $5000^{*}$ | 287.1 | 9.5       |

| Area (mm <sup>2</sup> ) | 0.05       | 0.054 | 0.00116   |

| * * * 200 1411          |            |       |           |

\*At 200 MHz

Flop, this configuration improves synchronization and area consumption. The parallel address is driven by a combinational circuit in which the LOAD signal, triggered by the front-end monostable, specify the writing or the shifting times. More in detail, when LOAD is "H", or "L", the word is respectively written, or shifted, in the latches. As a result, after four clock hits the serial address will be used to modulate the final switch. Minimum size transistors are used to save area, so that technology node downscaling is promising toward miniaturisation. As in [16], the transmitted packet is constituted by an header (bit 1 always) and three bits  $A_2$ ,  $A_1$ ,  $A_0$  for the signal address.

#### C. The Front-end Monostable

The FE monostable is the only block that receives the FE signal. It works as a rising edge detector (using a D-latch as delay element) and its output is the LOAD signal which operates on the PISO register. LOAD signal needs to be large enough (almost 1  $\mu$ s) in order to detect the possible variations of the parallel word coming from the multiplexer and to be sure that the clock can be seen into this interval. As a result, a LOAD pulse is triggered at each FE rising edge.

#### D. The Monostable Synchronizer

The Monostable Synchronizer is an inverter-based delay block sized accordingly to the number of components receiving the trigger (i.e. four latches for the PISO and one for the FE block). The output is almost a 1 ns pulse that needs to be over the transistors' activation threshold. The layout connection is made in order to be symmetrically centered with respect to all the triggered latches, so improving the synchronization [17].

Fig. 3: Four inputs PISO register.

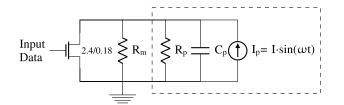

Fig. 4: Electrical model of the PZT receiver (dotted box), modulator  $R_m$  and NMOS-based switch.

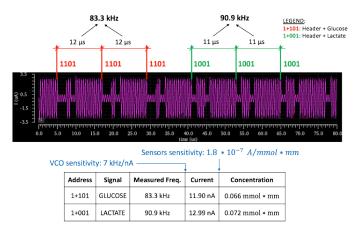

Fig. 5: Transient analysis to reconstruct different molecules concentration (i.e. glucose and lactate) using two different addresses (i.e. 1101 and 1001).

#### III. OOK MODULATOR

The final OOK modulation is made using an NMOS-based switch. Impedance modulation is performed controlling the drain current. Therefore, the transistor is sized accordingly to the transducer electrical equivalent impedance. The circuit is shown in Fig. 4, in which the resistance  $R_m$  of the modulator is exactly equal to the lumped resistance of the PZT receiver in order to implement the correct OOK modulation. Fully matched condition is achieved once the switch is open ( $R_m = R_p$ ). On the other hand, when the switch is closed, the modulator is in parallel with a short circuit ( $R_m = 0$ ), and the mismatched condition is achieved. In particular,  $R_m =$  $3552 \ \Omega$ ,  $C_p = 62.75 \ pF$  and  $I = 10 \ \mu A$  [6], [10].

#### IV. RESULTS AND DOWN-SCALING

A full-circuit simulation is presented in Fig. 5. Two different addresses (i.e. 1101 and 1001) permit the reconstruction of two different molecules concentrations (i.e. glucose and lactate). In particular, the pink wave of Fig. 5 represents the received signal at the control station (losses due to tissue absorption and reflection are neglected). Therefore, the information could be reconstructed by measuring the frequency across the same signal-type.

#### A. UMC 0.18 µm CMOS Technology

The above described circuit has been implemented in UMC  $0.18 \mu m$  CMOS technology. The total chip area is about

43x44  $\mu$ m<sup>2</sup>, exceeding the restrictive constrain of the Body Dust research. The majority of the area and more than 95% of the averaged power is consumed by the SRO. Postlayout simulations shows a total power consumption of 9.7  $\mu$ W. The instantaneous power needed for the oscillation is 630  $\mu$ W/pulse, while 810  $\mu$ W/pulse are needed for the total transmission.

#### B. FD-SOI 28 nm CMOS Technology

Critical limitation of the cheaper UMC 0.18 µm CMOS technology are solved using a more expensive and relatively new CMOS technology like the FD-SOI 28 nm. Together with the transistor down-scaling, some circuital adjustments have been applied. In particular, high resistive pass transistor. exploited using the smallest transistor channels provided by 28 nm process, combined with the effect of the parasitic capacitances finally result in the SRO miniaturisation. More in detail, the dominant effect of the parasitic is located between the output of the i-stage of the SRO and the input of the (i+1)-stage. As a result, three parasitic capacitor replaces the ones of Fig. 2 needed in 0.18 µm process. Accordingly to (1), the transistors have been sized limiting the current flowing across the ring. The SRO finally consumes an averaged power of about 100 nW while the instantaneous power needed for the oscillation is less than 250 nW/pulse, almost three order of magnitude less than the same circuit implemented in UMC 0.18 µm [10]. Then, using Transmission Gates (TG) the number of transistors of the D-latch is further reduced (i.e. 22 down to 8 [18]). This configuration also improves noise performances of the circuit, in particular during postlayout simulations. Finally, the total size of the full circuit implemented in FD-SOI 28 nm is smaller than 50  $\mu$ m<sup>2</sup>, while the majority of the area, almost 65%, is still occupied by the SRO. The implemented architecture also answers to ULP constrain, being the average power consumption smaller than 200 nW and the instantaneous power consumption during the transmission smaller than 500 nW/pulse.

#### V. CONCLUSION

A novel sub-10-µm-size CMOS architecture for data transmission in Body Dust diagnostics has been presented. This study demonstrated the feasibility to design an UltraSoundbased architecture for data transmission by using a 0.18-µm CMOS process. As a result, the average power consumption is less than 10 µW with a total chip area of  $43x44 \ \mu\text{m}^2$ . Transistor downscaling have shown a final improvement of about 40 times in size (2000 µm<sup>2</sup> down to 50 µm<sup>2</sup>) and almost two orders of magnitude in average power consumption: from 10 µW down to 200 nW. Future work will include corner analysis, fabrication and testing of the proposed system. At the very end, we have demonstrated that, opportunely scaling the nodes of the CMOS technology, it is truly feasible to design an ultra low power OOK modulation circuit for drinkable and sub-10 µm-size Body Dust systems.

#### References

- [1] S. Carrara, "Body Dust: Well Beyond Wearable and Implantable Sensors" *IEEE Sensors Journal*, 2020.

- [2] J. Snoeijs, P. Georgiou, and S. Carrara, "CMOS body dust Towards drinkable diagnostics," 2017 IEEE Biomedical Circuits and Systems Conference (BioCAS), Turin, 2017, pp. 1-4.

- [3] G. L. Barbruni et al. "Miniaturised wireless power transfer systems for neurostimulation: a review". In: *IEEE Transactions on Biomedical Circuits and Systems* 14.6 (2020), pp. 1160–1178.

- [4] J.-P. Curty, N. Joehl, C. Dehollain and M.J. Declercq, "Remotely powered addressable UHF RFID integrated system," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 11, pp. 2193-2202, Nov. 2005.

- [5] G. L. Barbruni, C. Bielli, D. Demarchi and S. Carrara, "Transistor Downscaling toward Ultra-Low-Power, sub-100 μm<sup>2</sup> and sub-Hz Oscillators," *In 2021 16th Conference on Ph. D Research in Microelectronics and Electronics (PRIME)*. IEEE, 2021.

- [6] F. Mazzilli, E. G. Kilinc and C. Dehollain, "3.2 mW ultrasonic LSK modulator for uplink communication in deep implanted medical devices," 2014 IEEE Biomedical Circuits and Systems Conference (Bio-CAS), Lausanne, 2014, pp. 636-639.

- [7] M. J. Weber, Y. Yoshihara, A. Sawaby, J. Charthad, T. C. Chang and A. Arbabian, "A miniaturized single-transducer implantable pressure sensor with time-multiplexed ultrasonic data and power links," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 4, pp. 1089-1101, 2018.

- [8] F. Song, J. Yin, H. L. Liao and R. Huang, "Ultra-low-power clock generation circuit for EPC standard UHF RDID transponders," *Electronics Letters*, vol. 44, no. 3, pp. 199-201, 2008.

- [9] D. Seo, J. M. Carmena, J. M. Rabaey, E. Alon and M. M. Maharbiz, "Neural dust: An ultrasonic, low power solution for chronic brainmachine interfaces," arXiv:1307.2196 [q-bio.NC], 2013.

- [10] G. L. Barbruni, P. M. Ros, S. Aiassa, D. Demarchi and S. Carrara, "Body Dust: Ultra-Low Power OOK Modulation Circuit for Wireless Data Transmission in Drinkable sub-100 µm-sized Biochips," arXiv preprint arXiv:1912.02670, 2019.

- [11] P. Motto Ros, B. Miccoli, A. Sanginario and D. Demarchi, "Low-power architecture for integrated CMOS bio-sensing," 2017 IEEE Biomedical Circuits and Systems Conference (BioCAS), Turin, 2017, pp. 1-4.

- [12] A. Stillmaker and B. Baas, "Scaling equations for the accurate prediction of CMOS device performance from 180 nm to 7 nm," *Elsevier*, *Integration*, vol. 86, no. 58, pp. 74-81, 2017.

- [13] M. Crepaldi, M. Stoppa, P. Motto Ros and D. Demarchi, "An analogmode impulse radio system for ultra-low power short-range audio streaming," *IEEE Transactions on Circuits and Systems I*, vol. 62, no. 12, pp. 2886-2897, 2015.

- [14] X. Yi, X. Chen and R. Yao, "Frequency-adjustable clock oscillator based on frequency-to-voltage converter," *Electronics Letters*, vol. 45, no. 11, pp. 530-532, 2009.

- [15] Z. P. Bian and R. H. Yao, "Process, voltage and temperature compensation in a 1-MHz 130nm CMOS monolithic clock oscillator with 2.3% accuracy," *International Journal of Electronics*, vol. 102, no. 10, pp. 1652-1663, 2015.

- [16] P. Motto Ros, M. Crepaldi, A. Bonanno and D. Demarchi, "Wireless multi-channel quasi-digital tactile Sensing glove-based system," 2013 Euromicro Conference on Digital System Design, Los Alamitos, CA, 2013, pp. 673-680.

- [17] J. M. Rabaey, A. Chandrakasan and B. Nikolic, *Digital Integrated Circuits*, 2nd ed. Englewood Cliffs: Prentice Hall, 2002.

- [18] R. J. Baker, CMOS: circuit design, layout, and simulation, John Wiley & Sons, Chapter 13, 2019.