# ${\it Doctoral \ Dissertation}$ Doctoral Program in Computer and Control Engineering (33 $^{\rm rd}$ cycle)

# New Reliable Operation Infrastructure for Dynamic, High-dependability Applications

**Thomas Lange**

### **Supervisors**

Prof. Luca Sterpone, Supervisor Dr. Dan Alexandrescu, Supervisor

#### **Doctoral Examination Committee:**

Prof. Fernanda Lima Kastensmidt, Federal University of Rio Grande do Sul

Prof. Luis Entrena, University Carlos III de Madrid

Prof. Milos Krstic, University of Potsdam

Prof. Diana Göhringer, Dresden University of Technology

Politecnico di Torino April 2021

| This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see <a href="https://www.creativecommons.org">www.creativecommons.org</a> . The text may be reproduced for non-commercial purposes, provided that credit is given to the original author. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.                                                                                  |

| Thomas Lange<br>Turin, April 2021                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                       |

# Summary

Due to the technology scaling, lower supply voltages and higher operating frequencies, modern electronic devices become more and more vulnerable to transient faults. At the same time the number of transistors in a single chip and the complexity of modern systems is increasing. This creates a challenge for performing a reliability assessment on today's circuits and requires many resources in terms of human efforts, processing power and cost. The thesis addresses some of these issues by advancing current analysis techniques on higher abstraction levels, especially focusing on a functional analysis.

In the first part, two new machine learning based approaches are presented to assist the functional failure analysis of complex circuits. The methodologies aim to reduce the efforts needed to determine the functional failure rate of the circuit's sequential logic. The machine learning models use a feature set which was developed to characterizes each sequential element in the circuit. The features combine attributes from static elements and dynamic elements.

The objective of the first approach is to accelerate a fine grained functional failure analysis. It reduces computational cost to determine the Functional De-Rating (FDR) factors of the circuit's sequential logic. The aim is to predict factors per individual instances, which is particularly difficult to obtain using classical approaches such as clustering, selective fault simulation or fault universe compaction techniques. The methodology was applied in a practical example where several machine learning models were evaluated, predicting different failure classes. It was shown that the cost of a fault injection campaign can be reduced by a factor of 2 up to 5 in comparison to a classical statistical fault injection campaign. Further, the ability of the method to be used in early design phases has been assessed. Therefore, a feature subset was identified which can be extracted from an elaborated Register-Transfer Level (RTL) description of the design. The results have shown that the impact on the prediction performance was marginal.

The second machine learning based methodology uses clustering techniques to group flip-flops together which are expected to have a similar contribution to the overall functional failure rate. In this way the fault space is reduced which allows a more efficient fault injection strategy. The advantage in comparison to already other already existing clustering approaches is that this approach is more flexible and no assumption of the circuit or its representation is made. The effectiveness of the grouping by different

machine learning clustering algorithms was evaluated on a practical example and compared to a random and ideal solution. With the approach it was possible to reduce fault injection efforts by a factor of  $5\times$  to  $20\times$ .

Typical design flows are hierarchical and rely on assembling many individual technology elements from standard cells to complete boards. Providers use compact models to provide simplified views of their products to their users. Designers group simpler elements in more complex structures and have to manage the corresponding propagation of reliability and functional safety information through the hierarchy of the system, accompanied by the obvious problems of IP confidentiality, the possibility of reverse engineering, etc. Therefore, in the second part of the thesis, a methodology is proposed which aims to help experts to deal with the complexity of hierarchical modelling of reliability and functional safety metrics. The presented approach allows the use, elaboration and distribution of compact machine learning models in a uniform and systematic manner, minimizing both human and CPU efforts while maintaining high accuracy and fidelity. The trained machine learning models will be able to quickly evaluate a large variety of effects, encapsulating very useful reliability and functional safety data in a compact and efficient solution that can be used and reused further down the design and manufacturing flow.

In the third part of the thesis, the focus is shifted to Single-Event Transients (SETs) in Clock Distribution Networks (CDNs). A methodology is proposed to analyse how SETs in the clock distribution network are impacting the functional behaviour of a circuit. A methodology and a fault model are presented which implement the main radiationinduced effects in clock networks. The method enables the computation of the functional failure rate in a logic-level simulation based on the RTL description of the design. Thus, a faster evaluation can be performed than by simulating on the electrical level or gate-level. The analysis is extended by introducing a Temporal Masking effect for SETs in clock distribution networks. The Temporal Masking is based on the shortest input path delay of the flip-flops and the shortest output path delay, which are defining an SET Timing Window within the clock cycle. SETs occurring outside of this window are masked. The fault model was extended considering this Temporal Masking effect which allows to compute the functional failure rate weighted with Temporal De-Rating (TDR) of a circuit. The approach was applied in a practical example where SET were injected into the clock network of the circuit under test in a fault injection campaign. It was shown that the proposed Temporal Masking implementation is able to compute a pessimistic worst case.

# Acknowledgements

Firstly, I wish to show my gratitude to my thesis supervisor Luca Sterpone, Vice Head of the Department of Control and Computer Engineering of Politecnico di Torino and Associate Professor in the CAD group, for supporting my research, for his guidance, criticism and encouragement.

To my thesis co-supervisor Dan Alexandrescu, CEO of iRoC Technologies, I wish to express my sincere appreciation. I am grateful for his support and encouragement, as well as for granting me time to write my thesis.

My sincere thanks also go to the entire staff at iRoC Technologies for providing a professional environment which allowed me to substantially learn about the field of Soft Errors. Especially, I am grateful to Dr. Maximilien Glorieux, with whom I collaborated on several topics.

Finally, I thank Maksim Jenihhin, Professor in the Department of Computer Systems of Tallinn University of Technology, for originating and managing the RESCUE project, which funded my research position. The project gave me the opportunity to meet other Early Stage Researchers and have enriching discussions at the numerous workshops.

# **Contents**

| Su | mma   | ıry              |                                                         | III        |

|----|-------|------------------|---------------------------------------------------------|------------|

| A  | knov  | wledge           | ments                                                   | v          |

| Li | st of | Tables           |                                                         | X          |

| Li | st of | Figures          | S                                                       | XI         |

| Gl | ossaı | y                |                                                         | XIII       |

| 1  | Intr  | oducti<br>Struct | on cure of the Thesis                                   | <b>1</b> 2 |

| 2  | Sing  | gle-Eve          | ent Effects                                             | 5          |

|    | 2.1   | Mecha            | anism and Classification                                | 5          |

|    |       | 2.1.1            | Soft Errors                                             | 6          |

|    |       | 2.1.2            | Hard Errors                                             | 7          |

|    |       | 2.1.3            | Cumulative Effects                                      | 7          |

|    |       | 2.1.4            | Summary of Radiation Effects                            | 8          |

|    | 2.2   | Maski            | ng Mechanisms                                           | 8          |

|    |       | 2.2.1            | Electrical Masking                                      | 8          |

|    |       | 2.2.2            | Temporal Masking                                        | 9          |

|    |       | 2.2.3            | Logical Masking                                         | 12         |

|    |       | 2.2.4            | Functional Masking                                      | 13         |

|    |       | 2.2.5            | Summary of Masking Mechanisms                           | 15         |

|    | 2.3   | Soft E           | rror Analysis                                           | 15         |

|    |       | 2.3.1            | Technology Soft Error Rate Characterization             | 17         |

|    |       | 2.3.2            | De-Rating Characterization                              | 17         |

|    |       | 2.3.3            | Computing the Overall Soft Error Rate                   | 17         |

| 3  | Mac   | hine L           | earning Techniques for Functional Failure Rate Analysis | 19         |

|    | 3.1   | Introd           | luction                                                 | 19         |

|    | 3.2   | Machi            | ine Learning                                            | 20         |

|   | 3.3  | Flip-Fl | op Feature Set                                                         | 21         |

|---|------|---------|------------------------------------------------------------------------|------------|

|   |      | 3.3.1   | Feature Preprocessing                                                  | 23         |

|   | 3.4  | Circuit | t Under Test                                                           | 23         |

|   |      | 3.4.1   | Failure Classes and Fault Injection Campaign                           | 24         |

|   |      | 3.4.2   | Feature and Target Pre-Analysis                                        | 25         |

|   | 3.5  | Machi   | ne Learning Regression for Predicting Functional De-Rating Factors     | 27         |

|   |      | 3.5.1   | Methodology                                                            | 27         |

|   |      | 3.5.2   | Evaluation of Machine Learning Regression Models for Predict-          |            |

|   |      |         | ing Functional De-Rating Factors                                       | 30         |

|   |      | 3.5.3   | Functional De-Rating Prediction on the Register-Transfer Level         | 39         |

|   | 3.6  | Machi   | ne Learning Clustering for Selective Mitigation                        | 41         |

|   |      | 3.6.1   | Clustering Techniques for Selective Mitigation                         | 42         |

|   |      | 3.6.2   | Methodology                                                            | 43         |

|   |      | 3.6.3   | <b>Evaluating Machine Learning Clustering for Selective Mitigation</b> | 44         |

|   | 3.7  | Conclu  | ısion                                                                  | 51         |

| 4 | Cros | ss-Laye | r Reliability and Functional Safety Assessment Through Ma-             |            |

|   |      | e Leari | ·                                                                      | <b>5</b> 3 |

|   | 4.1  | Introd  | uction                                                                 | 53         |

|   | 4.2  | Motiva  | ation                                                                  | 54         |

|   | 4.3  | Metho   | dology                                                                 | 57         |

|   | 4.4  | Demoi   | nstration on an Example                                                | 58         |

|   | 4.5  | Conclu  | asion                                                                  | 66         |

| 5 | Fun  | ctional | Failures Induced by Single-Event Transients in Clock Distri-           |            |

|   | buti | on Net  | works                                                                  | 67         |

|   | 5.1  | Introd  | uction                                                                 | 67         |

|   | 5.2  | Single- | -Event Effect Mechanisms with Regard to Clock Distribution Net-        |            |

|   |      | works   |                                                                        | 68         |

|   | 5.3  | Metho   | dology                                                                 | 69         |

|   |      | 5.3.1   | Fault Model for the Functional Level                                   | 69         |

|   |      | 5.3.2   | Temporal De-Rating                                                     | 72         |

|   | 5.4  |         | njection Campaign                                                      | 74         |

|   |      | 5.4.1   | Test Circuit, Testbench and Clock Distribution Network                 | 74         |

|   |      | 5.4.2   | Clock-SET Fault Injection Campaign                                     | 75         |

|   |      | 5.4.3   | Methodology to Approximate the Clock-SET Temporal De-Rating            | 78         |

|   |      | 5.4.4   | Results for Temporal Masking of SEUs in the Sequential Logic .         | 78         |

|   |      | 5.4.5   | Comparison and Discussion                                              | 81         |

|   | 5 5  | Concli  | ision                                                                  | 82         |

| 6  | Con   | clusion                                                                 | 85 |

|----|-------|-------------------------------------------------------------------------|----|

|    | 6.1   | Machine Learning Techniques for Functional Failure Analysis             | 85 |

|    | 6.2   | Cross-Layer Reliability and Functional Safety Assessment Through Ma-    |    |

|    |       | chine Learning                                                          | 86 |

|    | 6.3   | Functional Failures Induced by Single-Event Transients in Clock Distri- |    |

|    |       | bution Networks                                                         | 86 |

|    | 6.4   | Summary                                                                 | 87 |

| Bi | bliog | raphy                                                                   | 89 |

# **List of Tables**

| 2.1 | SET Pulse Alignment Cases and Corresponding Capture Probabilities .     | 13 |

|-----|-------------------------------------------------------------------------|----|

| 3.1 | Feature Set to Characterise a Flip-Flop Instance $FF_i$                 | 22 |

| 3.2 | SEU Fault Injection Campaign Results                                    | 25 |

| 3.3 | Performance Results for the Evaluated Regression Models (With Cross     |    |

|     | Validation = 10 and Training Size = 50 %)                               | 32 |

| 3.4 | Performance Comparison by Using Different Feature Subsets (With Cross   |    |

|     | Validation = 10 and Training Size = 50 %)                               | 41 |

| 3.5 | Comparison of the Different Clustering Algorithm                        | 50 |

| 4.1 | Neutron Flux Acceleration Factors                                       | 60 |

| 4.2 | Generated SER Values                                                    | 61 |

| 4.3 | Top Machine Learning Model Performance                                  | 65 |

| 5.1 | Results of the Clock-SET Fault Injection Campaigns with and without     |    |

|     | Temporal Masking                                                        | 77 |

| 5.2 | Estimated Timing De-Rating Factors                                      | 81 |

| 5.3 | Results of the SEU Fault Injection Campaign                             | 81 |

| 5.4 | Results of the Sequential Temporal De-Rating Analysis                   | 82 |

| 5.5 | Summary of the Functional Failure Rate Analysis of the 10GE MAC circuit | 82 |

# **List of Figures**

| 2.1  | Energetic particle striking through a transistor                                     | 6  |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | Temporal Masking of SEUs                                                             | 10 |

| 2.3  | Temporal Masking of SETs                                                             | 11 |

| 2.4  | SET pulse alignment cases                                                            | 12 |

| 2.5  | Logical Masking of SEUs and SETs                                                     | 14 |

| 2.6  | Single-Event Effects analysis                                                        | 16 |

| 3.1  | The Pearson Correlation of features and targets                                      | 26 |

| 3.2  | Functional De-Rating estimation and evaluation flow                                  | 28 |

| 3.3  | Prediction of the Output Failure for one test data fold (training size =             |    |

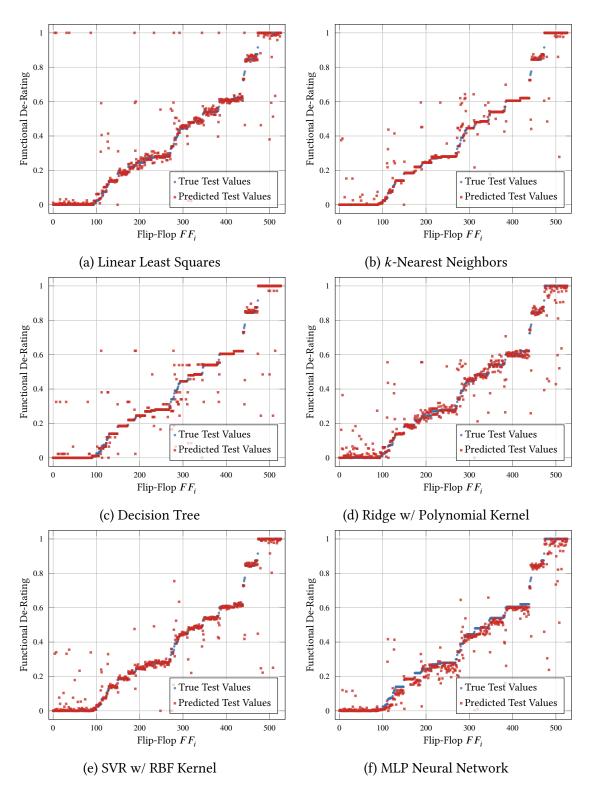

|      | 50 %)                                                                                | 34 |

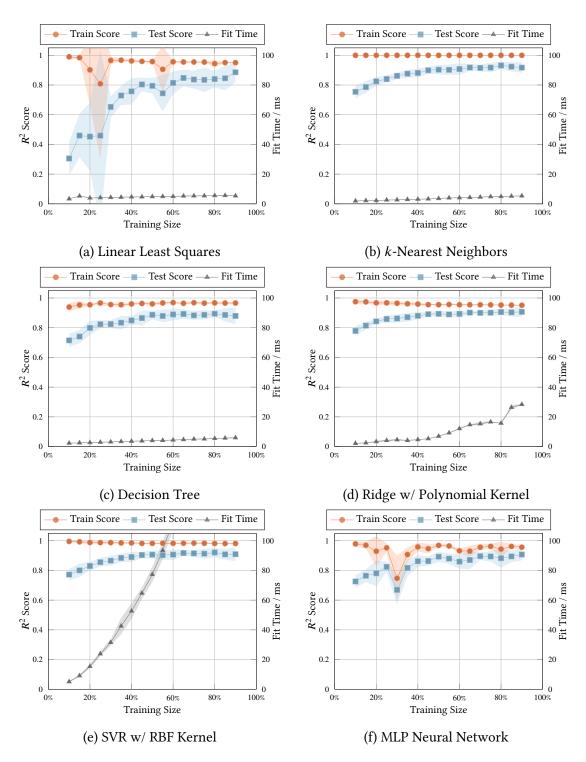

| 3.4  | Learning curve and fit time predicting the Output Failure (cross valida-             |    |

|      | tion = 10)                                                                           | 35 |

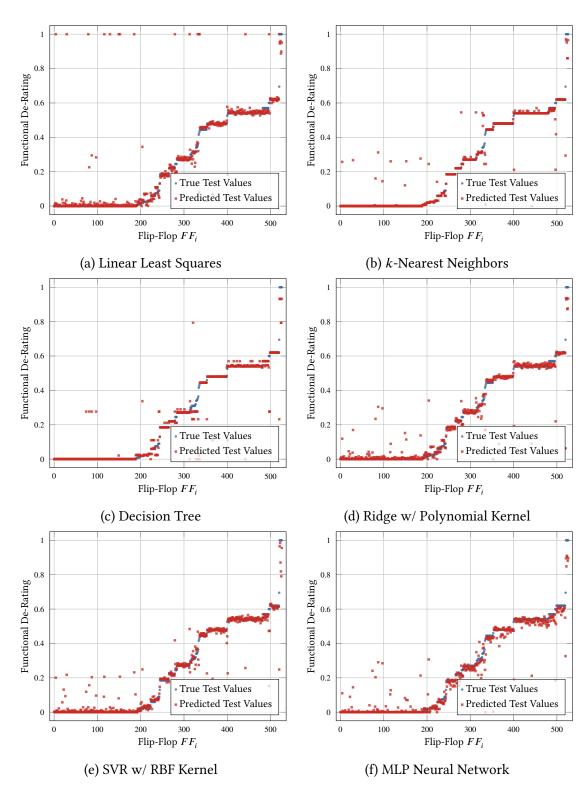

| 3.5  | Prediction of the Application Failure for one test data fold (training size          |    |

|      | = 50 %)                                                                              | 37 |

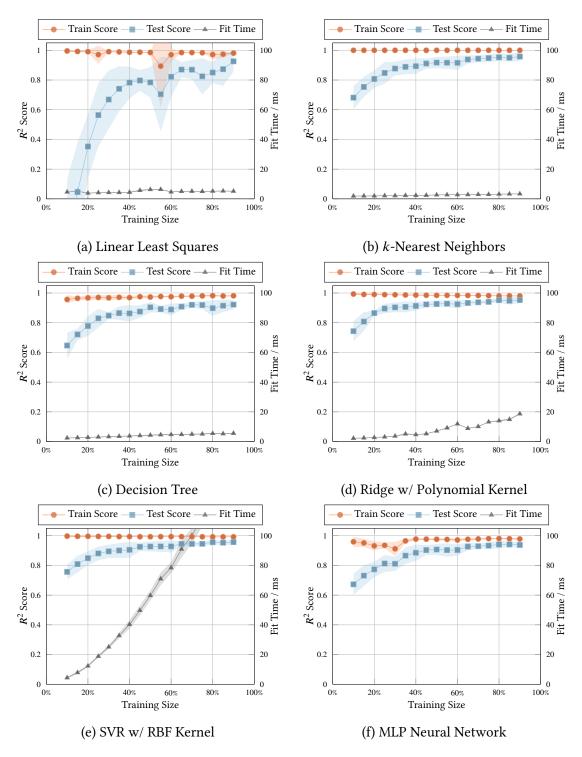

| 3.6  | Learning curve and fit time predicting the Application Failure (cross                |    |

|      | validation = 10)                                                                     | 38 |

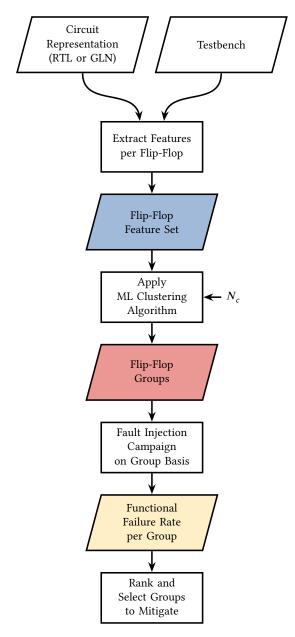

| 3.7  | Selective mitigation by using machine learning clustering                            | 44 |

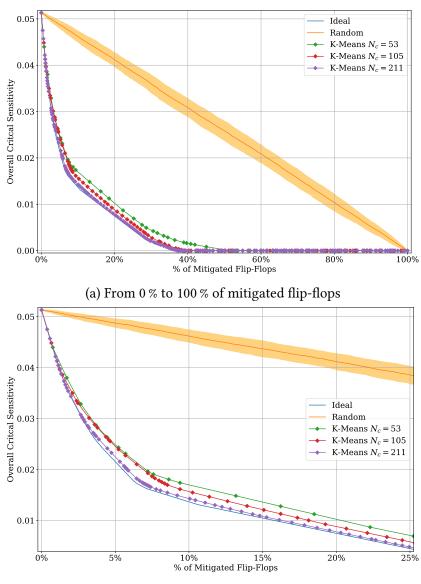

| 3.8  | K-Means Clustering                                                                   | 46 |

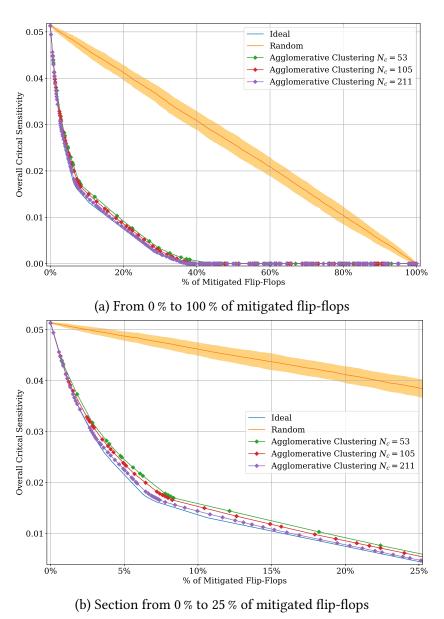

| 3.9  | Agglomerative Clustering                                                             | 47 |

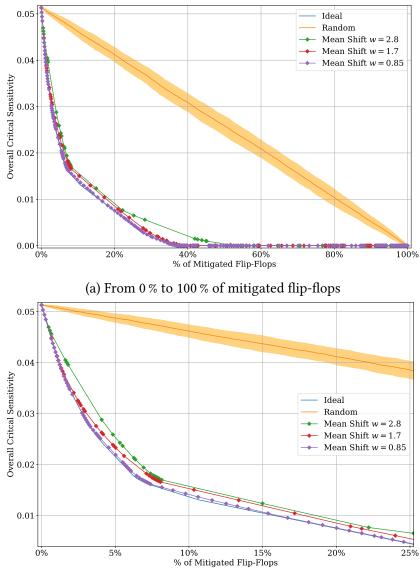

| 3.10 | Mean Shift Clustering                                                                | 48 |

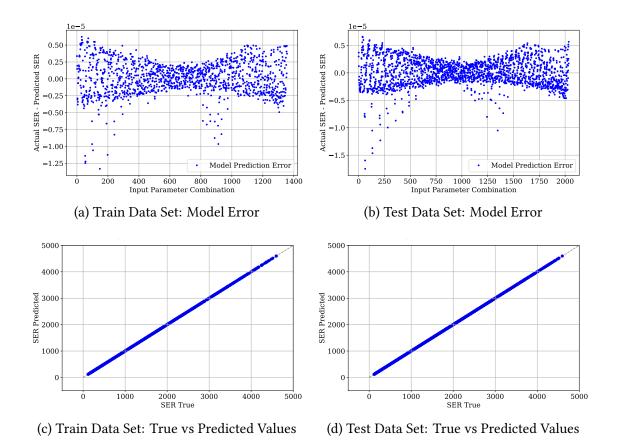

| 4.1  | Results of predicting the train and test data set by using Ridge regression          |    |

|      | with polynomial kernel                                                               | 62 |

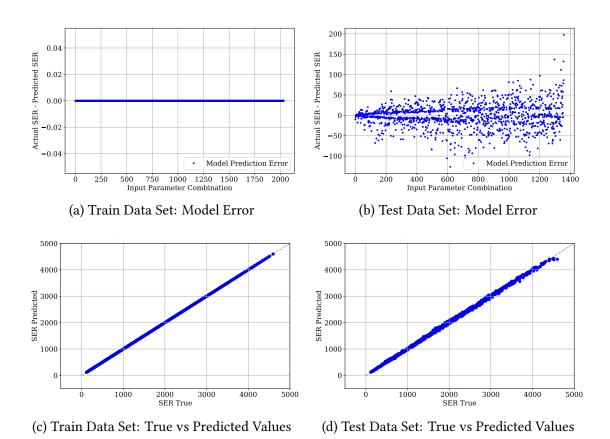

| 4.2  | Results of predicting the train and test data set by using k-Nearest Neigh-          |    |

|      | bors regression.                                                                     | 63 |

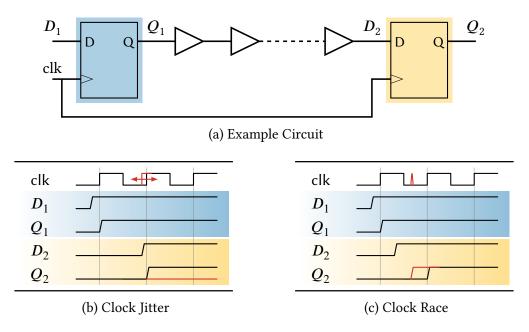

| 5.1  | Main effects caused by transients in the clock distribution network                  | 69 |

| 5.2  | Proposed fault model for Single-Event Transients in clock distribution               |    |

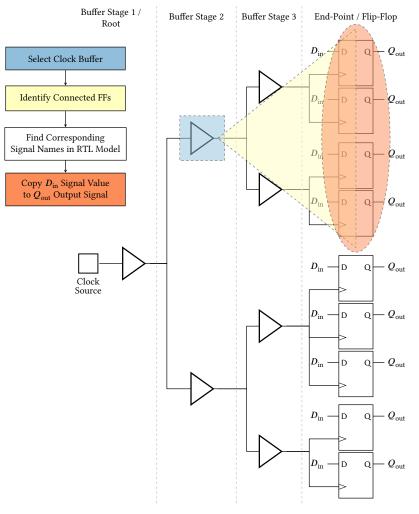

|      | networks based on logic level simulation                                             | 70 |

| 5.3  | Simplified extract of a clock network and connected flip-flops                       | 72 |

| 5.4  | Temporal masking mechanism for SETs in the clock distribution network.               | 73 |

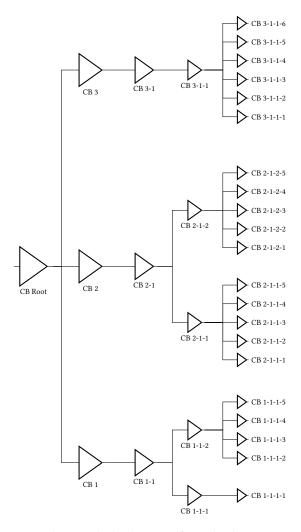

| 5.5  | Obtained clock tree after clock tree synthesis                                       | 75 |

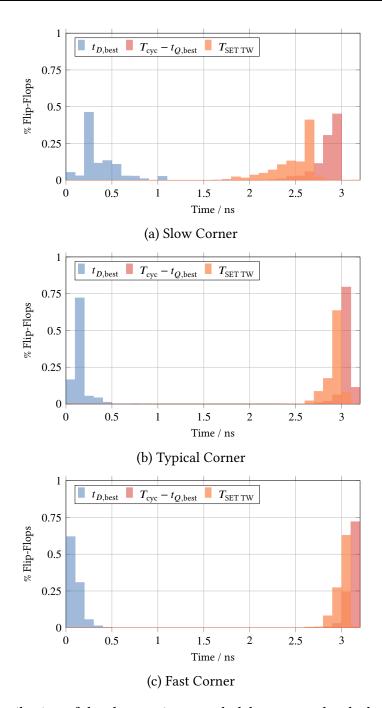

| 5.6  | Distribution of the shortest input path delay $t_{D,\text{best}}$ , the slack of the |    |

|      | shortest output path and the SET Timing Window length $T_{\text{SET TW}}$            | 79 |

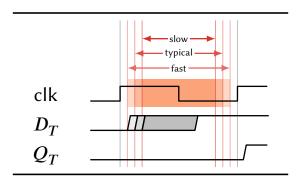

| 5.7 | Length of the SET Timing Window $T_{\text{SET TW}}$ for different operating con- |    |  |  |

|-----|----------------------------------------------------------------------------------|----|--|--|

|     | ditions                                                                          | 80 |  |  |

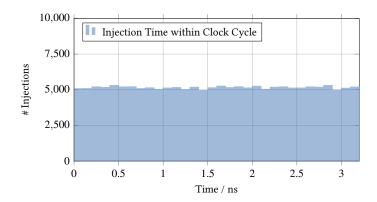

| 5.8 | Distribution of the injection times within the clock cycle                       | 80 |  |  |

# Glossary

```

ASIC Application Specific Integrated Circuit. 53, 55, 60, 62

CDN Clock Distribution Network. iv, 2, 3, 86

CMOS Complementary Metal-Oxide-Semiconductor. 8

CPU Central Processing Unit. 15, 24, 31, 55

CRC Cyclical Redundancy Check. 23

CUT Circuit Under Test. 14

DRAM Dynamic Random-Access Memory. 7

ECC Error Correcting Code. 55

EDC Error Detection Correction. 55

EDR Electrical De-Rating. 8, 68

FDR Functional De-Rating. iii, 13, 27, 31, 60, 68, 76, 78, 85

FET Field Effect Transistor. 7

FIFO First-In First Out. 23, 74

FIT Failure in Time. 1, 62, 81

FPGA Field Programmable Gate Array. 7

FuSa Functional Safety. 53, 55, 57, 64

GRF Geomagnetic Rigidity Factor. 59

IC Integrated Circuit. 1, 2

IP Intellectual Property. 55

```

LDR Logical De-Rating. 12, 60, 68

MBU Multiple Bit Upset. 54

MCU Multiple Cell Upset. 54, 55

**ML** Machine Learning. 57

MOS Metal-Oxide-Semiconductor. 7

NF Neutron Flux. 59

PDK Process Design Kit. 53, 54

**PIPB** Propagation Induced Pulse Broadening. 12

PLL Phase Locked Loop. 54, 68

PVT Process, Voltage, Temperature. 66

**PW** Pulse Width. 10, 11, 58, 62

RTL Register-Transfer Level. iii, iv, 69, 71, 74, 86

SBU Single Bit Upset. 54, 55

**SDF** Standard Delay Format. 76

**SEB** Single Event Burnout. 7

**SEE** Single-Event Effect. 5, 8, 16, 54, 55, 59

**SEFI** Single-Event Functional Interrupt. 7

**SEGR** Single-Event Gate Rapture. 7

**SEL** Single-Event Latch-up. 7

**SEMT** Single-Event Multiple Transient. 6

**SEMU** Single-Event Multiple Upset. 6

**SER** Soft Error Rate. 2, 16, 58–60, 62

**SET** Single-Event Transient. iv, 2, 3, 6, 8, 54, 58, 82, 83, 86, 87

**SEU** Single-Event Upset. 6, 8, 54, 55

**SRAM** Static Random-Access Memory. 1

${\bf STA}\;$  Static Timing Analysis. 74

**TDR** Temporal De-Rating. iv, 9, 60, 68, 87

**TID** Total Ionizing Dose. 66

**TMR** Triple Modular Redundancy. 45

# Chapter 1

# Introduction

The advancement in technology enabled the development of complex electronic systems and made it possible to embed more and more functionality into single devices and manufacture Integrated Circuits (ICs) with tens of millions of transistors. This trend led to a higher integration of electronics in our day-to-day lives, including critical applications where human lives is at stake. Especially, for these critical applications a reliable operation is extremely important.

A significant threat to the reliable operation of a system are transient faults induced by natural radiation. Without any mitigation the fault can propagate and manifest as an error in the system. This generated error can then lead to misbehaviour of the functionality and thus, creating a failure [57].

In the past radiation induced faults were mainly a problem for applications which demand a very high reliability, such as aero-space, nuclear facilities, and medical devices. However, due to the technology advancements the size of transistors is scaling down, devices operate with lower supply voltages and at higher operating frequencies which makes them more vulnerable to faults induced by radiation [8, 9]. Thus, radiation induced faults become also a greater hazard for systems working in normal environments and it is no longer possible to ignore them.

Today's reliability standards and customers' expectations set tough targets for the quality of electronic devices and systems. Among other reliability threats, the transient faults are known to contribute significantly to the overall failure rate of the system and possibly exceeding the set reliability targets. As an example, standard flip-flops and Static Random-Access Memory (SRAM) memories, manufactured in relatively recent technologies exhibit error rates of hundreds of events (Failure in Times (FITs); failures that can be expected in one billion working hours of operation) [9, 67]. Complex circuits using such cells can easily overshoot 10 FIT target mandated by the ISO 26262 standard [38] for an automotive ASIL D application.

A vast amount of research is devoted to analyse and mitigate these effects, with the focus on achieving accurate results when analysing relatively small circuits. Current

trends show, however, that the total number of ICs is growing and a large part of performance increase nowadays comes from parallelism, which translates in an increase of the total number of transistors per IC (Moore's Law [52]). This results in larger and more complex systems and the required effort, in terms of human resources, computation power and cost, is vastly increasing.

### 1.1 Structure of the Thesis

The focus of the thesis is on the advancement of the soft error analysis on higher abstraction levels. The main contributions consist of improvement in fault-injection simulations, a technique to reduce the fault space and a technique to model Single-Event Transients (SETs) in Clock Distribution Networks (CDNs) on the functional level.

The thesis will be organized as follows:

- Chapter 2: This chapter provides a summary of single-event effects, their causes and the basic masking mechanism. An overview of techniques to analyse fault propagation and determine the de-rating factors are described. Finally, the common methodology to calculate the overall Soft Error Rate (SER) is presented.

- Chapter 3: This chapter investigates the usage of machine learning techniques for the fault analysis on the functional level. Two new machine learning based methodologies are presented, which are using a feature set developed to characterise each sequential element in the circuit.

- The first approach aims to accelerate fine grained functional fault analysis on sequential cells. It uses regression models in a supervised approach to train machine learning models on the functional failure rates of the sequential cells in the circuit. The objective of the second approach is to reduce the fault space of the functional fault analysis. The technique is based on machine learning clustering techniques and groups flip-flops together which are expected to have a similar sensitivity to faults.

- Chapter 4: This chapter proposes a machine learning based methodology to tackle the complexity of hierarchical modelling of reliability and functional safety metrics. The presented approach allows the use, elaboration and distribution of compact machine learning models in a uniform and systematic manner, minimizing both human and CPU efforts while maintaining high accuracy and fidelity.

- Chapter 5: This chapter describes a methodology to simulate Single-Event Transients in the Clock Distribution Network on a higher abstraction level. A fault model was developed which implements the main radiation induced faults in clock networks by performing logic-level simulation. Additionally, the Temporal Masking effect for this type of faults is explored and the fault model is extended accordingly.

• Chapter 6: This is the last chapter and concludes the thesis and discusses plans for future work.

Overall, the thesis seeks to advance the fault analysis on the functional level. Therefore, chapter 2 describe the state-of-the-art methodologies and Chapter 3 applies Machine Learning techniques and thus, present novel methods to increase the efficiency of the fault analysis. Chapter 5 shifts the focus to the analysis of SETs in CDNs. Together, these techniques facilitate the analysis of radiation induced faults in complex integrated circuits on a higher abstraction level.

# **Chapter 2**

# **Single-Event Effects**

The amount of information processed of modern system is increasing which requires a higher performance and results in a higher complexity of the implemented circuits. This trend is also requested in markets which demand a high reliability and are usually running safety-critical applications, such as aerospace and the automotive market. These new requirements lead to the usage of smaller transistors technology, lower voltages and higher operating frequencies which makes them more prone to radiation induced transient faults. In order to cope with the additional complexity and new technologies of modern systems the research aims at the development of new assessment and mitigation techniques for transient faults and new test methodologies for complex electronic systems.

Due to technology scaling, lower supply voltages and higher operating frequencies, modern circuits become more and more vulnerable to reliability threats. Additionally, today's reliability standards and customers' expectations set tough targets for the quality of electronic devices and systems. Especially, transient faults, such as Single-Event Upsets and Single-Event Transients in the individual sequential and combinational cells, have been identified as the leading contributor to the overall failure rate for many applications [8, 9, 66].

### 2.1 Mechanism and Classification

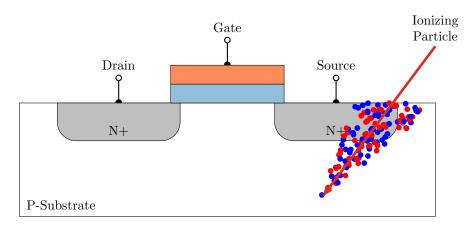

Single-Event Effects (SEEs), are caused by a single, energetic particle striking through a silicon device and depositing electrical charge, as shown in figure 2.1. On ground, the main sources of these energetic particles are alpha particles, high-energy neutrons and thermal neutrons [9]. The radiation environment in space is much harsher. Primarily, there are cosmic rays which are consisting of protons, alpha particles and heavy nuclei [35]. The earth's atmosphere and magnetic field blocks most of these cosmic particles. However, these particles can strike atoms in the atmosphere and create chains of secondary and tertiary particles [82].

Figure 2.1: Energetic particle striking through a transistor.

The occurring subsequent effects in an electronic circuit, due to radiation effects, depend on the type of circuit, the energy of the particles and the nature of the strike. The effects can be classified in hard errors, soft errors and cumulative effects. While it may be possible to recover from soft errors by a reset of the application, a power cycle of the device, or by overwriting the corrupted information, hard errors are non-recoverable. In the following a summary of the different effects is provided.

#### 2.1.1 Soft Errors

#### **Single-Event Transient**

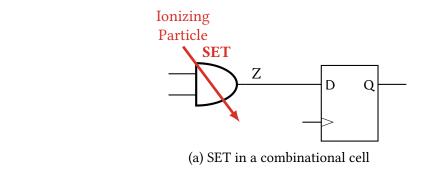

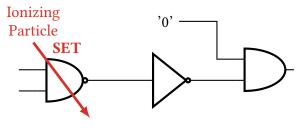

This effect occurs when the energetic particle is depositing the charge near the combinational logic cells of the circuit. The charge is then collected at one of the transistor nodes of the logic cells and thus, creating a transient current pulse, also called SET. SETs usually appear in the combinational cells of the circuit. They can also appear in the sequential element (such as a flip-flop or a latch) in the case the Single-Event only affects the output stage but not the internal feedback loop of the cell [3]. When a single particle affects more than one combinational gate, the effect is called Single-Event Multiple Transient (SEMT) [34]. This fault becomes an error when it propagates through the combinational logic and eventually is latched by at least one of the sequential elements during the sampling window [29].

#### **Single-Event Upset**

A Single-Event Upset (SEU) occurs when the induced charge of the energetic particle is causing the logic state of a discrete sequential element, such as a latch, a flip-flop or a memory cell, to change. In the case where a single particle affects more than one sequential cell, the effect is called Single-Event Multiple Upset (SEMU) [21].

#### **Single-Event Functional Interrupt**

The Single-Event Functional Interrupt (SEFI) refers to a loss of functionality in a more complex device, e.g. Dynamic Random-Access Memory (DRAM), Field Programmable Gate Array (FPGA), Microprocessor, etc. This can be the case, for example, when an SEU occurs in the control logic of the circuit. An SEFI does not lead to a permanent damage and can be recovered by resetting the device or performing a power cycle.

#### Single-Event Latch-up

A Single-Event Latch-up (SEL) is a latch-up caused by a radiation induced event. The deposited charge by the energetic particle triggers a parasitic structure in a transistor and thus, creating a short circuit from power to ground [68]. This disrupts the function of the transistor and due to the increased current consumption, can lead to a destruction of the part and thus, to a hard error. A power cycle is required in order to restore to normal operation.

#### 2.1.2 Hard Errors

#### **Single-Event Burnout**

When the energetic particle causes a power Field Effect Transistor (FET) to enter a second breakdown, the event is called Single Event Burnout (SEB). This results in a very high current and causes the device metal traces to vaporize, bond wires to fuse open and silicon regions to melt due to the thermal increase [68].

#### Single-Event Gate Rapture

The Single-Event Gate Rapture (SEGR) is initiated when the energetic particle strikes through a Metal-Oxide-Semiconductor (MOS) power transistor. The additional induced carriers are accelerated by the electric field, which in turn increases the field and eventually may cause the dielectric to breakdown [68]. This permanently damages the transistor.

#### 2.1.3 Cumulative Effects

Cumulative effects describe the long-term effects on the electronic devices, and the resulting degradation, due to exposure to radiation.

#### **Total Ionizing Dose**

The deposited charge by the radiation can be trapped in the oxide layer of the transistor. This can cause a shift in the switching characteristics, increased device leakage and

power consumption, and timing changes. This leads to a decreased functionality of the transistor and in the worst case can cause a circuit failure.

#### **Displacement Effects**

When highly energized particles striking the device they may displace the atoms in the silicon lattice. Although Complementary Metal-Oxide-Semiconductor (CMOS) devices are known not to be sensitive to displacement damage, bipolar and optical devices are very sensitive to this effect.

### 2.1.4 Summary of Radiation Effects

In order to analyse the overall SEE sensitivity of a system, all the described effects must be considered. However, in large digital circuits, the majority of failures are usually caused by SEU and SET. Therefore, the focus of this thesis is on analysing these effects.

# 2.2 Masking Mechanisms

When a radiation induced fault propagates in the system it can lead to observable effects up to the system level. Fortunately, not all faults necessarily manifest themselves as errors or failures in the system. There are several effects which can mask the event and de-rate the raw rate of faults. These effects are quantified by the de-rating factors which then can be used to determine the effective error rate.

The de-rating factor in this work is defined in such a way that, a value of 1.0 indicates that the faults are not masked and all of them propagate, leading to an error. A value of 0.0 on the other hand indicates that all faults are masked and none of them propagates.

In [55, 2] four main masking mechanisms are defined with their corresponding derating factors which can reduce the effect of SEEs on the actual error rate significantly.

### 2.2.1 Electrical Masking

Digital logic operates between logical zero and one values. To discriminate between these values the signals have to cross a switching threshold. The current pulse created from an SET may not be strong enough to change the voltage above the switching threshold on the effected node. Further, due to the capacitance and limited slew rates of the digital logic gates, a transient current pulse is usually narrowed and its rise and fall time is increased during the propagation. By the time it reaches the end of the path, either it has been completely filtered or the voltage transition is below the switching threshold! [32, 75]. The reduction of the fault rate due to these effects can be described as Electrical De-Rating (EDR).

### 2.2.2 Temporal Masking

Almost all digital circuits are synchronous. This means for a fault to propagate, it must be sampled by the sequential elements. A fault must occur within an opportunity window (OW) to be latched by a sequential element on the downstream path. If the fault misses this opportunity window it does not affect the behaviour of the circuit and is masked [65, 56, 30, 13]. The Temporal De-Rating (TDR) describes the reduction of the fault rate due to these effects and can be calculated depending on the type of fault.

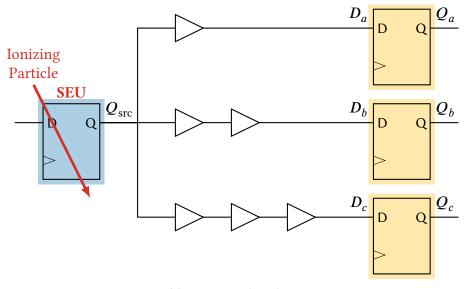

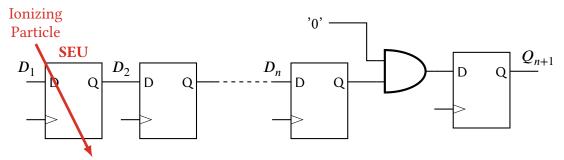

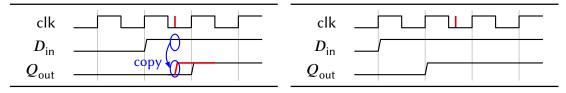

#### **Temporal De-Rating for SEUs**

An SEU in a sequential logic must occur sufficiently early in the clock cycle in order to meet the setup time of the flip-flops on the downstream path. Figure 2.2 shows the masked and unmasked case of an SEU in a flip-flop which is propagating to the flip-flops connected on the downstream path. Unless the SEU is masked otherwise, the fault will always propagate through the combinational network and reach the next sequential logic stage. The faulty flip-flop value remains on the output until the new value is latched in the next clock cycle.

The occurrence of an SEU can be considered uniform within the clock cycle. The opportunity window depends on the slack of the considered path, as well as the setup and hold time of the flip-flop on the downstream path [57]. The Temporal De-Rating for SEUs  $\mathrm{TDR}_{\mathrm{SEU}}$  is then defined as the ratio between the opportunity window and the clock period  $T_{\mathrm{cycle}}$

$$TDR_{SEU} = \frac{t_{\text{slack}} + \frac{t_{\text{setup}}}{2} - \frac{t_{\text{hold}}}{2}}{T_{\text{cycle}}}$$

(2.1)

According to the equation it can be derived that the opportunity window for an SEU is increasing with the slack of the downstream path and thus, the probability of an SEU being captured. In the case the SEU caused a setup or hold validation it is uncertain whether the fault is captured or not. The Temporal De-Rating can also be approximated with the ratio of the path slack to the clock period

$$TDR_{SEU} \approx \frac{t_{slack}}{T_{cycle}}$$

(2.2)

For the critical path in the circuit the slack is very low. For these paths the opportunity window is quite short which reflects in a low probability for the fault to propagate. Therefore, it can be reasoned that the Temporal Masking of SEUs is increasing with higher clock frequencies and vice versa, is increasing with lower clock frequencies.

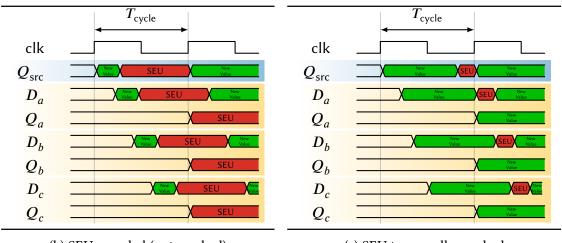

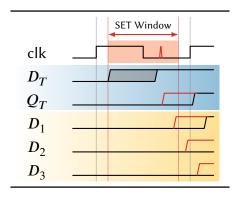

#### **Temporal Masking for SETs**

Similar to SEUs, SETs can also be subject to temporal masking. Single-Event Transients cause short pulses on the output of the affected cell. This transient pulse has to occur

(a) SEU in a Flip-Flop

(b) SEU sampled (not masked)

(c) SEU temporally masked

Figure 2.2: Temporal Masking of SEUs.

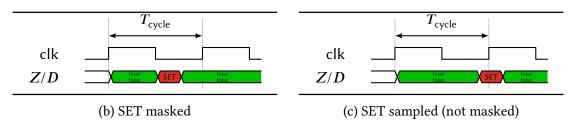

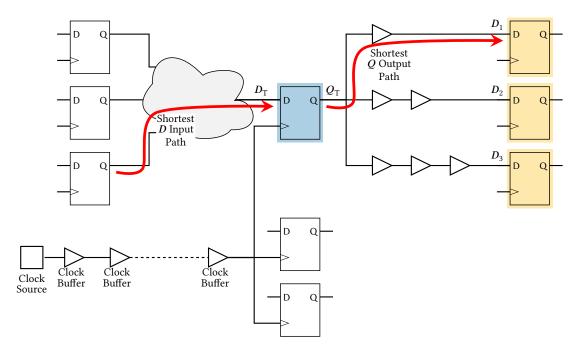

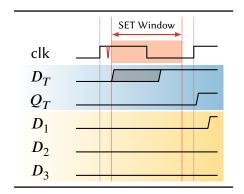

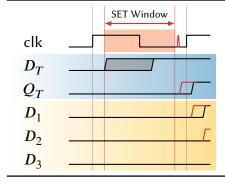

and propagate to the input of the sequential logic during its latching window. The masked and unmasked cases of an SET are shown in figure 2.3.

Unless otherwise masked, the SET is propagating thorough the combinational network and eventually, will reach a sequential element. Since the occurrence of the SETs can be considered as uniform within the clock cycle, a first approximation of the Temporal De-Rating TDR<sub>SET</sub> can be calculated as the ratio of the transient's Pulse Width

Figure 2.3: Temporal Masking of SETs.

(PW) to the clock period  $T_{

m cycle}$

$$TDR_{SET} = \frac{\int_{w=\min(PW)}^{w=\max(PW)} w \, dw}{T_{cycle}}$$

(2.3)

Many of today's circuit still run with clock periods in the nanosecond range. For recent technologies, studies show that the pulse duration of the combinational cells is in the range of picoseconds [19]. With the equation (2.3) it can be concluded that the Temporal Masking for SETs is quite high. However, the trend of modern circuits is going to higher operating frequencies which decreases the Temporal Masking and as further studies suggest, the effect of SETs become severe [56, 31, 47].

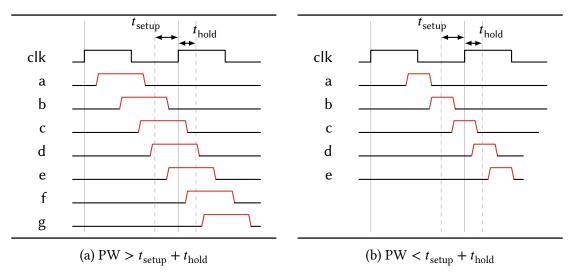

**SET Pulse Alignment Cases** The exact probability of the transient pulse to be latched depends on when it arrives at the input of the sequential element and how it is aligned to the sampling clock edge. Figure 2.4 shows all of these possible alignment cases. Figure 2.4a shows the case when the PW of the transient is longer than the setup-hold window of the sequential element and figure 2.4a shows the case when the pulse width is shorter. An Overlapping Width is defined as the part of the pulse that falls within the setup-hold window. In the case the pulse width is longer than the setup-hold window (PW >  $t_{\rm setup} + t_{\rm hold}$ ), the probability the fault is captured is considered to be proportional to the ratio of Overlapping Width (OW) to the setup-hold window  $\frac{\rm OW}{t_{\rm setup} + t_{\rm hold}}$ . In the case the pulse width is shorter than the setup-hold window (PW <  $t_{\rm setup} + t_{\rm hold}$ ),

the caused violations by the fault are treated together. The error latching probability is assumed to be linear with the Overlapping Width ratio [19].

Figure 2.4: SET pulse alignment cases.

For each case the corresponding latching probability is shown in table 2.1. Since an SET can occur uniformly within the clock cycle, the latching probability can be averaged over the full clock period. The overall latching probability for both cases is then  $\frac{PW}{T_{\rm cycle}}$ .

For this analysis, the discussed pulse width in figure 2.4 and table 2.1 is the one seen at the input of the sequential element. As the transient pulse propagates through the combinational network, it might be distorted. This effect is called Propagation Induced Pulse Broadening (PIPB) [26, 73, 27].

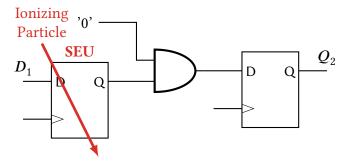

### 2.2.3 Logical Masking

If the propagation of a fault is prevented due to the state of the combinational network the fault is considered as logically masked. This can be due to a controlling input of a gate such as a zero value on a 2-input AND gate, as shown in figure 2.5. An SEU can either be masked in the same cycle it occurs (figure 2.5a), or it may be masked several cycles later (figure 2.5b). An SET can masked in the same way as SEUs as shown in figure 2.5c [57, 78].

The reduced fault rate due to these effects are quantified by the Logical De-Rating (LDR). For the evaluation of the LDR only a representation of the circuit without any knowledge of the function is required. Usually, the propagation of the fault starting from the output of the affected cell to the inputs of a sequential element is considered.

Table 2.1: SET Pulse Alignment Cases and Corresponding Capture Probabilities

| Pulse Width                               | Case | Error Probability                                                                                                                                             | Comments              |

|-------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                           | a    | 0                                                                                                                                                             | correct value latched |

|                                           | b    | $rac{1}{T_{ m clk}} \cdot \int_0^{t_{ m setup}} rac{ m OW}{t_{ m setup} + t_{ m hold}}  { m dOW}$                                                           | setup time violation  |

|                                           | c    | $\frac{1}{T_{\text{clk}}} \cdot \int_{t_{\text{setup}}}^{t_{\text{setup}}+t_{\text{hold}}} \frac{\text{OW}}{t_{\text{setup}}+t_{\text{hold}}}  d\text{OW}$    | hold time violation   |

| $PW > t_{\text{setup}} + t_{\text{hold}}$ | d    | $rac{	ext{PW} - t_{	ext{setup}} - t_{	ext{hold}}}{T_{	ext{cll}}}$                                                                                            | wrong value latched   |

|                                           | e    | $\frac{1}{T_{\text{clk}}} \cdot \int_{t_{\text{hold}}}^{t_{\text{setup}} + t_{\text{hold}}} \frac{\text{OW}}{t_{\text{setup}} + t_{\text{hold}}}  \text{dOW}$ | setup time violation  |

|                                           | f    | $\frac{1}{T_{ m clk}} \cdot \int_0^{t_{ m hold}} \frac{{ m OW}}{t_{ m setup} + t_{ m hold}}  { m dOW}$                                                        | hold time violation   |

|                                           | g    | 0                                                                                                                                                             | correct value latched |

|                                           | a    | 0                                                                                                                                                             | correct value latched |

|                                           | b    | $\frac{1}{T_{ m clk}} \cdot \int_0^{t_{ m setup}} \frac{ m OW}{t_{ m setup} + t_{ m hold}}  { m dOW}$                                                         | setup time violation  |

| $PW < t_{\text{setup}} + t_{\text{hold}}$ | c    | $\frac{\text{PW} \cdot (t_{\text{setup}} + t_{\text{hold}} - \text{PW})}{T_{\text{clk}} \cdot (t_{\text{setup}} + t_{\text{hold}})}$                          | metastability         |

|                                           | d    | $\frac{1}{T_{\text{clk}}} \cdot \int_0^{t_{\text{hold}}} \frac{\text{OW}}{t_{\text{setup}} + t_{\text{hold}}}  \text{dOW}$                                    | hold time violation   |

|                                           | e    | 0                                                                                                                                                             | correct value latched |

| Overall                                   | -    | $rac{	ext{PW}}{T_{	ext{clk}}}$                                                                                                                               | -                     |

### 2.2.4 Functional Masking

For the functional masking the fault is considered at an applicative level and takes the actual usage of the circuit and the function of the system into account. This means even when an SEU or SET is able to propagate (is not masked by any other masking effect), the impact at the function of the circuit can vary. The SEU or SET might significantly change the state of the circuit, however in many cases is benign. The fault could, for example, lead to a faulty pixel in a video stream or cause a delay of a data packet in a networking application. The effect on the functional behaviour in these cases is probably very minor.

The de-rating due to the functional behaviour of the circuit is referred to as Functional De-Rating (FDR) and can be quite significant [71, 57]. In comparison to the other masking effects the de-rating highly depends on the criteria defining the acceptable behaviour of the circuit during the execution of an application. This can include objective

(a) Logical Masking of an SEU

(b) Logical Masking of an SEU after *n* clock cycles

(c) Logical Masking of an SET

Figure 2.5: Logical Masking of SEUs and SETs.

aspects, as well as subjective aspects to define a fault-free or faulty behaviour of the system. An objective criterion would be for example, the behaviour of the primary outputs of the Circuit Under Test (CUT). Any difference to the fault-free reference could be classified as a failure. A subjective criterion, however, might take the actual criticality of the observed difference into account. The observed difference in the primary output might not be relevant for specific cases or applications and thus, can be ignored for the analysis. Usually, the effects of errors are divided into classes based on their system-level severity (correctable, uncorrectable, not detected by the hardware but detected by the software, if a retry is possible, if there is a time limit to receive the correct result, etc.).

This means, that there is subjectivity involved in the failure classification. The functional failure analysis is largely driven by the actual usage of the circuit and different

function modes or applications will lead to different failure rates. In the cases the circuit under test has a clearly defined function, the functional failure analysis has to take this specific function into account and the Functional De-Rating characterises faults masked due to this functional behaviour. The analysis becomes more complex for more general circuits, such as Central Processing Units (CPUs), since the actual application is unknown and the usage field is large.

The Functional Masking analysis takes the propagation of the fault over several clock cycles into account. Commonly it is evaluated if the fault has been silently masked and does not have any further effect on the functional behaviour of the circuit. Another usual criterion which is evaluated is, if the fault remains in the circuit in a latent sate which does not have any observable effect on the function. Additionally to these evaluations usually, several failure classes are defined for a given application which result in not just a single Functional De-Rating factor.

### 2.2.5 Summary of Masking Mechanisms

The described masking/de-rating mechanisms are used to evaluate the probability of the propagation of a fault and are usually determined by using probabilistic algorithms and simulation-based approaches. All the different evaluation steps can require significant investment in terms of human efforts, processing resources and licenses for different tools. Thereby, especially the simulation-based approaches to determine the Functional De-Rating are very computationally intensive. Techniques to determine the different de-rating factors and how to calculate an over error rate induced by soft errors are described in the next section.

# 2.3 Soft Error Analysis

While in the past Single-Event Effects were mostly considered in radiation harsh environments, such as space, recent technologies may suffer from Single-Event Effects even in terrestrial applications [8, 9]. For instance, Single-Event Effects may happen even at high altitude for avionic applications, close to nuclear reactor or just from the natural decay in the device material itself. Therefore, it is fundamental to investigate and characterize the susceptibility of a device to Single-Event Effects. Hence, in the last decades research put a lot of efforts in estimating the devices and applications dependability with respect to SEUs and SETs [45, 58, 10, 46, 20].

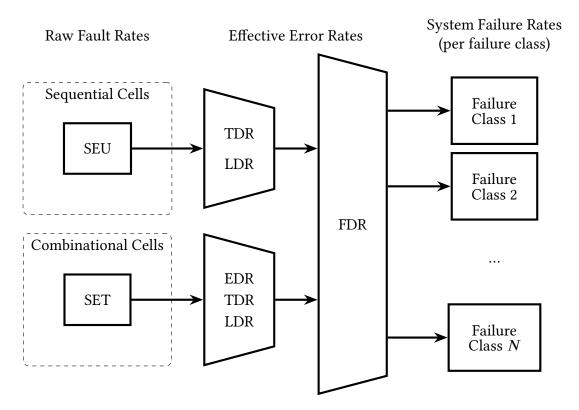

As discussed in the previous sections, the majority of faults does not propagate due to the various masking mechanism. It is necessary to determine the corresponding derating factors, in order to obtain a realistic failure rate of the system which is not fully overestimated. A high-level view of the Single-Event Effects analysis from the fault to system level failures is shown in figure 2.6. The faults which are induced by the sequential elements and the combinational cells are shown on the left. Due to the various

masking effects many of the faults are not propagating (Electrical Masking, Temporal Masking and Logical Masking). The lowering of the probability is quantified by the respective de-rating factors. After applying the de-rating factors, the effective rate of observable errors is calculated. Afterwards the effect of the errors on the functional behaviour of the system is analysed. This is done in the Functional Masking analysis and quantified by the Functional De-Rating. Obtained are the results which characterises the probability for the defined failures on the system level [23].

Figure 2.6: Single-Event Effects analysis.

The objective of the Soft Error analysis is to determine the probability of radiation induced faults resulting in a system-level error. The considered system-level failures must be defined prior to the analysis. With the quantify failure rates of the defined failure classes it can be ensured that the design meets the specified targets and complies with certain standards and regulations (e.g., ISO 26262 [38], DO-254 [25], IEC 61508 [37]]).

To summarize, the Soft Error analysis aims to compute the rate of system-level failures starting from the rate of technology level faults due to soft errors. In the following the three main steps are presented to perform a SER analysis. The technology SER characterization of standard cells and memory blocks, the various de-rating factors and finally the overall SER calculation. The SER methodology presented focuses on non-destructive SEEs: Bit Upsets in sequential cells, Transients in combinational cells.

### 2.3.1 Technology Soft Error Rate Characterization

The technology SER characterization is the first step of the SER analysis. Raw SER data should be provided in terms of raw (intrinsic) rate/probability of occurrence of logic SEU or SET for combinational, sequential and memory cells for a specific environment. The final operating environment should be also carefully analysed, of a particular interest to most commercial and aeronautical applications is the natural background, terrestrial environment characterized by a natural contribution of atmospheric neutrons and internal alpha particles from contaminants. The neutron SER is specific to the technology and the environment (altitude and localization). The alpha contribution depends strongly on the sensitivity of the cell to alpha particles and the alpha emissivity rate of the packaging materials.

### 2.3.2 De-Rating Characterization

The most common techniques to evaluate the propagation of a fault are based on fault injection or analytical approaches. In the fault injection analysis, many faults are injected into the circuit while it is measured if there is any observable effect. The fault injection can be performed on a model of the circuit. Depending on the used implementation of the design, such as the RT-level description or the gate-level netlist, the accuracy of the results might differ and which de-rating factors can be obtained.

An alternative to the fault injection techniques are the analytical approaches. They use a mathematical or abstracted model of the circuit to evaluate the effect of faults. Further techniques are based on a formal representation of the circuit as well as a definition of properties the circuit has to meet. Using tools for model checking or symbolic simulation, it can be verified whether the properties hold in the presence of faults. Another set of approaches is based on associating probability distributions to the nodes in a circuit and then using these to compute the probability that faults on a given node will propagate to an output.

### 2.3.3 Computing the Overall Soft Error Rate

To obtain the overall Soft-Error Rate (SER) for a full chip the SER of the used technology needs to be combined with the determined de-rating factors. For a given application and a specific failure class, the overall failure rate  $SER_{total}$  can be calculated by

$$SER_{total} = SER_{seq} + SER_{comb}$$

(2.4)

where  $SER_{seq}$  is the contribution of the sequential elements, such as flip-flops and latches, and  $SER_{comb}$  the contribution of the combinational elements, such as gates.

The individual parts are then calculated by

$$SER_{seq} = \sum_{i \in Flip\text{-}Flops} FIT_{SEU,i} \cdot TDR_i \cdot LDR_i \cdot FDR_i$$

(2.5)

$$SER_{comb} = \sum_{i \in Gates} \int_{w_{min}}^{w_{max}} FIT_{SET,i}(w) \cdot EDR_i(w) \cdot TDR_i(w) \cdot LDR_i \cdot FDR_i dw. \quad (2.6)$$

where

- $\mathsf{FIT}_{\mathsf{SEU},i}$  represents the SEU rate for the sequential element i,

- $\mathrm{FIT}_{\mathrm{SET},i}(w)$  represents the SET rate of the combinational element i depending on the transient pulse width w and

- the corresponding de-rating factors  $EDR_i$ ,  $TDR_i$ ,  $LDR_i$ ,  $FDR_i$  for element i

# **Chapter 3**

# Machine Learning Techniques for Functional Failure Rate Analysis

#### 3.1 Introduction

In chapter 2 it was discussed that flip-flops are the major contributor to the overall Soft-Error Rate of integrated circuits and one of the major metrics used in today's functional safety analysis are de-rating or vulnerability factors. Using classical methods, such as fault simulations, to obtain accurate per-instance Functional De-Rating data for the full list of circuit instances is a complex and computationally intensive task. Therefore, the objective of the work presented in this chapter is to explore how machine learning techniques can be used to advance the functional failure analysis of complex circuits.

Previous works have shown that certain characteristics of the circuit, such as structural properties and signal probabilities, can be related to the masking effect and thus, used to estimate vulnerability factors [14, 79, 61, 63]. Since machine learning algorithms are very suitable to learn even complex relationships, it can be expected that these models are able to learn and predict the Functional De-Rating by using similar circuit features.

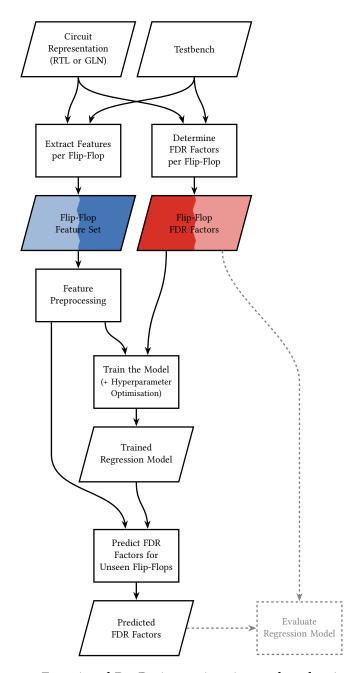

Two approaches are proposed in the following sections which accelerate and assists the functional failure analysis with the help of machine learning techniques. They aim in reducing fault injection efforts in terms of computing resources, human efforts and tool licenses. The first approach uses supervised machine learning algorithms to learn and estimate the Functional De-Rating factors for individual flip-flops in the circuit. The second approach uses machine learning clustering techniques to group flip-flops with a similar sensitivity to faults together and thus, reducing the fault space.

# 3.2 Machine Learning

Machine Learning is the concept of a machine learning from examples and making predictions based on its experience, without being explicitly programmed. Machine learning algorithms are usually built upon a mathematical model which uses sample data (also called training data) in order to make predictions. The machine learning process generally consists of two phases, namely the training or learning phase and the prediction phase. The learning phase can be further grouped in [5, 12]

- supervised learning,

- · unsupervised learning and

- reinforcement learning

The supervised learning algorithms try to model the dependency between the inputs and the target output in such a way that the output values for new data points can be predicted based on the learned relationships. The input data is used for training and consists of a set of training samples. A training sample describes the input values and the corresponding and expected output value. For the mathematical model, the training samples are represented by a vector, also called feature vector. The full training data is then represented by a matrix. in an iterative optimization process the training data is used to adjust parameters of the underlying mathematical function of the model. The learned function can be used to predict an output associated with new data input samples, which were not a part of the training data [62, 51, 5].

The main tasks of supervised learning models are classification and regression. While classification algorithms are used when the outputs are restricted to a limited set of values, regression algorithms are used when the outputs may have any numerical value within a range [5].

In contrary to supervised learning, unsupervised learning models try to find structures in the data set without external labelling or classification. This means, that the training data samples contain only input values for the model and not the expected corresponding output values. Instead of optimizing a mathematical function, unsupervised learning algorithms search for similarities in the training data. The reaction of the model on new data inputs is based on the found similarities and depends on how close each new data point resembles to the already trained data [12].

The two main tasks in this type of unsupervised machine learning methods are clustering and dimensionality reduction. In the cluster analysis the set of training data is divided into subsets, called clusters. Data points within the same cluster are similar according to the predefined criteria, while data points from different clusters are dissimilar. The various clustering algorithms make different assumptions on the structure of the data and therefore, use different similarity metrics to evaluate the similarity of

the members of the same clusters or evaluate the difference between clusters. The dimensionality reduction is a process to reduce the dimension of the feature set, often by eliminating or extract features.

The first developed approach which is presented in section 3.5 is based on supervised learning models and predicting Functional De-Rating factors of individual flipflops by performing a regression. The second approach presented in section 3.6 uses clustering analysis to group flip-flops together with a similar sensitivity to faults in order to decrease the faults space. Both approaches are based on a feature set which is presented in the next section.

#### 3.3 Flip-Flop Feature Set

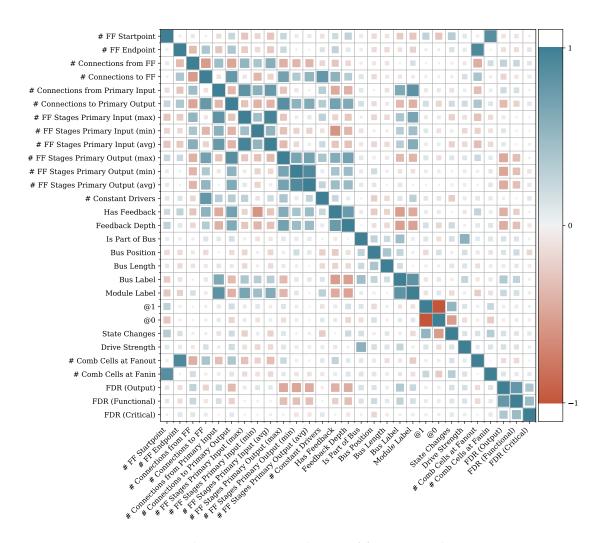

For the machine learning based approaches proposed in the following sections a feature set was developed, which characterises each flip-flop in the circuit. The extraction of the flip-flop feature set needs to be efficient in order to compete with the classical fault injection approach. Therefore, the developed feature set to characterise each flip-flop instance, contains only simple characteristics which are easy and fast to obtain. This feature set combines static elements, such as cell properties, circuit structure and synthesis attributes, as well as dynamic elements, such as the signal activity. The initial version of the feature set was published in [42] and was then extended in [44] and [43]. The features are described in detail in table 3.1.

The feature set can be divided into 3 parts. The structural related features which describe a flip-flop in relation with other flip-flops without taking the (technology dependent) combinational logic into account. The synthesis related features which describe a flip-flop with their assigned cell attributes and the combinational logic at the input and output. These synthesis related features can differ from one technology to another. To consider the workload of the circuit, a variety of features are evaluated to describe the dynamic behaviour of the flip-flops. As an initial approach it was considered that the information related to the signal activity (state distribution, transitions) could be an appropriate starting set of features.

The structural and synthesis related features can be extracted from the gate-level netlist of the circuit. The gate-level netlist is converted into a graph representation. Graph algorithms, such as Dijkstra's algorithm to find the shortest path, can be used to extract the features. The structural related features, can also be extracted just by using the elaborated RTL description of the design. The elaboration of the RTL description is faster than performing a full synthesis and does not necessarily need a full-fledged synthesis tool. This has the advantage that the analysis can already be performed in an early design stage. The signal activity related features are extracted by running a simulation using the corresponding testbench instantiating the RTL description or the gate-level netlist of the circuit and tracing the simulation signals.

Table 3.1: Feature Set to Characterise a Flip-Flop Instance  $\mathrm{FF}_{l}$

| Feature Name                                                                                                   | Type                                                                | Description                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Structural Related Features                                                                                    |                                                                     |                                                                                                                                                                                                                                                                                    |

| # FF at Startpoint/Endpoint                                                                                    | Numerical                                                           | The number of flip-flops directly connected to/by $FF_i$ of the next/previous flip-flop stage.                                                                                                                                                                                     |

| #Connections from/to FF                                                                                        | Numerical                                                           | The number of flip-flops connected to/by FF <sub>i</sub> within the circuit (over several flip-flop stages).                                                                                                                                                                       |

| # Connections from/to Primary Input/Output<br># FF Stages to/from Primary Input/Output (max/avg/min)           | Numerical<br>Numerical                                              | The number of primary inputs/outputs connected to/by FF <sub>i</sub> .  Number of flip-flop stages from/to the primary input/output of the circuit                                                                                                                                 |

| # Constant Drivers<br>Has Feedback                                                                             | Numerical<br>Categorical                                            | The number of constant drivers directly connected to FF <sub>i</sub> . Describes if FF <sub>i</sub> has a feedback loop (directly or over several flipflows etagges)                                                                                                               |

| Feedback Depth                                                                                                 | Numerical                                                           | The depth of the shortest feedback loop in terms of flip-flops                                                                                                                                                                                                                     |

| Is Part of Bus Bus Position Bus Length Bus Label Module Label                                                  | Categorical<br>Numerical<br>Numerical<br>Categorical<br>Categorical | Describes if $FF_i$ is part of a bus signal. Describes the position of $FF_i$ within the bus. Describes the total length of the bus signal $FF_i$ is part of. The number/label of the bus signal $FF_i$ is part of. The number/label of the hierarchical module $FF_i$ is part of. |

| Signal Activity Related Features  @0/@1 State Changes                                                          | Numerical<br>Numerical                                              | The relative time $\mathrm{FF}_i$ output is at logical 0/1. The number of state changes.                                                                                                                                                                                           |

| Synthesis Related Features  Drive Strength Depth combinational Path # Combinational Cells at/from Input/Output | Numerical<br>Numerical<br>Numerical                                 | The drive strength of the FF $_i$ cell instance. The depth of the combinational stage from FF $_i$ output. The total number of combinational cells in FF $_i$ fan-in/fan-out cone.                                                                                                 |

#### 3.3.1 Feature Preprocessing

In general, machine learning algorithms perform better if the data set is standardised. Ideally the data set is normally distributed with zero mean and unit variance. Further, for most machine learning algorithms categorical values have to be represented as numbers. They can be converted by using an ordinal encoder. However, such a number representation could be interpreted as if the categories are in a specific order. This is often not the case and therefore, a one-hot encoding should be used. This encoding transforms each categorical feature with *n* categories into *n* binary features.

The presented feature set consists of two different types of features, the numerical and categorical type. The numerical features are expressed as a number and the categorical features can be expressed by a number, label or Boolean value. The number representation for the numerical feature does have a meaning as a measurement. However, if a categorical feature is represented by a number, it does not have a mathematical meaning and the assignment is arbitrary.

For the presented approach in this chapter, the feature set can be extracted for the full circuit before the training of the models. This has the advantage that the distribution of the values is already known beforehand. Therefore, the standardisation on the numerical features and the one-hot encoding on the categorical features is applied on the full feature set before the training.

#### 3.4 Circuit Under Test

The two proposed techniques which are presented in the following sections are applied on a practical example. The used circuit under test is the Ethernet 10GE MAC Core from OpenCores. This circuit implements the Media Access Control (MAC) functions as defined in the IEEE 802.3ae standard [36]. The 10GE MAC core has a 10 Gbps interface (XGMII TX/RX) to connect it to different types of Ethernet PHYs and one packet interface to transmit and receive packets to/from the user logic [6]. The circuit consists of control logic, state machines, First-In First Outs (FIFOs) and memory interfaces. It is implemented at the Register-Transfer Level (RTL) and is publicly available on Open-Cores.

The corresponding testbench writes several packets to the 10GE MAC transmit packet interface. As packet frames become available in the transmit FIFO, the MAC calculates a Cyclical Redundancy Check (CRC) and sends them out to the XGMII transmitter. The XGMII TX interface is looped-back to the XGMII RX interface in the testbench. The frames are thus processed by the MAC receive engine and stored in the receive FIFO. Eventually, the testbench reads frames from the packet receive interface and prints out the results [6]. During the simulation all sent and received packets to and from the core are monitored and recorded. This record is used as the golden reference for the fault injection campaign.

The elaboration of the RTL implementation of the circuit identifies 1234 flip-flops.

The design was synthesised with Synopsys Design Compiler by using the NanGate FreePDK45 Open Cell Library [74]. Due to logic optimization by the synthesis tool the obtained gate-level netlist contains 1202 flip-flops, 32 flip-flops less than the elaborated RTL implementation.

#### 3.4.1 Failure Classes and Fault Injection Campaign

In order to evaluate the performance of the developed machine learning approaches in the following sections, the sensitivity of the considered design was measured by performing an exhaustive flat statistical fault injection campaign. In this way the sensitivity of each flip-flop was determined and thus, the Functional De-Rating. For comparison, the fault injection campaign was performed on both, the RTL implementation and gate-level netlist of the circuit. The fault injection mechanism is implemented by inverting the value stored in a flip-flop using a simulator function.

For the analysis, three different failure classes are considered. In case the injected fault propagates to the primary outputs of the circuit and thus, the output values are altered in comparison to the golden reference, an *Output Failure* is counted. If the payload of the final received packets is corrupted or the circuit stopped sending or receiving any data, the simulation run was considered as an *Application Failure*. In networking applications, such as the considered design, important data is protected by checksums. This means that a minor payload corruption can be handled by the error correction algorithm. However, in case the fault causes the circuit to stop working and interrupting the flow of sending packages or data is continuously corrupted, then the effect can be considered as critical and a *Critical Failure* is counted.

In each flip-flop 200 faults were injected at a random time during the active phase of the test-case. The fault injection simulations were parallelised by using 7 independent processes. To perform the fault injection campaign on the RTL design in total 12 hours 14 minutes and 31 seconds were needed. Performing the campaign on the gate-level netlist required in total 19 hours 38 minutes and 3 seconds<sup>1</sup>. The failure rate of each flip-flop is calculated by dividing the number of simulation runs which lead to a failure with the number of total simulation runs. The failure classes Output Failure, Application Failure and Critical Failure are considered separately and the overall results of the flat statistical fault-injection campaign are presented in table 3.2.

#### Register-Transfer Level Design Versus Gate-Level Netlist

The elaborated RTL design is not optimized by a synthesis tool and thus, contains 32 more flip-flops than the final gate-level netlist. To perform a comparison, the flip-flops from the gate-level netlist have been matched with the corresponding RTL signal names.

$<sup>^1\</sup>mathrm{Computations}$  were performed on a PC with an Intel Xeon E5-2687W CPU (8 cores/16 threads 3.10 GHz).

|                            |        | RT-Level      | Gate- | Level Netlist |

|----------------------------|--------|---------------|-------|---------------|

|                            | Total  | Per Injection | Total | Per Injection |

| Injection Targets (FFs)    | 1234   | -             | 1202  | -             |

| Injected Faults (SEU)      | 246800 | 246800 -      |       | -             |

| Output Failure             | 90306  | 36.59%        | 84159 | 35.01%        |

| <b>Application Failure</b> | 55187  | 22.36%        | 53756 | 21.78%        |

| Critical Failure           | 14012  | 5.68 %        | 12332 | 5.13 %        |

Table 3.2: SEU Fault Injection Campaign Results

The fault injection simulation campaign on the RTL design was performed with the same parameters (number of injections and injection time) as for the gate-level netlist. The failure rates for almost all flip-flops were identical, except of the additional flip-flops and some flip-flops which are connected to/by these additional flip-flops. The difference between the failure rates were less than 2 %.

#### 3.4.2 Feature and Target Pre-Analysis