$\label{eq:Doctoral Dissertation} Doctoral Program in Computer and Control Engineering (33^{th} cycle)$

# New Design Techniques for Dynamic Reconfigurable Architectures

Ludovica Bozzoli

\* \* \* \* \* \*

### Supervisor

Prof. Luca Sterpone

#### **Doctoral Examination Committee:**

Prof. Eduardo De La Torre, Universidad Politécnica de Madrid

Prof. Bartolomeo Montrucchio, Politecnico di Torino

Prof. Mario Porrmann, *Referee*, Osnabrück University

Prof. Anees Ullah, University of Engineering and Technology Peshawar

Prof. Stephan Wong, *Referee*, Delft University of Technology

Politecnico di Torino September 28, 2021

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

.....

Ludovica Bozzoli Turin, September 28, 2021

# Summary

Over the past decades, reconfigurable computing had increasingly gained attention for the high integration, performances, and in-field upgradability it can provide to a computing system. In fact, its main novelty consists of offering on a single platform the benefits of hardware customization coupled with the flexibility typical of software programming.

This has driven the effort in proposing and developing several reconfigurable architectures to efficiently tailor various and increasingly complex applications. Such trend led to the state-of-the-art architecture, consisting of a heterogeneous processing system including on-chip processors coupled with dynamically reconfigurable fabric to implement custom and run-time upgradable cores.

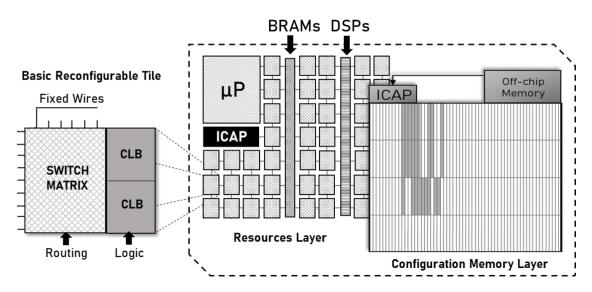

Today, the commercial technology to implement the reconfigurable fabric is represented by the SRAM-based Field Programmable Gate Array (FPGA) and consists of one layer of programmable resources and one layer of configuration, an SRAM memory holding the configuration data defining the behavior of the resource layer. These devices enable to access and modify specific portions of the memory content from the resource layer without stopping the application execution to adapt its functionality to requirements varying over time, to maximize its performance, and to increase its dependability.

This feature, called Dynamic Partial Reconfiguration, has been one of the leading characteristics that drove the rapid growth of this computational paradigm and increasingly widened the deployment of SRAM-based FPGAs in many computationalintensive and high-reliability applications, such as networking, High-Performance Computing, and satellite or high energy physics experiments fault-tolerant electronics.

However, the current SRAM-based FPGA architecture embeds some functionalities that demand to be addressed to fully express the promises of the reconfigurable computing paradigm and that provide opportunities for enhancing reconfigurable systems performance and dependability.

The performance optimizations are related to the relatively long time required to perform run-time reconfiguration in commercial devices that, if not properly managed, can jeopardize gain achieved through to the in-field upgradability.

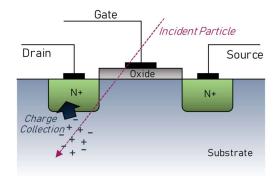

SRAM-based FPGAs' dependability instead becomes crucial when they operate in

presence of radiation, as in aerospace and high energy physics experiments, due to their configuration memory sensitivity to radiation-induced errors that must be considered and characterized according to the mission environment before deployment to avoid failures.

In this view, the doctoral research presented in this dissertation addresses dynamically and partially reconfigurable architectures' performance through novel techniques for the enhancement of the reconfiguration procedure, and self-reconfigurable systems dependability through the analysis of their radiation sensitivity to radiationinduced effects.

Therefore, the main opportunities and challenges embedded in reconfigurable architectures are firstly introduced and followed by an overview of the state-of-the-art architectural solutions and applications for high-performance and high-reliability reconfigurable platforms.

The main contributions to the optimization of the reconfiguration procedure performances are provided in the **Part 1** of the dissertation.

In detail, the Frame-driven Routing Algorithm (FeDRA) is presented as a novel and generalized approach to optimize within the development process the amount of configuration memory data involved in the reconfiguration of circuits deployed on commercial SRAM-based FPGAs. The proposed approach enables to achieve a consistent reduction of the reconfiguration overhead when compared to solutions obtained with the standard process.

Subsequently, the Reconfigurable Multipotent (ReM) cell, developed as the basic reconfigurable unit for novel architectural solutions oriented to the fast and detailed in-field reconfiguration, is presented. In detail, the proposed reconfigurable cell enables bit-level reconfiguration within a single clock cycle while minimizing the amount of data involved in the procedure thanks to the key feature of reconfiguring itself and the contiguous units.

The **Part 2** of the dissertation instead presents the main contributions to reconfigurable FPGAs dependability that consist of radiation sensitivity analyses centered on the self-reconfiguration controller, which represent the key component enabling in-field reconfiguration.

In detail, a soft-error analysis on different implementations of the self-reconfiguration controller managing the configuration memory access in dynamically and partially reconfigurable applications is presented. This analysis, which has been performed by miming different radiation profiles through detailed fault-injections, allowed to obtain indications about the controllers' dependability and applicability in different radiation environments according to their operational goals.

Accordingly, a self-monitoring setup based on the most suitable self-reconfiguration controller and instrumented for the online and automated radiation analysis of SRAM configuration memory sensitivity is presented. The proposed setup enabled the usage of a Neutron Generator as a radiation source and strongly reduces the time and the cost required by typical radiation testing facilities and approaches.

## Acknowledgements

I would like to acknowledge all the people who accompanied me in my doctoral experience aiding, supporting, and motivating me towards the accomplishment of this journey.

Firstly, I would like to thank Prof. Luca Sterpone for giving me the opportunity of taking part in such a fascinating research field and environment and for supporting, encouraging, and advising me all over the years of my Ph.D. strengthening my curiosity and motivation.

Then, I would like to thank all the people in CAD Group and my colleagues for enabling me to pursue my research activity in a truly stimulating and pleasant context. A special thank goes to Sarah Azimi, Corrado de Sio, and Boyang Du for everything I learned working with them and for friendly aiding me in this path. Furthermore, I would like to thank all the people from other Institutions I had the chance to collaborate with, especially Antonio Tramutola for the support in the research activity carried out with Thales Alenia Space and the people encountered in the training experience at the Los Alamos National Laboratory.

Finally, a special thank goes to Tommaso, my Family, and my Friends for their constant and warm presence and, above all, for the energy they give me and that encourages me every day.

### To my Parents...

...who, no matter how far away, always find their way of being close to me.

# Contents

| Li       | st of | Tables                                                                                         | XI  |

|----------|-------|------------------------------------------------------------------------------------------------|-----|

| Li       | st of | Figures                                                                                        | XII |

| 1        | Intr  | oduction                                                                                       | 1   |

|          | 1.1   | Reconfigurable Computing                                                                       | 1   |

|          |       | 1.1.1 Origin and Paradigm                                                                      | 1   |

|          |       | 1.1.2 Architectural Evolution and Granularity                                                  | 5   |

|          |       | 1.1.3 Reconfiguration for Reliability                                                          | 6   |

|          | 1.2   | SRAM-Based FPGAs                                                                               | 8   |

|          |       | 1.2.1 Configuration Memory                                                                     | 9   |

|          |       | 1.2.2 Current Heterogeneous Fabric                                                             | 10  |

|          | 1.3   | Opportunities and Challenges                                                                   | 12  |

|          |       | 1.3.1 High-performance and Reliable Applications                                               | 12  |

|          |       | 1.3.2 Reconfiguration Procedure Performances                                                   | 13  |

|          |       | 1.3.3 Reconfigurable FPGAs Dependability in Radiation Environ-                                 |     |

|          |       | ment $\ldots$ | 15  |

|          | 1.4   | Main Objectives and Contributions                                                              | 17  |

| <b>2</b> | Stat  | te of the Art                                                                                  | 21  |

|          | 2.1   | Reconfigurable Devices                                                                         | 21  |

|          |       | 2.1.1 Milestone Architectures                                                                  | 21  |

|          |       | 2.1.2 Commercial Devices                                                                       | 24  |

|          | 2.2   | High-Performance and Dependable Systems                                                        | 27  |

|          |       | 2.2.1 Dynamically Reconfigurable Hybrid Architecture                                           | 27  |

|          |       | 2.2.2 Dependable Platforms for Radiation Environments                                          | 30  |

|          |       | 2.2.3 HPC: Networking, Cloud and Exascale Computing                                            | 32  |

|          | 2.3   | Discussion and Highlights                                                                      | 34  |

| Ι        | Dy    | vnamic Reconfigurable Architecture Performance                                                 | 37  |

| 3        | -     | ated Works                                                                                     | 39  |

| J        | Trefe |                                                                                                | 59  |

|   | 3.1                                                                                                     | Overview                                                                                                                                                                                                                                                                                        | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39                                                                         |

|---|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | 3.2                                                                                                     | Develop                                                                                                                                                                                                                                                                                         | ment Flow Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40                                                                         |

|   |                                                                                                         | 3.2.1 \$                                                                                                                                                                                                                                                                                        | Standard FPGA Development Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Dynamic Reconfiguration Scenario                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                         |

|   | 3.3                                                                                                     |                                                                                                                                                                                                                                                                                                 | tural Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Reconfigurable Fabric Granularity and Heterogeneity                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                         |

| 4 | Tec                                                                                                     | hnical B                                                                                                                                                                                                                                                                                        | ackground                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                         |

|   | 4.1                                                                                                     | SRAM-l                                                                                                                                                                                                                                                                                          | based FPGAs Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51                                                                         |

|   |                                                                                                         | 4.1.1 H                                                                                                                                                                                                                                                                                         | Reconfigurable Resource Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Configuration Memory Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                         |

|   |                                                                                                         | 4.1.3 H                                                                                                                                                                                                                                                                                         | Hardwired Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                         |

|   | 4.2                                                                                                     |                                                                                                                                                                                                                                                                                                 | e and Configuration Memory Link                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57                                                                         |

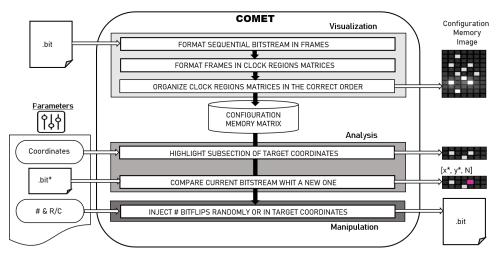

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | COMET: COnfiguration MEmory Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Bitstream Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                                         |

|   | 4.3                                                                                                     |                                                                                                                                                                                                                                                                                                 | guration Approaches and Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                         |

|   |                                                                                                         | -                                                                                                                                                                                                                                                                                               | Reconfiguration Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60                                                                         |

|   |                                                                                                         | 4.3.2 I                                                                                                                                                                                                                                                                                         | nterfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                         |

|   | 4.4                                                                                                     |                                                                                                                                                                                                                                                                                                 | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                         |

|   |                                                                                                         |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| 5 | FeD                                                                                                     |                                                                                                                                                                                                                                                                                                 | Frame-driven Routing Approach for Fast Partial Re-                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| 5 |                                                                                                         |                                                                                                                                                                                                                                                                                                 | Frame-driven Routing Approach for Fast Partial Re-<br>n                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                                         |

| 5 |                                                                                                         | )RA: a ]<br>figuratio                                                                                                                                                                                                                                                                           | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65 $65$                                                                    |

| 5 | con                                                                                                     | <b>RA:</b> a figuratio                                                                                                                                                                                                                                                                          | $\mathbf{n}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 5 | <b>con</b><br>5.1                                                                                       | <b>PRA:</b> a l<br>figuratio<br>Overviev<br>FeDRA:                                                                                                                                                                                                                                              | <b>n</b><br>wFrame-driven Routing Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65                                                                         |

| 5 | <b>con</b><br>5.1                                                                                       | <b>PRA:</b> a l<br>figuratio<br>Overview<br>FeDRA:<br>5.2.1 H                                                                                                                                                                                                                                   | n<br>wFrame-driven Routing Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{c} 65\\ 66\end{array}$                                      |

| 5 | <b>con</b><br>5.1                                                                                       | <b>PRA:</b> a 1<br>figuratio<br>Overview<br>FeDRA:<br>5.2.1 H<br>5.2.2 H                                                                                                                                                                                                                        | n<br>w                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65<br>66<br>66                                                             |

| 5 | <b>con</b><br>5.1                                                                                       | <b>PRA:</b> a 1         figuratio         Overview         FeDRA:         5.2.1         5.2.2         F.2.3                                                                                                                                                                                     | n         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         FeDRA Algorithm                                                                                                                                                                                                                                                                                                                                      | 65<br>66<br>66<br>68                                                       |

| 5 | <b>con</b><br>5.1<br>5.2                                                                                | <b>PRA:</b> a 1         figuratio         Overview         FeDRA:         5.2.1         5.2.2         FeDRA:         5.2.3         Fexperim                                                                                                                                                     | n         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         FeDRA Algorithm         Mental Results                                                                                                                                                                                                                                                                                                               | 65<br>66<br>66<br>68<br>73                                                 |

| 5 | <b>con</b><br>5.1<br>5.2                                                                                | <b>PRA:</b> a 1         figuration         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         Fexperime         5.3.1                                                                                                                                                    | n         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         FeDRA Algorithm         Mental Results         Experimental Setup                                                                                                                                                                                                                                                                                    | 65<br>66<br>68<br>73<br>79                                                 |

| 5 | <b>con</b><br>5.1<br>5.2                                                                                | <b>PRA:</b> a 1         figuration         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         Fexperime         5.3.1         F.3.2                                                                                                                                      | n         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         Gebra Algorithm         Imental Results         Experimental Setup         Optimization in Standard Condition                                                                                                                                                                                                    | 65<br>66<br>68<br>73<br>79<br>79                                           |

| 5 | <b>con</b><br>5.1<br>5.2                                                                                | <b>PRA:</b> a 1         figuration         Overview         FeDRA:         5.2.1         FeDRA:         5.2.2         FeDRA:         5.2.3         Fexperime         5.3.1         February         5.3.2         General State                                                                 | n         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Grame-driven Routing Policy         Frame-driven Routing Policy         Gebra Algorithm         Mental Results         Seperimental Setup         Optimization in Standard Condition         Optimization with Tight Area Constraints                                                                                                                                                    | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83                               |

| 5 | <b>con</b><br>5.1<br>5.2                                                                                | <b>PRA:</b> a 1         figuration         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         Fexperime         5.3.1         F.3.2         S.3.3         G.3.3         S.3.4                                                                                            | m         W         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         FeDRA Algorithm         Mental Results         Experimental Setup         Optimization in Standard Condition         Optimization with Tight Area Constraints         Performance and Routability Analysis                                                                                                       | 65<br>66<br>68<br>73<br>79<br>79<br>80                                     |

| 5 | <b>con</b><br>5.1<br>5.2                                                                                | <b>PRA:</b> a 1         figuratio         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         F.2.3         F.2.3         F.2.3         F.2.3         F.2.3         F.2.3         F.3.1         F.3.2         S.3.3         G.3.3         S.3.4         F.3.5             | n         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Grame-driven Routing Policy         Frame-driven Routing Policy         Gebra Algorithm         Mental Results         Seperimental Setup         Optimization in Standard Condition         Optimization with Tight Area Constraints                                                                                                                                                    | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83<br>85                         |

| 5 | <ul> <li>cont</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                            | <b>PRA:</b> a 1         figuration         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         Fexperime         5.3.1         F.3.2         Comparison         S.3.3         S.3.4         F.3.5         N         Research                                              | m         W         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         FeDRA Algorithm         Mental Results         Experimental Setup         Optimization in Standard Condition         Deformance and Routability Analysis         Modules Reconfiguration Scenario                                                                                                                | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83<br>85<br>85                   |

|   | <ul> <li>cont</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                            | <b>PRA:</b> a 1         figuration         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         Fexperime         5.3.1         F.3.2         Comparison         S.3.3         S.3.4         F.3.5         N         Research                                              | m         w         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         FeDRA Algorithm         mental Results         Experimental Setup         Optimization in Standard Condition         Optimization with Tight Area Constraints         Performance and Routability Analysis         Modules Reconfiguration Scenario                                                              | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83<br>85<br>85                   |

|   | <ul> <li>cont</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                            | <b>PRA:</b> a 1         figuratio         Overview         FeDRA:         5.2.1         F.2.2         F.2.3         FExperim         5.3.1         F.3.2         S.3.3         G         5.3.4         F.3.5         Research         t and Dia                                                 | m         W         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         FeDRA Algorithm         mental Results         Seperimental Setup         Dytimization in Standard Condition         Optimization with Tight Area Constraints         Performance and Routability Analysis         Modules Reconfiguration Scenario         Modules Reconfigurable Architecture with ReM Cells   | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83<br>85<br>87<br>90             |

|   | <ul> <li>cont</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Fast</li> <li>6.1</li> </ul> | <b>PRA:</b> a 1 <b>figuratio</b> Overview         FeDRA:         5.2.1         F.2.2         F.2.3         FExperime         5.3.1         F.3.2         S.3.3         G         5.3.4         F.3.5         Research <b>t and Di</b> Overview                                                  | m         W         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         FeDRA Algorithm         Mental Results         Seperimental Setup         Dytimization in Standard Condition         Optimization with Tight Area Constraints         Performance and Routability Analysis         Modules Reconfiguration Scenario         stributed Reconfigurable Architecture with ReM Cells | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83<br>85<br>87<br>90<br>93<br>93 |

|   | <ul> <li>cont</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>Fast</li> </ul>              | <b>PRA:</b> a 1 <b>figuratio</b> Overview         FeDRA:         5.2.1         FeDRA:         5.2.2         FeDRA:         5.2.3         Fexperime         5.3.1         Fexperime         5.3.2         5.3.3         C         5.3.4         Fesearch <b>t and Di</b> Overview         ReM-ba | m         W         Frame-driven Routing Algorithm         Routing Frames Decoding         Frame-driven Routing Policy         Frame-driven Routing Policy         FeDRA Algorithm         mental Results         Seperimental Setup         Dytimization in Standard Condition         Optimization with Tight Area Constraints         Performance and Routability Analysis         Modules Reconfiguration Scenario         Modules Reconfigurable Architecture with ReM Cells   | 65<br>66<br>68<br>73<br>79<br>79<br>80<br>83<br>85<br>87<br>90             |

|    | 6.3   |         | Circuit Mapping                                       | 102<br>105<br>105<br>107<br>108 |

|----|-------|---------|-------------------------------------------------------|---------------------------------|

|    | 6.4   | Resear  | rch Advancement                                       | 110                             |

| II | D     | ynam    | nic Reconfigurable Architecture Dependability         | 113                             |

| 7  | Rela  | ated W  | Vorks & Background                                    | 115                             |

|    | 7.1   | Relate  | ed Works                                              | 115                             |

|    |       | 7.1.1   | High-dependability Reconfigurable Systems             | 116                             |

|    |       | 7.1.2   | Dependability Characterization Techniques             | 117                             |

|    | 7.2   | Backg   | round                                                 | 122                             |

|    |       | 7.2.1   | SRAM-based FPGAs in Radiation Environments            | 122                             |

|    |       | 7.2.2   | Configuration Memory Run-time Access                  | 123                             |

|    | 7.3   | Discus  | ssion and Outlook                                     | 127                             |

| 8  | Self  | -Recor  | nfigurable Systems Dependability Analysis             | 129                             |

|    | 8.1   |         | dology                                                | 129                             |

|    | 8.2   |         | rrors Analysis on Self-reconfiguration Controllers    | 131                             |

|    |       | 8.2.1   | Evaluation Framework                                  | 131                             |

|    |       | 8.2.2   | Board Setup                                           | 132                             |

|    |       | 8.2.3   | Fault-injection Platform                              | 135                             |

|    |       | 8.2.4   | Experimental Results                                  | 137                             |

|    |       | 8.2.5   | Discussion & Highlights                               | 142                             |

|    | 8.3   | Self-te | sting Technique for Cost-effective Radiation Analysis | 143                             |

|    |       | 8.3.1   | Overview                                              | 143                             |

|    |       | 8.3.2   | Hardware Setup                                        | 144                             |

|    |       | 8.3.3   | Radiation Test Instrumentation & Equipment            | 147                             |

|    |       | 8.3.4   | Experimental Results                                  | 150                             |

|    |       | 8.3.5   | Discussion & Highlights                               | 152                             |

|    | 8.4   | Resear  | rch Advancement                                       | 152                             |

| 9  | Con   | clusio  | n and Future Developments                             | 155                             |

| Bi | bliog | raphy   |                                                       | 161                             |

# List of Tables

| 4.1 | Maximum Throughput for Configuration Ports in 7 Series Devices [47]           | 62  |

|-----|-------------------------------------------------------------------------------|-----|

| 5.1 | Characteristics of Benchmark Circuits Implemented within Xilinx               |     |

|     | Vivado IDE on Kintex-7 in Standard Condition                                  | 80  |

| 5.2 | Routing Frame Usage Comparison between Benchmarks Routed with                 |     |

|     | the Vendor Flow and Routed with FeDRA in Standard Condition .                 | 81  |

| 5.3 | Benchmark Circuits Compression Metrics Under Tight Area Con-                  |     |

|     | straints: Slice Usage and Congestion Rate                                     | 83  |

| 5.4 | Routing Frame Usage Comparison between Benchmarks Routed with                 |     |

|     | the Vendor Flow and Routed with FeDRA Under Tight Area Con-                   |     |

|     | straints                                                                      | 84  |

| 5.5 | Comparison between Standard and FeDRA Router Frames Usage for                 |     |

|     | Programming, Erasing and Swapping of Benchmark Hardware Tasks                 | 89  |

| 6.1 | Elaboration Configuration Encoding for Memory and Logic Units .               | 99  |

| 6.2 | Placement and Routing Resources for ReM Cell Layout                           | 106 |

| 6.3 | ITC '99 Benchmarks Characteristics: Combinational Gates, Filp-                |     |

|     | Flops and Functionality $[102]$                                               | 107 |

| 6.4 | Benchmark Implementation with ReM Cells: Type, Count, Config-                 |     |

|     | uration Bits and Total Area                                                   | 108 |

| 6.5 | Benchmark Implementation on ZYNQ and Reconfiguration Data and                 |     |

|     | Time Comparison with ReM-based Clusters (100 MHz has been used                |     |

|     | 1 5 7                                                                         | 109 |

| 8.1 | ZYNQ 7020 Resources Availability and Usage for the Two Self-reconfigu         |     |

|     | Controller Implementation: BRAM and Fabric                                    | 137 |

| 8.2 | Controllers Applicability to Radiation Environments and Missions              | 142 |

| 8.3 | ZYNQ 7020 FPGA Resource Availability and the Relative Utilization             |     |

|     |                                                                               | 148 |

| 8.4 | Neutron Generator Source Technical Specifications [129]                       | 148 |

| 8.5 | Correlated Bit Upsets Percentage of Occurrences in Test $0 \Rightarrow 1$ and |     |

|     | Test $1 \Rightarrow 0$ [125]                                                  | 151 |

# List of Figures

| 1.1 | Computing Implementations: Flexibility vs. Performance              | 2  |

|-----|---------------------------------------------------------------------|----|

| 1.2 | Reconfigurable Device's Two Layers Architecture: Reconfigurable     |    |

|     | Hardware Layer and Configuration Memory Layer                       | 3  |

| 1.3 | a) Single Context Reconfiguration: the Whole Configuration Mem-     |    |

|     | ory Content is Updated; b)Partial Reconfiguration: Only the Target  |    |

|     | Portion of the Configuration is Involved in the Procedure           | 3  |

| 1.4 | Reconfiguration Granularity: Flexibility vs. Complexity             | 6  |

| 1.5 | High-Level Island-Style FPGA Architecture                           | 9  |

| 1.6 | Current FPGA Heterogeneous Architecture                             | 11 |

| 1.7 | Ionizing Particle Effect on MOS Technology                          | 15 |

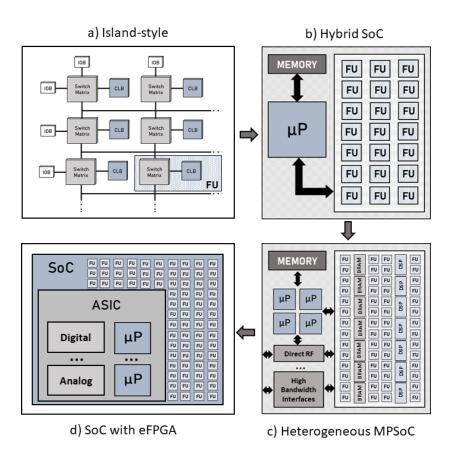

| 2.1 | Architectural Models: a) Hybrid Architecture, b) Array of Func-     |    |

|     | tional Units, c) Array of Processors                                | 22 |

| 2.2 | Architectural Trend towards Higly Integrated and Heterogeneous De-  |    |

|     | vices: a) Island-bases Architecture, b) Hybrid SoC Architecture, c) |    |

|     | Heterogeneous MPSoC Architecture, d) SoC with Embedded FPGA         |    |

|     | (eFPGA) Architecture                                                | 23 |

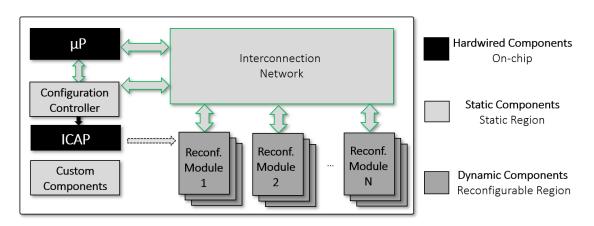

| 2.3 | DRPM Architecture Overview                                          | 28 |

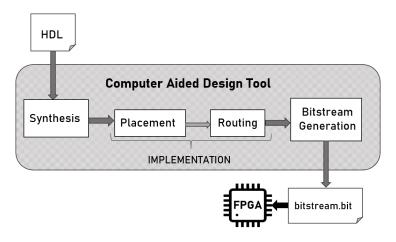

| 3.1 | FPGA Development Flow                                               | 41 |

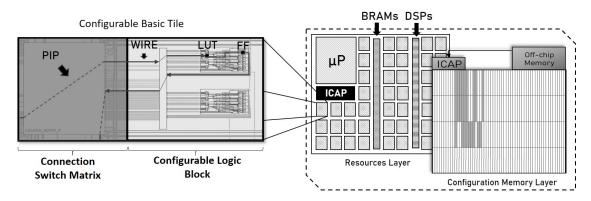

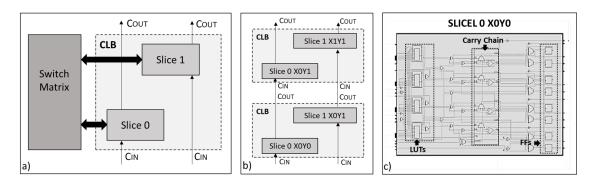

| 4.1 | 7 Series Basic Tile and Heterogeneous Architecture                  | 52 |

| 4.2 | 7 Series CLB: a) Slice Arrangement and SM Connectivity; b) Column   |    |

|     | Connectivity between CLB Slices; c) SLICEL Schematic from Vivado    |    |

|     | View                                                                | 53 |

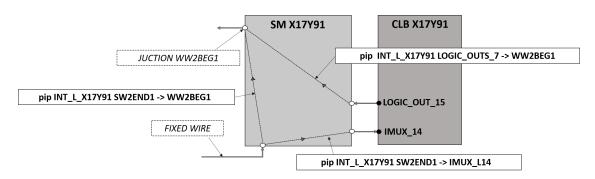

| 4.3 | Switch Matrix Organization: PIPs, Junctions, and Wires Function     |    |

|     | and Taxonomy Examples                                               | 54 |

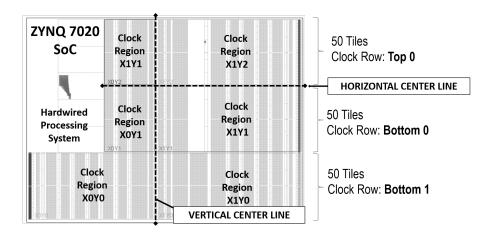

| 4.4 | ZYNQ 7020 SoC Clock Regions Organization                            | 55 |

| 4.5 | COMET Tool Flow and Functions [99]                                  | 58 |

| 4.6 | Bitstream logic organization for Xilinx 7 Series FPGA on Kintex-7   |    |

|     | Device $[27]$                                                       | 59 |

| 4.7 | Configuration Memory Mapping of Kintex7 (a) and its Tile (b) [27]   | 60 |

| 4.8 | Techniques: Full Context (b), Module-based (c), and Difference-     |    |

|     | based (d) Reconfiguration on a Sample Configuration Memory Usage    |    |

|     | (a) $[27]$                                                          | 61 |

|     |                                                                     |    |

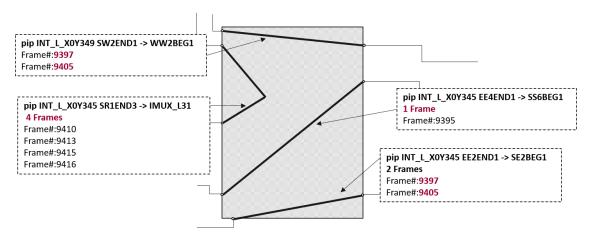

| 5.1         | Flow Diagram of the Routing Frames Decoding                           |

|-------------|-----------------------------------------------------------------------|

| 5.2         | Sample Configurations of PIPs within the Switch Matrix: 1, 2 or 4     |

|             | Programmed Frames and their Possible Overlapping 6                    |

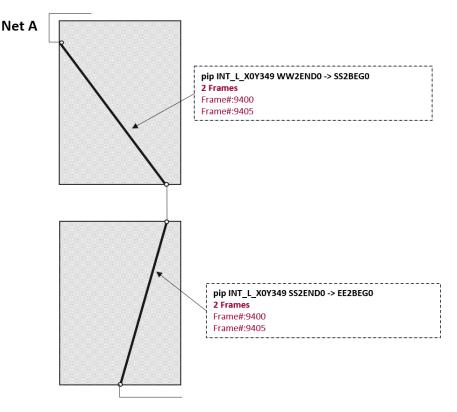

| 5.3         | Absolute Scenario: between two PIPs with the same Connectivity        |

|             | Behavior the the one introducing the Absolute Minimal Number of       |

|             | Frames is Selected                                                    |

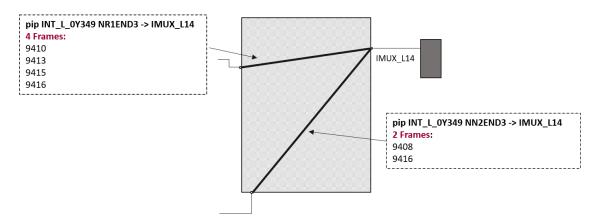

| 5.4         | Intra-net Scenario: PIPs within the Same Net which Belong to the      |

|             | Same Tile Column Allow their Selection to Maximize the Frame          |

|             | Overlapping                                                           |

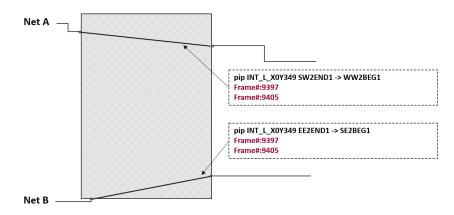

| 5.5         | Inter-net Scenario: PIPs Building Different Nets and Belonging to     |

|             | the same Tile Column Allow their Selection to Maximize the Frame      |

|             | Overlapping                                                           |

| 5.6         | FeDRA Routing Policies: a) Standard Net Routed by the Vendor          |

|             | Tool; b) The Same Net Routed with FeDRA Optimization with 3           |

|             | Saved Frames                                                          |

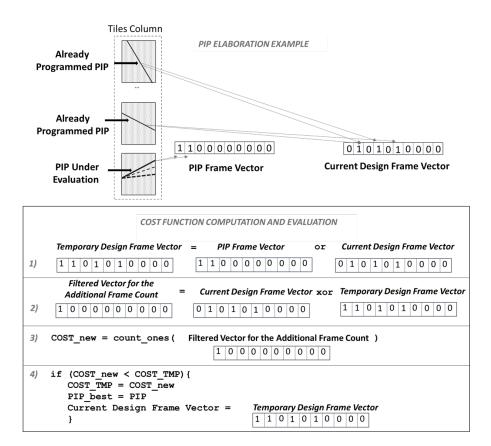

| 5.7         | The FeDRA Approach Pseudo-code [27]                                   |

| 5.8         | PIP Elaboration Example: Highlights of Cost Function Computation      |

|             | and Evaluation                                                        |

| 5.9         | FeDRA Algorithmic Description [100]    7                              |

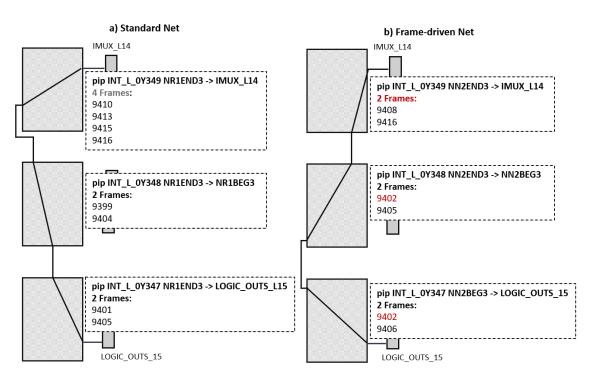

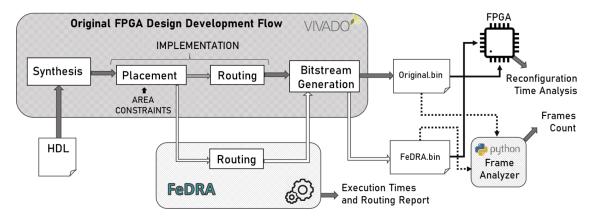

|             | FeDRA Evaluation framework [27]                                       |

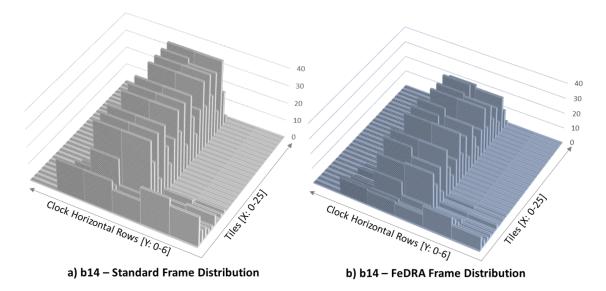

| 5.11        | Frame Distribution and Circuit Topology comparisons for b14 bench-    |

|             | mark: obtained with the vendor tool (a), and with FeDRA routing       |

|             | (b)                                                                   |

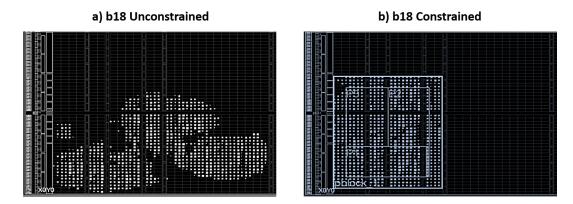

| 5.12        | Slice Placement Solutions for b18 Benchmark: s) Unconstrained, and    |

| <b>F</b> 10 | b) Constrained $[27]$                                                 |

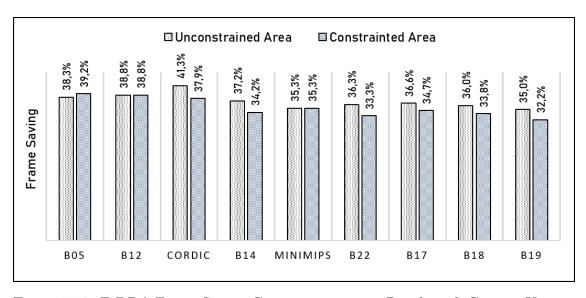

| 5.13        | FeDRA Frame Saving Comparison among Benchmark Circuits Un-            |

|             | constrained (Unconstrained Area) and with Tight Placement Area        |

| F 1 /       | Constraints (Constrained Area)                                        |

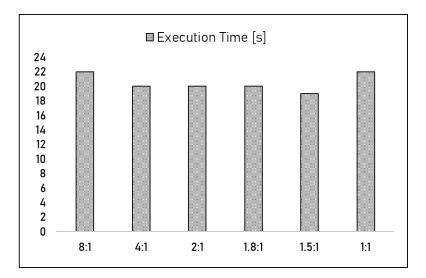

| 5.14        | The FeDRA Algorithm Results on Execution Times with different         |

| 5 15        | Area Constraints for the Benchmark b12                                |

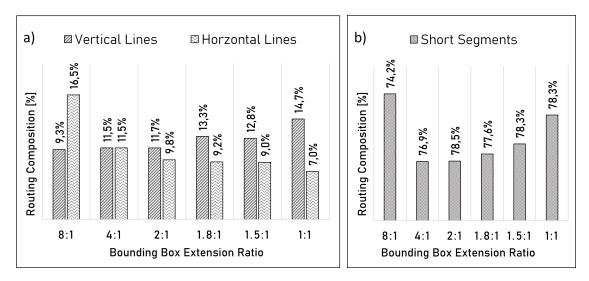

| 0.10        | Lines (a) and Short Segments (b) Utilization Ratio for Different Area |

|             | Constraints for the Benchmark b12                                     |

| 5.16        | Routing Frames Overlapping in Tiles Column for Cordic and b14 . 8     |

| 6.1         | ReM Cell High-level Architecture with the Highlights of its Func-     |

| 0.1         | tional Modes and Connectivity [101]                                   |

| 6.2         | ReM Cell Configuration Register CNGF_REG Detail                       |

| 6.3         | ReM Connectivity: a) Configuration Register Format; b) Signals        |

| 0.0         | Activation Encoding; c) Double Connection Example [101]               |

| 6.4         | ReM Elaboration: a) Memory Block; b) Logic Block [101] 9              |

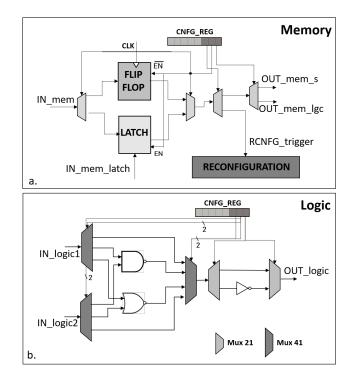

|             |                                                                       |

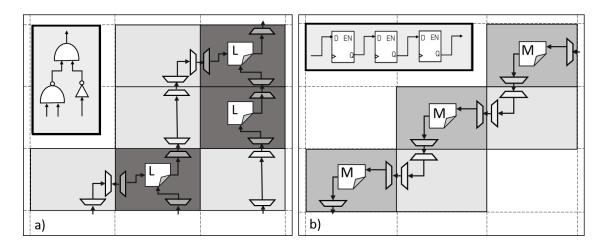

| 6.5        | 3-Inputs Function (a) and Flip-Flop Chain (b) Implemented Pro-                                      |     |

|------------|-----------------------------------------------------------------------------------------------------|-----|

|            | gramming respectively a Cluster 7 and 5 ReM Cell within a Cells                                     | 100 |

| C C        | Matrix                                                                                              | 100 |

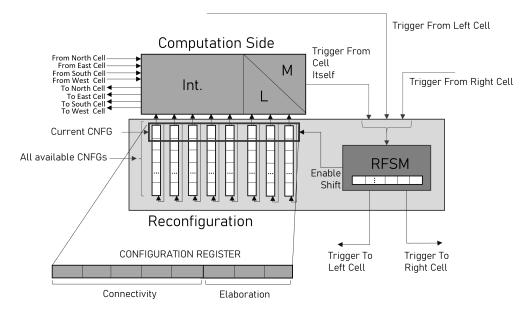

| 6.6        | Overview of ReM Reconfiguration Engine: Mechanism and Interac-                                      | 101 |

| c <b>7</b> | tion with Neighbor Cells [101]                                                                      | 101 |

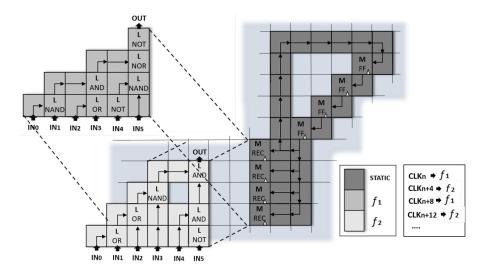

| 6.7        | 6-Inputs Dynamically Reconfigurable Function Implementation within                                  | 100 |

| 0.0        | a ReM Cells Cluster                                                                                 | 103 |

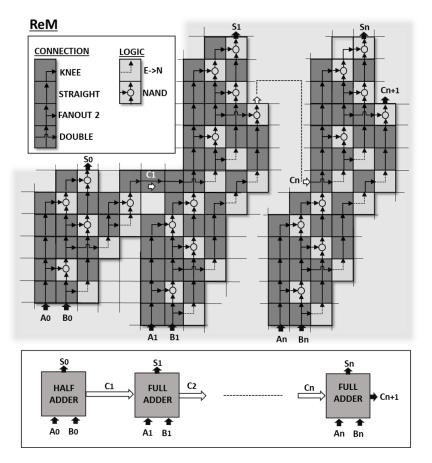

| 6.8        | N-bits Full-Adder Implementation within a ReM Cells Cluster                                         | 104 |

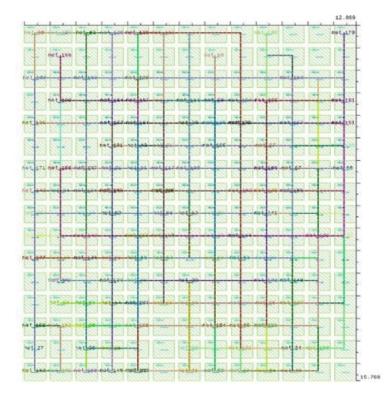

| 6.9        | ReM Cell Layout of the Placed and Routed Standard Cells                                             | 106 |

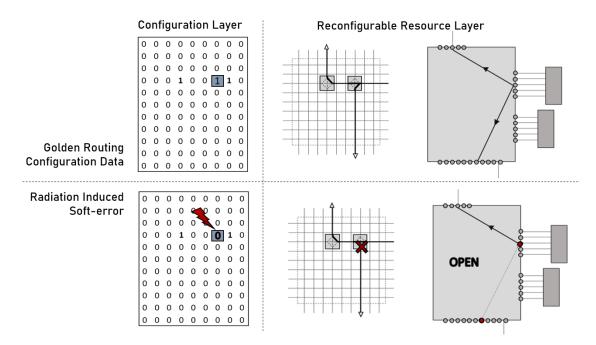

| 7.1        | Configuration Memory Upset: Sample Routing Configuration Set-                                       | 100 |

|            | tings before and after a Radiation-induced Soft-error                                               | 123 |

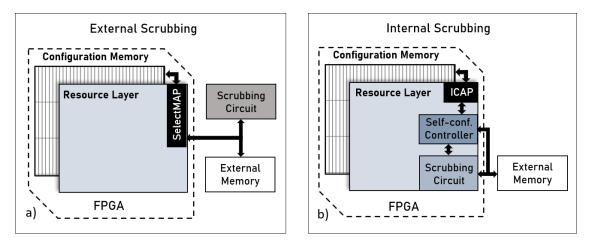

| 7.2        | External (a) and Internal (b) Scrubbing Mechanisms                                                  | 125 |

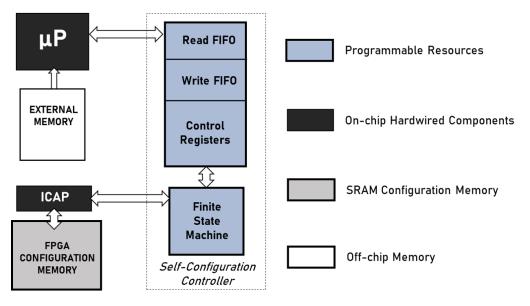

| 7.3        | Simplified Architecture the of Self-configuration Controller                                        | 126 |

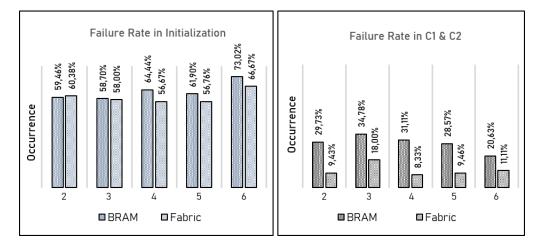

| 8.1        | Simplified Architecture of the DRPM System                                                          | 133 |

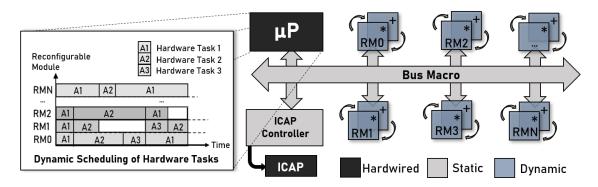

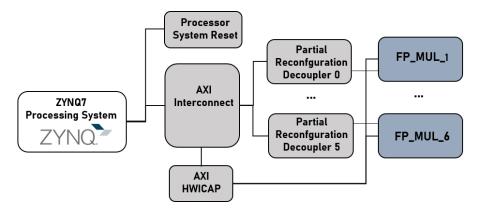

| 8.2        | Block Design of the DRPM Implemented on ZYNQ 7020 SoC $\ldots$                                      | 133 |

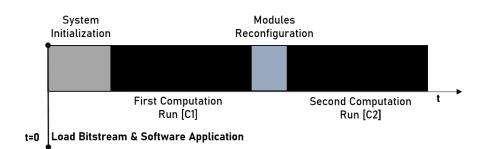

| 8.3        | The DRPM Execution Flow Instrumented for Soft-errors Monitoring                                     |     |

|            | and Stage Classification                                                                            | 134 |

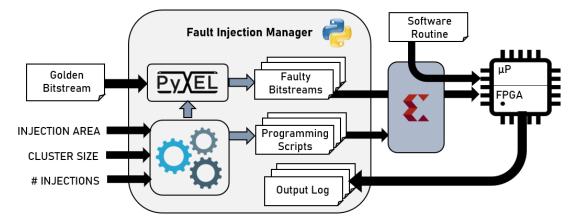

| 8.4        | Fault Injection Manager and Instrumentation Overview                                                | 135 |

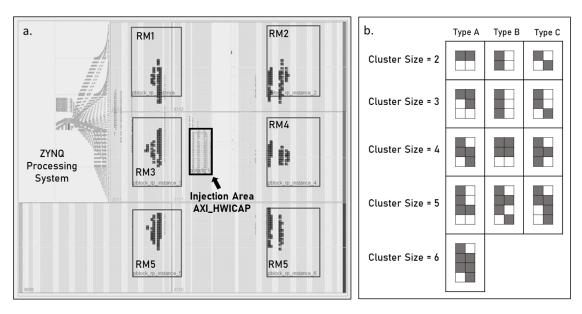

| 8.5        | Fault Injection Parameters: a) Highlights of the AXI_HWICAP                                         |     |

|            | Fault Injection Area within the DRPM on ZYNQ 7020; b) Injec-                                        |     |

|            | tion Cluster Sizes and Shapes as Observed in [109]                                                  | 136 |

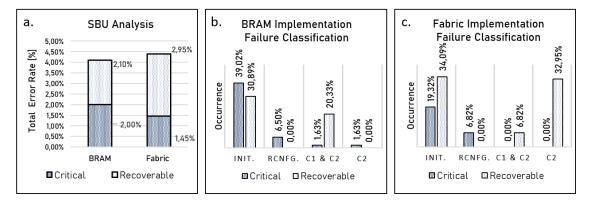

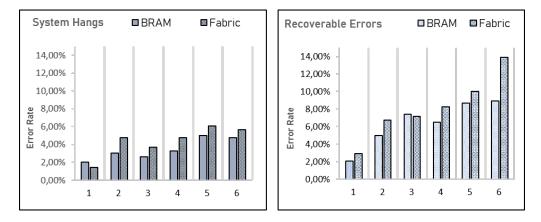

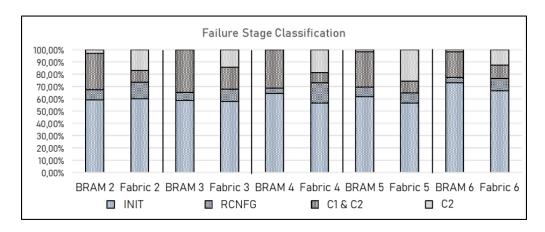

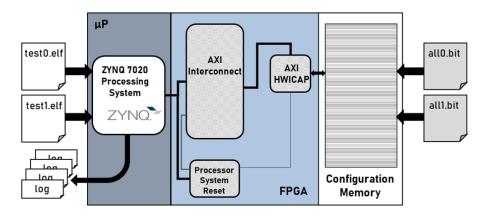

| 8.6        | Soft-errors Analysis Comparison for Single Bit Upset in BRAM and                                    |     |

|            | Fabric Implementation: Total Error Rate (.a) and Stage and Criti-                                   |     |

|            | cality Classification Rates (.b and .c) [112]                                                       | 138 |

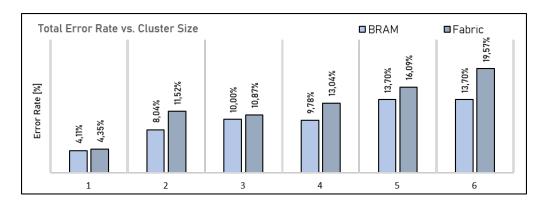

| 8.7        | Total Error Rate for Multiple Bit Upset in BRAM and Fabric Im-                                      |     |

|            | plementations for Different Cluster Sizes                                                           | 140 |

| 8.8        | Multiple Bit Upset Criticality Comparisons: System Hang vs. Re-                                     |     |

|            | coverable Errors for BRAM and Fabric Implementations for Different                                  |     |

|            | Cluster Sizes                                                                                       | 140 |

| 8.9        | Failure Rate Distribution on DRPM Operational Stages according                                      |     |

|            | to the MBU cluster Sizes for BRAM and Fabric Implementations .                                      | 141 |

| 8.10       | Highlight of Initialization and Computation (C1&C2) Stages Per-                                     |     |

|            | centages on the Total Errors Rate according to the MBU cluster                                      |     |

|            | Sizes                                                                                               | 141 |

| 8.11       | ZYNQ 7020 SoC Setup for the On-line Semi-static Self-testing [125]                                  | 145 |

|            | Online Self-testing Software Routine Pseudocode [125]                                               | 145 |

|            | Bitstream Bitmaps for $0 \Rightarrow 1$ (a) and $1 \Rightarrow 0$ Tests (b) Obtained                |     |

|            | with PyXEL and the Vivado Implementation View of the $1 \Rightarrow 0$                              |     |

|            | Setup (c) $\ldots$ | 146 |

| 8.14       | Overview of the Instrumented Neutron Generator Radiation Test                                       | -   |

|            | Automated Setup [125]                                                                               | 147 |

|            | ÷ L J                                                                                               |     |

- 8.15 Instrumented Neutron Generator Radiation Test Setup: the ZYNQ-7020 SoC FPGA Sample Board Juxtaposed to the ThermoFisher P385 NG, which is Monitored by the Albatross 2080 [125].... 149

## Chapter 1

# Introduction

### 1.1 Reconfigurable Computing

#### 1.1.1 Origin and Paradigm

The concept of *Reconfigurable Computing* has been suggested for the first time in '60s by Gerald Estrin and his group at the University of California at Los Angeles (UCLA) [1]. The idea was driven by the fact the performances of available computing machines ware not scaling efficiently with the increasing computational demand and complexity of the algorithms to be faced at that time, highlighting the need to explore novel computing architectures moving forward the consolidated Von Neumann paradigm.

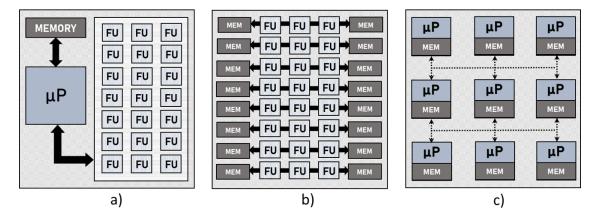

Starting from this idea, the first prototype of a reconfigurable platform was proposed by Estrin in [2] as a standard processor tightly coupled with an array of reconfigurable cells, which behavior could be defined by the processor during the execution according to the task effectively required at a specific time.

The key idea behind this reconfigurable machine consisted of coupling on a single computing architecture the flexibility typical of a software program running on standard processors and the high performances typical of dedicated custom hardware exploiting the advantages of both computing approaches.

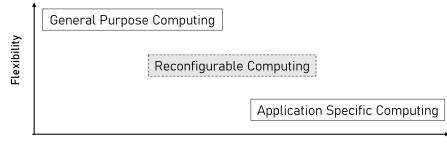

In fact, specialized hardware circuits, such as Application-Specific Integrated Circuits (ASICs), offer high performance since they are fabricated for a specific task, and thus fully optimized during design and manufacturing to achieve the highest performance in terms of delay, power consumption, and area for the target computation. At the same time, this specialization results in very poor flexibility and implies very high production costs.

On the other side, standard processors and general-purpose programmable systems offer high flexibility enabling the implementation of different software algorithms on the same machine after production and deployment.

Performance

Figure 1.1: Computing Implementations: Flexibility vs. Performance

However, their flexibility and lower costs result in performance losses because even if different algorithms can be easily tailored on them the fixed and generalpurpose hardware cannot optimally support all their varying computational requirements.

Therefore, the Reconfigurable Computing paradigm aims at filling the gap between the two classic computing approaches by enabling hardware designs to be customized and optimized while deployed and achieving the in-field flexibility typical of software [3][4].

Accordingly, in 1999, Andre Dèhon and John Wawrzynek defined in [5] reconfigurable architectures as computing machines that enable, simultaneously, customization after fabrication to execute any algorithm, and spatial computation to execute their tasks.

In their view, these two properties are the ones allowing the definition of computing architectures able to adapt and change their functionalities while operating by repurposing their resources according to the needs required at a specific time.

This concept of on-line circuit specialization has been defined as *Run-time* or *Dy*namic Reconfiguration, and has been one of the leading features which have driven the increasing interest from both industries and academia in the development and deployment of reconfigurable architectures.

In fact, the feature of adapting the hardware circuitry according to the needs enables new opportunities for the efficient implementation and optimization of complex and intensive computations: the possibility to dynamically allocate resources to computing tasks at run-time allows the implementation of applications able to adapt to varying conditions and requirements, the deployment of systems requiring more resources than the ones physically available on the target device, and the introduction of error recovery and prevention techniques to avoid application failures.

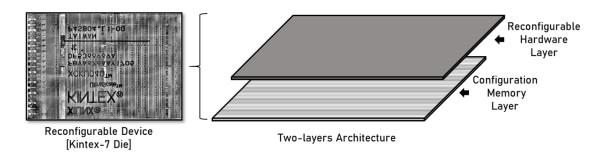

In general, reconfigurable hardware relies on a two-layers architectural model consisting of one layer of reconfigurable resources and one layer of configuration, a storage memory to hold the configuration data defining the behavior of the reconfigurable hardware layer (Fig. 1.2).

Figure 1.2: Reconfigurable Device's Two Layers Architecture: Reconfigurable Hardware Layer and Configuration Memory Layer

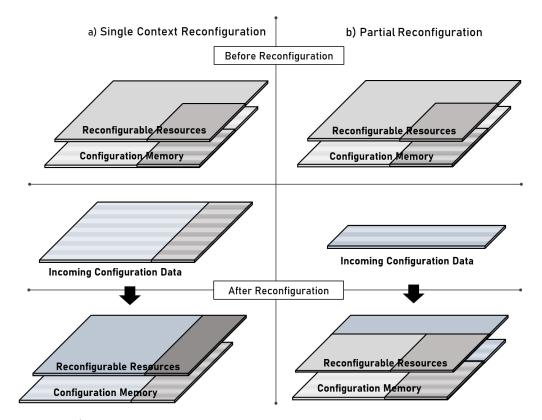

The content of the configuration memory layer representing the circuitry implemented on the hardware layer can be is referred also as *context*. According to the architecture and the purpose, reconfiguration can be applied to the whole hardware context (*Single Context Reconfiguration*, Fig. 1.3a) or selectively to sub-portions of the reconfigurable layer (*Partial Reconfiguration* Fig. 1.3b).

Figure 1.3: a) Single Context Reconfiguration: the Whole Configuration Memory Content is Updated; b)Partial Reconfiguration: Only the Target Portion of the Configuration is Involved in the Procedure

In Single Context Reconfiguration, the full content of the configuration memory is written, and the configuration data involved in the reconfiguration coincide with the full image of the circuit programmed on the reconfigurable resource layer. This kind of reconfiguration is efficient in the case that the whole context deployed on the reconfigurable hardware needs to be modified. Conversely, when just some portions of the context require updates or modifications, the Single Context Reconfiguration is inefficient, as the longer reconfiguration times needed to write the full configuration memory are unjustified since also memory segments that do not require any updates are involved in the procedure.

On the other hand, Partial Reconfiguration enables rewriting only specific portions of the configuration memory, targeting only the data holding the settings for the target portion of the reconfigurable resource layer that requires modifications or updates. This enables to save reconfiguration time, reducing also the risk to affect context portions not involved in the procedure.

Furthermore, as both Single Context and Partial Reconfiguration can be performed offline or at run-time, when Partial Reconfiguration is performed at run-time, it enables the possibility for the rest of the hardware not involved in the procedure to continue its operation while reconfiguration is performed.

#### **Dynamic Partial Reconfiguration**

In detail, when reconfiguration is performed only on specific portions of the hardware fabric while the overall application is running, it is called *Dynamic Partial Reconfiguration* (DPR) and it can strongly improve the Reconfigurable Computing paradigm since it truly maximizes its efficiency and flexibility.

In fact, the possibility to address only a specific portion of the configuration memory allows to selectively apply optimizations just to the target area without stopping the execution, requires less data transfer, and reduces the time needed to perform the reconfiguration procedure [6][7].

In general, DPR is supported by hardware fabrics that allow detailed access to specific memory segments, both in reading and writing, without affecting the operation of the parts of the system not subject to reconfiguration and typically can be performed to pursue three main goals: area efficiency, power saving, and reliability [8][9][10].

In detail, thanks to DPR it is possible to time-multiplex the resources available on the fabric, to adapt or update target portions of the application to meet varying requirements, to activate or deactivate computing tasks to tune power consumption according to the required computational effort, and to repair or relocate damaged or critical hardware modules.

#### 1.1.2 Architectural Evolution and Granularity

Although an early prototype of the reconfigurable machine suggested in [2] was realized at UCLA, the Reconfigurable Computing paradigm remains theoretical until the '80s.

In those years the earliest devices allowing to be customized after manufacturing appear on the market, while from the '90s the production of more sophisticated and capable reconfigurable devices started to rapidly gain commercial attention among the consolidated ASIC and standard processors.

In fact, those years have witnessed a rapid evolution of programmable logic devices (PLDs), logic circuits allowing to define their behavior after the fabrication process one or multiple times programming their configuration settings through dedicated procedures.

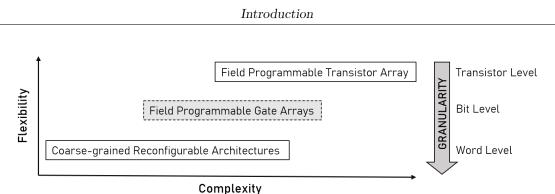

The smaller Programmable Array Logic (PAL) and Generic Array Logic (GAL), made of fixed simple logic nodes which could be combined through fuse patterns after fabrication to obtain the wanted Boolean functions, evolved into larger configurable devices, as the Complex Programmable Logic Devices (CPLDs), enabling the post-manufacturing customization of bigger digital circuits.

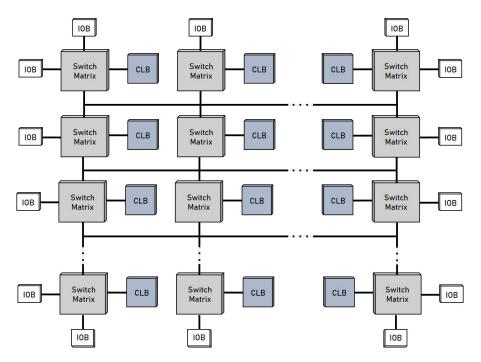

Eventually, Field Programmable Gate Arrays (FPGAs) reached the market. Early FPGA devices were based on an island-style architecture made programmable functional and connection tiles, allowing the implementation of more complex circuits thanks to their different gate array technology, which relies on programmable Look-up Tables (LUTs).

Providing an higher capacity, flexibility, integration, and in-field programmability versus their predecessors, FPGAs had increasingly become a more attractive solution for logic emulation, prototyping, and eventually, for the implementation of complex applications demanding high computational effort.

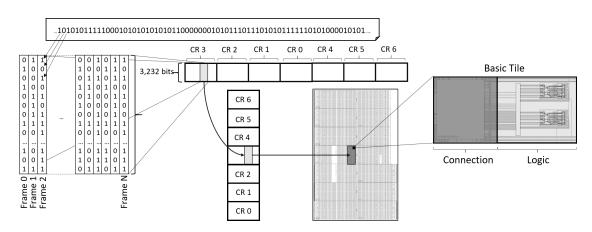

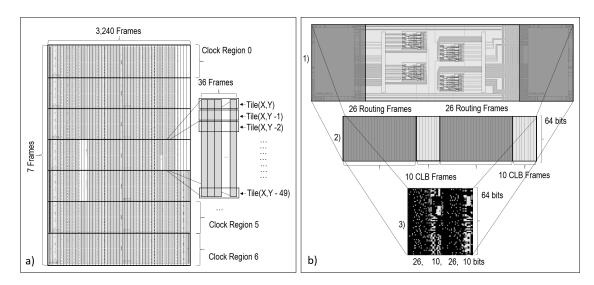

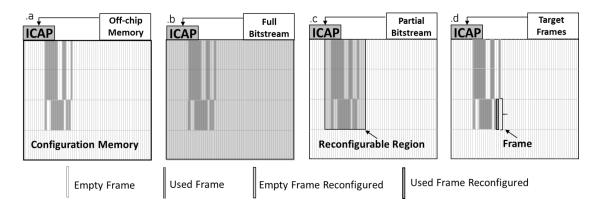

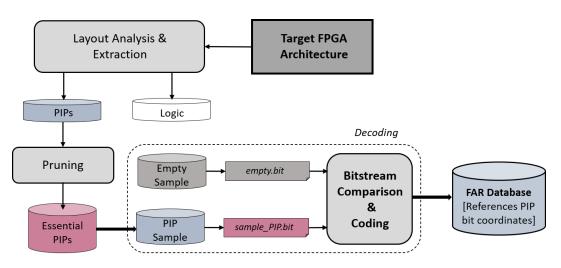

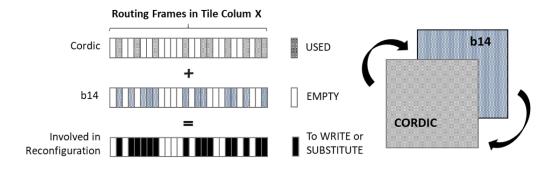

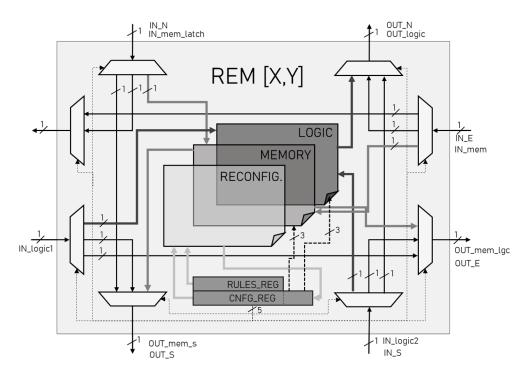

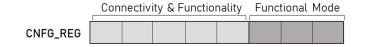

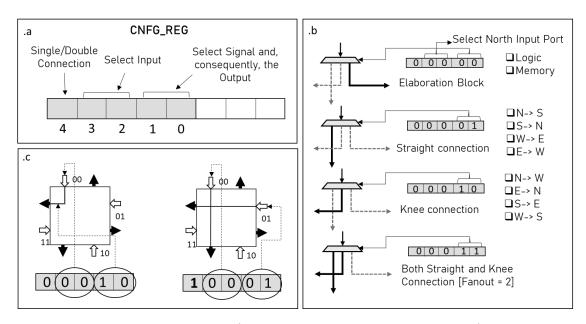

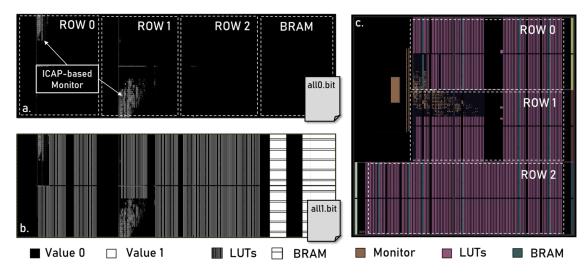

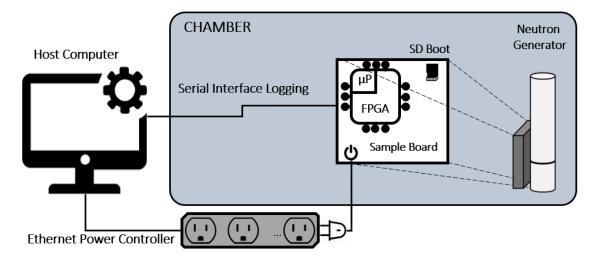

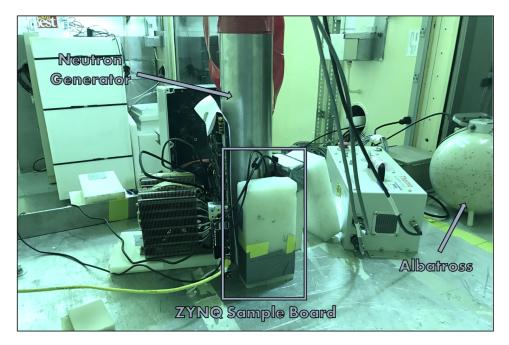

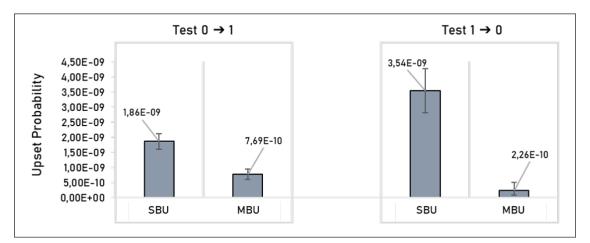

Thanks to their growing popularity, FPGA architectures have rapidly evolved over the last decades enhancing their flexibility in the reconfiguration process and implementing more efficient configuration supports and mechanisms.