## POLITECNICO DI TORINO Repository ISTITUZIONALE

Three-Level Unidirectional Rectifiers under Non-Unity Power Factor Operation and Unbalanced Split DC-Link Loading: Analytical and Experimental Assessment

| Original Three-Level Unidirectional Rectifiers under Non-Unity Power Factor Operation and Unbalanced Split DC-Link Loading: Analytical and Experimental Assessment / Cittanti, Davide; Gregorio, Matteo; Bossotto, Eugenio; Mandrile, Fabio; Bojoi, Radu In: ENERGIES ISSN 1996-1073 ELETTRONICO 14:17(2021), p. 5280. [10.3390/en14175280] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2919832 since: 2021-08-31T16:27:23Z                                                                                                                                                                                                                                                       |

| Publisher:<br>MDPI                                                                                                                                                                                                                                                                                                                          |

| Published<br>DOI:10.3390/en14175280                                                                                                                                                                                                                                                                                                         |

| Terms of use:                                                                                                                                                                                                                                                                                                                               |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                             |

| Publisher copyright                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                             |

(Article begins on next page)

Energies **2021**, 14, 5280 14 of 33

to as zero mid-point current modulation (ZMPCPWM) and ensures the converter operation with ideally zero low-frequency charge ripple [8,15,19].

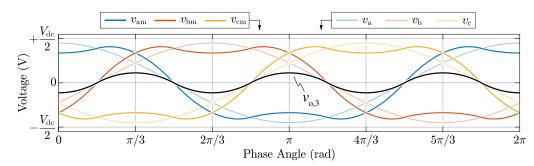

**Figure 9.** Zero-sequence voltage injection  $v_{\rm 0,3}$  according to the zero mid-point current modulation (ZMPCPWM) with M=0.9 and  $\varphi=0$ . The reference phase voltages  $v_{\rm a}$ ,  $v_{\rm b}$ ,  $v_{\rm c}$  and the resulting bridge-leg voltages  $v_{\rm am}$ ,  $v_{\rm bm}$ ,  $v_{\rm cm}$  are shown for completeness.

Unfortunately, the adoption of ZMPCPWM cannot ensure  $i_{\rm m}=0$  over the complete period when  $\varphi\neq 0$ , as pointed out in Section 2.5, since  $i_{\rm m,max}$  and  $i_{\rm m,min}$  cross the line defined by  $i_{\rm m}=0$  (see Figure 7). In fact,  $v_{\rm o,3}$  encounters the zero-sequence voltage limits  $v_{\rm o,max}, v_{\rm o,min}$  as soon as  $\varphi\neq 0$  (see Figure A4 in Appendix B). Nevertheless, the injection of (26) ensures the minimum possible value of  $\Delta Q_{\rm m,pp}=\Delta Q_{\rm m,pp,min}$  for a given power factor angle  $\varphi$ , since the saturated  $v_{\rm o}$  is as near as possible to the desired  $v_{\rm o,3}$  value. Therefore, the adoption of ZMPCPWM allows the minimization of the size of the split DC-link capacitors for a given mid-point voltage ripple requirement and is therefore particularly beneficial in three-level rectifiers.

Figure 7 shows the mid-point current local average obtained with ZMPCPWM (i.e.,  $i_{m,ZMPC}$ ) for different values of  $\varphi$ . It is directly observed that higher absolute values of  $\varphi$  increase the minimum mid-point charge ripple.

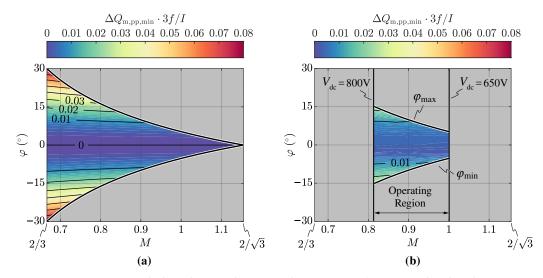

The exact analytical expression of  $\Delta Q_{m,pp,min}(M,\varphi)$  is derived in Appendix B for the complete operating region of the converter (i.e.,  $0 \le M \le 2/\sqrt{3}$  and  $-\pi/6 \le \varphi \le \pi/6$ ). These results are illustrated in normalized form in Figure 10, where the analytical expression (A13) is compared to experimental measurements (see Section 3.2.4), showing excellent agreement.

Figure 10. Minimum DC-link mid-point charge ripple  $\Delta Q_{\text{m,pp,min}}$  (i.e., normalized with respect to the peak phase current I and three-times the grid frequency 3f) for  $2/3 \le M \le 2/\sqrt{3}$ . (a) Analytical results and (b) experimental results, limited to the operating region of the rectifier prototype (see Section 3).

Energies **2021**, 14, 5280 15 of 33

It is worth noting that (A13) provides a straightforward approach to size the three-level rectifier DC-link capacitors according to a maximum mid-point voltage ripple  $\Delta V_{m,pp,max}$  criterion, as

$$C_{\rm dc} \ge \frac{\Delta Q_{\rm m,pp,min}(M,\varphi)}{2\Delta V_{\rm m,pp,max}},\tag{27}$$

where M and  $\varphi$  must be selected as the worst-case values within the operating range of the considered application. However, since (27) tends to 0 for  $\varphi = 0$  (i.e., the analytical approach neglects the switching-frequency charge ripple), if the rectifier is exclusively operated under unity power factor,  $C_{\rm dc}$  can be sized with conventional approaches derived for two-level inverters [38].

## 3. Experimental Results

Ι

$V_{\rm dc}$

L

$C_{dc}$

$f_{\rm sw}, f_{\rm s}$

In this section, the rectifier limits and performance in terms of displacement power factor (DPF), current total harmonic distortion (THD), maximum mid-point current capability and minimum mid-point charge ripple are experimentally assessed on a digitally controlled T-type converter prototype, supporting the theoretical analysis provided in Section 2, Appendices A and B. For reasons of conciseness, the converter performances are here evaluated only in steady-state conditions, nevertheless a complete assessment of the dynamical behavior of the considered rectifier prototype is provided in [16].

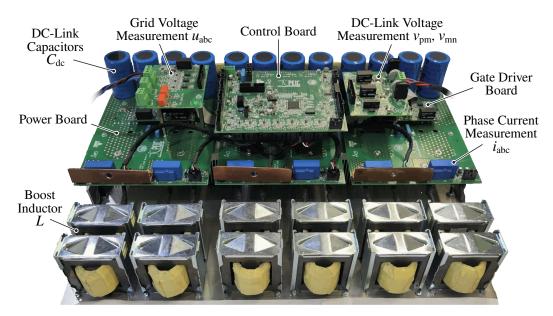

The specifications and the nominal operating conditions of the three-level T-type unidirectional rectifier exploited for the experimental validation are reported in Table 1. It is worth noting that this converter has been designed as the active front-end stage of an electric vehicle ultra-fast battery charger [16,39]. The rectifier prototype is illustrated in Figure 11 and consists of two paralleled three-phase 30 kW units, realized for modularity reasons. Nevertheless, only one converter unit is used in the experimental tests, due to the maximum power limitation of the available equipment.

| Parameter | Description            | Value  |

|-----------|------------------------|--------|

| f         | grid frequency         | 50 Hz  |

| P         | nominal active power   | 30 kW  |

| S         | nominal apparent power | 30 kVA |

| V         | peak phase voltage     | 325 V  |

peak phase current

DC-link voltage

boost inductance

DC-link capacitance switching, control frequency

61.5 A

650-800 V

$150-190 \, \mu H$

4080 µF

20 kHz

Table 1. Three-level unidirectional T-type rectifier specifications and nominal operating conditions.

Each converter bridge-leg employs two 650 V Si MOSFETs connected in anti-series (i.e., as 4Q switch) operating at 20 kHz and two 1200 V Si fast-recovery diodes. Furthermore, the converter boost inductors employ XFlux  $60\mu$  powder cores from Magnetics [40], which are characterized by a soft-saturating B–H characteristic. This feature leads to a current-dependent variable inductance value (see Table 1), which must be taken into account in the control tuning [16]. The detailed characteristics of the inductor design are reported in [39], obtained as a result of the optimization procedure described in [41].

Energies **2021**, 14, 5280 16 of 33

**Figure 11.** Overview of the three-level unidirectional T-type rectifier prototype used for the experimental tests. The converter consists of two paralleled 30 kW units: only one unit is exploited for the experimental verification, due to the maximum power limitation of the available equipment.

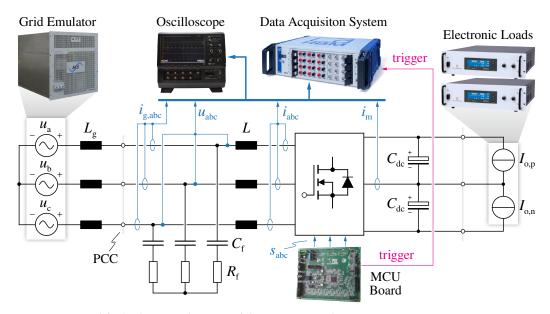

Figure 12 shows a schematic diagram of the adopted experimental setup. The T-type rectifier is connected to a grid emulator (i.e., emulating the 50 Hz, 400 V European lowvoltage grid) by means of an LCL filter, consisting of the converter boost inductors (L), filter capacitors ( $C_f = 15 \,\mu\text{F}$ ) equipped with series damping resistors ( $R_f = 0.8 \,\Omega$ ), and grid-side inductors ( $L_{\rm g}=100\,\mu{\rm H}$ ). The main scope of the LCL filter is to eliminate the switching-frequency harmonic content from the grid currents  $i_{g,abc}$  [17,42], so that a lower current total harmonic distortion (THD) is achieved and the converter may comply with grid-code standards [43,44]. Furthermore, the presence of the LCL filter allows isolation of the low-frequency component of the distortion, which depends on the control strategy, from the switching-frequency one, which only depends on the selected modulation scheme, allowing for a proper assessment of the converter closed-loop control performance. In the present case, the values of  $C_f$  and  $R_f$  are selected according to [39], and the value of  $L_g$  is representative of an equivalent inner grid impedance of  $\approx$ 0.02 pu. On the DC-side, the converter is connected to two independent electronic loads, which emulate the rectifier split DC-link loads. The measurements are performed both with a Teledyne LeCroy 500 MHz, 12-bit, 10 GS/s, 8-channel oscilloscope (i.e., employing isolated high-voltage differential probes for voltage measurements and standard current probes for current measurements), and with an HBM GEN4tB 2 MS/s data acquisition system, leveraging current and voltage sensors with high rated accuracy (i.e., <0.1%). In particular, the latter approach has been exploited to automatically map the rectifier performance over its complete operating region. Energies **2021**, 14, 5280 17 of 33

Figure 12. Simplified schematic diagram of the experimental setup.

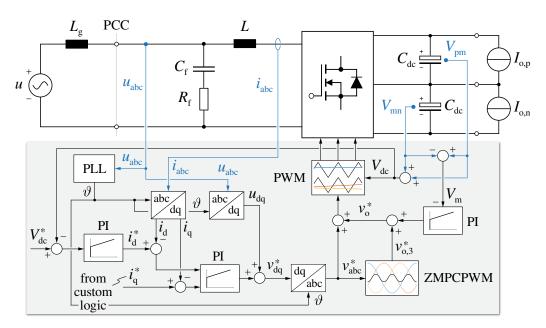

## 3.1. Multi-Loop Control Scheme

The rectifier is controlled with the full-digital multi-loop control strategy reported in [16], where the detailed description and tuning of all loops is provided. A conventional voltage-oriented dq current control scheme is adopted [17,45–47], complemented by a DC-link voltage loop, tracking the desired DC-link voltage value  $V_{\rm dc}$ , and a DC-link mid-point voltage balancing loop, ensuring limited steady-state and dynamical  $V_{\rm m}$  voltage deviation. A simplified block diagram of the complete system and the adopted control strategy is provided in Figure 13.

The voltages at the point of common coupling (PCC) are measured to achieve the reference frame synchronization with the grid by means of a phase locked loop (PLL) [48,49]. The measured grid voltages are then fed forward in the current control loop, to unburden the integral part of the PI regulator. Even though the digital sampling and update process is performed once per switching/control period, the  $i_{abc}$  current feedback values are obtained by means of oversampling (32 samples per control period) and averaging, to enhance the measurement quality around the current zero-crossings. In fact, traditional synchronous/asynchronous sampling approaches do not provide the correct average current value when discontinuous conduction mode (DCM) takes place [21,50], thus affecting the current control accuracy and leading to increased low-frequency distortion. The DC-link voltage loop controls the active power transfer of the rectifier and therefore provides the reference to the d-axis current control loop. The q-axis current  $i_q$ , instead, is typically controlled to compensate the reactive power injected by the filter capacitors  $C_{\rm f}$  (i.e., to ensure unity power factor operation at the PCC), nevertheless it can be set to any value that complies with the converter-side power factor angle limitations of the rectifier (see Section 2.4), being  $\varphi = \tan^{-1}(i_q/i_d)$ . Finally, the DC-link mid-point voltage balancing loop ensures  $V_{\rm pm} \approx V_{\rm mn}$  at all times, acting on the zero-sequence voltage  $v_{\rm o}$ injection [9,14-16,51]. In particular, this control loop theoretically does not interfere with the others, as  $v_0$  affects neither the active power transfer nor the phase current formation process (see Section 2.1.1). Furthermore, the measured  $V_{\rm m}$  is passed through a moving average filter operated at 3 f, so that the control loop does not react to the possibly occurring low-frequency mid-point voltage oscillation.

Energies **2021**, 14, 5280 18 of 33

**Figure 13.** Simplified single-phase equivalent circuit of the considered system and overview of the adopted digital multi-loop control strategy [16].

In practice, the complete converter multi-loop control strategy is implemented on a STM32G474VE MCU from ST Microelectronics [52] with an interrupt service routine running at  $f_s = 20 \, \text{kHz}$ .

## 3.2. Steady-State Performance Evaluation

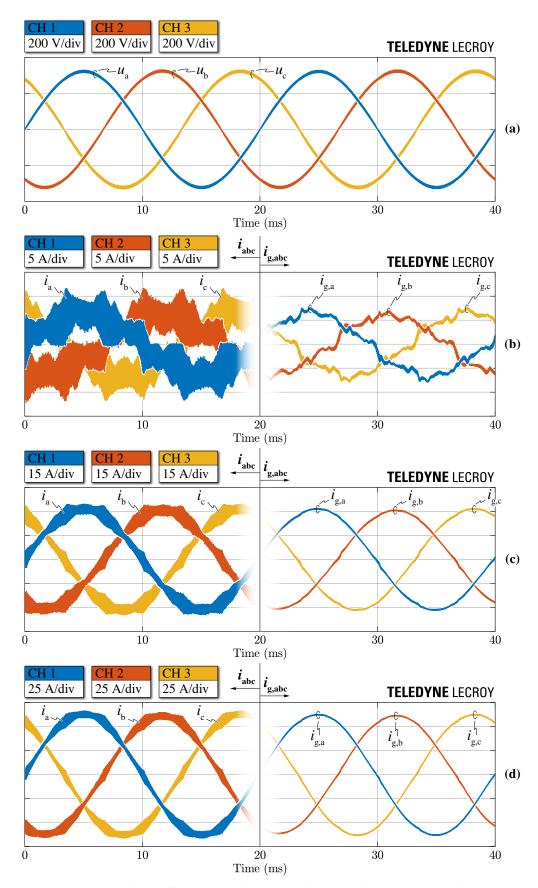

The most significant rectifier waveforms in steady-state operation are illustrated in Figure 14, where the grid voltages  $u_{abc}$ , the converter-side currents  $i_{abc}$  and the grid-side (i.e., filtered) currents  $i_{\mathrm{g,abc}}$  are shown for  $V_{\mathrm{dc}}=800\,\mathrm{V}$ ,  $\varphi=0$  and different values of transferred power. It is observed that the grid-side current quality improves with the rectifier loading. For instance, at 10% of the rated power (see Figure 14b) the converter-side current ripple amplitude becomes comparable to the current peak value, therefore leading to marked low-frequency zero-crossing distortion that bypasses the filter capacitor and appears in the grid-side currents. Even though the distortion at light load may seem large, the pronounced DCM operation of unidirectional rectifiers typically leads to much higher distortion levels [21]. In the present case, the pseudo-sinusoidal shape of the currents is maintained thanks to the adopted current oversampling and averaging strategy, the high current control loop bandwidth and the feed-forward contributions reported in Figure 13 [16]. At 50% and 100% of the rated power (see Figure 14c,d the quality of both converter-side and grid-side currents improves substantially, as the relative amplitude of the current ripple decreases and the zero-crossing distortion related to DCM operation is mostly eliminated by the current control loop [16].

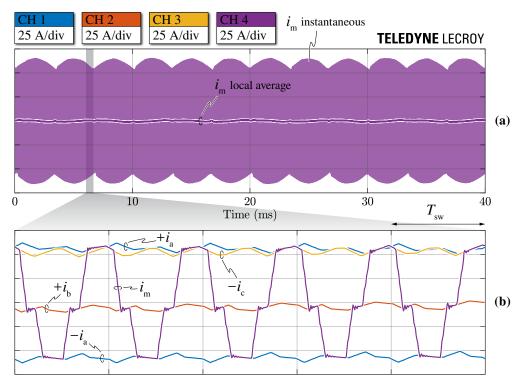

Both instantaneous and local average values of the DC-link mid-point current  $i_{\rm m}$  for  $V_{\rm dc}=800\,{\rm V}$  ( $M\approx0.81$ ),  $\varphi=0$  and  $P=30\,{\rm kW}$  are illustrated in Figure 15, where a focus is also provided in (b). Although the instantaneous value of  $i_{\rm m}$  jumps between the converter-side phase current values  $\pm i_{\rm a}$ ,  $\pm i_{\rm b}$ ,  $\pm i_{\rm c}$  and 0 (i.e., visible from the current envelopes), the local average value of  $i_{\rm m}$  remains approximately 0 along the complete grid period, due to the adopted zero-mid-point current modulation (ZMPCPWM) strategy. A focus of the instantaneous values of  $i_{\rm a}$ ,  $i_{\rm b}$ ,  $i_{\rm c}$  and  $i_{\rm m}$  towards the end of current sector  $\oplus$  is provided in Figure 15b, where the mid-point current is shown to jump between  $+i_{\rm a}$  (state 100),  $-i_{\rm a}$  (state 011),  $+i_{\rm b}$  (state 010) and  $-i_{\rm c}$  (state 110), as expected from space vector theory (see Figure 3b).

Energies **2021**, 14, 5280 19 of 33

**Figure 14.** Experimental waveforms in steady-state conditions with  $V_{\rm dc}=800\,{\rm V}$  and  $\varphi=0$ . Measured grid voltages  $u_{\rm abc}$  (a) and both converter-side currents  $i_{\rm abc}$  and grid-side currents  $i_{\rm g,abc}$  at (b) 10%, (c) 50%, and (d) 100% of the nominal power (i.e.,  $P=30\,{\rm kW}$ ).

Energies **2021**, 14, 5280 20 of 33

**Figure 15.** Experimental waveforms of the mid-point current  $i_{\rm m}$  instantaneous and local average values in steady-state conditions with  $V_{\rm dc}=800\,{\rm V},\ \varphi=0$  and  $P=30\,{\rm kW}$  (a). Focus of the instantaneous mid-point current towards the end of current sector ① (see Figure 3) and converter-side phase current values  $\pm i_{\rm a}$ ,  $+i_{\rm b}$ ,  $-i_{\rm c}$  (b).

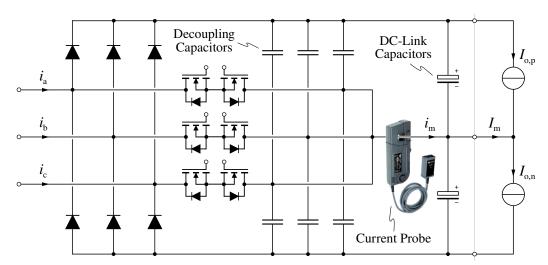

It is worth noting that the measurement of the instantaneous mid-point current value is not common in the literature (i.e., the only case known to the authors is [53]), as it represents a challenging task to achieve. In practice, the current measurement must be placed within the commutation loop of all bridge-legs, thus negatively affecting the switching performance of the rectifier. In the present case, the measurement of  $i_{\rm m}$  has been achieved by placing the current probe between the bridge-leg decoupling capacitors (i.e., 220 nF ceramic capacitors) and the DC-link capacitors (i.e., 4080  $\mu$ F electrolytic capacitors), as schematically illustrated in Figure 16. Even though the decoupling capacitors are placed in parallel to the DC-link capacitors, their small capacitance value does not substantially affect the mid-point current, especially considering the relatively low switching frequency of the rectifier.

**Figure 16.** Schematic overview of the DC-link mid-point current  $i_m$  measurement setup. The current probe is placed between the bridge-leg decoupling capacitors and the DC-link capacitors.

Energies **2021**, 14, 5280 21 of 33

Figures 17 and 18 show the most relevant rectifier waveforms under non-unity power factor operation and constant zero-sequence voltage injection, respectively. In particular, the reference bridge-leg voltages  $v_{\rm am}$ ,  $v_{\rm bm}$ ,  $v_{\rm cm}$ , the reference zero-sequence voltage  $v_{\rm o}$ , the converter-side currents  $i_{\rm abc}$ , the grid-side currents  $i_{\rm g,abc}$  and the DC-link mid-point current  $i_{\rm m}$  are shown for  $V_{\rm dc}=800\,{\rm V}$  and  $S=15\,{\rm kVA}$ . Furthermore, the effect of the zero-sequence voltage saturation  $v_{\rm o,max/min}$  on all measured quantities is highlighted by comparing the results with a conventional control implementation (i.e., with no saturation acting on  $v_{\rm o}$ ). It is worth noting that  $v_{\rm am}$ ,  $v_{\rm bm}$ ,  $v_{\rm cm}$  and  $v_{\rm o}$  are obtained from separate digital-to-analog converters (DACs) of the MCU (i.e., with a 0–3.3 V scale) and are thus rescaled in Figures 17a and 18a.

Figure 17 shows the operation of the rectifier with  $\varphi=15^\circ$ . In particular, Figure 17c highlights that non-unity power factor operation generates a large zero-crossing distortion if no zero-sequence voltage saturation is implemented. The enforcement of  $v_{\rm o,max/min}$ , in fact, allows the rectifier to correctly apply the desired bridge-leg voltage values even when the phase currents are phase-shifted with respect to the reference voltages, as described in Section 2. Consequently, undistorted operation under non-unity power factor is achieved. Furthermore, Figure 17d shows that by saturating the zero-sequence voltage, a larger midpoint current local average  $i_{\rm m}$  and thus a higher DC-link mid-point peak-to-peak charge ripple  $\Delta Q_{\rm m,pp}$  are obtained. This is because, to ensure the undistorted operation of the rectifier, the applied zero-sequence voltage  $v_{\rm o}$  departs from the ideal  $v_{\rm o,3}$  value introduced by the ZMPCPWM (see Figure 17a). It is also worth observing that the local average of  $i_{\rm m}$  obtained experimentally is in good agreement with the simulated waveforms reported in Figures 7 and A4b.

The rectifier waveforms with a constant zero-sequence voltage  $v_0 = 0.15 \, V_{\rm dc}/2$  added to  $v_{0,3}$  (i.e., ZMPCPWM injection) are shown in Figure 18. This injection emulates the converter performance under unbalanced split DC-link loading, i.e., when a constant mid-point current periodical average  $I_{\rm m} = I_{\rm o,n} - I_{\rm o,p}$  is required. This is highlighted in Figure 18d, where the injection of a positive zero-sequence voltage is shown to generate a negative value of mid-point periodical average  $I_{\rm m}$ , as expected from theoretical considerations. Additionally in this case larger  $i_m$  and  $\Delta Q_{m,pp}$  ripple values are obtained when the  $v_{o,max/min}$  saturation is enabled. Figure 18c shows that the zero-sequence voltage saturation  $v_{o,max/min}$  allows substantial improvement of the phase current waveforms. Nevertheless, in this case the zero-crossing distortion cannot be completely avoided, since the injection of the constant zero-sequence voltage contribution increases the amplitude of the converter-side current ripple (see Figure 14c for comparison), which widens the DCM window around the current zero-crossings and leads to higher distortion. It is worth noting that this issue can be greatly reduced in practice by independently controlling the two anti-series mid-point switches, such that the free-wheeling of the current through the mid-point is always possible [26]. In fact, even though in the present case the two antiseries switches are supplied by independent gate drivers, they receive equal PWM signals, greatly simplifying the modulation and the control of the rectifier. It should be pointed out that the low-frequency distortion would mostly disappear at full load (i.e.,  $P = 30 \,\mathrm{kW}$ ), due to the lower ratio between the current ripple and the current peak. However, this condition could not be tested, due to the power limitations of the adopted electronic loads.