# POLITECNICO DI TORINO Repository ISTITUZIONALE

Through-The-Barrier Communications in Isolated Class-E Converters Embedding a Low-k Transformer

# Original

Through-The-Barrier Communications in Isolated Class-E Converters Embedding a Low-k Transformer / Pareschi, Fabio; Celentano, Andrea; Mangia, Mauro; Rovatti, Riccardo; Setti, Gianluca. - STAMPA. - (2020), pp. 1-5. (Intervento presentato al convegno 2020 IEEE International Symposium on Circuits and Systems nel October 10-21, 2020) [10.1109/ISCAS45731.2020.9180486].

Availability:

This version is available at: 11583/2867036 since: 2021-01-25T16:24:45Z

Publisher:

**IEEE**

Published

DOI:10.1109/ISCAS45731.2020.9180486

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# Through-the-Barrier Communications in Isolated Class-E Converters embedding a low-k Transformer

Fabio Pareschi\*,<sup>‡</sup>, Andrea Celentano\*, Mauro Mangia<sup>†</sup>,<sup>‡</sup>, Riccardo Rovatti<sup>†</sup>,<sup>‡</sup>, Gianluca Setti\*,<sup>‡</sup>

\* DET – Politecnico of Torino, corso Duca degli Abruzzi 24, 10129 Torino, Italy.

email:{fabio.pareschi, andrea.celentano, gianluca.setti}@polito.it

DEI – University of Bologna, viale Risorgimento 2, 40136 Bologna, Italy. email: {mauro.mangia2, riccardo.rovatti}@unibo.it

\$ ARCES – University of Bologna, via Toffano 2/2, 40125 Bologna, Italy.

Abstract—In a recent paper, a through-the-barrier communication technique suitable for isolated resonant converters has been proposed. The approach is capable of sending data bidirectionally at high speed (one bit for each converter clock period) without the need of any additional isolating device other than the transformer necessary for the power transfer, and has been demonstrated by means of a proof-of-concept low-frequency prototype. In this paper we review that work under the assumption of increasing the operating frequency by using a coreless transformer presenting low losses, but also a low coupling factor k. This allows to increase the efficiency of the converter to a very high value (92% in the proposed design working at 6.78 MHz), but the communication speed has to be reduced (one bit every four clock cycles).

#### I. INTRODUCTION

Due to safety or grounding purposes, galvanic isolation from the main power supply is in many cases useful or even mandatory. Applications requiring such a feature range from safety-critical devices, such as medical equipment, to the most different scenarios [1]–[5].

To achieve this target, special approaches are required both for transferring the energy trough the isolation barrier, and for allowing the two isolated parts to communicate with the each other. The adoption of an isolation transformer is the classical solution almost always adopted for transferring energy; conversely, many different approaches can be found for creating an electrically isolated communication channel. Common solutions include extra pulse transformers, optocouplers, or high-voltage capacitors. Yet, these solutions pose several limitations in the realization of miniaturized or even fully integrated systems, as all these devices are typically the most cumbersome and difficult to integrate parts.

In the effort of moving towards miniaturized solutions, some recent approaches proposed to use a single isolation transformers both for energy and data transfer. Even if they strongly differ in methodology and application, the underlying idea is to use the data signal to modulate the power signal. Efficiency, effectiveness and complexity of the decoding depend on the particular case [6]–[8].

In this paper we focus on the methodology proposed in [9] that applies to a resonant class-E dc-dc converters. Briefly, the principle is based on the modification of a circuit parameter (in detail, the value of a capacitance by connecting in parallel or disconnecting an additional one) that, due to the properties of the resonant architecture, generates detectable changes in all circuit waveforms. The approach allows a bidirectional (half-duplex) fast communication, since a binary symbol (either backward, i.e., from the secondary to the primary side, or forward, i.e., from the primary to the secondary side) can be transmitted at each converter clock cycle. In [9] a 1 MHz prototype capable of delivering up to 1.2 W is presented as a proofof-concept. We review here the methodology, considering the case where a coreless transformer with a low coupling factor k is adopted to increase the converter working frequency. Communication is still possible; indeed, due to the lower coupling, the transmission of one bit requires more than one clock cycle, with a slightly different sensing strategy.

This paper is organized as follows. In Sec. II we review the methodology proposed in [9], highlighting the problems that may

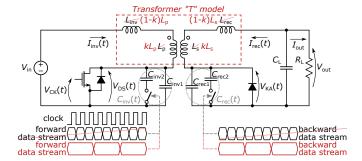

Fig. 1. Schematic and working principle (black color) of the class-E converter with bidirectional communication capability proposed in [9], and modification (red color) proposed when using a low-k transformer.

arise when k is too small. In Sec. III we propose a modification in the communication strategy to solve the identified problems, and in Sec. IV we validate this strategy by means of realistic circuit-level simulations of a case study. Finally, we draw the conclusion.

#### II. SYSTEM DESIGN AND CONSIDERATIONS

The schematic of the circuit proposed in [9] is depicted in Fig. 1. Basically, it is a class-E dc-dc converter [10]–[12] operating at frequency  $f_s=1/T$ , and featuring zero-voltage switching (ZVS), i.e., a resonant converter where reactive elements are designed to ensure that  $V_{\rm DS}(t)$ , when the main MOS is off, oscillates and reaches exactly zero level at the same instant when the MOS has to be turned on. This alleviates the turn-on transient problems, reduces the power consumption and allows higher speed operation [13], [14].

The strategy used to introduce communication relies on the semi-analytic design approach proposed in [15] and improved in [16]. Basically, it is enough to add two additional capacitances  $C_{\rm inv2}$  and  $C_{\rm rec2}$  in parallel to the already existing ones  $C_{\rm inv1}$  and  $C_{\rm rec1}$ , respectively, thus giving rise to the two time-varying capacitances  $C_{\rm inv}(t)$  and  $C_{\rm rec}(t)$ , whose value is modulated by the symbol to be transmitted, as sketched in Fig. 1. When communicating backward we set

$$\begin{split} C_{\rm inv}(t) &= C_{\rm inv1} + C_{\rm inv2} \\ C_{\rm rec}(t) &= \begin{cases} C_{\rm rec1} & \text{when transmitting '0'}_b \\ C_{\rm rec1} + C_{\rm rec2} & \text{when transmitting '1'}_b \end{cases} \end{split}$$

and when communicating forward

$$\begin{split} C_{\rm inv}(t) = \begin{cases} C_{\rm inv1} & \text{when transmitting '0'}_f \\ C_{\rm inv1} + C_{\rm inv2} & \text{when transmitting '1'}_f \\ C_{\rm rec}(t) = C_{\rm rec1} + C_{\rm rec2} \end{cases} \end{split}$$

where the notation 's' $_b$  or 's' $_f$  stands for a symbol or a sequence s transmitted backward or forward, respectively.

In this way, the perfect ZVS property is lost and replaced by a (perfectly tolerable) quasi-ZVS, where the  $V_{\rm DS}(t)$  at the MOS turn-

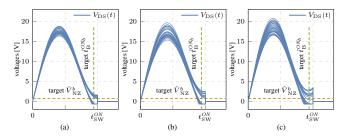

Fig. 2. Eye-diagram of the  $V_{\rm DS}(t)$  in backward communication mode according to the theoretical model developed in [9] using a transformer with coupling factor: (a): k=0.98; (b): k=0.9; and (c): k=0.8.

on time is *almost* zero. However, this enables communication between the two sides of the transformers.

In backward communication mode, decoding is achieved by sensing  $V_{\rm DS}(t)$  as illustrated in Fig. 2(a). When sending '1'<sub>b</sub>, the body diode of the MOS turns on at a time  $t_{\rm B}^{ON_b} < t_{\rm SW}^{ON}$ , whereas when sending '0'<sub>b</sub>, at the MOS turn-on instant  $t_{\rm SW}^{ON}$ , it is  $V_{\rm DS}(t_{\rm SW}^{ON}) =$  $V_{\rm NZ}^b > 0$ . Without entering into details that can be found in [9], two main problems arise in the converter behavior. First, the power transferred to the load depends on the transmitted symbol. This issue can be solved by adopting a coding strategy where '1'<sub>b</sub> and '0'<sub>b</sub> are balanced, so that the actual transferred power is the average we get in the two cases independently of the transmitted sequence. Second, there is a memory effect. Mathematically, the behavior of the converter in one clock period can be schematized as depending both on  $C_{inv}(t)$ and  $C_{\rm rec}(t)$ , and on the converter state that can be summarized with the two initial currents  $\{I_{inv}(0), I_{rec}(0)\}$ . The latter however depends on all previously transmitted symbols, and the same happens for  $V_{

m NZ}^b$ and  $t_{\rm B}^{ON_b}$ . According to [9], the dependence is weak, and it is possible to design a system according to its worst-case: designers should consider  $\hat{t}_{\rm B}^{ON_b}$ , defined as the *latest value* of  $t_{\rm B}^{ON_b}$  when transmitting '0'<sub>b</sub>, and  $V_{\rm NZ}^{b}$ , defined as the *lowest value* of  $V_{\rm NZ}^{b}$  when sending '0'<sub>b</sub>.

In backward communication, the suggested decoding strategy is differential and based on the sensing of  $V_{\rm KA}(t)$ . Being  $T_{\rm D}^f$  the time between two consecutive rectifying diode turn-on instants, when the transmitted symbol is the same as the previous one, it is  $T_{\rm D}^f \approx T$ . When transmitting a symbol '1' $_f$  after a '0' $_f$ , it is  $T_{\rm D}^f \approx T - \Delta \bar{t}_{\rm D}^{ONf}$ , and when transmitting a symbol '0' $_f$  after a '1' $_f$ , it is  $T_{\rm D}^f \approx T + \Delta \bar{t}_{\rm D}^{ONf}$  with  $T_{\rm D}^f \approx T$ .

The methodology was experimentally verified on a prototype operating at  $f_s=1\,\mathrm{MHz}$  using a WE-FLEX transformer by Würth Elektronik, with a coupling factor  $k\approx0.98$ . As almost all commercial devices, it is built using ferro-magnetic core that ensures a very high coupling factor, but losses are rapidly decaying when increasing the frequency. As an example, in the considered transformer, the quality factor drops to 4 at a frequency of  $10\,\mathrm{MHz}$ . Such a low value unfortunately prevents any useful application.

A possible workaround for high-frequency designs is to use coreless transformers, that may ensure at the same time a high operating frequency and low losses. This however comes at the cost of a lower coupling factor k, due to the lack of the ferromagnetic core that concentrates the magnetic flux.

Indeed, using a transformer with a low k requires to modify the described communication technique. In Fig. 2 we have shown the eye-diagram of  $V_{\rm DS}(t)$  when re-designing the circuit proposed in [9] using a transformer where k has been reduced from k=0.98 to k=0.9 and to k=0.8. The obtained eye-diagrams are compared with the target values of  $\hat{t}_{\rm B}^{ONb}$  and  $\hat{V}_{\rm NZ}^b$ , superimposed to the figure. Is it clear that, as k decreases, the spread between all possible waveforms increases. Furthermore, for k=0.8, desired values are only approximately reached. For lower values of k, the convergence of the mathematical script was not reached, and we were not able to

Fig. 3. Layout of the PCB inductor used both as primary and secondary coil in the coreless transformer.

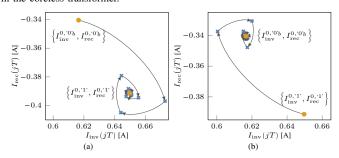

Fig. 4. Example of transitions to the two stable states during backward communication.

find a design with the given constraints.

Intuitively speaking, a possible explanation is the following one. When the coupling between the primary and the secondary side decreases, it is reasonable to assume that a larger variation in parameters at the secondary side (i.e., of  $C_{\rm rec}(t)$ ) is necessary to get the same change in the waveform at the primary side. This however implies a larger spread of the system state  $\{I_{\rm inv}(jT),I_{\rm rec}(jT)\}$  at the j-th clock cycle, and as a consequence, a stronger memory effect, with a growing difficulty in ensuring a good converter behavior for any possible transmitted sequence.

## III. Converter design with a low k transformer

In this paper we consider the design of a system using a transformer made of two printed circuit board (PCB) inductors of Fig. 3. The coils have been designed to operate at the ISM band centered at  $6.78\,\mathrm{MHz}$  in a wireless power transfer system, and their inductance is equal to  $1.47\,\mu\mathrm{H}$ . The transformer is obtained by using two of these coils, one on the top side of the PCB used a primary coil, and one on the bottom side of the PCB used a secondary one. The structure behaves as a 1:1 transformer, with a measured coupling factor k=0.52 and a quality factor of about 200 when implemented over a standard  $1.6\,\mathrm{mm}$  board with FR4 dielectric when working at  $6.78\,\mathrm{MHz}$ .

To enable communication between primary and secondary side, we propose two modifications with respect to the original technique proposed in [9].

First, the schematic can be simplified. When considering the classic "T" model for a transformer, with coupling factor k and a total inductance  $L_{\rm p}$  at the primary side (and  $L_{\rm s}$  at the secondary side, with  $L_{\rm p}/L_{\rm s}=(n_{\rm s}/n_p)^2$ , being  $n_{\rm s}/n_p$  the transformer turns ratio), we have two large leakage inductors  $(1-k)L_{\rm p}$  and  $(1-k)L_{\rm s}$  that can be used instead of the original resonance ones  $L_{\rm inv}$  and  $L_{\rm rec}$ , along with a perfectly coupled transformer with inductance  $kL_{\rm p}$  at the primary side and  $kL_{\rm s}$  at the secondary side 1. This has been illustrated in Fig. 1.

Second, it is mandatory to mitigate the catastrophic consequences of the stronger memory effect. The solution we propose is to repeat the transmission of any symbol for a number R of consecutive clock periods. The intuitive effect on the system state  $\{I_{\mathrm{inv}}(jT), I_{\mathrm{rec}}(jT)\}$  of allowing the converter to work in the same configuration (i.e., with

<sup>1</sup>Note that  $L_{\rm inv}=0$  was assumed in [9] to work with a simpler schematic.

Fig. 5. Basic working principle of the decoding. (a) Backward communication. (b) Forward communication.

the same value of  $C_{inv}(t)$  and  $C_{rec}(t)$ ) for many consecutive clock periods is illustrated in Fig. 4: independently of the initial condition, the converter is moving towards a stable state that does not depend anymore on previous transmitted symbols. In other words, for large R, the converter is always moving towards one of the three stable

- s:  $\left\{ I_{\text{inv}}^{0,'1'}, I_{\text{rec}}^{0,'1'} \right\}$  when transmitting either '1'<sub>b</sub> or '1'<sub>f</sub> (i.e.,  $C_{\text{inv}}(t) = C_{\text{inv1}} + C_{\text{inv2}}$  and  $C_{\text{rec}}(t) = C_{\text{rec1}} + C_{\text{rec2}}$ );  $\left\{ I_{\text{inv}}^{0,'0b}, I_{\text{rec}}^{0,'0b} \right\}$  when transmitting '0'<sub>b</sub> (i.e.,  $C_{\text{inv}}(t) = C_{\text{inv1}} + C_{\text{inv2}}$  and  $C_{\text{rec}}(t) = C_{\text{rec1}}$ );  $\left\{ I_{\text{inv}}^{0,'0f}, I_{\text{rec}}^{0,'0f} \right\}$  when transmitting '0'<sub>f</sub> (i.e.,  $C_{\text{inv}}(t) = C_{\text{inv1}} + C_{\text{inv2}} \right\}$

and  $C_{\rm rec}(t) = C_{\rm rec1} + C_{\rm rec2}$ . The transition from  $\left\{I_{\rm inv}^{0,0_b}, I_{\rm rec}^{0,0_b}\right\}$  to  $\left\{I_{\rm inv}^{0,1'}, I_{\rm rec}^{0,1'}\right\}$  is shown in Fig. 4(a), and the transition from  $\left\{I_{\rm inv}^{0,1'}, I_{\rm rec}^{0,1'}\right\}$  to  $\left\{I_{\rm inv}^{0,0_b}, I_{\rm rec}^{0,0_b}\right\}$ is shown in Fig. 4(b).

Of course, using a limited value for R will only produce an attenuation, and not a complete cancellation, of the memory effect. Yet, according to the figure, a value of R slightly larger than 3 is enough to ensure that the converter, when sending a new symbol, is in a state that is almost superimposed with one of the three above identified stable points.

The repetition of the transmitted bits imposes an update of the decoding strategy with respect to the original scheme proposed in [9]. In backward communication the detection is related to the way in which  $V_{\rm DS}(t)$  reaches the zero level. To let such a feature correctly show up, it is suggested to look at the last among the R clock cycles, where the dependence of previously transmitted symbol is attenuated. In forward communication, the decoding is on the  $V_{\rm KA}(t)$  and is differential; in this case, it is mandatory to observe the transition between the last clock cycles of the transmission of a symbol, and the first clock cycle in the transmission of the successive symbol.

An example for the backward communication mode is sketched in 5(a). The case R=3 is assumed. Any possible combination of three symbols is transmitted from the same initial condition, and only the final part of  $V_{\rm DS}(t)$  is shown. The reference time t = 0 is set to the rising edge of the clock cycle associated to the first transmission of the third symbol. We refer to waveforms associated to the transmission of sequences ending with symbol '1' with  $V_{\rm DS}^{\rm tx1b}(t)$ , and to waveforms associated to sequence ending with '0' with  $V_{\rm DS}^{\rm tx0b}(t)$ . From the figure it is clear that the two decoding quantities  $t_{\rm D}^{\rm tx0b}(t)$  are not well defined in the first clock period (i.e.,  $t \in [0,T]$  in the figure) of the transmitted bit. Instead, they converge to two well-defined values as the time increases.

The forward communication is considered in 5(b). As in the previous case, the transmission of all combination of three symbols is considered. Here the  $V_{\rm KA}(t)$  is plotted and the reference time t=0is set to the rectifying diode turn-on time during the last clock cycle

of the second transmitted bit, thus simplifying the evaluation of  $T_D^f$ as the first rectifying diode turn-on instant. Using a notation similar to the previous case, it is clear that all  $V_{\mathrm{KA}}^{'}(t)$  and  $V_{\mathrm{KA}}^{'}(t)$  are characterized by  $T_{\mathrm{D}}^{f} \approx T$ , whereas we have  $T_{\mathrm{D}}^{f} \approx T - \Delta \bar{t}_{\mathrm{D}}^{ONf}$  for all waveforms  $V_{\mathrm{KA}}^{'}(t)$ , and  $T_{\mathrm{D}}^{f} \approx T + \Delta \bar{t}_{\mathrm{D}}^{ONf}$ ) for all  $V_{\mathrm{KA}}^{'}(t)$ . Conversely, even if the choice of the reference time does not allow an immediate evaluation, it easy to see that measuring  $T_D^f$  in the following clock cycles brings no information. The reason is that the converter is moving toward a stable state, where  $T_{\rm D}^f=T$ . Note that, even if the decoding is performed at the first clock cycle, waiting R cycles before transmitting a new symbol is fundamental to reset the memory effect, and to allow a successful decoding of the new symbol.

3T

#### IV. PROOF OF CONCEPT: DESIGN EXAMPLE AT HIGH FREQUENCY

In this section, we consider the design of a 12 V-to-12 V class-E isolated converter ( $V_{\rm in} = 12 \, \text{V}$ ,  $V_{\rm out} = 12 \, \text{V}$ ) with bidirectional communication capabilities and an output current  $I_{\rm out}=175\,{\rm mA}.$ The resonant converter is designed to operate at a 6.78 MHz frequency, using the transformer made with two inductors illustrated in Fig. 3, with quality factor 198, turns ratio 1:1, total inductance  $L_{\rm p}=L_{\rm s}=1.47\,\mu{\rm H}.$  The main MOS switch is a Si2392ADS from Vishay (modeled with a on resistance of  $0.1 \Omega$ , and considering  $V_{

m B}^{ON} = 0.7 \, {

m V}$  for its body diode) and the rectifying diode is a Nexperia PMEG6030ELP Schottky barrier (modeled with  $V_{

m D}^{ON}=$  $0.55\,\mathrm{V}$  and an ON resistance of  $0.1\,\Omega$ ). The additional MOS used for attaching/detaching  $C_{inv2}$  and  $C_{rec2}$  is a standard small signal 2N7002. This solution allows to limit the parasitic introduced into the circuit. Capacitors are considered ideal, and by setting R=4, we get the values  $C_{\text{inv1}} = 142 \,\text{pF}$ ,  $C_{\text{inv2}} = 64 \,\text{pF}$ ,  $C_{\text{rec1}} = 178 \,\text{pF}$ , and  $C_{\text{rec2}} = 71 \,\text{pF}$ . With respect to the straightforward solution of the system, these values have been reduced to take into account the parasitic capacitances added to the circuit by the Si2392ADS, the PMEG6030ELP and the 2N7002, that have been evaluated as 112 pF, 127 pF and 6 pF, respectively. By setting R=4, the communication speed is set to about 1.7 Mbit/s.

The design of the system has been achieved under the assumption that R = 4 is enough to reset the memory effect, i.e., that the converter when sending a new symbol is always in one of the three stable states identified above. This simplifying assumption allows us to compute the design quantities as:

- 1)  $t_{\rm B}^{ON_b}$  and  $V_{\rm NZ}^b$  the body diode turn-on time and as  $V_{\rm DS}(t_{\rm SW}^{ON})$  in a system transmitting '1'<sub>b</sub> and '0'<sub>b</sub>, respectively;

- $\Delta \bar{t}_{\rm D}^{ON_f}$  is the best fit for the two assumptions: *i* the time passed between the two rectifying diode turn-on instants (as according to the decoding strategy described in the previous section) when transmitting '01'<sub>f</sub> is  $T + \Delta \bar{t}_{\rm D}^{ON_f}$ ; and ii- the

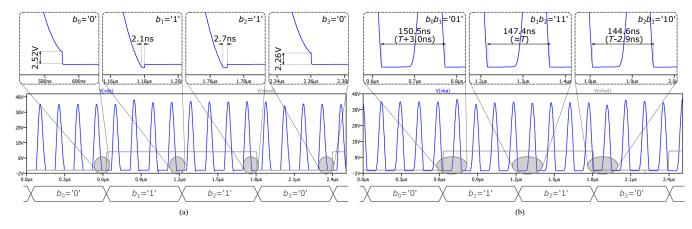

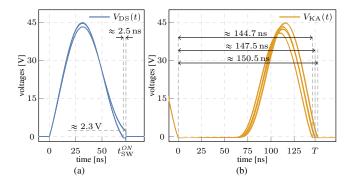

Fig. 6. Spice simulation of the proposed design. (a) Backward communication, showing the  $V_{\rm DS}(t)$  and the transmitted symbol. (b) Forward communication, showing the  $V_{\rm KA}(t)$  and the transmitted symbol.

time passed between the two rectifying diode turn-on instants when transmitting '10'<sub>f</sub> is  $T-\Delta \bar{t}_{\rm D}^{ONf}$ ;

3) the converter output power (in backward communication mode) is the average value of: i- the output power when transmitting '1' $_b$ ; ii- the output power when transmitting '0' $_b$ ; ii- the output power when sending '0' $_b$  for R clock cycle starting from the initial condition  $\{I_{\mathrm{inv}}^{0, \text{'1'}}, I_{\mathrm{rec}}^{0, \text{'1'}}\}$ ; and iv- the output power when sending '1' $_b$  for R clock cycle condition starting from the initial condition  $\{I_{\mathrm{inv}}^{0, \text{'0}_b}, I_{\mathrm{rec}}^{0, \text{'0}_b}\}$ . In forward communication mode, the converter output power is computed in a similar mode, considering  $\{I_{\mathrm{inv}}^{0, \text{'0}_b}, I_{\mathrm{rec}}^{0, \text{'0}_b}\}$  as initial condition in the last case.

While the first two conditions are quite easy to understand, we would like to give more details on the last one. We have implicitly assumed that all four combinations of two symbols '11', '10' '01' and '00' are equiprobable. The transmission of two symbols requires 2R clock cycles; we focus here on the power transferred during the last R clock cycle. When sending '00', and recalling the simplifying assumption that the system is capable to reach a stable state point in R clock cycles, the transferred power is given by the quantity at the item i. Similarly, the quantity at the item i is the power transferred in the last R clock cycles when sending '11', the quantity at the item i it he power when sending '10', and the quantity at the item i the power when sending '01'. The average value of these four quantities is the average power of the converter.

The proposed design has been obtained by imposing

$$V_{\rm NZ}^b = 2.5\,{\rm V},\ t_{\rm B}^{ON_b} = 3\,{\rm ns},\ \Delta \overline{t}_{\rm D}^{ON_f} = 3\,{\rm ns},\ I_{\rm out} = 175\,{\rm mA}$$

The screenshots from a SPICE simulation using realistic models developed by the manufacturer for all active devices is depicted in Fig. 6. In both cases of backward and forward communication, we have transmitted a pseudo-random sequence given by the maximum-length linear-feedback shift register (LSFR) of width  $\ell=7$ , whose periodicity is  $n=2^\ell-1=127$  bits. The figure shows only a portion of the simulation, where the transmitted bits are '0110'. The simulation of the transmission of the entire pseudorandom sequence shows a correct decoding both for backward and forward transmission. The average output current is evaluated in 176.6 mA for the backward communication, and 174.8 mA for the forward communication. Converter efficiency is 92.3% and 91.8%, respectively. As already noted in [9], the efficiency in the forward communication is lower due to higher losses on the MOS body diode.

The eye-diagrams for backward and forward communication extracted from the SPICE simulations are plotted in Fig. 7(a) and 7(b), respectively. For the backward communication we have considered only the R-th clock cycle in each bit transmission. From the figure,

Fig. 7. Eye diagrams extracted from a spice simulation. (a) Backward communication. (b) Forward communication.

we have  $V_{\mathrm{NZ}}^b \approx 2.2\,\mathrm{V}$  and  $t_{\mathrm{B}}^{ON_b} \approx 2.3\,\mathrm{ns}$  as worst-case conditions. For the forward communication, we have considered the transition between the two clock cycles immediately before and immediately after the change of the transmitted bit. The worst-case condition is  $\Delta \bar{t}_{\mathrm{D}}^{ON_f} \approx 2.4\,\mathrm{ns}$ . All observed values are very similar to that imposed by using the approximated design procedure described.

## V. CONCLUSION

We have reviewed a through-the-barrier communication strategy recently proposed in the literature, that allows the two sides of an isolated class-E resonant converter to communicate with each other by a simple modulation of the energy signal across the main power transformer, and without the need of any other additional isolating devices. In this paper the case of using a low-k coreless transformer as isolating device is considered, and the effect of the low coupling on the communication is analyzed. With a few modifications with respect to the original work it is still possible to establish a communication channel. Realistic circuit-level simulations of a case study show the possibility to design an isolated converter operating at 6.78 MHz with an additional isolated data channel with almost  $2\,\mathrm{Mbit/s}$  capacity, and an efficiency of about 92%.

#### ACKNOWLEDGMENT

This project has received funding from the ECSEL Joint Undertaking under grant agreement No 737434. This Joint Undertaking receives support from the European Unions Horizon 2020 research and innovation program and Germany, Slovakia, Netherlands, Spain, Italy.

#### REFERENCES

- [1] W. Liu *et al.*, "A neuro-stimulus chip with telemetry unit for retinal prosthetic device," *IEEE J. Solid-State Circuits*, vol. 35, no. 10, pp. 1487–1497, Oct. 2000.

- [2] M. Ghovanloo and S. Atluri, "A wide-band power-efficient inductive wireless link for implantable microelectronic devices using multiple carriers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 10, pp. 2211–2221, Oct. 2007.

- [3] G. Wang, P. Wang, Y. Tang, and W. Liu, "Analysis of dual band power and data telemetry for biomedical implants," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 3, pp. 208–215, Jun. 2012.

- Circuits Syst., vol. 6, no. 3, pp. 208–215, Jun. 2012.

[4] M. Jain, M. Daniele, and P. K. Jain, "A bidirectional DC-DC converter topology for low power application," *IEEE Trans. Power Electron.*, vol. 15, no. 4, pp. 595–606, Jul. 2000.

- [5] I. Barbi and R. Gules, "Isolated DC-DC converters with high-output voltage for TWTA telecommunication satellite applications," *IEEE Trans. Power Electron.*, vol. 18, no. 4, pp. 975–984, Jul. 2003.

[6] R. S. Yang, L. K. Chang, and H. C. Chen, "An isolated full-bridge DC-

- [6] R. S. Yang, L. K. Chang, and H. C. Chen, "An isolated full-bridge DC-DC converter with 1-MHz bidirectional communication channel," *IEEE Trans. Ind. Electron*, vol. 58, no. 9, pp. 4407–4413, Sep. 2011.

[7] A. Seidel, M. Costa, J. Joos, and B. Wicht, "Isolated 100% PWM gate

- [7] A. Seidel, M. Costa, J. Joos, and B. Wicht, "Isolated 100% PWM gate driver with auxiliary energy and bidirectional FM/AM signal transmission via single transformer," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2015, pp. 2581–2584.

- [8] P. Lombardo, V. Fiore, E. Ragonese, and G. Palmisano, "A fully-integrated half-duplex data/power transfer system with up to 40mb/s data rate, 23mw output power and on-chip 5kv galvanic isolation," in *IEEE international solid-state circuits conference (ISSCC)*, Feb. 2016, pp. 300–301.

- [9] F. Pareschi, N. Bertoni, M. Mangia, R. G. Massolini, G. Frattini, R. Rovatti, and G. Setti, "Class-E isolated DC-DC converter with highrate and cost-effective bidirectional data channel," *IEEE Trans. Power Electron.*, 2020, doi: 10.1109/TPEL.2019.2940661.

- [10] R. Gutmann, "Application of RF Circuit Design Principles to Distributed Power Converters," *IEEE Trans. Ind. Electron. and Control Instr.*, vol. IECI-27, no. 3, pp. 156–164, Aug. 1980.

[11] R. Redl, B. Molnar, and N. Sokal, "Class E Resonant Regulated DC/DC

- [11] R. Redl, B. Molnar, and N. Sokal, "Class E Resonant Regulated DC/DC Power Converters: Analysis of Operations, and Experimental Results at 1.5 MHz," *IEEE Trans. Power Electron.*, vol. PE-1, no. 2, pp. 111–120, Apr. 1986.

- [12] M. K. Kazimierczuk and D. Czarkowski, Resonant Power Converters, 2nd ed. Wiley, Mar. 2011.

- [13] N. Sokal and A. Sokal, "Class E-A new class of high-efficiency tuned single-ended switching power amplifiers," *IEEE J. Solid-State Circuits*, vol. 10, no. 3, pp. 168–176, Jun. 1975.

- [14] M. K. Kazimierczuk, RF Power Amplifiers, 2nd ed. Wiley, Nov. 2014.

- [15] N. Bertoni, G. Frattini, R. Massolini, F. Pareschi, R. Rovatti, and G. Setti, "An Analytical Approach for the Design of Class-E Resonant DC-DC Converters," *IEEE Trans. Power Electron.*, vol. 31, no. 11, pp. 7701– 7713, Nov. 2016.

- [16] F. Pareschi, N. Bertoni, M. Mangia, R. Rovatti, and G. Setti, "A Unified Design Theory for Class-E Resonant DC-DC Converter Topologies," *IEEE Access*, vol. 7, pp. 83 825–83 838, 2019.