## POLITECNICO DI TORINO Repository ISTITUZIONALE

## Securing Critical Infrastructures

| Original Securing Critical Infrastructures / Carelli, Alberto (2020 Sep 03), pp. 1-167.                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Availability: This version is available at: 11583/2850592 since: 2020-10-30T11:25:26Z                                                   |  |

| Publisher: Politecnico di Torino                                                                                                        |  |

| Published DOI:                                                                                                                          |  |

| Terms of use: Altro tipo di accesso                                                                                                     |  |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |  |

|                                                                                                                                         |  |

| Publisher copyright                                                                                                                     |  |

|                                                                                                                                         |  |

|                                                                                                                                         |  |

|                                                                                                                                         |  |

(Article begins on next page)

# Doctoral Dissertation Doctoral Program in Computer and Control Engineering ( $32^{nd}$ cycle)

# Securing Critical Infrastructures

#### Alberto Carelli

\* \* \* \* \* \*

### Supervisor

Prof. Stefano Di Carlo, Supervisor

#### **Doctoral Examination Committee:**

Prof., Ramon Canal, UPC - Universitat Politècnica de Catalunya (Spain)

Prof., Luca Maria Cassano, Politecnico di Milano (Italy)

Prof., Giorgio Di Natale, CNRS - Centre national de la recherche scientifique (France)

Prof., Alberto Bosio, Ecole Centrale de Lyon (France)

Prof., Marco Torchiano, Politecnico di Torino (Italy)

Politecnico di Torino 2020

| This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.                                   |

| Alberto Carelli<br>Turin, 2020                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                        |

# Summary

The growing threat of advanced cyber-attacks is a major cause of concerns for Information-Technology (IT) systems. Cybersecurity implies guaranteeing the security of the cyberspace from threats, which might present in different forms. Among the different classes of system that employ IT systems, there are the Critical Infrastructures. Critical infrastructures describe all physical and cyber systems, assets and other elements on which the society of a nation relies upon to maintain national security, economic vitality, and public health and safety. Examples of critical infrastructures for a nation can be power plants and energy supply networks, water supply systems, healthcare and hospital structures, transportation infrastructures, etc.

Originally Critical Infrastructures were designed as isolated systems not connected to the internet. They were based on old legacy systems, lacking the security protocols that are now built in. In recent years there has been a proliferation of new digital technologies that are designed to provides beneficial features to the systems where they are embedded. However, also the integration of such technologies makes the systems more vulnerable from a cybersecurity point of view by expanding the attack surface. The lack or inadequacy of appropriate security mechanisms leads to malicious attacks. If successful, attacks to these classes of systems, may lead to physical disruption or business operations and intellectual property theft. This may result in extensive economic losses and expose health or social well-being of people to safety and security risks.

This thesis focuses on the study of protection mechanisms for Critical Infrastructures from new cyberattacks. Different classes of attacks are considered.

Microarchitectural side-channel attacks exploit the microarchitecture of a microprocessor for unintended leakage of sensitive information. Targeting the computational cores, which are at the base of the majority of cyber assets, makes Critical Infrastructures and industrial control systems potentially vulnerable. Particular attention must be paid to the implementation of countermeasures against this type of attacks, because they might interfere with other crucial aspects of the system, such as safety.

Critical Infrastructures employ new technologies, such as reconfigurable platforms to exploit additional flexibility and acceleration capabilities. Also FPGAbased systems are vulnerable to attacks targeting the design to be deployed in-thefield. These attacks might target the confidentiality of the design or the injection of unintended features allowing the system to be controlled by malicious attackers or discover and exfiltrate sensitive information, such as intellectual property data. Although existing security measures already mitigate the attacks, they do not deal with a complex scenario where multiple different designers are involved.

Finally, a broader protection mechanism is provided through a hardware security module featuring secure key management and cryptographic functionalities. The robustness of the device is assessed through a physical and non-invasive side-channel attack aiming at the recovery of the stored encryption keys.

# Acknowledgements

I express my sincere appreciation to those who have contributed during this journey. I cannot help but recognize the invaluable support of colleagues, family and friends. Without any of them, this research work would not have been possible.

First, I thank my Ph.D. advisor, Professor Stefano Di Carlo, for giving me the chance to continue on this long journey. I express my endless gratitude for his endless and continuous support. I thank him for his wisdom, for the patience he has shown and for teaching me the work of rigorous research. I value and admire every word spent and every precious advice received. But most important, I appreciate all the time he dedicated to me.

I acknowledge every member of my thesis committee for their effort and the time they dedicated to read my dissertation. In particular, I would like to thank the reviewers, Prof. Luca Maria Cassano and Prof. Ramon Canal, with their kind and insightful comments in the last few steps of this journey.

I am grateful to my family for the constant support provided. I thank them for their continuous presence, luckily starting long before the Ph.D. (and also before primary school). I thank them for their help and for the invaluable lessons non-academia-related that shaped me during all these years.

Heartfelt thanks goes to my fellow travellers who made my stay in Lab 6 more enjoyable. In no-particular-order: thanks to Roberta, for her understanding, insight and empathy shown along the travel. Thanks to Alessandro, for having my back and for the great help given while working together "against" the publications.

Thanks to Pascal, Andrea, Stefano, Francesco, Fabio, Teo, Juan, Alberto, Luisa, Lorenzo, Luigi, Irene, Marilena and Flavia for sharing your time with me during the lab-life. Thank you all for the happiness and the funny moments shared together.

I thank also the lab-neighbors, Evelina Di Corso, Ph.D. and her friends, who have always been kind to me. Particular thanks to Valerio Tenace, Ph.D. and Amirhosein Toosi, Ph.D. for their support and their encouragement (not only) in a difficult situation. Many thanks to Valentino Razza, Ph.D. for his help, for every

coffee offered and for the many "tips and tricks" of the job. I gratefully acknowledge my friend Paolo Viotti, Ph.D. for his advices and suggestions along the way.

Also my gratitude goes to thesis students and friends met here: Gheorghe, Lubin, Lorenzo, Nicola, Giulio, Edrian, Mauro e Carlo Alberto.

A special thank goes to my other comrades outside the school. Though dispersed throughout the world, we are still somehow connected...

a.

# Contents

| Li | st of | Tables                                     | XI  |

|----|-------|--------------------------------------------|-----|

| Li | st of | Figures                                    | XII |

| 1  | Intr  | oduction                                   | 1   |

|    | 1.1   | Critical Infrastructures                   | 1   |

|    | 1.2   | Critical Infrastructures Technologies      | 6   |

|    | 1.3   | Security considerations                    | 8   |

|    | 1.4   | Safety domain                              | 10  |

|    | 1.5   | Goal of the Thesis                         | 10  |

| 2  | Het   | erogeneous Computing Architectures         | 13  |

|    | 2.1   | Heterogeneity in CPS                       | 13  |

|    | 2.2   | CPU                                        | 14  |

|    | 2.3   | GPU                                        | 15  |

|    | 2.4   | CPU + GPU                                  | 17  |

|    | 2.5   | FPGA                                       | 18  |

|    | 2.6   | Hardware Security Modules                  | 21  |

| 3  | Sect  | urity Attacks                              | 25  |

|    | 3.1   | Security overview                          | 25  |

|    | 3.2   | Side-Channel Attacks                       | 29  |

|    |       | 3.2.1 Side-Channel Attacks - Taxonomy      | 30  |

|    | 3.3   | Microarchitectural Side-Channel Attacks    | 32  |

|    |       | 3.3.1 Attack points in Microarchitecture   | 33  |

|    | 3.4   | Attacks on FPGA                            | 41  |

|    |       | 3.4.1 Introduction                         | 41  |

|    |       | 3.4.2 Bitstream Confidentiality            | 41  |

|    |       | 3.4.3 Bitstream Integrity and Authenticity | 42  |

|    |       | 3.4.4 IP Licensing and Activation          | 43  |

| 4 | Per        | formance Monitor Counter Attacks             | 45 |

|---|------------|----------------------------------------------|----|

|   | 4.1        | Introduction                                 | 45 |

|   | 4.2        | Performance Counters                         | 47 |

|   | 4.3        | CPS Architecture                             | 49 |

|   |            | 4.3.1 CPS and node architecture              | 49 |

|   |            | 4.3.2 Safety task                            | 50 |

|   |            | 4.3.3 Attack model                           | 52 |

|   | 4.4        | Attack mitigation                            | 54 |

|   |            | 4.4.1 Proportional Corruption                | 55 |

|   |            | 4.4.2 Selective Corruption                   | 56 |

|   |            | 4.4.3 Observations                           | 58 |

|   | 4.5        | Experimental Results                         | 59 |

|   |            | 4.5.1 Experimental setup                     | 59 |

|   |            |                                              | 62 |

|   |            | 4.5.3 Safety results                         | 65 |

|   | 4.6        |                                              | 69 |

| _ | DD/        |                                              | 71 |

| 5 |            |                                              | 73 |

|   | 5.1        |                                              | 73 |

|   | 5.2        | Assumptions, models and requirements         | 76 |

|   |            | 5.2.1 Actors                                 | 77 |

|   |            | v 1                                          | 78 |

|   |            | 5.2.3 Attack model                           | 79 |

|   | <b>-</b> 0 | v I                                          | 80 |

|   | 5.3        |                                              | 81 |

|   |            | 1                                            | 81 |

|   | _ ,        |                                              | 84 |

|   | 5.4        | *                                            | 89 |

|   |            |                                              | 89 |

|   |            |                                              | 90 |

|   |            | ±                                            | 90 |

|   |            |                                              | 91 |

|   | 5.5        |                                              | 91 |

|   |            | 1                                            | 92 |

|   |            |                                              | 94 |

|   |            | · ·                                          | 95 |

|   | 5.6        | Conclusion                                   | 97 |

| 6 | HSI        | M Secure Firmware Development and Analysis 1 | 01 |

|   | 6.1        |                                              | 01 |

|   | 6.2        |                                              | 02 |

|   | 6.3        | ·                                            | 04 |

|    | 6.4   | Softwa | are Architecture | 105 |

|----|-------|--------|------------------|-----|

|    |       | 6.4.1  | Firmware - Core  | 107 |

|    |       | 6.4.2  | Host library     | 112 |

|    | 6.5   | Securi | ty Analysis      | 115 |

|    |       | 6.5.1  | DPA              | 115 |

|    |       | 6.5.2  | Setup            | 116 |

|    |       | 6.5.3  | Results          | 118 |

|    |       | 6.5.4  | Discussion       | 120 |

|    |       | 6.5.5  | Acknowloedgments | 121 |

| 7  | Con   | clusio | ns               | 123 |

| A۱ | uthor | 's Pub | olication List   | 125 |

| Li | st of | Acron  | nyms             | 127 |

| Bi | bliog | raphy  |                  | 131 |

# List of Tables

| 2.1 | Comparison of the main features of GPU and CPU | 16  |

|-----|------------------------------------------------|-----|

| 4.1 | CCC and DCM Benchmarks Profiling               | 60  |

| 4.2 | CCC and DCM Benchmarks Profiling               | 61  |

| 6.1 | Flash sector layout                            | 110 |

| 6.2 | List of supported mode of operation for AES    | 113 |

| 6.3 | List of cryptographic primitives supported     | 113 |

| 6.4 | AES standard Key                               | 119 |

| 6.5 | AES standard Plaintext                         | 119 |

| 6.6 | DPA Results - Reference Device                 | 120 |

| 6.7 | DPA Results - HSM                              | 121 |

# List of Figures

| 2.1  | Comparison of simplified GPU and CPU architectures | 16  |

|------|----------------------------------------------------|-----|

| 2.2  | FPGA Logic Block (LUT-based)                       | 19  |

| 2.3  | FPGA internal architecture                         | 20  |

| 2.4  | FPGA Configuration process                         | 21  |

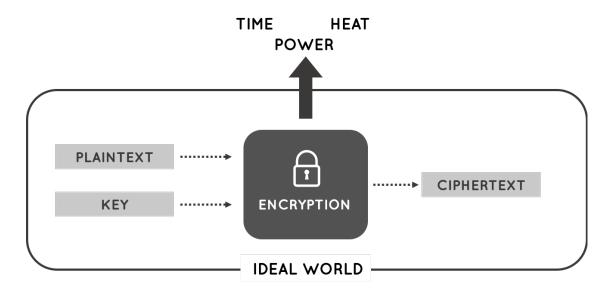

| 3.1  | Information Leakage                                | 30  |

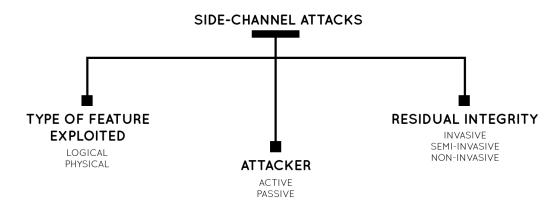

| 3.2  | Taxonomy of Side-Channel Attacks                   | 31  |

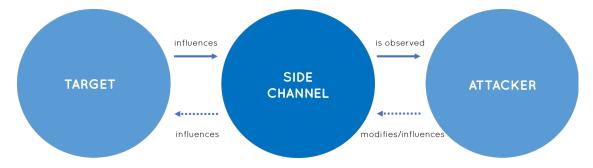

| 3.3  | Representation of active vs passive SCA            | 31  |

| 3.4  | Memory Hierarchy representation                    | 34  |

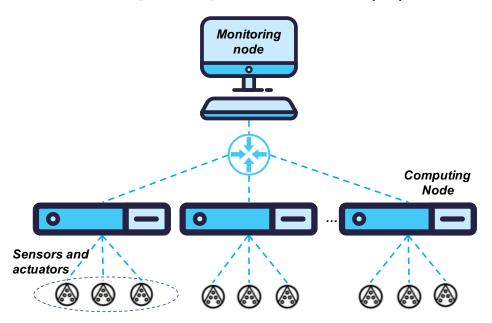

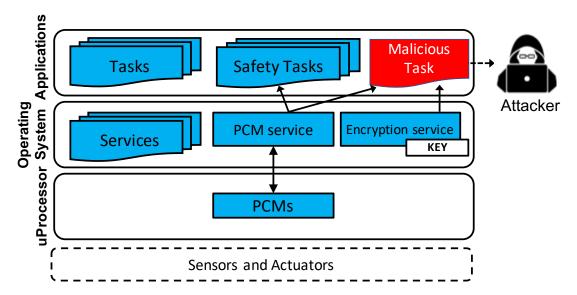

| 4.1  | CPS Architecture                                   | 49  |

| 4.2  | Node Architecture                                  | 50  |

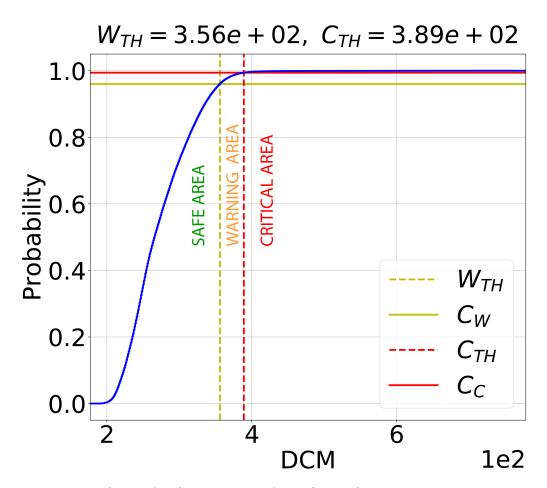

| 4.3  | CDF of DCM Counter - Benchmark                     | 51  |

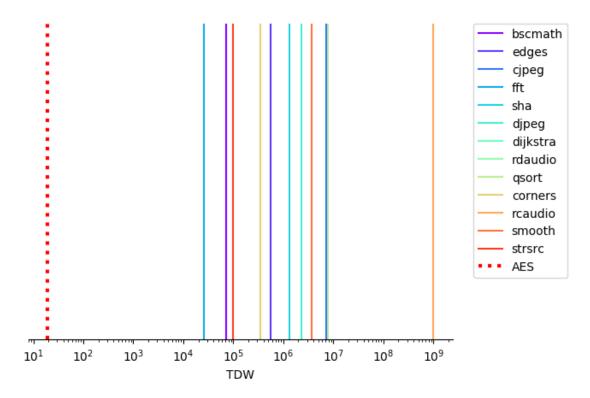

| 4.4  | CCC Counter - Benchmark Profiling                  | 56  |

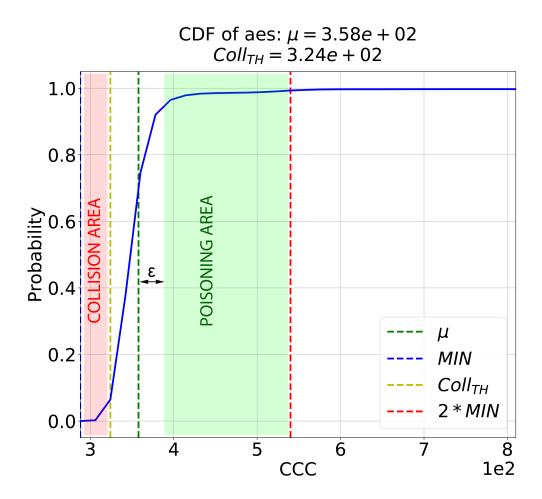

| 4.5  | CDF of CCC Counter - Encryption Service            | 57  |

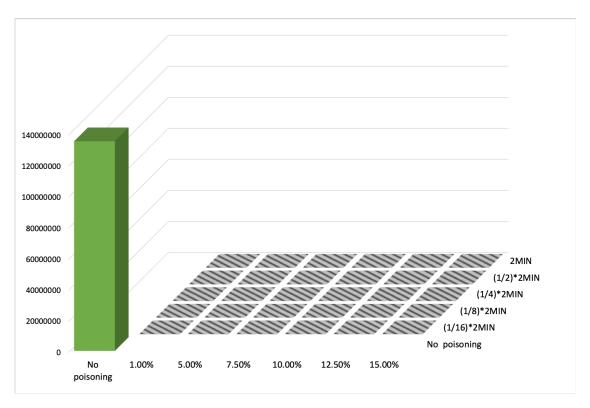

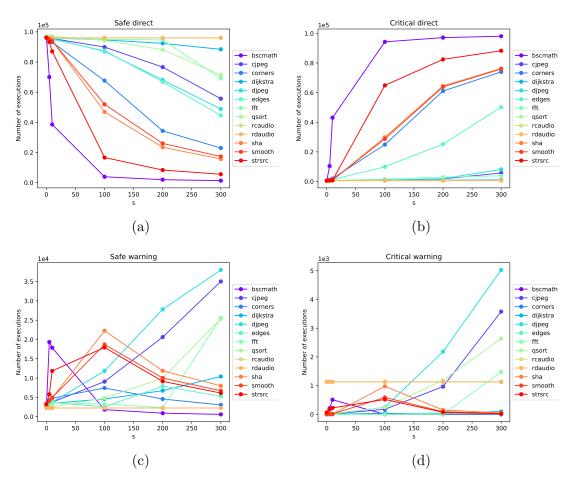

| 4.6  | Attack Results - CCC - Selective Corruption        | 63  |

| 4.7  | Attack Results - CCC - Proportional Corruption     | 64  |

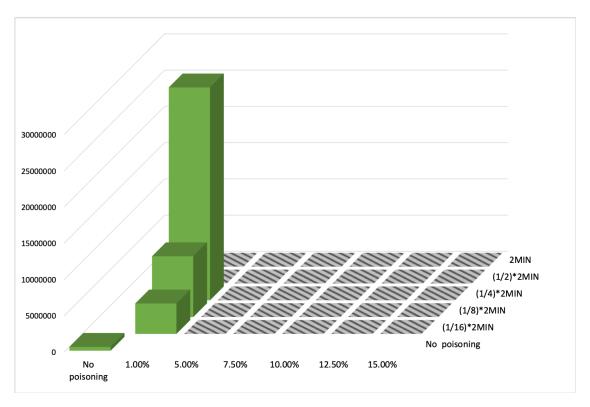

| 4.8  | Attack Results - DCM - Selective Corruption        | 65  |

| 4.9  | Attack Results - DCM - Proportional Corruption     | 66  |

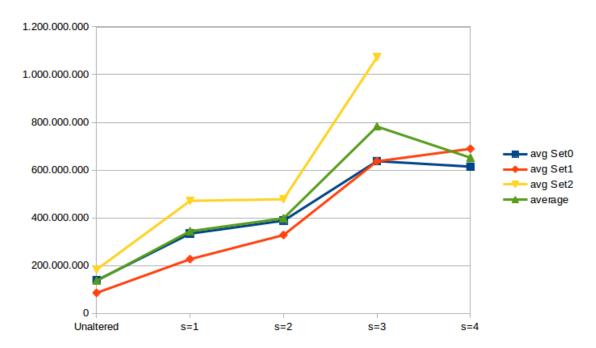

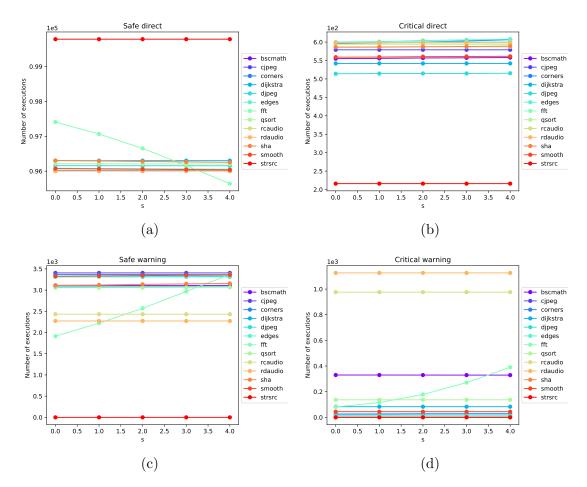

| 4.10 | Safety Results - CCC - Proportional Corruption     | 67  |

| 4.11 | Safety Results - DCM - Proportional Corruption     | 68  |

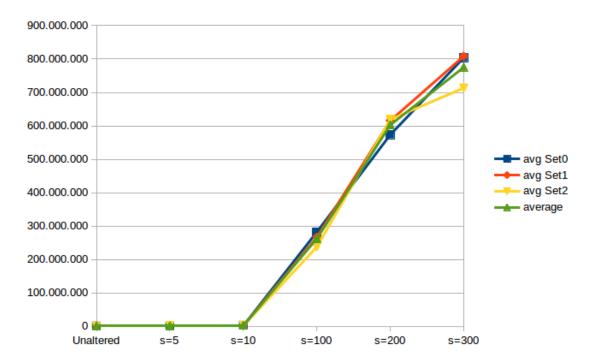

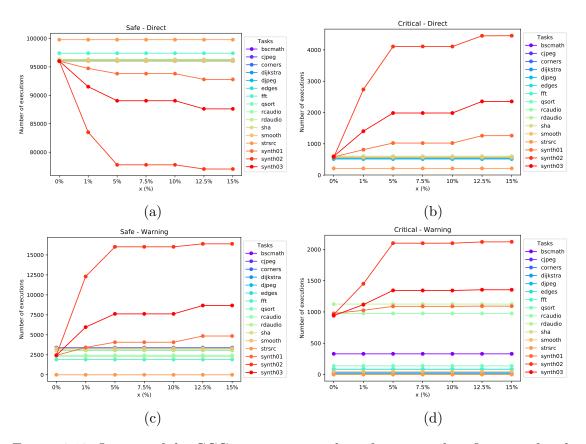

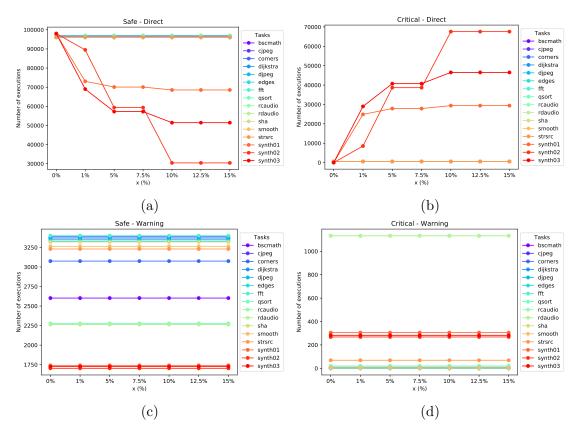

| 4.12 | Safety Results - CCC - Selective Corruption        | 70  |

| 4.13 | Safety Results - CCC - Selective Corruption        | 71  |

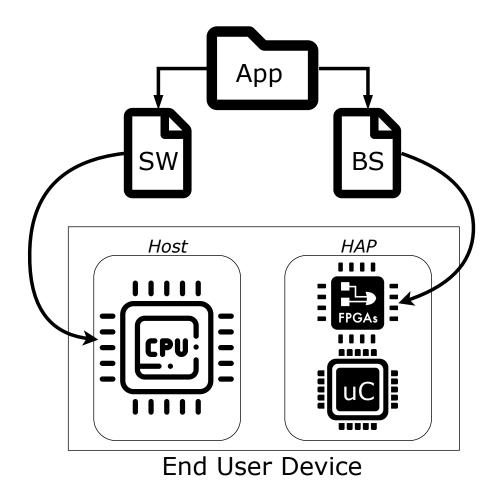

| 5.1  | Heterogeneous mobile application paradigm          | 76  |

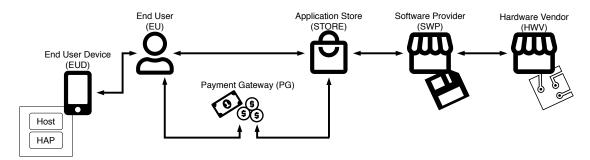

| 5.2  | Actors involved                                    | 77  |

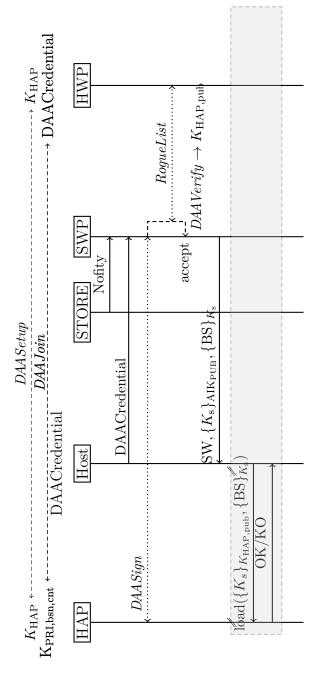

| 5.3  | Workflow Simple Scenario                           | 98  |

| 5.4  | Workflow Full Scenario                             | 99  |

| 5.5  | End User Device Architecture                       | 100 |

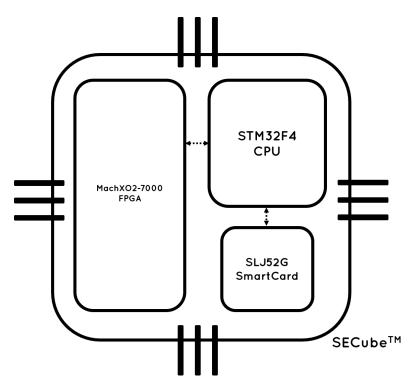

| 6.1  | Hardware Architecture                              | 105 |

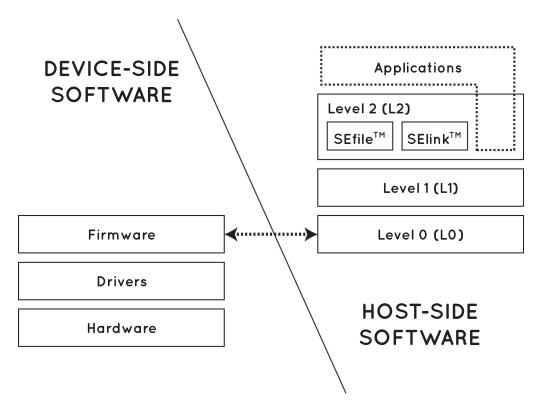

| 6.2  | Software Architecture                              | 107 |

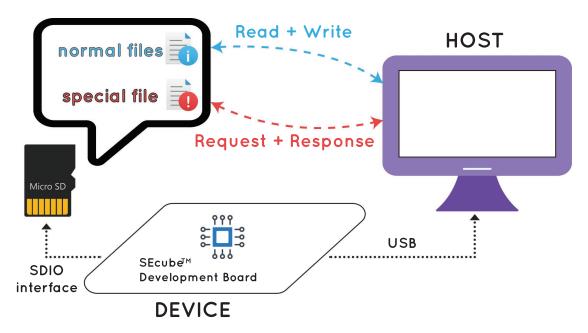

| 6.3  | Basic Request-Response communication protocol      | 108 |

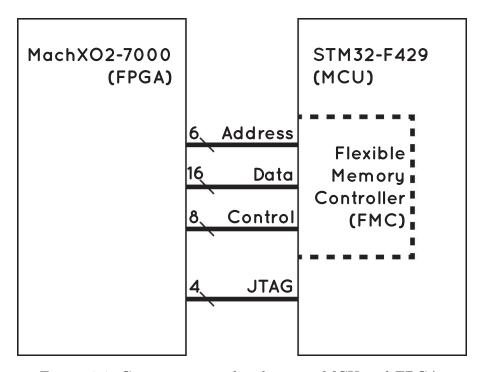

| 6.4  | Communication bus between MCU and FPGA             | 111 |

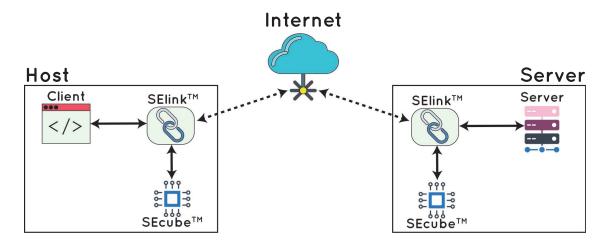

| 6.5  | Secure encryption layer architecture               | 114 |

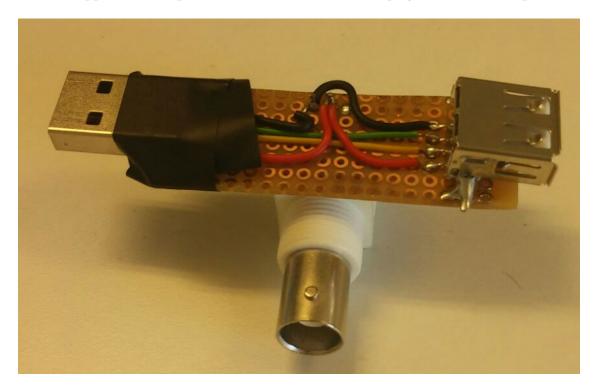

| 6.6  | USB-USB/BNC Connector                              | 117 |

|      |                                                    |     |

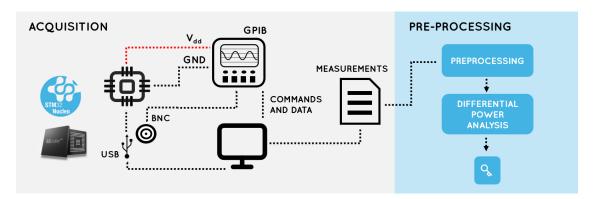

| 6.7 Workflow setup for DPA $\dots \dots \dots$ |

|------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------|

# Chapter 1

## Introduction

This chapter contains the description of the context of the research in the field of the security for Critical Infrastructures.

#### 1.1 Critical Infrastructures

Critical infrastructures describe all physical and cyber systems that are crucial to a nation, i.e., their malfunction, incapacity or destruction would have an important debilitating impact on the physical or economic security, public health or safety of citizens of the nation involved. Critical infrastructures include also the assets, the systems, the facilities, the networks, and other elements on which the society relies upon to maintain national security, economic vitality, and public health and safety. Informally, critical infrastructures can be seen as the power used in homes, the water supply systems, the transportation service that connect cities, the various communication systems people rely on to maintain contact with others. Depending on each country, the Critical Infrastructures or part of them might be owned by the private sector or by the State itself. In the U.S.A., the elements of an infrastructure, either physical or cyber, are typically owned and operated by the private sector, though some belongs to federal, state, or local governments. Not every infrastructure can be considered critical to a nation or region. Thus, to formalize the definition, it is necessary to identify which infrastructure is both critical to maintain continued services or functions and vulnerable to some type of threat or hazard.

Although it is easy to perceive the sense and the importance of a Critical Infrastructure, there is no worldwide definition globally valid. Instead, several definitions do exist.

In the U.S.A., Critical Infrastructures are defined as "systems and assets, whether physical or virtual, so vital to the United States that the incapacity or destruction of such systems and assets would have a debilitating impact on security, national economic security, national public health or safety, or any combination of those matters" [110].

In Europe, instead, there are two definitions:

- 1. Critical Infrastructures are defined as "assets, systems or parts thereof located in Member States, which are essential for the maintenance of vital societal functions, health, safety, security, economic or social well-being of people, and the disruption or destruction of which would have a significant impact in a Member State as a result of the failure to maintain those functions",

- 2. European critical infrastructures (ECI) are defined as "critical infrastructures located in Member States the disruption or destruction of which would have a significant impact on at least two Member States. The significance of the impactshall be assessed in terms of cross-cutting criteria. This includes effects resulting from cross-sector dependencies on other types of infrastructures".

The first definition refers to a Critical infrastructure within a Member State while the second definition refers to a Critical infrastructure considering the European Union as a whole. The above definitions are extracted from [70].

It is possible to see that the actual definition of Critical Infrastructure depends at least on the Region where it resides. Apart from U.S.A. and Europe, each sub-State or region might consider a different definition (e.g., each Member State within European Union has its own definition - which resemble the one of U.S.A.).

There are, however, generic definitions provided by international entities, such as:

- 1. ITU-T: "The key systems, services and functions whose disruption or destruction would have a debilitating impact on public health and safety, commerce, and national security, or any combination of these" [212];

- 2. NATO: "Physical or virtual systems and assets under the jurisdiction of a State that are so vital that their incapacitation or destruction may debilitate a State's security, economy, public health or safety, or the environment" [209];

- 3. IETF: "Those systems that are so vital to a nation that their incapacity or destruction would have a debilitating effect on national security, the economy, or public health and safety" [213].

Another discriminating characteristic is the operational field of the Critical Intrastructures. A sector can be categorized depending on the ownership:

• public ownership (also called State ownership or government ownership): the majority of the companies, the assets and the networks of a Critical Infrastructure is owned by the State;

• private ownership: the majority of the companies, the assets and the networks of a Critical Infrastructure is owned by a private group of individuals.

Not every sector is equally critical for the citizens. The Department of Homeland Security (DHS) of the United States of America considers 16 critical infrastructure sectors whose assets, systems, and networks, whether physical or virtual, are considered so vital to the United States that their incapacitation or destruction would have a debilitating effect on security, national economic security, national public health or safety, or any combination thereof. The sectors in which critical infrastructures are employed, reported for U.S.A. in Homeland Security Presidential Directive 7 [107], superseded by Presidential Policy Directive 21 (PPD-21) [111], can be summarized as follows.

Chemical Sector: The Chemical Sector encomprises several chemical facilities in a global supply chain and is able to convert various raw materials into several diverse products that are essential to modern life and to other supply chains. This sector can be in turn subdivided into five main segments: Basic chemicals, Specialty chemicals, Agricultural chemicals, Pharmaceuticals and Consumer products. Securing the treated chemicals against growing and evolving threats requires vigilance from both the public and private sector, given that the majority of Chemical Sector facilities are privately owned.

Commercial Facilities Sector: The Commercial Facilities Sector includes a diverse range of sites visited by several people or crowds for shopping, business, entertainment. In general the public can move freely within the site area. The majority of these facilities are privately owned and operated with minimal interaction required by the government.

Communications Sector: The Communications Sector underlies the operations of all businesses, organizations, and government. It is critical because it provides an "enabling function" across all critical infrastructure sectors. It provides communication services, which have evolved from voice services into an interconnected industry using terrestrial, satellite, and wireless transmission systems. The private sector, as owners and operators of the majority of communications infrastructure, is the primary entity responsible for protecting sector infrastructure and assets.

Critical Manufacturing Sector: The Critical Manufacturing Sector identifies several industries such as Metals Manufacturing, Machinery Manufacturing, Electrical Equipment, Appliance, and Component Manufacturing and Transportation Equipment Manufacturing. It is classified as critical because the products made by these manufacturing industries are essential to many other critical infrastructure sectors.

Dams Sector: The Dams Sector offers critical water retention and control services as well as hydroelectric power generation, water supply systems, agricultural irrigation, flood control, river navigation and industrial waste management. Also in this case, the services support multiple critical infrastructure sectors and industries. In the United States, the majority of the facilities (about 80%) are regulated by state dams safety offices.

Defense Industrial Base Sector: The Defense Industrial Base Sector is the industrial complex that enables research and development of the military systems, during the phases of design, production, delivery, and maintenance of military weapons systems, subsystems and components required by the military. The sector provides also products and services that are essential to mobilize, deploy, and sustain military operations.

Emergency Services Sector: The Emergency Services Sector (ESS) incorporates physical and cyber resources together with trained and skilled work force and is able to provide a wide range of prevention, preparedness, response, and recovery services during both day-to-day operations and incident response. The facilities are geographically distributed across the territory, at varios levels of government (e.g., federal, state, local, etc.). The ESS also includes private sector resources, such as industrial fire departments, private security organizations, and private emergency medical services providers. The organizations can be composed also by volunteers. Five distinct disciplines compose the ESS: Law Enforcement, Fire and Rescue Services, Emergency Medical Services, Emergency Management, Public Works. Finally, the ESS also provides specialized emergency services through individual personnel and teams (e.g., tactical teams, Search and Rescue Teams, National Guard Civil Support, etc.).

Energy Sector: The Energy Sector is considered as uniquely critical because it provides an "enabling function" across all critical infrastructure sectors. The energy infrastructure is divided into three interrelated segments: electricity, oil, and natural gas. In the U.S.A., the electricity segment contains more than 6,413 power plants. The reliance of virtually all industries on electric power and fuels means that all sectors have some dependence on the Energy Sector.

Financial Services Sector: The Financial Services Sector includes thousands of bank institutions, providers of investment products, insurance companies, other credit and financing organizations. Financial institutions vary widely in size and presence, ranging from some of the world's largest global companies with thousands of employees and many billions of dollars in assets, to

community banks and credit unions with a small number of employees serving individual communities. Thi sector represents a vital component of the nation's critical infrastructures.

Food and Agriculture Sector: The Food and Agriculture Sector is composed of farms, restaurants and other facilities that store, manufacture and process food. It has several critical dependencies in other sectors, but particularly with the Water and Wastewater Systems for clean irrigation and processed water, Transportation Systems for movement of products and livestock, the Energy Sector to power the equipment needed for agriculture production and food processing and the Chemical Sector for fertilizers and pesticides used in the production of crops. This sector is almost entirely under private ownership.

Government Facilities Sector: The Government Facilities Sector includes a wide variety of buildings, physically located on the territory of a nation and overseas. The buildings and the infrastructures are owned by the different levels of government (e.g., federal, state, local, etc.). Some of the facilities might be open to public (such as public offices), while others contain highly sensitive information, materials, processes or equipment (e.g., special-use military installations, embassies, courthouses, etc.). Apart from the physical infrastructures, the sector includes all the cyber elements that contribute to the protection of the sector assets.

Healthcare and Public Health Sector: The Healthcare and Public Health Sector protects all sectors of the economy from hazards such as terrorism, infectious disease outbreaks, and natural disasters. The sector plays a significant role in response and recovery across all other sectors in the event of a natural or manmade disaster. The assets of this sector are both private and public owned depending on the country. In both cases, the sector is managed across all levels of government.

Information Technology Sector: The Information Technology Sector is central to a country security, economy and safety, which are increasify dependent on this sector's functions. These virtual and distributed functions produce and provide hardware, software, and information technology systems and services. Since the Internet represents the backbone of these infrastructures, this sector is tightly related with the Communication Sector. This sector is complex and dynamic, which makes the identification of threats and the assessment of vulnerabilities difficult tasks to achieve.

Nuclear Reactors, Materials, and Waste Sector: The Nuclear Reactors, Materials, and Waste Sector allows power reactors to provide electricity to the inhabitants of a country. The nuclear energy sector is, among the others,

one of the most safety-critical domains and well regulated to avoid harmful consequences to the users and the environment.

**Transportation Systems Sector:** The Transportation Systems wraps all the structures, both physical or virtual, people and means used to to move quickly, safely, and securely people and goods through places. In the U.S.A., seven subsectors belong to this field: Aviation, Highway and Motor Carrier, Maritime Transportation System, Mass Transit and Passenger Rail, Pipeline Systems, Freight Rail and Postal and Shipping.

Water and Wastewater Systems Sector: The Water and Wastewater Systems Sector is central to a nation public health sector, because safe drinking water is a prerequisite for protecting public health and all human activities. The Sector provides for public health and environmental protection. It is considered critical because a drinking water contamination accident or the denial of drinking water services would have a catastrophic impact across a Nation resulting in a large numbers of illnesses or casualties. Indeed, it is vulnerable to a variety of attacks, including contamination with deadly agents, physical attacks, such as the release of toxic chemicals and cyberattacks.

Each of these sectors has unique characteristics and operational modes. Thus, different risk profiles to characterize and mitigate. In the U.S.A., the Sector Specific Agencies (SSAs) were created to leverage expertise and institutional knowledge to enhance the protection and resilience of the national critical infrastructure. Each sector has a designated SSA, which employs its particular expertise to coordinate and collaborate with DHS and other relevant Federal departments and agencies for the protection of the infrastructure.

While the definitions may vary slightly depending the entities involved, Critical Infrastructures are generally considered as the key systems for the society. In all cases, they are composed of both physical (e.g., buildings, facilities, etc.) and virtual elements (e.g., data, networks, etc.). What constitutes the "critical" portion may vary as well. Other countries define different sectors from those reported above according to the available government organizations. In any case, the low-level structures (e.g., hospital, waterduct, etc.) to protect remain the same. Typically, these might include elements of information and communications technologies (ICT), energy, public health, transportation and all the other sectors that a country determines too important in the sense they provide security to the nation inhabitants and support economic stability.

### 1.2 Critical Infrastructures Technologies

According to the Section 1.1, there are several terms and technologies associated to the concept of Critical Infrastructure.

In particular, this thesis focuses on the protection of Critical Information Infrastructures (CII). Independently on the sector, each Critical Infrastructure is composed of physical and virtual parts. Within the virtual parts, there are ICT systems that control, process, transmit or store information in any form, such as data, voice, etc. All this information can be considered vital to the functioning of the critical infrastructure. Also for CIIs, there are several possible definitions. In [70], CII is defined as any "ICT systems that are Critical Infrastructures for themselves or that are essential for the operation of Critical Infrastructures (telecommunications, computers/software, Internet, satellites, etc.)". The CIIs include all the systems and the services of a CI. The CIIs include also the communication (e.g., the telephone network, the Internet, the cabled and wireless networks and terrestrial and satellite communication networks). Moreover, CIIs might contain other infrastructures as well. The CIIs constitute the underlying support platform for all Critical Infrastructures. Also CIIs are at risk of attacks, disaster and, for their nature, technical failures. The high dependence of Critical Infrastructures on CIIs makes the last of vital importance.

Several types of systems, such as embedded, mobile, Cyber-Physical Systems (CPSs) and industrial control systems (ICSs) are used in critical infrastructures. One of the main components in a CII is an ICS, which includes one or more types of control systems that monitor processes and control flows of information. Operators must continuously monitor and control many different sections a Critical Infrastructure to ensure its correct operation. During the last decades this remote command and control has been made feasible due to the development of networking technologies together with ICS. ICSs are command and control networks and systems designed to support industrial processes [116].

A large and estabilished subcategory of ICSs are Supervisory Control and Data Acquisition (SCADA) systems. This technology allows for real-time data collection by means of sensors. Data are then transferred to a control and monitoring part of the system, across local communication links or through the Internet. The control and monitoring system is generally physically distant from the sensors.

Another technology parallel to SCADA, in past few years, are the so called Programmable Logic Controllers (PLCs). Also PLCs are important components belonging to the ICSs category. PLCs support manufacturing automation (e.g., production lines machinery) usually within the industrial field. PLCs are remote or distributed devices automating specific operations. The commands to operate are issued by qualified personnel or can be pre-programmed as set of actions.

Nowadays, both PLC and SCADA are types of technology that can be considered slightly outdated when compared with the Internet-of-Things (IoT) and the so-called Industry 4.0. The IoT is an important concept including a wide range of networked devices and sensors used to create a new set of applications. The IoT is deeply changing several fields by enabling the diffusion of home-automation

concepts, such as smart energy management and "smart-homes", or new medical devices revolutionizing health care sectors [214]. In the context of Critical Infrastructures, the integration of Industrial Internet-of-Things (IIoT) into the technologies employed is aiming to improve efficiency in many crucial areas [155].

The increasing flexibility of these technologies introduce several advantages, but also disadvantages. This exposes the Critical Infrastructures to cyber-risks and to faults, as will be discussed in Sect. 1.4 and in Sect. 1.3. The criticality of the infrastructure results in a demand for building such systems to be resilient and with protection against cyber-threats in mind, even more than conventional ICT systems, considering that a failing Critical Infrastructure could result in a cascading failure of systems, provoking also fatal effects [182].

### 1.3 Security considerations

Security is among the most important aspects of a Critical Infrastructure. Insufficient security measures or even absence of appropriate security mechanisms, may lead to the distruption of a Critical Infrastructure, turning into catastrophic consequences to physical or economic security, public health or safety of citizens of a nation.

The new technological advancements that are integrated into Critical Infrastructures lead to new cyber-security threats. The deriving risks are required to be taken into account beforehand and to be managed with specific security solutions. There are constant growing concerns about how to effectively protect Critical Infrastructures, given their crucial importance for the society and the environment they are embbedded in. Massive technological advances in this field for performance, efficiency and productivity increase the possible risks. Moreover, nowadays, these systems work no longer in isolation. Instead, they are becoming integrated into other systems shaping inter-dependence with other infrastructures [11, 14]. This requires that Critical Infrastructures must be kept secure from any possible source of danger, to avoid the negative consequences. Thus, it is important to address effectively potential security threats to successfully protect these systems [16]. Positive gains from new technologies, such as IIoT, are counterbalanced from improper security design foundations of new devices increasingly integrated in such systems. Many of these IoT devices address security as a remedy. Different vendors of the same device can follow different security recomendation, caused by the lack of an accepted security standards. A single device can represent a security weak point that an attacker can exploit to compromise a larger network. Thus, the lack of security standards among IoT devices is a major concern [155] because of the impact of a possible corruption on a Critical Infrastructure.

The ICSs employed in a Critical Infrastructure have some resemblance to common information systems. However, in the past, ICSs were traditionally isolated

ad-hoc systems with proprietary devices, software and control protocols [201]. This represents one of the major weaknesses in ICSs: communication protocols and their implementations can be one of the main sources of vulnerabilities, according to [38].

PLCs can be considered almost as any common desktop PCs, so they are vulnerable to the same types of attacks as traditional ICT systems [206, 156, 44]. However, in some cases, the security of SCADA systems can be more challenging than the traditional ICT systems. Indeed, early SCADA designs do not provide industrial systems with the protection against cyber attacks, because the majority of Critical Infrastructures were completely isolated. Old facilities employing these kinds of control systems are still in use as of today. However, they can be partially interconnected to other networks flowing to the Internet. This public surface is the source of attack for malicious and remote attackers, i.e., cyber terrorists. Although there exists protection countermeasures, such as firewalls, these might fail and in some cases they might not be even used because they were absent in the design of old control systems [39]. Moreover, common communication protocols are not suitable for all possibile control systems. Indeed, SCADA and other industrial protocols (e.g., Modbus/TCP and DNP3) are critical remote communications of data and control of the devices. However, these protocols were not designed considering the security aspect and, in some cases, they lack basic security primitives, such as authentication to execute commands [39].

Considering the technological advancements and the spreading of new technological devices in CPSs, the number of cyber-attacks directed towards power stations, gas, and nuclear control systems is ever increasing [16]. In the past, the attacks performed were limited to Denial of Service (DoS) or Man-in-the-Middle (MITM) [167]. Instead, recent attacks are increasingly complex. The damage is aggravated in the case the attack targets a CI, given the repercussion to the community served by the system.

On December 23, 2015 a regional electricity distribution company in Ukraine reported service outages to customers. Approximately 225,000 users lost power across various areas. Shortly after the attack, Ukrainian government officially claimed that the outages were caused by a cyber attack. The attackers employed a variety of capabilities, including spear phishing emails and modification of documents by embedding malwares. The attackers were able to harvest credentials and sensitive information to gain access to the ICS network [52].

Another example of dangerous security attacks targeting the Critical Infrastructures is Stuxnet [140]. Stuxnet was reported in Natanz, Iran in June 2010. This complex attack has apparently infected over 60,000 computers, more than half of them in Iran. However, other countries affected included India, Indonesia, China, Azerbaijan, South Korea, Malaysia, the United States, the United Kingdom, Australia, Finland and Germany. Stuxnet is a sophisticated cyber attack designed to penetrate and establish control over remote systems almost autonomously [82]. The attack targeted only ICS controllers from one specific manufacturer (Siemens).

### 1.4 Safety domain

Besides security, also the safety aspects is important in the context of Critical Infrastructures. A safety problem in a subsystem of a Critical infrastructure may result in dangerous issues for a Nation. The CPSs and their components employed in the field of Critical Infrastructures differ from the traditional components for the operational system requirements. Indeed, during the design and the lifecycle of CPS, several aspects need to be considered, such as: components temperature range of operation, power supply, redundancy and fault tolerance properties, testing policies, etc. [238]. Human errors like misconfiguration or poor maintenance of the CPSs also negatively contribute to the system safety.

Safety aspects are tighly related to security. In both domains, adverse events might result in system corruption, which brings negative consequences. This is especially important for a subtype of systems, i.e., safety-critical systems. In these systems a failure could result in loss of lifes, significant property damage, or damage to the environment. There are several well-known examples of such systems, such as medical devices, flight control, nuclear power plants, etc. New technologies are often embedded in control systems, originating new failure modes to be taken into account during the design phase of a system in order to guarantee adequate safety mechanisms able to avoid, manage or mitigate the faults [134]. In this sense, safety and security are therefore two critical aspects for a CPS employed in a Critical Infrastructure, both sharing the same objective: protecting the CPS from risks due to accidental failures (safety) or due to intentional attacks (security).

#### 1.5 Goal of the Thesis

The most ambitious objective of this thesis is to try to guarantee an improved security and resilience for the Critical Infrastructures.

To achieve this goal, I focused on the most important requirements that a Critical Infrastructure must possess, i.e., safety and security. In this context, a Critical Infrastructure is considered as a safety-critical system (whose failure could result in loss of human lifes or serious injuries, significant property damage or damage to the environment) and as a security-critical system (in which sensitive data must be protected against external malicious attackers or accidental disclosure).

Due to recent technological advancements, these systems largely exploit heterogeneous technologies. The heterogeneous components are used as computational devices to improve the performance or to provide greater flexibility of the whole system. In this work, heterogeneous system employed in critical infrastructures are analyzed under both safety and security domains.

More in details, the contributions of this thesis are as follows.

Chapter 2 presents an overview of the heterogeneous technologies employed in

CIs and in CPSs. The focus will be on the components largely used as accelerators or integrated to provide additional functionalities. In particular, are presented technologies exploiting reconfigurability, parallel computation and security-oriented features.

Chapter 3 offers an updated review of the State-of-the-Art, considering several works carried out in the domain of security. It explores the related works on the security of the microarchitecture of processors, which gained interest during recent years due to the new generation of side-channel attacks. In addition, an overview of security issues related to possible attacks on reconfigurable platforms is also provided.

Chapter 4 focuses on the security at the microarchitectural level. This chapter provides an analysis of a vulnerability exploiting a side-channel attack on a consumer microprocessor. It analyzes the interplay between two relevant design aspects of a critical system, i.e., safety and security. Moreover, this chapter presents the work published in: [46, 45].

In Chapter 5 the focus shifts on the protection of the communications against security attacks. In particular, the systems considered are mobile heterogeneous platforms, i.e., portable systems equipped with reconfigurable logic. Moreover, this chapter presents the work published in [47, 48].

Chapter 6 details the development of the open-source library for an heterogeneous device exposing functions typical of hardware security modules. It analyzes the security-oriented features of the firmware of the hardware device and the libraries of the host. An attack is performed against the platform to assess its robustness from the security point of view.

Finally Chapter 7 concludes the dissertation, summarizing the key aspects related for the protection of Critical Infrastructures.

# Chapter 2

# Heterogeneous Computing Architectures

The computing platform employed in Critical Infrastructures and corresponding Cyber-Physical Systems are based on several types of heterogeneous components. In addition to microprocessors, each platform can contain many types of components, such as sensors, peripherals, memories, accelerators, etc. This chapter presents an overview of the computing technologies employed in this kind of systems.

### 2.1 Heterogeneity in CPS

Critical Infrastructures are composed by various types of systems, such as Cyber-Physical Systems. CPSs are made up of physical parts, virtual parts and cyber-physical parts. The cyber components are employed to monitor and control processes in the real world, and receive data sensed from the external environment. This provides a feedback loop to help dynamically adjust the behavior where physical and cyber overlap.

As stated in [151], CPSs can be considered as the product resulting from the integration of heterogeneous systems. They are composed of heterogeneous parts and distributed systems that integrate and interact with other information systems and physical systems. For example, CPSs employed in existing manufacturing practices are blended into the production, logistics and services [144].

Recent technological advancements have led to greater sensor availability and accessibility, high-throughput data processing systems and computer networks. This forced a growing number companies and factories of the industrial environment to shift towards the adoption of different technologies. In consideration of the demands on the needed functionalities, the safety, the security and the cost of a CPS, the choice of implementation involves the use of a variety of different types of technologies in both architecture and functional domains, originating various

solutions. In recent years, the range of available alternatives has transformed to include different types of devices. The heterogeneity is represented in the design of the various features and in its implementation, which includes different components such as Digital Signal Processors (DSPs), microprocessors, memories, components with networking capabilities, sensors, actuators, etc. All these components are often integrated into a single chip. Moreover, in these platforms one or more types of programmable components is integrated on the same system to offer specialized capabilities giving the possibility to handle particular tasks. As an example, a programmable logic device can be combined with a microprocessor, resulting in an heterogeneous system.

The following sections, illustrates the various types of components that can be integrated among the computing components of a CPSs. This integration produces some form of gain for the whole systems. The benefits are usually related to the different system design dimensions, such as:

- Performances: the presence of hardware accelerators ad-hoc engineered for a specific application increases the performances;

- Power Consumption: the employment of low-power devices for specific tasks decreases the overall power consumption;

- Flexibility: the capability to modify or improve the system setup leads to maximize a certain cost dimension (not necessarily fixed);

- Security: certain components can bring improvements and specific functionalities from a security point of view.

However, these dimensions are inter-related. For example, a component that brings a speed-up in performances might increase as well the total power consumption. Thus, it is necessary to carefully design the system resorting to effective design space exploration techniques (e.g., [202]).

#### 2.2 CPU

Traditionally, the cyber part of CPS and the backbone of the CII rely on CPUs as the main components to build systems and networks. CPUs are an established technology that dates back around 1950 and they are at the base of every type of computer. Processors are able to carry out computations and possess general-purpose computational capabilities, i.e., they are not optimized for a specific domain. The trend in processor development has been toward the integration of multiple processing units (or computational cores) in the same CPU. Currently, desktop CPUs are equipped with 8 cores, while CPUs used in server computers have 16 cores available. In this way, CPUs become the optimal choice for handling

concurrent processes. Indeed the instructions to be executed can be run on separate cores of the same CPU at the same time, increasing overall computational performance.

Although software applications support techniques such as multithreading or other parallel computing techniques, the multi-core CPU architecture might not be capable enough to handle large-scale parallel computations. CPUs can exploit multithread processing to achieve faster execution. However, in case of very high number of threads, the performance on CPU do not scale well. Indeed, the context switching operation causes a not negligible overhead resulting in performance penalties. Also the dispatcher, the scheduler and the cache operations do not scale well when the number of threads is high.

#### 2.3 GPU

GPU (Graphics Processing Unit) is a relatively new technology designed for parallelizable problems. It was initially created specifically to handle graphics-intensive applications, however it has become more capable of general computations (i.e., so-called General-purpose computing on Graphics Processing Units - GPGPU). A GPU is a heterogeneous chip multi-processor.

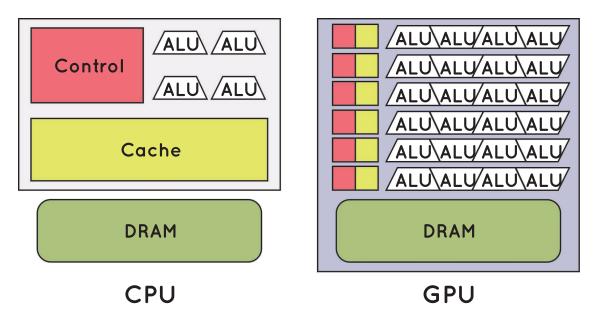

From the architecture point of view, a GPU is composed of hundreds of processing units. The high number of cores allows to handle thousands of threads simultaneously. Conversely, multi-core CPUs are composed by few cores and are able to handle quite few software threads. However, CPUs are designed to minimize latency resorting to cache memories. Instead, GPUs are high-latency but high-throughput processors. This consideration allows for GPUs to have a better transistor/area ratio to be employed for more ALUs and therefore to be able to run many more threads of computation. A simplified comparison between the architecture of CPU and GPU is shown in Fig. 2.1.

Running tens of thousands of computational threads, lead to synchronizations issues. To avoid synchronization stalls and preserve the speedup, each computational thread is required to be independent from each other. GPU is indeed an architecture in which multiple processing units process multiple data streams in parallel, i.e., Single Instruction stream, Multiple Data stream (SIMD) architecture. SIMD represents a category of instructions in which perform the same operation on multiple registers simultaneously. The data parallel problems are those that benefit the most from the SIMD architecture. Exploiting data parallelism allows to distributing the data across different processing units. All of them perform in parallel the same operation, but on a different small piece of data. Several problems belong to this category, such as scientific computing, physics, simulations and especially graphics, image and video processing. CPUs also have SIMD instructions. However, a CPU has a limited number of sequential cores, while a GPU employs thousands

Figure 2.1: Comparison of simplified GPU and CPU architectures.

of parallel cores. A comparison of the main distinguishing features between CPUs and GPUs is reported in Table 2.1.

| Table 2.1: | Comparison | of the i | main features | of GPU | and CPU. |

|------------|------------|----------|---------------|--------|----------|

|            |            |          |               |        |          |

| Feature           | GPU               | CPU                    |

|-------------------|-------------------|------------------------|

|                   | G1 U              |                        |

| Parallelism       | Data              | Task                   |

| Instruction       | Same instruction, | Different instruction, |

| THSTIUCTION       | different data    | different data         |

| Latency           | High              | Low                    |

| Throughput        | Moderate          | High                   |

| Cache size        | Small             | Large                  |

| No. of Cores      | Hundreds          | Tens                   |

| No. of Threads    | Tens of thousand  | Thousand               |

| Thread Management | Implicit          | Explicit               |

| Power Consumption | High              | Low to High            |

GPUs use various optimizations to improve throughput. Usually the GPU chip is embedded into a card, which is attached to the host platform where the CPU resides. Data transfer between the CPU and the GPU is time-consuming. Thus, GPUs often integrate memories, such as on-chip memory and local caches, to reduce bandwidth to external memory. To improve the throughput, GPUs use stream processing where the same series of operations, called *kernels functions*, are executed against each element composing a set of data, that is the *stream*. These kernel

functions are usually pipelined to avoid stalls and performance loss. Moreover, to avoid performance losses deriving by thousand of thread, their management occurs in hardware by the GPU itself.

#### $2.4 \quad CPU + GPU$

An architecture composed by a CPU coupled with a GPU as an external computational device can suffer of different factors that limit the efficacy brought by the heterogeneity of the components.

One of these limitations derive from the communication between the CPU and the GPU. From the architectural point of view, the data to be processed reside in the main memory. In order to exploit the parallel computational capabilities of the GPUs, the data have to be moved from the main memory to the GPU memory. After the kernel functions have been executed on the GPUs, the output of the computation has to be moved back to the main memory. This kind of data transfers requires time, which is related to the available interconnection bandwidth. Altough the transfers unburden the CPU from computation, they constitute a bottleneck. Thus, this slow down partially defeats the benefits of the GPU computational efficiency and greatly reduce the performance of the whole system.

Another issue related to GPUs is the power consumption. Given the high number of computational resources, a GPUs is considerably more power-hungry with respect to a CPU.

For these reasons, technology trends show that CPUs vendors are shifting towards a tighter integration of CPU and GPU on the same die. Already back in 2010, AMD released Fusion APUs, Intel released Sandy Bridge architecture and ARM with MALI represented technological solutions that integrate general purpose CPUs together with GPUs.

These heterogeneous devices merge the functionalities of both architectures, by combining the benefits and limiting the drawbacks of the two separate components. The integration of CPU and GPU into a single unit on the same chip provides several advantages. The components integration allows the use of shared structures which translates in a reduction of costs. Moreover, CPU+GPU architecture reduces the bottleneck of communication because no explicit data transfers are required between the CPU and GPU. Finally, integrating the GPU and CPU has a positive impact in power consumption than having a CPU with a separate and dedicated GPU. Altough currently these integrated devices are quite powerful, a modern dedicated GPU almost always outweighs the CPU+GPU from the computational point of view.

#### 2.5 FPGA

Field-Programmable Gate Array (FPGA) is a type of reconfigurable hardware. It is essentially a semiconductor device as an integrated circuit (IC), but it offers the possibility to be re-programmed, i.e., it can change the functionality of the hardware itself. The programming can be performed once or multiple times. One of the main advantages of FPGAs is that the circuit can be programmed in-the-field, i.e., after the manufacturing process.

This characteristic allows the user to redesign repeatedly an hardware solution to solve specific types of problems more efficiently and to deploy it on the same device without requiring expensive procedures. The design can also be changed after the final product embedding an FPGAs has been shipped to customers out in the field. This reconfigurable feature also distinguishes FPGAs from Application Specific Integrated Circuits (ASICs), which are custom IC designed for specific tasks that cannot be modified after manufacturing. Moreover, the manufacturing time for ASIC might require many months. In addition to their flexibility, limited product development costs and continuously growing computing capabilities make FPGAs a viable alternative to ASICs. Modern FPGAs offer programmable logic blocks, flexible clock generation and interconnection circuitry, memory blocks and embedded hard DSPs. Some specific device families also feature special embedded hard blocks, such as entire microprocessors, memory controllers, RAM blocks transceiver I/O providing high-speed, allowing additional flexibility and incressing computational capabilities. Other families are characterized by low-power consumption. On some types of applications FPGAs can greatly improve the performance over conventional microprocessors. The reconfigurable hardware can be used to implement application specific accelerators on demand. To improve the performances the accelarators can exploits parallelism property, where multiple independent operations are executed at the same time in parallel. This is very crucial in applications that performs operations such as convolution, bit manipulation, multiplication, etc. In these cases, FPGAs can execute these instructions on multiple data at once, with low control overhead and reducing the power consumption, unlike conventional microprocessors. For these reasons, FPGA devices can be exploited in a variety of applications ranging from HPC (High Performance Computing) and enterprise environments to mobile devices. FPGA can be employed in critical application scenarios to increase system dependability and lifetime [66, 50, 64]. They can be employed as a stand-alone platform (i.e., like a normal IC) or can be integrated in heterogeneous computing architectures of reconfigurable systems. FPGAs can be paired with a CPU, composing a system in which hardware acceleration and processing units run in parallel, effectively exploiting all the components and enhancing the throughput of the system. Among the reasons behind FPGAs popularity, there is a simplified design flow with respect to ASIC ICs. As a consequence, there is a reduction of design costs which translates to a shorter Time-To-Market (TTM)

leading to revenues increase.

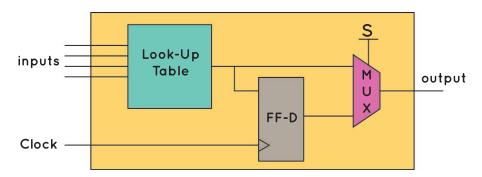

The architecture of an FPGA is made up of a regular structure composed of a two-dimensional array of Configurable Logic Blocks (CLBs). The elements in a logic block can be configured to implement a certain set of functions. Each logic block has a fixed number of inputs and outputs. The CLB can contain Look-Up Tables (LUTs), Flip-Flops (FFs), and multiplexers. However, FPGAs realized from different vendors use different architectures and also different components. The basic structure of a LUT-based logic block<sup>1</sup>, shown in Fig. 2.2, is composed of:

- LUT: logic device which gives in output a specified value as a function of its input;

- Flip-Flop (D-FF): asynchronous set and clear flip-flop, it is used as storage elements for sequential circuits;

- Mux: multiplexer used to bypass the D-FF in the case of pure combinatory cells.

Figure 2.2: LUT-based FPGA Logic Block (S is set from the configuration bit-stream).

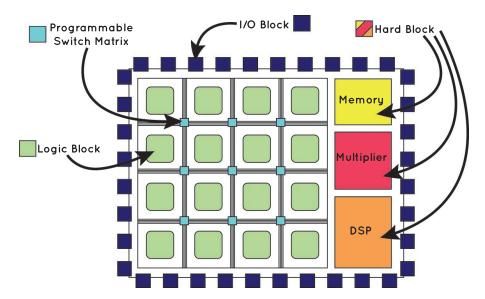

The array of logic blocks is entangled within an interconnection network, i.e., each reconfigurable block is surrounded with communication lines. Also the interconnection network can be configured through Programmable Switch Matrices (PSMs). Modern FPGA devices usually embed additional special purpose blocks, such as I/O Blocks, RAM Blocks, Multipliers, CPUs, and dedicated DSPs. Figure 2.3 shows the high-level internal architecture of a generic FPGA.

The programmable components in an FPGA must first be configured, in order to implement the user-defined design. To configure the FPGA one need to set the logic blocks and program accordingly the interconnections. The *bitstream* describes the developed design in terms of boolean functions and interconnections to be set

<sup>&</sup>lt;sup>1</sup>There could be also Mux- or ALU-based logic blocks

Figure 2.3: FPGA internal architecture.

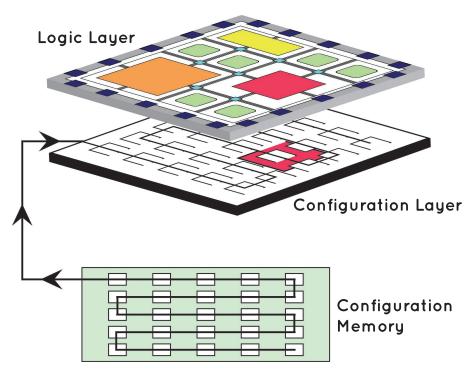

up on the FPGA. The bitstream is the final result of the design phase and it is generated by the tools aiding the design provided by the vendors of the FPGA. The configuration process, described visually in Fig. 2.4 is essentially the deployment of the design. Basically, it involves the transfer of the bitstream into the target device.

The bitstream flows from the configuration memory to the Configuration Layer of the FPGA. This layer determines the kind of computation that shall be performed. This level changes the behavior of the above Logic Layer, which is the one actually performing the computations.

FPGAs can be distinguished based on the technology employed in their configuration memory:

- PROM-based: the memory is writeable only once. It implies that the FPGA cannot be reprogrammed, but it is One-Time-Programmable (OTP);

- (E)EPROM/Flash-based: the memory is non-volatile. However this technology allows limited re-writeability;

- SRAM based: exploit static memory cells. It is a volatile memory, thus FPGA requires to be reconfigure every time after the boot up.

- Hybrid: the memory is composed by EEPROM and SRAM memories. In this case, the power consumption is generally higher and is required a larger area.

Apart from the reconfigurability feature, some families of FPGAs also provide adaptability through a feature called Dynamic Partial Reconfiguration (DPR). DPR

Figure 2.4: FPGA Configuration process.

provides the opportunity to alter at run-time the functionalities impemented in selected parts of the FPGA, while the remaining portion of the system stays fully operational, without interruptions. This feature enhances the native flexibility of FPGAs by enabling the capabilities for time-multiplexing of hardware resources. DPR can be exploited in many application fields where it is necessary to optimize designs [147] and to fulfill severe area constraints [169], to create a system-on-a-chip with a high degree of flexibility [252], to realize adaptive algorithms [177], to be more resilient against errors [170], etc.

### 2.6 Hardware Security Modules

Modern general-purpose computers, such as personal computers, smartphones, tablets, etc. usually run many applications concurrently in a shared environment. The Operating System (OS) does not guarantee that the resources used by various applications are entirely separated, because this would hinder usability. This exposes sensitive data used by applications to great risk.

Altough all those applications that perform critical operations on sensitive data might resort to some encryption mechanism to protect the information, a malicious application might be able to gain access to the cryptographic keys stored in RAM or in permanent storage.

Using dedicated hardware specifically to enhance the security of a system is often advisable, especially in contexts where security is a key aspect. In the real world, this occurs very frequently: for example, banks offer various types of smart cards to their clients for authorization of transactions, and also mobile network providers have been using smart cards to authenticate their subscribers for accessing their services. Smart cards, however, do not cover all the potential scenario for cryptography: very often, a more comprehensive and more flexible solution is needed.

Hardware Security Modules (HSMs) are special-purpose computational devices, tailored to provide a wide range of security features. HSMs can be used together with a general-purpose computer or integrated into a larger system. Simpler hardware tokens, such as smart cards and SIM cards, can be considered as a common example of HSM employed for authentication purposes. However, HSMs are able to perform additional tasks.

These devices can secure various sensitive data processing operations and provide robust mechanisms for authentication and encryption processes. They are usually anti-tamper hardware devices realizing security and cryptographic functions. HSMs can perform several cryptographic algorithms, without exposing the secret keys employed. Most of them can aid the evironment where they are employed to manage multiple keys associated with respective processes. In general, organizations make extensive use of HSMs to enforce their security policies and efficiently maintain their access controls mechanisms. Basically, security modules are used for encryption/decryption of various cipher algorithms and key management operations (e.g., key generation, key storing, key exchange).

Appropriate handling of cryptographic secrets for the practical use of cryptography is crucial. A cryptographic key goes through several life stages such as key generation, secure storage, secure key exchange and distribution, backup and finally destruction. An HSM is specifically used to protect these secret information in every stages of their life cycle. HSMs control logical and physical security of cryptographic keys from attackers and unauthorized activity.

HSMs can also provide improved cryptographic performance. Its integration in a security-critical environment results in a more effective architecture. In this case, the HSM is an advantageous component to provide security functionalities able to reduce security risks and to achieves high performance in cryptographic operations, by offloading expensive computations from the central unit.

The functionalities and capababilites of HSMs are ever changing and increasing. An extended and detailed list of standardized characteristics is provided in the PCI PTS HSM v3 [183]. Considering the importance of HSMs, it is essential that they provide some assurance of their security. FIPS 140-2 [84] is an international security standard used to approve cryptographic modules. In [84], four levels of security (Level 1 to Level 4), are defined: HSMs that are compliant with FIPS 140-2 security Level 3 and above provide the highest level of security.

Several commercial HSMs are available. Portable versions are available too. Common and wide-spread HSMs of this kind are reported below:

- YubiKey<sup>2</sup>: it is a USB device providing secure authentication. It provides one-time-password (OTP) and other authentication features. It is not programmable.

- USB Armory<sup>3</sup>: it is flash drive-sized computer in an USB device. It is open hardware and software. It includes a 800MHz ARM Cortex-A8 CPU, 512MB RAM and microSD card slot for storage. It can run some Linux distributions. It is programmable and customizable.

- SEcube<sup>TM</sup> <sup>4</sup>: it is an hardware chip. It is composed of a microcontroller, an FPGA and a smart card in a single package. It is open source (further details on this platform will be discussed in Chapter 6).

- TREZOR Bitcoin safe<sup>5</sup>: a hardware bitcoin wallet used to protect cryptocurrency funds. However it provides also password manager and secure authentication capabilities. It is not programmable.

- NitroKey<sup>6</sup>: it is a USB device providing secure authentication and encryption services. It is both hardware and software open-source.

Some of these devices are fully programmable, by being open-source. Those with closed-source code can no longer be independently reviewed for security flaws. There are devices also more similar to a normal computer, i.e., running an Operating System. Others are considered as *security tokens*, because they share some similarities with handheld devices. Usually, thay are shaped in a "key" form-factor and communicate with an host device through USB CDC device emulation. Some devices also act as a password manager, supporting key management operations. In general, this kind of devices can be also integrated into larger systems.

<sup>&</sup>lt;sup>2</sup>https://www.yubico.com/

<sup>&</sup>lt;sup>3</sup>https://inversepath.com/usbarmory.html

<sup>4</sup>https://www.secube.eu/

<sup>5</sup>https://trezor.io/

<sup>6</sup>https://www.nitrokey.com/

# Chapter 3

# Security Attacks

This chapter provides an updated review of the state-of-the-art regarding related works on security attacks with a focus on hardware-level attacks. First a global overview of the security landscape is provided, focusing on side-channel attacks. Then, microarchitectural security attacks are analyzed. Finally, a review on security issues regarding reconfigurable logic is described.

# 3.1 Security overview

(Cyber)Security is not a clearly demarcated field of academic study that lends itself readily to scientific investigation. Rather, it combines a multiplicity of disciplines, such as technical as well as, in some cases, behavioural [80].

According to NIST [132], computer security is defined as:

Computer Security Measures and controls that ensure confidentiality, integrity, and availability of information system assets including hardware, software, firmware, and information being processed, stored, and communicated.

Security has its roots in three pillars, i.e., confidentiality, integrity and availability, constituting the so-called **CIA triad**. These three properties establish the *key objectives* of the computer security. The interpretations of these three aspects vary, as do the contexts in which they arise. The interpretation of an aspect in a given environment is dictated by the needs of the individuals, customs, and laws of the particular organization [28].

Confidentiality is the property concerning the obfuscation of sensitive information or resources. This term involves two other concepts: (1) Data confidentiality: it concerns the protection of data that is private or confidential information by making it unavailable or undisclosed to unauthorized parties. (2) Privacy: Ensures that the information related to individuals can be controlled in terms of who can collect them and to whom they can be disclosed to. It is focused on individuals, such as persons, organizations or any other entity, especially on their sensitive data.

The need to keep information confidential stems from the diffused use of computers and computational devices in organizations handling classified information, including governments and industries. As an example, let us consider institutions such as military and civilian agencies. These institutions very often limit the access to information to those who need that information. Confidentiality enforces the so-called "need to know" principle which is a general principle, developed in the context of information security and in the management of security systems, according to which only the subjects who must perform information processing activities are authorized to process only the data essential to the fulfilment of the task assigned to them and the data must not be shared, communicated or sent to third parties who do not need it. This principle also applies to industrial companies, which desire to maintain their design and projects confidential and secure them from competitors that might try to steal and copy the property, allowing financial losses to arise. Further examples are given by every type of institutions that keep employee and personnel records secret.

Confidentiality is ensured through mechanisms of access control that regulate data access. Access control mechanisms allow authorized parties to access the protected data and deny access to unauthorized parties, thus preventing confidentiality breaches. One access control mechanism for preserving confidentiality is cryptography. Simplifying, cryptography transforms human-readable data through a process (i.e., encryption) so that the data becomes unrecognizable and incomprehensible. Encrypted data can only be accessed by individuals who possess the key to decrypt the data. However, the cryptographic key itself becomes another piece of information to be protected and to be kept secret.

Confidentiality also applies to the *existence of data*. The existence of data, in some cases, reveals more information than the data itself. Access control mechanisms can be used to disguises the existence of data, because the presence of data itself might reveal information that should be protected.

A further important component of confidentiality is resources hiding. Sometimes, companies try to mask their network configuration, as well as the technologies they use. Organizations may not allow everyone to know about the particular equipment they employ. Access control mechanisms provide these capabilities as well.

Integrity refers to the reliability of data or resources, and it is generally meant to prevent illegal, unwanted or unauthorized changes. This term covers two related concepts: (1) Data integrity: Ensures that information stored or exchanged is only changed in a defined and authorized way; (2) System integrity: Ensures that a system performs its intended function without any impairments and without unwanted or unauthorized modifications of the system behavior.