# An Efficient Strategy for the Development of Software Test Libraries for an Automotive Microcontroller Family

D. Piumatti<sup>1</sup>, *Member*, *IEEE*, E. Sanchez<sup>1</sup>, *Senior Member*, *IEEE*, P. Bernardi<sup>1</sup>, *Member*, *IEEE*, R. Martorana<sup>2</sup>, M.A. Pernice<sup>2</sup>

Abstract — With the introduction of the ISO26262 standard in the automotive field, numerous solutions for the in-field and online testing have been proposed. Among the several test solutions available, the Built-In Self-Test (BIST) approach is the most used for manufacturing test of chips, while the Software-Based Self-Test (SBST) approach is the most commonly used for on-line test the modern processors. This paper faces a very concrete problem concerning SBST development. In order to address more market demands, semiconductor industries are usually developing families of microcontroller, usually based on similar processors, instead of a single instance. This variety of architectures makes the development of SBST programs a repetitive, time and human consuming activity.

The main aim of this work is to propose a methodology according with the SBST paradigm that permits to develop test programs able to achieve high coverage on different microcontrollers of the same family. The developed test programs are not showing any significant drop in coverage performance when they are used on different processors included in product of the same microcontroller family. The approach is based on the analysis of the processor hierarchy to identify the common units between the processors of the same family, first of all looking at those that show design differences. The module classification permits than to plan the most effective SBST development.

A segment of industrial microcontrollers developed by STMicroelectronics for the automotive field, adapting many processors belonging to the same processor family, is used as a case of study. The experimental results demonstrate the effectiveness of the proposed approach, i.e., to reach the same fault coverage figures over many processors while dramatically reducing the development time.

Index Terms — Automotive microcontroller ISO26262 test, In-Field Self-Test, On-Line Self-Test, Reliability and Testing

Corresponding author: Davide Piumatti davide.piumatti@polito.it

#### I. INTRODUCTION

Today vehicles are equipped with very complex functionalities that use of many electronic components. In fact, in a modern vehicle, it is possible to find many different Electronic Control Units (ECUs) placed inside of the vehicle; Actually, in a vehicle's engine, there may exist more than 7.000 semiconductor components able to perform very different tasks. Typical tasks are devoted, for example, to manage safety systems such as the ABS or the ESP, to perform powertrain functionalities, or to improve the end-user experience by means of new applications circumscribed as infotainment [1], [2], [3].

The automotive sector is one of the most dynamic ones, since potential users are always asking for additional but safe and secure features. Actually, the manufacturers of electronic devices for automotive, and in particular the microcontrollers manufacturers, try to launch every few months a new product; all these new products belong to the same family of processors and share some features present in each device. The differences between the family products are mainly focused on the memory sizes, the type and quantity of peripherals available, and the safety mechanisms included in the device. Considering the processors that belong to a given family, in most cases only small variations are applied, e.g., including small modifications to the Instruction Set Architecture (ISA). In this way, the manufacturers exploit the selected architecture and guarantee an appropriate level of compatibility among the products on the same family.

Guaranteeing the correct behavior of the electronic devices composing a vehicle is very complex, and its expected behavior has to be assured in very harsh environments. In fact, vehicles are prone to vibration, noise, extreme temperatures and electromagnetic fields that may affect and degrade the electronic components. The effects of possible faults may lead to significant damages, either from an economic point of view or in terms of consequences for the human users that may produce even human casualties. In safety-critical applications, such as the automotive ones, a set of very good practices have been introduced, trying to guarantee the correct functioning of the electronic devices during their normal life operation. During the last years, the trend is to resort to self-test procedures that operate in-field in autonomous mode. These in-field procedures

<sup>&</sup>lt;sup>1</sup> Dipartimento di Automatica e Informatica (DAUIN), Politecnico di Torino, Torino, Italy {davide.piumatti; ernesto.sanchez; paolo.bernirdi}@polito.it

<sup>&</sup>lt;sup>2</sup> STMicroelectronics, Catania, Italy {rosario.martorana; mose.pernice}@st.com

have been ruled by the introduction of some safety standards, such as the *ISO* 26262 in the automotive field, or ARP-4761 for avionics.

In order to guarantee the system reliability, hardware and software-based approaches have been proposed, e.g., [4] and [5]. In the first case, even though the introduced hardware reaches to assure very high reliability levels, the area overhead and the difficulties to use them without destroying the system status create some difficulties in its adoption. On the other hand, software-based approaches usually reach lower reliability levels than the obtained by the hardware-based counterparts but require very few overheads in terms of hardware and memory. However, the most commonly used implementation methodologies to develop software-based solutions are mostly based on manual processes that involve very long development times making these approaches less attractive for the car manufacturers.

In a family of microcontrollers, the implementation of safety mechanisms based on hardware or software solutions must be implemented and inherited starting from the initial devices to the following ones. These mechanisms should guarantee very good reliability levels for all the components of the whole family. Inheriting hardware-based solutions is usually handled by the use of commercial tools that implement these mechanisms almost automatically. On the other side, software-based solutions are rarely inheriting due to the implementation methodologies that in most cases tackle only one processor at a time.

In this paper, we present a development methodology for software-based solutions oriented to provide a quick and cheap strategy that considers a whole family of microcontrollers at a time, instead of addressing each single processor cores separately. We propose to exploit the similarities among the different components of a family of microcontrollers during the development process. In particular, we define a *portable classification* topology that permits us to take advantage of the processor similarities during the early development stages of the SBST programs. Additionally, we define how to develop a set of test programs for the most common modules available in a family of microcontrollers in order to reduce the development time of the software test libraries.

Through a very consistent set of experiments, run in a family automotive oriented devices manufactured STMicroelectronics, we experimentally observed that the generation of a software-based solution for a family may require the same development times as of the individual approach for each single products of the portfolio. The family oriented approach is also guaranteeing very high fault coverage (FC) levels for all components of the considered family. In this direction, to avoid the loss of effectiveness of the test programs from one processor to another, a threshold is defined. The identification of the minimum FC threshold is discussed in this paper. Additionally, the proposed approach describes how to maximize the processor FC by reusing test programs previously developed.

The paper is organized as follows: Section II proposes a broad background concerning the on-line self-test, with a particular emphasis on the Software-Based Self-Test (SBST) approach.

The development steps of a new processor family are also discussed in Section II. In Section III the proposed approach is discussed and analyzed; it allows the development of software test programs that are easily portable between the different processors of the same family under examination. Section IV reports the case study, i.e. the SPC58 processor family used in this work is analyzed. Section V reports the experimental results that support the proposed approach. Some industrial problems related to the development of the test programs are reported in Section VI. Finally, Section VII close this work with some conclusions.

#### II. BACKGROUND

This section proposes an overview of the safety standards used in different fields, with a particular emphasis on the automotive field. The motivations related to the in-field self-test are introduced and the two main categories of safety mechanisms used to perform in-field testing are reported. Later, an overview of the software-based test approach is provided. The structure of a generic Software Test Library (STL) used for testing a processor is discussed and analyzed. Finally, a description of the design process of a new industrial processor is shown.

## A. Safety standards

The IEC 61508 [6] is an international standard introduced at the end of the 1990s. The International Electrotechnical Commission has proposed this standard with the goal of introducing some methods to apply, design, deploy and maintain automatic protection systems called safety-related systems. As the standard reported, it defines the functional safety as: "part of the overall safety relating to the EUC (Equipment Under Control) and the EUC control system which depends on the correct functioning Electrical/Electronic/Programmable Electronic Safety-related systems (E/E/PES), and other technology safety-related systems and external risk reduction facilities." [6]

The fundamental concept described in the standard is that any critical-system must work correctly or fail in a predictable (safe) way. As a consequence of the *IEC 61508*, many specific standards are introduced for different application fields. In the medical field, the *IEC 62304* standard has been introduced, the *EN 5012x* has been introduced in the railway field. The *DO-178* standard is used in the aviation field, while in the automotive industry the *ISO 26262* standard has been introduced.

The ISO 26262 [7] is an international standard introduced in 2011. The target of this standard is to define a functional safety metric for all Electrical/Electronic Systems used in automotive applications. The ISO 26262, in opposition to previous standards, introduced the concept of controllability [4]. The controllability is the ability to avoid a hazardous event by an action taken by a driver or by a system. The standard introduces four Automotive Safety Integration Level (ASIL) classes depending on severity, probably of exposure and controllability of dangerous events. The standard faces the steps to analyze the hardware failures of the electrical and electronic parts of cars. In addition, the ISO 26262 classifies the faults in some categories [4]:

- Perceived: This fault is perceived by the driver, but the fault is not detected by a safety mechanism in a prescribed time.

- Detected: This fault is detected by safety mechanisms in a prescribed time.

- Latent: This fault is neither detected by a safety mechanism and it is not perceived by the driver.

- Safe fault: Fault whose occurrence will not significantly increase the probability of violation of a safety goal.

- Residual fault: The effect of this fault does not affect the system.

# B. Safety mechanisms

Different solutions facing the problem of the in-field self-test are proposed to be compliant with the introduced safety standards. Roughly speaking, the proposed solutions can be categorized into two main categories that separate pure hardware and software-based solutions; however, in the last years, hybrid proposals are also finding some space as safety mechanisms. Typically, the safety mechanisms are targeted to detect the permanent stuck-at faults, but it is possible to extend the test strategies to other fault models as the delay faults, the transient faults or the bridge faults. In every case, the FC figure can be evaluated with a fault-simulator software tool [8] [9]. In the automotive field, the FC is also called Diagnostic Coverage (DC) [7].

## 1) Hardware-based approaches

Belonging to hardware-based approaches [10], the Logic-BIST (L-BIST) is one of the most popular approaches. In this approach, a state machine applies some non-functional test patterns to the Unit Under Test (UUT). The BIST system collecting and checking the results at the end of the process. When applied to a processor core, this test strategy can be used only during the power-on because it requires the system to be in a specific test-mode. On the other side, some safety mechanisms can be based on duplication and triplication of the UUT. In particular, the Triple Modular Redundancy (TMR) [11] technique uses three implementations of the same UUT and the output signals of these modules vote adopting a voting mechanism. The most basic voting algorithm is the majority voter, where the voter selects the most common output. The Lockstep configuration is a redundant system based on UUT duplication. Regarding the memory testing, two approaches are most used today: the Memory-BIST (M-BIST), and the Error Correction Code (ECC) approach. The first one uses a March test sequence to test the RAM or Flash memory [12]. The M-BIST approaches write and read sequence of test patterns in the memory cells oriented to detect different types of faults; these approaches modify the content of the memory. For this reason, the M-BIST can be used only at the power-on of the processor when the memory contains useless values. On the other hand, the ECC one uses a redundant code to perform an on-line check [13]. All hardware-based approaches require the instantiation of additional hardware to perform the testing processes. The amount of added hardware to perform the test can be a significant part of the whole device area.

## 2) Software-based approach

In order to use this approach, a test library able to detect the possible permanent hardware faults must be developed. The Software-Test Library (STL) is a collection of software programs able to excite the possible faults inside of the processor and the peripherals surrounding it. This strategy, initially proposed in [14], has been studied by different research groups as described in [15] [16] [17], and later extended targeting the automotive field [5]. Currently, the STL approaches are used by different companies to mainly test their own processors, for example: STMicroelectronics [18], Infineon [19], Cypress [20], Renesas [21], Microchip [22] and ARM [23]. The STL technique is based on the so-called Software-Based Self-Test (SBST) paradigms. The SBST consists of letting the CPU running a sequence of instructions to excite and propagate the faults that may affect the digital circuit [24]. The processor is periodically forced to execute the self-test code [5] able to detect the possible occurrence of permanent faults in the processor core itself, or in the peripherals connected to it. Such procedures are developed to activate possible faults and report their presence.

Usually, the test programs return a value called signature. In the presence of a fault, the signature value produced by the test is different from the expected one. The signature value is produced by accumulating the results of the assembly instructions that perform the test. It is a good practice to develop a test program for specifically testing one unit of the processor. As described in [25], a test program can be developed mainly resorting to three different approaches: ATPG-based approach, deterministic approach, and evolutionary-based approach. The first one uses the test patterns generated by an ATPG tool [26] to test a functional unit of the processor. The ATPG-based approach is very powerful to test the arithmetic and logic units as the adder, the multiplier, and the divider units. The test program executes an assembly instruction able to apply the ATPG functional test pattern; for example, using the test patterns as the operands of an add instruction to test the adder unit. The results of the test instruction are used to produce the signature of the test.

In the deterministic approach, the test program is developed studying the Unit Under Test (UUT). A deep knowledge of the UUT is necessary to develop a good test program and for implementing a specific test algorithm. Some examples of deterministic test algorithms are available in the literature, for example, in [27] for the Register File Unit and in [28] for the BTB unit. A testing algorithm to test the decoder unit is proposed in [29], while the test for the FPU is proposed in [30]. The last possible approach to develop a test program is the evolutionary-based approach. A first pseudo-random set of test programs is written, then, resorting to some genetic operators. The test programs are modified generating new and hopefully better test programs. The goodness of every individual or test program is evaluated against a given metric, e.g., the fault coverage reached by the program in the UUT. Then, the best individuals are selected for generating the next set of individuals. The evolutionary algorithm is executed until a stable condition is reached. As an example, an evolutionary optimizer called µGP [31] has been used to evolve the test programs.

The test programs that belong to a STL can be classified according to their ability to be integrated with the mission software application. The STL is usually composed of *intrusive* and non-intrusive test programs [32]. The former ones influence the behavior of the operating system or the mission software application because the intrusive test needs to take the total control of the processor to perform the test; e.g., test programs triggering exceptions, or using very special addresses in the RAM memory, or manipulating special registers. The intrusive tests need to be executed at the power-on or power-off, for example before launching the Operating System. On the other hand, the *non-intrusive* tests can be executed by the Operating System as a simple application because they do not require special conditions. The non-intrusive tests are usually performed with the processor configured in user-mode and they are periodically executed at run-time scheduled by the Operating System.

A last test program category, which is also usually included in a STL is the so-called Instructions Self-Test (IST). The goal of the IST test programs is to execute at least once all the assembly instructions of the Instruction Set Architecture (ISA) supported by the processor.

Compared to the hardware-based solutions, the STL presents many advantages, such as the ability to perform the test at the boot time as well as at run-time; the test programs are executed at-speed (i.e., at the circuit nominal frequency); and the STL does not require any hardware modification. On the other hand, the STL programs require to be allocated in the flash memory, and according to the execution schedule, these programs require be executed concurrently with the mission application. In the automotive sector, for example, the memory occupation as well as the execution time must comply with the system constraints in order to do not impair the execution of the actual application. In an automotive solution, the full flash memory occupation counts with about 200KB, while a single non-intrusive test program must spend at most 255 clock cycles [32], at every run. The STL-based approaches still present a serious limitation due to the difficulty of both writing efficient and effective test programs and devising suitable methodologies for test application.

In order to allow the STL test programs to be compliant with the mission software environment, a viable solution is the adoption of the Embedded-Application Binary Interface (EABI) [33]. The EABI specifies standard conventions for the data types, the registers usage, the stack frame organization, and the function parameter passing of a software program. Thus, every test program includes an EABI prologue and epilogue, able to save and restore the mission status.

In order to assess the test program suitability, the test programs are evaluated through a fault-simulation process as described in [34] and [35]. Each test program is evaluated targeting only the faults in the UUT as described in [5]. When the Fault Coverage of the single units reach a good level, a synchronization process [5] is performed, i.e., all test programs are fault-simulated targeting the whole processor obtaining a general Fault Coverage of the processor. Following this process, the fault-simulation time is reduced as shown in [5], and it is possible to take advantage of the cascade phenomenon [5][36]. The cascade phenomenon consists of exploiting the beneficial

effects on the fault coverage introduced by a test program, devised for a specific unit, on the other units of the processor.

## 3) Hybrid approaches

Among the test strategies proposed by the scientific and industrial community, a new third category is currently under development: the Hybrid approach, see [37], [38], [39], [40], [41], [42]. The hybrid approach merges the software approach with the hardware one. The hybrid approach tries to take advantage of the positive features of both techniques. It is able to reach a high fault coverage, as the hardware-based approach, with the ability to work on-line, as a software-based approach. The idea is, for example, to use a hardware test architecture driven by a software test program for applying some test patterns. The architecture works in a similar manner as the L-BIST approach, but it is not limited to work at power-on. The hybrid approach allows to perform periodical on-line self-tests. In order to integrate these techniques in new devices, it is required to modify the hardware device; for this reason, hybrid approaches are not targeted in this paper.

## C. STL architecture

The goal of this subsection is to show how an STL works, considering the final user point of view. Usually, two different sets of Application Programming Interfaces (APIs) are available, one for the tests performed at boot-time and one for the run-time test programs.

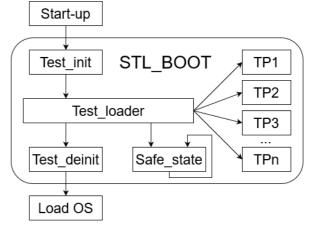

At the boot-time, a single API calls a software task able to execute the test programs, as shown in Figure 1. Typically, the STL BOOT is performed at the start-up before loading the Operating System. A *Test init* function prepares the processor to perform all the test programs. In particular, the Test init configures the interrupt controller to manage the interrupt requests generated by the test programs, initializes the RAM memory, disables all peripherals and configures a watchdog timer to avoid the program to be stuck in an infinite loop. The Test loader function launches each test program and checks the signature value against the expected one. In case of a test program fails the Safe state function is performed. The Safe state function freezes the ECU in a safe state. If all the test programs return the expected signature, a Test deinit function restores the processor state. Finally, the Operating System is launched.

Figure 1: STL architecture for the boot-time tests

The non-intrusive test programs are performed at run-time, in this case, APIs complaints with the AUTOSAR standard is required [43]. Three APIs are usually implemented: Prepare\_STL, Call\_test\_routine and Return\_last\_test\_state. The Prepare\_STL function initializes the variables used by the loader of the test programs. The Call\_test\_routine executes the test whose ID is passed as a parameter. While the Return\_last\_test\_state indicates if the last test program executed has detected a fault or not. In the presence of a fault, the system must be placed in a safe state.

#### D. Design process and industrial production timeline

The development of a processor is a long and complex process that requires many steps to reach the final product [44]. Analysing the process at a high level, the features of the new device are initially defined and described. This higher level is known as the behavioural level. In the case of the processors, the general architecture and the Instruction Set Architecture (ISA) is established. In the next step, a formal description of the processor using a high-level language is performed. In this step, called Register Transfer Level (RTL), every single unit of the processor is described and its behaviour verified. The RTL is independent of the technology that will be used to implement the processor, but the RTL description is sufficiently detailed to allow the synthesis of the digital circuits. Furthermore, the RTL description allows us to perform formal verification of the processor using a logic simulator [45]. The next step is automatically generated from the RTL level through a synthesis process, this new level is called Gate-Level. At Gate-Level the circuit is described at the level of logical gates considering a specific technological library. In the last step called Switch-Level, the processor is described at the transistor level. The Switch-Level is used to generate the chip layout. The layout is the description of the geometric information necessary to activate the final production process. An integrated circuit consists of a succession of silicon, oxide and aluminium layers that must be arranged in a certain way to create the transistors and the connections between them. Each of these layers corresponds to one or more production processes that are regulated by one or more masks. The complete set of the masks derived from the layout defines all the operations to be performed in production to create the final die. The die is the thin plate of semiconductor material on which the electronic circuit of the integrated circuit has been made. Finally, the die is closed in the plastic package, and the wires bonding is realized to connect the *die* with the external package contacts. Obtained the first sample of the new processor, a verification phase is performed. The aim of the verification phase is to check the device to an electrical point of view, e.g. the electrical power consumption of the processor.

Typically, the processor manufacturer releases a Microcontroller Abstraction Layer (MCAL) [46] package containing the drivers and APIs for using the processor itself. The MCAL is a software module that directly accesses the onchip MCU peripheral units mapped in memory. The MCAL contain, for example, a set of drivers for the peripherals as the GPT (General Purpose Timer), the WDG (Watchdog), the MCU (Micro Controller Unit) as the MMU (Memory Management Unit) or the MPU (Memory Protection Unit), and for all communication devices as the CAN bus, the LIN bus, the

Flex Ray bus, the Ethernet and the UART interface. In the automotive field, the MCAL structure is defined by the AUTOSAR standards [46]. The MCAL package is developed and tested by the manufacturer of the processor.

The whole development process of a processor used in an embedded system may take about one year from the initial behaviour description to the first physical sample. The verification phase may require an additional 4 months for checking the physical device, and about 7 months to produce and check the MCAL library [47][48].

The technical and commercial planning are very important aspects, among the aspects that concern the development of a new processor. In particular, the roadmap of the new processors is defined in order to establish the development plan and the production plan. The aim of these plans is to establish the characteristics of each processor. In particular, to establish the characteristics that change from processor to processor over time; for example, the size of the memories or the number and type of peripherals present in each processor [49]. In addition, the financial investment plan is established for the future years. The economic plan is associated with each development step and with each production activity [50]. In general, from a processor to another processor of the same family two develop roads are available. In the first one, the "child" processor is built by reducing the features of the "father" processor. In the second one, some features of the "father" processor are redesigned and improved. With these two approaches, it is possible to produce a wide range of processors belonging to the same family. However, the basic structure of the processors remains unchanged for all processors of the same family. The family tree of the processors can be produced considering the two possible develop roads.

#### III. PROPOSED APPROACH

This section discusses the proposed approach, the aim is to reduce STL development time for each processor of the same family; Secondly, the proposed approach allows to identify a structure for the development of test programs. The test programs developed with the proposed approach are efficient on different processors, i.e., the ability of the test programs to detect faults does not degrade from one processor to another processor of the same family.

The proposed approach is supported by three different items of the new processors family: 1) the family tree of the new processors; 2) the development plan of the processors; 3) the features of each processor of the new family. All these three items, discussed in Section II, must be available before starting with the development planning of the portable tests.

Briefly, the proposed approach is based on the classification of the processor's units. The proposed unit classification, called *portable classification*, is used to define how to develop the test programs for each unit.

In the following, the first subsection introduces the idea of portable test programs; the second subsection reports the proposed portable classification, and finally, the last subsection discusses the proposed porting approach.

## A. Definition of portable test program

A portable test program mainly operates in a functional way, i.e., it works independently of the hardware implementation of the unit that it tests. This consideration is useful in order to abstract the test program from the hardware, and in particular from the specific UUT.

For example, the *ATPG-based* approach should be avoided when aiming to produce portable test programs. In fact, the *ATPG-based* approach tries to find a set of optimal test patterns for a given hardware implementation of the UUT. These test patterns are generated by special ATPG tools that operate at the gate-level. Clearly, a new synthesis of the circuit using different technological library or different synthesis parameters produces a different gate-level implementation, that requires a new set of test patterns. Thus, the ATPG test patterns generated for the UUT of a processor are not suitable for testing the same unit in a new processor, since a consistent loss of FC is predictable.

In a similar way, the evolutionary-based approach should be also avoided aiming to developed portable test programs. Actually, in the evolutionary approach, the test program evolves according to the specific gate-level network in order to obtain high FC values. The test program developed is therefore specific for a single implementation of the UUT, and also in this case, there is a considerable decrease of the FC by reusing the test programs developed with the evolutionary-based approaches.

In general, all the test programs developed using approaches based on a direct exploitation of the gate-level information are not suitable for the development of portable test programs. This is due to the considerations of the synthesis phase above described.

As a matter of facts, in order to develop portable test programs, the *deterministic* approach is therefore preferred because it is based on the functional study of the UUT at RTL. Obviously, the *deterministic* approach lengthens the development time of the test programs because a study of the UUT is required, as described in subsection B.2 of the Background. However, this development phase is performed only one time on a processor of the new family. In the long term, there is a considerable saving of time and resources necessary to develop the test programs.

## B. The proposed portable classification

This classification analyses the units of a processor with respect to similar versions present in other processors of the same family. Four possible categories are analyzed and discussed:

The EXCLUSIVE unit: The exclusive unit is present only in the processor under examination, and it is not present in other processors of the same family. In general, the exclusive units are included in a processor to optimized some specific operations requested by the customer.

The *SHARED* unit: In contrast to the previous category, the *shared* units are present unchanged in many processors of the same family. In a more general sense, it is possible to consider these units as belonging to the processor family.

The *REDUCED* unit: These units are included in many processors of the same family, but from processor to processor these units miss some functionalities. For example, the multiplier unit able to perform operations on 64-bit operands

has been simplified, and in its next version the multiplier performs operations only on 32-bit operands.

The *INCREASED* unit: Similar to the *reduced* unit, the *increased* units are present in many processors of the family. Furthermore, the *increased* units improve their functionalities in the next version. A possible example is the extension of the instruction set of the processor. With the addition of some instructions, new features must be implemented in the processor units

The *REDUCED* and the *INCREASED* categories can be considered as a sub-category of the *SHARED* one.

## C. Porting methodology

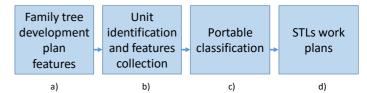

In this section, the proposed approach to develop a portable STL is shown and discussed. The steps of the proposed approach are shown in Figure 2.

Figure 2: The classification of the units of the processor family

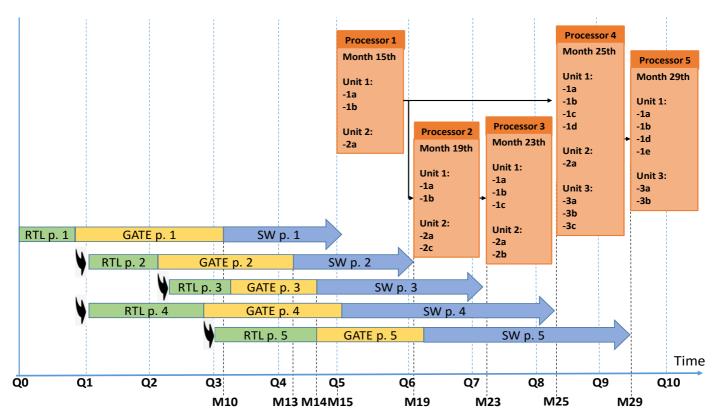

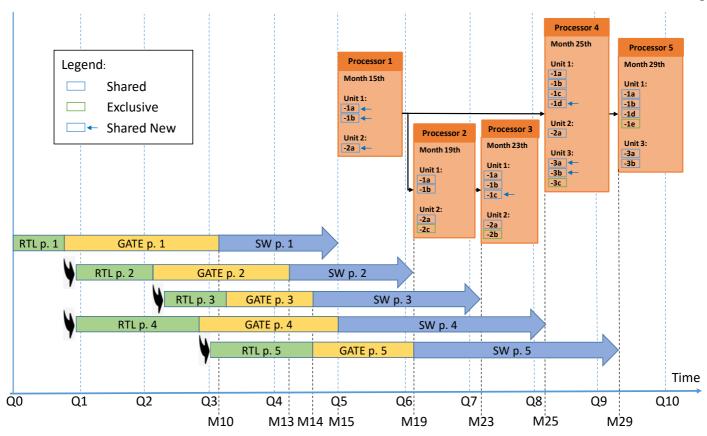

- Step a: The family tree of the processors family, the release times to the market of every device, and the features of each processor are gathered. At this point, it is important to determine when every phase of the development plan for every processor core in the family will take place. In particular, it must be defined the delivery times for the RTL, GATE, and Software MCAL. Figure 3 shows an example of a family tree composed of 5 different processors. From the figure, it is possible to see that the processor 1 must be delivered at M15, at the end of the fifth quarter (Q5), the RTL of the processor 1 is to be released during Q0 and the gate level near the end of Q3. It is possible to notice also that there is a dependence between the RTL of the processor 1 and the ones of processors 2 and 4.

- Step b: The units of the different processors of the family are identified and the features of every unit extracted. It is important to identify the features in every processor and their evolution on the other cores in the whole family. Additionally, resorting to [5], a first analysis of the processor units is performed and the different units are classified according to their functionality. Five categories are identified: the first one includes all the functional units. These units execute specific operations in the processor such as the addition, shift, division, and the logic operations, these units are labelled as FUNCT units. The second category is named SPECIAL. The units belonging to this category are associated with the management of the instruction flow or the memories; the exception unit, the memory management unit and the branch predictor belong to the SPECIAL category. The third category only includes the processor REGISTER FILE. All the General-Purpose Registers and the Special-Purpose Registers belong to the REGISTER FILE category. The program counter unit and the effective address calculation unit belong to the ADDRESS category. The last category is the one that

Figure 3: Family tree example

includes *CONTROL* units. All the units able to management the pipelines belong to the *CONTROL* category.

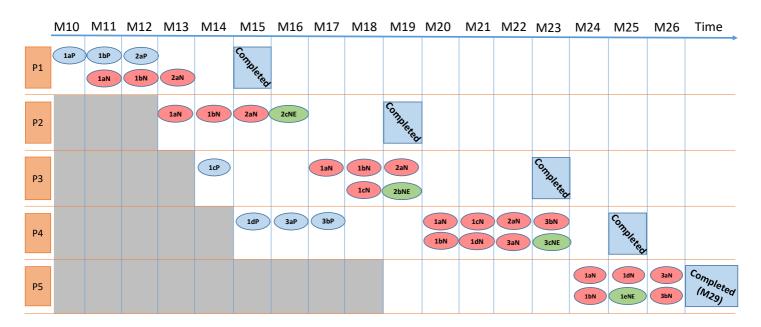

According to [5] the test program development process must follow an almost sequential order, starting with the FUNCT units, followed by the SPECIAL, REGISTER FILE, ADDRESS and CONTROL ones. In some intermediate points, a general synchronization is performed in order to take advantage of the beneficial results of the developed programs in the whole processor fault coverage. The development strategy proposed in [5] does not consider the portability of the programs, actually, it uses extensively non-portable solutions. Figure 4 shows a possible development process based on this technique while considering the delivery times for the family processors in the previous figure.

Figure 4: Development process in [5]

In this case, it is possible that the development process takes so long time and the expected delivery time of the processor as well as the STLs may not coincide.

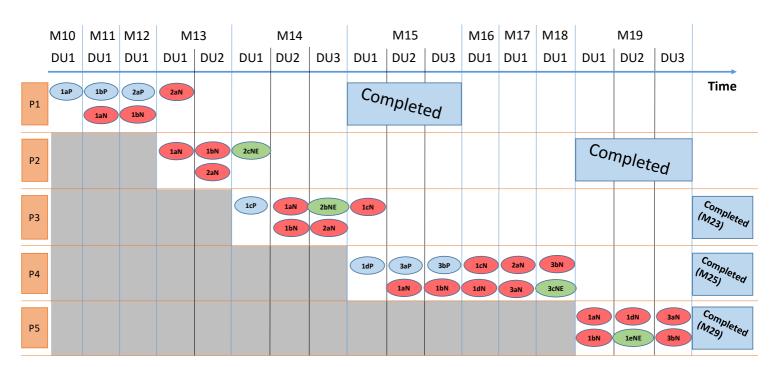

- Step c: The processor units are classified according to the portable classification (see Section III.A). For the units classified as *shared*, *reduced* or *increased* the test programs must include portable test programs for every feature of the unit. On the other side, units classified as exclusive require a traditional non-portable test program. In general, portable test programs are structured in a modular way considering the unit features, i.e., an independent sub-test is developed for each feature. Once the portable sub-tests have been developed, an additional non-portable sub-test is usually required. This new non-portable test guarantees the targeted FC, i.e., the aim of the additional sub-test is to cover the gap of remaining FC, with respect to the expected FC value. In the example reported in Figure 5, the processors units are graphically classified as shared (blue borders) and exclusive (green borders). Additionally, the figure also highlights when a new feature appears in the development process for the shared units; this is named shared new, and is indicated by a blue arrow.

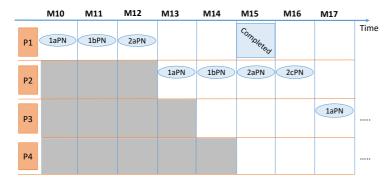

- Step d: The STL Development Plan (SDP) is produced in this phase, is then important to define the number of Development Units (DU) composing the project. A DU is a team composed by at least one test engineer and an appropriate computation system where the development process is computed; here we assume that initially there is a unique DU in the development process, and that a DU is able to develop only a portable and a non-portable test program

Figure 5: Portable classification of the processors family

Figure 6: SDP for a unique DU

every month, or even two non-portable test programs but never two portable test programs.

The development plan creation is divided in two phases: in the first one, an initial SDP is proposed ordering the development of the tests with respect to the release date of the processors to the market and the classification reported in *step* b, as the one reported in Figure 4. In this figure, the test development of the portable and non-portable parts for every unit are represented together; for example, for the processor 1 (PI), the development of the test programs for the feature a, of the unit 2, is performed during M12 for both parts: the portable P and non-portable N.

At this point, the second phase starts incorporating the information about the portable classification made in *step c*.

For every unit, the portable part must be developed before the non-portable part.

Thus, the following algorithm is applied to the original development order:

- Allocation of the portable part of the shared new units considering the processor delivering time. In this allocation, given 2 portable tests to develop, the priority is given to the one with the nearest delivering time

- Allocation of the non-portable units in the remaining free slots considering:

- a. The portable part should be already developed;

- b. Given 2 non-portable test to develop, the priority is given to the one with the nearest delivering time

Applying this algorithm to the example in Figure 4, let us with the development plan provided in Figure 6. In the figure, the portable and non-portable parts are represented using blue and red elements, respectively; in addition, the green elements represent the development of non-portable test programs for exclusive features that need not share the results later to other processors.

The development must consider the case in which the number of DU increase, for example, it may happen that at the very early development steps, the number of DU is only one, but after a while, when a parallel process is necessary, the number of DU is increased to two or even more resources if available. The same example described previously is developed considering additional DU in Figure 7. During the definition of the development plan, the order of development of the individual tests for the individual features of each unit is

modified to anticipate the development of the units classified as *shared* according to the previous algorithm. It is expected that the resulting test programs are then ported to the other processors of the same family. Porting a test program to processors containing *reduced* units need minor efforts since the test program is a reduced set of the original one. In contrast, for the units classified as *increased*, the test programs need additional test programs that are specific for testing only the new functionalities. At the end of the generation process, every portable test program is combined with a non-portable test program.

The purpose of this second non-portable test program is to compensate for small FC drop on the considered unit. In order to accomplish with the marketing times offered by the microcontroller producers, it is very important to synchronize the development of the STL with the final production steps of any microcontroller in the family.

For the sake of simplicity, it is assumed that any development process needs the same time unit  $\Delta T$ , in this case represented by 1 month, and as reported in the Figure 7 for example, in M13 and M14 a second and third DU are introduced to the development team. It is possible to notice that in the time M14 one portable test program, two exclusive and three non-portable sub-test programs are developed simultaneously.

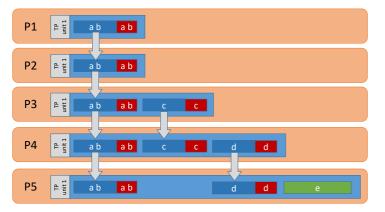

During the last step of the proposed algorithm, the test program structure is created for any one of the units belonging to the processor family. Figure 8 shows the structure of the test program for *Unit 1* of the example. The whole test program for the *Unit 1* needs to consider the five different features that the unit may count with in any processor implementation. In Figure 8, the portable sub-tests are shown in blue, while the non-portable sub-tests are shown in red. In Figure 8 are reported in

Figure 7: SDP for increasing DUs

green the exclusive sub-test. Initially, the test program is developed for the  $Processor\ 1\ (P1)$  feature a and b as discussed previously, and then ported to the  $Processor\ 2\ (P2)$  and  $Processor\ 3\ (P3)$ . For any processor, it is necessary to develop a non-portable sub-test independently. In the  $Processor\ 3\ (P3)$  a new portable sub-test for the feature c is developed similarly. The test program for the feature d is developed for the  $Processor\ 4\ (P4)$  and ported to  $Processor\ 5\ (P5)$ .

Figure 8: Test program structure for a common unit in the processor family

#### IV. CASE STUDY

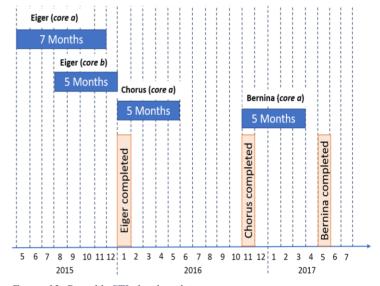

This section introduces the case study. Different STLs have been developed, according to the proposed approach, for testing different automotive processors produced by STMicroelectronics. The STLs of the different processors have been developed with the approach proposed in Section III. Initially, this section provides an overview of the *SPC58* processor family. Afterwards, this section reports the most important features of some of the SPC58 family processors.

# A. The SPC58 processor family

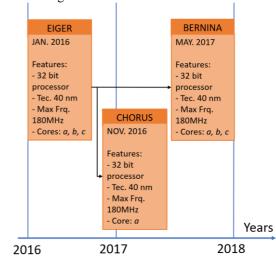

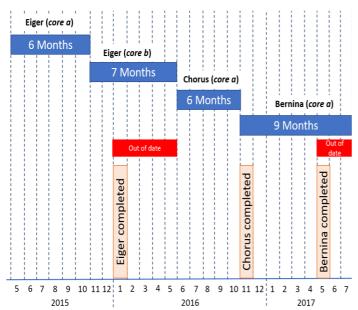

The SPC5X processors developed by STMicroelectronics are specifically developed for the automotive sector and for the different applications required by this sector. The last family designed by STMicroelectronics is the SPC58, it is available to the ECU development engineers since 2016. In this new family, there are numerous processors operating in a multicore context. The introduction of multicore architectures allows greater data computing on the ECU, it is necessary to meet the new needs of the automotive market. Today, the vehicles have sophisticated management and control systems for their parts; such as the engine, the suspension and the management of safety systems on board. Moreover, in the new vehicles, there is great importance to the infotainment applications. The aim of the infotainment applications is improving and facilitating the driving experience. Moreover, with the future introduction of the autonomous guide, the necessary computational abilities on the ECU remains a great technological challenge. The SPC58 family processors are based on the 32 bits Power-PC architecture able to work up to 200MHz. They have large flash memory, from 1MB up to 10MB, and different types and sizes of RAM memory. The RAM memory shared between all cores and the private local RAM memory for each core. These different RAM memories are accessible by the cores with different time latency. The processors are equipped with numerous communication channels; such as the CAN bus, the LINFLEX bus, the UART, the USB interface and the Ethernet interface. In the SPC58 architecture the cores, peripherals and memories are divided over several AMBA BUS; to guarantee the best performance in terms of access speed. The Hardware Security Module (HSM) is introduced in the SPC58 family for managing the security aspects of the communication interfaces. The SPC58 family is segmentation in more lines of products [51]. The processor of the A and M lines are specifically developed for the engine propulsion control and for the transmission control. The A-line and M-line processors are high performance processor to managing complex real-time control software. The Digital Signal Processing (DSP) features are available on these processors. The processors of the P and L lines are used to managing the electrical sensors and to elaborate the measured performed by the acquisition systems. They are equipped with different 12 bits Analog-Digital Converter (ADC) able to work at high speed. The processors of the D, B and C lines are thinking to the network and low power applications. The description of the SPC58 family processors considered is shown in Figure 9, it is temporally organized. Figure 9 shows the period in which the processor and the MCAL software package are available to the customer. Moreover, the processor construction technology, maximum work frequency and the number of the cores present are shown in Figure 9.

Figure 9: Roadmap of the developed processors of the SPC58 family

# B. Compare the processors of the SPC58 family

This subsection provides a description of the cores used in the SPC58 family processors. Moreover, the features of the core units are also compared. In this paper the processors *Eiger*, *Bernina* and *Chorus* are considered.

#### 1) Eiger

The *Eiger* processor (SPC58NEx) [52] is a multicore processor equipped with 6MB of flash memory, 600KB of shared RAM and 64KB of local RAM for each core. The processor is

organized in two AMBA BUSs on which the different peripherals are connected. The processor is equipped with three cores (core a, core b and core c) of different type. All the cores are based on a double issues pipeline with five stages each, and all cores are able to execute the ISA Variable-Length Encoding (VLE) [53] assembly instructions and the Book-E [54] compatible VLE assembly instructions. In addition, the core a also supports the Lightweight Signal Processing (LSP) [55] instructions. All the cores are equipped with 32 General-Purpose Register (GPR) at 32-bit each, and some Special-Purpose Registers (SPR) used for configuring the core features. Moreover, all cores are equipped with an Embedded Floating-Point Unit (EFPU2) and a Performance Monitor unit. The Performance Monitor is used for profiling the core activities at run-time, it is composed of 4 counters able to count different events. The Nexus3 debug module is present in both core types. The *core b* is equipped with 8KB of first-level (L1) instruction cache memory and 4KB of first-level (L1) data cache memory; while the core a has 8KB of L1 instruction cache. All cores have a Memory Protection Unit (MPU) and don't have the virtual Memory Management Unit (MMU), which was present in the previous STMicroelectronics processor family. The main features of the core a and core b are shown in Table 1. The Eigher processor belongs to the A-line devices.

|                    | Eiger         | Eiger          | Bernina       | Chorus               |

|--------------------|---------------|----------------|---------------|----------------------|

|                    | (core b)      | (core a)       | (core a)      | (core a)             |

| #pipeline          | Dual issues   | Dual issues    | Dual issues   | Single               |

|                    |               |                |               | issues               |

| #stage of pipeline | 5             | 5              | 5             | 4                    |

| ISA                | VLE,          | VLE,           | VLE,          | VLE,                 |

|                    | Book-E        | Book-E,<br>LSP | Book-E, LSP   | Book-E               |

| #GPR               | 32 registers  | 32 registers   | 32 registers  | 32                   |

|                    | (32 bit each) | (32 bit each)  | (32 bit each) | registers            |

|                    |               |                |               | (32 bit              |

| UCDD               | 100           | 100            | 111 : .       | each)                |

| #SPR               | 109 registers | 108 registers  | 111 registers | 99                   |

|                    | (32 bit each) | (32 bit each)  | (32 bit each) | registers<br>(32 bit |

|                    |               |                |               | each)                |

| Data cache         | 4KB           | _              | 8KB           | -                    |

| Instruction        | 8KB           | 8KB            | 16KB          | -                    |

| cache              |               |                |               |                      |

| Debug unit         | Nexus3        | Nexus3         | Nexus3        | Nexus3               |

| BTB                | 8 entries     | 8 entries      | 8 entries     | 4 entries            |

| FPU                | EFPU2         | EFPU2          | EFPU2         | EFPU2                |

| Performance        | 71 events     | 69 events      | 71 events     | 57 events            |

| monitor            |               |                |               |                      |

| MMU                | -             | -              | -             | _                    |

| MPU                | 24 entries    | 24 entries     | 24 entries    | -                    |

|                    | configurable  | configurable   | configurable  |                      |

Table 1: The features of the SPC58 cores

## 2) Bernina

The *Bernina* processor (SPC58NNx) [56] is a multicore processor equipped with 6MB of flash memory, 512KB of shared RAM and 128KB of local RAM for each core. Two AMBA BUSs are present in the *Bernina* processors. The processor is equipped with three cores of the same type (called *core a, core b* and *core c*), and additional two cores used in lockstep configuration. The *core a* is based on a dual issues pipeline with five stages each. The VLE, Book-E and LSP assembly instructions are available in Bernina. In this core,

there are 8KB of L1 data cache and 16KB of L1 instruction cache. The main features of the *Bernina's* core are shown in Table 1. The *Bernina* processor belongs to the *A-line* devices.

#### 3) Chorus

The *Chorus* processor (SPC582Bx) [56] is a single-core (*core a*) processor equipped with 1MB of flash memory and 96KB of RAM. A single AMBA BUS is present in the processor. *Core a* is based on a single issue with four stages each. The VLE and Book-E assembly instructions are available in *core a*. In this core, there are not data cache and instruction cache. The main features of the *core a* are shown in Table 1. The *Chorus* processor belongs to the *C-line* devices.

## C. Compare the core and the units of the SPC58 family

This subsection compares the main features of the cores used in the processors previously described. In Table 2 the features of different units of the core are compared. The processor's development roadmap analyzed in Figure 9 is considered. In general, the units inside of the Eiger core b are classified as reduction compared to the Eiger core a. A similar consideration is possible for the units of the Chorus core a respected to the Eiger core b. Instead, the units of the Bernina core a are classified as increases compared with the Eiger core a. From Table 2, it can be seen that the Branch Target Buffer (BTB) unit remains almost unchanged for all processors, except for the Chorus where the number of entries is halved. The BTB is based on the Branch Instruction Cache (BTIC). It consists of a small cache memory contain two information: the address of the conditional jump instructions and the statistical prediction of the branch executed. The entries are populated and updated in accord with the Least-Frequently Used (LFU) approach, where the less frequently used entry is overwritten. The BTB has one SPR used to config the unit, to enable and disable the BTB, or to invalidate all entries. The BTIC implementation is architecturally transparent, so it does not have to be saved during the context switch.

In all the cores there is only one divider unit shared between the two pipelines. In the cores that manage the LSP instructions, the divider operates at 64 bits, in the other cores it operates at 32 bits. Table 2 shows the number of clock cycles needed to perform a single division. The number of clock cycles is variable, it depends on the implementation of the divisor unit and depends on the number of low logical bits present in the operands of the division. In the proposed architecture, the whole processor stalled while the division is performed. As the division unit, the multiplier unit is also shared between the two pipelines. However, each multiplication instruction is always executed in two clock cycles. In the cores that manage the LSP instructions, the multiplier is considerably more complex and it is able to perform a considerable number of different types of multiplication instructions. Moreover, in the cores with the LSP ISA instructions are management, the multiplier operates at 64 bits; while in the other cores it operates at 32 bits. It should be noted that two distinct multipliers are present internally in the ISA LSP cores. The first multiplier is used to managed the VLE multiplications instructions that perform 32 bits multiplication, while the second multiplier is used for LSP instructions. In the LSP instruction multiplier is also present a hardware

accumulator used by some particular instructions. A decoder unit is integrated into the multiplier, it is able to decode the LSP multiplication instruction. The register file consists of 32 generic registers (GPR) equal for all processors of the Power-PC architecture, while the number of special registers (SPR) depends on the number of peripherals and their functionalities. All the registers are physically implemented in 32 bits, but in the cores that handle the LSP instructions, there is the possibility of concatenating two registers to obtain a 64-bit logic register. The register file has three read ports and two write ports in the cores that implementing the VLE and Book-E instructions, while the ports are four in reading and four in writing in the cores that implementing the LSP instructions. In accord with the EABI standard [33], the R1 register is used as Stack Point. The R2 and R13 registers are used to access the Small Data Area (SDA) memory regions. The SDA regions are used managing the global variables and the global constants. The registers from R3 to R10 are volatile and they are used for passing the parameters to the functions written in C language. Moreover, the register R3 is used for the return value of the C functions. The volatile registers do not need to be saved in the stack frame during the context switch or when a function is called. Instead, the registers from R14 to R31 are non-volatile and must be saved in the stack frame.

The shifter unit is able to performed shift and rotate instructions to right or to left. It can operate on 32 bits register in cores that handle the VLE instructions, or 64 bits register in cores that handle the LSP instructions. Each pipeline is equipped with its own shifter unit. Similarly to the shifter units, the adder units are also duplicated. There is the adder unit for each pipeline. The adder performs the operations in one single clock cycle. Whit the VLE instructions the adder units performing operation at 32 bits. In the cores that manage the LSP instructions, the adder unit is adapted to work with data of 64 bits.

|                     |              |        | BTB                               | DIVIDER                                                                    | MULTIPLIER                                                                                                                                             | REGISTER FILE                                                                                     | SHIFTER                                                      | ADDER                                 |

|---------------------|--------------|--------|-----------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------|

| Eiger<br>(core a)   | Features     |        | 1) 8 entries<br>2) BTAC<br>3) LFU | 1) 3-24 clock<br>cycle for a<br>division     2) 64 bits integer<br>divider | 1) Multiplier with 64 bits output 2) Multiplier with 32 bits input 3) Accumulator 4) Own decoder unit 5) Two internal multipliers: 16 bit and 32 bits  | 1) 32 GPR     2) 76 SPR     3) Concatenation of two registers for management the LSP instructions | 1) 64 bits<br>rotate and<br>shift<br>left/right<br>operation | 1) 64 bits<br>and 32<br>bits adder    |

|                     |              |        | -                                 | 1                                                                          | 457                                                                                                                                                    | 0                                                                                                 | 16                                                           | 24                                    |

|                     | #Instruction | VLE    | -                                 | 22                                                                         | 4                                                                                                                                                      | 8                                                                                                 | 8                                                            | 8                                     |

|                     |              | Book-E | -                                 | 8                                                                          | 8                                                                                                                                                      | 20                                                                                                | 4                                                            | 20                                    |

|                     | #SPR u       | ised   | 1                                 | -                                                                          | -                                                                                                                                                      | -                                                                                                 | -                                                            | -                                     |

| Eiger<br>(core b)   | Featur       |        | 1) 8 entries<br>2) BTAC<br>3) LFU | 1) 6-16 clock cycle<br>for a division<br>2) 32 bits integer<br>divider     | 1) Multiplier with<br>32 bits output<br>2) Multiplier with<br>16 bits input                                                                            | 1) 32 GPR<br>2) 77 SPR                                                                            | 1) 32 bits<br>rotate and<br>shift<br>left/right<br>operation | 1) 32 bits<br>adder                   |

| (core v)            |              | LSP    | -                                 | -                                                                          | -                                                                                                                                                      | -                                                                                                 | -                                                            | -                                     |

|                     | #Instruction | VLE    | -                                 | 22                                                                         | 4                                                                                                                                                      | 8                                                                                                 | 8                                                            | 8                                     |

|                     |              | Book-E | -                                 | 8                                                                          | 8                                                                                                                                                      | 20                                                                                                | 4                                                            | 20                                    |

|                     | #SPR u       | ised   | 1                                 | -                                                                          | -                                                                                                                                                      | -                                                                                                 | -                                                            | -                                     |

| Bernina<br>(core a) | Featui       | res    | 1) 8 entries<br>2) BTAC<br>3) LFU | 1) 6-24 clock cycle for a division     2) 64 bits integer divider          | 1) Multiplier with 64 bits output 2) Multiplier with 32 bits input 3) Accumulator 4) Own decoder unit 5) Two internal multipliers: 16 bits and 32 bits | 1) 32 GPR     2) 79 SPR     3) Concatenation of two registers for management the LSP instructions | 1) 64 bits<br>rotate and<br>shift<br>left/right<br>operation | 1) 64 bits<br>and 32<br>bits<br>adder |

|                     |              | LSP    | -                                 | 1                                                                          | 457                                                                                                                                                    | 0                                                                                                 | 16                                                           | 24                                    |

|                     | #Instruction | VLE    | -                                 | 22                                                                         | 4                                                                                                                                                      | 8                                                                                                 | 8                                                            | 8                                     |

|                     |              | Book-E | -                                 | 8                                                                          | 8                                                                                                                                                      | 20                                                                                                | 4                                                            | 20                                    |

|                     | #SPR u       | ised   | 1                                 | -                                                                          | -                                                                                                                                                      | -                                                                                                 | -                                                            | -                                     |

| Chorus              | Features     |        | 1) 4 entries<br>2) BTAC<br>3) LFU | 1) 7-35 clock cycle<br>for a division<br>2) 32 bits integer<br>divider     | 1) Multiplier with<br>32 bits<br>2) Multiplier with<br>16 bits                                                                                         | 1) 32 GPR<br>2) 67 SPR                                                                            | 1) 32 bits<br>rotate and<br>shift<br>left/right<br>operation | 1) 32 bits<br>adder                   |

| (core a)            |              | LSP    | -                                 | -                                                                          | -                                                                                                                                                      | -                                                                                                 | -                                                            | -                                     |

|                     | #Instruction | VLE    | -                                 | 22                                                                         | 4                                                                                                                                                      | 8                                                                                                 | 8                                                            | 8                                     |

|                     |              | Book-E | -                                 | 8                                                                          | 8                                                                                                                                                      | 20                                                                                                | 4                                                            | 20                                    |

|                     |              |        |                                   |                                                                            |                                                                                                                                                        |                                                                                                   |                                                              |                                       |

Table 2: The features of the different units inside of the cores

#### V. EXPERIMENTAL RESULTS

This section reports the experimental results for the SPC58 processor family produced by STMicroelectronics. The features of the family and the features of its processors have been described in Section IV. In particular, the first subsection reports the Fault Coverage figures for the different units of the cores of the different processors, in accord with the proposed porting methodology described in Section III. Furthermore, the development times of the STLs and the fault-simulation times are also reported. Later, some interesting examples of the reduction units are discussed and analyzed. Afterwards, the efficiency of the ATPG-base and Evolutionary-base approaches are discussed. Finally, the ISA contribution is analyzed.

#### A. Portable STL results

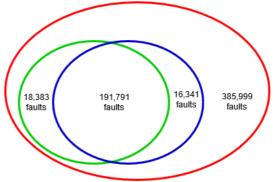

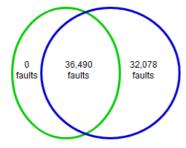

In order to demonstrate the effectiveness of the proposed methodology discussed in Section III, the FC values obtained using the same portable test programs on the different processors are reported. In particular, the results for BTB, Divider, Multiplier, Register File, Shifter, and Adder are analyzed.

## 1) BTB

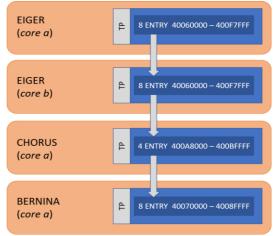

A possible BTB test methodology is proposed in [28]. In [28] the test is performed by performing a sufficient number of conditional branches used to load the BTB entries. After that the BTB has been initialized, a new sequence of branches is performed to verify the BTB prediction. The test methodology proposed in [28] is portable because it is developed with the deterministic approach. It considers the BTB to a functional point of view and it is independent of its synthesis. The structure of the test programs is shown in Figure 10. The test program is implemented considering the sizes of the different RAM memories present in the different processors, the space available for each test program is shown in Figure 10. The algorithm proposed in [28] is adapted to the memory size of each processor. The numbers of possible permanent stuck-at faults for each BTB unit of the different core are shown in Table 3, while the Fault Coverage figure for each processor is shown in Table 4. The first column, called FC, reports the Fault Coverage obtained considering all possible BTB faults. The second column (FC increm.) considers the incremental faultsimulation approach. In the incremental approach, the faults previous detected by other test programs are not again considerate during a new fault-simulation campaign. The last column reports the time necessary to perform the faultsimulation of the single test program considering all faults present in the UUT. The FC total value report the fault coverage

obtained considering the union of all test programs. While the FC total and cascade value report the final FC. FC total and cascade value also includes the contribution of non-portable test programs eventually implemented. It is possible to note that no other test program introduces a cascade phenomenon on the FC of the BTB, and no other non-portable test programs are implemented for the BTB unit. Analyzing the FC values obtained with the same test program on all processors, it is possible to note a constant FC value around 70% for the Eiger core a, the Eiger core b and the Bernina core a, as shown in Table 4. It is possible to see from Table 2 that the BTBs unit of these three cores have the same features. It should be noted that at the GATE level these three BTBs are different because the number of faults is significantly different as shown in Table 3.

|               | Eiger<br>(core a) | Eiger<br>(core b) | Bernina<br>(core a) | Chorus<br>(core a) |

|---------------|-------------------|-------------------|---------------------|--------------------|

| BTB           | 21,434            | 16,506            | 19,892              | 11,037             |

| Divider       | 34,013            | 18,928            | 35,018              | 20,337             |

| Multiplied    | 73,638            | 29,717            | 63,962              | 32,868             |

| Register file | 146,217           | 82,518            | 140,654             | 68,217             |

| Shifter       | 12,422            | 3,132             | 17,115              | 3,136              |

| Adder         | 14,762            | 6,446             | 19,758              | 3,972              |

Table 3: Number of faults for each unit of each core

Figure 10: BTB test program structure

The BTB unit of the *Chorus core a* is classified as REDUCED, compared to the BTB of the other cores considered in this family. In the *Chorus core a*, the number of BTB entries is halved. Only for this core, it is necessary to modify the test program. It is necessary to reduce the number of branches performed to initialize the BTB, and the number of branches performed to verify the predictions of the BTB. The test method proposed in [28] is easily scalable with respect to the number of

|                      | E      | iger (core a   | a)             | E      | Eiger (core b) |                |        | Bernina (core a) |                |        | Chorus (core a) |                |  |

|----------------------|--------|----------------|----------------|--------|----------------|----------------|--------|------------------|----------------|--------|-----------------|----------------|--|

| TEST PROGRAMS        | FC [%] | FC increm. [%] | Time<br>[Hour] | FC [%] | FC increm. [%] | Time<br>[Hour] | FC [%] | FC increm. [%]   | Time<br>[Hour] | FC [%] | FC increm. [%]  | Time<br>[Hour] |  |

| BTB1                 | 63.38  | +63.38         | 168            | 57.76  | +57.76         | 195            | 63.40  | +63.40           | 227            | 53.43  | +53.43          | 98             |  |

| BTB2                 | 50.71  | +6.24          | 161            | 45.65  | +9.82          | 174            | 54.98  | +6.20            | 206            | 42.13  | +7.06           | 88             |  |

| BTB3                 | 27.41  | +2.28          | 85             | 14.81  | +1.92          | 92             | 19.54  | +1.34            | 161            | 18.54  | +3.83           | 41             |  |

|                      |        |                |                |        |                |                |        |                  |                |        |                 |                |  |

| FC total             |        | 71.90          |                |        | 69.50          |                |        | 71.16            |                |        | 64.32           |                |  |

| FC total and cascade |        | 71.90          |                |        | 69.51          |                |        | 71.16            |                |        | 64.33           |                |  |

Table 4: The BTB case

BTB entries. The FC reduction is due to the decrease of the memory available in the *Chorus* processor, as discusses in subsection B.3 of the Case Study. The variety of the memory addresses that can be loaded in the BTB entries is considerably lower in the *Chorus* processor.

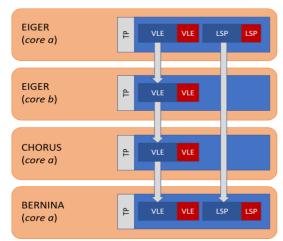

## 2) DIVIDER

The test programs for the division unit consider divisions executed between the checkerboard patterns (0x0000, 0xFFFF, 0xAAAA, 0x5555, 0xCCCC, 0x3333) and numbers of power of two (2, 4, 8, 16, ....). The use of these generic patterns does not require the calculation of ATPG patterns valid only for a specific implementation of the divisor, as discussed in Section III. The structure of the test programs is shown in Figure 11. Two sub-tests have been implemented, one considering the VLE instructions on 32-bit operands and one considering those with 64-bit operands. Furthermore, a non-portable test program was implemented using the ATPG approach.

The Fault Coverage value obtained on the different processors of the family under examination is about 78% (77% Eiger core a, 83% Eiger core b, 76% Bernina core a, 77% Chorus core a), as shown in Table 5. In the Eiger core a and Bernina core a, the test methodology is extended to 64-bit patterns using LSP instructions. On the other cores, the VLE instructions with 32-bit patterns are used. It is interesting to note that the DIV3 test

Figure 11: Divider, multiplier, shifter, and adder test programs structure

program on the *Chorus* processor does not give a useful contribution to the final FC, this test program was discarded in the final STL. In order to increase the FC of the dividers, some

non-portable test programs are implemented with the ATPG approach. The contribution of these test programs is indicated by comparing the FC total value with the FC total and cascade value of Table 5.

### 3) MULTIPLIER