# Doctoral Dissertation Doctoral Program in ELECTRICAL, ELECTRONICS AND COMMUNICATIONS ENGINEERING (32.th cycle)

# Development of CMOS Integrated Circuits for SiPM Readout

Weishuai Cheng

\* \* \* \* \* \*

#### **Supervisors**

Prof. Amedeo Staiano, Supervisor Prof. Michele Goano, Co-supervisor

#### **Doctoral Examination Committee:**

Prof.Gianluca Traversi, Referee, Università degli Studi di Bergamo Prof.Piero Giubilato, Referee, Università di Padova

Politecnico di Torino To be define, 2020

| This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.                                   |

| Weishuai Cheng Turin, To be define, 2020                                                                                                                                                                                                                               |

### Summary

Silicon photo-multiplier (SiPM) is a new generation of solid-state photon sensors, invented by Russian scientists during the 1990s, which working principle is based on the operation of photo-diode arrays in Geiger mode. Similarly to the conventional Photon-Multiplier Tube (PMT), a SiPM features a high gain in the same range, high Photon Detect Efficiency (PDE) and excellent time response. On top of that, SiPMs provide important advantages such as low operating voltage, compactness and insensitivity to magnetic fields. Initial drawbacks in terms of high cross-talk, dark count and generally high correlated noise, has been significantly reduced with constant improvements in manufacturing technology. As a consequence, SiPMs became an attractive choice for an increased number of applications in nuclear medicine, high energy and astroparticle physics experiments, automotive (LIDAR) and homeland security.

ASICs (Application Specified Integrated Circuits) have been used in radiation sensor readout for more than 40 years, providing specific solutions in terms of signal amplification, shaping, and digitization. The development of custom integrated electronics for the readout of highly segmented SiPM matrices allowed for the construction of compact photoelectronic modules for detectors implementing aggressive spatial resolution and channel density.

This thesis exploits the development of innovative CMOS integrated electronics for SiPM readout. The versatility of the architecture of the ASICs herein described should allow for the use of these electronics in system-grade detectors for medical imaging, particle and nuclear physics, using both room temperature inorganic (crystal) scintillators or the fast scintillation of compton scattering in novel noble-liquid based PET detectors operating at cryogenic temperatures.

This manuscript provides detailed description, analytical depiction and silicon characterisation results of the front-end CMOS circuitry to readout SiPM sensors at liquid nitrogen temperature and room temperature. In order to study and verify the functionalities of the basic circuit modules for a chip-level integration.

Then, a 32-pixel mixed-signal ASIC for the readout of SiPM matrices at cryogenic temperature is developed. This chip arranges its channels in  $4 \times 8$  arrays, expected to readout large area SiPMs. The readout channel consists of high bandwidth and low input-impedance pre-amplifier, leading edge discriminators, low

power TDCs and logic control and data transmission blocks, providing the time based SiPM readout up tp 1 cm<sup>2</sup> and maximum event rate of 5 MHz per channel, with the power consumption less than 10 mW per channel and time bin 50ps(25ps).

A 64-channel mixed-signal ASIC for highly capacitive silicon detectors is also described.

# Acknowledgements

And I would like to acknowledge  $\dots$  To be written...

I would like to dedicate this thesis to my loving family

# Contents

| Li | st of | Tables                                                         | X  |

|----|-------|----------------------------------------------------------------|----|

| Li | st of | Figures                                                        | XI |

| 1  | Intr  | roduction                                                      | 1  |

|    | 1.1   | SiPM Principles and Characteristics                            | 1  |

|    |       | 1.1.1 SiPM Operating Principles                                | 1  |

|    |       | 1.1.2 SiPM Properties at Room and Cryogenic temperature        | 5  |

|    |       | 1.1.3 State of the art: SiPM products                          | 13 |

|    | 1.2   | SiPM applications                                              | 15 |

|    |       | 1.2.1 SiPM in particle and nuclear physics                     | 15 |

|    |       | 1.2.2 SiPM in medical imaging                                  | 16 |

| 2  | Rev   | riew of SiPM readout ASICs                                     | 21 |

|    | 2.1   | TOFPET                                                         | 21 |

|    | 2.2   | PACIFIC                                                        | 24 |

|    | 2.3   | ANGUS                                                          | 25 |

|    | 2.4   | VATA64-HDR16                                                   | 26 |

|    | 2.5   | SPIROC                                                         | 27 |

|    | 2.6   | MD-SiPMs                                                       | 28 |

|    | 2.7   | Conclusion                                                     | 29 |

| 3  | Test  | t chips studies for SiPM readout at cryogenic temperature      | 33 |

|    | 3.1   | SiPM electrical model                                          | 33 |

|    | 3.2   | Cold CMOS electronics design review                            | 39 |

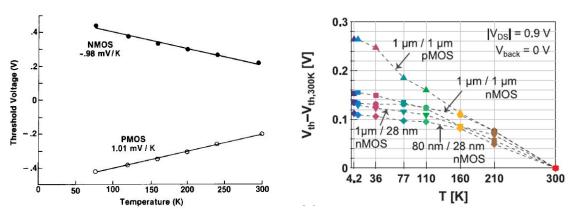

|    |       | 3.2.1 Transistor properties and temperature                    | 39 |

|    |       | 3.2.2 Conclusion and guidance for cryogenic circuits design    | 46 |

|    | 3.3   | Test structures design and study                               | 47 |

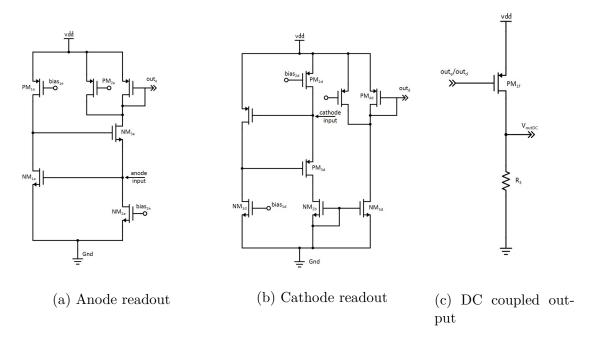

|    |       | 3.3.1 Schemes of front-end electronics and the test structures | 47 |

|    |       | 3.3.2 Input stage: the very front end structure                | 49 |

|    |       | 3.3.3 TestChip1 design                                         | 55 |

|    |       | 3 3 4 TestChip2 design                                         | 58 |

|    | 3.4    | Experimental results of test chips                            | 62  |

|----|--------|---------------------------------------------------------------|-----|

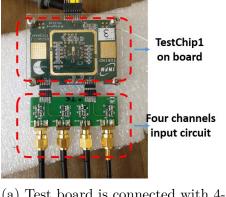

|    |        | 3.4.1 Characterization environment set up                     | 62  |

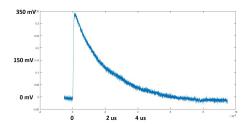

|    |        | 3.4.2 TestChip1 test                                          | 63  |

|    |        | 3.4.3 TestChip2 test                                          | 68  |

|    | 3.5    | Summary                                                       | 71  |

| 4  | Des    | ign of multi-channel front-end ASICs for capacitive sensors i | n   |

|    | 110    | nm CMOS                                                       | 73  |

|    | 4.1    | Overview of the ASIC architecture                             | 74  |

|    | 4.2    | Versatile Front-End Amplifier Design                          | 75  |

|    | 4.3    | Shaper stages and discriminators                              |     |

|    | 4.4    | Time and Amplitude Digitisation Circuits                      |     |

|    | 4.5    | Characterisation results                                      | 81  |

|    | 4.6    | Conclusions and outlook                                       | 85  |

| 5  | A n    | nixed-signal ASIC for SiPM readout                            | 89  |

|    | 5.1    | Overview the full chip                                        | 89  |

|    | 5.2    | Very front end                                                | 89  |

|    |        | 5.2.1 Very front end design                                   |     |

|    |        | 5.2.2 Very front end simulation                               | 97  |

|    | 5.3    | Discriminator and TDC                                         | 103 |

|    | 5.4    | Calibration circuit and debug buffer                          | 107 |

|    | 5.5    | Full pixel operation and data transmission                    | 109 |

|    | 5.6    | Summary                                                       | 113 |

| 6  | Cor    | nclusions and future perspectives                             | 115 |

| Bi | ibliog | graphy                                                        | 117 |

# List of Tables

| 1.1 | Properties comparison of different Photon sensors                              | 5   |

|-----|--------------------------------------------------------------------------------|-----|

| 1.2 | List of SiPM products                                                          | 14  |

| 1.3 | SiPM applied in liquid Xenon (LXe) or Argon (LAr) detectors                    | 15  |

| 2.1 | Summary of reviewed ASICs for SiPM readout                                     | 31  |

| 3.1 | List of SiPM parameters used for simulation                                    | 39  |

| 3.2 | Variables description in drain current equation                                | 40  |

| 3.3 | Stability simulation results                                                   | 54  |

| 3.4 | Bias setting of the front-end                                                  | 57  |

| 3.5 | Post-layout simulation results                                                 | 57  |

| 3.6 | Parameters of TestChip1 input circuit                                          | 64  |

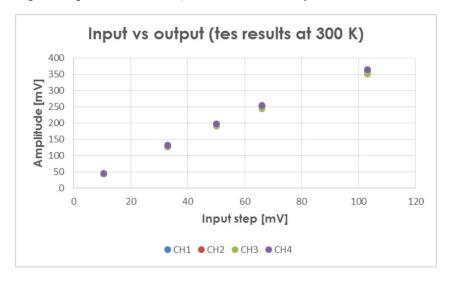

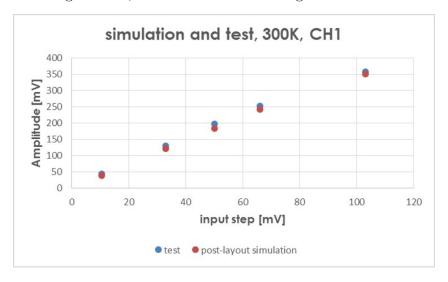

| 3.7 | Comparison results between post layout simulation and test in 300 K            | 68  |

| 3.8 | 300K, Test-Chip2 VFE, parameters comparison between the post                   |     |

|     | layout simulation and test (DC-cathode VFE, input capacitance 1                |     |

|     | nF, the rising time is measured with input step voltage of $85~\mathrm{mV})$ . | 70  |

| 3.9 | 77K, TestChip2 VFE, parameters comparison between the post lay-                |     |

|     | out simulation and test(DC-cathode VFE, input capacitance 1 nF,                |     |

|     | the rising time is measured with input step voltage of 85 mV) $$               | 71  |

| 4.1 | Design parameters of the chip                                                  | 73  |

| 4.2 | Dimensions of front-end transistors                                            | 76  |

| 4.3 | Gains test of timing branch                                                    | 83  |

| 4.4 | Summary of electrical test results                                             | 86  |

| 5.1 | Dimensions of ALCOR very front-end transistors                                 | 92  |

| 5.2 | Summary of configuration in ALCOR VFE                                          | 95  |

| 5.3 |                                                                                | 100 |

| 5.4 | List of simulation results of the VFE for different working modes,             |     |

|     |                                                                                | 103 |

| 5.5 | List of ALCOR parameters                                                       | 114 |

# List of Figures

| 1.1  | SiPM Structure                                                        | 2  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Simplified schematic structures of different types of photon diodes   | 3  |

| 1.3  | APD Bias regions and avalanche in Geiger mode                         | 4  |

| 1.4  | 2D structure of SiPM and the product example                          | 5  |

| 1.5  | SiPM output example [47]                                              | 7  |

| 1.6  | PDE optimized for Cherenkov telescope array [47]                      | 9  |

| 1.7  | Dark count rate as a function of temperature for different over volt- |    |

|      | ages [5]                                                              | 10 |

| 1.8  | The cross talk and after pulse                                        | 11 |

| 1.9  | Cross talk characterization of SiPM by FBK, from 300 K to 40 K[5].    | 11 |

| 1.10 | After pulse as a function of temperature and over voltage             | 12 |

| 1.11 | Dynamic range measurement compared with ideal response                | 13 |

| 1.12 | LAr TPC equipment and working principle in Darkside-20k project.      | 16 |

| 1.13 | Positron Emission Tomography working principle [40]                   | 17 |

| 1.14 | Structure of the typical scintillator detector                        | 17 |

| 1.15 | Time of Flight information to boost the reconstruction quality [92].  | 18 |

|      | Conceptional structure of $3D\pi$ equipment [78]                      | 19 |

| 1.17 | Basic schematic of SPECT system [97]                                  | 20 |

| 2.1  | Basic architecture of TOFPET single channel [87]                      | 21 |

| 2.2  | Basic architecture of TOFPET front-end amplifier (shown for n-        |    |

|      | input circuit)[87]                                                    | 22 |

| 2.3  | Dual thresholds for dark count rejection[87]                          | 23 |

| 2.4  | Working principle of analogue interpolation TDC [20]                  | 23 |

| 2.5  | PACIFIC analog chain and control blocks [25]                          | 24 |

| 2.6  | PACIFIC input stage [25]                                              | 25 |

| 2.7  | Architecture of the ANGUS ASIC channel[97]                            | 26 |

| 2.8  | Working principle of input stage in ANGUS ASIC [97]                   | 27 |

| 2.9  | Architecture of the VATA64-HDR16 ASIC channel[10]                     | 27 |

| 2.10 | Readout scheme of SPIROC ASIC                                         | 28 |

| 2.11 | Diagram structure of DS-SiPM system in EndoTOFPET-US project          |    |

|      | [16]                                                                  | 29 |

| 2.12 | comparison between Analog and MD-SiPM simulations [44]                | 30 |

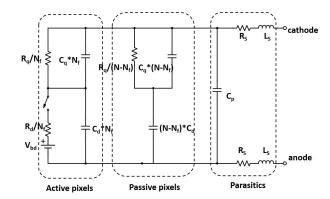

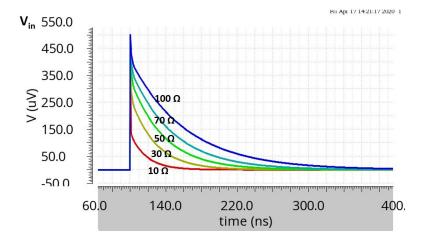

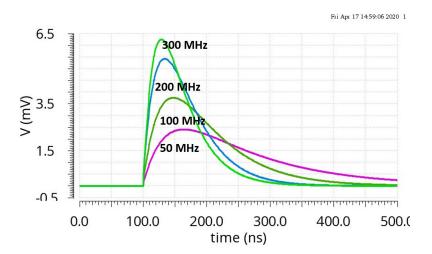

| 3.1  | SiPM electrical model for single pixel fired                              | 34 |

|------|---------------------------------------------------------------------------|----|

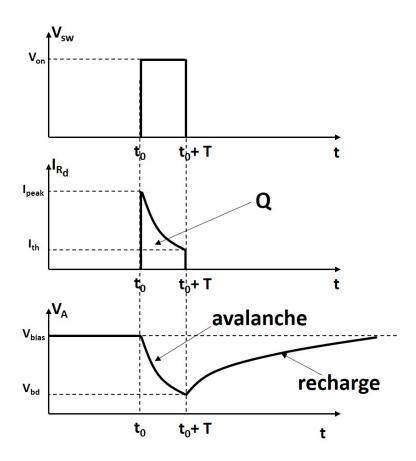

| 3.2  | Transient current, voltage waveforms of SPAD model, realized with         |    |

|      | voltage control switch, simulates a detected event                        | 36 |

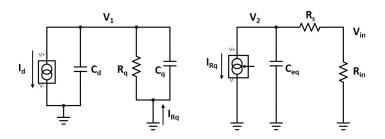

| 3.3  | Small signal equivalent circuit of SiPM readout                           | 37 |

| 3.4  | Simplified simulation schematic of SiPM and readout circuit               | 38 |

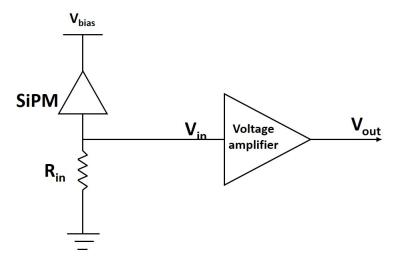

| 3.5  | Input voltage and input resistance of readout circuit                     | 38 |

| 3.6  | Output voltage and bandwidth of readout circuit, the gain of voltage      |    |

|      | amplifier is 20, $R_{in} = 50\Omega$                                      | 39 |

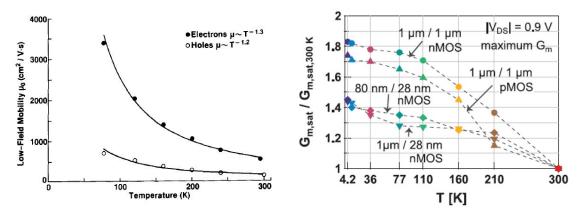

| 3.7  | Increase in mobility as temperature is reduced                            | 41 |

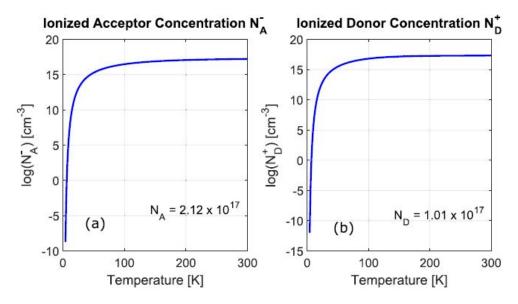

| 3.8  | Temperature dependence of ionized acceptor and donor concentra-           |    |

|      | tion [31]                                                                 | 42 |

| 3.9  | Increase in mobility as temperature is reduced                            | 43 |

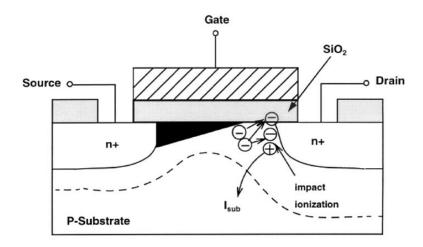

| 3.10 | Schematic representation of impact ionization by hot electrons in         |    |

|      | the channel of an NMOS device. The holes produced by impact               |    |

|      | ionization constitute the substrate current [59]                          | 44 |

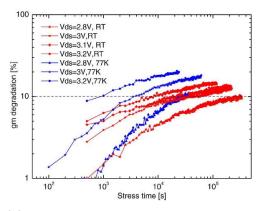

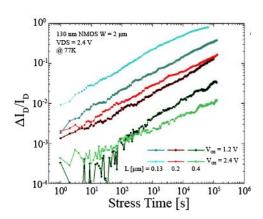

| 3.11 | Example of experimental results for hot carrier effect test               | 45 |

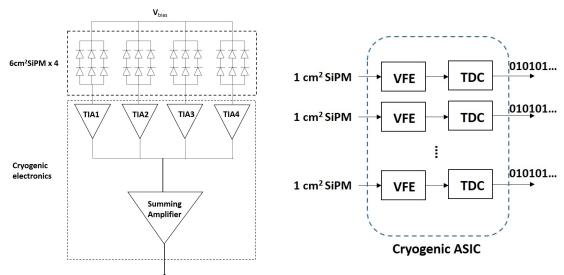

|      | Two approaches to read out out large area SiPM and work at cryo-          |    |

|      | genic temperatures                                                        | 48 |

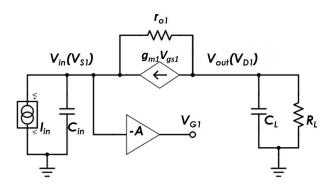

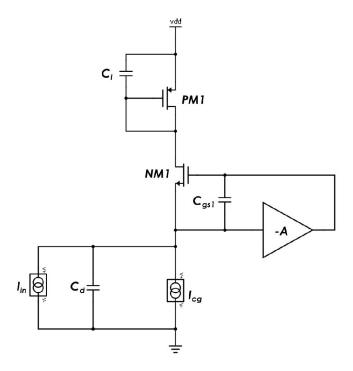

| 3.13 | Working principle of Regulated Common Gate structure                      | 50 |

|      | Small-signal equivalent of RCG                                            | 51 |

|      | Schematic for stability simulation                                        | 53 |

|      | Readout scheme for large area SiPM in one channel                         | 55 |

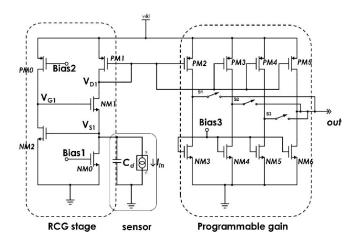

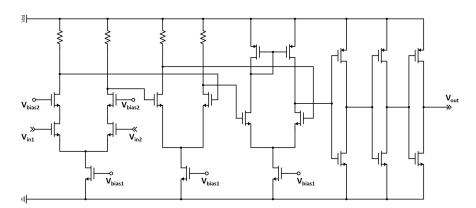

|      | Transistor level schematic design                                         | 56 |

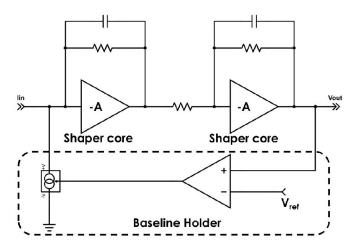

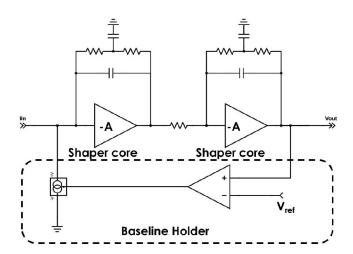

|      | Transistor level design of shaper-core amplifier                          | 56 |

|      | Transistor level design of Baseline Holder                                | 57 |

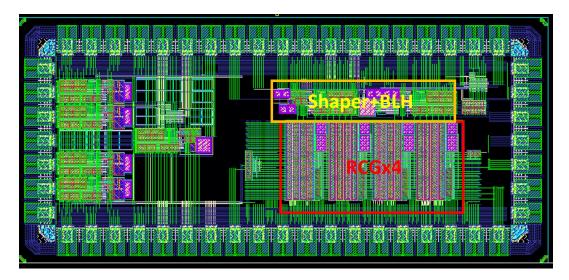

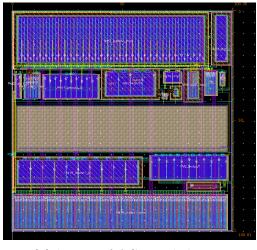

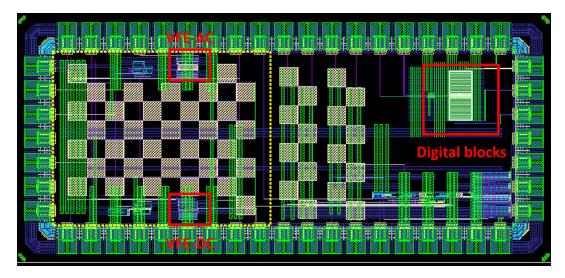

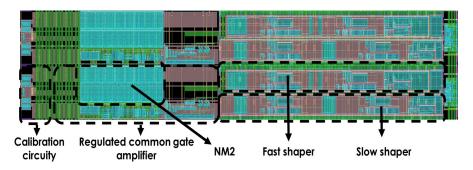

| 3.20 | Layout view of TestChip1, 2.6 mm x 1.2 mm                                 | 58 |

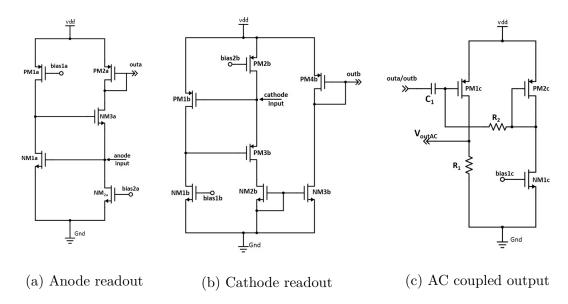

| 3.21 | Dual polarities readout RCGs with AC coupled scheme                       | 58 |

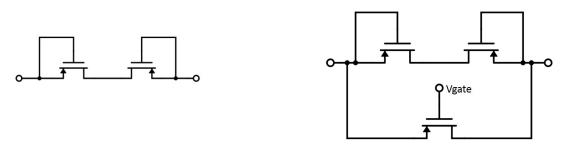

| 3.22 | Large resistance implemented by MOSFETs to set DC operating point         | 59 |

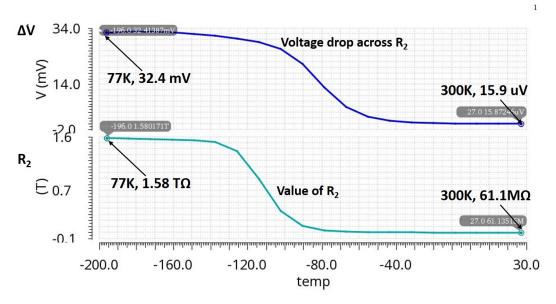

| 3.23 | Temperature simulation to show the variation of voltage drop $(\Delta V)$ |    |

|      | and value of $R_2$                                                        | 60 |

| 3.24 | Dual polarities readout RCGs with DC coupled scheme                       | 60 |

| 3.25 | Layouts of two VFEs                                                       | 61 |

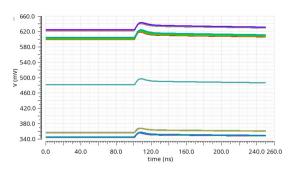

| 3.26 | Simulation of the very front end (cathode-DC coupled) at both 300K        |    |

|      | and 77K                                                                   | 61 |

| 3.27 | Layout view of TestChip2, 2.6 mm x 1.2 mm                                 | 62 |

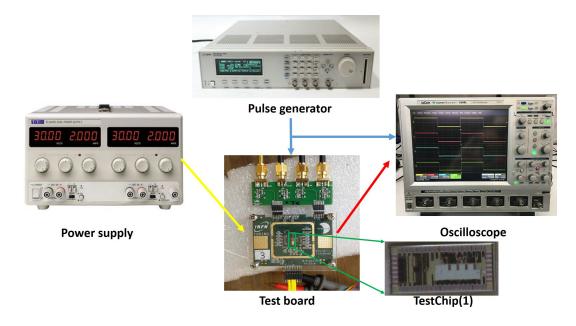

| 3.28 | Test environment set-up                                                   | 63 |

| 3.29 | Study of the Test chips in cryogenic condition                            | 64 |

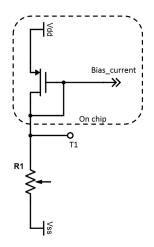

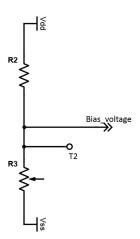

| 3.30 | Bias setting                                                              | 65 |

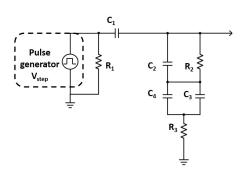

| 3.31 | The input circuit of TestChip1 board                                      | 65 |

|      | Architecture of new version of TestChip1                                  | 66 |

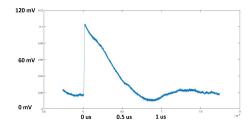

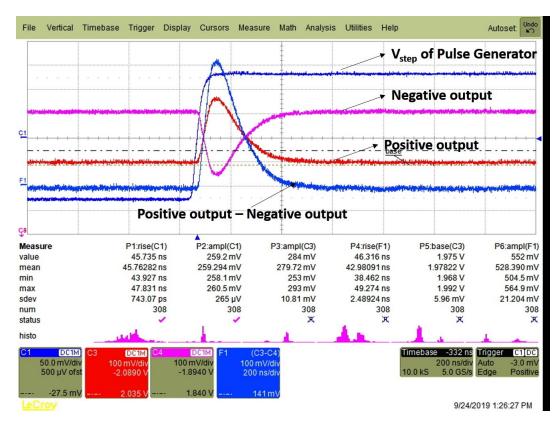

| 3.33 | Waveforms observed by oscilloscope                                        | 66 |

|      | Test results of 4 channels input and output at 300 K                      | 67 |

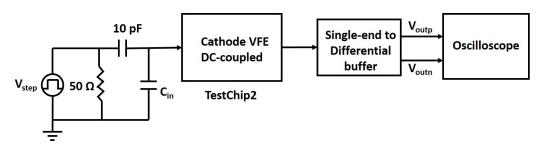

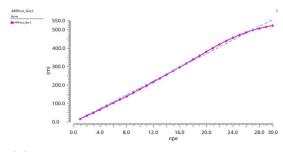

| 3.35 | Simulation and test of input to output relation at 300 K (CH1) |

|------|----------------------------------------------------------------|

| 3.36 | Setup of TestChip2 VFEs characterization (300K)                |

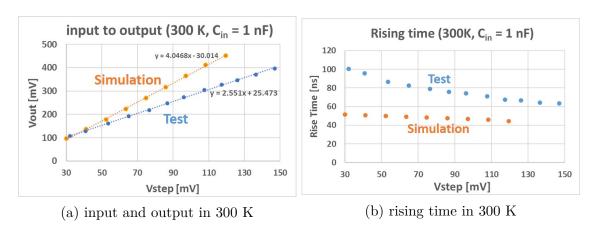

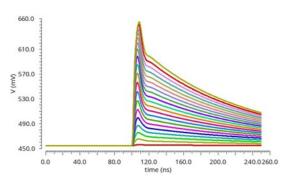

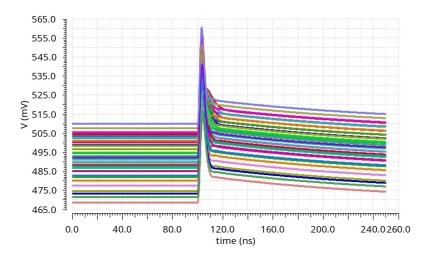

| 3.37 | Waveform from VFE in Test-Chip2                                |

| 3.38 | Amplitude and rising time measurement                          |

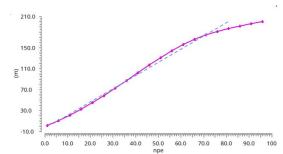

| 3.39 | Amplitude and rising time measurement in 77K                   |

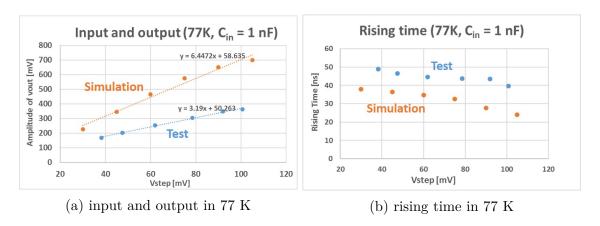

| 4.1  | Architecture of one channel                                    |

| 4.2  | Transistor-level schematics of the pre-amplifier               |

| 4.3  | Layout of front-end                                            |

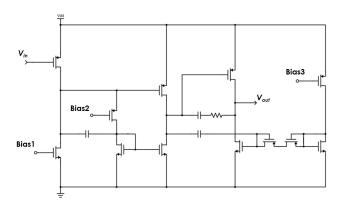

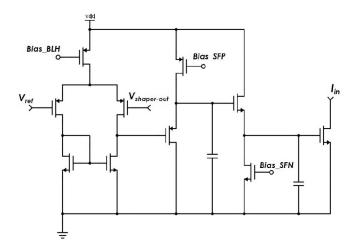

| 4.4  | Schematic of Fast Shaper                                       |

| 4.5  | Schematic of Slow Shaper                                       |

| 4.6  | Transistor level design of shaper core                         |

| 4.7  | Transistor level design of baseline holder                     |

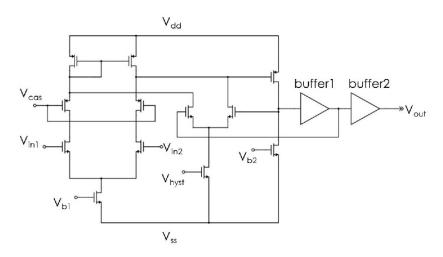

| 4.8  | Schematic of the discriminator                                 |

| 4.9  | Multi-buffer TDC block diagram                                 |

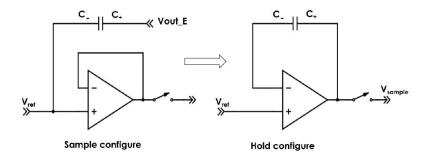

| 4.10 | The principle of S&H mode                                      |

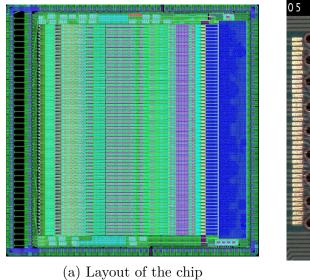

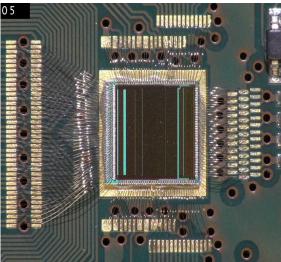

| 4.11 | Layout and silicon chip on test board                          |

| 4.12 | Adjustable Gains Characterisation                              |

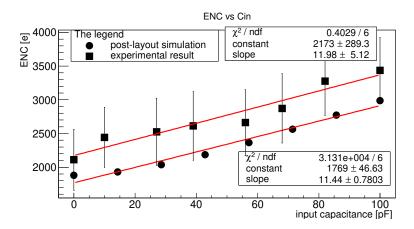

| 4.13 | Timing branch noise versus input capacitance                   |

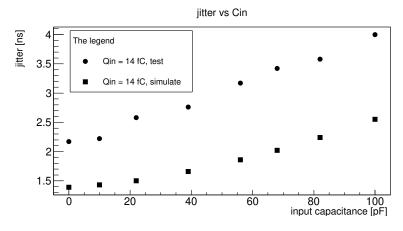

| 4.14 | Timing resolution test in T-branch                             |

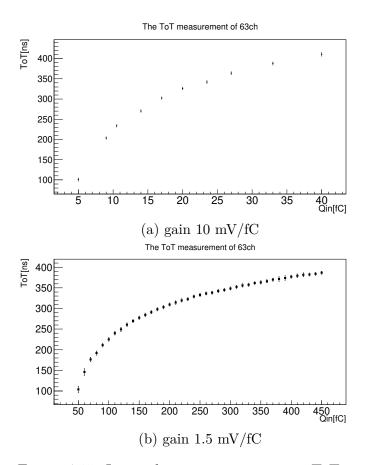

| 4.15 | Input charge measurement in ToT mode                           |

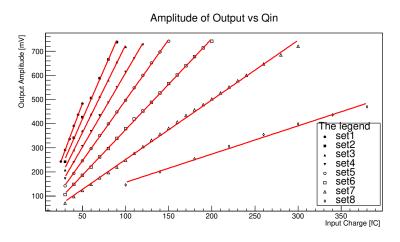

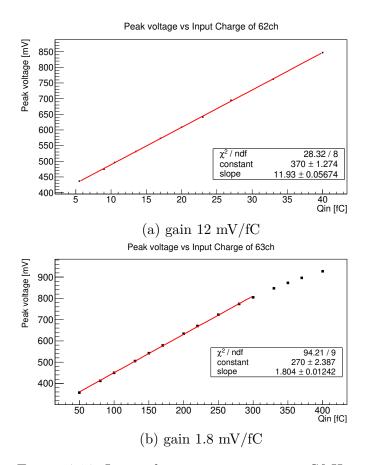

| 4.16 | Input charge measurement in S&H mode                           |

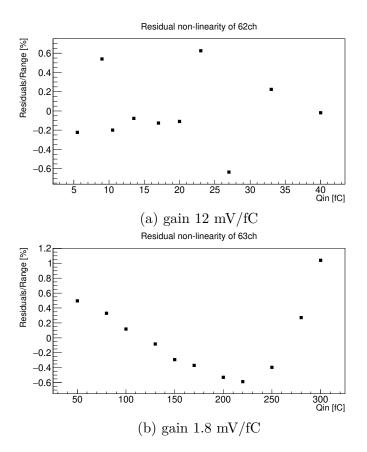

| 4.17 | Residuals in S&H linear fit                                    |

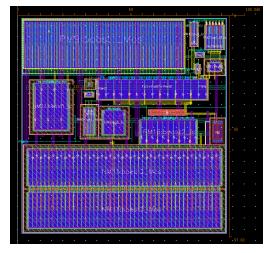

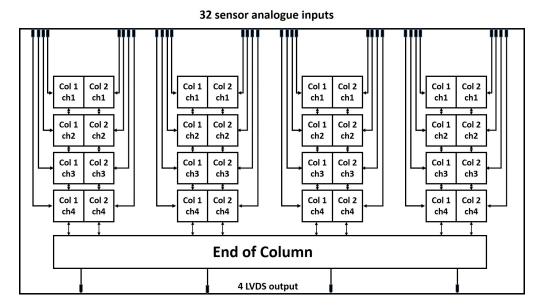

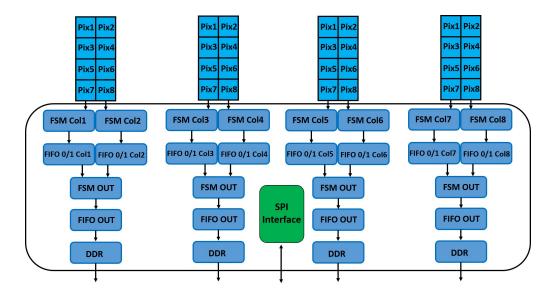

| 5.1  | Architecture of full chip                                      |

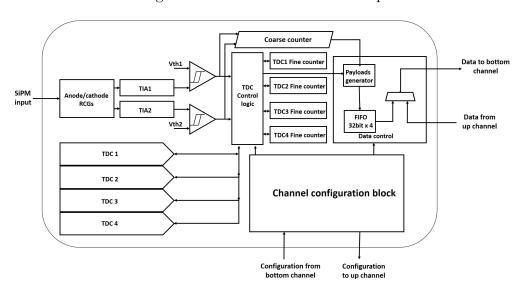

| 5.2  | Architecture of each readout pixel                             |

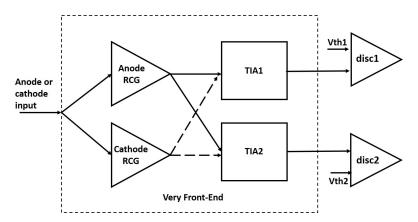

| 5.3  | Architecture of very front end                                 |

| 5.4  | Schematic of complementary VFE                                 |

| 5.5  | ALCOR RCGs Bias circuits integrated in the End of Column part  |

|      | of the chip                                                    |

| 5.6  | Programmable gain in output stage of ALCOR VFE                 |

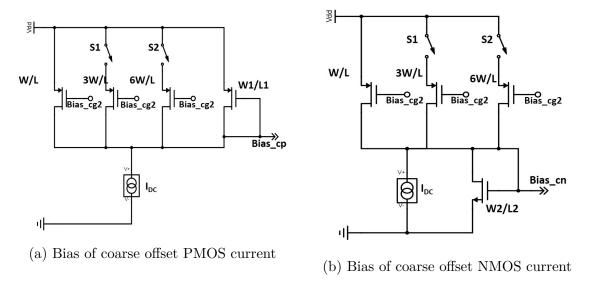

| 5.7  | Bias circuits of coarse offset to keep baseline constant       |

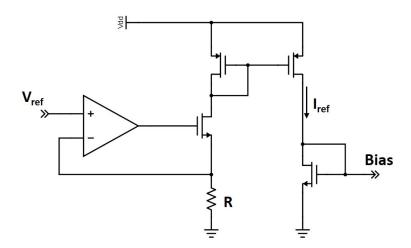

| 5.8  | Reference current generation circuit and bias distribution     |

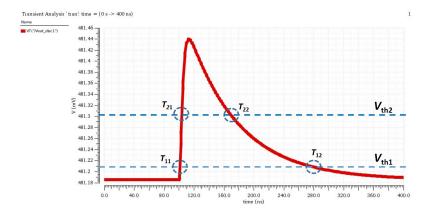

| 5.9  | Working principle of dual threshold voltages                   |

|      | Layout design of very front end                                |

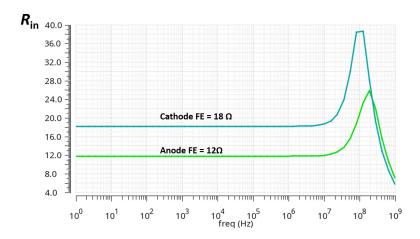

|      | ALCOR input impedance simulation $(C_{\rm in}=0)$              |

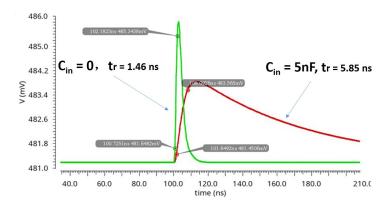

|      | Bandwidth simulation of very front end circuit                 |

|      | The linear dynamic range simulation with maximum gain setting  |

|      | (300K)                                                         |

| 5.14 | The linear dynamic range simulation with minimum gain setting  |

|      | (300K)                                                         |

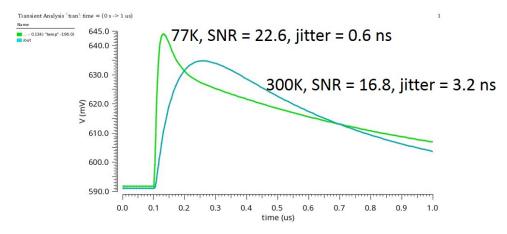

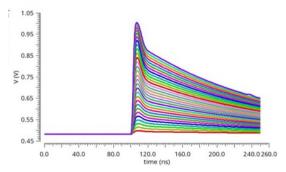

| 5.15 | Output waveforms of the different common gate current and gain |

|      | settings                                                       |

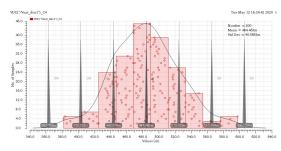

| 5.16 | Corner and Monte Carlo simulation of the very front end output       |     |

|------|----------------------------------------------------------------------|-----|

|      | baseline                                                             | 101 |

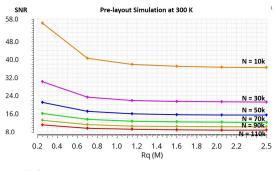

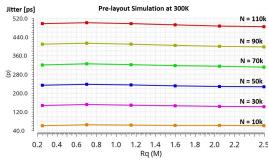

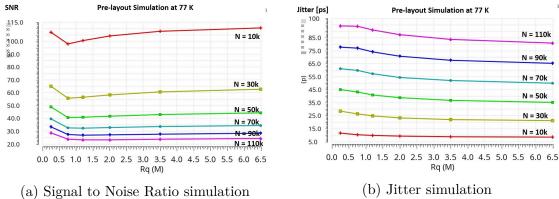

| 5.17 | The SNR and jitter of very front end with different number of sub-   |     |

|      | cells (N) and quenching resistance at 300K, single photon signal and |     |

|      | anode signal readout                                                 | 101 |

| 5.18 | The SNR and jitter of very front end with different number of sub-   |     |

|      | cells (N) and quenching resistance at 77K, single photon signal and  |     |

|      | anode signal readout                                                 | 102 |

|      | Discriminator schematic in ALCOR                                     | 103 |

| 5.20 | Working principle of ALCOR TDC                                       | 104 |

| 5.21 | ALCOR TDC simulation                                                 | 105 |

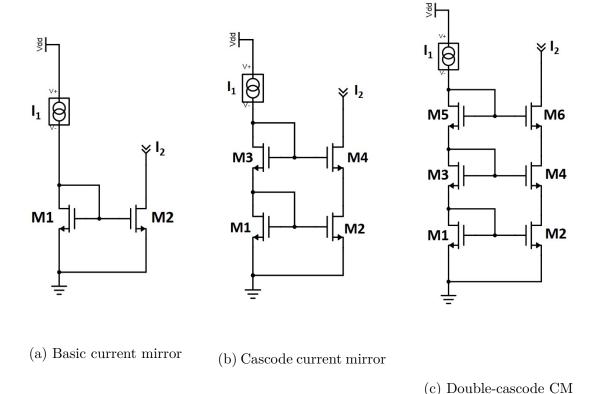

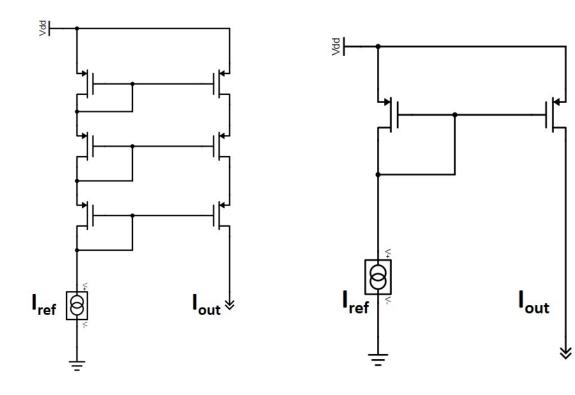

| 5.22 | Different structures of current mirror                               | 106 |

| 5.23 | Current ramp source in TDC of the ASIC in chapter 4 and ALCOR        | 107 |

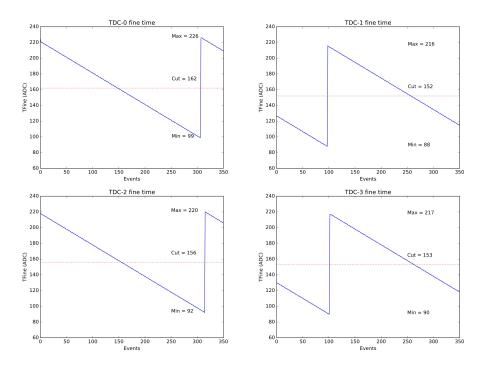

| 5.24 | Test pulse scan of the four TDCs, the TDCs are configured with time  |     |

|      | bin of 25 ps                                                         | 108 |

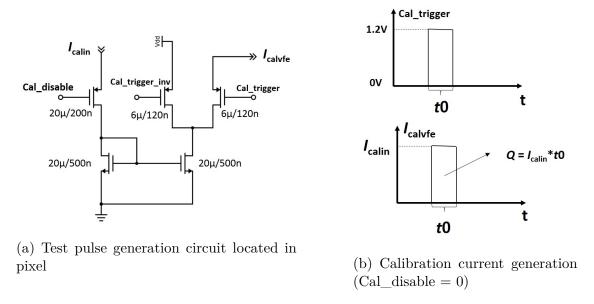

| 5.25 | The calibration circuit                                              | 108 |

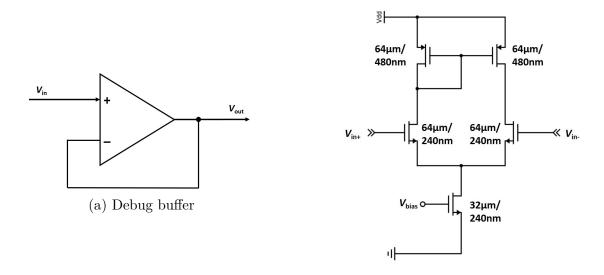

| 5.26 | Buffer used to debug the output of ALCOR VFE                         | 109 |

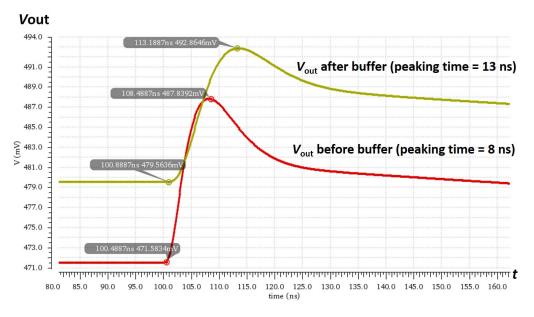

| 5.27 | The input and output simulation waveforms of the debug buffer, with  |     |

|      | $50\Omega$ and 18pF output load to model the oscilloscope            | 110 |

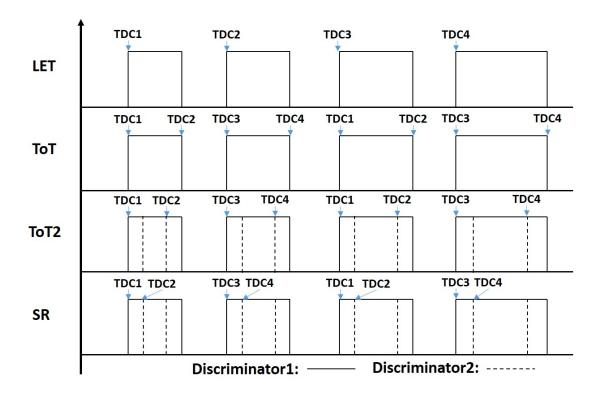

| 5.28 | TDCs distribution with different working modes                       | 111 |

| 5.29 | Format of event payload and status word                              | 111 |

| 5.30 | Data transmission in ALCOR                                           | 112 |

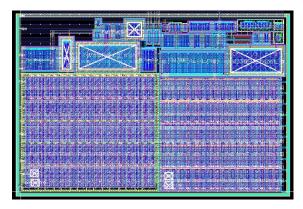

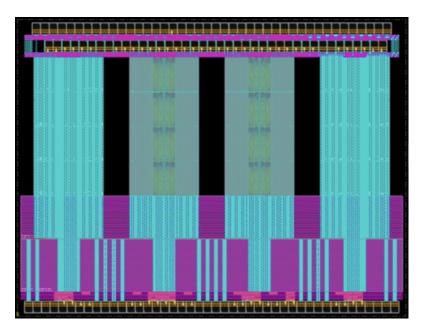

| 5.31 | Lavout view of ALCOR                                                 | 113 |

## Chapter 1

### Introduction

Silicon photon-multiplier (SiPM) is a novel solid-state photon sensor with single-photon detection capability. A SiPM consists of an array of Single Photon Avalanche Diodes (SPADs) working in Geiger mode and summing the output in one collection electrode. The technology and design of the single cell defines the sensor's characteristics in terms of photon sensitivity (quantum efficiency), gain and operation voltage, whereas the number of cells in the array impact the dynamic range of the device.

Compared to more conventional photon sensors like PMTs, SiPMs have additional advantages in terms of compactness and robustness, insensitivity to magnetic fields, low bias voltage, which make SiPMs up-and-coming candidates substitute these conventional sensors and also to develop new applications in different fields like nuclear and high energy physics experiments, nuclear medicine, distance measurement.

In this chapter, the fundamental physics of the SiPM is firstly introduced, along with the comparison with other families of photon sensors. Thereafter, the motivation of each dedicated project is introduced, and the outline of this thesis is depicted.

### 1.1 SiPM Principles and Characteristics

### 1.1.1 SiPM Operating Principles

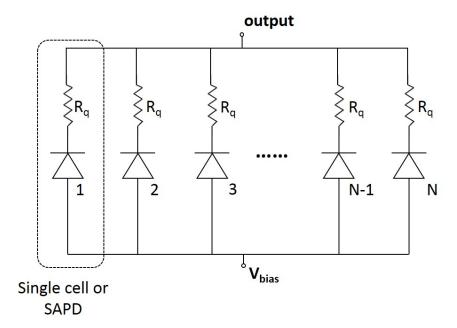

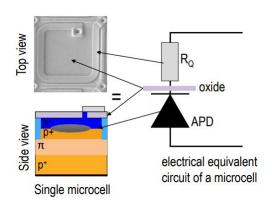

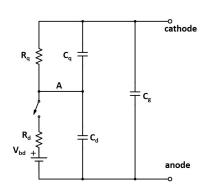

The Silicon Photo-multiplier (SiPM, also multi-pixel photon counter, MPPC) is a solid-state photon sensor consisting of a parallel array of independent cells, each of them is equal and made of a PN junction operating in Geiger mode, in series with a resistor (called quenching resistor,  $R_q$ ); all micro cells are connected to a common output.

Figure 1.1 is a simplified illustration of the SiPM structure. Each microcell is sensitive to incident photons and the photon detection efficiency (PDE) peaks at

Figure 1.1: SiPM Structure.

a given wavelength, which is a strong function of technology parameters and the SPAD design. The incident photon creates an electron-hole pair and the geiger mode operation causes an avalanche pulse which is only mitigated by the series connection of a quenching resistor, which causes a dynamic drop of the biasing voltage.

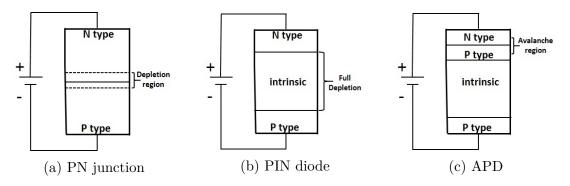

In order to have a better understanding of the working principle of each cell, figure 1.2 shows the main types of diodes in parallel: PN junction, PIN (P: p-type, I: intrinsic, N: n-type) diode, Avalanche Photon Diode (APD).

A PN junction (figure 1.2a) is the simplest diode and ranks also amongst the most basic embodiments of a semiconductor detector. It is formed by two homogeneous regions of p- and n-type semiconductor material [76]. The gradient of electrons and holes in two types of material causes the diffusion process (electrons from n to p, holes from p to n), which creates the depletion region.

The depletion region is an attractive medium for the photon detection and it can be enlarged by applying the reversely biased voltage. The interaction with an incident photon creates electron-hole pair in medium volume, under the mechanisms of photoelectric absorption, Compton scattering or pair production [55]. The free charge drifts under the electric field of the depletion region and is collected by the electrodes, where the instantaneous current signal induced by moving charged particles can be calculated by Shockley–Ramo theorem [48].

The two drawbacks of PN juction for photon detection are limited depletion

volume and unity gain.

In a PIN diode structure, shown in figure 1.2b, a much thicker layer of intrinsic semiconductor is added between the two layers of n- and p-type material, resulting in a much wider depletion region (sensitive volume). But the PIN diode is still not able to detection the low flux light because there is no amplification process.

Compared with the PIN, an APD contains an additional p-type layer between the n-type and intrinsic layer, providing a high doping gradient at this p-n junction. The bias voltage, therefore, creates a strong electrical field in this region. Electrons or holes generated by absorption of incident photons drift to this region where they could gain enough energy to make secondary multiplication.

Figure 1.2: Simplified schematic structures of different types of photon diodes.

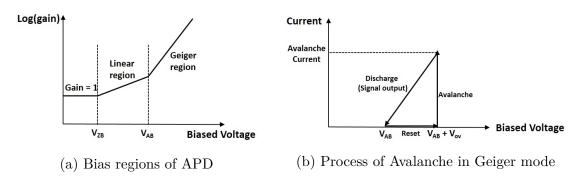

Several working regimes exist that vary depending on the applied bias voltage on APD. The relation of Bias Voltage and the multiplication process (gain) depicts in figure 1.3a [61]:

- At low electric field, the bias voltage less than "Zener Breakdown" voltage  $(V_{ZB})$ , no secondary carriers are created, similar to PIN diode.

- When the bias voltage is over than "Zener Breakdown" voltage but less than the "Avalanche Breakdown" voltage  $(V_{AB})$ , only the electrons can gain enough energy and generate secondary electron-hole pairs, thus this avalanche process stops when electrons leave the avalanche region, creating an amplified signal that will be proportional to the primary ionization signal. The gain can typically reach values in the order of  $10^3$ .

- After the bias voltage exceeds the "Avalanche Breakdown" (Geiger) voltage, both the electrons and holes can create avalanche multiplication, resulting in the self-sustaining avalanche process. The gain can be as high as  $10^5$   $10^6$ , providing the ability to detect single photon.

The micro cell of the SiPM is composed of Geiger mode APD in series with a passive resistor  $(R_q)$ , as shown in figure 1.1, and figure 1.3b shows the three main processes of operating principle for single photon detection:

- Avalanche: the SPAD is biased with the voltage higher than  $V_{AB}$ , usually several Volts higher than  $V_{AB}$ , called Over Voltage ( $V_{OV}$ ). In this condition, the SPAD is very sensitive to the incident single photon, which could generate a primary electron-hole pair and then start the avalanche process. It should be mentioned that the avalanche current value is a constant value, which is not related to the initial amount of charge, and consequently the total charge of the single SPAD is not proportional to the number of contemporary incident photons.

- Discharge: This process can be also called as "Quenching", the avalanche current flows across the quenching resistor and creates a sufficiently large drop on the bias voltage of the diode, consequently stopping the avalanche.

- Reset: during this "Recharge" phase, the external bias supply will recharge the junction capacitance through the quenching resistor. The diode is ready again to detect a new incident photon.

Figure 1.3: APD Bias regions and avalanche in Geiger mode.

A SiPM integrates up to hundreds to thousands of SPADs (each one in series with a quenching resistor), where all the cells are summed in a common output. More detailed structure views is shown in figure 1.4a. The analogue amplitude of the superimposed signal from multiple fired cells can provide the information on the number of detected photons: the dynamic range is defined by the number of sub-cells in the SiPM. Figure 1.4b shows an example of a SiPM by Hamamatsu company which is optimized for PET imaging, with the single pitch of 50  $\mu$ m and the optional number of cells.

The operation of the SiPM in Geiger mode gives it single-photon sensitivity and fast timing response. Table 1.1 shows the comparison among different photon sensors.

(b) SiPM product example [47]

(a) Structure views of SiPM cell [72]

Figure 1.4: 2D structure of SiPM and the product example.

|                         | PIN       | APD         | SiPM           | PMT      |

|-------------------------|-----------|-------------|----------------|----------|

| Gain                    | 1         | $10^{2}$    | $10^{6}$       | $10^{6}$ |

| Operation voltage       | 5 V       | 100 - 500 V | 20 - 60 V      | 1000 V   |

| Large area              | No        | No          | Yes (scalable) | Yes      |

| Noise                   | Low       | Medium      | Medium         | Low      |

| Uniformity              | Excellent | Good        | Excellent      | Good     |

| Time response           | Fast      | Fast        | Very fast      | Fast     |

| Energy resolution       | High      | Medium      | High           | High     |

| Temperature sensitivity | Low       | High        | Medium         | Low      |

| Magnetic resist         | Yes       | Yes         | Yes            | No       |

| Compact                 | Yes       | Yes         | Yes            | No       |

Table 1.1: Properties comparison of different Photon sensors.

#### 1.1.2 SiPM Properties at Room and Cryogenic temperature

As the latest advance of solid-state photon sensors, SiPMs have been replacing conventional PMTs in many fields. Indeed, the advantage of SiPM stems both from its working principle and also due to the fact that initial drawbacks like high dark current and cross talk are now substantially reduced with rapid technology development. In this section, the basic properties of SiPMs will be introduced. In respect to the state of the art knowledge of SiPM technology and applications at commercial temperature range (-40 up to 125 °C), we extend the analysis to the operation of SiPMs at cryogenic temperatures.

#### Gain

As described before, the charge released in the avalanche process of the SPAD is acting on the PN junction. Thus the gain of single-photon detection can be written as:

$$Gain = \frac{C_d \cdot (V_{Bias} - V_{AB})}{e} = \frac{C_d \cdot V_{OV}}{e}$$

(1.1)

where  $C_d$  is the capacitance of the diode depletion region, e is the elementary charge, and  $V_{Bias}$ ,  $V_{AB}$ , and  $V_{OV}$  are bias voltage on the diode, avalanche breakdown voltage, and over-voltage respectively. The gain of SiPM single cell is typically in the order of  $10^6$ , while process and statistical local variations can impact the uniformity of the gain within the pixel matrix.

From equation (1.1), we can obtain the equation below to study the temperature dependence if we assume a constant bias voltage.

$$\frac{\partial Gain}{\partial T} = \frac{\partial C_d}{\partial T} - \frac{\partial V_{AB}}{\partial T} \tag{1.2}$$

Actually, the breakdown voltage is more sensitive to temperature than junction capacitance. In paper [70], the authors characterized three products manufactured respectively by FBK, Hamamatsu and SensL. When the junction temperature spans from - 40 to + 40 °C, the breakdown voltage variation is about 8% while the junction capacitance only about 1%. Consequently, a temperature-compensated high-voltage power supply needs to be adopted for large temperature range applications.

In paper [5], SiPM properties were measured with the temperature ranges from 40 K to 300 K, with similar trend on the breakdown voltage.

#### Timing Response

The good time resolution of SiPMs makes them a good candidate for fast timing systems where a very good time measurement is needed, like PET and LIDAR. The timing jitter of the SiPM arises from the process of photon-volume interaction and avalanche. The main contributions to this effect can be categorized into two parts [93]:

- Signal Fluctuations: Finite Light Pulse Width Effect, Avalanche Buildup Process, Minor Carrier Diffusion for Non-peaking Wavelength in PDE, Noise Source in Passive Quenching Elements, Thermal Noise Pile-up Effects, Detector Leakage Current. These effects can be summarized as the stochastic parameters in each process and the noise sources, which can be written as:  $\sigma_{fluc}$ .

- Signal Slope: Avalanche Propagation Process, Parasitic Capacitor, Pixel Uniformity, can be written as: *Slope*.

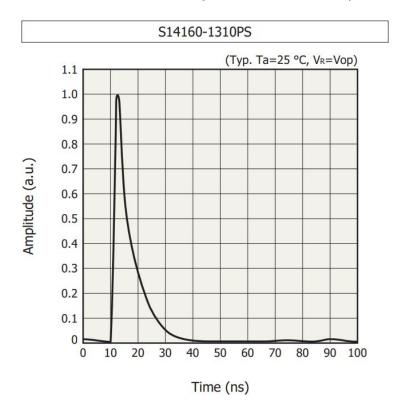

Whenever the time stamp of the photodetector module is obtained with a frontend electronics implementing a leading-edge threshold, the time resolution can be determined by:  $\sigma_{fluc}/Slope$ . Thereby, since the signal slope is determined also by the number of detected photon in the same time, the timing characteristics of the SiPM are usually defined in terms of single-photon time resolution. An example output waveform for a single photon event (S14160-1310PS product from Hamamatsu) is shown in figure 1.5. The typical rising time of single-photon signal is in order of nanosecond, and the falling time constants is O(20-100 ns).

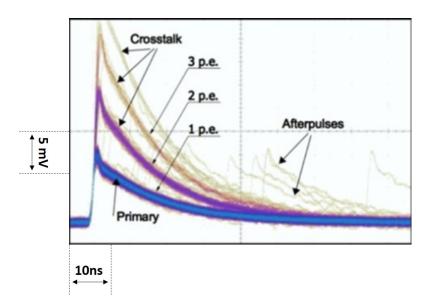

Figure 1.5: SiPM output example [47].

In the avalanche process, the diode discharges after receiving a photon, its potential has a drop of over-voltage  $(V_{OV})$  and releases the amount of charge defined by equation (1.1). This process has a time constant calculated by equation (1.3) which impacts the intrinsic time resolution of the SPAD.

$$t_{rise} = (C_d + C_q) \cdot (R_q || R_d) \tag{1.3}$$

Where  $C_d$  and  $R_d$  are the capacitance and resistance of the photon diode, and  $C_q$  and  $R_q$  are parasitic capacitance and resistance of quenching resistor, respectively.

The timing resolution of SiPM is also related to the number of cells, since the passive SPADs have the loading effects to the fired ones.

The conventional SiPMs have the single-photon time resolution of 100 ps - 200 ps [24].

This value is related to the number of sub-cells in SiPM and size of the matrix. In one hand, a higher number of cells typically increases the total resistance of the connection path between the quenching resistor and the low-impedance collection electrode. On the other hand, the size of the matrix is proportional to the total parasitic capacitance in parallel with the fired cell.

The Hamamatsu MPPC s10632-11 (1x1 mm2) series has an intrinsic single-photon resolution of about 160ps FWHM, while the FWHM of the MPPC S10632-33 (3x3 mm2) quotes more than 600ps [47]. Besides, the single-cell (SPAD) resolution has the theoretical performance of the order of 10 ps [95] and was reported a resolution of about 40 ps in experimental result [81].

#### Photon Detection Efficiency

The photon detection efficiency (PDE) is the statistical probability that a signal is generated by an incoming photon. The relation can be written as:

$$PDE = QE * P_{av} * Fill factor (1.4)$$

Where:

- QE: Quantum efficiency, function of photon wavelength  $(\lambda)$ , expresses the probability for a photon with given energy  $(E = hc/\lambda)$  to create an electronhole pair inside the pixel. This efficiency is related to the interaction mechanism between photon and silicon [55].

- $P_{av}$ : Avalanche initiation probability, the probability of the photon-created carrier to trigger the avalanche process, which is a function of the bias voltage.

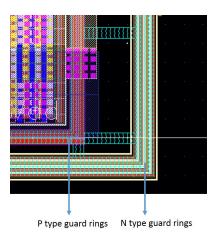

- Fill factor: the ratio of photon sensitive area to the total area. The fill factor is generally range from 25% to 75% depending on sub-cell and pitch layout: insensitive area could result from the passive quenching resistance, signal routing lines and guard ring structures. A larger size of the pixel could increase the fill factor but will also decrease the pixel density.

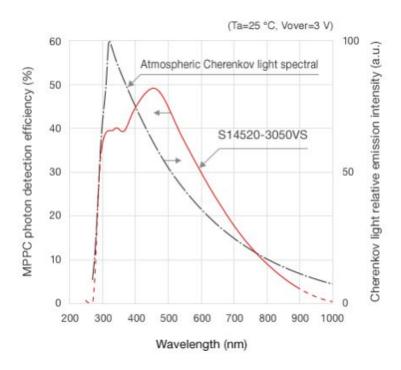

The PDE of a SiPM at peak sensitivity wavelength usually ranges from 20% to 50%. Commercial SiPM manufacturers could provide products with different properties. PDE is a key parameter to take into account, and this parameter can be optimized for specific applications. As an example, figure 1.6 shows the product S14520 series made by Hamamatsu featuring high UV sensitivity suitable for Cherenkov light detection.

Figure 1.6: PDE optimized for Cherenkov telescope array [47].

#### **Dark Count Rate**

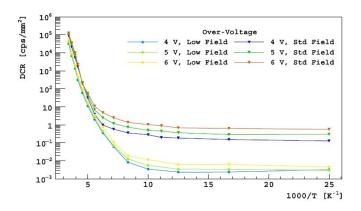

Dark Count Rate (DCR) evaluates the probability of avalanche process generated by thermal generation or tunnelling effect instead of a real photon event. The dark count rate is the main limitation for SiPM in low flux light application, especially for single-photon detection. Signal outputs happen even if the SiPM operates in complete dark, most of them corresponding to single-photon amplitude, thus called dark count. DCR is defined by the dark count number divided by the total area, usually with the unit of  $Hz/mm^2$ . In operation, DRC mainly depends on temperature and breakdown voltage. The temperature dependence can be expressed as [71]:

$$DCR \propto T^2 \cdot exp(-\frac{E_c - E_T}{kT}) \tag{1.5}$$

DCR is also related to crystal parameter like lattice defect, which could intermediate energy levels and thus enhance the excitation [98]. With the development of wafer and material process, the DCR provided by commercial companies has been sufficiently reduced for the last few years. To date, S13360 series from Hamamastu have a typical DRC about  $55 \ kHz/mm^2$  [47].

Figure 1.7 shows an example of DCR as a function of the temperature for

different values of bias voltage. The NUV-HD-LF SiPM produced by FBK show a DCR that can be as low as  $0.01Hz/mm^2$  [5] at cryogenic temperatures.

Figure 1.7: Dark count rate as a function of temperature for different over voltages [5].

#### Cross Talk and After pulse

Similarly to DCR, both the cross-talk and after pulse can be considered as "correlated noise". Figure 1.8 shows the output signal waveform of the single photon and associated crosstalk and afterpulse events.

Cross talk is the effect that avalanche process causes to adjacent pixels and can be categorized by optical cross-talk and electrical cross-talk.

Optical cross talk origins the fact that every 10<sup>5</sup> carriers can generate about three photons with the energy over the silicon bandgap (1.14 eV) during the avalanche process. These secondary photons can travel to the neighbouring cell and produce a new avalanche.

Electrical cross talk is produced with the reason that avalanche carriers have the probability of going through the boundary of the fired pixel and reaching a neighbouring SPAD, causing new avalanche processes [53].

Depending on the principle, the cross talk signal has, therefore, a correlated time to the initial signal with a delay (order of few ns) which acts as the signal superposition. Besides, cross-talk is related to overvoltage, and pixel size since the overvoltage directly impacts the gain of APD corresponding to the number of avalanche carriers, and the smaller size of the pixel can enhance the ability of photons or carriers to reach the neighbouring pixels. Cross-talk can be efficiently reduced improving the manufacturing process, like implementing the optical trenches around each SiPM pixel and block the photons travelling to close pixels [46].

Figure 1.8: The cross talk and after pulse.

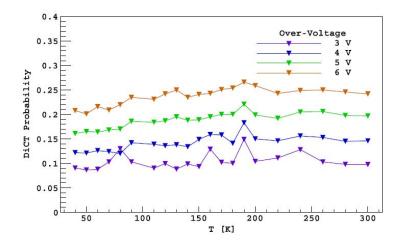

Cross talk doesn't show a strong dependence on temperature. The experimental result is shown in figure 1.9, where the NUV-HD-LF SiPM fabricated by FBK is characterized at the temperature range between 40K and 300K.

Figure 1.9: Cross talk characterization of SiPM by FBK, from 300 K to 40 K[5].

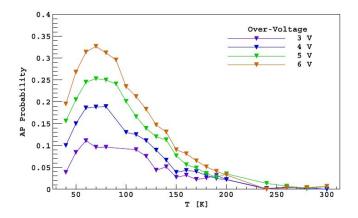

After pulse is caused by carriers trapped by the lattice during an avalanche and with some probability to be released after a particular time, usually during the recovery time. Therefore, it can generate pulses (second avalanche) after the peak of the real event, but smaller in amplitude since the electric field of the pixel is not

fully recovered.

After pulse depends on both the overvoltage and the temperature. A higher overvoltage could increase the number of avalanche carriers (gain) and thus enhance the probability of a carrier to be trapped.

Temperature dependence of After pulse is due to two effects: the trapping constant increases at low temperature and thus enhance the probability of release of carrier to cause the After-Pulse event; Quenching resistance varies with the temperature, and a longer recharge time (caused by growing quenching resistance) can suppress the After-Pulse effect [73].

Figure 1.10 shows an experimental result:

Figure 1.10: After pulse as a function of temperature and over voltage. [5]

#### Dynamic Range

As mentioned before, microcell (SPAD) of SiPM works like a digital counter since the pixel can not have a response to a new photon during the avalanche process. Therefore, the number of photons can only be reflected by the number of fired pixels. The number of fired pixels  $(N_{fired})$  is related to the number of pixels  $(N_{pixel})$ , number of incident photons  $(N_{incident})$  and PDE, with the following equation [15]:

$$N_{fired} = N_{pixel} \cdot (1 - exp \frac{N_{incident} \cdot PDE}{N_{pixel}})$$

(1.6)

This is, however, valid only if the following condition is observed:

$$PDE \cdot N_{incident} << N_{pixel}$$

The equation can be approximated as:

$$N_{fired} = N_{incident} \cdot PDE \tag{1.7}$$

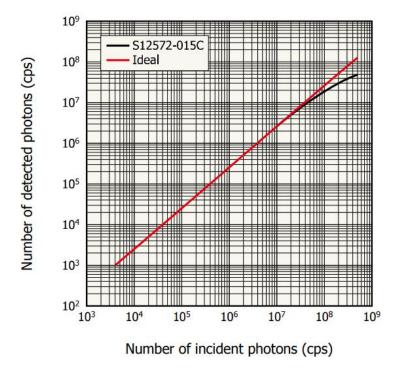

The dynamic range of SiPM is limited by the number of sub-cells, and the worse inlinearity occurs when the number of incident photon approximates the total number of sub-cells.

Figure 1.11 shows the example of S12572-015C from Hamamatsu [46].

Figure 1.11: Dynamic range measurement compared with ideal response.

#### 1.1.3 State of the art: SiPM products

Owing both to its working principle and relevant progress in the manufacturing technology, SiPMs present nowadays excellent performances for light detection and they have been applied in many different fields.

In general, different properties of SiPM can show a trade-off relation. Such as improving the overvoltage have the advantages of larger gain and better PDE and time response but could worsen the dark count rate, cross-talk and after pulse. Similarly, a large number of total pixels improves the dynamic range but increases dark count (DCR·area) and degrades the time response. Therefore, commercial companies typically provide a wide range of products for different applications.

Products like MPPC S14160 series of Hamamatsu, MICROFC Series of SensL are optimized for low dark, high timing resolution, suitable for the applications such like PET or radiation monitors; MPPC S13720 series of Hamamatsu and MICROR series of SensL are optimized for high PDE in near-infrared, which can be used to measure distance (LiDAR). MPPC S13370 series of Hamamatsu are featured with high efficiency in detecting vacuum ultraviolet (VUV), expecting for detecting scintillation light of liquid xenon (175 nm, PDE = 25%) and liquid argon (120 nm, PDE = 15%). MPPC S14520 series have good UV sensitivity suitable for Cherenkov light detection (mentioned in the last section); NUV-HD-Cryo SiPM from FBK is optimized for cryogenic temperature operations. [47][91][64]

Table 1.2 shows the parameters of some off-the-shelf SiPM products from commercial companies.

| Label | Area              | Pitch              | Gain               | DCR                   | Cross | Peak $\lambda$ | $V_{br} + V_{ov}$ |

|-------|-------------------|--------------------|--------------------|-----------------------|-------|----------------|-------------------|

| Laber | $[\mathrm{mm}^2]$ | $[\mu \mathrm{m}]$ | Gain               | $[\mathrm{kHz/mm^2}]$ | -talk | and PDE        | [V]               |

| [1]   | 3 x 3             | 50                 | $2.5 \cdot 10^{6}$ | 167                   | 7%    | 50%/450  nm    | 38 + 2.7          |

| [2]   | 3 x 3             | 50                 | $1.7 \cdot 10^{6}$ | 56                    | 3%    | 40%/450  nm    | 53 + 3            |

| [3]   | 3 x 3             | 50                 | $3.6 \cdot 10^6$   | 178                   | 5%    | 40%/600  nm    | 42 + 5            |

| [4]   | 3 x 3             | 25                 | $1.1 \cdot 10^{6}$ | 296                   | 5%    | 22%/660  nm,   | 57 + 7            |

| [=]   | OAO               | 20                 |                    | 250                   |       | 7%/905  nm     | 01   1            |

| [5]   | $1 \times 1$      | 35                 | $1.7 \cdot 10^6$   | 3800                  | 43%   | 9.1%/905  nm   | 25 + 7            |

| [6]   | 3 x 3             | 20                 | $1 \cdot 10^{6}$   | 33                    | 3%    | 24%/420  nm    | 24.5 + 2.5        |

| [7]   | 6 x 6             | 35                 | $1 \cdot 10^{6}$   | 150                   | 25%   | 50%/420  nm    | 24.5 + 6          |

| [8]   | 4 x 4             | 40                 | $3 \cdot 10^{6}$   | 100                   | 25%   | 43%/420  nm    | 26 + 6            |

Table 1.2: List of SiPM products.

With the manufacturers and Series:

- [1] Hamamatsu MPPC S14160-3050HS

- [2] Hamamatsu MPPC S13360-3050PE

- [3] Hamamatsu MPPC S14420-3050MG

- [4] Hamamatsu MPPC S13720

- [5] SensL MICRORB-10035

- [6] SensL MICROFC-30020

- [7] SensL MICROFJ-60035

- [8] FBK ASD-NUV4S-P

### 1.2 SiPM applications

#### 1.2.1 SiPM in particle and nuclear physics

Calorimetry is the dominant field of the SiPMs application in particle physics. The pioneer is CALICE Analog Hadron Calorimeter (AHCAL) prototype [7], completed in the year 2007, which is aimed to study hadron showers and test the concept of particle flow, and also expected to study the performance and reliability of SiPMs readout in a large scale. In the AHCAL project, in total 7608 SiPMs, made by MEPhI/PULSAR, each works with a scintillator tile and provide necessarily high granularity detection modules for events reconstruction [94]. The Tokai-to-Kamioka (T2K) [4] is a baseline neutrino oscillation experiment and the first physics experiment to adopt large scale of SiPMs.

Silicon photomultipliers have been proposed for a wide range of future detectors for dark matter and neutrino experiments using noble elements. Table 1.3 lists the status and main characteristics of the current and planned developments in this field.

| Project            | Application                 | Status       | Fiducial Volume | SiPM area   |

|--------------------|-----------------------------|--------------|-----------------|-------------|

| DarkSide-20k [3]   | DM                          | Design       | LAr 20 t        | $20 \ m^2$  |

| DARWIN [1]         | DM                          | Design       | LXe, 50 t       | $8 m^2$     |

| Proto-DUNE-SP [14] | $\nu$ oscillation           | Operation    | LAr, 77 t       |             |

| DUNE [37]          | $\nu$ oscillation           | Concept      | LAr, 17,000 t   |             |

| nEXO [36]          | $\beta \beta \text{ decay}$ | Design       | LXe 5 t         | $5 m^2$     |

| MEG-2 [69]         | $\mu \to e\gamma$           | Construction | LXe             | $0.6 \ m^2$ |

Table 1.3: SiPM applied in liquid Xenon (LXe) or Argon (LAr) detectors.

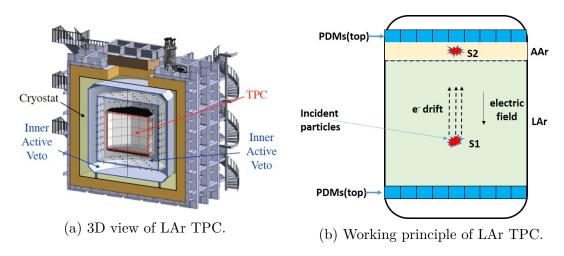

Figure 1.12 shows the basic information of LAr TPC detection equipment applied in Darkside-20k project for WIMP (Weakly Interacting Massive Particles, one possibility of dark matter) search, and it shares the similar working principle with detectors summarized in table 1.3.

As shown in figure 1.12b, the incident particles make interactions with the liquid Argon atoms, creating the scintillation light (called S1 signal) with a wavelength of 128 nm, and ionizing free electrons. The S1 signal will be detected by the Photon Detection Module (abbreviation with PDM, applying SiPM as the photon sensor) mounted in both top and bottom of the TPC. The electrons will drift under the applied electric field, arrive at the air argon region and create the second scintillation light called S2 signal. The S2 signal will be detected by SiPMs on the top (anode) of the TPC.

S1 signal can be used for energy information extraction and Pulse Shape Discrimination (PSD). S2 signal is proportional to the initial ionization thus can be

Figure 1.12: LAr TPC equipment and working principle in Darkside-20k project.

used for energy extraction of the event. The distribution of S2 at top PDMs reveals the horizontal coordinate of the initial event, and the drift time of S2 (time difference between S1 and S2) can be used to exact the vertical position. Furthermore, accurate time information of S1 from both top and bottom PDMs can be also used for reconstruction of 3D position of the initial event.

#### 1.2.2 SiPM in medical imaging

SiPM is an excellent candidate for nuclear medical techniques, mainly because of its high gain, fast response, low operating voltage, insensitivity to magnetic field and compactness. The applications of SiPM in nuclear medical, mainly PET (Positron Emission Tomography) and SPECT (Single-photon emission computed tomography), are reviewed in the following contents.

#### PET

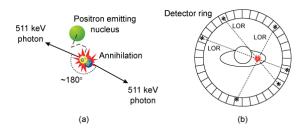

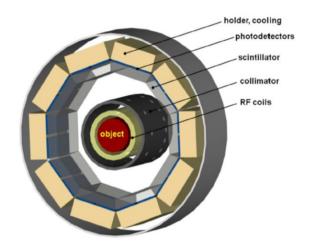

PET is able to provide metabolic and functional information by detecting gamma rays emitted by radio-tracers with the radioactive atom emitting positrons. Figure 1.13 illustrates the working principle and a simplified design of a PET detector ring.

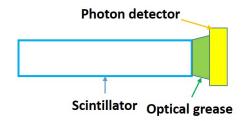

In a typical embodiment, each photodetector module of the detector ring comprises the front-end readout electronics, the photosensor (e.g. SiPM) and a scintillating crystal that converts the 511 keV photon into visible light, detectable by the SiPM. The simplified representation in figure 1.14 is called scintillator detector, which consists of scintillator material, optical grease and the photon sensor. The scintillator material converts incident particles or radiation into a large number of

Figure 1.13: Positron Emission Tomography working principle [40].

low-energy photons, the photon sensor converts the optical signal into electrical signal, and the optical grease works to improve the coupling between the scintillator material and the photon sensor (for solid state scintillator).

Figure 1.14: Structure of the typical scintillator detector.

The nuclear reaction shown by equation 1.8 can happen in proton-rich nuclei: one proton decays to a neutron, a positron and a neutrino, which is so-called  $\beta^+$  decay.

$$p \to n + e^+ + v_e \tag{1.8}$$

The radioisotopes like <sup>11</sup>C, <sup>31</sup>N, <sup>15</sup>O, and <sup>18</sup>F can work as the radio-tracers and be injected to the patient body. The PET scanner detects and records the positron emission events and reconstructs the accumulation information of the radio-pharmaceutical in order to reveal the properties of the living tissues.

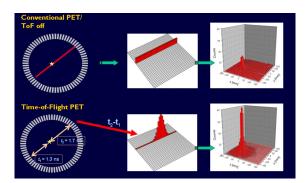

The released positron will soon reach approximately its thermal energy and annihilates with an electron, creating a pair of gamma rays with an energy of 511 keV each in the opposite direction. The PET sensor can detect the two events and build a Line of Response (LOR), which indicates the line along which the annihilation occurred. A given amount of LORs is used to reconstruct the positron emission zone. Whenever made possible by the photodetector and associated electronics, time of flight (ToF) information of each event is recorded to discard the background and noise, which improves sufficiently the reconstructed resolution. The principle of resolution improved by ToF information is shown in figure 1.15.

Figure 1.15: Time of Flight information to boost the reconstruction quality [92].

In a ToF measurement, Coincidence Time Resolution (CTR) in FWHM is the crucial parameter to evaluate the ToF-PET system. To date, clinical ToF-PET systems have a CTR below 600 ps FWHM [100]. More accurate detection is able to build a high-quality image with fewer radio events which could reduce the radiation dose to the patients or, equivalently, reduce the examination time.

SiPM is firstly used to replace the PMT in the hybrid system PET/MRI [104] in order to combine the functional information (PET) and the excellent anatomical information (MRI), called multi-modal diagnostic imaging, because of its insensitivity to the magnetic field. PMT is reported that its performance starts to show significant distortion with a magnetic field of only 3 mT [102], while the clinical MRI devices work at magnetic field strength in the order of several T. Besides, compared with PMT, SiPM also has advantages of compactness, relatively low cost and easy integration with electronics, which makes it an ideal replacement of PMT in next-generation of ToF-PET systems. The major players in molecular imaging, like GE Healthcare, Philips and Siemens Healthineers, have chosen SiPM to implement their more advanced ToF-PET systems (combined with CT or MRI) [50][80][38], corresponding to the CTR FWHM of 200 ps to 400 ps.

Some research PET system, like EndoTOFPET-US project, can achieve a time resolution of 200 ps [105], which builds a novel multi-modal tool integrated PET and ultrasound imaging aimed for prostate and pancreatic tumours diagnosis. The PET system includes a head extension for a commercial US endoscope and a PET plate outside the body in coincidence with the PET head, and the photon detection is implemented by scintillator based digital SiPMs and analogue SiPMs respectively.

In the laboratory, the capability of near 100 ps FWHM was demonstrated by measuring the time coincidence of two scintillators coupled SiPMs with a laser source [43], which showed the intrinsic time resolution of these detection modules were limited by scintillator instead of SiPM. Further effort is towards developing new scintillating materials and data acquisition systems in order to provide a minimal degradation of the intrinsic timing performance of the photo-detector.

In PETALO project [88], a novel concept for PET scanner based on liquid Xenon with TOF measurement is proposed. Liquid Xenon used for scintillating offers the features of high scintillation yield, fast decay time, and uniform response. The Monte Carlo investigation shows an instinct time resolution of 70ps and a time resolution of 30-50 ps can be obtained by using Cherenkov light.

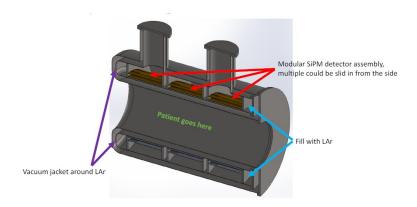

The  $3D\pi$  project is aimed to develop three dimensional positron identification with liquid Argon total-body TOF-PET (conceptional structure shown in figure 1.16), benefits directly from the technologies of Darkside-20k project like cryogenic SiPM and readout electronics. In principle, this proposed work can make it possible for direct 3D position imaging (the conventional approach combine multiple 2D projections obtained from different angles), achieve the clinical imaging in mm order resolution, and reduce the radiation dose to the patients by two orders of magnitude (10 mSv to 0.1 mSv) in each clinical exam [2].

Figure 1.16: Conceptional structure of  $3D\pi$  equipment [78].

PET systems with such performance at the system level are not yet available. Further research in new scintillating materials and data acquisition systems able to provide a minimal degradation of the intrinsic timing performance of the photodetector plus scintillator is necessary.

#### SPECT

In addition to PET, the other widely applied nuclear medicine technique of functional imaging is SPECT (Single-photon emission computed tomography). The single photon is emitted by radiotracer injected to patients' body and detected by the photon sensor. Different with PET technique, radioisotopes used in SPECT do not release back-to-back photons but only single gamma photon at about 100 keV to 300 keV, therefore, the photon sensors have to work with collimators in order to know the direction of incoming photons. Figure 1.17 shows the schematic of SPECT system. Although SPECT has less resolution than PET technique depending on

its working principle, more radio-tracers can be used to label the different organs: different radio-nucleus may be linked to specific pharmacological medicines that interact with different biological processes. Thus a single technique is capable of distinguishing more pathologies simultaneously.

Figure 1.17: Basic schematic of SPECT system [97].

SiPM is employed in SPECT system mainly because it is insensitive to the magnetic field. Since the multi-modal diagnostic imaging is the mainstream, SiPM based gamma camera makes it possible to combine SPECT with MRI. The IN-SERT (INtegrated SPECT/MRI for Enhanced Stratification in RadiochemoTherapy) project, funded by the European Community developed the first clinical SPECT/MRI system [52]. The SPECT detector is implemented by continuous CsI scintillator of 8 mm thickness, coupled to an array of 144 SiPMs produced by FBK, merging in 8 mm x 8 mm pixel.

SiPM is not so commonly used in SPECT compared to PET since the collimator dominates the spatial resolution and the photon sensor is expected to provide better energy resolution where the CdTe and CZT semiconductor detectors are more feasible by direct gamma-ray energy conversion scheme compared with the scintillator coupled with photon sensor. While in the before-mentioned INSERT project, SiPMs are adopted since they are cheap and simplify the electronic system [97].

## Chapter 2

### Review of SiPM readout ASICs

With the wide application of SiPMs in different fields, several ASICs have been developed to readout SiPMs with corresponding requirements. These requirements are related to the sensors and systems, such like: event rate, power consumption, readout density (channels in parallel), measurements (Timing or Energy), resolution and working environment (temperature, radiation hardness). In this chapter, some representative ASICs developed for different projects and applications are reviewed.

#### 2.1 TOFPET

The TOFPET (Time Of Flight for Positron Emission Tomography) ASIC was developed in the framework of the EndoTOFPET-US collaboration, a multi-modal imaging technique for endoscopic exams of the pancreas or the prostate. The design targets the readout of L(Y)SO scintillator coupled SiPMs of 3 mm x 3mm area in ToF PET system, and a system level CTR resolution of 200 ps FWHM [87].

Figure 2.1: Basic architecture of TOFPET single channel [87]

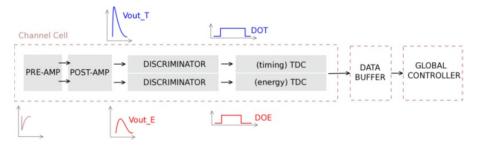

The TOFPET ASIC had its first silicon results in 2013, integrating 64 channels and implemented in 8-metal IBM CMOS 130nm technology. The basic architecture of one channel is shown in figure 2.1. Each channel consists of two independent

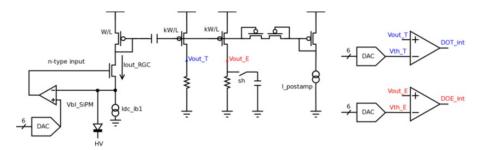

input stages for two polarities readout (electrons or holes), then the signal is divided into two branches, the faster branch is optimized for better timing resolution, and the slower one is used to measure the energy information with Time over Threshold (ToT) method. The front-end part is shown in figure 2.2.

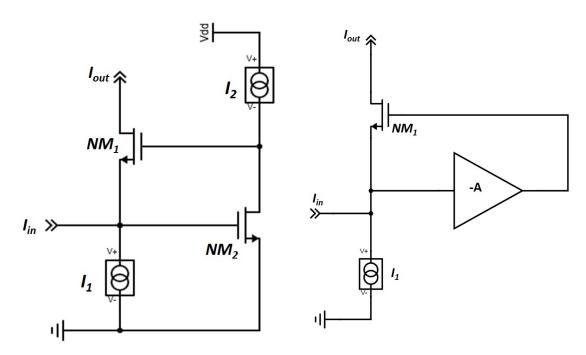

Figure 2.2: Basic architecture of TOFPET front-end amplifier (shown for n-input circuit)[87]

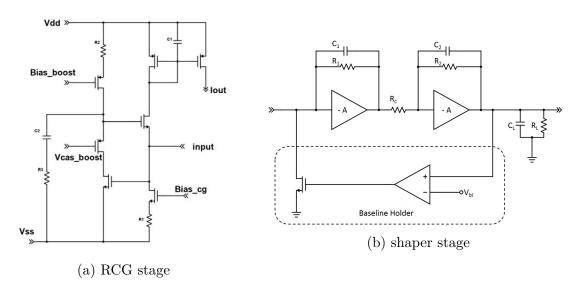

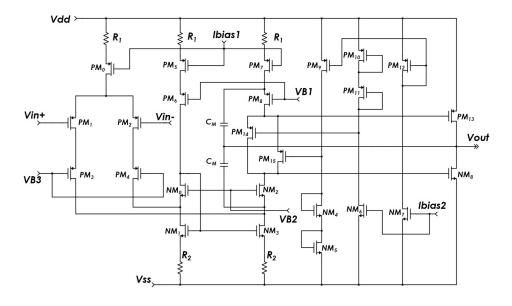

The main feature of front-end amplifier is the topology: Regulated Common Gate (RCG) or Regulated Cascode (RGC) structure, which is a common gate amplifier with differential feedback between the gate and source and works as a very low impedance current buffer, providing a fast response with low power consumption. Two independent types of RCGs implemented with complementary transistors to have more flexibility. Then a fast branch and slow branch optimized for timing and energy measurement respectively, the discriminator of fast branch provides the arrival time of each event, and the discriminator in slow branch configures a higher threshold to validate the event with energy larger than single photon, which can be used for dark count rejection.

Figure 2.3 describes the scheme for dark count rejection. With the lower threshold in timing branch, the trigger will have more accurate time arrival information, and the higher threshold (higher than single-photon amplitude) in energy branch provides the validation for a given event.

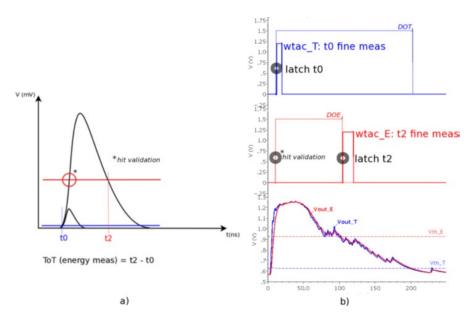

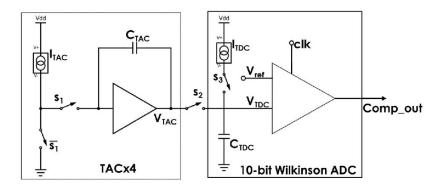

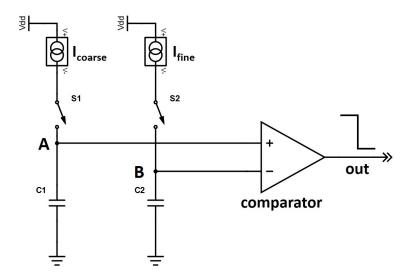

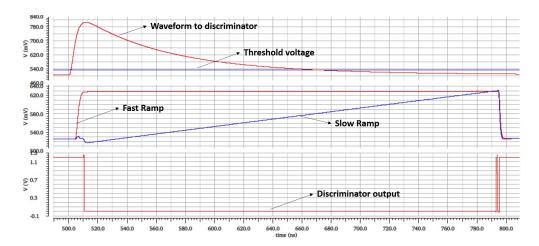

In TOFPET ASIC the Time to Digital Converter (TDC) is based on analogue interpolation, a technique that is very suitable for very low-power operation and low-to-moderate event rate capability.

The schematic of the working principle is shown in figure 2.4. The trigger signal from the fast branch will start a discharge with a constant current  $(I_{TAC})$  on a capacitor  $(C_{TAC})$  and stop when the next clock cycle arrives. Then the voltage value will be copied to a new but four times larger capacitor  $(C_{TDC})$ , with 32 times smaller current  $(I_{TDC})$  recharging to the reference voltage. Consequently, the binning of the timing measurement becomes a function of the clock period divided by the interpolation factor, which is defined by the ratio of the charge/discharge

Figure 2.3: Dual thresholds for dark count rejection[87]

Figure 2.4: Working principle of analogue interpolation TDC [20]

time constants:

$$T_{bin} = \frac{T_{cycle}}{4 \times 32} \tag{2.1}$$

where  $T_{cycle}$  is the operating clock cycle. For the nominal value of 160 MHz in TOFPET, the time bin of 50 ps can be achieved with about 1 mW of power consumption and the maximum event rate of 100 kHz per channel is estimated in TOFPET ASIC. The same back-end part is also shared in the work [83] [20].

A second version of this ASIC TOFPET2 [35] was submitted in 2015, mainly with the optimizations: adding a new linear charge measurement block in each

channel implemented by a charge integrator and ADC; improved event rate capability by increasing the clock frequency.

In summary, the TOFPET ASICs family is one of the most representative readout ASICs for SiPMs in time of flight application. The main features are low power high bandwidth pre-amplifier, dual thresholds for dark count rejection and low power interpolation TDC. It should be emphasized that the analogue interpolation TDCs are widely adopted in most of ASICs for SiPMs readout since their good time resolution potential (tens of ps compared with the intrinsic time resolution in the order of 100 ps in scintillator coupled SiPM system), good linearity, simple structure and low power consumption.

#### 2.2 PACIFIC

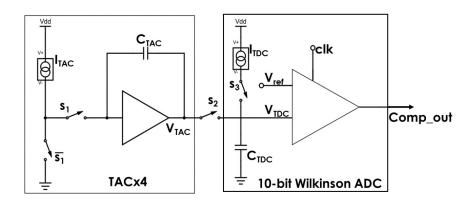

PACIFIC (Low Power ASIC for the SCIntillating Fibre TraCker readout) was developed to readout SiPMs in SciFi Tracker of the LHCb detector, where the SiPMs are used to readout scintillator fibre [25][23].

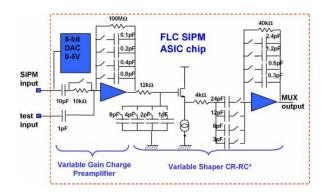

Figure 2.5: PACIFIC analog chain and control blocks [25]

Figure 2.5 shows the latest version architecture of PACIFIC. This chip is submitted in 2017, 64-channel and fabricated in TSMC 130 nm process [25].

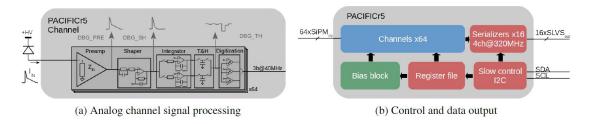

The schematic of PACIFIC input stage is shown in figure 2.6, which works as a current conveyor and reads out the anode signal.

The current conveyor provides constant input impedance and input voltage implemented by two feedback loops, aimed for low impedance and high bandwidth readout from SiPM (60  $\mu m \times 60~\mu m$  each micro-cell, 104 cells per channel). The following Trans-impedance amplifier (TIA) is used to transfer the current signal to the voltage. Then a pole-zero cancellation circuit and fast shaper stage manage to remove the slow component from recharge time of SiPM as well as the shorter time component, associated with parasitic capacitance and the amplifier input impedance. They achieve to integrate the pulse signal within 10 ns which is required to overcome the fluctuations of the scintillation signal shape due to the low photostatistics [27]. Two time-interleaved gated integrators are employed to minimize the dead time and followed by a dual passive track and hold structure.

Figure 2.6: PACIFIC input stage [25]

A 2-bit non-linear flash ADC operating at 40 MHz is used to digitize the tracked and held voltage. Finally, every four adjacent channels are summed by a serializer which transmits the data off-chip with differential SLVS.

The channel architecture allows the trigger-less readout from scintillator fibre coupled SiPM, managing to complete all the processes of readout, shaping, integration, track and hold and digitization (2-bit) within one clock cycle (25 ns). This ASIC has a power consumption below 10 mW per channel and is optimized for radiation tolerance because of its working environment.

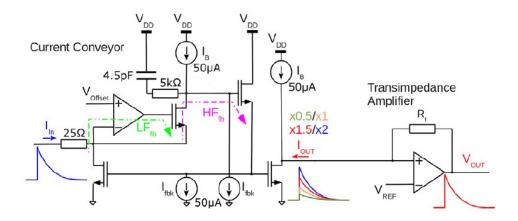

#### 2.3 ANGUS

ANGUS, a 36-channel ASIC in CMOS 0.35  $\mu m$  technology, was developed in the framework of the INSERT project. This collaboration proposed the development of a novel Single Photon Emission Computed Tomography (SPECT) system compatible with a magnetic resonance (MR) apparatus, where the SiPMs are able to show their high immunity to strong magnetic field environment. This ASIC targets the achievement of high spectroscopy performances at the low gamma energies (in the 100 to 300 keV range) used in SPECT [97].

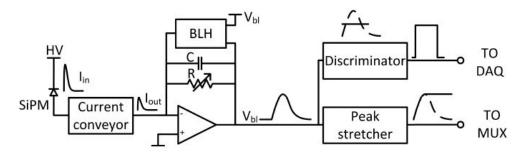

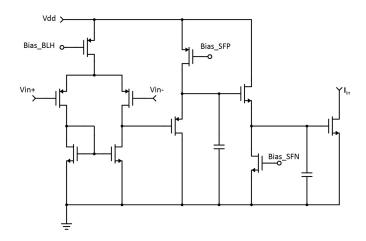

Figure 2.7 shows the channel architecture of ANGUS, and each channel is expected to readout an 8 x 8  $mm^2$  SiPM. The input stage is a current conveyor to have a low input impedance. Then the current signal is contained with a shaper, to transfer the current to voltage signal and improve the signal to noise (SNR) ratio by the RC filter with a time constant programmable from 200 ns up to 10  $\mu s$ . A Baseline Holder (BLH) structure is used to hold the baseline of output in the expected value. Finally, the signal is divided into two branches: one is followed with a discriminator for timing measurement; the other is a peak stretcher to capture

the peak of shaper output, which is proportional to the event energy. Both the outputs are sent off-chip for the digitization process.

Figure 2.7: Architecture of the ANGUS ASIC channel [97]

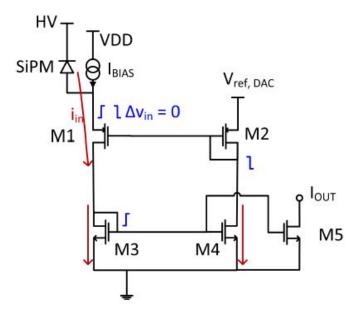

The input stage is a low input impedance current conveyor and its working principle is described in figure 2.8. A negative signal from SiPM causes the rise of source voltage of transistor M1, then this variation is mirrored by M3 and M4. With the relation of  $(W/L)_3/(W/L)_4 = (W/L)_1/(W/L)_2$ , M2 is able to make a perfect compensation to the gate of M1, resulting a null input impedance in the ideal condition. In the real case, limited by the finite drain resistance of transistors and the asymmetry, the input impedance is not zero and an approximate relation is given by equation 2.2, and in ANGUS, its value is about dozens of  $\Omega$ .

$$R_{in} \approx \frac{1}{g_{m1}} \left[ \frac{g_{d1} + g_{d3}}{g_{m3}} \frac{g_{d2} + g_{d4}}{g_{m2}} \right]$$

(2.2)

#### 2.4 VATA64-HDR16

VATA64-HDR16, fabricated by 0.35 um CMOS process and developed by GM-IDEAS (Norway), is a 64 channel front-end ASIC for SiPM readout [45]. The dedicated SiPMs are used in the detection of Cherenkov light, a field that may require the capability to deal with very low light levels. This ASIC provides accurate time arrival information in addition to the energy measurement, in order to take advantage of the synchronous emission of photons from Cherenkov cone and distinguished with SiPM dark count events.

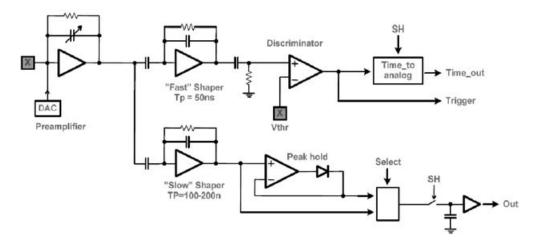

The input stage is a charge sensitive amplifier, which integrated the input charge and sent out a voltage waveform proportional to the event energy. Then the signal is divided into two branches, one is fed to a fast shaper followed by a discriminator. An on-chip Time to analogue converter (TAC) and a Sample-and-Hold (SH) circuit are implemented; The other branch has a slow shaper followed by a peak-hold circuit. These outputs of full chip are sent outside via two multiplexers and the digitization is provided off-chip.

Figure 2.8: Working principle of input stage in ANGUS ASIC [97]

Figure 2.9: Architecture of the VATA64-HDR16 ASIC channel[10]

## 2.5 SPIROC

SPIROC (Silicon Photomultiplier Integrated Read Out Chip) is a 36-channel ASIC implemented by 0.35 um SiGe technology and originally developed to read out SiPMs for a prototype hadronic calorimeter at the proposed International Linear Collider of Desy [13] [58].

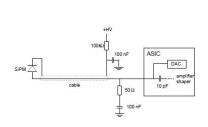

As shown in figure 2.10a, a 50  $\Omega$  load resistor is used to connect the SiPM and

converts the SiPM current to voltage, providing an impedance matching with the transmission line and limiting the voltage variation at the input node. One 100 nF capacitor is in series to the 50  $\Omega$  resistor, which works as short circuit for very short signal delivered by SiPM.

In the ASIC, a  $CR-(RC)^2$  filter is adopted to filter the noise with programmable shaping times from 40 ns to 180 ns. Another fast shaper (not shown in the figure) is used to generate the trigger signal. Then, a peak stretcher works to sample and hold the peak amplitude of the shaper output.

(a) Connection scheme of SiPM to ASIC chip

(b) Overview of the channel architecture in SPIROC

Figure 2.10: Readout scheme of SPIROC ASIC

#### 2.6 MD-SiPMs

According to the working principle of SiPM, a given number of SPADs are summed to a common output and then readout by electronics. These SPADs can also be read out individually with electronics where SPADs are integrated into the same substrate with the electronics, called digital SiPM or SPAD array. In principle, this embodiment has a high potential to detect the photons since it is able to collect the maximum information and the intrinsic time resolution of each SPAD. This solution requires the implementation of the photosensor and CMOS readout in the same substrate, which poses severe constraints to the optimisation of the sensor, in particular concerning correlated noise.

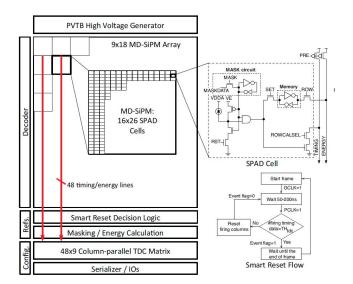

In the previously mentioned EndoTOFPET-US project, a multi-digital SiPM (MD-SiPM) system is developed for TOF-PET detection inside the endoscopic ultrasound probe, where an extremely miniaturized PET detector is implemented [16].

As depicted in figure 2.11, the detection module consists of 9 x 18 MD-SiPM arrays and each MD-SiPM has a 16 x 26 pixel array in total area of 800 x 780  $\mu m^2$ ,

Figure 2.11: Diagram structure of DS-SiPM system in EndoTOFPET-US project [16]

$50 \times 30 \ \mu m^2$  of single size. Each pixel consists of a SPAD and a 1-bit counter for pixel firing registration.

Each section of 416 pixels in each MD-SiPM share 48 TDCs, and the timestamp is triggered by the 1-bit counter and digitized by TDC. This endoscopic sensor can detect 67,392 photons and the first 432 time-of-arrival events in every detection frame of  $6.4 \ \mu s$  [16].

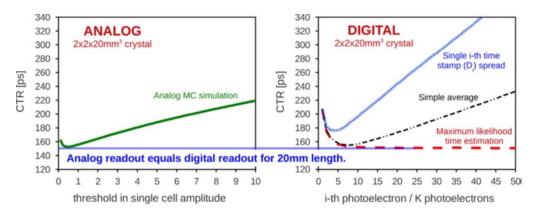

A detailed Monte Carlo simulation is reported in [44], which aims to study the potential time resolution between analogue SiPM and MD-SiPM scheme. One of the results is shown in figure 2.12, where both simulate the result of readout from a crystal with dimensions of  $2 \times 2 \times 20 \ mm^3$ . In the simulations, dark count and cross talk of the SiPM, as well as the electronic noise, are neglected.

The conclusion can be summarized as the analogue SiPM, and MD-SiPM readout from scintillator can have comparable time resolution when the latter scheme makes use of maximum likelihood estimation, and the digital scheme has more robustness. In contrast, the analogue scheme requires more critical threshold values.

#### 2.7 Conclusion

Table 2.1 summarized the specifications of reviewed SiPM readout ASICs. Compared to digital SiPM, the analogue SiPM has a better compromise on low cost and excellent resolution. In general, multi-channel ASICs used for SiPMs readout need to cope with the high capacitance of this kind of sensor (typically in the order

Figure 2.12: comparison between Analog and MD-SiPM simulations [44]

of  $50 \ pF/mm^2$ ), while providing a time-based readout with sub-nanosecond timing resolution. Due to the common stringent system requirement in terms of high channel density and limited budget for heat dissipation, most of the dedicated ASICs need an input stage with high bandwidth but limited power consumption. Analogue interpolation TDC is preferred in on-chip digitization since its lower power and suitable time resolution in time of flight application of SiPMs. Almost all the SiPM ASICs are developed with the application in room temperature or cooled down to about  $0 \ ^{\circ}C$ .

The growing interest on the use of SiPMs on detectors operating at cryogenic temperatures would call for the design of dedicated ASICs. At the time of this work, there are no solutions proposed in terms of mixed-signal ASICs for SiPM readout that are able to operate in a temperature range down to 87K (LAr boiling temperature). Indeed, such a development would allow for the construction of cryogenic photon-detection modules capable of operating inside the detector cryostat, providing amplification, signal conditioning and digitization of each event. This thesis introduces the challenges and circuit level design of a multi-channel mixed-signal CMOS readout integrated circuit for SiPM readout at cryogenic temperature.

| Entries        | TOFPET2     | PACIFICr5     | ANGUS    | VATA64        | SPIROC2c    |

|----------------|-------------|---------------|----------|---------------|-------------|

| number of ch   | 64          | 64            | 36       | 64            | 36          |

| Process        | CMOS        | CMOS          | CMOS     | CMOS          | SiGe        |

| Node           | 110 nm      | 130 nm        | 350  nm  | 350  nm       | 350  nm     |

| Readout type   | current     | current       | current  | charge        | voltage     |

| Application    | ToF-PET     | SciFi Tracker | SPECT    | astroparticle | calorimeter |

| Measurement    | T&E         | T&E           | T&E      | T&E           | T&E         |

| Energy extract | ToT/Peak    | Peak          | Peak     | Peak          | Peak        |

| Digitization   | on-chip     | on-chip       | off-chip | off-chip      | off-chip    |

| Power supply   | 1.2 V       | 1.2 V         | 3.3 V    | 3.3 V         | 3.3 V       |

| Power          | 10 mW       | 10 mW         | 8 mW     | no            | 25 uW       |

| Consumption    | /channel    | /channel      | /channel | /channel      | /channel    |

| Clock          | 200 MHz     | 40 MHz        | none     | none          | 5 MHz       |

| Event rate     | 600  kHz/ch |               |          |               |             |

| Dynamic range  | 2500 p.e    |               |          | 12 pC         | 2000 p.e    |

Table 2.1: Summary of reviewed ASICs for SiPM readout

# Chapter 3

# Test chips studies for SiPM readout at cryogenic temperature

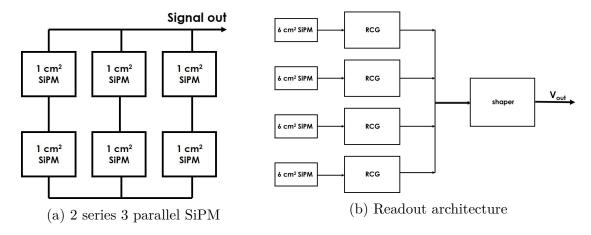

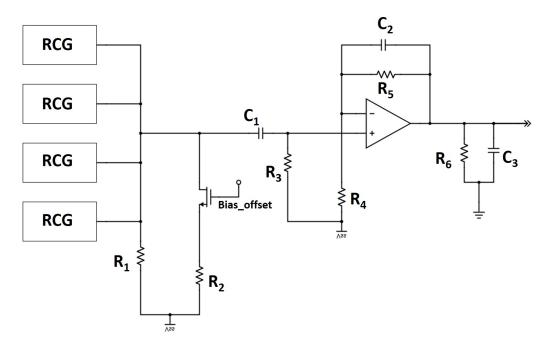

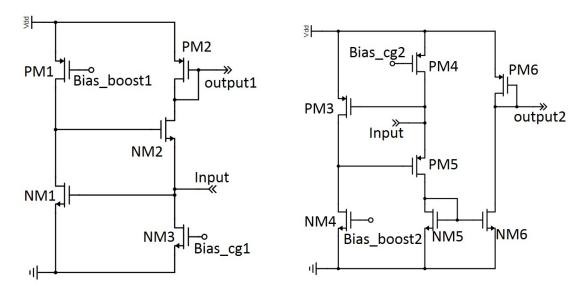

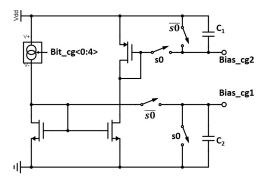

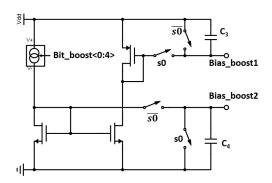

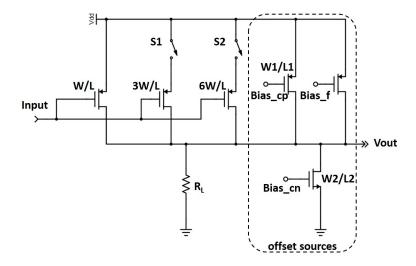

This chapter introduces the study of the front end circuit for SiPM readout, which are expected to read out large area of SiPMs and work at cryogenic temperatures.