## Doctoral Dissertation

Doctoral Program in in Electrical, electronics and Communications Enginering, with curriculum in "Electronic Devices" in convention with the National Institute for Nuclear Physics (32<sup>nd</sup> cycle)

# Low-Power Mixed-Signal ASIC for Cryogenic SiPM Readout

Ramshan Kugathasan

**Supervisors**

Prof. Angelo Rivetti, Supervisor, Turin INFN Dr. Manuel Dionisio Da Rocha Rolo, Co-supervisor, Turin INFN Prof. Michele Goano, Co-supervisor, Turin Polytechnic

### **Doctoral Examination Committee:**

Prof. Alessandro Gabrielli, Referee, University of Bologna Prof. Lucio Pancheri, Referee, University of Trento

> Politecnico di Torino 2020

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Ramshan Kugathasan Turin, 2020

## Summary

There is a growing interest in the use of Silicon photomultipliers (SiPMs) operating at cryogenic temperatures. The largely suppressed dark count rate observed at liquid Xenon and liquid Argon temperature makes such sensors ideally suited to equip large area detectors like those needed in dark matter and neutrino experiments. Research programs to explore the possibility of building total body PET scanners based on noble liquids readout by SiPM are also ongoing. Highly integrated front-end electronics embedded in the cold volume close to the sensor allows for a significant reduction of the interconnections and feed-through as data can be easily multiplexed and serialised in the digital domain. Depending on the application, the SiPM pixel size may range from a few mm<sup>2</sup> to a few cm<sup>2</sup>.

The INFN-Torino group developed a low-power mixed-signal ASIC to readout SiPM at low temperature. The chip, called ALCOR, is designed in 110 nm CMOS technology, is a first prototype suitable for future 3D integration with the photon sensor. The architecture comprises of 32 independent pixels, each of them features an analogue front-end, discriminators, digital logic and low-power TDCs based on analogue interpolation. The total area of the IC is 4.95 × 3.78  $mm^2$ , where each pixel occupies 500 × 500  $\mu$   $m^2$  for a power consumption less than 10 mW. The pixel generates the timestamp of the arrival time of the event when it operates in a single photon detection mode, but it can be programmed to operate also in Time-over-Threshold where two timestamps are generated for each event. This modality is useful when many photons pile-up to yield a continuous signal. In single photon counting mode, an event rate of up to 5 MHz per pixel can be accommodated. The time binning of TDCs is 50 ps at the maximum system clock frequency of 320 MHz. The 32-bit data payloads are transmitted externally to a FPGA through four LVDS drivers with maximum throughput of 640 Mb/s.

Normally, digital standard cell models below  $-40 \,^{\circ}C$  are not provided by the technology vendor. Therefore, a preliminary Test Chip ASIC has been produced and tested in order to get insight into cryogenic behaviour. This ASIC embeds some of critical building blocks that are employed in the mixed-signal ASIC. In particular, a digital synchronisation circuit designed with 110 *nm* standard cells has been included. This thesis reports the dedicated test results at cryogenic temperature and a comparison with SPICE simulation of extrapolated models at 77 *K* of the same circuits.

My personal contribution to the development of this work has been divided into three parts. The first part concerns the definition of specifications, simulation and implementation of digital circuits for ALCOR. Subsequently, I dealt with the development and cryogenic characterization of some critical digital blocks. Finally, I carried out a preliminary study of a distributed sensor network that allows to minimize the number of interconnections with the outside world while maintaining a high fault tolerance.

The Chapter 1 introduces the DarkSide-20k experiment, an underground detector for direct dark matter detection which is the future upgrade of the DarkSide-50 detector built in Laboratori Nazionali del Gran Sasso (LNGS). The detector is based on a twophase Liquid Argon Time Project Chamber and cryogenic SiPM photo sensors to detect scintillation events.

The Chapter 2 describes briefly the structure and behaviour of SiPM photosensor and reports the state-of-art of ASICs for both analogue and digital SiPM readout.

The Chapter 3 discussed the design of the mixed-signal ASIC suitable for cryogenic SiPM readout. The chapter describes the architecture employed and the chip simulation results that describe the behaviour of the circuit.

The Chapter 4 reports the issue related to designing a digital circuit for the cryogenic environment, showing the characterisation and results of a test chip fabricated embedding important building blocks.

The Chapter 5 describes a preliminary study of a distributed readout network suitable for a large area of sensor. It describes the implementation of the network in a 3D digital SiPM where data are digitised and multiplexed reducing the cable connection at the minimum necessary. **Keywords**: Noble liquid detectors, Mixed analogue digital integrated circuits, Timing, Cryogenic electronics.

## Acknowledgements

I would like to acknowledge my supervisor Angelo Rivetti, for his wise advice and for all his support during my doctoral studies. Special thanks to Manuel Rolo for his teaching and expertise that made this work possible.

My gratitude also goes to the VLSI office: Federico, Jonhatan and Fabio that welcomed me from the very beginning in this group; Antonio, Simona and Weishuai my  $32^{nd}$  cycle mates with whom I shared incredible experience during this three years; Alejandro, Lorenzo and Raffaele whom brought experiences and laugh to this group. Many thanks to the INFN Torino Darkside group: Giulio Dellacasa, Marco Mignone and Richard Wheadon.

I would like to express my most sincere thanks to my parents, my relatives and my friends for their support. In particular, my brother Thanushan that has guided me since I was born and made me what I am today.

Finally, the best thanks goes to my fiancée Babithra, who through her love, her advice and her patience has supported me till the end and beyond.

To all people that find the courage to change their life for a brighter future.

# Contents

| Li | st of 7 | Fables  |                                          | XIII |

|----|---------|---------|------------------------------------------|------|

| Li | st of l | Figures |                                          | xv   |

| 1  | Eng     | ineerin | g challenges in dark matter detectors    | 1    |

|    | 1.1     | DarkSi  | de-20k                                   | 2    |

|    |         | 1.1.1   | SiPM readout in DS-20k                   | 7    |

|    | 1.2     | SiPM s  | ignal digitisation on-cold               | 9    |

| 2  | Adv     | anced r | readout concepts for photon detectors    | 11   |

|    | 2.1     | Silicon | photomultipliers                         | 12   |

|    |         | 2.1.1   | Photon detection efficiency              | 14   |

|    |         | 2.1.2   | Dark Count, After-Pulsing and Cross-Talk | 15   |

|    | 2.2     | Analog  | gue SiPMs                                | 18   |

|    |         | 2.2.1   | TIA                                      | 19   |

|    |         | 2.2.2   | Voltage mode                             | 20   |

|    |         | 2.2.3   | Current mode                             | 21   |

|    |         | 2.2.4   | Energy measurements                      | 23   |

|    |         | 2.2.5   | Time measurement                         | 24   |

|    |         | 2.2.6   | SPIROC2                                  | 27   |

|    |         | 2.2.7   | TOFPET2                                  | 29   |

|    | 2.3     | Digital | SiPMs                                    | 31   |

|    |         | 2.3.1   | Philips Digital Photon Counter           | 32   |

|    |         | 2.3.2   | SPADnet photosensor                      | 33   |

|    |         | 2.3.3   | 3D-SiPMs                                 | 34   |

| 3 | Desi | ign of an innovative low power ASIC for SiPM readout          | 37 |

|---|------|---------------------------------------------------------------|----|

|   | 3.1  | Motivation and Specification                                  | 38 |

|   | 3.2  | ALCOR                                                         | 40 |

|   | 3.3  | Pixel Architecture                                            | 43 |

|   |      | 3.3.1 Pixel configuration                                     | 46 |

|   |      | 3.3.2 Pixel operation mode                                    | 48 |

|   | 3.4  | TDC behaviour                                                 | 50 |

|   |      | 3.4.1 TDC operation range                                     | 53 |

|   |      | 3.4.2 Simulation                                              | 56 |

|   | 3.5  | Data payloads format                                          | 57 |

|   |      | 3.5.1 Special payloads                                        | 59 |

|   | 3.6  | Data transmission                                             | 60 |

|   |      | 3.6.1 Data payload                                            | 60 |

|   |      | 3.6.2 Status payload                                          | 61 |

|   | 3.7  | End of Column                                                 | 63 |

|   |      | 3.7.1 SPI interface                                           | 64 |

|   |      | 3.7.2 Data encapsulation                                      | 67 |

|   |      | 3.7.3 Cyclic Redundancy Check                                 | 68 |

|   |      | 3.7.4 Double data rate output register                        | 69 |

|   |      | 3.7.5 Reset                                                   | 69 |

|   | 3.8  | Radiation protection                                          | 70 |

|   |      | 3.8.1 Triple Modular Redundancy                               | 71 |

|   |      | 3.8.2 Hamming Code                                            | 73 |

|   | 3.9  | Conclusions                                                   | 76 |

|   |      |                                                               |    |

| 4 |      | con implementation and cryogenic characterisation of key IPs. | 77 |

|   | 4.1  | Delay propagation in CMOS                                     | 78 |

|   | 4.2  | The Test Chip                                                 | 81 |

|   |      | 4.2.1 Experimental Setup                                      | 82 |

|   |      | 4.2.2 Digital synchronisation circuit                         | 84 |

|   |      | 4.2.3 Low Voltage Differential Signaling                      | 89 |

|   | 4.3  | Conclusions                                                   | 94 |

| 5  | Desi  | gn of smart integrated networks for large area photo-sensors read <sup>.</sup> | -   |

|----|-------|--------------------------------------------------------------------------------|-----|

|    | out.  |                                                                                | 95  |

|    | 5.1   | Motivation                                                                     | 96  |

|    | 5.2   | DSN topology                                                                   | 98  |

|    |       | 5.2.1 Data transmission between pixel nodes                                    | 99  |

|    | 5.3   | Reliability of the DSN to pixel failure                                        | 105 |

|    | 5.4   | Conclusions                                                                    | 110 |

| A  | Alco  | or                                                                             | 111 |

|    | A.1   | Configuration registers                                                        | 111 |

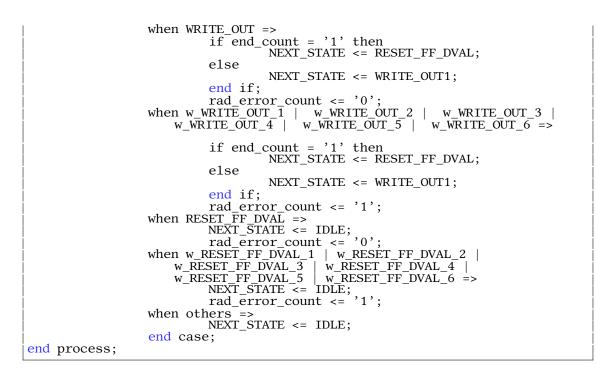

|    | A.2   | FSM with Hamming code implementation                                           | 115 |

|    | A.3   | Python scripts                                                                 | 117 |

|    |       | A.3.1 LET script                                                               | 117 |

|    |       | A.3.2 ToT and SR script                                                        | 119 |

| Bi | bliog | raphy                                                                          | 123 |

| Ac | rony  | ms                                                                             | 133 |

# List of Tables

| Input and Output signal of Alcor chip                                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Describes how amplifier's gain changes according to $\operatorname{Gain}_1$ and $\operatorname{Gain}_2$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| value                                                                                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| The bit in position 12 to 9 of PCR3 are used to define the operation mode                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| of the single Pixel                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| The Fine counter register bit length, changes according to cgf_I_ratio                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| and cfg_Safety_bit.                                                                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPI commands                                                                                            | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPI Status Register content                                                                             | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| K codes encoded with 8b/10b protocol.                                                                   | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ALCOR output data stream.                                                                               | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

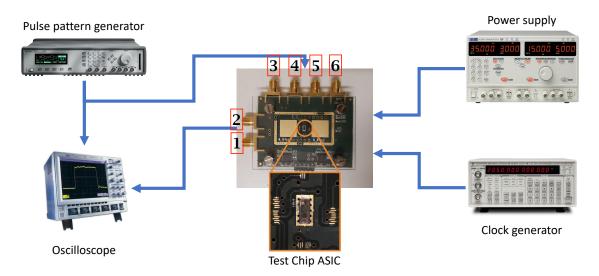

| Input/Output SMA ports of the test board for testing digital circuits of                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Test Chip                                                                                               | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Eye diagram measurements of LVDS driver, with data transmission at                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| low frequency.                                                                                          | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Eye diagram measurements of LVDS driver, with data transmission at                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| high frequency.                                                                                         | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Number of possible paths from $Pix0$ to $Pix23$ for each network 1                                      | .07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BCR_0, defines global analogue bias settings                                                            | .11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BCR_1, defines global analogue bias settings                                                            | .11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Configuration registers to set coarse TDC's fast current                                                | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Configuration register to set fine TDC's fast current                                                   | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Configuration register to set discriminator threshold voltages and ranges. 1                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                         | Describes how amplifier's gain changes according to $Gain_1$ and $Gain_2$ valueThe bit in position 12 to 9 of PCR3 are used to define the operation modeof the single Pixel.The Fine counter register bit length, changes according to $cgf_I_ratio$ and $cfg_Safety_bit$ .SPI commandsSPI commandsSPI Status Register content.K codes encoded with 8b/10b protocol.ALCOR output data stream.Input/Output SMA ports of the test board for testing digital circuits ofTest Chip.Eye diagram measurements of LVDS driver, with data transmission atlow frequency.Number of possible paths from $Pix0$ to $Pix23$ for each network.Number of possible paths from $Pix0$ to $Pix23$ for each network.BCR_0, defines global analogue bias settings.Configuration registers to set coarse TDC's fast current. |

| A.6 | Configuration register to set amplifiers configuration and pixel opera- |     |

|-----|-------------------------------------------------------------------------|-----|

|     | tion mode                                                               | 113 |

| A.7 | End of Column Configuration Register                                    | 113 |

# List of Figures

| 1.1 | 3D schematic of the DS-20k experiment.                                               | 2  |

|-----|--------------------------------------------------------------------------------------|----|

| 1.2 | Single PDM of $5 \times 5 cm^2$ has mounted 24 SiPMs of $12 \times 8 mm^2$ each. The |    |

|     | structure comprises also the readout electronics [21]                                | 3  |

| 1.3 | Single SQB motherboard fully equipped with 25 PDMs                                   | 4  |

| 1.4 | Patterning scheme of the motherboards on the base surface of the TPC.                | 5  |

| 1.5 | Simulation of arrival time of S1 (left) and S2 (right) signals in DarkSide-          |    |

|     | 20k experiment. [2]                                                                  | 6  |

| 1.6 | Schematic diagram of SiPM sensor of DS-2-k experiment                                | 7  |

| 1.7 | Schematic diagram of data acquisition system.                                        | 8  |

| 2.1 | Electric model of SPAD on the right. On the left the time response of                |    |

|     | the circuit.                                                                         | 12 |

| 2.2 | Electric model of SPAD on the right. On the left the time response of                |    |

|     | the circuit.                                                                         | 13 |

| 2.3 | SiPM cross-section showing different dark noises: After-pulsing, Dark                |    |

|     | count rate, Direct and Delayed Cross-Talk.                                           | 16 |

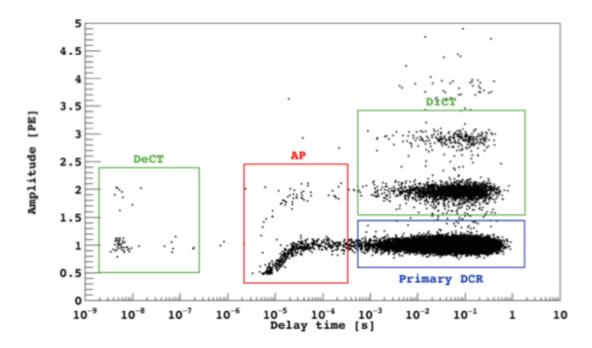

| 2.4 | Distribution of peak amplitude versus time since last event for an RGB-              |    |

|     | HD-HRq SiPM operating at 40 K and 4 V of over-voltage in the absence                 |    |

|     | of light. It is possible to identify the different noise components of the           |    |

|     | SiPM response described in the text: DCR, DiCT, DeCT and AP. $\ .\ .$ .              | 17 |

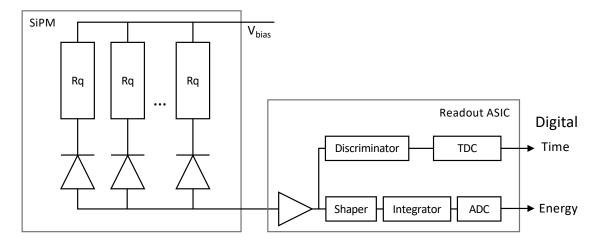

| 2.5 | Schematic block of an analogue SiPM readout                                          | 18 |

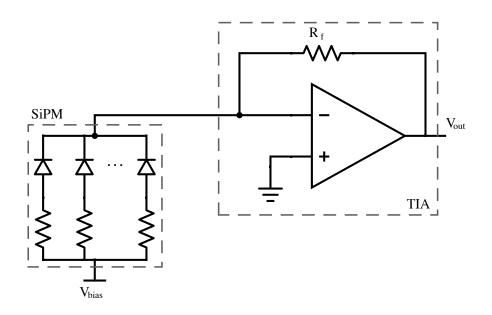

| 2.6 | Example of Transimpedance amplifier coupled with SiPM sensor. $\ . \ .$              | 20 |

| 2.7 | Example of voltage mode readout, using an integrator for energy mea-                 |    |

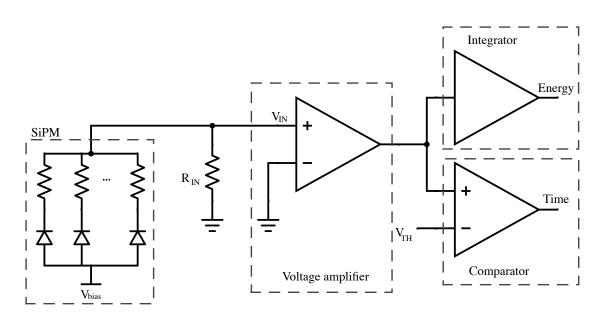

|     | surament and comparator for time measurament.                                        | 21 |

| 2.8  | Example of current mode readout, using an integrator for energy mea-                            |    |

|------|-------------------------------------------------------------------------------------------------|----|

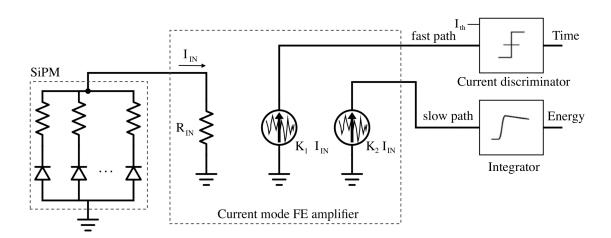

|      | surement and comparator for time measurement.                                                   | 22 |

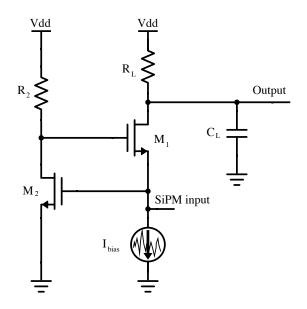

| 2.9  | Example of regulated common gate circuit                                                        | 22 |

| 2.10 | Time-over-threshold technique for energy measurement [20]                                       | 24 |

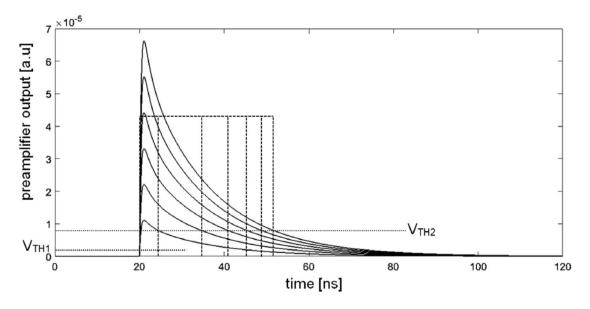

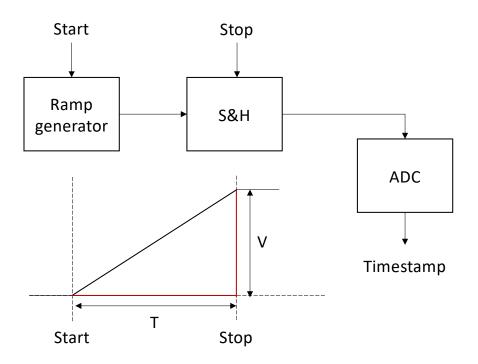

| 2.11 | Ramp interpolator scheme diagram. The $\Delta$ <i>T</i> period is defined by the                |    |

|      | Start and Stop signals. The $\Delta$ $V$ defines the time amplitude to be digitised.            | 25 |

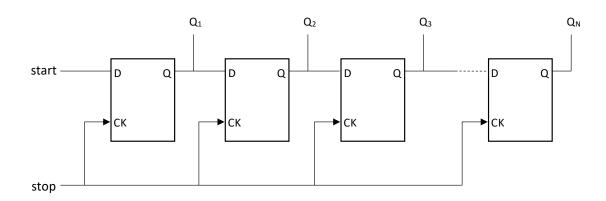

| 2.12 | The tapped delay line uses n D-FF placed in series which each compo-                            |    |

|      | nent has a well defined time delay. The Start signal is delayed through                         |    |

|      | the line and when the Stop signal arrives samples the $\mathrm{Q}_{\mathrm{N}}$ output. $\ .$ . | 26 |

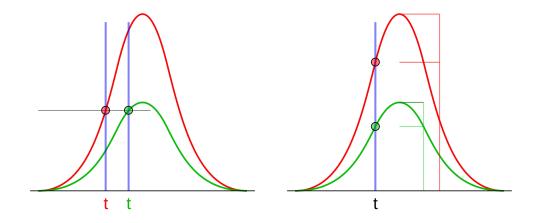

| 2.13 | The different signal amplitude overcome the threshold at two different                          |    |

|      | time. The CFD generates the same arrival time independently by the                              |    |

|      | signal amplitude. [32]                                                                          | 26 |

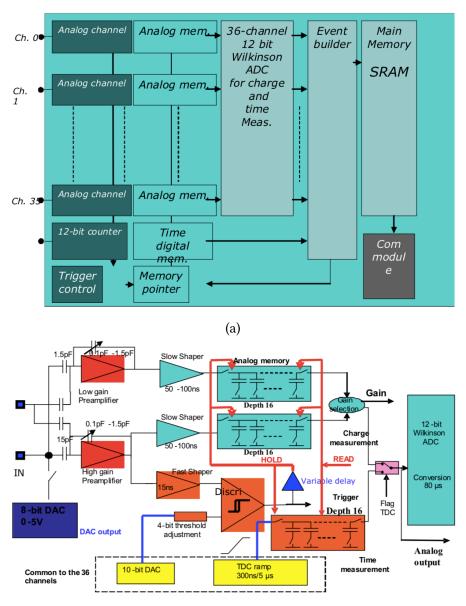

| 2.14 | Schematic diagram of SPIROC ASIC, full chip (a) and single channel                              |    |

|      | (b) [16]                                                                                        | 28 |

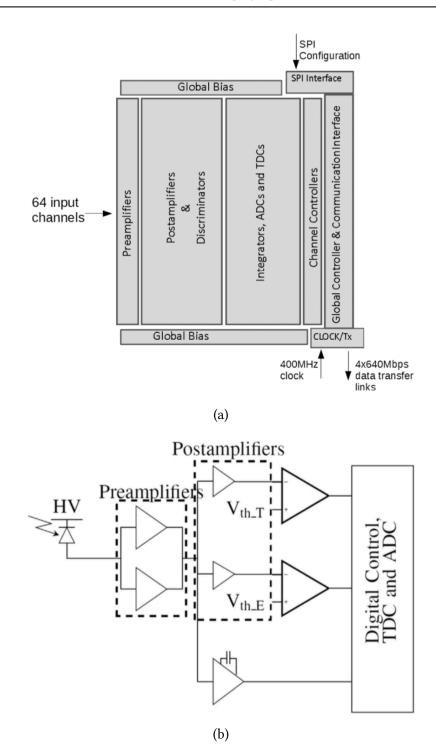

| 2.15 | Schematic diagram of TOFPET2 ASIC, full chip (a) and single channel                             |    |

|      | (b) [18]                                                                                        | 30 |

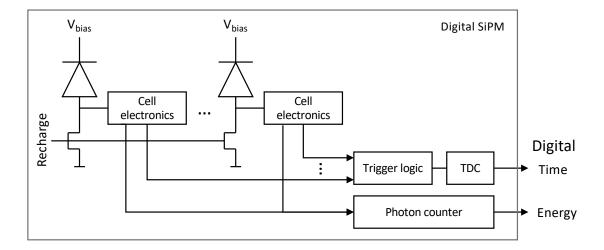

| 2.16 | Schematic block of a digital SiPM readout.                                                      | 31 |

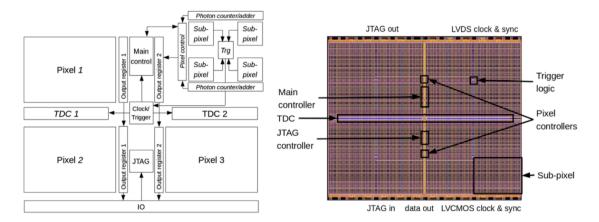

| 2.17 | On the left the DPC3200-22 digital SiPM block diagram. On the right                             |    |

|      | the layout diagram of the sensor [35]                                                           | 32 |

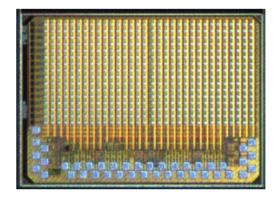

| 2.18 | Photography of the SPADnet sensor chip [17]                                                     | 33 |

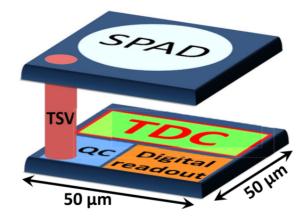

| 2.19 | 3D-SiPM architecture, the SPAD is connected to the readout electronics                          |    |

|      | through silicon vias (TSV) [71].                                                                | 34 |

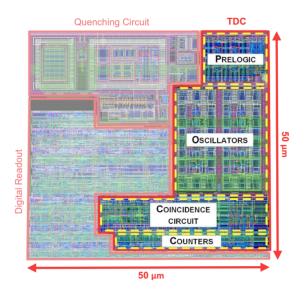

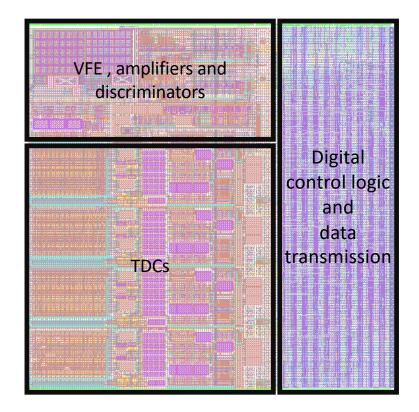

| 2.20 | Layout of the CMOS chip designed in 65 nm technology. $\ldots$                                  | 35 |

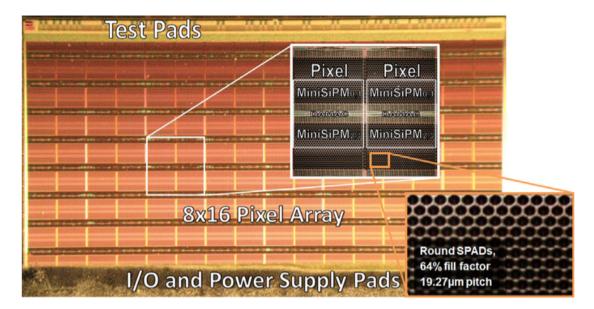

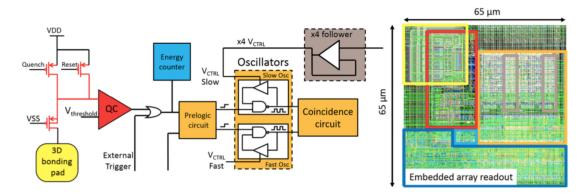

| 2.21 | ASIC with 256 pixels for 3D SiPM implementation.[55]                                            | 35 |

| 2.22 | Schematic diagram and layout of the single pixel channel. The pixel has                         |    |

|      | a dimension of 65 $\mu m \times 65 \mu m$ [55]                                                  | 36 |

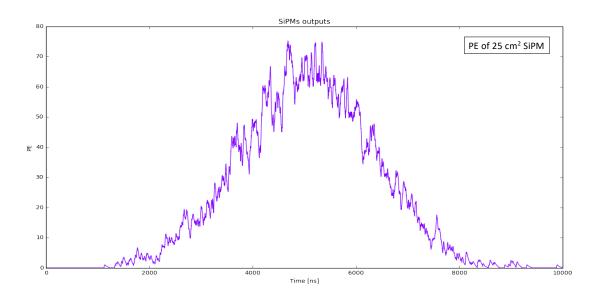

| 3.1  | Python simulation of PE distribution over a SiPM of 24 $cm^2$ . In this                         |    |

|      | example there are 4000 $PE$                                                                     | 39 |

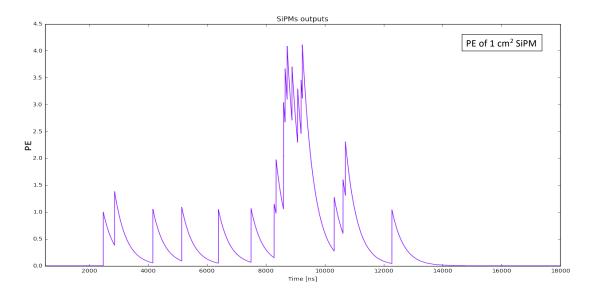

| 3.2  | Python simulation of photo distribution over a SiPM of 1 $cm^2$ . In this                       |    |

|      | example there are 100 $PE$                                                                      | 39 |

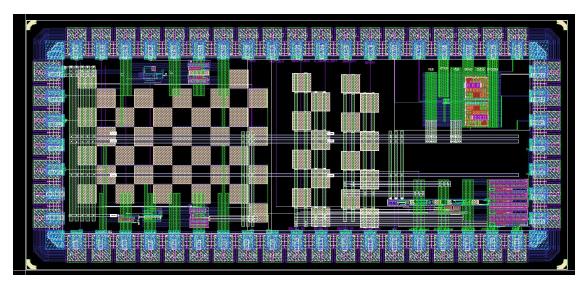

| 3.3  | ALCOR full ASIC layout. It occupies a total area of $4.95 \times 3.78 mm^2$                     | 40 |

| 3.4  | Pixel layout where the area of each block is defined. The total pixel area                       |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | occupies $500 \times 500 \mu m^2$                                                                | 44 |

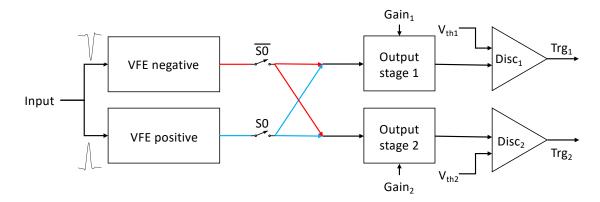

| 3.5  | Front-End schematic block. The FE embeds input signal VFE with pro-                              |    |

|      | grammable polarity, two programmable amplifiers and two programmable                             |    |

|      | discriminators                                                                                   | 44 |

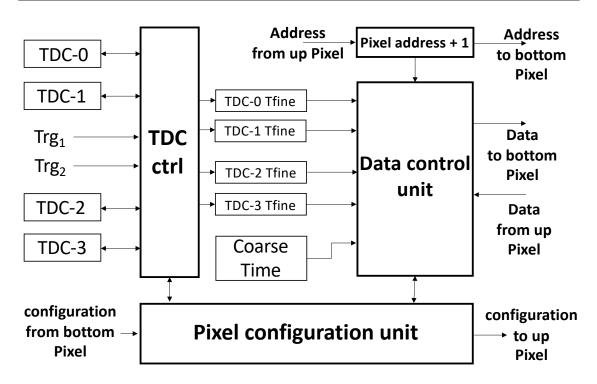

| 3.6  | Pixel schematic block diagram. The $\mathrm{Trg}_1$ and $\mathrm{Trg}_2$ are the trigger signal  |    |

|      | generated from the FE. Each pixel contains the digital control logic, data                       |    |

|      | ADC formatting, four low-power TDCs, fine and coarse counters                                    | 46 |

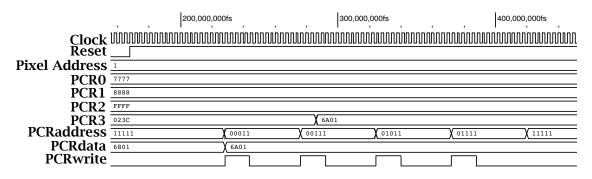

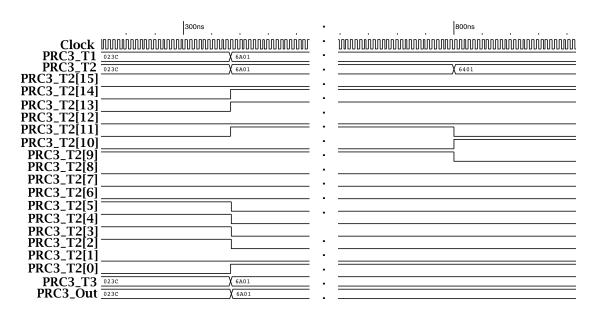

| 3.7  | Pixel configuration simulation. This time diagram reports the configu-                           |    |

|      | ration of the PCR3 register of Pixel1. Each configuration is target with                         |    |

|      | the PCR<br>address, which contains the Pixel address and PCR address and                         |    |

|      | the PCR data                                                                                     | 47 |

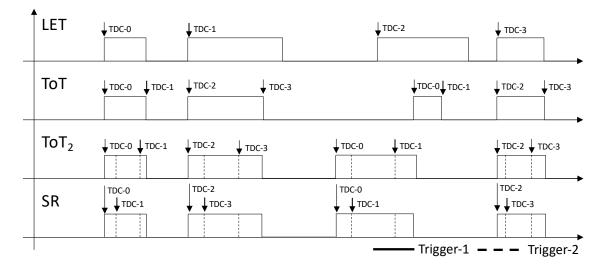

| 3.8  | The TDCs are enabled accordingly to the operation mode. The LET and                              |    |

|      | To<br>T modes use only the $\mathrm{Trg}_1,$ while the<br>$\mathrm{ToT}_2$ and SR modes use both |    |

|      | $\mathrm{Trg}_1$ and $\mathrm{Trg}_2$ triggers.                                                  | 49 |

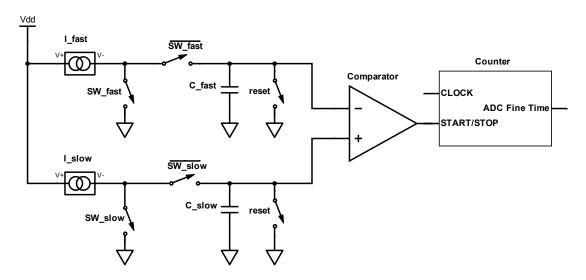

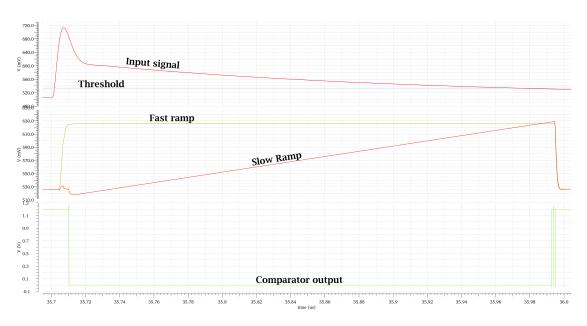

| 3.9  | TDC schematic circuit.                                                                           | 52 |

| 3.10 | TDC simulation                                                                                   | 53 |

| 3.11 | In case the trigger occurs in the red area of clock period, immediately                          |    |

|      | before the trailing edge, the fine measurement is measured from the                              |    |

|      | trigger arrival time till the first clock rising edge                                            | 54 |

| 3.12 | In case the trigger occurs in the red area of clock period, immediately af-                      |    |

|      | ter the trailing edge, the fine measurement is measured from the trigger                         |    |

|      | arrival time till the second clock rising edge.                                                  | 54 |

| 3.13 | Simulation of a TDC with 128 ratio counter.                                                      | 55 |

| 3.14 | Arrival time of an event expressed as time difference between pixel                              |    |

|      | timestamp and simulation timestamp                                                               | 56 |

| 3.15 | Time-over-Threshold simulation performed with a train of TP signal,                              |    |

|      | with a time delay of 15 $ps$ between one signal to the other                                     | 57 |

| 3.16 | Event-word and status-word payloads.                                                             | 58 |

|      |                                                                                                  |    |

|      | ing edge of the trigger for 2 <sup>15</sup> clock periods from the rising edge of the |    |

|------|---------------------------------------------------------------------------------------|----|

|      |                                                                                       |    |

|      | trigger. If the timers reaches the maximum value this payload is gener-               |    |

|      | ated off-pixel to notify the problem                                                  | 59 |

| 3.18 | Event-word generated when the f.c. reaches its maximum value and                      |    |

|      | TDC doesn't give a stop conversion signal. The f.c. stores a value that               |    |

|      | cannot be obtained from a time conversion                                             | 60 |

| 3.19 | Timing diagram of: (a) data transmission protocol between pixel and                   |    |

|      | EoC, (b) data transmission between pixels, (c) status data request and                |    |

|      | transmission between pixel and EoC.                                                   | 62 |

| 3.20 | Schematic diagram of EoC data storage and transmission                                | 63 |

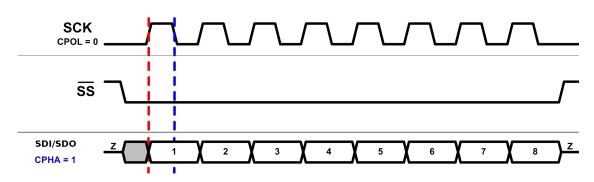

| 3.21 | SPI interface timing diagram                                                          | 65 |

| 3.22 | The SPI command word.                                                                 | 65 |

| 3.23 | The SPI point addressing the BCR, ECCR and PCR registers                              | 66 |

| 3.24 | Status word of End-of-Column.                                                         | 67 |

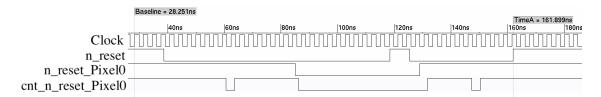

| 3.25 | Reset time diagram of the ALCOR chip. Depending on the duration of                    |    |

|      | the n_reset signal at the pixel level the registers (n_reset_Pixel)) or the           |    |

|      | course counters (cnt_n_reset_Pixel0) are reset                                        | 70 |

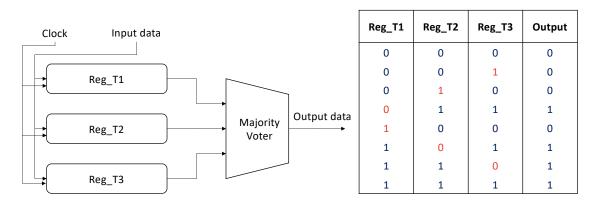

| 3.26 | Triple modular redundancy architecture applied to registers. The truth                |    |

|      | table on the right shows the output of the majority voter when a SEU                  |    |

|      | affects one of the bit in one of the register. This bit is expressed in red           |    |

|      | colour, while the blue colour expresses the correct value. $\ldots$                   | 71 |

| 3.27 | Schematic time diagram of TMR simulation. The PCR3 register is af-                    |    |

|      | fected by SEU event on bit position 11 at time 800 ns. The SEU event                  |    |

|      | does not affect the PCR3_Out which continues to generate the correct                  |    |

|      |                                                                                       |    |

|      | output                                                                                | 72 |

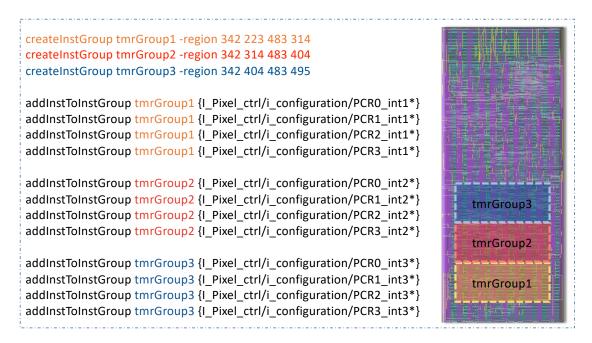

|      | outputImplementation of TMR technique on layout phase of the design. On               | 72 |

| 3.28 | -                                                                                     | 72 |

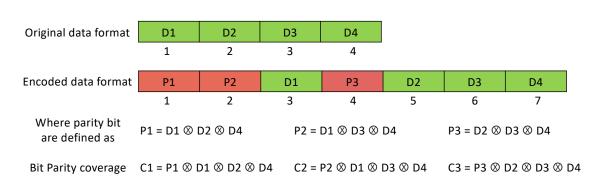

| 3.29 | Implementation of Hamming code of 4 bit register to 7 bit register. The              |    |

|------|--------------------------------------------------------------------------------------|----|

|      | original data format is encoded in Hamming code including parity bits                |    |

|      | (P1/P2/P3) defined with bit-XOR operations. The bit parity coverage is               |    |

|      | used to index the bit affected by SEU event                                          | 74 |

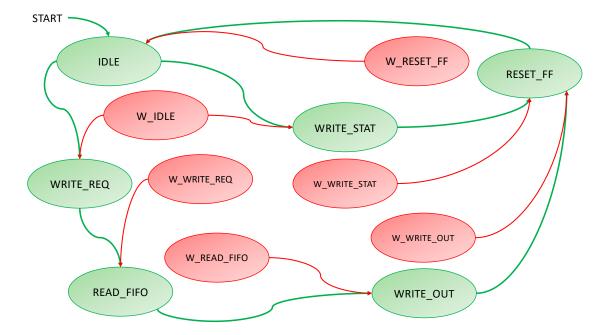

| 3.30 | Post-layout simulation of Hamming code applied to FIFO readout. This                 |    |

|      | FSM is defined with six states where the green nodes are the correct                 |    |

|      | states, while the red nodes are the wrong nodes that are accessible only             |    |

|      | in case of SEU event on the state register. From the red nodes it is pos-            |    |

|      | sible to restore the correct behaviour.                                              | 75 |

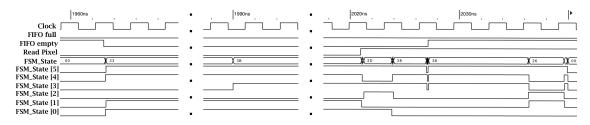

| 3.31 | Post-layout simulation of Hamming code applied to FIFO readout FSM.                  |    |

|      | This simulation example shows hot the state register is restored after a             |    |

|      | SEU event generated by simulation                                                    | 75 |

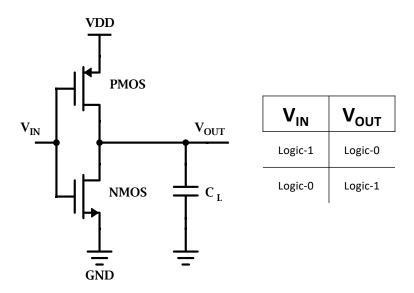

| 4.1  | Schematic circuit of a CMOS inverter                                                 | 78 |

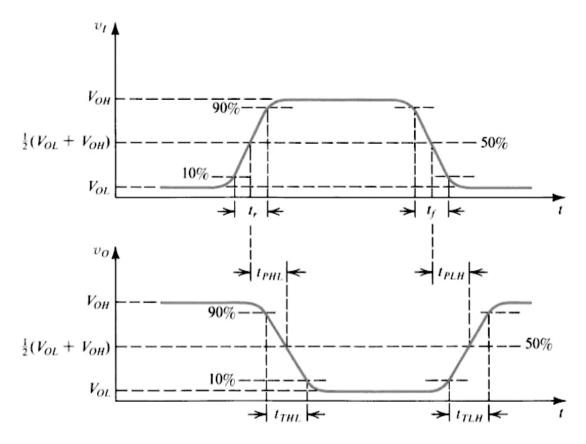

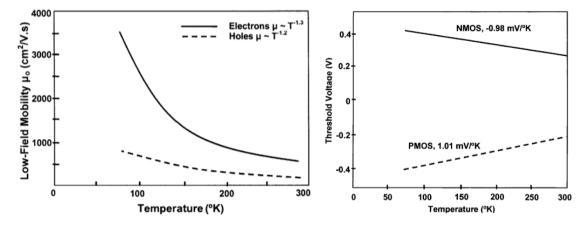

| 4.2  | Schematic circuit of a CMOS inverter                                                 | 79 |

| 4.3  | Variation of the mobility and threshold voltage when the temperature                 |    |

|      | decreases.[81]                                                                       | 80 |

| 4.4  | Layout of the Test Chip ASIC.                                                        | 81 |

| 4.5  | Test setup for the electrical characterisation of TC ASIC                            | 82 |

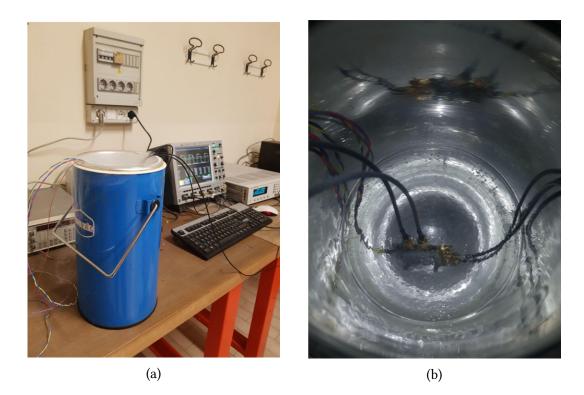

| 4.6  | Figure (a) depicts the test setup and the dewer used to perform test with            |    |

|      | liquid nitrogen. Figure (b) depicts the test board imersed completly in              |    |

|      | liquid Nitrogen. All the cable are bring outside the dewer as show in                |    |

|      | images                                                                               | 83 |

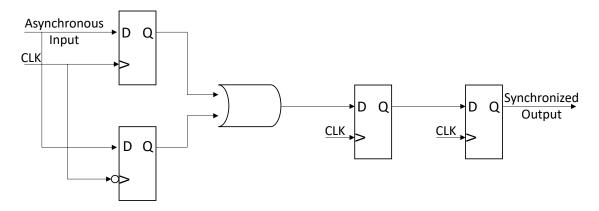

| 4.7  | Schematic diagram of synchronisation module. The two FFs sample the                  |    |

|      | asynchronous input signal with different clock phase. One FF samples                 |    |

|      | at the rising edge of the clock, while the other FF samples at the falling           |    |

|      | edge of the clock. The synchronised signal is processed into a bitwise               |    |

|      | OR logic gate. Eventually, the outcome of the logic port passes through              |    |

|      | two FF in cascade that minimise potential metastability signals                      | 84 |

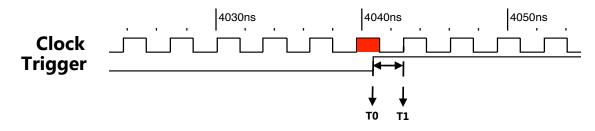

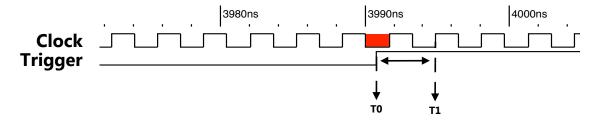

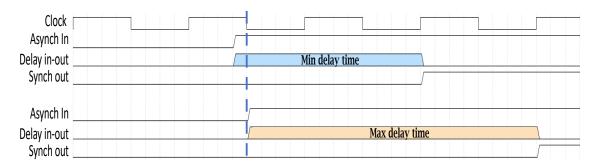

| 4.8  | Time diagram of synchronisation module. Depending on the arrival                     |    |

|      | time of the asynchronous signal, the synchronisation time of the in-                 |    |

|      | put takes $1\frac{1}{2}$ if the signal occurs immediately before the falling edge of |    |

|      | the clock, otherwise the synchronisation lasts for $2\frac{1}{2}$ .                  | 85 |

|      |                                                                                      |    |

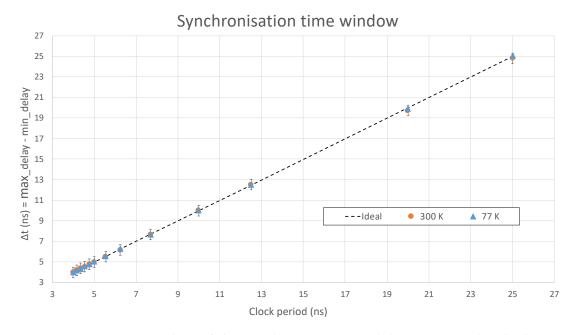

| 4.9  | The time window of the synchronisation module is respected in both                    |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | 77 $K$ and 300 $K$ temperatures. The points lay on the ideal curve within             |     |

|      | the error bar                                                                         | 86  |

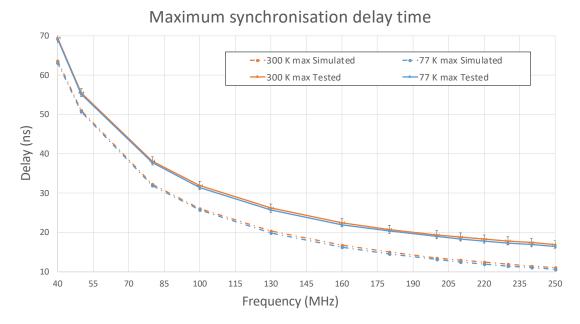

| 4.10 | Maximum delay time between input signal and synchronised output                       |     |

|      | signal. Graphs show results of simulated (dashed line) and measured                   |     |

|      | values (continuous line) at two different temperature, $300 K$ and $77 K$ .           |     |

|      | In both graphs the blue curves and the orange curves are nearly overlap,              |     |

|      | showing the same trend.                                                               | 87  |

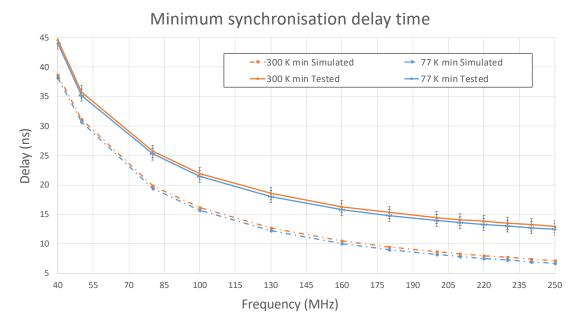

| 4.11 | Minimum delay time between input signal and synchronised output sig-                  |     |

|      | nal. Graphs show results of simulated (dashed line) and measured val-                 |     |

|      | ues (continuous line) at two different temperature, 300 <i>K</i> and 77 <i>K</i> . In |     |

|      | both graphs the blue curves and the orange curves are nearly overlap,                 |     |

|      | showing the same trend.                                                               | 87  |

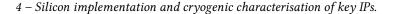

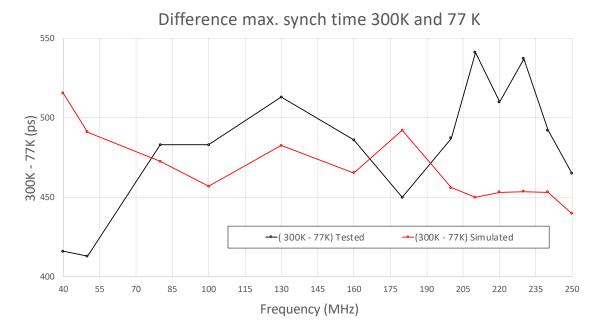

| 4.12 | Results of maximum synchronisation delay expressed as time difference                 |     |

|      | between temperature for both tested (black line) and measured (red line)              |     |

|      | values.                                                                               | 88  |

| 4.13 | Results of minimum synchronisation delay expressed as time difference                 |     |

|      | between temperature for both tested (black line) and measured (red line)              |     |

|      | values.                                                                               | 88  |

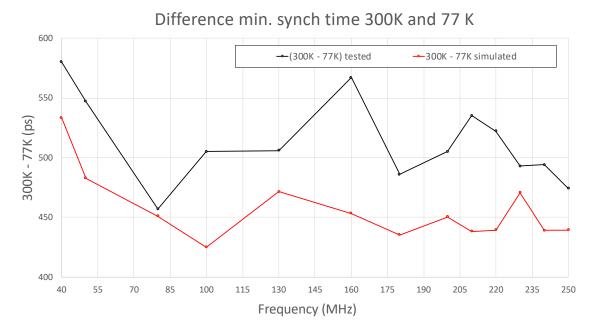

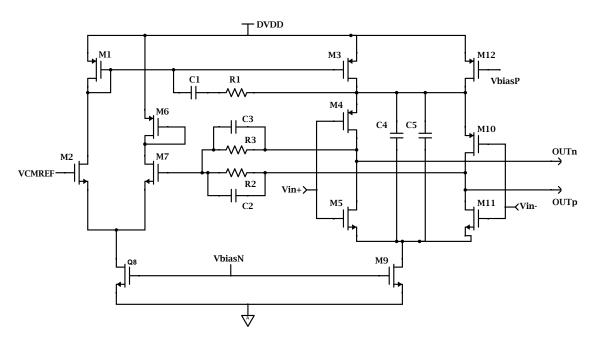

| 4.14 | Schematic diagram of the LVDS transmitter.                                            | 89  |

| 4.15 | Schematic diagram of Drive Stage of the LVDS transmitter                              | 90  |

| 4.16 | Eye diagram of LVDS transmitter driver at two different frequency: (a)                |     |

|      | 40 $MHz$ and (b) 320 $MHz$ .                                                          | 93  |

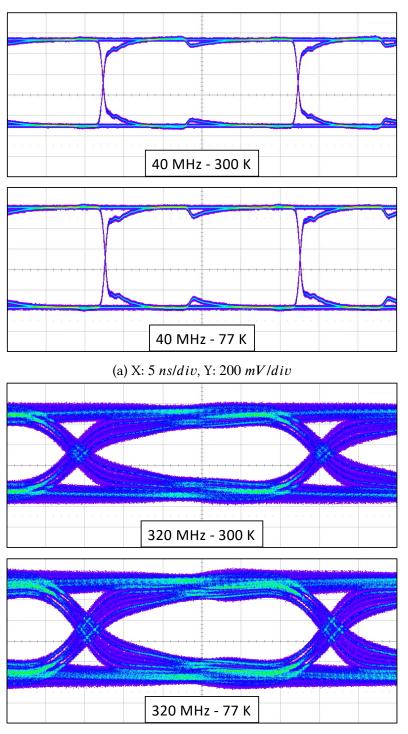

| 5.1  | Simplified block diagram of the CMOS sensor circuitry and data links                  | 97  |

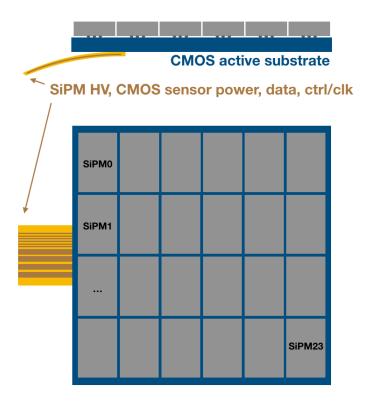

| 5.2  | Illustration of a possible embodiment of the CMOS distributed-sensor                  |     |

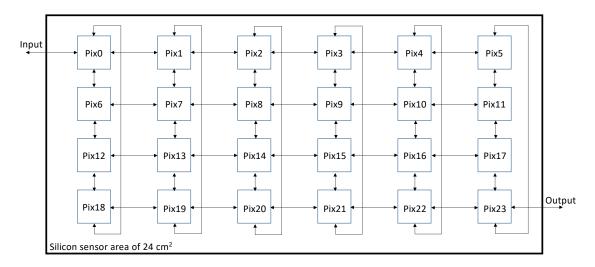

|      | active substrate for SiPM readout and assembly.                                       | 97  |

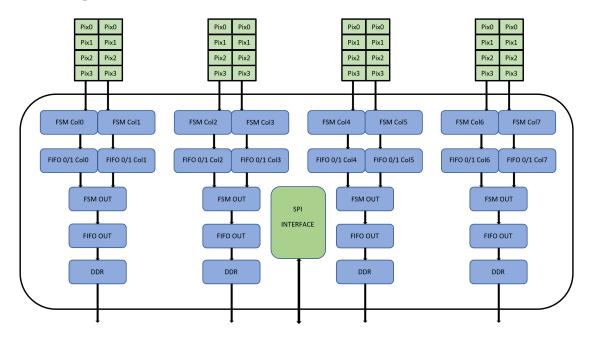

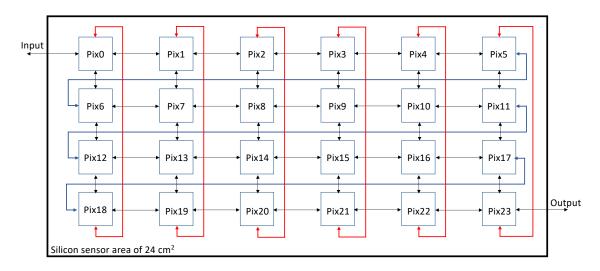

| 5.3  | Block diagram of distributed-sensor network over a sub-sensor area of                 |     |

|      | $24 \text{ cm}^2$                                                                     | 99  |

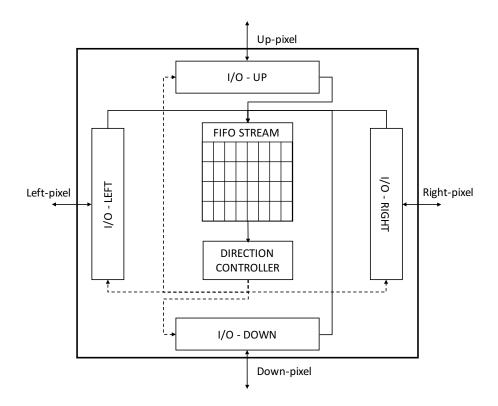

| 5.4  | Pixel Data Control block diagram.                                                     | 100 |

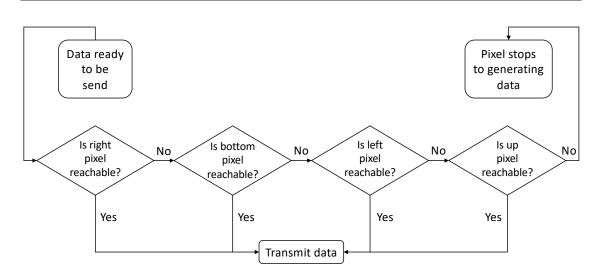

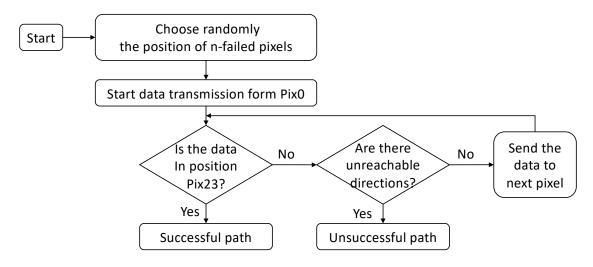

| 5.5  | Data transmission algorithm, the pixel follows these steps in order to                |     |

|      | send the data: starting from the right-direction and ends to up-direction.            |     |

|      | If all the connection are unreachable, the pixel stops to generate data.              | 101 |

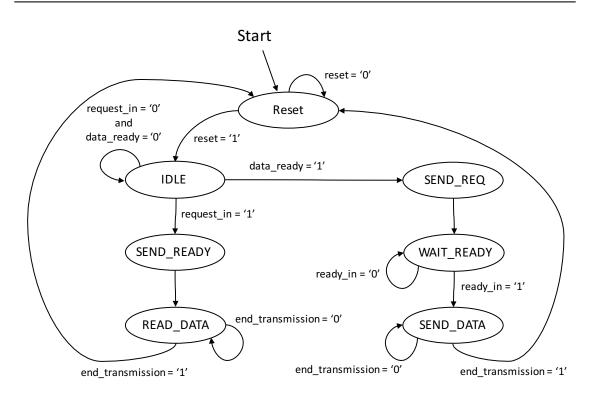

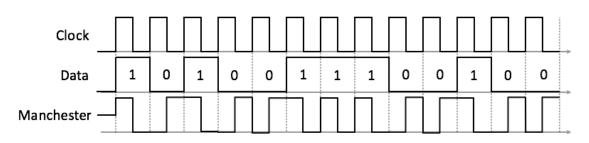

| 5.6  | Block diagram of data transmission FSM                                        | 102 |

|------|-------------------------------------------------------------------------------|-----|

| 5.7  | Example of Manchester encoded data transmission                               | 103 |

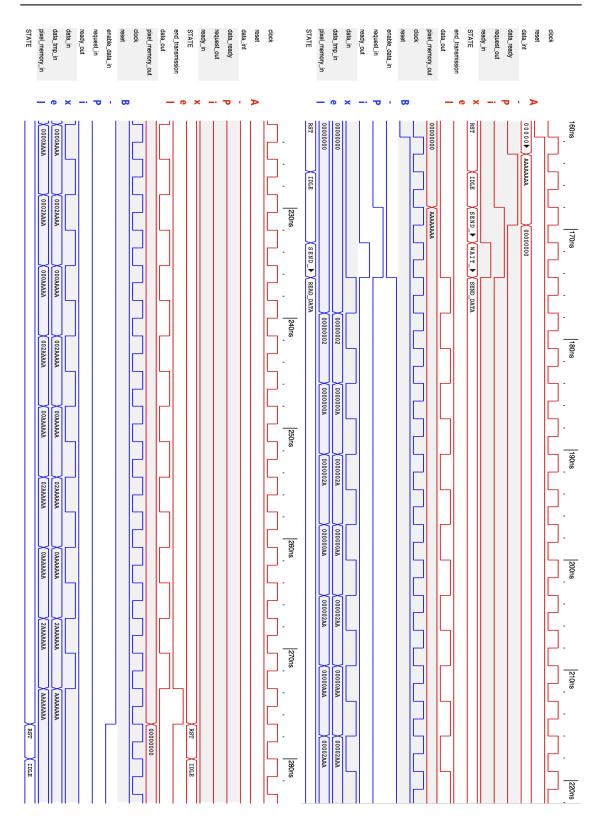

| 5.8  | Time diagram of VHDL simulation, handshaking and data transmission            |     |

|      | between two pixels                                                            | 104 |

| 5.9  | Pseudo code of DSN network                                                    | 105 |

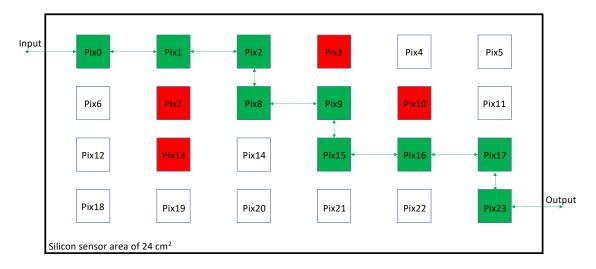

| 5.10 | Simulation example of a successful data path from Pix0 to Pix23. In red       |     |

|      | failed pixels (Pix3, Pix7, Pix10, pix13), while in green the path that the    |     |

|      | data payload took to reach the Pix23 from Pix0.                               | 106 |

| 5.11 | DSN network with inner connections (black), up-bottom connections             |     |

|      | (red) and left-right connections (blue)                                       | 107 |

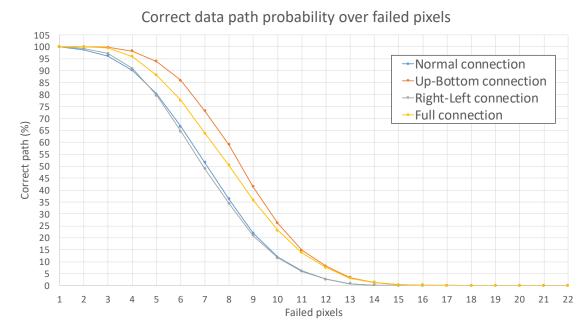

| 5.12 | Result of the simulation: x-axis shows the number of pixel failed over        |     |

|      | 24 pixels, y-axis shows the percentage of successful path                     | 108 |

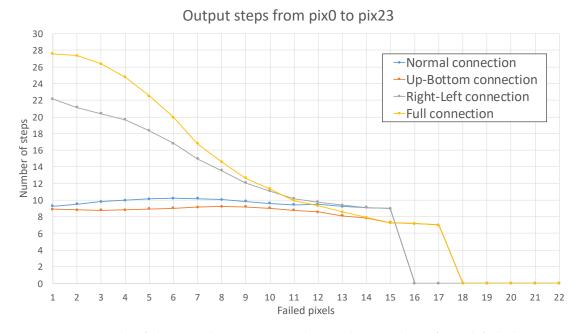

| 5.13 | Result of the simulation: x-axis shows the number of pixel failed over        |     |

|      | 24 pixels, y-axis shows the number of steps that the date takes to reach      |     |

|      | Pix23 from $Pix0$                                                             | 109 |

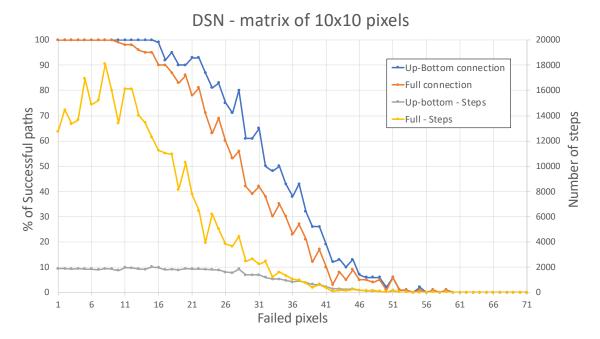

| 5.14 | Simulation results of a DSN network with 100 pixels. x-axis reports the       |     |

|      | number of pixel failed, right y-axis reports the number of steps that the     |     |

|      | date takes to reach $Pix23$ from $Pix0$ , right y-axis reports the percentage |     |

|      | of successful paths.                                                          | 109 |

## Chapter 1

# Engineering challenges in dark matter detectors

The existence of dark matter in the Universe is commonly accepted as the explanation of many astrophysical and cosmological phenomena. Roughly 85 % of the matter in the universe is in some non-baryonic form that neither emits nor absorbs electromagnetic radiation, material that scientists cannot directly observe. Dark matter particle should interact weakly or sub-weakly with photons and ordinary baryonic matter. Therefore, one of the most promising hypothesis that explains these observations is that dark matter is made of Weakly Interacting Massive Particles (WIMP) [70, 14, 33]. However, no such particles exist in the Standard Model, and none have been directly observed at particle accelerators or elsewhere. Hence, the nature of the dark matter remains unknown. WIPMs can be observed in three classes of searches: indirect detection based on the observation of gravitational effects thanks to satellites (LAT [7]), balloons (GAPS [12]) and ground-based telescope (CTA [22]); direct detection in shield underground detectors and detection at particle colliders where dark matter particles may be directly produced in high-energy collisions (DEAP-3600 [8], XENON1T [11]).

This chapter will take the DarkSide-20k experiment as example to discuss the engineer challenges in the dark matter detector.

## 1.1 DarkSide-20k

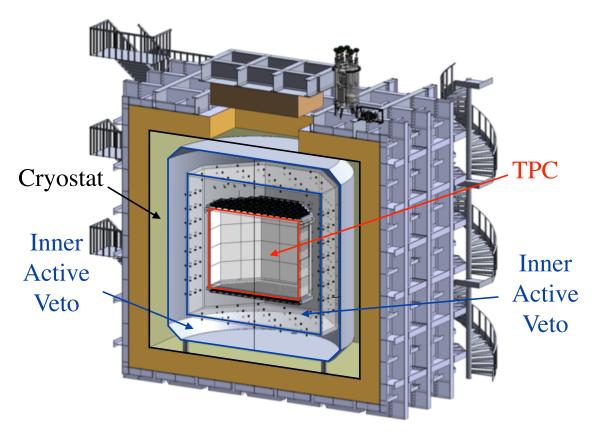

The DarkSide Collaboration, following the operational experience with the DarkSide-50 detector in a background-free mode at Laboratori Nazionali del Gran Sasso (LNGS) laboratory, is building DarkSide-20k (DS-20k), a direct WIMP detector that employs two-phase Liquid Argon Time Projection Chamber (LAr TPC) with a total active mass of 38.6t and a fiducial mass of 31.8t with 10 *cm* cut both vertically and laterally. The target sensitivity for this upgrade is to reach a cross sections of  $1.2x10^{-47}$  *cm*<sup>2</sup> for WIMPs of 1 *TeV/c*<sub>2</sub> mass, achievable in a 5 year run producing an exposure of 100t per year free from any instrumental background interaction lower than 0.1 events. The structure of DS-20k experiment, shown in Figure 1.1, consist of two detectors: the inner and the veto detector. [2, 83, 52, 13, 31]

Figure 1.1: 3D schematic of the DS-20k experiment.

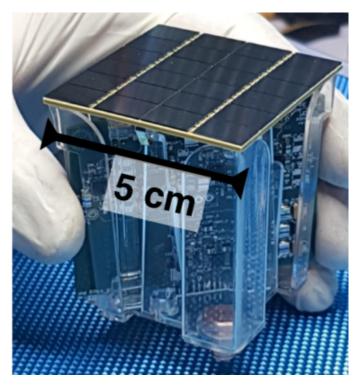

The inner detector is an octagonal shape TPC filled with underground argon (87 *K*) with a dimension from edge to edge of 3.5 *m* and a high of 2.63 *m*. Top and bottom of TPC are covered by SiPM detectors. The SiPM sensor employed in DS-20k experiment are mounted on basic Photodetector Module (PDM) such a way to include mechanical structure required to assemble all sensors and to efficiently dissipate heat in order to minimize the production of bubbles inside the detector (Figure 1.2). The single PDM has a dimension of 5 *cm* × 5 *cm* and it is build with 24 rectangular SiPM of 12 *mm* × 8 *mm* developed by Fondazione Bruno Kessler (FBK) [1]. The characteristics of SiPM required for this experiment are: a PDE parameter equal or greater than 45% at 420 *nm* wavelength and a total correlated noise probability lower than 60%.

Figure 1.2: Single PDM of  $5 \times 5cm^2$  has mounted 24 SiPMs of  $12 \times 8 mm^2$  each. The structure comprises also the readout electronics [21].

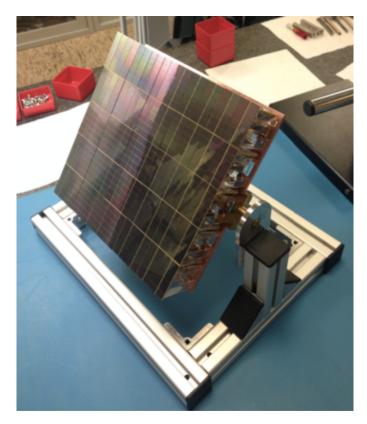

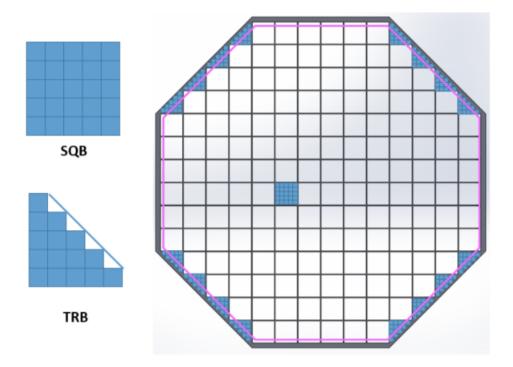

PDMs are then combined in two different shapes: Square Board (SQB) and Triangular Board (TRB) motherboards. Each SQB contains 25 PDMs and are used to cover the majority of active area of the bases of TPC. Figure 1.3 depicts the first fully mounted motherboard structure of a SQB. While TRB are bild with 15 PDMs and are used to fill remaining holes of the octagonal shape. The motherboard structure is made such that each PDM can be easily removed and replaced, during the assembly and construction phase, with a new one in case of a failed sensor. Inside the inner detector there are 8280 PDMs equally distributed on the top and on the bottom of the TPC for a total area of 20.7  $m^2$ . The Fig.1.4 shows the pattern scheme of motherboards distributed at the base of TPC detector.

Figure 1.3: Single SQB motherboard fully equipped with 25 PDMs.

The energy deposited in the LAr by an energetic charged particle, electron or nuclear recoil results in a production of excited and ionized argon atoms that carry out a formation of argon excimers decaying thorough emission of scintillation light. This first instant light contains two components with different time constant of emission, the combination of both is marked as S1. This signal is used for energy determination and pulse-shape discriminator. LAr scintillation has a wavelength of 128 *nm* that is absorbed in most of the materials, therefore a wavelength shifter must be used to cover all the area that the light will hit. The first scintillation produces ionization electrons that escape from the recombination are accelerated through a strong electric field to the

Figure 1.4: Patterning scheme of the motherboards on the base surface of the TPC.

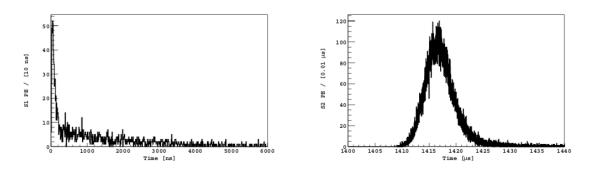

top of TPC, where gaseous Argon reacts with those electrons generating a secondary scintillation signal proportional to the ionization charge, marked as S2. This secondary signal is used for energy and 3D position of the event, the z coordinate is recovered from the drift time between S1 and S2, while the x/y coordinates are given from the pattern of light in the top photosensor area of the TPC. Figure 1.5 shows a full simulation of S1 and S2 signal in TPC detector. The S2 signal generated from the gas layer is mainly detected by top SiPM, while S1 signal is distributed approximately on both top and bottom sensors and it produces at maximum 1*PhotonElectron(PE)* per tile, for expected  $3.3 \times 10^3$  noise hits during the drift time. The S2 signal is a sum of pileup photons, and it lasts for 20  $\mu s$ . The number of photons depends on mainly on the details of LAr TPC design, where half of the photons may be concentrated on a few PDMs. The single sensor may produce 4000 *PE* at a peak rate of 0.4PE/ns.

SiPM arrays are placed above the anode and below the cathode and are set on the top and on the bottom of TPC in order to detect both light scintillations with high efficiency. Each PDM will also embed a cryogenic preamplifier that amplifies and shapes the signal before it is sent to a signal transmitter. It must be pointed out that all components

Figure 1.5: Simulation of arrival time of S1 (left) and S2 (right) signals in DarkSide-20k experiment. [2]

making the detector, like the cryostat, the LAr TPC, the SiPMs and cables, must be made from material of the highest radiopurity to keep backgrounds as small as possible in order to reduce any contamination to the measurements. Therefore, the SiPMs on the same PDM are grouped in a single readout channel, in order to reduce the total mass of signal cabling and the number of flanges. The SiPM sensors typically have a total terminal capacitance in the order of 50  $pF/mm^2$ . This implies a careful design of the readout electronics circuits and SiPMs connection scheme on the tile in order to maximise the signal to noise ratio. The aim in DS-20k is to operate with 8280 channels, each as a single analogue element which is transmitted outside the cryostat layer and digitized by a DAQ system placed in the warm area.

A correlated S1 and S2 event rate of 45 Hz is expected in the DS-20k experiment. The average event rate in the single channel is dominated by the SiPM's Dark Count Rate (DCR), where the experiment specification requests about 250 Hz per single module, therefore total expected rate for the TPC is about 250  $MHz \times 8280 = 2.07 MHz$ .

The veto detector surrounds the TPC, the total volume is composed by an Inner Active atmospheric argon Buffer (IAB) surrounding the LAr TPC, a passive Gd-loaded pure polymethyl methacrylate shell an Outer Active atmospheric argon Buffer (OAB). AAr scintillation light will be detected employing SiPM's and dedicated front-end electronics. The contamination of both buffer's signal will be used to mark and reject neutroninduced signals.

#### 1.1.1 SiPM readout in DS-20k

The SiPM readout electronics for the DS-20k experiment has been developed considering the single PDM tile equipped with 24 SiPMs [27, 28]. The discrete electronics will be mounted with the sensor module inside the cryogenic environment. Therefore, all the system has been designed considering the low temperature requirement, and in particular the materials employed have been chosen in order to be immersed in the LAr. Placing the readout electronics inside the cryostat allows to minimize the capacitance at the input of front-end amplifiers and to improve the signal integrity [62].

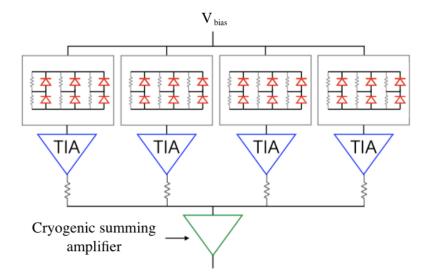

The tile is divided in 6 SiPMs quadrants and each of them is read with an independent low-noise Transimpedance Amplifier (TIA) based on *LMH6629* from Texas Instrument for high-speed operational amplifier [29]. Then a second-stage amplifier is used to sum the four TIAs and bring out the analogue signal from the cryostat. The schematic diagram of this circuit is depicted in Figure 1.6, where the SiPM inside the single quadrant are placed in three branches with two sensors in series. This topology allows to reduce the noise since the series arranging reduces the detector capacitance seen from the TIA. The cryogenic summing amplifier uses the operational amplifier *LMH6624* from Texas Instrument [30]. The signal gain is 10 *V/V*, while the noise gain is 41. The maximum bandwidth achievable is 36 MHz at room temperature and 30 MHz at cryogenic temperature.

Figure 1.6: Schematic diagram of SiPM sensor of DS-2-k experiment.

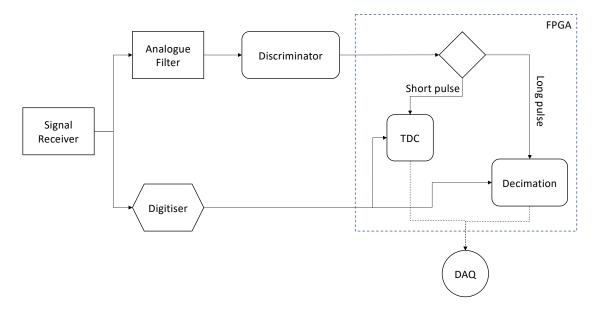

The amplified analogue signal is then driven outside the cryostat and digitised by a Data Aquistition (DAQ) system. The DAQ system digitizes each channel in order to characterise each PDM signal in terms of the work function, pulse shape, single photon response, dark rate, stability in time, correlated pulses, and robustness to mechanical stress tests. Figure 1.7 depicts the schematic diagram of the DAQ system developing for DS-20k experiment. The DAQ is a multi channel board hosting fast 14 – *bit* Analog to Digital Converter (ADC) and 125 MS/s sampling rate, linked to Field-Programmable Gate Array (FPGA) for digital signal processing. The analogue filter will minimize the rate of fake rates, depending on the SNR of the cryogenic readout electronics. The FPGA will choose the short pulse (case S1) or long pulse (case S2) path according to the length of the discriminator pulse. In case of S1 signal, a TDC algorithm will search for the time of the event and its amplitude. While in case of S2 signal, the corresponding samples will be down-sampled with a CIC filter to frequency compatible with the signal (about 10 MHz). The DAQ is trigger-less, with the system clock frequency of 1 Hz. The connection with this system and an external computer will be through a 1 Gbit/s to 10 Gbit/s Ethernet connection.

Figure 1.7: Schematic diagram of data acquisition system.

## 1.2 SiPM signal digitisation on-cold

In DS-20k, the current solution to readout SiPM sensors of the TPC are based on discrete electronics that provides 8280 analogue cable connection signals to the outside DAQ system [2]. This thesis addresses the technology and engineering challenges of future designs that implement the signal digitisation on-cold, where the SiPM sensor pulse is processed and digitised by CMOS integrated electronics working at cryogenic temperature. The digital data payload generated by the cold photoelectronics module can be further multiplexed and serialised, thereby reducing the number of fibers required for data transmission.

Two different approaches can be evaluated. The first case is based on cryogenic ADC [85], where a high resolution converter is placed after the analogue readout circuit and waveform digitisation is performed. In this case, the ADC must ensure a sampling rate high enough to allow signal analysis in the warm environment. Therefore, the DAQ system must be designed accordingly to the ADC in order to sustain the output data rate.

This work assumes that, using a more aggressive pixelisation of the photosensor, a simpler readout circuit based on event-discriminator and Time to Digital Converter (TDC) can be employed to perform a single-photon timestamping of the arrival time and charge information of the event detected by SiPMs. In this way, signal digitisation can be brought into the cold volume without the need of complex large dynamic range ADCs. Moreover this solution allows to reduce the single channel readout area, thereby reducing the sensor capacitance at the input of each front-end amplifier. As a consequence, from a system-level perspective, the same signal-to-noise ratio can be achieved with lower current per front-end channel, maintaining the overall power dissipation comparable to that required in solutions adopting analogue summing of SiPM signals. The output data rate is reduced to transmitting only relevant information of the detected event. This solution also reduces dramatically the complexity of the DAQ system, where a simpler FPGA is enough.

State of art of ASICs employing single-photon detection technique are showed and discussed in Section 2.2, in particular readout ASICs for analogue and digital SiPM. In Chapter 3 the design of a first prototype suitable for cryogenic SiPM readout is presented.

## **Chapter 2**

# Advanced readout concepts for photon detectors

Silicon Photomultiplier (SiPM) [26, 38] are solid-state light sensors which robustness, compactness and compatibility with magnetic field, high photodetection efficiency and gain make them strong candidates for a wide range of applications and detectors in the fields of high-energy physics [72], medical imaging [73, 15, 80], dark matter detection experiment [42, 23] or automotive [10].

In this chapter a brief introduction of SiPM working principle is given and examples of read-out architectures are presented.

## 2.1 Silicon photomultipliers

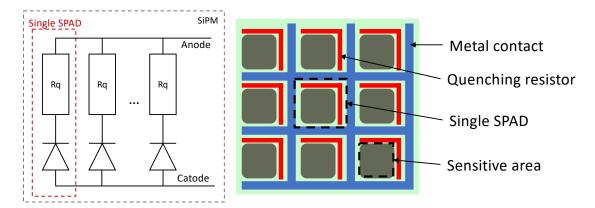

SiPMs are solid-state devices based on two dimensional arrays of 100 to several 10000 Single-Photon Avalanche Diodes (SPADs) with typical dimensions between  $10 \times 10 \ \mu m^2$  and  $100 \times 100 \ \mu m^2$  [64]. The single SPAD is a photo-diode based on a silicon junction that is biased beyond the breakdown voltage and operates in Geiger mode.

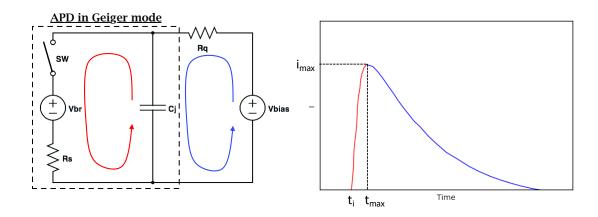

A photon absorbed in the depletion region of the SPAD generates an electron-hole pair. These charge carriers thanks to the high electric field applied to the diode, initiates the so called impact ionization effect<sup>1</sup> that produces other electron-hole pairs. Thus, an avalanche of charge carriers cross the SPAD generating a signal from a single photon. The bias voltage of the SPAD must be quenched in order to be able to detect another photon. The schematic circuit of SiPM is depicted in Figure 2.1. The single SPAD cell is defined by the sensitive area where the photons are absorbed and by the quenching resistors.

Figure 2.1: Electric model of SPAD on the right. On the left the time response of the circuit.

The signal generated by the SPAD cell is always independent of the number of photons that have been absorbed. Therefore, each SPAD generate the signal of a single photon (1 Photon Electron (PE)). Figure 2.2 depicts an equivalent circuit model of a SPAD and the pulse shape in time delivered by this circuit. The capacitor  $C_i$  is the SPAD

<sup>&</sup>lt;sup>1</sup>Impact ionization is the process in a material by which one energetic charge carrier can lose energy by the creation of other electron-hole pairs.

diode,  $R_s$  is the series resistance,  $R_q$  is the quenching resistance and  $V_{br}$  is the breakdown voltage, where  $V_{bias}$  is greater than  $V_{br}$ .

Figure 2.2: Electric model of SPAD on the right. On the left the time response of the circuit.

Closing the switch *SW* simulates the detection of a photon and the avalanche signal through the  $C_j$  capacitance is generated with a fast component according to Equation 2.1. When the switch *SW* is open, the diode is recharging in the slow component according to the Equation 2.2. Therefore, the output signal is characterised by two components, a fast and sharp signal, followed by a slow and long tail. This tail is primarily due to the recharge that flows through the quenching resistor. The maximum amplitude, which is the signal of 1 *PE*, is proportional to the over-voltage applied to the circuit as defined in Equation 2.3.

$$i_{fast}(t) = 1 - e^{(\frac{-t}{R_s C_j})}$$

(2.1)

$$i_{slow}(t) = e^{\left(\frac{-t}{RqC_j}\right)} \tag{2.2}$$

$$i_{max} = \frac{V bias - V br}{Rq + Rs}$$

(2.3)

The gain value of the SPAD gives the amount of carriers flowing during the avalanche phase. Considering the electrical model in Figure 2.2 is it possible to define the gain value as:

$$Gain = \frac{(Vbias - Vbr) Cj}{q0}$$

(2.4)

Where q0 is the electron charge of  $1.602 \cdot 10^{-19}$  C, the voltage difference *Vbias-Vbr* gives the over-voltage applied to the SPAD cell and *Cj* is the diode capacitance. Typically, the gain value is in the order of  $10^6$  thus generating a well defined photon pulse above the noise level. Attention must be paid to the *Vbias* voltage that may change over temperature, while *Cj* is proportional to the size of the SPAD diode. A bigger cell gives a higher gain and a better photon number resolution, but it is slower to recharge. The well-defined gain gives the analogue SiPM very good photon number resolving capabilities, which can be estimated by the amplitude spectrum. SiPMs with large areas generate typically smaller signal amplitude due to the bigger grid capacitance and parasitics capacitance on the long interconnections between the sensor and the bonding pads that act as a low pass filter on the output signal.

#### 2.1.1 **Photon detection efficiency**

Photon Detection Efficiency (PDE) defines the probability of a SiPM to detect a photon and can be expressed as the ratio between the number of photons detected and the total number of photons impinging on the detector:

$$PDE = \frac{N_{ph\_detected}}{N_{ph\_arrived}} = QE \cdot P_{Trig} \cdot FF$$

(2.5)

Where QE is the quantum efficiency of photoelectron conversion,  $P_{Trig}$  is the avalanche triggering probability and FF is the fill factor of the pixel. The QE is the probability a photon generates an electron-hole pair once it falls in the sensitive area of the SPAD. This depends on the reflectivity of the silicon surface and if it has been coated with an anti-reflection material. The  $P_{Trig}$  is the probability to generate an avalanche later a charge carrier. In silicon this parameter is associate to the ionization coefficient which increases by electric field, and it is higher for electrons rather than for holes. The fill factor depends on the geometry of the single SPAD, and can be expressed as the ratio between the sensitive area over the total area of the sensor. This value increases with the cell size. Combining the doping profiles for the p/n junction and the absorption

depth in silicon, it is possible to develop different flavours of SiPMs depending on the wavelength of photons [6, 60, 65].

The Single Photon Time Resolution (SPTR) is one of the important parameters that define a SiPM. This value includes the timing jitter of the detector. The SPTR is important parameter that defines the maximum resolution achievable in Time-of-Flight measurements Time-of-Flight (ToF) in high energy physics and medical application or low-light detection experiments. Normally this parameter assumes a value in the range of 180 ps - 50 ps depending on the sensor size. [5].

SiPMs can be designed in an analogue or digital fashion way[36, 69, 86, 54]. Both solutions allows to count and detect events with good sensitivity and time resolution in the order of picoseconds [43].

#### 2.1.2 Dark Count, After-Pulsing and Cross-Talk

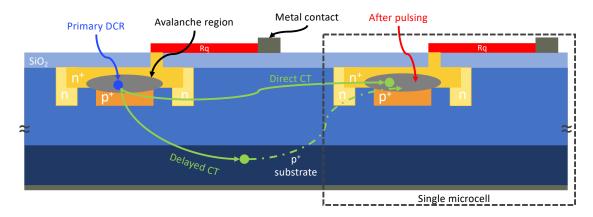

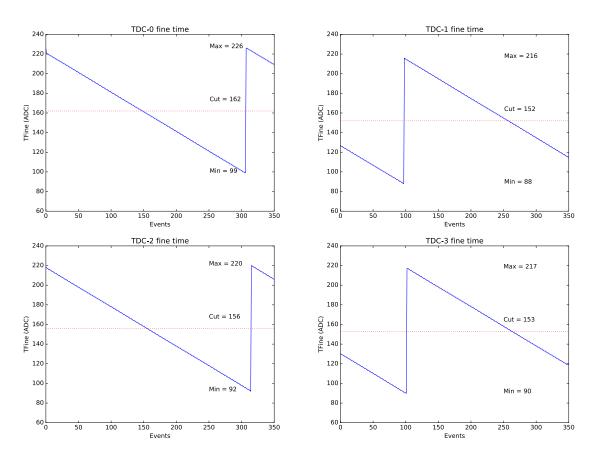

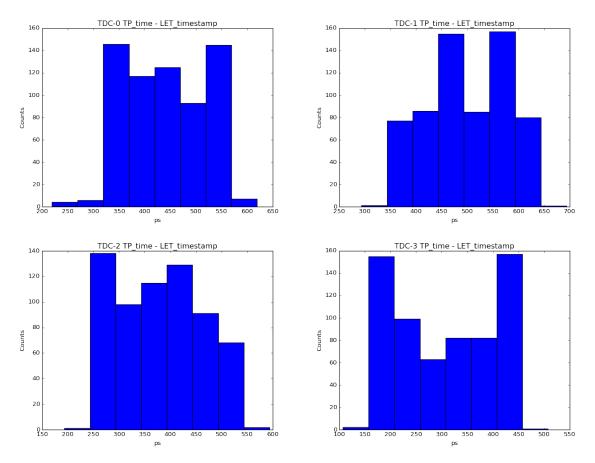

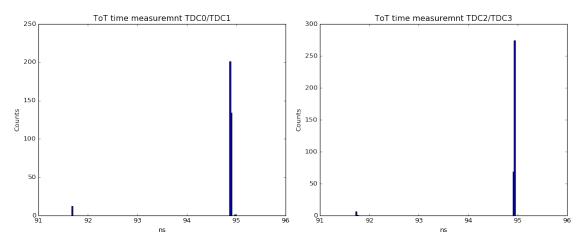

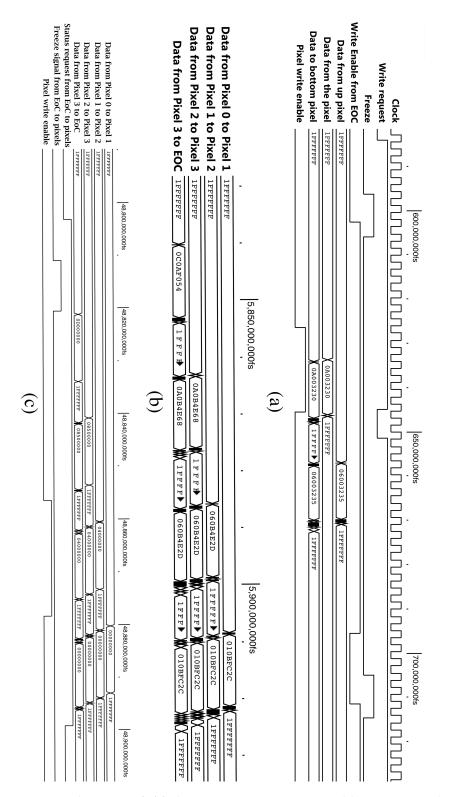

The SiPM is affected by dark noise pulses that are a production of spontaneous Geiger discharge in a SPAD in absence of photon detection. Figure 2.3 depicts a crosssection of an SiPM and shows how different dark noise source can be present inside the sensor.