## POLITECNICO DI TORINO Repository ISTITUZIONALE

### Fully Depleted MAPS in 110-nm CMOS Process With 100-300-m Active Substrate

Original

Fully Depleted MAPS in 110-nm CMOS Process With 100–300-m Active Substrate / Pancheri, Lucio; Giampaolo, Raffaele A.; Salvo, Andrea Di; Mattiazzo, Serena; Corradino, Thomas; Giubilato, Piero; Santoro, Romualdo; Caccia, Massimo; Margutti, Giovanni; Olave, Jonhatan E.; Rolo, Manuel; Rivetti, Angelo. - In: IEEE TRANSACTIONS ON ELECTRON DEVICES. - ISSN 0018-9383. - 67:6(2020), pp. 2393-2399. [10.1109/TED.2020.2985639]

Availability: This version is available at: 11583/2828873 since: 2020-05-23T17:21:32Z

Publisher: IEEE

Published DOI:10.1109/TED.2020.2985639

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

### AUTHOR QUERIES

## AUTHOR PLEASE ANSWER ALL QUERIES

PLEASE NOTE: We cannot accept new source files as corrections for your article. If possible, please annotate the PDF proof we have sent you with your corrections and upload it via the Author Gateway. Alternatively, you may send us your corrections in list format. You may also upload revised graphics via the Author Gateway.

Carefully check the page proofs (and coordinate with all authors); additional changes or updates WILL NOT be accepted after the article is published online/print in its final form. Please check author names and affiliations, funding, as well as the overall article for any errors prior to sending in your author proof corrections.

- AQ:1 = Please confirm or add details for any funding or financial support for the research of this article.

- AQ:2 = Please confirm that all authors' affiliations are accurate as shown in the first footnote.

- AQ:3 = Please provide the location and postal code for Istituto Nazionale di Fisica Nucleare—Sezione Milano.

- AQ:4 = Please provide the expansion for DUT, DAQ, and RBI.

- AQ:5 = Please provide the page range for Ref. [8].

# Fully Depleted MAPS in 110-nm CMOS Process With 100–300- $\mu$ m Active Substrate

Lucio Pancheri<sup>®</sup>, *Member, IEEE*, Raffaele A. Giampaolo, Andrea Di Salvo, Serena Mattiazzo<sup>®</sup>, Thomas Corradino, Piero Giubilato, Romualdo Santoro<sup>10</sup>, Massimo Caccia<sup>10</sup>, Giovanni Margutti, Jonhatan E. Olave, Manuel Rolo, and Angelo Rivetti

Abstract—This article presents a fully depleted monolithic active pixel sensor technology compatible with 2 a standard deep submicrometer 110-nm CMOS process. 3 Passive test pixels structures, produced in various flavors, have proved the feasibility of 100- and 300- $\mu$ m-thick 5 active substrates. Active pixel sensors with monolithically 6 integrated analog and digital electronics, consisting of a 24  $\times$  24 array of pixels with 50- $\mu$ m pitch, have been shown to be fully functional when operating in the full depletion mode. 9 Characterization results obtained with a proton microbeam 10 and a <sup>55</sup>Fe radiation source are presented and discussed. 11

Index Terms-CMOS, monolithic active pixel sensor 12 (MAPS), radiation detector, silicon. 13

### I. INTRODUCTION

ONOLITHIC active pixel sensors (MAPSs) are emerg-15 ing as a viable alternative to hybrid pixels in charged-16 particles' detection and high-energy photons imaging, showing 17 advantages in both performance and overall costs per unit 18 area [1]–[3]. 19

The reconstruction with the highest precision of the 20 perigee parameters of charged-particle trajectories in a dense

Manuscript received February 7, 2020; revised March 30, 2020; accepted March 30, 2020. This work was supported in part by the Istituto Nazionale di Fisica Nucleare (INFN), CSN5, and in part by the H2020 Project AIDA-2020 under Grant 654168. The review of this article was arranged by Editor J. Huang. (Corresponding author: Lucio Pancheri.)

Lucio Pancheri and Thomas Corradino are with the Dipartimento di Ingegneria Industriale, TIFPA Istituto Nazionale di Fisica Nucleare (INFN), Università di Trento, 38123 Trento, Italy (e-mail: lucio.pancheri@unitn.it).

Raffaele A. Giampaolo and Andrea Di Salvo are with the Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Turin, Italy, and also with the Istituto Nazionale di Fisica Nucleare (INFN)-Torino, 10125 Turin, Italy (e-mail: raffaeleaaron.giampaolo@to.infn.it; andrea disalvo@polito.it).

Serena Mattiazzo and Piero Giubilato are with the Dipartimento di Fisica e Astronomia, Istituto Nazionale di Fisica Nucleare-Sezione di Padova, Università di Padova, 35131 Padua, Italy (e-mail: serena.mattiazzo@unipd.it; piero.giubilato@unipd.it).

Romualdo Santoro and Massimo Caccia are with the Dipartimento di Scienze ed Alta Tecnologia, Università dell'Insubria, 22100 Varese, Italy, and also with the Istituto Nazionale di Fisica Nucleare-Sezione Milano.

Giovanni Margutti is with LFoundry S.r.l., 67051 Avezzano, Italy Jonhatan E. Olave, Manuel Rolo, and Angelo Rivetti are with the Istituto Nazionale di Fisica Nucleare-Torino, 10125 Turin, Italy.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org

Digital Object Identifier 10.1109/TED.2020.2985639

environment calls for pixel pitches of tens of micrometers, low material budget, a high signal-over-noise ratio, and limited diffusion of the charge carriers originated by the impinging particle. These specifications can be obtained with a monolithic design implemented on a fully depleted (FD) high-resistivity substrate. As a consequence, FD-MAPSs are raising a signif-27 icant interest in the high-energy physics community [4], [5].

FD-MAPSs have also been proposed for X-ray imaging [6], where an active substrate of 300-500  $\mu$ m would enable an efficient detection of photon energies up to 15 keV. Other applications, such as medical particle tomography and tracking in space experiments, would benefit from the low material budget, fine pixel pitch, and low power consumption offered by MAPS sensors [7], [8].

As a general trend in the development of pixel sensors, the complexity of on-chip digital functions is increasing, making it easier to integrate and deploy a complete sensor system. Moreover, event-driven readout schemes are frequently adopted to reduce power consumption and, in turn, relax the requirements of the cooling systems, impacting on the overall system material budget. To these purposes, very scaled process nodes should be used to reduce the area and to increase the speed of on-chip digital electronics.

The latest FD-MAPS design efforts in the high-energy physics community are adopting 180- and 150-nm process nodes. Most of the developments, in this respect, have been devoted to the implementation of devices with a depletion region ranging from a few tens of micrometer and hundreds of micrometer [4], [5]. In [4], large depletion regions are obtained by including the electronics inside a deep n-well that is used as a collection node for the electrons generated by the incident charged particles. This approach has demonstrated an excellent radiation hardness and a fast charge collection, but the sensor capacitance is relatively large, and a nonnegligible part of the pixel area cannot be used to accommodate the readout circuits. Scaling to very small pixels is thus very challenging while using such topology.

An alternative approach, arising from an evolution of the 59 pixels designed for the ALICE detector [1], uses small sensing 60 nodes while implanting a low-doped n-type region below the 61 electronics [5]. In this way, most of the generated charges can 62 be collected by drift, while the area and the capacitance of 63 the sensors are maintained small, granting scalability toward 64

0018-9383 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

AQ:1

AQ:2

14

22

23

24

25

26

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

small pixel sizes. This approach, although excellent for particle tracking, cannot be easily extended to an active thickness in excess of 100  $\mu$ m since the space-charge region extends from the top surface of the sensor, thus limiting the applicable voltage at the sensor top side.

The possibility of FD thick substrates in CMOS-integrated sensors has been first explored in [9], demonstrating an FD sensor with p-type substrate and a n-type backside implantation. In the first prototype, the electronics were made entirely of p-type transistors. A similar approach was adopted in [10], using a CMOS process with n-type substrates and implanting a p+ region on the back.

Full depletion can also be obtained using a silicon-oninsulator process. Although the radiation damage of the insulator oxide poses several challenges related to parameter drift in the transistor characteristics, the latest advancements have greatly improved the radiation hardness of the process, and sensors with depletion regions up to 500  $\mu$ m thick have been demonstrated [11].

In this article, we present a technology platform for the implementation of FD MAPS based on a modified 110-nm CMOS process. The process node was chosen to enable the in-pixel implementation of complex digital functions while keeping low prototyping and production costs. Backside processing was used to create a junction on the bottom surface that is biased to deplete the whole sensor substrate.

This article is structured as follows. Section II discusses 91 the simulated characteristics with reference to geometry and 92 process parameters. In Section III, the design of pixel test 93 structures and a small array of active pixels with integrated 94 electronics are presented. Section IV presents the results of 95 the characterization of the arrays compared with the expec-96 tations according to the simulation. The perspectives for this 97 technology are highlighted in Section V. 98

99

### II. SENSOR CONCEPT

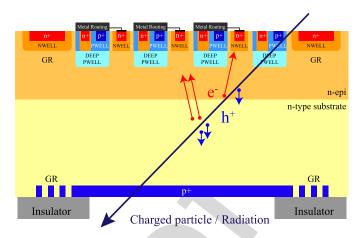

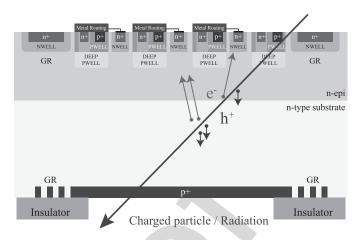

The process was developed starting from a 110-nm industrial CMOS with 1.2-V transistors and six metal layers. A few add-ons were necessary to allow for full substrate depletion with electron collection at the sensing electrodes. A concept cross section of the pixel array is shown in Fig. 1 [12].

The standard p-type substrate was replaced with an n-type 105 floating zone material. Wafer thinning and backside lithog-106 raphy were necessary to introduce a junction at the bottom 107 surface, used to bias the substrate to full depletion while 108 maintaining a low voltage at the front side. A shallow boron-109 doped region was implanted on the rear side of the wafer, and 110 the dopants were activated by laser annealing. Since, at large 111 wafer thicknesses, the voltage needed for sensor full depletion 112 exceeds 150 V, a termination structure composed of multiple 113 guard rings was introduced. 114

A deep p-well scheme was used to prevent the n-wells hosting p-MOSFETs from collecting the charge generated by radiation in the substrate. Care had to be taken to limit the punchthrough current between the back-side junction and the deep p-well at sensor full depletion. A good control of punchthrough could be obtained either by increasing the bias

Fig. 1. FD pixel sensor cross section.

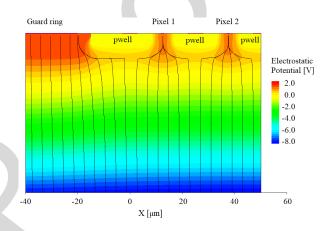

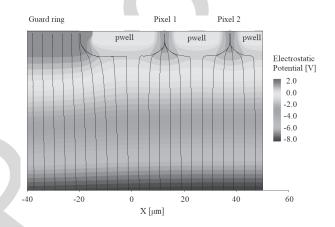

Fig. 2. Simulated 2-D potential profile and electric-field lines at full depletion. The simulation domain includes part of the guard rings and 2 pixels with  $25\mu$ m pitch. Only the sensor surface region is shown.

voltage at the pixel sensor nodes or by increasing the n-dopant121concentration below the p-wells. Since the sensors had to be122directly coupled to the low-voltage electronics, the second123solution was adopted, by adding an n-doped epitaxial layer,124having a resistivity lower than the substrate, to the process125flow.126

TCAD simulations were used to tune the process parameters. The simulated potential profile at full depletion for a domain, including 2 pixels and part of the surface guard ring, is shown in Fig. 2. Electric-field lines are orthogonal to the sensor surface up to the bottom of the deep p-wells, and then, they deviate horizontally toward the collection electrodes.

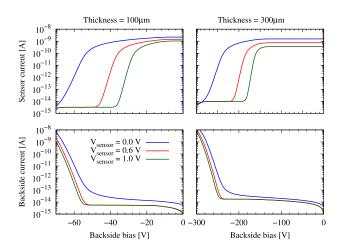

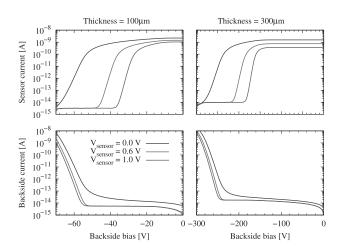

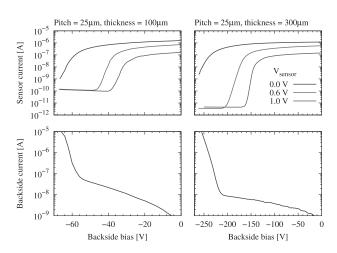

The full depletion and punchthrough voltages were simu-133 lated on this domain by introducing a small unbalance (10 mV) 134 between pixel and guard ring bias voltages. The current 135 flowing at the sensing electrodes and at the backside as a 136 function of applied backside bias is shown in Fig. 3. At low 137 reverse voltage, the substrate is not FD, and resistive paths 138 exist between the pixels and the guard ring, leading to a macro-139 scopic current. As the bias voltage is increased, a sharp current 140 drop is observed, indicating the onset of full depletion. The 141 depletion voltage is reduced by increasing the voltage applied 142 at the front side to the sensor nodes. If the backside voltage 143 is further increased, a punchthrough current starts flowing and 144

129

130

131

Fig. 3. Simulated sensor and backside current as a function of backside voltage for two values of sensor thickness [100  $\mu$ m, (left) and 300  $\mu$ m (right)]. Pixel pitch is 25  $\mu$ m.

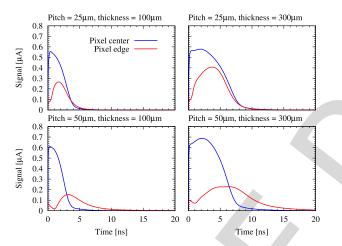

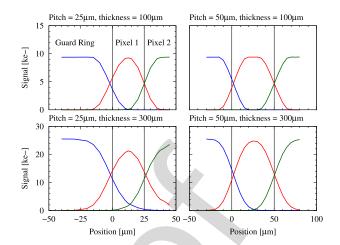

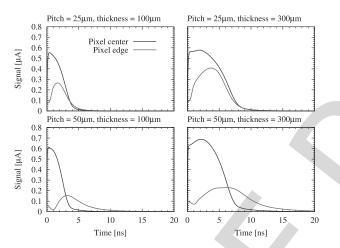

Fig. 4. Simulated transient current signal with an incident MIP for two different values of sensor thickness [100  $\mu$ m (left) and 300  $\mu$ m (right)] and pixel pitch [25  $\mu$ m (top) and 50  $\mu$ m (bottom)].

eventually reaches very large values. The voltage difference 145 between breakdown and punchthrough voltages depends on the 146 sensor bias. At a sensor voltage between 0.6 and 1 V that can 147 be applied if the sensor is directly coupled to the electronic 148 readout channels, the difference between full depletion and 149 punchthrough is a fraction of 10%-20% of the applied bias 150 voltage. This value is large enough to reliably accommodate 151 the operation of a pixel array, considered possible doping 152 gradients and nonuniformities between the pixels. 153

Charge collection dynamics upon the incidence of a min-154 imum ionizing particle (MIP) were also simulated. The 155 MIP was modeled as a continuous charge density of 156 80 e-h pairs/ $\mu$ m, orthogonal to the sensor surface and extend-157 ing throughout the sensor thickness. With reference to the sim-158 ulation domain shown in Fig. 2, several positions of incidence 159 were considered for the MIP. The current signal generated at 160 the sensor is shown in Fig. 4 for two different MIP incidence 161 positions, two values of pixel pitch (25 and 50  $\mu$ m), and two 162 values of sensor thickness (100 and 300  $\mu$ m). As expected, 163 complete charge collection is observed in less than 5 and 10 ns. 164

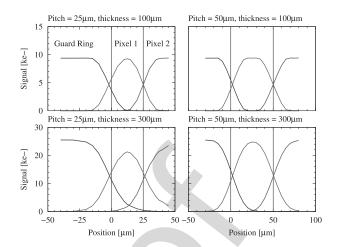

Fig. 5. Simulated collected charge at the sensor periphery as a function of the position of the incident particle for two different values of sensor thickness [100  $\mu$ m (top) and 300  $\mu$ m (bottom)] and pixel pitch [25  $\mu$ m (left) and 50  $\mu$ m (right)].

respectively, for 100 and 300  $\mu$ m thickness when the MIP is 165 incident in the center of the pixel. If the MIP is incident at 166 the pixel periphery, the collection speed depends on the pixel 167 pitch; at 50- $\mu$ m pitch, the collection time approximately dou-168 bles since the charge generated in the substrate first reaches the 169 bottom of the deep p-well and then drifts horizontally toward 170 the collection node. Even considering this worst case situation, 171 however, the charge is completely collected within 20 ns. 172 In 25- $\mu$ m pixels, on the contrary, the collection time is only 173 slightly degraded, as a result of the smaller horizontal distance 174 traveled by electrons generated at the pixel periphery. 175

The integrated charge as a function of the MIP incidence position is shown in Fig. 5. Charge sharing between the pixels for two values of thickness and pixel pitch can be observed. As expected, sharing slightly increases by increasing the pixel pitch and sensor thickness, but, in all the cases considered here, the effect is confined to the nearest neighboring pixels.

### III. ACTIVE PIXEL ARRAY AND TEST STRUCTURES

A 576-active pixel array was designed as a test bench to val-183 idate the performance of the proposed technology [13], [14]. 184 The pixels are organized in four sectors, each one consisting 185 of 6 columns of 24 pixels. An end-of-column (EoC) block 186 manages the column logic, handling pixel configuration and 187 controlling data transmission. In this way, each sector works in 188 parallel with the others. To read out the data for a single sector, 189 two clocks are used. The first controls the shift register in the 190 EoC to select the column, whereas the second one is dedicated 191 to the row shift register. In a typical case, they, respectively, 192 work at 5 and 0.2 MHz. Thus, the whole array can be read in 193 less than 30  $\mu$ s using a 5-MHz clock. 194

A single 50- $\mu$ m pitch pixel hosts both the electrode and the in-pixel electronics. The sensing electrode, together with a surrounding area clear from electronic circuits, occupies a region of 20  $\mu$ m × 20  $\mu$ m, and it is centered in the pixel area. The remaining area is partitioned between the analog front end and the digital logic. 200

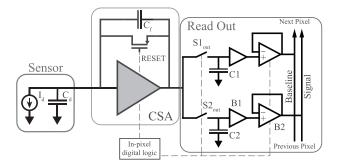

Fig. 6. Pixel readout block scheme.

The readout chain is shown in Fig. 6. The radiation-201 generated current signal is amplified by a charge-sensitive 202 amplifier (CSA) circuit. A sample and hold circuitry, designed 203 to perform correlated double sampling (CDS) operation, 204 follows the CSA. Metal-insulator-metal (MIM) capacitors 205 are used to store the signal at this stage. Two analog buffers are 206 included to transmit the analog output signal along the column. 207 The charge-integrating amplifier, designed to maximize the 208 signal-to-noise ratio (SNR), is based on a telescopic cascode 209 architecture with a feedback capacitor  $C_f$  and a minimum-210 size pMOS reset switch.  $C_f$  has been chosen equal to 5.8 fF, 211 giving a postlayout simulation gain of 130 mV/fC. The output 212 dynamic range of the amplifier is defined by considering the 213 expected signal for an MIP in a  $300-\mu$ m-thick detector. Thus, 214 for 3.8 fC (corresponding to 80 e-h pairs/  $\mu$ m in 300  $\mu$ m 215 thickness), the output voltage signal matches the linear output 216

CSA

In-pixel ligital logi

range of the amplifier, which is around 500 mV. This gain also 217 ensures a good SNR for MIPs in substrates with a thickness 218 as low as 50  $\mu$ m. 219 The pixel unit is also equipped with a digital logic to

220 manage data readout and to define the pixel functions. A 3-bit 221 in-pixel register allows to switch OFF defective pixels, enable 222 the injection of a test pulse for the electrical characterization 223 of the readout electronics, and enable the buffer amplifier for 224 data transmission. To study digital noise coupling between 225 the analog and digital sections of the design, each pixel 226 accommodates a digital buffer made by 18 elements, each with 227 a bandwidth of 5 GHz, designed to inject digital noise. 228

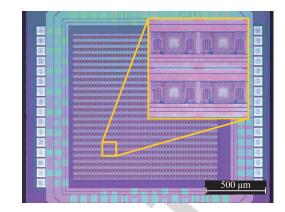

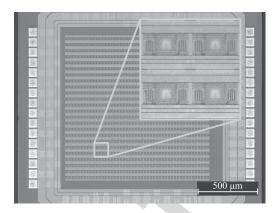

229 Fig. 7 shows a micrograph of the active pixel array, with a group of 4 pixels in the magnified area. At the center of 230 the pixels, an area free from metal is present to allow the 231 illumination from the top. This feature was included to carry 232 out studies with laser sources. 233

The pixels were designed for a power consumption around 234 6  $\mu$ W. Providing a power supply of 1.2 V, the power consump-235 tion of the pixel array in the static and dynamic conditions 236 is, respectively, 3.84 and 6.4 mW, without considering the 237 contribution of digital and EoC logic. 238

Small pixel arrays, formed by pixels free from electronic 239 readout circuits, were designed to allow additional flexibility 240 in the experimental evaluation of sensor and process charac-241 teristics [12]. In these arrays, these are termed pseudomatrices 242 (PMs) since all the sensing electrodes in the pixels are con-243 nected to the same pad, and pixels with both 50- and  $25-\mu m$ 244 pitch were included. 245

Fig. 7. Micrograph of active pixel array. Inset: close-up of 4 pixels.

TABLE I **PRODUCED SENSOR SAMPLES**

| Sensor type         | Thickness [µm] | Pixel Pitch $[\mu m^2]$      |

|---------------------|----------------|------------------------------|

| Full Sensor         | 300            | $50 \times 50$               |

| PM                  | 100            | $25 \times 25, 50 \times 50$ |

| РМ                  | 300            | $25 \times 25, 50 \times 50$ |

| PM Pixel pitch [µm] | Pseudo-pixels  | Metal width [µm]             |

| $25 \times 25$      | $16 \times 18$ | 8                            |

| $50 \times 50$      | $8 \times 9$   | 15                           |

Two fabrication runs, including both pixel arrays and 246 PM test structures, were produced on high-resistivity wafers 247  $(\rho > 2 \text{ k}\Omega \cdot \text{cm})$  that were thinned to 300 and 100  $\mu$ m prior 248 to backside processing. A summary of the devices presented 249 in this article is shown in Table I, highlighting their main 250 geometrical characteristics. 251

#### IV. EXPERIMENTAL RESULTS

An extensive experimental test campaign has been carried 253 out on both the test structures and the active pixel arrays in 254 order to assess their functionality. This section summarizes the most meaningful results, discussed with reference to the 256 simulated characteristics presented in Section II. 257

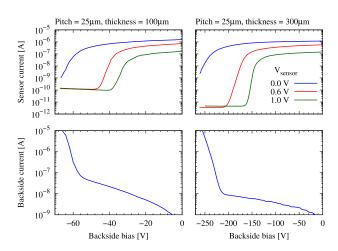

### A. Electrical Characterization

Static electrical characterizations have been performed at 259 room temperature on PM structures in order to evaluate 260 full depletion and punchthrough voltages for different pixel 261 sizes, thicknesses, and bias conditions. Current–voltage (I-V)262 curves have been measured using a four-channel semicon-263 ductor parameter analyzer. In the measurements, the same 264 conditions used for the simulations described in Section II 265 have been applied; the p-wells were biased at 0 V, the sensing 266 nodes and the guard ring were biased between 0 and 1 V, and 267 a negative bias sweep was applied to the backside contact. The 268 measured sensor and backside currents are shown in Fig. 8 as 269 a function of the backside bias voltage for PMs with  $25-\mu m$ 270 pitch. While the sensor current is plotted for three different 271 values of sensor voltage, only one curve is shown for the 272 backside current since no dependence on sensor voltage was 273 observed. 274

255

252

Fig. 8. Measured I-V curves for 100  $\mu$ m (left) and 300  $\mu$ m (right) thick PM sensors. Pixel pitch is 25  $\mu$ m.

When compared with the simulated curves in Fig. 3, 275 an excellent agreement was found in both the full depletion 276 and the punchthrough voltage for both the device thicknesses 277 and sensor bias voltages. The simulated and measured currents 278 differ by several orders of magnitude due to the different 279 sizes of the simulation domain (single pixel, 25  $\mu$ m  $\times$  1  $\mu$ m 280 in 2-D simulations) and PM sensors (400  $\mu$ m × 450  $\mu$ m total 281 active area). In the 300- $\mu$ m-thick sensors, the measured dark 282 current is more than one order of magnitude smaller than in 283  $100-\mu$ m-thick sensors. Further investigations are going on to 284 understand the origin of this difference, probably due to the 285 different processing conditions. The I-V curves measured on 286 pixels with 50- $\mu$ m pitch are very similar to the ones shown 287 in Fig. 8. 288

#### B. Microbeam Sensor Characterization 289

The PMs have been tested at the RBI microbeam facility 290 in Zagreb, Croatia [15]. The microbeam has been generated 291 using a 1-MV Tandetron accelerator capable of delivering 292 protons in the 0.5-2.0-MeV range; 2-MeV proton beams with 293  $\sigma_{\rm spot} \approx 2 \ \mu {\rm m}$  have been focused onto PM structures with 294 different pixel sizes and thickness (see Table I). Protons of 295 296 this energy have been simulated to have a Bragg peak located at a depth  $\lambda \approx 47 \ \mu m$  in silicon. As a result, the number of 297 collected carriers and, in turn, the output signal is expected to 298 be independent of the sensor thickness. The proton flux was 299 adjusted to provide a maximum hit rate of 2 kHz. 300

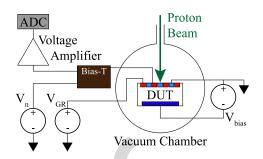

AO:4

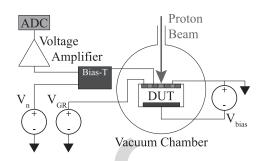

The DUTs have been wire bonded to a specifically designed 301 PCB equipped with p-i-n connectors to bias the collection 302 electrodes, guard rings, and p-wells. The bias voltages were 303 supplied by a HAMEG HMP2030 power supply, while the 304 high-voltage power supply was an NHQ 202M. As shown 305 in Fig. 9, an ORTEC 142-A bias-T preamplifier with a 306 20-mV/MeV gain has been connected between the pixel 307 array and the biasing module. An ORTEC 570 voltage 308 amplifier was connected between the preamplifier and a 309 CANBERRA 8075 12-bit 10-V ADC. 310

Different bidimensional scans were performed by varying 311 the sensor bias voltage to measure the uniformity in the charge 312

Schematic of the PM bias and amplification circuits used at the Fig. 9. proton microbeam.

collection efficiency (CCE) and characterize the transition at 313 the boundary between the pixels and the guard ring. 314

The gain of the full readout chain was optimized to maxi-315 mize the SNR of the output signal. The overall gain, depending 316 on the gain of the different amplification stages, was tuned as 317 follows: 318

$$G = G_1 \times G_2 = 20 \frac{\text{mV}}{\text{MeV}} \times 1.5 \times 100 \frac{\text{mV}}{\text{mV}} = 3 \frac{\text{V}}{\text{MeV}}$$

(1) 319

where  $G_1$  and  $G_2$  are, respectively, the gain of the preamplifier 320 and the voltage amplifier. 32.

Considering the beam energy, E = 2 MeV, which is fully absorbed within 60  $\mu$ m, the following theoretical output voltage is expected:

$$V_{\rm th} = G \times E \approx 6 \text{ V}. \tag{2}$$

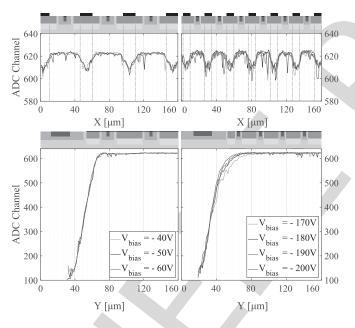

In the measurements, the signal output was acquired as 326 a function of the microbeam position. Maps with 128 Х 327 128 points were acquired in different areas of the sensor, both 328 in the center of the pixel array and near the boundary between 329 the pixels and the guard ring. In the former case, the map can 330 be used to calculate uniformity of the CCE along the array, 331 whereas in the latter case, some information on the spatial 332 resolution of the sensor can be inferred. 333

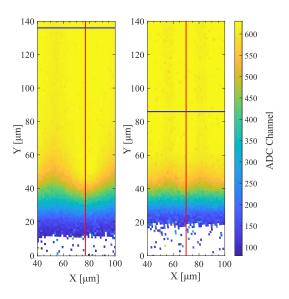

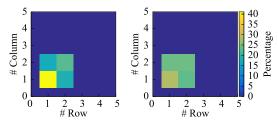

The sensor output signal, expressed in ADC counts, 334 is shown in Fig. 10 for two PM structures. To better appreciate 335 the variation of the signal with beam position, the maps have 336 been sliced along and across the sensing electrodes. The results 337 are shown in Fig. 11. 338

The top plots show the CCE variation between the sensor 339 electrodes and the metal lines. In the uniform regions between two metal lines, the mean value was 6.10 V, in good agreement 341 with the expected one.

In the regions under the metal lines, having a width 343 of 15 and 8  $\mu$ m for the PMs with 50- and 25- $\mu$ m pitch, 344 respectively, and a thickness of 2.32  $\mu$ m, a 2% reduction in the 345 collected charge can be estimated, while simulations predict a 346 reduction of 3.5%. This slight discrepancy is due to the limited 347 width of the metal lines, which does not allow observing a 348 region with uniform response due to the finite spot size. 349

The bottom plots in Fig. 11, showing the signal along the 350 vertical slices, offer information on charge sharing between 351 the pixels and the guard ring. In the 100- $\mu$ m sensor, the signal 352 rises from 10% to 90% in 22  $\mu$ m independently of the reverse 353 bias. In the 300- $\mu$ m sensor, on the other hand, the width of the 354

322

323

324

340

Fig. 10. Microbeam scan of 100  $\mu$ m sensor with 50- $\mu$ m pixel pitch (left) and 300- $\mu$ m sensor with a 25- $\mu$ m pixel pitch (right). The microbeam scan step is equal to  $\Delta X \approx 1.35 \ \mu$ m. The horizontal cut (blue line) is done across the second electrode from the matrix edge, whereas the vertical cut (red line) is performed halfway between the metal lines, i.e., along the collecting electrodes.

Fig. 11. Signal amplitude profiles at different bias voltages on the 100- $\mu$ m (left) and 300- $\mu$ m (right) thick sensors. The profiles are shown along (top) and across (bottom) the sensing electrodes in the same location as in Fig. 10.

transition region decreases from 34 to 26  $\mu$ m as the reverse bias increases. These results are in good agreement with the simulations in Fig. 5.

## C. Active Pixel Sensor Characterization With <sup>55</sup>Fe Source

A test campaign on the active pixel array with a <sup>55</sup>Fe calibration source was carried out in order to characterize both the sensor and its front-end electronics.

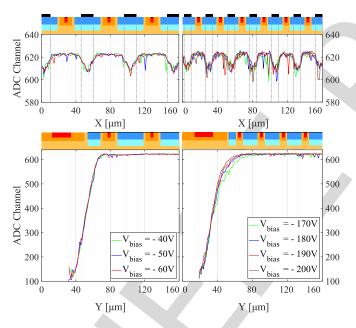

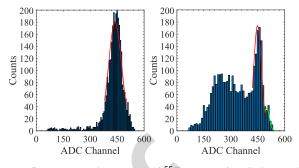

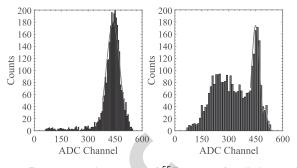

Fig. 12. Reconstructed spectrum of <sup>55</sup>Fe source for all clusters (left) and for seed signals (right) at  $V_{\text{bias}} = -200$  V. The fits are superimposed to the distributions.

The reconstructed spectrum of the absorbed photoelectrons 363 was first used to calibrate the pixel response sector by sector. 364 In the following discussion, all data refer to one of the 365 four sectors at  $V_{\text{bias}} = -200 \text{ V}$  and for an integration time 366 of 12.8  $\mu$ s. This value has been chosen to collect enough 367 statistics in a reasonable amount of time, without increas-368 ing the noise contribution, due to the leakage current, too 369 much. Cluster signals were reconstructed by applying a double 370 threshold method on a matrix of  $5 \times 5$  pixels selected around a 371 candidate cluster seed. Clusters were requested to have a seed 372 pixel with an SNR, S/N, of at least 6.0 and the neighboring 373 pixels an S/N in excess of 4.0. 374

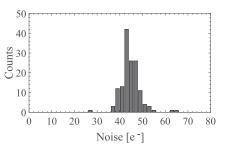

In Fig. 12, we show the spectrum of the cluster signals 375 (left) and the one of the seed pixels only (right). The energy 376 peak of the distribution, including all clusters (mean value 377  $\approx$  439 ADC), was used to calibrate the pixel response. 378 The analog gain of the full readout chain was found to 379 be  $\approx$  124 mV/fC, in good agreement with simulations 380 ( $\approx$  130 mV/fC). The energy resolution [full-width at half-381 maximum (FWHM)] depends on the cluster multiplicity; it is 382  $\approx$  1.1 keV when all clusters are included (regardless of their 383 size) and is reduced to  $\approx 0.7$  keV for single-pixel clusters. 384 On the seed value distribution, the peak corresponding to 385 the full charge collection of the 5.9-keV photoelectrons can 386 be recognized at  $\approx$  449 ADC. The charge deficit of  $\approx$  1% 387 with respect to the distribution, including all clusters, puts 388 a lower limit to the CCE of the detector. It is interesting 389 to note that also the peak of the 6.5-keV photons, centered 390 at  $\approx$  500 ADC, can be distinguished. We used the gain 39 information to evaluate the noise performance of the prototype 392 (sensor and electronics). For each pixel, its noise was measured 393 as the rms of the pedestal distribution in dark conditions. The 394 noise distribution for the full matrix is  $\approx 12$  ADC (two ADCs 395 coming from the readout chain: DAQ and readout boards) 396 which, expressed in electrons after the calibration, is shown 397 in Fig. 13. The mean noise value is found to be  $\approx 40 \text{ e}^-$  at 398 room temperature. 399

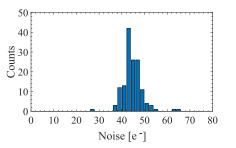

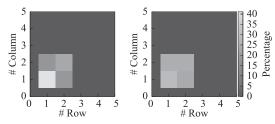

In order to study the charge sharing between the pixels in 400 the two configurations, the cluster size and shape were also 401 analyzed, applying both front- and back-side irradiation. The 402 results are shown in Fig. 14, on the left for front illumination 403 and on the right for back illumination. It can be observed, 404 in both cases, how the cluster size is limited to 4 pixels 405 since clusters with a multiplicity larger than 5 are only a 406 small fraction of the total (<1%). This proves how charge 407

Fig. 13. Noise distribution at room temperature with  $V_{\text{bias}} = -200 \text{ V}$  and an integration time of 12.8  $\mu$ s.

Fig. 14. Cluster size at  $V_{\text{bias}} = -200 \text{ V}$  in front illumination (left) and in back illumination (right).

sharing is small, and the cluster size is mainly affected by the

photon conversion position. In addition, the observation that

the cluster size in back illumination is comparable with the

one in front illumination confirms that, at the selected voltage,

the sensor is FD and charge collection is dominated by the drift

mechanism.

### V. CONCLUSION

414

428

In this article, we have demonstrated the feasibility of 415 FD-MAPS in a 110-nm CMOS process. The first experimental 416 results confirm the expected sensor characteristics for a pixel 417 thickness up to 300  $\mu$ m and a pixel pitch down to 25  $\mu$ m. 418 A large-area active pixel detector is currently under develop-419 ment and will be used to validate the technology in the context 420 of a charged-particle tracking experiment. The interest of the 421 developed process, however, is not limited to charged-particle 422 detection applications. The detection of photons with high 423 penetration depth, i.e., X-ray imaging as well as time-resolved 424 near-infrared imaging, are potentially interesting application 425 scenarios where the proposed technology can be competitive 426 with other state-of-the-art approaches. 427

### ACKNOWLEDGMENT

The research activity presented in this article has been carried out in the framework of the SEED and ARCADIA experiments. The authors acknowledge the support from our colleagues at RBI, Zagreb, Croatia, in operating the tandetron experimental setup. 431

#### REFERENCES

- M. Mager, "ALPIDE, the monolithic active pixel sensor for the ALICE ITS upgrade," *Nucl. Instrum. Methods Phys. Res. A, Accel., Spectrometers, Detectors Associated Equip.*, vol. 824, pp. 434–438, Jul. 2016, doi: 10.1016/j.nima.2015.09.057.

- [2] C. B. Winderer *et al.*, "The PERCIVAL soft X-ray imager," *J. Instrum.*, vol. 9, no. 3, 2014, Art. no. C03056, doi: 10.1088/1748-0221/9/03/ C03056.

- [3] I. Perić, "A novel monolithic pixelated particle detector implemented in high-voltage CMOS technology," *Nucl. Instrum. Methods Phys. Res. Sect. A, Accel., Spectrometers, Detectors Associated Equip.*, vol. 582, no. 3, pp. 876–885, Dec. 2007, doi: 10.1016/j.nima.2007.07.115.

- [4] T. Wang *et al.*, "Development of a depleted monolithic CMOS sensor in a 150 nm CMOS technology for the ATLAS inner tracker upgrade," *J. Instrum.*, vol. 12, no. 1, 2017, Art. no. C01039, doi: 10.1088/1748-0221/12/01/C01039.

- [5] H. Pernegger *et al.*, "First tests of a novel radiation hard CMOS sensor process for depleted monolithic active pixel sensors," *J. Instrum.*, vol. 12, no. 6, 2017, Art. no. P06008, doi: 10.1088/1748-0221/12/06/ P06008.

- [6] T. Hatsui *et al.*, "A direct-detection X-ray CMOS image sensor with 500  $\mu$ m thick high resistivity silicon," in *Proc. Int. Image Sensor Workshop*, Snowbird Resort, UT, USA, Jun. 2013, p. 4.

- [7] S. Mattiazzo *et al.*, "IMPACT: An innovative tracker and calorimeter for proton computed tomography," *IEEE Trans. Radiat. Plasma Med. Sci.*, vol. 2, no. 4, pp. 345–352, Jul. 2018, doi: 10.1109/TRPMS.2018. 2825499.

- [8] V. Scotti *et al.*, "The high energy particle detector onboard CSES-02 satellite," in *Proc. 36th Int. Cosmic Ray Conf. (ICRC)*, Madison, WI, USA, Jul./Aug. 2019.

- [9] W. Snoeys, J. D. Plummer, S. Parker, and C. Kenney, "PIN detector arrays and integrated readout circuitry on high-resistivity float-zone silicon," *IEEE Trans. Electron Devices*, vol. 41, no. 6, pp. 903–912, Jun. 1994, doi: 10.1109/16.293300.

- [10] S. Lauxtermann, J. Fisher, and M. McDougal, "A monolithic 640 × 512 CMOS imager with high-NIR sensitivity," *Proc. SPIE*, vol. 9070, Jun. 2014, Art. no. 907002, doi: 10.1117/12.2053449.

- [11] M. Asano *et al.*, "Characteristics of non-irradiated and irradiated double SOI integration type pixel sensor," *Nucl. Instrum. Methods Phys. Res. Sect. A, Accel., Spectrometers, Detectors Associated Equip.*, vol. 831, pp. 315–321, Sep. 2016, doi: 10.1016/j.nima.2016.03.095.

- [12] L. Pancheri *et al.*, "A 110 nm CMOS process for fully-depleted pixel sensors," *J. Instrum.*, vol. 14, no. 6, 2019, Art. no. C06016, doi: 10.1088/ 1748-0221/14/06/C06016.

- [13] E. J. Olave *et al.*, "MATISSE: A low power front-end electronics for MAPS characterization," in *Proc. Topical Workshop Electron. Part. Phys. PoS(TWEPP)*, Santa Cruz, CA, USA, Mar. 2018, pp. 11–14, doi: 10.22323/1.313.0016.

- [14] S. Panati *et al.*, "MATISSE: A versatile readout electronics for monolithic active pixel sensors characterization," in *Proc. IEEE Nucl. Sci. Symp. Med. Imag. Conf. (NSS/MIC)*, Atlanta, GA, USA, Oct. 2017, pp. 1–4, doi: 10.1109/NSSMIC.2017.8532806.

- [15] M. Jakšić et al., "New capabilities of the Zagreb ion microbeam system," Nucl. Instrum. Methods Phys. Res. Sect. B, Beam Interact. Mater. At., vol. 260, no. 1, pp. 114–118, Jul. 2007, doi: 10.1016/ j.nimb.2007.01.252.

434

435

436

437

438

439

440

441

442

443

444

445

446

447

448

449

450

451

452

453

454

455

456

457

458

459

460

461

462

464

465

466

467

468

469

470

471

472

473

474

475

476

477

478

479

480

481

482

483

484

485

486

487

488

489

463 AQ:5

### AUTHOR QUERIES

## AUTHOR PLEASE ANSWER ALL QUERIES

PLEASE NOTE: We cannot accept new source files as corrections for your article. If possible, please annotate the PDF proof we have sent you with your corrections and upload it via the Author Gateway. Alternatively, you may send us your corrections in list format. You may also upload revised graphics via the Author Gateway.

Carefully check the page proofs (and coordinate with all authors); additional changes or updates WILL NOT be accepted after the article is published online/print in its final form. Please check author names and affiliations, funding, as well as the overall article for any errors prior to sending in your author proof corrections.

- AQ:1 = Please confirm or add details for any funding or financial support for the research of this article.

- AQ:2 = Please confirm that all authors' affiliations are accurate as shown in the first footnote.

- AQ:3 = Please provide the location and postal code for Istituto Nazionale di Fisica Nucleare—Sezione Milano.

- AQ:4 = Please provide the expansion for DUT, DAQ, and RBI.

- AQ:5 = Please provide the page range for Ref. [8].

# Fully Depleted MAPS in 110-nm CMOS Process With 100–300-µm Active Substrate

Lucio Pancheri<sup>®</sup>, *Member, IEEE*, Raffaele A. Giampaolo, Andrea Di Salvo, Serena Mattiazzo<sup>®</sup>, Thomas Corradino, Piero Giubilato, Romualdo Santoro<sup>®</sup>, Massimo Caccia<sup>®</sup>, Giovanni Margutti, Jonhatan E. Olave, Manuel Rolo, and Angelo Rivetti

Abstract—This article presents a fully depleted monolithic active pixel sensor technology compatible with 2 a standard deep submicrometer 110-nm CMOS process. 3 Passive test pixels structures, produced in various flavors, have proved the feasibility of 100- and 300- $\mu$ m-thick 5 active substrates. Active pixel sensors with monolithically 6 integrated analog and digital electronics, consisting of a 24  $\times$  24 array of pixels with 50- $\mu$ m pitch, have been shown to be fully functional when operating in the full depletion mode. 9 Characterization results obtained with a proton microbeam 10 and a <sup>55</sup>Fe radiation source are presented and discussed. 11

Index Terms—CMOS, monolithic active pixel sensor

(MAPS), radiation detector, silicon.

### I. INTRODUCTION

<sup>15</sup> MONOLITHIC active pixel sensors (MAPSs) are emerging as a viable alternative to hybrid pixels in charged<sup>17</sup> particles' detection and high-energy photons imaging, showing

<sup>18</sup> advantages in both performance and overall costs per unit

<sup>19</sup> area [1]–[3].

The reconstruction with the highest precision of the perigee parameters of charged-particle trajectories in a dense

Manuscript received February 7, 2020; revised March 30, 2020; accepted March 30, 2020. This work was supported in part by the Istituto Nazionale di Fisica Nucleare (INFN), CSN5, and in part by the H2020 Project AIDA-2020 under Grant 654168. The review of this article was arranged by Editor J. Huang. (*Corresponding author: Lucio Pancheri.*)

Lucio Pancheri and Thomas Corradino are with the Dipartimento di Ingegneria Industriale, TIFPA Istituto Nazionale di Fisica Nucleare (INFN), Università di Trento, 38123 Trento, Italy (e-mail: lucio.pancheri@unitn.it).

Raffaele A. Giampaolo and Andrea Di Salvo are with the Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Turin, Italy, and also with the Istituto Nazionale di Fisica Nucleare (INFN)— Torino, 10125 Turin, Italy (e-mail: raffaeleaaron.giampaolo@to.infn.it; andrea\_disalvo@polito.it).

Serena Mattiazzo and Piero Giubilato are with the Dipartimento di Fisica e Astronomia, Istituto Nazionale di Fisica Nucleare— Sezione di Padova, Università di Padova, 35131 Padua, Italy (e-mail: serena.mattiazzo@unipd.it; piero.giubilato@unipd.it).

Romualdo Santoro and Massimo Caccia are with the Dipartimento di Scienze ed Alta Tecnologia, Università dell'Insubria, 22100 Varese, Italy, and also with the Istituto Nazionale di Fisica Nucleare—Sezione Milano.

Giovanni Margutti is with LFoundry S.r.I., 67051 Avezzano, Italy. Jonhatan E. Olave, Manuel Rolo, and Angelo Rivetti are with the Istituto Nazionale di Fisica Nucleare—Torino, 10125 Turin, Italy.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2020.2985639

environment calls for pixel pitches of tens of micrometers, low material budget, a high signal-over-noise ratio, and limited diffusion of the charge carriers originated by the impinging particle. These specifications can be obtained with a monolithic design implemented on a fully depleted (FD) high-resistivity substrate. As a consequence, FD-MAPSs are raising a significant interest in the high-energy physics community [4], [5].

FD-MAPSs have also been proposed for X-ray imaging [6], where an active substrate of 300–500  $\mu$ m would enable an efficient detection of photon energies up to 15 keV. Other applications, such as medical particle tomography and tracking in space experiments, would benefit from the low material budget, fine pixel pitch, and low power consumption offered by MAPS sensors [7], [8].

As a general trend in the development of pixel sensors, the complexity of on-chip digital functions is increasing, making it easier to integrate and deploy a complete sensor system. Moreover, event-driven readout schemes are frequently adopted to reduce power consumption and, in turn, relax the requirements of the cooling systems, impacting on the overall system material budget. To these purposes, very scaled process nodes should be used to reduce the area and to increase the speed of on-chip digital electronics.

The latest FD-MAPS design efforts in the high-energy physics community are adopting 180- and 150-nm process nodes. Most of the developments, in this respect, have been devoted to the implementation of devices with a depletion region ranging from a few tens of micrometer and hundreds of micrometer [4], [5]. In [4], large depletion regions are obtained by including the electronics inside a deep n-well that is used as a collection node for the electrons generated by the incident charged particles. This approach has demonstrated an excellent radiation hardness and a fast charge collection, but the sensor capacitance is relatively large, and a nonnegligible part of the pixel area cannot be used to accommodate the readout circuits. Scaling to very small pixels is thus very challenging while using such topology.

An alternative approach, arising from an evolution of the pixels designed for the ALICE detector [1], uses small sensing nodes while implanting a low-doped n-type region below the electronics [5]. In this way, most of the generated charges can be collected by drift, while the area and the capacitance of the sensors are maintained small, granting scalability toward

AQ:1

AQ:2

14

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

<sup>0018-9383 © 2020</sup> IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

small pixel sizes. This approach, although excellent for particle 65 tracking, cannot be easily extended to an active thickness in 66 excess of 100  $\mu$ m since the space-charge region extends from 67 the top surface of the sensor, thus limiting the applicable voltage at the sensor top side. 69

The possibility of FD thick substrates in CMOS-integrated 70 sensors has been first explored in [9], demonstrating an FD 71 sensor with p-type substrate and a n-type backside implanta-72 tion. In the first prototype, the electronics were made entirely 73 of p-type transistors. A similar approach was adopted in [10], 74 using a CMOS process with n-type substrates and implanting 75 a p+ region on the back. 76

Full depletion can also be obtained using a silicon-on-77 insulator process. Although the radiation damage of the insu-78 lator oxide poses several challenges related to parameter drift 79 in the transistor characteristics, the latest advancements have 80 greatly improved the radiation hardness of the process, and 81 sensors with depletion regions up to 500  $\mu$ m thick have been 82 demonstrated [11]. 83

In this article, we present a technology platform for the 84 implementation of FD MAPS based on a modified 110-nm 85 CMOS process. The process node was chosen to enable the 86 in-pixel implementation of complex digital functions while 87 keeping low prototyping and production costs. Backside 88 processing was used to create a junction on the bottom 89 surface that is biased to deplete the whole sensor substrate. 90

This article is structured as follows. Section II discusses 91 the simulated characteristics with reference to geometry and 92 process parameters. In Section III, the design of pixel test 93 structures and a small array of active pixels with integrated 94 electronics are presented. Section IV presents the results of 95 the characterization of the arrays compared with the expec-96 tations according to the simulation. The perspectives for this 97 technology are highlighted in Section V. 98

### **II. SENSOR CONCEPT**

The process was developed starting from a 110-nm indus-100 trial CMOS with 1.2-V transistors and six metal layers. A few 101 add-ons were necessary to allow for full substrate depletion 102 with electron collection at the sensing electrodes. A concept 103 cross section of the pixel array is shown in Fig. 1 [12]. 104

The standard p-type substrate was replaced with an n-type 105 floating zone material. Wafer thinning and backside lithog-106 raphy were necessary to introduce a junction at the bottom 107 surface, used to bias the substrate to full depletion while 108 maintaining a low voltage at the front side. A shallow boron-109 doped region was implanted on the rear side of the wafer, and 110 the dopants were activated by laser annealing. Since, at large 111 wafer thicknesses, the voltage needed for sensor full depletion 112 exceeds 150 V, a termination structure composed of multiple 113 guard rings was introduced. 114

A deep p-well scheme was used to prevent the n-wells 115 hosting p-MOSFETs from collecting the charge generated 116 by radiation in the substrate. Care had to be taken to limit 117 the punchthrough current between the back-side junction and 118 the deep p-well at sensor full depletion. A good control of 119 punchthrough could be obtained either by increasing the bias 120

Fig. 1. FD pixel sensor cross section.

Simulated 2-D potential profile and electric-field lines at full Fig. 2. depletion. The simulation domain includes part of the guard rings and 2 pixels with 25- $\mu$ m pitch. Only the sensor surface region is shown.

voltage at the pixel sensor nodes or by increasing the n-dopant 121 concentration below the p-wells. Since the sensors had to be 122 directly coupled to the low-voltage electronics, the second 123 solution was adopted, by adding an n-doped epitaxial layer, 124 having a resistivity lower than the substrate, to the process 125 flow. 126

TCAD simulations were used to tune the process parame-127 ters. The simulated potential profile at full depletion for a domain, including 2 pixels and part of the surface guard ring, 129 is shown in Fig. 2. Electric-field lines are orthogonal to the 130 sensor surface up to the bottom of the deep p-wells, and then, 131 they deviate horizontally toward the collection electrodes.

128

132

The full depletion and punchthrough voltages were simu-133 lated on this domain by introducing a small unbalance (10 mV) 134 between pixel and guard ring bias voltages. The current 135 flowing at the sensing electrodes and at the backside as a 136 function of applied backside bias is shown in Fig. 3. At low 137 reverse voltage, the substrate is not FD, and resistive paths 138 exist between the pixels and the guard ring, leading to a macro-139 scopic current. As the bias voltage is increased, a sharp current 140 drop is observed, indicating the onset of full depletion. The 141 depletion voltage is reduced by increasing the voltage applied 142 at the front side to the sensor nodes. If the backside voltage 143 is further increased, a punchthrough current starts flowing and 144

Fig. 3. Simulated sensor and backside current as a function of backside voltage for two values of sensor thickness [100  $\mu$ m, (left) and 300  $\mu$ m (right)]. Pixel pitch is 25  $\mu$ m.

Fig. 4. Simulated transient current signal with an incident MIP for two different values of sensor thickness [100  $\mu$ m (left) and 300  $\mu$ m (right)] and pixel pitch [25  $\mu$ m (top) and 50  $\mu$ m (bottom)].

eventually reaches very large values. The voltage difference 145 between breakdown and punchthrough voltages depends on the 146 sensor bias. At a sensor voltage between 0.6 and 1 V that can 147 be applied if the sensor is directly coupled to the electronic 148 readout channels, the difference between full depletion and 149 punchthrough is a fraction of 10%-20% of the applied bias 150 voltage. This value is large enough to reliably accommodate 151 the operation of a pixel array, considered possible doping 152 gradients and nonuniformities between the pixels. 153

Charge collection dynamics upon the incidence of a min-154 imum ionizing particle (MIP) were also simulated. The 155 MIP was modeled as a continuous charge density of 156 80 e-h pairs/ $\mu$ m, orthogonal to the sensor surface and extend-157 ing throughout the sensor thickness. With reference to the sim-158 ulation domain shown in Fig. 2, several positions of incidence 159 were considered for the MIP. The current signal generated at 160 the sensor is shown in Fig. 4 for two different MIP incidence 161 positions, two values of pixel pitch (25 and 50  $\mu$ m), and two 162 values of sensor thickness (100 and 300  $\mu$ m). As expected, 163 complete charge collection is observed in less than 5 and 10 ns. 164

Fig. 5. Simulated collected charge at the sensor periphery as a function of the position of the incident particle for two different values of sensor thickness [100  $\mu$ m (top) and 300  $\mu$ m (bottom)] and pixel pitch [25  $\mu$ m (left) and 50  $\mu$ m (right)].

respectively, for 100 and 300  $\mu$ m thickness when the MIP is 165 incident in the center of the pixel. If the MIP is incident at 166 the pixel periphery, the collection speed depends on the pixel 167 pitch; at 50- $\mu$ m pitch, the collection time approximately dou-168 bles since the charge generated in the substrate first reaches the 169 bottom of the deep p-well and then drifts horizontally toward 170 the collection node. Even considering this worst case situation, 171 however, the charge is completely collected within 20 ns. 172 In 25- $\mu$ m pixels, on the contrary, the collection time is only 173 slightly degraded, as a result of the smaller horizontal distance 174 traveled by electrons generated at the pixel periphery. 175

The integrated charge as a function of the MIP incidence position is shown in Fig. 5. Charge sharing between the pixels for two values of thickness and pixel pitch can be observed. As expected, sharing slightly increases by increasing the pixel pitch and sensor thickness, but, in all the cases considered here, the effect is confined to the nearest neighboring pixels.

### III. ACTIVE PIXEL ARRAY AND TEST STRUCTURES

A 576-active pixel array was designed as a test bench to val-183 idate the performance of the proposed technology [13], [14]. 184 The pixels are organized in four sectors, each one consisting 185 of 6 columns of 24 pixels. An end-of-column (EoC) block 186 manages the column logic, handling pixel configuration and 187 controlling data transmission. In this way, each sector works in 188 parallel with the others. To read out the data for a single sector, 189 two clocks are used. The first controls the shift register in the 190 EoC to select the column, whereas the second one is dedicated 191 to the row shift register. In a typical case, they, respectively, 192 work at 5 and 0.2 MHz. Thus, the whole array can be read in 193 less than 30  $\mu$ s using a 5-MHz clock. 194

A single 50- $\mu$ m pitch pixel hosts both the electrode and the in-pixel electronics. The sensing electrode, together with a surrounding area clear from electronic circuits, occupies a region of 20  $\mu$ m × 20  $\mu$ m, and it is centered in the pixel area. The remaining area is partitioned between the analog front end and the digital logic. 200

Fig. 6. Pixel readout block scheme.

The readout chain is shown in Fig. 6. The radiation-201 generated current signal is amplified by a charge-sensitive 202 amplifier (CSA) circuit. A sample and hold circuitry, designed 203 to perform correlated double sampling (CDS) operation, 204 follows the CSA. Metal-insulator-metal (MIM) capacitors 205 are used to store the signal at this stage. Two analog buffers are 206 included to transmit the analog output signal along the column. 207 The charge-integrating amplifier, designed to maximize the 208 signal-to-noise ratio (SNR), is based on a telescopic cascode 209 architecture with a feedback capacitor  $C_f$  and a minimum-210 size pMOS reset switch.  $C_f$  has been chosen equal to 5.8 fF, 211 giving a postlayout simulation gain of 130 mV/fC. The output 212 dynamic range of the amplifier is defined by considering the 213 expected signal for an MIP in a  $300-\mu$ m-thick detector. Thus, 214 for 3.8 fC (corresponding to 80 e-h pairs/  $\mu$ m in 300  $\mu$ m 215 thickness), the output voltage signal matches the linear output 216 range of the amplifier, which is around 500 mV. This gain also 217 ensures a good SNR for MIPs in substrates with a thickness 218 as low as 50  $\mu$ m. 219

The pixel unit is also equipped with a digital logic to 220 manage data readout and to define the pixel functions. A 3-bit 221 in-pixel register allows to switch OFF defective pixels, enable 222 the injection of a test pulse for the electrical characterization 223 of the readout electronics, and enable the buffer amplifier for 224 data transmission. To study digital noise coupling between 225 the analog and digital sections of the design, each pixel 226 accommodates a digital buffer made by 18 elements, each with 227 a bandwidth of 5 GHz, designed to inject digital noise. 228

Fig. 7 shows a micrograph of the active pixel array, with a group of 4 pixels in the magnified area. At the center of the pixels, an area free from metal is present to allow the illumination from the top. This feature was included to carry out studies with laser sources.

The pixels were designed for a power consumption around  $6 \mu$ W. Providing a power supply of 1.2 V, the power consumption of the pixel array in the static and dynamic conditions is, respectively, 3.84 and 6.4 mW, without considering the contribution of digital and EoC logic.

Small pixel arrays, formed by pixels free from electronic readout circuits, were designed to allow additional flexibility in the experimental evaluation of sensor and process characteristics [12]. In these arrays, these are termed pseudomatrices (PMs) since all the sensing electrodes in the pixels are connected to the same pad, and pixels with both 50- and  $25-\mu$ m pitch were included.

Fig. 7. Micrograph of active pixel array. Inset: close-up of 4 pixels.

TABLE I PRODUCED SENSOR SAMPLES

| Sensor type         | Thickness [µm] | Pixel Pitch $[\mu m^2]$      |

|---------------------|----------------|------------------------------|

| Full Sensor         | 300            | $50 \times 50$               |

| PM                  | 100            | $25 \times 25, 50 \times 50$ |

| PM                  | 300            | $25 \times 25, 50 \times 50$ |

| PM Pixel pitch [µm] | Pseudo-pixels  | Metal width [µm]             |

| $25 \times 25$      | $16 \times 18$ | 8                            |

| $50 \times 50$      | $8 \times 9$   | 15                           |

Two fabrication runs, including both pixel arrays and PM test structures, were produced on high-resistivity wafers  $(\rho > 2 \text{ k}\Omega \cdot \text{cm})$  that were thinned to 300 and 100  $\mu$ m prior to backside processing. A summary of the devices presented in this article is shown in Table I, highlighting their main geometrical characteristics. 251

#### IV. EXPERIMENTAL RESULTS

An extensive experimental test campaign has been carried out on both the test structures and the active pixel arrays in order to assess their functionality. This section summarizes the most meaningful results, discussed with reference to the simulated characteristics presented in Section II.

### A. Electrical Characterization

Static electrical characterizations have been performed at 259 room temperature on PM structures in order to evaluate 260 full depletion and punchthrough voltages for different pixel 261 sizes, thicknesses, and bias conditions. Current–voltage (I-V)262 curves have been measured using a four-channel semicon-263 ductor parameter analyzer. In the measurements, the same 264 conditions used for the simulations described in Section II 265 have been applied; the p-wells were biased at 0 V, the sensing 266 nodes and the guard ring were biased between 0 and 1 V, and 267 a negative bias sweep was applied to the backside contact. The 268 measured sensor and backside currents are shown in Fig. 8 as 269 a function of the backside bias voltage for PMs with  $25-\mu m$ 270 pitch. While the sensor current is plotted for three different 271 values of sensor voltage, only one curve is shown for the 272 backside current since no dependence on sensor voltage was 273 observed. 274

7

252

Fig. 8. Measured I-V curves for 100  $\mu$ m (left) and 300  $\mu$ m (right) thick PM sensors. Pixel pitch is 25  $\mu$ m.

When compared with the simulated curves in Fig. 3, 275 an excellent agreement was found in both the full depletion 276 and the punchthrough voltage for both the device thicknesses 277 and sensor bias voltages. The simulated and measured currents 278 differ by several orders of magnitude due to the different 279 sizes of the simulation domain (single pixel, 25  $\mu$ m  $\times$  1  $\mu$ m 280 in 2-D simulations) and PM sensors (400  $\mu$ m × 450  $\mu$ m total 281 active area). In the 300- $\mu$ m-thick sensors, the measured dark 282 current is more than one order of magnitude smaller than in 283  $100-\mu$ m-thick sensors. Further investigations are going on to 284 understand the origin of this difference, probably due to the 285 different processing conditions. The I-V curves measured on 286 pixels with 50- $\mu$ m pitch are very similar to the ones shown 287 in Fig. 8. 288

#### B. Microbeam Sensor Characterization 289

The PMs have been tested at the RBI microbeam facility 290 in Zagreb, Croatia [15]. The microbeam has been generated 291 using a 1-MV Tandetron accelerator capable of delivering 292 protons in the 0.5-2.0-MeV range; 2-MeV proton beams with 293  $\sigma_{\rm spot} \approx 2 \ \mu {\rm m}$  have been focused onto PM structures with 294 different pixel sizes and thickness (see Table I). Protons of 295 296 this energy have been simulated to have a Bragg peak located at a depth  $\lambda \approx 47 \ \mu m$  in silicon. As a result, the number of 297 collected carriers and, in turn, the output signal is expected to 298 be independent of the sensor thickness. The proton flux was 299 adjusted to provide a maximum hit rate of 2 kHz. 300

AO:4

The DUTs have been wire bonded to a specifically designed 301 PCB equipped with p-i-n connectors to bias the collection 302 electrodes, guard rings, and p-wells. The bias voltages were 303 supplied by a HAMEG HMP2030 power supply, while the 304 high-voltage power supply was an NHQ 202M. As shown 305 in Fig. 9, an ORTEC 142-A bias-T preamplifier with a 306 20-mV/MeV gain has been connected between the pixel 307 array and the biasing module. An ORTEC 570 voltage 308 amplifier was connected between the preamplifier and a 309 CANBERRA 8075 12-bit 10-V ADC. 310

Different bidimensional scans were performed by varying 311 the sensor bias voltage to measure the uniformity in the charge 312

Fig. 9. Schematic of the PM bias and amplification circuits used at the proton microbeam.

collection efficiency (CCE) and characterize the transition at 313 the boundary between the pixels and the guard ring. 314

The gain of the full readout chain was optimized to maxi-315 mize the SNR of the output signal. The overall gain, depending 316 on the gain of the different amplification stages, was tuned as 317 follows: 318

$$G = G_1 \times G_2 = 20 \frac{\text{mV}}{\text{MeV}} \times 1.5 \times 100 \frac{\text{mV}}{\text{mV}} = 3 \frac{\text{V}}{\text{MeV}}$$

(1) 319

where  $G_1$  and  $G_2$  are, respectively, the gain of the preamplifier 320 and the voltage amplifier. 32.

Considering the beam energy, E = 2 MeV, which is fully absorbed within 60  $\mu$ m, the following theoretical output voltage is expected:

$$V_{\rm th} = G \times E \approx 6 \,\,\mathrm{V}.\tag{2}$$

In the measurements, the signal output was acquired as 326 a function of the microbeam position. Maps with 128  $\times$ 327 128 points were acquired in different areas of the sensor, both 328 in the center of the pixel array and near the boundary between 329 the pixels and the guard ring. In the former case, the map can 330 be used to calculate uniformity of the CCE along the array, 331 whereas in the latter case, some information on the spatial 332 resolution of the sensor can be inferred. 333

The sensor output signal, expressed in ADC counts, 334 is shown in Fig. 10 for two PM structures. To better appreciate 335 the variation of the signal with beam position, the maps have 336 been sliced along and across the sensing electrodes. The results 337 are shown in Fig. 11.

The top plots show the CCE variation between the sensor 339 electrodes and the metal lines. In the uniform regions between two metal lines, the mean value was 6.10 V, in good agreement 341 with the expected one.

In the regions under the metal lines, having a width 343 of 15 and 8  $\mu$ m for the PMs with 50- and 25- $\mu$ m pitch, 344 respectively, and a thickness of 2.32  $\mu$ m, a 2% reduction in the 345 collected charge can be estimated, while simulations predict a 346 reduction of 3.5%. This slight discrepancy is due to the limited 347 width of the metal lines, which does not allow observing a 348 region with uniform response due to the finite spot size. 349

The bottom plots in Fig. 11, showing the signal along the 350 vertical slices, offer information on charge sharing between 351 the pixels and the guard ring. In the 100- $\mu$ m sensor, the signal 352 rises from 10% to 90% in 22  $\mu$ m independently of the reverse 353 bias. In the 300- $\mu$ m sensor, on the other hand, the width of the 354

322

323

324

338

340

Fig. 10. Microbeam scan of 100  $\mu$ m sensor with 50- $\mu$ m pixel pitch (left) and 300- $\mu$ m sensor with a 25- $\mu$ m pixel pitch (right). The microbeam scan step is equal to  $\Delta X \approx 1.35 \ \mu$ m. The horizontal cut (blue line) is done across the second electrode from the matrix edge, whereas the vertical cut (red line ) is performed halfway between the metal lines, i.e., along the collecting electrodes.

Fig. 11. Signal amplitude profiles at different bias voltages on the 100- $\mu$ m (left) and 300- $\mu$ m (right) thick sensors. The profiles are shown along (top) and across (bottom) the sensing electrodes in the same location as in Fig. 10.

transition region decreases from 34 to 26  $\mu$ m as the reverse bias increases. These results are in good agreement with the simulations in Fig. 5.

## C. Active Pixel Sensor Characterization With <sup>55</sup>Fe Source

A test campaign on the active pixel array with a <sup>55</sup>Fe calibration source was carried out in order to characterize both the sensor and its front-end electronics.

Fig. 12. Reconstructed spectrum of <sup>55</sup>Fe source for all clusters (left) and for seed signals (right) at  $V_{\text{bias}} = -200$  V. The fits are superimposed to the distributions.

The reconstructed spectrum of the absorbed photoelectrons 363 was first used to calibrate the pixel response sector by sector. 364 In the following discussion, all data refer to one of the 365 four sectors at  $V_{\text{bias}} = -200 \text{ V}$  and for an integration time 366 of 12.8  $\mu$ s. This value has been chosen to collect enough 367 statistics in a reasonable amount of time, without increas-368 ing the noise contribution, due to the leakage current, too 369 much. Cluster signals were reconstructed by applying a double 370 threshold method on a matrix of  $5 \times 5$  pixels selected around a 371 candidate cluster seed. Clusters were requested to have a seed 372 pixel with an SNR, S/N, of at least 6.0 and the neighboring 373 pixels an S/N in excess of 4.0. 374

In Fig. 12, we show the spectrum of the cluster signals 375 (left) and the one of the seed pixels only (right). The energy 376 peak of the distribution, including all clusters (mean value 377  $\approx$  439 ADC), was used to calibrate the pixel response. 378 The analog gain of the full readout chain was found to 379 be  $\approx$  124 mV/fC, in good agreement with simulations 380 ( $\approx$  130 mV/fC). The energy resolution [full-width at half-381 maximum (FWHM)] depends on the cluster multiplicity; it is 382  $\approx$  1.1 keV when all clusters are included (regardless of their 383 size) and is reduced to  $\approx 0.7$  keV for single-pixel clusters. 384 On the seed value distribution, the peak corresponding to 385 the full charge collection of the 5.9-keV photoelectrons can 386 be recognized at  $\approx$  449 ADC. The charge deficit of  $\approx$  1% 387 with respect to the distribution, including all clusters, puts 388 a lower limit to the CCE of the detector. It is interesting 389 to note that also the peak of the 6.5-keV photons, centered 390 at  $\approx$  500 ADC, can be distinguished. We used the gain 39 information to evaluate the noise performance of the prototype 392 (sensor and electronics). For each pixel, its noise was measured 393 as the rms of the pedestal distribution in dark conditions. The 394 noise distribution for the full matrix is  $\approx 12$  ADC (two ADCs 395 coming from the readout chain: DAQ and readout boards) 396 which, expressed in electrons after the calibration, is shown 397 in Fig. 13. The mean noise value is found to be  $\approx 40 \text{ e}^-$  at 398 room temperature. 399

In order to study the charge sharing between the pixels in 400 the two configurations, the cluster size and shape were also 401 analyzed, applying both front- and back-side irradiation. The 402 results are shown in Fig. 14, on the left for front illumination 403 and on the right for back illumination. It can be observed, 404 in both cases, how the cluster size is limited to 4 pixels 405 since clusters with a multiplicity larger than 5 are only a 406 small fraction of the total (<1%). This proves how charge 407

Fig. 13. Noise distribution at room temperature with  $V_{\text{bias}} = -200 \text{ V}$  and an integration time of 12.8  $\mu$ s.

Fig. 14. Cluster size at  $V_{\text{bias}} = -200 \text{ V}$  in front illumination (left) and in back illumination (right).

sharing is small, and the cluster size is mainly affected by the

photon conversion position. In addition, the observation that

the cluster size in back illumination is comparable with the

one in front illumination confirms that, at the selected voltage,

the sensor is FD and charge collection is dominated by the drift

mechanism.

### V. CONCLUSION

414

428

In this article, we have demonstrated the feasibility of 415 FD-MAPS in a 110-nm CMOS process. The first experimental 416 results confirm the expected sensor characteristics for a pixel 417 thickness up to 300  $\mu$ m and a pixel pitch down to 25  $\mu$ m. 418 A large-area active pixel detector is currently under develop-419 ment and will be used to validate the technology in the context 420 of a charged-particle tracking experiment. The interest of the 421 developed process, however, is not limited to charged-particle 422 detection applications. The detection of photons with high 423 penetration depth, i.e., X-ray imaging as well as time-resolved 424 near-infrared imaging, are potentially interesting application 425 scenarios where the proposed technology can be competitive 426 with other state-of-the-art approaches. 427

### ACKNOWLEDGMENT

The research activity presented in this article has been carried out in the framework of the SEED and ARCADIA experiments. The authors acknowledge the support from our colleagues at RBI, Zagreb, Croatia, in operating the tandetron experimental setup. 431

#### REFERENCES

- M. Mager, "ALPIDE, the monolithic active pixel sensor for the ALICE ITS upgrade," *Nucl. Instrum. Methods Phys. Res. A, Accel., Spectrometers, Detectors Associated Equip.*, vol. 824, pp. 434–438, Jul. 2016, doi: 10.1016/j.nima.2015.09.057.

- [2] C. B. Winderer *et al.*, "The PERCIVAL soft X-ray imager," *J. Instrum.*, vol. 9, no. 3, 2014, Art. no. C03056, doi: 10.1088/1748-0221/9/03/ C03056.

- [3] I. Perić, "A novel monolithic pixelated particle detector implemented in high-voltage CMOS technology," *Nucl. Instrum. Methods Phys. Res. Sect. A, Accel., Spectrometers, Detectors Associated Equip.*, vol. 582, no. 3, pp. 876–885, Dec. 2007, doi: 10.1016/j.nima.2007.07.115.

- [4] T. Wang *et al.*, "Development of a depleted monolithic CMOS sensor in a 150 nm CMOS technology for the ATLAS inner tracker upgrade," *J. Instrum.*, vol. 12, no. 1, 2017, Art. no. C01039, doi: 10.1088/1748-0221/12/01/C01039.

- [5] H. Pernegger *et al.*, "First tests of a novel radiation hard CMOS sensor process for depleted monolithic active pixel sensors," *J. Instrum.*, vol. 12, no. 6, 2017, Art. no. P06008, doi: 10.1088/1748-0221/12/06/ P06008.

- [6] T. Hatsui *et al.*, "A direct-detection X-ray CMOS image sensor with 500  $\mu$ m thick high resistivity silicon," in *Proc. Int. Image Sensor Workshop*, Snowbird Resort, UT, USA, Jun. 2013, p. 4.

- [7] S. Mattiazzo *et al.*, "IMPACT: An innovative tracker and calorimeter for proton computed tomography," *IEEE Trans. Radiat. Plasma Med. Sci.*, vol. 2, no. 4, pp. 345–352, Jul. 2018, doi: 10.1109/TRPMS.2018. 2825499.

- [8] V. Scotti *et al.*, "The high energy particle detector onboard CSES-02 satellite," in *Proc. 36th Int. Cosmic Ray Conf. (ICRC)*, Madison, WI, USA, Jul./Aug. 2019.

- [9] W. Snoeys, J. D. Plummer, S. Parker, and C. Kenney, "PIN detector arrays and integrated readout circuitry on high-resistivity float-zone silicon," *IEEE Trans. Electron Devices*, vol. 41, no. 6, pp. 903–912, Jun. 1994, doi: 10.1109/16.293300.

- [10] S. Lauxtermann, J. Fisher, and M. McDougal, "A monolithic 640 × 512 CMOS imager with high-NIR sensitivity," *Proc. SPIE*, vol. 9070, Jun. 2014, Art. no. 907002, doi: 10.1117/12.2053449.

- [11] M. Asano *et al.*, "Characteristics of non-irradiated and irradiated double SOI integration type pixel sensor," *Nucl. Instrum. Methods Phys. Res. Sect. A, Accel., Spectrometers, Detectors Associated Equip.*, vol. 831, pp. 315–321, Sep. 2016, doi: 10.1016/j.nima.2016.03.095.

- [12] L. Pancheri *et al.*, "A 110 nm CMOS process for fully-depleted pixel sensors," *J. Instrum.*, vol. 14, no. 6, 2019, Art. no. C06016, doi: 10.1088/ 1748-0221/14/06/C06016.

- [13] E. J. Olave *et al.*, "MATISSE: A low power front-end electronics for MAPS characterization," in *Proc. Topical Workshop Electron. Part. Phys. PoS(TWEPP)*, Santa Cruz, CA, USA, Mar. 2018, pp. 11–14, doi: 10.22323/1.313.0016.

- [14] S. Panati *et al.*, "MATISSE: A versatile readout electronics for monolithic active pixel sensors characterization," in *Proc. IEEE Nucl. Sci. Symp. Med. Imag. Conf. (NSS/MIC)*, Atlanta, GA, USA, Oct. 2017, pp. 1–4, doi: 10.1109/NSSMIC.2017.8532806.

- [15] M. Jakšić et al., "New capabilities of the Zagreb ion microbeam system," Nucl. Instrum. Methods Phys. Res. Sect. B, Beam Interact. Mater. At., vol. 260, no. 1, pp. 114–118, Jul. 2007, doi: 10.1016/ j.nimb.2007.01.252.

7

434

435

436

437

438

439

440

441

442

443

444

445

446

447

448

449

450

451

452

453

454

455

456

457

458

459

460

461

462

465

466

467

468

469

470

471

472

473

474

475

476

477

478

479

480

481

482

483

484

485

486

487

488

489

463 AQ:5