## POLITECNICO DI TORINO Repository ISTITUZIONALE

### Investigation on the Switching Waveforms of GaN Power Devices to Gate Current Profiles

Original

Investigation on the Switching Waveforms of GaN Power Devices to Gate Current Profiles / Quitadamo, MATTEO VINCENZO; Raviola, Erica; Fiori, Franco. - STAMPA. - (2019). (Intervento presentato al convegno International Conference On Power Electronics, Control & Automation (ICPECA 2019) tenutosi a New Delhi (India) nel 16-17 November 2019) [10.1109/ICPECA47973.2019.8975559].

Availability: This version is available at: 11583/2756652 since: 2019-09-30T15:37:49Z

Publisher: IEEE

Published DOI:10.1109/ICPECA47973.2019.8975559

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# Investigation on the Switching Waveforms of GaN Power Devices to Gate Current Profiles

Abstract-The extended use of Gallium Nitride (GaN) transistors in power applications, such as automotive, industrial and power distribution, leads practitioners and researchers to a review of the classical driving techniques, to meet the different characteristics of such devices compared to traditional ones, such as MOS and IGBT. In particular, the smaller intrinsic capacitances of GaN transistors allows faster switching transitions, thus decreasing the power dissipation during commutations. On the other hand, the higher slope of the switching waveforms drives high frequency resonant circuit that, using slower devices, would not be excited. This paper proposes a technique to obtain an optimal pair of non-oscillating switching waveforms, which exploits time-varying resistances in the power loop. A gate charge driving technique, based on the modulation of the gate current, is exploited for shaping the optimal waveforms by means of the power transistor itself. A simulation analysis was carried out considering two different driving waveforms and studying the sensitivity of ringing as a function of their significant parameters. Such analysis highlights that the optimal switching waveforms can be obtained by means of several driving shapes. Finally, a comparison with the RC snubbered circuit, in terms of efficiency and ringing, is reported to highlight the advantages of the proposed technique.

Index Terms—GaN gate driver, EMI reduction, ringing suppression

#### I. INTRODUCTION

In recent years, wide bandgap semiconductors have become more and more popular in power electronics applications because of their higher efficiency with respect to traditional silicon devices [1]. In particular, GaN transistors exhibit a lower intrinsic parasitic capacitances, resulting in a higher switching frequency. Voltage and current transitions, therefore, are characterized by high dv/dt and di/dt, which may cause oscillations, worsen the electromagnetic (EM) performance and permanently damage the circuit components as a result of over-currents and/or over-voltages. Thus, switching waveforms should be tightly controlled to have the entire system operating in an optimal way.

The traditional approach when dealing with Si transistors is the use of RC snubbers and series gate resistance. Such solution allows one to remove the undesired oscillations, at the cost of lower efficiency and duration of transitions. Nevertheless, in the case of GaN transistors, the aforementioned drawbacks may not be acceptable.

Active Gate Driver (AGD) has become an established technique to address such issues. It consists of shaping the switching waveforms with the aim to reduce oscillations and overshoots, with negligible effect on efficiency. If the driver strength is modulated in a proper manner during transients, resonant circuits in the power loop are not excited and the slope of switching waveforms is barely affected, at the same time. In particular, gate resistance modulation [2], [3], staircase shaped gate voltage [4] or current [5], [6], have been successfully exploited. In principle, the power transistor should be slowed down during the Miller's plateau to not excite the resonant circuits, which results in a higher dissipation, since the transistor is kept in saturation.

On the other hand, little attention has been paid to AGD techniques for GaN devices. In this case, the gate driver should be able to modulate its strength with a sub-nanosecond time resolution. In particular, [8] and [9] propose a variable gate resistance, [10] and [11] an active dv/dt control and [12] a two-current level driver. However, a GaN driver with an optimal gate current waveform has not been presented yet. This work proposes a driving technique to lower the ringing phenomenon occurring on the switching node and current. A method to evaluate the optimal switching waveforms as a function of parasitic elements, and a technique to drive the power switch acting on gate charge are proposed. In particular, two different gate current waveforms are considered to highlight the pros and cons of each of them.

The paper is organized as follows: in Section II, a high side buck converter is analyzed to understand the effects of parasitic elements on the ringing. Section III proposes a criterion to prevent oscillations and a technique to obtain the optimal waveforms using the power GaN itself. Section IV reports a sensitivity analysis of the switching current as a function of significant parameters of the driving waveforms and a comparison between the proposed gate driver and the classical solution. Final remarks are withdrawn in the concluding section.

#### II. SWITCHING TRANSIENTS IN A BUCK CONVERTER

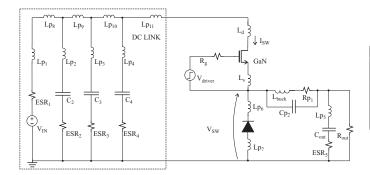

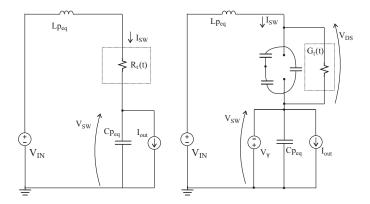

In this section, the switching behavior of a buck converter, shown in Fig. 1, is analyzed. Both high side and low side switches are GaN transistors, however, for the sake of simplicity, the low side one behaves like a free wheeling diode, meaning that its gate and source terminals are short circuited. The aim of the following analysis is to highlight which transitions cause voltage and current oscillations. In particular, it is assumed that the parasitic inductances  $L_d, L_s, L_{p_6}, L_{p_7}$  (Fig. 1) are far smaller than the equivalent inductance of the DC link. Such hypothesis is meaningful, since GaN devices

Fig. 1. Buck converter including its parasitic elements.

are typically available in lead-free packages. The analysis was performed assuming that the driver can source/sink all the needed current to turn-on/turn-off the switch, instantaneously.

#### A. High side switch turn-on

As long as the high side transistor is kept off, the load current flows through the freewheeling diode, which keeps the switching voltage  $V_{\rm sw}$  to the constant value  $-V_{\gamma}$ . When the driver voltage  $V_{\rm driver}$  goes up to its on-value, the current flowing in the high side transistor,  $I_{\rm sw}$  starts to increase, but the voltage  $V_{\rm sw}$  remains at  $-V_{\gamma}$  until the diode turns off, i.e. when  $I_{\rm sw}$  equals the load current  $I_{\rm out}$ . The rise time  $t_{\rm r}$  of  $I_{\rm sw}$  is only limited by the DC link parasitic inductance,  $L_{\rm peq}$ , (Fig. 3) accordingly to Eqn. 1.

$$t_r = L_{p_{eq}} \frac{I_{out}}{V_{in}}.$$

(1)

Such current transition can not cause any oscillations, because a constant voltage drops on all parasitic capacitances.

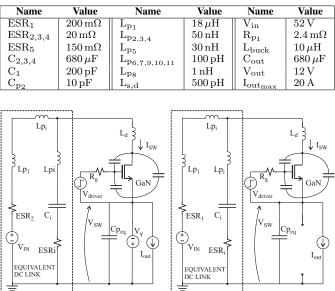

When the current  $I_{\rm sw}$  reaches its nominal value, the diode turns-off and the voltage  $V_{\rm sw}$  begins to rise. The power loop involved in this phase contains both the  $L_{\rm peq}$  and the low side parasitic capacitance. This means that the transient of  $V_{\rm sw}$  excites a resonant circuit, and uncontrolled oscillations of voltages and current take place. Fig. 2 shows the equivalent circuits modeling current and the voltage transitions, on the left and right side, respectively.

#### B. High side switch turn-off

When the driver turns-off the GaN transistor, the voltage drop across the high side switch starts to decrease. In this phase, the current  $I_{sw}$  is kept constant by the load, thus any current variation affects the inductance, and no resonance is excited (Fig. 2 on the right side).

Once the voltage  $V_{\rm sw}$  has reached the value  $-V\,\gamma$ , the freewheeling diode turns-on and the current  $I_{\rm sw}$  starts to decrease (Fig. 2 on the left side). Now the resonant circuit, consisting of the parasitic inductance  $L_{\rm peq}$  and the high side parasitic capacitance, oscillates.

#### C. Equivalent Circuit

The previous analysis suggests that only one transition, the voltage one for the turn-on and the current one for the turnoff, is responsible for exciting the corresponding resonant

TABLE I

Used values for components in buck converter.

Fig. 2. Equivalent circuits for the current transition (left side) and for the voltage transition (right side) during turn-on and turn-off.

circuit. Moreover, the analysis highlights that the frequency of oscillations could be different, since that the parasitic capacitance involved in the phenomena is not the same.

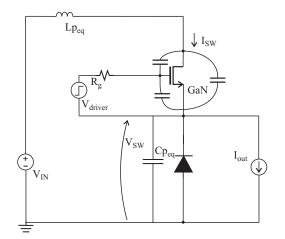

Fig. 3 shows an equivalent circuit modeling the ringing behavior of the proposed buck converter (Fig. 1).

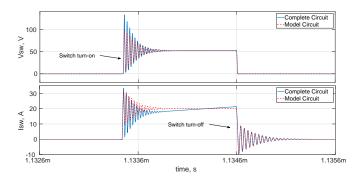

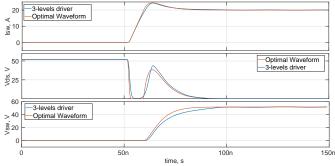

The values of  $L_{p_{eq}}$  and of  $C_{p_{eq}}$  can be extrapolated from the circuit in Fig. 1 using the procedure adopted in [13]. In order to validate the proposed equivalent circuit, a buck converter to step down an input voltage of 52 V to an output voltage of 12 V with the capability to provide the load with a current of 20 A, was designed. The devices used in the converter are EPC2001C GaN transistors [7]. Table I shows the adopted values regarding the other components. All simulations were performed in Cadence Virtuoso environment. In particular, the switching current exhibits an oscillation at  $f_{r1} = 37 \text{ MHz}$ after the turn-on, and one at  $f_{r2} = 56 \text{ MHz}$  after the turn-off. From these values, it is possible to compute the parameters of the proposed equivalent model, resulting in  $C_{p_{eq}} = 1 \, nF$ and  $L_{p_{eq}} = 18.5 \, nH$ . It should be noticed that the high side parasitic capacitance is already included in the model of the GaN transistor. The resonant frequencies of the complete circuit and of the proposed model are in good agreement both for the current  $I_{\rm sw}$  and the voltage  $V_{\rm sw},$  as shown in Fig. 4. On the other hand, the amplitudes of oscillations are different, since the ESR parasitic resistances are not included in the equivalent model.

#### **III. OSCILLATION DAMPING**

The equivalent circuit proposed in the previous section has been exploited to develop a method for damping oscillations. Such technique requires to properly dissipate the energy that,

Fig. 3. Equivalent circuit modeling the ringing behavior of the buck converter.

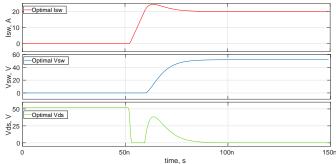

Fig. 4. Comparison between the switching waveforms of the buck circuit with parasitic elements (blue lines) and that of its equivalent circuit (red line). The voltage switching waveform is characterized only by the ringing at  $f_{r_1}$ , while, the switching current exhibits both ringing at  $f_{r_1}$  and  $f_{r_2}$ .

otherwise, would be exchanged by the aforementioned parasitics. For this purpose, a time-varying resistance in series to the high side switch and proportional to the derivative of  $V_{\rm sw}$  (see Fig. 5 on the left side), and a time-varying conductance in parallel to it, proportional to the derivative of  $I_{\rm sw}$  (see Fig. 2 on the right side), have been included in the circuit. Such power consuming elements are effective only during the transitions that can cause the oscillations, meaning that  $R_t(t)$  works only during the voltage transition of the turn-on, while  $G_t(t)$  is active only during the current transition of turn-off commutation. The values of  $R_t(t)$  and  $G_t(t)$  are chosen accordingly to Eqn. (2) where  $k_1$  and  $k_2$  are two constant coefficients.

$$R_t(t) = k_1 \frac{dV_{sw}}{dt} \qquad G_t(t) = -k_2 \frac{dI_{sw}}{dt} \qquad (2)$$

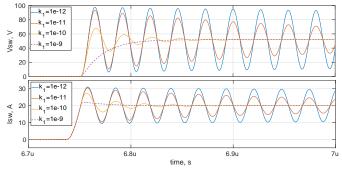

#### A. Evaluation of coefficient $k_1$

In order to find the optimal value of  $k_1$  coefficient, parametric simulations were carried out (Fig. 6). The aim of such simulations is to find out the best compromise between the amplitude of ringing and the transition speed. In accordance with the aforementioned analysis, only the slope of the switch-

Fig. 5. Equivalent circuits of voltage transition during the turn-on with the  $R_t(t)$  element (left side) and during the turn-off current transition with  $G_t(t)$  element (right side).

Fig. 6. Switching voltages and currents obtained performing a parametric simulation on  $k_1$  coefficient during the voltage transition of the turn-on phase.

ing voltage decreases because of R(t). For the proposed goals, the optimal value of  $k_1$  is approximately 400 ps/A.

#### B. Evaluation of coefficient $k_2$

The same type of simulation was performed for evaluating the  $k_2$  coefficient (Fig. 7). Also in this case, an inverse relationship between the amplitude of oscillations and the duration of the current transient exists. As in the previous case, a high value of such parameter implies a slower transition, whereas a lower value leads to oscillations. The optimal value of  $k_2$  results to be 90 ps/V, eventually.

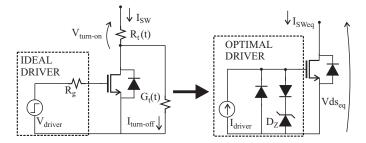

#### C. Using GaN transistor to reproduce the optimal waveforms

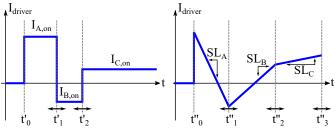

$R_t(t)$  and  $G_t(t)$  represent an intermediate step required to obtain the optimal switching waveforms, i.e. the faster and non oscillating ones. The behavior of such dissipative components should be reproduced exploiting the GaN transistor itself. In particular, during the turn-on, the voltage  $V_{turn_{on}}$  (Fig. 8) should drop on the power transistor, whereas, during the turnoff, the current  $I_{turn_{off}}$  (Fig. 8) should be entirely absorbed by the GaN switch. It is worth noticing that the diodes in the optimal driver circuit are only needed to clamp the driving voltage. For the sake of simplicity, only the turn-on optimal waveforms are considered in the following sections. In this paper, two different  $I_{driver}$  current waveforms, shown

Fig. 7. Switching voltage and current obtained performing a parametric simulation on  $k_2$  coefficient during the current transition of turn-off phase.

Fig. 8. Equivalent switch circuit with  $R_t(t)$  and  $G_t(t)$  (left side) and switch with optimal current driver (right side).

Fig. 9. Voltage and current waveforms that should be reproduced using the switch to obtain the optimal commutation during turn-on.

Fig. 10. Three-level current driver (on the left side) and three-slopes current driver (on the right side).

in Fig.10, are analyzed to highlight that the shape of the gate current is not crucial, but the key point is the matching of the optimal waveforms by means of the transistor itself. The first shape is a constant piecewise waveform where the second current level is negative, instead the second one is a variable slope saw-tooth waveform. Also in this case, there is a phase in which charge is extracted from the gate.

#### **IV. SIMULATION ANALYSIS**

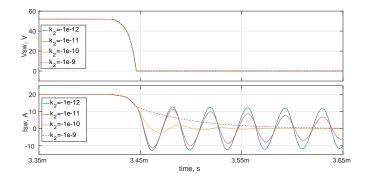

This section provides a validation of the proposed method by means of simulations. The parameters involved in the simulations are, for three-level constant waveforms, the first, the second and the third current levels,  $I_{A,on}$ ,  $I_{B,on}$ ,  $I_{C,on}$ , respectively, and the time instants  $t'_1$ ,  $t'_2$  (Fig. 10 on the left side). Instead, for the variable slope saw-tooth driver, the considered parameters are the slopes  $SL_A$ ,  $SL_B$ ,  $SL_C$  and the time instances  $t''_1$ ,  $t''_2$  (see Fig. 10 on the right side). All involved parameters are swept of 5% around optimal value.

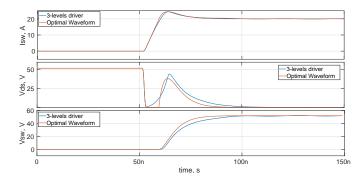

#### A. Three level constant piecewise driver

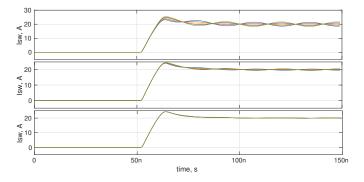

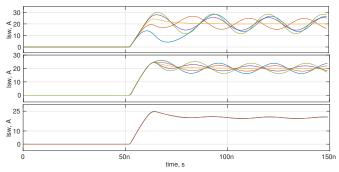

Firstly the finest parameters of the three-level constant piecewise were extrapolated to match the optimal waveforms. As shown in Fig. 11, they are in good agreement, meaning that the first proposed current driver, if properly tuned, allows the power transistor to emulate the R(t) behavior, thus removing the oscillations, completely. In order to assess such gate current waveform, sensitivity analysis were carried out, exploiting parametric simulations. In particular, Fig.12 depicts how the I<sub>sw</sub> current is affected by a variation of I<sub>A,on</sub>, I<sub>B,on</sub>, I<sub>C,on</sub>. It can be noticed that the first level is the most critical, since

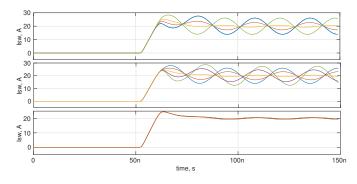

the ringing amplitude increases, significantly. Similarly, Fig. 13 (top and middle plots) shows the higher sensitivity of parameters  $t'_1, t'_2$  with respect to the previous ones. In the bottom plot of Fig. 13, finally, a variation of the slopes, i.e. the transitions from level 0 to  $I_{A,on}$ ,  $I_{A,on}$  to  $I_{B,on}$  and  $I_{B,on}$  to  $I_{C,on}$ , is simulated, keeping the middle point constant in time. It should be noticed that no variation occurs on  $I_{sw}$ , highlighting that the particular shape of the gate current is not crucial, if the injected/removed charge from the transistor is the same.

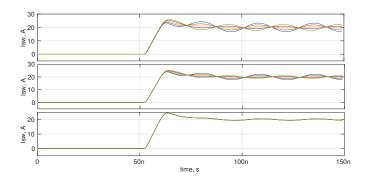

#### B. Variable slope saw-tooth driver

After the validation of the three-level current driver, a variable slope saw-tooth one was considered. A preliminary comparison with the optimal switching waveforms is reported, as shown in Fig. 14. Also in this case, the curves are in good agreement, as expected from the previously results of the slope variations, since only the net gate charge affects the results. As in the previous analysis, the sensitivity of significant parameters is simulated. Firstly, the different slopes were swept around the optimal value, resulting in a relevant sensitivity on slope  $SL_A$  with respect to the other two. Then, Fig. 16 reports the sensitivity analysis performed translating, at the same time,  $t''_0, t''_1$  (top), $t''_1, t''_2$  (middle) and  $t''_2, t''_3$  (bottom), and keeping the slopes constant at their optimal values. It can be noticed that the first two are the most significant for the ringing suppression.

Fig. 11. Comparison between the optimal switching waveforms (red) and the that obtained exploiting the tuned three-level current driver (blue).

Fig. 12. Switching current waveforms obtained varying with a 5 % the level of  $I_{\rm A,on}$  (top),  $I_{\rm B,on},$  (middle) and  $I_{\rm C,on},$  (bottom).

TABLE II Comparison between the most significant parameters interesting the buck converter working

|                              | No Snubber | Snubber RC with Rg | 3-level | Slope sawtooth |

|------------------------------|------------|--------------------|---------|----------------|

| $P_{sw}$                     | 1.62 W     | 4.68 W             | 3.66 W  | 3.65 W         |

| $\mathbf{P_{diode}}$         | 221 mW     | 198 mW             | 200  mW | 199  mW        |

| $P_{lsnb}$                   | //         | 1.43 W             | //      | //             |

| $\mathbf{P}_{\mathbf{hsnb}}$ | //         | 1.26 W             | //      | //             |

| $\mathbf{P_{tot}}$           | 1.84  mW   | 7.57 W             | 3.86 W  | 3.85 W         |

| $V_{swp}$                    | 103 V      | 58V                | 52V     | 52V            |

| $V_{ds_p}$                   | 193 V      | 65 V               | 68 V    | 68V            |

| $I_{swp}$                    | 33 A       | 30 A               | 25 A    | 25 V           |

#### C. Comparison with standard solution

The traditional solution consists of an high side and low side snubber with a fixed  $R_g$ . The design of the two snubbers was performed as reported in [13]. The comparison was carried out between no snubber, traditional approach and the two proposed gate waveforms. Table II lists the considered figures of merit which are: the power dissipated by the low side switch ( $P_{sw}$ ), by the high side diode ( $P_{diode}$ ), by the snubbers ( $P_{lsnb}$  and  $P_{hsnb}$ ) and their sum ( $P_{tot}$ ), and finally their peak values ( $V_{sw_p}$ ,  $V_{ds_p}$ ,  $I_{sw_p}$ ). The data shows an increment of the efficiency of more than 50%, reducing the peak of the switching current and voltage. Finally, the threelevel driver and the variable slope one are characterized by similar performance because they match the optimal waveform in the same way.

Fig. 13. Switching current waveforms obtained varying with a 5% the value of  $t'_1$  (top),  $t'_2$  (middle) and the current slopes (bottom).

Fig. 14. Comparison between the optimal switching waveforms (red) and the that obtained exploiting the tuned slope variable saw-tooth current driver (blue).

#### V. CONCLUSION

In this paper, a method to extract the optimal switching waveforms for GaN transistors is presented. Firstly, the turnon and turn-off commutations are analyzed referring to a high-side buck converter, then, the optimal switching waveforms are extracted by means of intermediate dissipative timevariant elements. The GaN transistor was driven to reproduce the obtained waveforms. In particular, a three-level constant current and a variable slope sawtooth current driver were considered, proving the effectiveness of the proposed method. Simulation results show that both current drivers are able to match the optimal waveforms. Finally, a comparison with standard solution, i.e. RC snubber and gate series resistance, shows that the proposed technique reduces the total dissipated power of about 50% respect to traditional approach, reducing the peaks of switching current and voltage significantly. The similar performance of the three-level gate driver and of the variable slopes one supports that the input waveform are equivalent, proving that the optimal matching can be obtained with several waveforms.

#### REFERENCES

F. Roccaforte, P. Fiorenza, G. Greco, R. Lo Nigro, F. Giannazzo, F. Iucolano, M. Saggio, "Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices", Microelectronic Engineering, vol. 187–188, pp. 66-77, 2018.

Fig. 15. Switching current curves with a  $5\,\%$  variation on level  $\rm SL_A, SL_B, SL_C$  (from the top to the bottom).

Fig. 16. Switching current curves with a 5% variation of time offset (from the top to the bottom).

- [2] L. Middelstaedt, J. Wang, B. Stark, and A. Lindemann, "Direct Approach of Simultaneously Eliminating EMI-Critical Oscillations and Decreasing Switching Losses for Wide Bandgap Power Semiconductors", IEEE Transactions on Power Electronics, vol XX, pages YY, April 2019.

- [3] H. Dymond, J. Wang, et al. "A 6.7-GHz Active Gate Driver for GaN FETs to Combat Overshoot, Ringing, and EMI", IEEE Transactions on Power Electronics, vol. 33, issue 1, pp. 581-594, Jan. 2018.

- [4] N. Idir, R. Bausiere and J. J. Franchaud, "Active gate voltage control of turn-on di/dt and turn-off dv/dt in insulated gate transistors," in IEEE Transactions on Power Electronics, vol. 21, no. 4, pp. 849-855, July 2006.

- [5] M. Rose, J.Krupar, and H. Hauswald, "Adaptive dv/dt and di/dt control for isolated gate power devices", 2010 IEEE Energy Conversion Congress and Exposition, Sept. 2010.

- [6] M. Blank, T. Glück, A. Kugi and H.-P. Kreuter, "Slew rate control strategies for smart power ics based on iterative learning control", in Proceedings of Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX,USA, Mar. 2014, pp. 2860–2866

- $\cite{tabular} [7] epc-co.com/epc/documents/datasheets/EPC2001C_datasheet.pdf$

- [8] J. Yu, W. J. Zhang, A. Shorten, R. Li and W. T. Ng, "A smart gate driver IC for GaN power transistors," 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, 2018, pp. 84-87.

- [9] H. C. P. Dymond et al., "A 6.7-GHz Active Gate Driver for GaN FETs to Combat Overshoot, Ringing, and EMI," in IEEE Transactions on Power Electronics, vol. 33, no. 1, pp. 581-594, Jan. 2018.

- [10] P. Bau, M. Cousineau, B. Cougo, F. Richardeau, D. Colin and N. Rouger, "A CMOS gate driver with ultra-fast dV/dt embedded control dedicated to optimum EMI and turn-on losses management for GaN power transistors," 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, 2018, pp. 105-108.

- [11] B. Sun, R. Burgos, X. Zhang and D. Boroyevich, "Active dv/dt control of 600V GaN transistors," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-8.

- [12] S. T. Li, P. Y. Wang, C. J. Chen and C. Hsu, "A 10MHz GaN Driver with Gate Ringing Suppression and Active Bootstrap Control," 2019

IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Taipei, Taiwan, 2019, pp. 1-4.

- [13] R. Severns, "Snubber Circuits For Power Electronics", Rudolf Severns, 2006.

- [14] K. Harada, T. Ninomiya, "Optimum Design of RC Snubbers for Switching Regulators", IEEE Transactions on Aerospace and Electronic Systems, vol. AES-15, pp. 209-218, March 1979.