# Doctoral Dissertation Doctoral Program in Computer and Systems Engineering (XXXI cycle)

# Network-on-Chip -based Multi-Processor System-on-Chip: Towards Mixed-Criticality System Certification

By

#### Serhiy Avramenko

\*\*\*\*\*

#### **Supervisor(s):**

Prof. M. Violante

#### **Doctoral Examination Committee:**

Prof. A. Bosio, École Centrale de Lyon, France

Prof. M. Jenihhin, Tallinn University of Technology, Estonia

Prof. M. Ottavi, Università degli Studi di Roma Tor Vergata, Italy

Politecnico di Torino 2019

#### **Declaration**

Serhiy Avramenko 2019

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

To my family, for everything I am.

To my friends, for being part of my family.

## Acknowledgements

I would like to thank my advisor M. Violante for his teachings, insights and patience.

I would also like to thank S. Esposito, for his precious insights.

#### **Abstract**

The usage of single-core—based microprocessors is slowly disappearing, while multi-core—based devices are becoming the only normally used nowadays. This is true also for the critical domains, like for instance avionics domain. However, the key point for such domains is that the multi-core microprocessors are de facto used as single-core devices. In fact, all-but-one executing cores are powered off. Meanwhile, the market offers more and more sophisticated solutions, proposing so called Multi-Processor System-on-Chip (MPSoC) device generation. These devices integrate tens or even hundreds of processing cores and peripherals on the same chip, connected through the network-on-chip (NoC) interconnection

The main obstacle for the usage of multi-core and MPSoC devices in the context of critical systems is the high certification effort required to ensure the proper level of dependability (and especially safety) for a system based on such kind of devices. Considering the commercial off-the-shelf (COTS) devices, these do not present any safety-dedicated features as the critical domains market size is relatively negligible. In fact, the high non-recurring engineering cost prevents the development of any COTS MPSoC specifically designed for the safety-critical applications.

This thesis presents several solutions to address the main dependability issues, preventing the usage of MPSoC-based systems in the critical systems context. In particular the avionics domain is considered, and the main focus is put upon the safety issues related to the usage of a shared interconnection, for what it concerns the temporal isolation between the software components. Although, the avionics domain is explicitly considered, the techniques presented are expected to be applicable for a generic safety-critical and even mission-critical domains, given that the required adaptation to the domain-specific peculiarities is done. As further contribution, this dissertation presents solutions to easier the dependability assessment of software components at executing core level.

Considering the executing core level, a proper fault tolerance against radiation induced soft errors was and remains crucial for the space applications. However, as the geometries keep shrinking and power saving techniques are becoming more and more aggressive, the issue of soft errors is no longer a space domain's prerogative. This thesis proposes an approach to rank a set of candidate software modules according to their intrinsic robustness to the soft errors. The main advantage of the proposed approach is that it's almost agnostic of the actual architectural details of the executing platform as it is based on software-level fault injections. The information collected during the proposed high-level analysis can also be used optimize the hardening phase.

As main contributions of this thesis, I address the main safety issues concerning the shared (NoC) interconnection of an MPSoC, both considering COTS and custom components. In particular, I focus on the temporal isolation of software components running on the same MPSoC. A typical safety-critical scenario is considered, where the software components have different levels of criticality (or severity of failure), i.e., mixed criticality scenario. As the main contribution, I propose some partitioning techniques to enable the usage of (NoC-based) MPSoC for the mixed criticality systems, both considering COTS and custom devices. For what it concerns the usage of COTS devices, where the main effort was spent, the proposed technique exploits the deterministic routing algorithm of the NoC. The proposed solution is suitable for an ample range of MPSoC devices as its requirements consider a fairly common MPSoC characteristics. The partitioning technique is intended to have a purely software implementation, as a module of a real-time operating system, which targets both the certification potential and reusability aspects. For what it concerns the custom NoC architectures, a set of simple solutions has been derived with the specific purpose of high certification potential.

# **Contents**

| Li | st of I | Figures       |                                                                | X    |

|----|---------|---------------|----------------------------------------------------------------|------|

| Li | st of T | <b>Fables</b> |                                                                | xiii |

| No | omeno   | clature       |                                                                | XV   |

| 1  | Intr    | oduction      | n                                                              | 1    |

|    | 1.1     | Mixed-        | -Criticality System: NoC-based MPSoC                           | 3    |

|    | 1.2     | Function      | onal Safety: Temporal Partitioning                             | 6    |

|    |         | 1.2.1         | State-of-the-art                                               | 8    |

|    |         | 1.2.2         | Author's Contribution (Functional Safety)                      | 11   |

|    | 1.3     | Reliabi       | lity Analysis: Comparing Program Susceptibility to Soft Errors | 14   |

|    |         | 1.3.1         | State-of-the-art                                               | 15   |

|    |         | 1.3.2         | Author's Contribution (Reliability Analysis)                   | 15   |

|    | 1.4     | Outline       | 2                                                              | 17   |

| 2  | Proc    | cessor-b      | ased Critical Systems                                          | 21   |

|    | 2.1     | Multi-p       | processor System-on-Chip                                       | 21   |

|    |         | 2.1.1         | Network-on-Chip: Structure and Design Space                    | 23   |

|    |         | 2.1.2         | NoC Performance Parameters                                     | 32   |

|    |         | 213           | MPSoC examples                                                 | 34   |

viii Contents

|   | 2.2   | Depen    | dability                                               | 36 |

|---|-------|----------|--------------------------------------------------------|----|

|   |       | 2.2.1    | Attributes                                             | 36 |

|   |       | 2.2.2    | Threats                                                | 37 |

|   |       | 2.2.3    | Means                                                  | 43 |

|   | 2.3   | Safety   | -critical, Mission-critical and Non-critical Systems   | 44 |

|   | 2.4   | Mixed    | -criticality: Requirements and Issues                  | 45 |

|   |       | 2.4.1    | Critical System Design                                 | 45 |

|   |       | 2.4.2    | Mixed-criticality System: Processor Level              | 51 |

|   | 2.5   | MPSo     | C-based Mixed-criticality System                       | 52 |

| 3 | NoC   | partiti  | oning and RTOS filtering module: COTS NoC-based MCS    | 54 |

|   | 3.1   | COTS     | NoC-based MCS: State-of-the-art                        | 55 |

|   |       | 3.1.1    | NoC Resource Sharing -based techniques                 | 56 |

|   |       | 3.1.2    | NoC Resource Permanent Reservation -based techniques   | 58 |

|   |       | 3.1.3    | Gaps Inside the State-of-the-art                       | 59 |

|   | 3.2   | Propos   | ed Partitioning Solution                               | 59 |

|   |       | 3.2.1    | Considered NoC Model                                   | 60 |

|   |       | 3.2.2    | Off-line Partitioning: Applications Placement          | 61 |

|   |       | 3.2.3    | On-line Monitoring: Filtering                          | 65 |

|   |       | 3.2.4    | On-line Connectivity Reduction Mitigation: Redirection | 66 |

|   | 3.3   | Filterin | ng Module Implementation                               | 67 |

|   | 3.4   | Redire   | ction Module Implementation                            | 74 |

|   | 3.5   | Experi   | mental Evaluation                                      | 77 |

|   | 3.6   | Summ     | ary                                                    | 81 |

| 4 | QoS   | inNoC:   | hardware-implemented NoC partitioning for mixed criti- | •  |

|   | calit | y        |                                                        | 83 |

|   | 4.1   | Custor   | n NoC-hased MCS: State-of-the-art                      | 85 |

|          | •  |

|----------|----|

| Contents | 17 |

| Contonts | 11 |

|          |    |

|   | 4.2  | Propos    | sed Partitioning Solution                                   | 87  |

|---|------|-----------|-------------------------------------------------------------|-----|

|   |      | 4.2.1     | Considered NoC Model                                        | 87  |

|   |      | 4.2.2     | Application Placement Phase                                 | 90  |

|   |      | 4.2.3     | Partitioning Enforcement                                    | 92  |

|   | 4.3  | NoC A     | Architectures and Partitioning Solution Implementation      | 92  |

|   |      | 4.3.1     | Baseline LBDR                                               | 93  |

|   |      | 4.3.2     | Extended LBDR                                               | 93  |

|   |      | 4.3.3     | Routing-table Based                                         | 94  |

|   | 4.4  | QoSin     | NoC                                                         | 94  |

|   | 4.5  | Experi    | imental Evaluation                                          | 96  |

|   | 4.6  | Summ      | ary                                                         | 99  |

| 5 | Higł | 1-level 1 | ranking of candidate software susceptibility to soft errors | 102 |

|   | 5.1  | Radiat    | tion Effects Evaluation: State-of-the-art                   | 103 |

|   | 5.2  | Propos    | sed Ranking Technique                                       | 104 |

|   |      | 5.2.1     | The Overall Approach                                        | 104 |

|   |      | 5.2.2     | Use Case: Sensor Data Lossless Compression                  | 107 |

|   |      | 5.2.3     | Candidate Executing Hardware Platform                       | 112 |

|   |      | 5.2.4     | Run-time Environment                                        | 112 |

|   |      | 5.2.5     | Fault Injection Environment                                 | 113 |

|   |      | 5.2.6     | Post-processing and Candidate Ranking Process               | 116 |

|   | 5.3  | Experi    | imental Evaluation                                          | 118 |

|   |      | 5.3.1     | Validation Environment                                      | 118 |

|   |      | 5.3.2     | Results Analysis                                            | 119 |

|   | 5.4  | Summ      | ary                                                         | 120 |

| 6 | Con  | clusions  | s and Future Work                                           | 124 |

| Referer | ices           | 135 |

|---------|----------------|-----|

| 6.4     | Future Work    | 132 |

| 6.3     | Contribution 3 | 130 |

| 6.2     | Contribution 2 | 127 |

| 6.1     | Contribution 1 | 125 |

|         |                |     |

# **List of Figures**

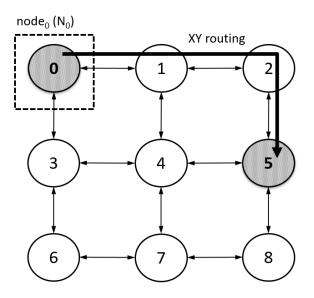

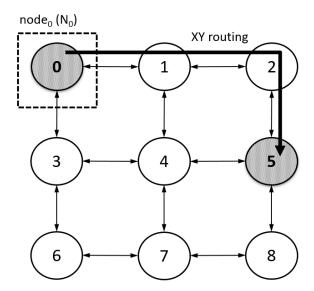

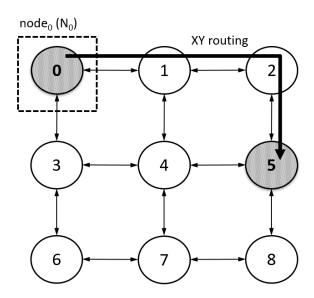

| 2.1 | A schematic view of a $3x3$ (2D) mesh topology NoC; $N_0$ to $N_5$ packet path under XY routing algorithm.                                                                                                                                                                                                                                          | 24 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

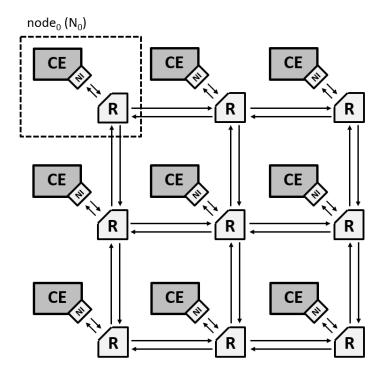

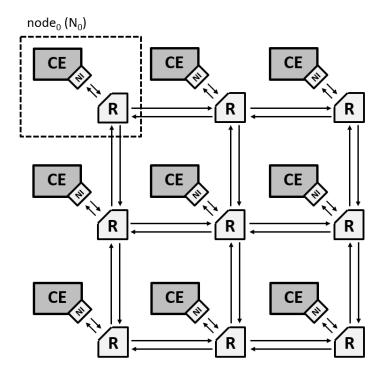

| 2.2 | A detailed view of a 3x3 2D mesh topology NoC; R - router; NI - network interface; CE - connected element                                                                                                                                                                                                                                           | 25 |

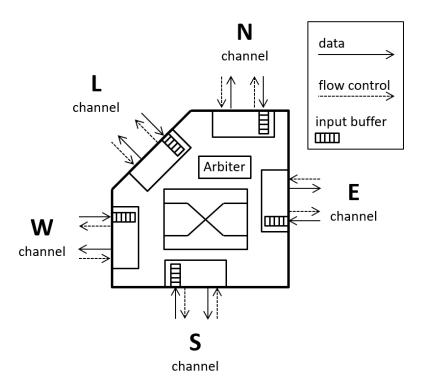

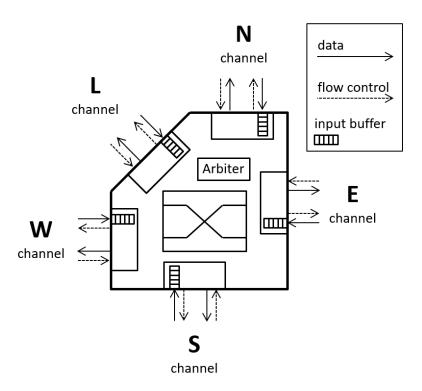

| 2.3 | A schematic view of a simple NoC router architecture for 2D mesh topology: input-buffered, based on a single physical network with no virtual channels, link made of two physical channels (one per direction)                                                                                                                                      | 32 |

| 3.1 | A schematic view of a $3x3$ (2D) mesh topology NoC; $N_0$ to $N_5$ packet path under XY routing algorithm.                                                                                                                                                                                                                                          | 61 |

| 3.2 | A detailed view of a 3x3 2D mesh topology NoC; R - router; NI - network interface; CE - connected element.                                                                                                                                                                                                                                          | 62 |

| 3.3 | A schematic view of a NoC router architecture; a simplest input-<br>buffered router architecture is considered, based on a single physical<br>network with no virtual channels; link made of two physical channels,<br>one per direction.                                                                                                           | 63 |

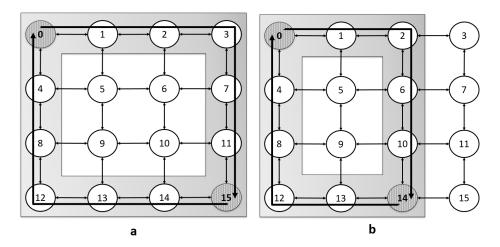

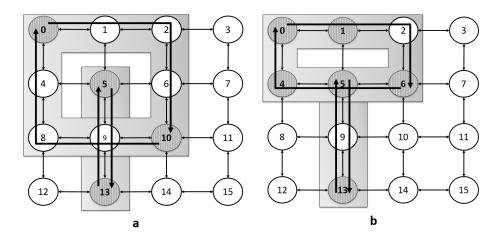

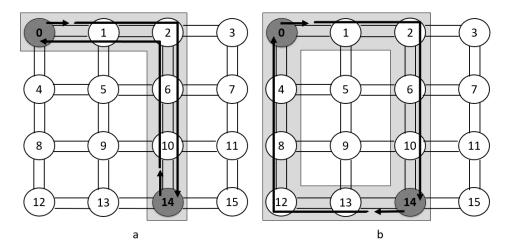

| 3.4 | MPSoC with 4x4 mesh topology NoC, XY routing; mixed-criticality system example $mcs_1$ : one C_app, one NC_app; black arrows: critical traffic paths; gray-shaded: critical regions (or domains) a) placing scenario $mcs_1_a$ : C_app_1 - $N_0$ and $N_{15}$ , NC_app_1 - all the remaining nodes; b) placing scenario $mcs_1_b$ : C_app_1 - $N_0$ |    |

|     | and $N_{14}$ , NC_app_1 - all the remaining nodes;                                                                                                                                                                                                                                                                                                  | 70 |

xii List of Figures

| 3.5 | MPSoC with 4x4 mesh topology NoC, XY routing; mixed-criticality system example $mcs_2$ : two C_apps, one NC_app; black arrows: critical traffic paths; gray-shaded: critical regions (or domains) a) placing scenario $mcs_2a$ : C_app_1 - $N_0$ and $N_{10}$ , C_app_2 - $N_5$ and $N_{13}$ , NC_app_1 - all the remaining nodes; b) placing scenario $mcs_2b$ : C_app_1 - $N_0$ , $N_1$ , $N_4$ and $N_6$ , C_app_2 - $N_5$ and $N_{13}$ , NC_app_1 - all the remaining nodes; | 73  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

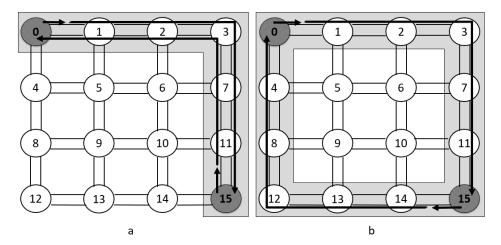

| 3.6 | MPSoC with 4x4 mesh topology NoC, XY routing; mixed-criticality system example $mcs_3$ : three C_apps, one NC_app; black arrows: critical traffic paths; gray-shaded: critical regions (or domains) placing scenario $mcs_3_a$ : C_app_1 - $N_0$ and $N_{10}$ , C_app_2 - $N_5$ and $N_{13}$ , C_app_3 - $N_3$ and $N_{15}$ , NC_app_1 - all the remaining nodes;                                                                                                                | 80  |

| 4.1 | A schematic view of a $3x3$ (2D) mesh topology NoC; $N_0$ to $N_5$ packet path under XY routing algorithm.                                                                                                                                                                                                                                                                                                                                                                       | 88  |

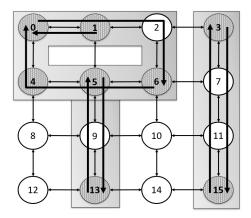

| 4.2 | MPSoC with 4x4 mesh topology NoC; mixed-criticality system example: one C_app, one NC_app; black arrows: critical traffic paths; gray-shaded: critical regions (or domains) a) placing scenario $mcs_1_a$ : C_app_1 - $N_0$ and $N_{15}$ , NC_app_1 - all the remaining nodes, rout_alg_A is used for C_app_1; b) placing scenario $mcs_1_b$ : C_app_1 - $N_0$ and $N_{15}$ , NC_app_1 - all the remaining nodes, rout_alg_B is used for C_app_1;                                | 89  |

| 4.3 | MPSoC with 4x4 mesh topology NoC; mixed-criticality system example: one C_app, one NC_app; black arrows: critical traffic paths; gray-shaded: critical regions (or domains) a) placing scenario $mcs_2a$ : C_app_1 - $N_0$ and $N_{14}$ , NC_app_1 - all the remaining nodes, rout_alg_A is used for C_app_1; b) placing scenario $mcs_2b$ : C_app_1 - $N_0$ and $N_{14}$ , NC_app_1 - all the remaining nodes, rout_alg_B is used for C_app_1;                                  | 97  |

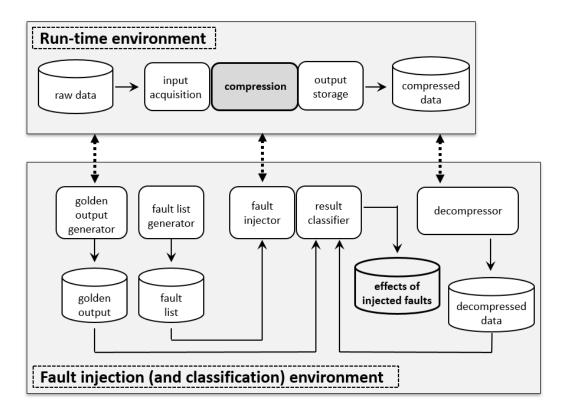

| 5.1 | The experimental environment                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106 |

# **List of Tables**

| 2.1 | DAL: failure condition severity, probabilities [1/flight hour], and levels                                                              | 48  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Placement scenario $mcs_1_a$ : connectivity table for $N_2 \dots \dots$                                                                 | 72  |

| 3.2 | Placement scenario $mcs_1_a$ : redirection table for $N_2 \dots \dots$                                                                  | 76  |

| 3.3 | Critical traffic latency (ns): baseline setup                                                                                           | 78  |

| 3.4 | Critical traffic latency (ns): proposed solution implemented                                                                            | 78  |

| 3.5 | Reachability without redirection for $mcs_1_a$ scenario (non-critical nodes only)                                                       | 79  |

| 4.1 | Architectural only figures of merit (4x4 network)                                                                                       | 98  |

| 4.2 | Figures of merit: mcs_1                                                                                                                 | 98  |

| 4.3 | Figures of merit: mcs_2                                                                                                                 | 99  |

| 5.1 | Compression programs characteristics                                                                                                    | 111 |

| 5.2 | Compression programs figures of merit: compression ratio and compression rate                                                           | 112 |

| 5.3 | Number of actually used general purpose registers                                                                                       | 19  |

| 5.4 | Results of fault injection into program variables, normalized per number of used registers                                              | 120 |

| 5.5 | Results of fault injection into program variables, normalized with respect to both the number of used registers and the execution time. | 120 |

| 5.6 | Results of fault injection into general purpose registers                                                                               | 121 |

| 5.7 | Results of fault injection into general purpose registers, normalized |

|-----|-----------------------------------------------------------------------|

|     | with respect to the execution time                                    |

## **Nomenclature**

#### **Acronyms / Abbreviations**

1D one-dimensional

2D two-dimensional

APEX APplication EXecutive

API application programming interface

ASIL automotive safety integrity level

C\_app critical application

CE connected element

COTS commercial off-the-shelf

DAL design assurance level

EASA European Aviation Safety Agency

FAA Federal Aviation Administration

FDAL functional development assurance level

flit flow control unit

GPR general-purpose registers

HI high-criticality

I/O Input/Output

**xvi** Nomenclature

IDAL item development assurance level

IP intellectual property

IP core intellectual property core

LBDR logic-based distributed routing

LO low-criticality

MBU multiple-bit upset

MCS mixed-criticality system

MMU memory management unit

MPSoC multiprocessor system-on-chip

NC\_app non-critical application

NI network interface

NoC network-on-chip

NRE non-recurring engineering

PE processing element

PIR packet injection rate

QoS quality of service

RAM reliability, availability and maintainability

RTOS real-time operating system

SBU single-bit upset

SEB single event burnout

SEE single event effect

SEFI single event functional interruption

SEL single event latchup

Nomenclature xvii

SET single event transient

SEU single event upset

SIL safety integrity level

SoC system-on-chip

SWaP space, weight and power

TDM time-division multiplexing

TID total ionizing dose

WCTT worst-case traversal time

# **Chapter 1**

#### Introduction

In the distant 1971, the first commercial microprocessor was born to create a calculator. That microprocessor was Intel 4004 and the calculator was Busicom 141-PF. Nowadays it is hard to imagine a system which does not contain a computer, from a refrigerator to an aircraft, computer systems penetrated all the areas of technology.

Among the processor-based systems, *mission-critical systems* (e.g., satellite systems) and *safety-critical systems* (e.g., power plain control, avionics) form a niche domain. These systems (from now on referred as *critical systems*) are both characterized by the fact a failure of one of such systems can lead to extremely negative consequences. For a safety-critical system such consequences can be injuries or death of people and/or severe environmental damage, for a mission-critical system – a huge economic damage.

For such systems, the nonfunctional requirements (such as cost and energy efficiency) become secondary with respect to requirements like *dependability* and in particular *safety*. The dependability can be defined in many ways, one of which is presented in [1] as: "the trustworthiness of a computing system that allows reliance to be justifiably placed on the services it delivers." The safety is an important attribute of the dependability, and concerns the "absence of catastrophic consequences" [2].

On the other hand, each new generation of processors exhibit higher densities and lower operating voltages [3]. This decreases the dependability of such devices as several phenomena (e.g., susceptibility to hardware faults caused by electromagnetic radiation) become more and more relevant.

Unfortunately, the history knows some episodes when the hypothetical consequences of a critical system failure actually took place. Among the most known cases there is the one concerning some Toyota car models. These cars were reported to autonomously accelerate and even contemporary reduce the controllability of the car by the driver. This issue was active between 2000 to 2010 and led to at least 89 casualties [4, 5]. The exact cause is unknown, but the radiation induced bit flips (and no protection against them) are assumed to be a possible cause [6].

Driven by the incidents like the aforementioned, by the end of 2011, first edition of ISO26262 standard [7] was created. The standard, entitled *Road vehicles* – *Functional safety*, became indispensable for automotive companies to assure their products are as safe as possible. The ISO26262 derives from the IEC-61508 standard [8] and it is adopted for the specific requirements of automotive domain. Other safety critical domains have similar standards as for instance RTCA DO-178C [9] and the RTCA DO-254 [10] for avionics. For a safety-critical system to have a dependability certification in general — and safety certification in particular — is a must. The standards are developed, among other, to reduce the certification effort as the latter is extremely high for a safety-critical system.

Apart from facing the issue of faults (and bugs) as such, a critical system must provide a proper level of isolation between the functions it implements. This isolation is required in order to assure a faulty function will not be able to corrupt other functions of the system. I.e., given a function, made of a set of hardware and software components, it is mandatory to assure that a fault can not propagate from one of its components to a component of another function.

Given this isolation requirement, for a critical system it was historically strongly discouraged to execute multiple applications on the same processing platform, while in some domains (e.g., avionics) this was explicitly forbidden [11]. Thus, each application (or a set of tightly correlated applications) was deployed on a dedicated computer, isolated from the resources of the other, although the computers could be interconnected. This paradigm is called *federated architecture* and aims to minimize any resource sharing. The reason was the difficulty to assure, in case a set of application would share a resource, one of those application will not corrupt the data or degrade the timing properties of the other applications. For the same reason the usage of multi-core processors was absolutely disregarded for critical

systems. In fact, a multi-core processor will for sure have at least the interconnection infrastructure to be shared between the cores.

Section 2 will provide precise terminology and more insight into concepts briefly introduced so far (as well as related to those concepts introduced by the following part this introduction chapter). The following Section 1.1 will briefly introduce the context of this dissertation – MPSoC-based critical systems. Then, in Section 1.2 and Section 1.3 the contributions of this dissertation will be briefly introduced. Section 1.4 gives an outline of this dissertation.

#### 1.1 Mixed-Criticality System: NoC-based MPSoC

The concept of *level of assurance against failure* is crucial for the design of a safety-critical system and thus for this dissertation. Considering an avionic example, the flight control system and the system in charge of in-flight entertainment, are both systems expected to work properly. However, the flight control system is expected to be developed in such a way to assure the related component will never fail during the functioning of the system. On the other hand, the failure in-flight entertainment is a function much less important with respect to the previous one.

The concept of level of assurance against failure is adopted by each critical domain or sector with slightly different peculiarities and it is referred to with different names. Safety integrity level (SIL) defined by IEC-61508 as generic functional safety concept, automotive safety integrity level (ASIL) is defined by ISO 26262 for automotive domain, design assurance level (DAL) is defined by RTCA DO-178C for avionic domain, etc. Considering for instance the avionic domain, if a certain function is considered of the highest DAL (i.e., DAL A), then the developer is required to certify that a failure of such function is virtually impossible. Analogously, a function is considered DAL E if its failure will have no effect. A key consequence is a much lower effort required to develop a DAL E component.

Industrial standards usually define four or five levels of criticality. However, in this introduction (and in the rest of the dissertation) I will consider two levels of criticality. This simplification will allow a simpler problem modeling (and solution description), without removing nothing from the latter. In detail, I refer to them as *low-criticality* (LO) task (or application) and the *high-criticality* (HI) one. I will also

consider LO to be a *non-critical application* (NC\_app), while HI to be a *critical application* (C\_app). Thus, in this dissertation LO and HI are synonyms of NC\_app and C\_app respectively.

The existence of the concept of a *component* having a given level of assurance against failure directly implies the existence of the concept of *isolation* between the components. If the independence between components cannot be demonstrated that all the components must be considered as a single macro-component. In this case the DAL assigned to this macro-component is the highest among the DALs of the components it is made of. This eventuality will result in much higher development cost, which can easily make the product economically unfeasible. In the first place, several components would require a higher DAL, as all the components should have a DAL equal to the highest among the DALs of the components the macro-component is made of. Furthermore, this macro-component will exhibit a complexity level well above the one related to the set of independent components.

From the aforementioned, it is clear how the federated architecture was an easy solution to assure the isolation between the components of the system. However, the ever-growing number of functions and their complexity made federated architecture paradigm no longer sustainable. Driven by the growing maintenance cost and other factors, industry developed several standards (e.g., [12], [7]) to allow multiple functions or applications to run on the same hardware platform. Furthermore, even the execution of software components having different DAL (or level related to the specific domain) was standardized. Thus, the *mixed-criticality systems* (MCS) paradigm was born, as components having different levels of assurance against failure was executed on the same platform.

When academic literature and the industrial standards are considered, the term *criticality* is used to indicate similar — but still different — concepts. In this dissertation *level of criticality* will be used as a synonym of level of severity of consequences of failure.

Nowadays, the mixed criticality is a common practice, for most critical domains and it is supported by the widely accepted standards. However, the executing platform of such systems have be *single-processor-based*. Considering the avionic domain, in case multi-core processors are used, the certification authority requires the designer to disable all the cores but one and to demonstrate that the disabled cores will remain disabled even in case of unexpected behavior.

On the other hand, the cutting-edge COTS processors can integrate tens of intellectual property (IP) cores on the same chip. These devices, generally referred to as *multiprocessor system-on-chip* (MPSoC), make use of a network-on-chip (NoC) interconnection which meets the scalability needs. From the aforementioned, it is evident the gap between the market products and the industry single-core—based systems.

As the number of required functionalities (and its complexity) keeps growing, it is reasonable to consider that the single-core—based system paradigm will become no longer sustainable, the same way it was for federated architecture paradigm. For instance, considering the avionics and space domains, the space, weight and power (SWaP) are extremely important from the economic point of view. The usage of multi-core would allow to move applications currently running on a set of single-core processors to much smaller number of multi-core processors. Thus, an important reduction of number of onboard hardware components will be achieved.

Both academic and industrial sectors are active in the study of issues related to the usage of multi-core systems in the context of mixed criticality. Considering avionics domain, some certifications are expected by the end of 2019 [13], while currently no certified (thus, no deployed on the field) multi-core–based MCS exists.

The main reason the multi-core—based systems are not used by most critical domains is the high complexity to certify a proper dependability level. The main issue is represented by the resources shared by the applications (or tasks) running on a multi-core processor or a MPSoC. This sharing can create data corruption and unacceptable delays. As already briefly introduced before, the isolation between the components must be demonstrated, otherwise the very concept of component disappears and the whole system can only be seen as *monolithic entity*.

For a critical system a missed deadline is (generally) considered a failure. Thus, it should be certified a sufficiently low probability of a system failure provoked, among the other, by different tasks competing for the same resource. In practice, this requires estimating, with a sufficiently high confidence, the worst-case interference between applications running on the different cores of a multi-core processor. This estimation should consider both hardware and software faults, and should be sufficiently convenient for the certification entity.

An additional factor for the complexity to achieve such estimation is the fact that, on one hand the custom design struggles to justify the non-recurring engineering

(NRE) as the number of required components is relatively small; on the other hand, the commercial off-the-shelf (COTS) components have almost no mechanism to enforce the bounded interference or at least facilitate the interference analysis (as many micro-architectural details remain confidential).

From the certification point of view, the usage of MPSoC-based systems requires a further effort with respect to the multi-core-based systems. This is due the additional complexity of NoC interconnection with respect to the classic bus interconnection used multi-core processors. In order to get closer to the creation of MPSoC-based MCS we need a set of sufficiently simple techniques to face the issues currently open [14].

The thesis focuses on safety improvement and reliability analysis techniques for a MPSoC-based MCS creation, in particular in avionics and space domains.

#### 1.2 Functional Safety: Temporal Partitioning

The main focus is put on deriving techniques to create a COTS MPSoC-based MCS with a certification potential. As already described in the previous section, the presence of shared resources is the main reason the MPSoC technology is not used for critical systems design. A shared resource which is for sure present in any realistic usage of MPSoC is its on-chip interconnection infrastructure, i.e., NoC. The main contribution of this thesis are the techniques aiming to solve the issues related to this specific component. Alongside with COTS MPSoC, this dissertation presents some of the solutions derived considering a custom NoC architectures.

When a safety-critical system is considered, a specific set of standards must be followed during all the phases of its developments. In this thesis I will mainly refer to the IEC-61508 and RTCA DO-178C, where the former is a basic functional safety standard while the latter is the standard concerning software development of an avionic system. Functional safety of a system is defined by IEC-61508 as active or passive means to "prevent hazardous events arising or providing mitigation to reduce the consequence of the hazardous event".

Considering the avionics, RTCA DO-178C describes a set of techniques to prevent software failures and/or limit their effects to the system functions. The main requirement to achieve this goal is to demonstrate that the software macro-

components will execute with a sufficient *independence*. If this independence cannot be demonstrated, then all those software components will be seen as a single software component when assigning the software DAL. This, in turn will imply that the DAL assigned to this software macro-component will reflect the highest failure severity of the software components it is composed of. Thus, the cost of this macro-component development will be much higher and will undermine the economical feasibility of the system.

Under RTCA DO-178C, the following software design methods are described: partitioning, dissimilarity (of multi-versioning) and safety monitoring. The software component isolation should be implemented by the partitioning. This is one of the most important design instruments (or concepts) to safety-critical systems (not only for avionics domain). The multi-versioning consists in two or more components implementing the same function to be developed independently. The goal of this technique is to provide the redundancy (thus to improve the reliability) to the system, while avoiding common source of errors. Finally, the safety monitoring is an active mechanism to implement the protection against specific failures. This mechanism also monitors the correct functioning of the partitioning technique.

The partitioning mechanism, described by the RTCA DO-178C, must address both the extent and the scope of the interactions between the partitioned components as well as how to isolate the components from each other. The isolation must be achieved in both spatial and temporal domains. *Spatial isolation* means that one application shall not corrupt data of another application. *Temporal isolation* on other hand concerns the timing properties and means that one application shall not cause failure (i.e., deadline miss) of another application by blocking a shared resource (e.g., CPU, interconnection). To achieve spatial isolation is relatively easy as the hardware means like memory management unit (MMU) can be exploit. The situation with the temporal isolation is more complex. The safety-critical domain is niche market so the COTS MPSoC features no hardware means to address with temporal isolation issue. On the other hand, the development of custom solutions should justify the related NRE cost.

An eventual timing interference between applications is due to implicit contention for micro-architectural resources (e.g., processor caches, interconnection) and by explicit contention for resources (e.g., processor time, peripherals, shared data structures). In this dissertation I target a specific source of implicit contention: NoC

interconnection. On the other hand, the explicit contention is out of the scope of this thesis.

#### 1.2.1 State-of-the-art

To cope with the temporal isolation issue in MPSoC, the literature provides several solutions. Some of these solutions are adopted from bus-based multi-core related techniques, while the other have been created specifically for NoC-based MPSoC. The main issues with these solutions are certification potential, as them do not consider the industrialist's perspective. A more extended discussion on the state-of-the-art is presented in the chapters dedicated to the single contributions of this thesis.

An important distinction I make in this thesis is whether a technique can be applied for COTS components or relies on some custom hardware design. This distinction is done as this thesis contributions concerning the timing isolation can be classified in the aforementioned way. While the solutions from the COTS group can be used for the custom design solutions, the contrary is not true.

The techniques that can be applied to COTS MPSoC can be further classified according to the main idea behind them. This classification can be done according to several criterion. In the scope of this dissertation I identify two macro-categories of techniques, according on how the NoC resources (links, FIFOs, etc.) are managed to ensure timing isolation: resource sharing and permanent resource reservation. Where the techniques of *permanent resource reservation* (or *resource privatization*) macro-category refer to the opposite situation with respect to the *resource sharing* scenario. I.e., each NoC resource is dedicated to an application an it is not shared with other applications running on the MPSoC. The QoS is often mentioned by the techniques from resource sharing macro-group, as the HI tasks are guaranteed with bounded transmission latency, throughput o similar metrics.

Another minor distinction concerns whether a technique is conceived for a specific MPSoC or it can be applied for a generic MPSoC (although fulfilling a set of requisites).

A first group of solutions are those targeting robust estimation WCET, explicitly facing the shared (NoC) interconnection issue. Some of these solutions face the temporal isolation issue explicitly, while other either face that issue implicitly and

indirectly or directly ignore the issue. Those techniques which ignore the temporal isolation issue are considered out of the scope of this dissertation. The authors in [15] explicitly target the time partitioning issue by implementing a NoC usage monitoring and bandwidth enforcing mechanism. The proposed mechanism is fairly simple and does not require VCs to be implemented. However, the NoC is considered as a black box for what it concerns the WCTT, which makes the whole solution incomplete. In [16] the authors provide a technique to estimate WCTT of a NoC, which could complete the solution proposed in [15]. However, the overall solution must be carefully evaluated as it seems to induce a heavy resource under-utilization. Furthermore, this overall solution appears to be complex and have several other small issues. Another approach to estimate WCET is the one making usage of VCs, and the related priority-based preemption mechanism [17]. One of the issues related to VCs usage is the complexity of the priority-based preemptive arbitration, which will play against the certification potential. This kind of solutions are also partial as there is no isolation between the processes having the same level of priority, and there are also some other minor issues. There are also some solutions aiming to monitor the interconnection actual congestion and to identify the anomalies [18]. This technique can be used to cope with the issues of the previously described techniques. However, at the best of my knowledge, these solutions are so far only for bus-based systems. Furthermore, an integration of this technique inside the previously described ones could make to overall complexity rise above the certification feasibility threshold.

Another group of techniques is based on hierarchical scheduling. This approach is based on the usage of a scheduling entity which queues the tasks of a certain priority. This scheduling entity will execute the tasks starting from the queues having higher priority. For instance, in [19] authors propose a solution which uses nodes of the NoC as centralized arbitration units called *resource managers*, which are in charge of controlling network access. The main issue of hierarchical scheduling is a high complexity and issues to connect two distant nodes.

Apart from the techniques derived for a class of NoC architectures, there are some conceived specifically for specific MPSoC (i.e., its NoC architecture). Among the latter, several techniques based on hierarchical scheduling are conceived for Kalray MPPA® 256 [20]. These techniques [21–23] exploit the special hardware the MPSoC is featuring. The main limit of these techniques is that they rely on a complex hardware could be an issue under the certification point of view.

An alternative to the resources sharing techniques (presented so far) consists in permanent resource reservation or resource privatization. In this macro-category, the NoC is not seen as a monolithic resource, instead it is considered as a set of resources (i.e., links, FIFOs, routers, etc.) potentially independent from each other. One of these techniques [24] is developed for for Tilera Tile Processor [25]. This technique (permanently) partition the NoC into regions, each node belonging to a region can only communicate to nodes of the same region. This solution is simple, which is an advantage from the certification point of view. The issues related to this approach are limits of proximity requirements for the nodes, as well as the specific hardware like the one featured by Tilera Tile Processor.

Considering the techniques relying on custom NoC architecture design, I will use the same classification used for techniques related to COTS MPSoC.

QNoC [26] was one of the first efforts to design a NoC architecture suitable for the creation of an MCS. The proposed architecture was based on preemptive priority scheduling. The architecture makes use of wormhole packet-based roundrobin scheduling which is used by the NoC architectures of many modern MPSoC. Several similar solutions, also based on the concept of priority based preemptive packet-based usage of the NoC were derived [27–33]. Each of these solutions is characterized by some peculiarities, but all make use of virtual channels, which is their main disadvantage when certification potential is considered.

One of the first solutions was also Æthereal [34] architecture implementing time-division multiplexing (TDM)-based circuit switching approach, where wires and buffers remain reserved for certain points in time. The resources are reserved for critical applications, while the non-critical applications use leftover bandwidth from the critical applications. This solution however presents several problems like the difficulty to support communication between distant nodes and presents a not negligible complexity as well.

The authors in [35] present a NI modification to allow TT-based scheduling of the NoC. This solution grants a bounded latency on high-criticality traffic by using a contention-free channel. However, to support the proposed approach the overall system should present a high level of complexity.

A different approach to the problem is *link division multiplexing technique* [36]. In this solution, each physical link is partitioned to simultaneously transmit serialized packets belonging to distinct traffic flows. The idea of this solution is appealing;

however, it presents a high complexity from both hardware and conceptual point of view.

Apart from the (NoC) resource sharing technique presented so far, there are some solutions based on avoiding resource sharing. In this macro-category, the NoC is not seen as a monolithic resource, instead it is considered as a set of resources (i.e., links, FIFOs, etc.) potentially independent from each other.

The authors in [37] use hardware-enforced segregation between a safety-critical domain and a non-safety-critical domain. The main limit of this solution, as it was for [24], is the high cost required to connect two distant nodes. The authors in [38] present a NoCDepend method to allow communication between critical regions, implemented by a set of nodes used as input and output gateways. Thus, this feature can solve the issue of connecting two (or more) distant nodes. However, this solution presents a certain complexity which can be a prohibitive for the certification cost. In addition, the authors in [38] present a dynamic reconfiguration technique. This can be used as an alternative to the inter critical region communication, however this solution presents the same disadvantages of circuit-switching—based solutions.

#### 1.2.2 Author's Contribution (Functional Safety)

As the main contributions of this thesis, I propose a technique to solve temporal isolation issues related to implicit contention of NoC interconnection. Both the COTS- and custom NoC-based MPSoC were considered, mainly targeting the avionic field.

All the proposed techniques provide the temporal isolation to critical applications and all are based on traffic flows isolation. For the COTS NoC-based MPSoC this isolation is implemented purely in software, targeting several architectures. For the custom-NoC-based MPSoC the temporal isolation is implemented purely by hardware means.

From the QoS point of view the proposed techniques offer two levels of service: guaranteed service (GS) and best effort (BE). An application running assigned with GS level is guaranteed to have bounded latency and throughput. On the other hand, applications running under BE level have no guarantees. The proposed techniques support an unbounded number of criticality levels, as each application running under the GS level is granted with the temporal isolation.

The rest of this section will first describe the contribution related to COTS-based MPSoC devices (seesectionsec:intro-contrib-NOC-COTS), then the custom NoC-based MPSoC will be considered in seesectionsec:intro-contrib-qosinnoc. Finally, in seesectionsec:intro-summary-contrib-functional an itemized summary of this contributions will be provided.

#### RTOS filtering module: COTS NoC-based MCS

Considering the COTS MPSoC, a technique requiring few information about the implementation details of NoC infrastructure was derived [39]. The proposed technique has been developed as a software module to be interred in a certified real-time operating system (RTOS). Once the RTOS is upgraded with the proposed module, the whole RTOS must undergo the certification process, as any modification invalidates the existing certification. This certification will be required only once, and the proposed solution can be reused for the future projects without requiring a new dedicated certification. It should worth to notice that generally (and especially for avionics), a new system must be certified as a whole. However, if the proposed solution will be already certified, then the whole certification process is easier.

This solution is based on traffic flows isolation and can be applied to a set of architectures. From the quality of service (QoS) point of view, it features two levels of service: guaranteed service (GS) and best effort (BE). However, the proposed solution allows an unbounded number of applications and criticality levels to be implemented. Each application, which is set to have GS level of service, is guaranteed to have bounded latency and throughput. I.e., the proposed approach guarantees that no interference from the other applications does exists. I analyze the limits of the proposed solution especially for it concerns the connectivity issue and draw some rules to allow an efficient usage of the proposed methodology.

#### QoSinNoC: framework to custom NoC comparison for mixed criticality

Concerning the custom NoC design, QoSinNoC framework [40] was developed to analyze a set of NoC architectures and techniques to allow their usage in the context of mixed criticality. The goal of the framework is to provide to the designer a tool support him or her in the chose of the NoC architecture. The architectures currently supported by the framework are:

- a basic version of logic-based distributed routing (LBDR) [41] with no direct support for mixed criticality;

- a modification of LBDR to better support the mixed criticality;

- a basic version of logic-based distributed routing, to also consider an architecture able to support a non-minimal routing.

As low complexity is fundamental to have a certification potential, all the considered NoC architecture are intentionally chosen to be as simple as possible. Thus, the considered architectures do not feature virtual channels and are based on a single physical network.

The framework supports a technique, for each of the considered architectures, to allow their usage in the context of the mixed criticality. As the placement of the applications is fundamental when reservation-based techniques are used, the framework helps the designer to collect precious information during design space exploration. In particular, the framework configures the chosen architecture according to the placing and communication constrains of GS applications, eventually signaling the impossibility to meet such constrains. If the configuration is possible, it will be possible to collect some useful information (i.e., throughput and logical connectivity between nodes) about the leftover resources for BE applications.

#### **Summary: Functional Safety Contributions**

The main ideas and aspects of the contributions described in Section 1.2.2 can be represented by the following itemized list:

- COTS NoC-based MPSoC:

- software components implicit NoC contention: temporal isolation;

- purely software solution

- main idea:

- critical software component: temporal isolation (guaranteed service

GS):

- \* non-critical software component: no guarantees (best effort BE);

- \* traffic isolation established during application mapping phase;

- \* traffic isolation monitored by a dedicated RTOS module;

main requirement: deterministic and known routing being used by the NoC;

- avionic field;

- certification-friendly solution: as simple as possible;

- custom NoC-based MPSoC:

- software components implicit NoC contention: temporal isolation;

- set of NoC architectures and techniques to allow their usage in the context of mixed criticality

- main idea:

- \* critical software component: temporal isolation (guaranteed service GS);

- \* non-critical software component: no guarantees (best effort BE);

- hardware-implemented traffic isolation established at application mapping time;

- \* framework to perform a comparison of different NoC architectures;

- avionic field;

- certification-friendly solution: as simple as possible.

# 1.3 Reliability Analysis: Comparing Program Susceptibility to Soft Errors

A further contribution of this thesis focuses on the reliability of the MPSoC related to core-level. In detail, I present a technique to assess the software reliability at early stages of the system design cycle. The technique considers the issue of radiation induced transient hardware faults also known as soft errors. The technique is based on fault injection and only considers the software data structures (i.e., variables). The technique can be used when the final computing platform is not known yet, in fact only a limited knowledge of the latter is required.

Considering the MPSoC at core level, this thesis presents a technique to assess the software reliability at early stages of the system design cycle. In detail, this dissertation addressed the robustness against the radiation induced transient hardware faults also known as soft errors. The technique is based on fault injection and only considers the software data structures (i.e., variables). The technique can be used when the final computing platform is not known yet, in fact only a limited knowledge of the latter is required. Considering a candidate for final computing platform, such information can be gathered from its compiler and an execution time estimator with no need to actually execute the software on that computing platform.

#### 1.3.1 State-of-the-art

Evaluating the dependability characteristics of a compression program when no information about the target execution platform is available yet is a challenging task. Considering the early phases of the design process, only a high-level version of the algorithms (e.g., in C or C++) to be considered available, while the target executing platform has still to be decided.

At this stage, a possible approach for performing reliability analysis that could provide useful information about the robustness of the considered compression algorithms is based on executing them using a meaningful workload, injecting faults modeling the radiation effects and observing the resulting behavior.

From a technical point of view, such a kind of analysis typically adopts simulation-based fault injection [42], where bit flips are injected inside the data structures of the program [43–49]. In some cases, other representations of the compression program may also exist (e.g., a Matlab's Simulink model): in these cases, a preliminary analysis can be performed by executing fault injection campaigns on this model [50]. The formal technique [51, 52] can be used as an alternative to the fault injection simulation.

The main issue concerning the aforementioned is the lack of precision. Having no information about the hardware, the injected faults could never precisely model the radiation effects [53].

#### **1.3.2** Author's Contribution (Reliability Analysis)

As a further contribution of this thesis, I propose a solution to address the reliability issue of COTS MPSoC used for space and avionics systems. The proposed technique focusses on the node level of the MPSoC and considers the reliability of the software

components against radiation induced soft errors. The purpose of the proposed technique is to help the designer in the choice of most suitable (in terms of reliability) software component for a given system function, when more candidates for that function exist. The proposed technique is intended to be used in the early stages of design phase, when the target executing platform has not been chosen yet.

The rest of this section will first describe the contribution related to High-level technique for ranking candidate software susceptibility to soft errors (seesectionsec:introfocus-FI-contrib-ranking), then seesectionsec:intro-summary-contrib-reliability will provide a itemized summary of this contribution.

# High-level technique for ranking candidate software susceptibility to soft errors

The proposed technique allows to perform a ranking of a set of different software implementations of a given functionality. A typical situation, the proposed technique is intended to be used for, is when different algorithms or even paradigms exist to implement the required function (e.g., data compression function). Thus, the proposed solution is intended to help the designer in the choice of the most suitable (in terms of reliability) software implementation for a given system function, when more candidates for that function exist. The overall solution also provides some information to be used during an eventual hardening phase, as an extra feature (naturally implemented by the ranking process).

The proposed solution is aware that the main drawback of any high-level approach is the limited capability to capture the exact behavior of the hardware affected by radiation-induced soft errors [53]. Indeed, the aim of the proposed technique is to perform a ranking of a set of software components, while any usage to compute the quantitative reliability figures is discouraged. Thus, this technique benefits from the fact that a comparison requires a lower level of precision with respect to the quantitative reliability figures computation. However, main challenge of this technique is to achieve a sufficient precision to allow a meaningful comparison.

The proposed approach is evaluated by ranking a set of lossless compression programs, candidate for the data logging sub-system. To validate the proposed approach, the results of high-level fault injection have been compared with those gathered with register-level fault injection simulation. In detail, general-purpose

1.4 Outline 17

registers (GPRs) of a candidate executing platform have been considered. The injection of faults inside the memory has not been considered, as memories (both on chip and external) used in space applications, are typically protected by error detection/correction capabilities [54, 55], and can be considered as immune to radiation-induced soft errors. Despite the GPR-level injections do not provide precise reliability figures, I explain why it is reasonable to assume that their precision allows the comparison among candidate programs of a particular type (e.g., compression programs). In detail I analyze how the fault not covered by GPR-level fault injection will contribute mainly as common mode error.

#### **Summary: Reliability Analysis Contributions**

The main ideas and aspects of the contribution described in Section 1.3.2 can be represented by the following itemized list:

- reliability analysis:

- assessing software component robustness against radiation induced soft errors;

- ranking a set of software components implementing the same function;

- early stage design;

- almost hardware independent;

- program-variables-level fault injection simulation;

- main idea:

- hardware-specific effects obtained from low-level fault injection are mostly common-mode.

#### 1.4 Outline

This section gives an outline of this dissertation.

• Chapter 2 provides more background on the context of this dissertation. The issues related to the (NoC-based) MPSoC usage in the critical domain, already introduced in the current chapter, will be comprehensively covered. The

chapter will provide precise terminology and will define basic terms and metrics. The focus will be put mainly on the safety and reliability aspects.

• Chapter 3 describes the first contribution of this dissertation: a technique to solve one of functional safety issues related COTS (NoC-based) MPSoC usage in the context of mixed criticality. In detail, the technique addresses the temporal isolation issue related to implicit contention of the NoC interconnection. The approach is to reserve NoC resources and avoid their sharing. This is done by virtually partition the system and to enforce this partitioning by filtering faulty traffic (i.e., by blocking NoC usage that would break the partitioning). The traffic partitioning exploits the deterministic routing used by the NoC. Thus, the main requisite for the proposed solution is that the routing algorithm (used by the NoC) is deterministic and known (which is fairly common). The traffic filtering is implemented as purely software module to be inserted inside the RTOS. The overall solution is deliberately simple to exhibit a high certification potential. Furthermore, a solution to improve the overhead of the reservation approach is proposed.

The chapter will also further extend the analysis of the-stat-of-the-art landscape, allowing a better locate the proposed solution inside the latter.

- Chapter 4 describes the second contribution of this dissertation: a technique to solve one of functional safety issues related (NoC-based) custom MPSoC usage in the context of mixed criticality. In detail, the technique addresses the temporal isolation issue related to implicit contention of the NoC interconnection. The approach relies on privatization of NoC resources, thus sharing avoidance. QoSinNoC framework was developed to analyze a set of NoC architectures and techniques to allow their usage in the context of mixed criticality. The goal of the framework is to provide to the designer a tool to support him or her in the chose of the NoC architecture. The architectures currently supported by the framework are:

- a basic version of LBDR with no direct support for mixed criticality;

- a modification of LBDR to better support the mixed criticality;

- a basic version of routing table—based routing, to also consider an architecture able to support a non-minimal routing.

1.4 Outline **19**

As low complexity is fundamental for certification purposes, all the considered NoC architecture are intentionally chosen to be as simple as possible. Thus, the considered architectures do not feature virtual channels and are based on a single physical network.

The framework supports a technique, for each of the considered architectures, to allow their usage in the context of the mixed criticality. As the placement of the applications is fundamental when reservation-based techniques are used, the framework helps the designer to collect precious information during design space exploration. In particular, the framework configures the chosen architecture according to the placing and communication constrains of GS applications, eventually signaling the impossibility to meet such constrains. If the configuration is possible, it will be possible to collect some useful information (i.e., throughput and logical connectivity between nodes) about the leftover resources for BE applications.

The chapter will also further extend the analysis of the-stat-of-the-art landscape, allowing a better locate the proposed solution inside the latter.

• Chapter 5 describes the third contribution of this dissertation: a solution to address the reliability issue of COTS MPSoC used for space and avionics systems. The proposed technique focusses on the node level of the MPSoC and considers the reliability of the software components against radiation induced soft errors. The purpose of the proposed technique is to help the designer in the choice of most suitable (in terms of reliability) software component for a given system function, when more candidates for that function exist. The proposed technique is intended to be used in the early stages of design phase, when the target executing platform has not been chosen yet. The proposed technique performs a reliability comparison between a set of software components candidates, when more options exist for a given system function. This comparison is done at high level, considering very few information about the computing hardware platform and concerns the robustness against radiation-induced soft errors, especially single event upset errors. In detail, the proposed solution is based on the execution of the software component and injecting single bit-flip faults in the program variables during its execution. Finally, observing the effects of the injected faults on the program execution and on its results. In this way, we can perform a first level analysis of the fault 20 Introduction

masking and self-convergence capabilities of the code, as well as get some information about its intrinsic capabilities to detect errors.

The chapter will also further extend the analysis of the-stat-of-the-art landscape, allowing a better locate the proposed solution inside the latter.

• Chapter 6 concludes my dissertation. The contributions are summarized as well as the related current limitations. Finally, some suggestion for future research are presented.

## **Chapter 2**

## **Processor-based Critical Systems**

A critical system, as the name suggests, is system which proper functioning is strongly required. This chapter will define the basic terminology on the critical systems and the dependability of a system. This chapter will provide background on context of this dissertation, i.e., Multi-processor System-on-Chip (MPSoC) devices as well as the requirements and issues of a mixed-criticality system (MCS).

This chapter will first describe (Section 2.1) what is a Multi-processor System-on-Chip (MPSoC).

Then, in Section 2.2 it will be described the concept of dependability. In particular, it will be described how the dependability of a system can be defined and measured (i.e., dependability attributes), which are the threats to its dependability, and which are the means to cope with these threats.

Once the basic dependability concepts are defined, a critical system will be defined as well as the related requirements and issues will be analyzed (taking into account the avionics domain), respectively, in Section 2.3 and Section 2.4.

Finally, Section 2.5 will specifically target the multi-core processors in general and the MPSoC devices in particular.

## 2.1 Multi-processor System-on-Chip

The first integrated circuit (IC) was produced in 1969 and contains 1,200 transistors. These devices represented the main step of the third industrial revolution, known as

digital revolution, and marked the beginning of the Information (or Computer) Age. Since then, these devices followed the Moore's law in an ever-improving size, speed, and capacity.

However, in the early 2000s, general-purpose processors manufacturers were observing the single-core paradigm to hit several technological walls. To overcome these walls the multi-processor design paradigm was adopted [56]. In detail, these are power wall, memory wall, instruction-level parallelism wall and complexity wall. The power wall was hit by the single-core processor design around 2004. The trend of scaling down the gate size, reducing supply voltage and increasing the clock frequency became no longer feasible, mainly due to the heat dissipation issue [57]. The *memory wall* is provoked by the much slower memory performance growth, when compared to the performance growth [58]. The sophisticated multi-level cache hierarchy architectures became no longer sufficient to face the memory latency bottleneck. The instruction-level parallelism wall is the impossibility (or unfeasibility) to improve instruction-level parallelism extraction for singe-core paradigm [59]. The *complexity wall* is the issue related to the ever-growing architectural complexity to deal with the previously listed issues. This issue has a huge impact as the verification costs grows enormously with complexity growth. The multi-core paradigm overcomes the power wall by replacing the single fast-but-power-hungry core with a set of slower cores. These slower cores will cooperate providing much more computational power and also solving the heat generation issue (as the power consumption is linearly proportional to the clock frequency). For what it concerns the power wall, multi-processor paradigm faces this issue in two ways. First, as the frequency is lower than for single-core approach, the performance-latency gap becomes less evident. Second, the latency gap is compensated by the overall bandwidth of the system, which scales much better [60]. The instruction-level parallelism wall issue is solved by considering the task-level parallelism instead. This allows to move at parallel programming level, rather than complex hardware to (transparently) extract instruction-level parallelism from the instruction stream. Finally, multi-core approach overcomes the complexity wall by considering much simpler cores. Furthermore, a core must be designed once and replicated multiple times inside a chip, which further cuts the verification effort.

Alongside with the growing number of processing cores integrated on the same chip, also the on-chip peripherals number increases. This creates a system which is often referred to as system-on-chip (SoC). As the number of on-chip components

connected to the same bus-based interconnection was ever-growing, this interconnection infrastructure quickly became no longer suitable to sustain the meet intensive parallel communication requirements. To solve this communication bottleneck an off-chip networking approach was investigated. This led to the implementation of an on-chip switching network, called network-on-chip (NoC), to interconnect the IP modules in SoCs.

In the scope of this dissertation a *multi-processor SoC (MPSoC)* is referred to a SoC featured with NoC interconnection infrastructure. This term will be referred to a generic design which could be either homogeneous or heterogeneous for what it concerns its computing cores.

This section will fill first provide the NoC background both on its structure and its metrics. Finally, some examples of state-of-the-art MPSoC will be briefly described.

#### 2.1.1 Network-on-Chip: Structure and Design Space

As an MPSoC is characterized by a high number of on chip IPs, a salable interconnection is a must. NoC interconnection has been created to answer this scalability requirement, as the main idea behind the NoC is the adaptation of the network concept to the context of on-chip interconnection. Furthermore, a NoC allows a much larger number of solutions for what it concerns, not only routing and arbitration strategies, but also the organizations of the communication infrastructure as such. This provides to the designer a large design space and thus allows him/her to adopt a solution that better fit the project peculiarities.

The first classification of a NoC is made according to its topology. The ring and mesh topologies are the simplest ones, but also different types of torus are used (also for commercial products). A schematic view of a NoC with a two-dimensional (2D) mesh topology can be seen in Fig. 2.1. The figure also shows the path taken by a packet send by  $N_0$  towards  $N_5$ , assuming XY routing algorithm is used by the NoC. A detailed view of the same NoC can be seen in Fig. 2.2. It can be seen how nodes connected through the links forms a network. Each node of such network is formed by a *connected element* (CE) connected to a *router* through the dedicated *network interface* (NI). The nodes are connected to each other through the two mono-directional *communication links* (or *channels*). Thus, a NoC can be seen as composed of tree building blocks: link, router and NI. The structure of

the NoC is more complex than the one of the bus. This extra complexity does not only meet the scalability requirement but also allows to implement several different network communication protocols to better fit a specific set of requirements of a given application. A CE is not a part of the NoC; however, it will be briefly described as the only goal of the NoC interconnection is to implement the communication among CEs.

Fig. 2.1 A schematic view of a 3x3 (2D) mesh topology NoC;  $N_0$  to  $N_5$  packet path under XY routing algorithm.

#### Link

A communication link is made of a set of physical wires and connects two routers in the network as well as a router and a NI. Each link can be composed of one or more physical or logical channels, which are groups of wires connection two entities. Typically, a NoC link has two physical channels making a full-duplex connection between the routers, i.e., there are two uni-direction channels in opposite directions. The number of wires per channel, called channel bitwidth, is uniform throughout the network. A synchronization protocol between the  $N_{source}$  and  $N_{destination}$  must be considered as part of link implementation. Some implementation based on asynchronous links were also proposed to implement globally asynchronous locally synchronous (GALS) systems. However, normally synchronous links are used, implemented

Fig. 2.2 A detailed view of a 3x3 2D mesh topology NoC; R - router; NI - network interface; CE - connected element.

either by some dedicated wires to support the synchronization mechanism or through other approaches such as FIFOs. It comes natural for designers to implement fast, low-power and reliable wiring between the nodes of the NoC.

From the information point of view, a *packet* is composed of a set of *flow control units* or *flits*. A flit represents an atomic unit of packet. On the other hand, the minimum amount of data that is transmitted in one link transaction is called *phit*. However, usually a flit is exactly equal to a phit, i.e., (once a transmission is initiated) a flit is transmitted at each NoC clock cycle.

#### **Connected Element**

In this dissertation I will call *connected element* (CE) whatever IP core connected (through the NI) to a router of the NoC. Thus, in the considered NoC model, a CE can be either a passive slave (e.g., memory) or an active element (e.g., processor). Considering the MPSoC-level scope, each CE sees other CEs as global resources connected through the NoC interconnection. Moreover, a CE can also have local

resources connected to the local bus. Each node of the NoC (i.e., the related CE) is considered as a remote resource and mapped to a memory map as any local resources (if any). Local resources are accessed as usual through the local bus, whereas remote resources are mapped to the driver in charge of instruct the NI in order to reach the global resources. Thus, the idea is to make NoC transparent to the CE.

#### **Network Interface**

The NI (also called as network adapter) is a peripheral on the local bus of the CE it is connected to. It receives requests from the local CE according to the protocol defined on the local bus. The CE can then wait for a response (bus-transaction communication model) or it can continue its computations, pending an interrupt that signals that requested data is available at a predefined location on a local memory (DMA communication model).

The NI performs the following tasks (although some of these tasks can be partially performed by a software module acting as the NI peripheral driver):