## POLITECNICO DI TORINO Repository ISTITUZIONALE

### Front-End Integrated Circuits For Readout of Large Area SiPMs at cryogenic temperature

Original

Front-End Integrated Circuits For Readout of Large Area SiPMs at cryogenic temperature / MARTINEZ ROJAS, ALEJANDRO DAVID. - (2019). (Intervento presentato al convegno 2019 8th International Conference on Modern Circuits and Systems Technologies (MOCAST) tenutosi a Greece).

Availability: This version is available at: 11583/2751059 since: 2020-08-26T15:40:57Z

Publisher: IEEE

Published DOI:

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# Front-End Integrated Circuits For Readout of Large Area SiPMs at cryogenic temperature

Alejandro D. Martinez R.

Department of Electronics and Telecommunications, Politecnico di Torino Istituto Nazionale di Fisica Nucleare, Sez. Torino Turin, Italy alejandro.martinez@polito.it

Abstract—This work describes the architecture and transistorlevel design of CMOS front-end amplifiers for the readout of large area SiPMs at LAr temperature (87K). Two circuit topologies, based on trans-impedance and common-gate input stages, are discussed and compared. Both circuits were designed using a standard CMOS 110nm technology, and the simulation results obtained with the foundry PDK are presented. The circuits use a power rail of +1.25 V and -1.25 V, and a power budget below 100 mW, for a total gain of 58 dB. The target sensor is a  $24cm^2$  SiPM tile developed in the framework of the Darkside Collaboration. Post-layout simulations with a cryogenic SiPM electrical model indicate that a signal-to-noise ratio above 8 and a jitter better than 15 ns should be achieved for a single photoelectron.

*Index Terms*—Photomultipliers, Hot carriers, Cryogenic electronics, Operational amplifiers

#### I. INTRODUCTION

Liquid argon (LAr) time projection chamber (TPC) technology will be used on future experiments for neutrino and direct dark matter detection [1] [2]. The high photodetection efficiency, robustness and the low cost of state-of-the-art silicon photomultipliers (SiPMs) has created wide interest on the possibility to use these sensors for the instrumentation of such frontier detectors. Extensive R&D on the cryogenic performance of silicon sensors allowed for the development of near ultra-violet SiPM technology optimised for operation at LAr temperature [3]. While typical SiPM sizes are below 10 mm2, LAr TPC detectors use large areas of SiPMs connected together in an effort to minimise the total number of readout channels. This constraint is imposed not only by the number of feedthroughs from the cryostat, but because the requirement for low radioactive background in experiments looking for rare events imply the minimisation of the total mass of photodetectors, associated electronics and cabling.

This work, developed in the framework of the Darkside Collaboration [4], describes the design of two alternative frontend amplifier topologies for the readout of large areas of SiPMs at LAr boiling temperature (87 K) using a standard CMOS 110nm technology. The target sensor is a 24 cm<sup>2</sup> SiPM tile developed for the Darkside-20K TPC photodetector module. A 2-series 3-parallel grouping configuration is used to decrease the total sensor capacitance, estimated 7 nF/cm<sup>2</sup>, and thereby the tile is divided into 4 quadrants of 6 cm<sup>2</sup> each, for a capacitance of 10 nF per quadrant. The proposed amplifiers read independently each one of the 4 SiPM channels and sum together the total signal, providing a single-ended output voltage signal for digitisation with warm electronics.

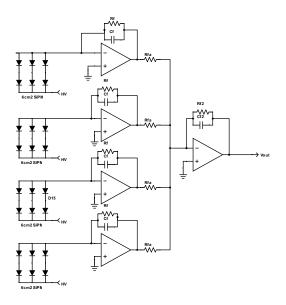

A first design uses a trans-impedance configuration based on the work proposed in [5]. The input stage is based on a foldedcascode amplifier [6], providing a large gain and dynamic range with a large unity-gain frequency [7]. The second stage is configured as a voltage amplifier, and sums the signal from the 4 input branches.

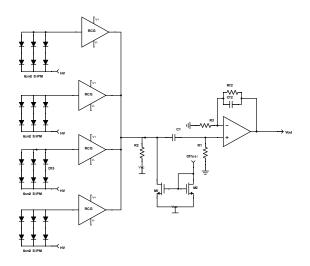

A second design, based on a regulated common-gate configuration, uses the input stage as a current conveyor in order to decouple the effect of the large detector capacitance from the transfer function [8] [9]. A second stage, based on a foldedcascode amplifier, amplifies and sums the signal from the 4 branches.

A Spice model was developed, based on extracted characterisation parameters, for simulations at 300K and 77K [13]. The electrical characterisation of the CMOS prototypes will be performed at 77K using Liquid Nitrogen.

#### **II. DESIGN AND IMPLEMENTATION**

This paper describes the transistor-level design and simulations for both the Trans-impedance input stage amplifier (TIA) and that based on a regulated common-gate input stage (RCG).

#### A. TIA amplifier

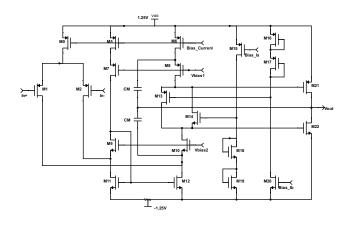

The transistor-level design of the folded-cascode operational amplifier is shown in Fig. 1. The circuit uses a PMOS input stage with an NMOS cascode, a typical choice for the minimisation of the flicker noise [12]. The input transistors (M1, M2) operate in weak inversion (Eq. (1)) and with a transconductance of 80 mS, using a bias current below 1 mA.

$$\frac{W}{L} = \frac{Id}{2n * Cox * \mu c * \Phi t^2 * e^{\frac{Vgs - Vth}{n * \Phi t}}}$$

Weak Inversion (1)

The circuit uses a class AB amplifier circuit on the output of cascode stage, which provides an increment in the total gain (i 40dB). Additionally, a Miller compensation capacitor is used in order to avoid instability related to the second pole and right-hand zero (RHZ). The Miller capacitors ( $C_m$ ) together

Fig. 1. Transistor-level circuit of Folded Cascode.

with the trans-conductance of M21 and M22 compose the new second pole, which keeps the circuit in a stable area, consequently limiting the total bandwidth.

Fig. 2. Folded Cascode Front-End for readout of large area sensor (i.e  $24 cm^2$  SiPM.

In order to minimise the effect of hot carriers, which would otherwise have an impact on the reliability of the device, we choose to use a minimum channel length of 4 times the minimum length (110nm). This technique reduces the internal electric field of the MOSFET and increases the transistor lifetime [11].

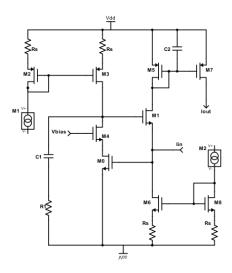

#### B. RGC

The use of a common-gate input allows to use an input resistance that is inversely proportional to the trans-conductance of M1. The use of a local feedback further reduces the input impedance by a factor of A. Figure 3 illustrates the transistorlevel design of a regulated common-gate (or regulated gate cascode) circuit using a cascoded common-source amplifier, a technique that is often called  $g_m$ -boosting.

Fig. 3. Transistor-level circuit of Regulated Common Gate(RCG).

In this configuration, the main contributor to the total output noise voltage of the circuit is the common-source amplifier NMOS M0. The transistor M4, in series with M0, reduces the drain-source voltage of M0 for an increased lifetime of the device at cryogenic operation. Therefore, this transistor was designed with a large aspect-ratio (20mm/800nm) increase its trans-conductance to 120 mS, which minimises its thermal noise.

The four RCG input stages are connected to the adder circuit, as shown in Fig. 4.

#### **III. SIMULATION RESULTS**

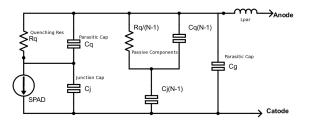

The designs were simulated using standard Spice models provided by the foundry PDK (Process Design Kit). The mathematical extrapolation of the BSIM models allows to have an approximate response of the MOSFET at cryogenic temperature, since semiconductor foundries do not provide characterisation qualified models for temperature corners below -40 C. To perform the simulations, a  $1cm^2$  SiPM electrical model with an output capacitance around 7 nF and a quenching resistance of 6M $\Omega$  at 77K [10] is used, as shown in Fig. 5. The SiPM model is connected in series and parallel to obtain  $6cm^2$ , as shown in Fig. 4.

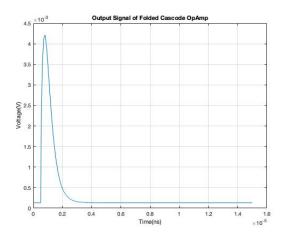

The output signal of the TIA circuit for a single photoelectron (PE) impinging the SiPM is shown in Fig. 6.

A summary of electrical simulation of the post-layout netlist for both amplifier topologies is shown in Table I. The comparison is done in terms of trans-impedance gain, total r.m.s. output noise voltage, peaking time, power, signal-tonoise ratio (SNR) and jitter for 1 PE, considering a timing

Fig. 4. RCG Front-End for readout of large area sensor (i.e 24cm<sup>2</sup> SiPM.

Fig. 5. SiPM electrical model with the interconnection inductance

Fig. 6. Output voltage signal of TIA for a single PE.

TABLE I

SIMULATED PARAMETERS OF RCG AND TIA CIRCUITS

| Parameters         | FE Topology |     |

|--------------------|-------------|-----|

|                    | RCG         | TIA |

| Gain (dB V/I)      | 74          | 58  |

| RMS noise (mV)     | 2.5         | 0.5 |

| SNR                | 10.1        | 8.8 |

| Jitter (ns)        | 10.9        | 7.2 |

| Peaking Time (ns)  | 700         | 250 |

| Power (mW)         | 82          | 95  |

| Dynamic Range (pe) | 40          | 75  |

measurement derived from a leading-edge discriminator at the output of the amplifier. The dynamic range, which is a function of the raill-to-rail voltage used (2.5V), is normalised to the signal produced by one photoelectron.

The higher dynamic range of the TIA in respect to the RGC circuit will not be used for comparison, since this is inevitably a function of the total gain. However, the seemingly worst performance of the RGC in terms of noise and, consequently, jitter, are caused by an excessive series resistance of the metal interconnects at the gate of the input transistor and the larger gain which amplifiers the RMS noise from the input. In schematic level simulations, these figures-of-merit are approximately equivalent.

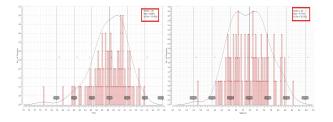

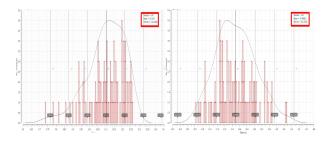

A Montecarlo simulation was performed to estimate the stability of the circuit for stochastic variations of the active and passive devices. Figures 7 and 8 show the behaviour of the timing jitter and SNR at 77K for both circuits. The TIA provides a mean SNR = 8.8 (std. dev. = 0.3) and a mean jitter = 7.2 ns (std. dev. = 530 ps), while the RGC shows a mean SNR = 10.1 (std. dev. = 0.1) and a mean jitter = 10.9 ns (std. dev. = 520 ps).

Fig. 7. Montecarlo simulation of TIA, SNR(left) and Jitter(right).

#### IV. CONCLUSION

We present the design and simulation results of two frontend amplifiers for the readout of large area SiPMs at LAr temperature. Both circuits were designed using a standard CMOS 110nm technology and fit in a test-chip of  $\approx 2 mm^2$ . The prototype was sent to fabrication and will be tested with external charge injectors and a 24 cm<sup>2</sup> tile in a liquid nitrogen bath. Post-layout simulation results show that both circuits should achieve a SNR above 8 and a jitter better than 15 ns for the signal produced by a single photo-electron. The design

Fig. 8. Montecarlo simulation of RGC, SNR(left) and Jitter(right).

of the RGC circuit, which uses rather large W/L on the input transistor, suffers from a degradation of the noise caused by excessive resistive parasitics at the input net.

#### REFERENCES

- C. E. Aalseth, F. Acerbi, et al., "DarkSide 20K: A Yellow book technical proporsal/pre-technical design report" INFN, 2016

- [2] J. Stewart, "The ProtoDUNE Single-Phase Detector", IEEE Nuclear Science Symposium and Medical Imaging Conference, 2017

- [3] F. Acerbi et al., "Cryogenic Characterization of FBK HD Near-UV Sensitive SiPMs", IEEE Transactions on Electron Devices, Vol. 64, Iss. 2, 2017

- [4] C. Aalseth et al., "DarkSide-20k: A 20 tonne two-phase LAr TPC for direct dark matter detection at LNGS", Eur.Phys.J.Plus 133 (2018) 131

- [5] M. D'Incecco et al., "Development of electronics for a single-channel, 24 cm2, SiPM-based, cryogenic photodetector", IEEE Trans.Nucl.Sci. 65 (2017) no.1, 591-596

- [6] D. K. Shedge, P. W. Wani , et al., "CMOS Telescopic Cascode Operational Amplifier", International Conference on Green Computing, Communication and Conservation of Energy (ICGCE), December 2013

- [7] S. Zhang, "A 90-dB DC Gain High-Speed Nested Gain-Boosted Folded-Cascode Opamp", 11th Conference on Ph.D. Research in Microelectronics and Electronics, 2015

- [8] G.Piccinni, G. Avitabile, et al., "A Novel Design Optimization Framework for Regulated Cascode Transimpedance Amplifiers," European Conference on Circuit Theory and Design, 2017

- [9] M. Rolo et al., "A low-noise CMOS front-end for TOF-PET", Journal of Instrumentation, Vol. 6, 2011

- [10] M. D'Incecco, et al., "Development of a very low-noise cryogenic preamplifier for large-area SiPM devices, Nov,2017.

- [11] J. Hoff, G. Deptuch, et al., "Cryogenic Lifetime Studies of 130nm and 65nm nMOS Transistors for High-Energy Physics Experiments", IEEE Transactions on Nuclear Science, 62(3), pp.1255-1261, 2015.

- [12] A. Rivetti, "CMOS Front end electronics for radiation sensors,", CRC press, 2015.

- [13] M. Biroth, P. Achenbach, et al, Modelling and Characterization of SiPM Parameters at Temperatures between 95K and 300K," IEEE Transaction on Nuclear Science, pp.1-1, Oct, 2017.