## POLITECNICO DI TORINO Repository ISTITUZIONALE

### A 0.3-1.2V Schottky-Based CMOS ZTC Voltage Reference

Original

A 0.3-1.2V Schottky-Based CMOS ZTC Voltage Reference / Pedro, Toledo; Cordova, David; Klimach, Hamilton; Bampi, Sergio; Crovetti, PAOLO STEFANO. - In: IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS. II, EXPRESS BRIEFS. - ISSN 1549-7747. - STAMPA. - (2019). [10.1109/TCSII.2019.2932281]

Availability: This version is available at: 11583/2745652 since: 2019-10-08T11:50:28Z

Publisher: IEEE

Published DOI:10.1109/TCSII.2019.2932281

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright IEEE postprint/Author's Accepted Manuscript

©2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS

# A 0.3-1.2V Schottky-Based CMOS ZTC Voltage Reference

Pedro Toledo, David Cordova, Student Member, IEEE, Hamilton Klimach, Member, IEEE, Sergio Bampi, Senior Member, IEEE and Paolo Crovetti, Member, IEEE

Abstract-A voltage reference based on MOSFETs operated under Zero Temperature Coefficient (ZTC) bias is proposed. The circuit operates in a power supply voltage range from 0.3V up to 1.2V and outputs three different reference voltages using Standard- $V_T$  (SVT), Low- $V_T$  (LVT), and Zero- $V_T$  (ZVT) MOS transistors biased near their ZTC point by a single PTAT current reference. Measurements on 15 circuit samples fabricated in a standard 0.13-µm CMOS process show a worst-case normalized standard deviation ( $\sigma/\mu$ ) of 3% (SVT), 5.1% (LVT) and 10.8% (ZVT) respectively with a 75% of confidence level. At the nominal supply voltage of 0.45 V, the measured effective temperature coefficients (TC<sub>eff</sub>) range from 140 to 200 ppm/°C over the full commercial temperature range. At room temperature (25°C), line sensitivity in the ZVT VR is just 1.3%/100mV, over the whole supply range. The proposed reference draws around 5  $\mu$ W and occupies 0.014 mm<sup>2</sup> of silicon area.

*Index Terms*—low voltage, voltage reference, Schottky diode, zero temperature coefficient (ZTC) condition.

#### I. INTRODUCTION

IN recent years, MOSFET-only voltage references at sub-1V supply have been extensively studied [1] to address the limits of nanoscale technologies and the requirements of low power applications. Most MOSFET-only voltage references have been obtained taking advantage of the thermal drift of the difference in the threshold voltages ( $V_T$ ) either of two NMOS devices [2–4] or of an NMOS and of a PMOS device [5], or exploiting the  $V_T$  dependence on the transistors geometry [6], [7], or even biasing the MOSFET at its Zero Temperature Coefficient (ZTC) operating point [8–11].

Aiming to reconfigurability, which is highly demanded in present-day energy constrained applications [12], ZTC-based references are particularly attractive since, unlike in other solutions, where thermal compensation is achieved at a single, fixed, process-dependent voltage  $V_{REF}$ , they can be more easily re-configured to operate at different output voltages without extra circuitry and power overhead. Moreover, ZTC-based references are appealing since a ZTC bias point can be found in UTBB SOI, FinFET devices and advanced MOSFETs technologies as well [13], indicating itself as good strategy for future reference designs.

In this paper, an ZTC-based integrated reference exploiting the approach outlined in [14] is demonstrated on silicon for the first time. Based on the ZTC theoretical modeling aspects reviewed herein, the reconfigurability of the final desired voltage reference by changing the PTAT current generator under the same device is also demonstrated. The measured power consumption of the proposed circuit ( $5\mu$ W) is in the average of other ZTC-based solutions such as [15], [16], and it could be pushed down to the hundred nanowatt range by the

1

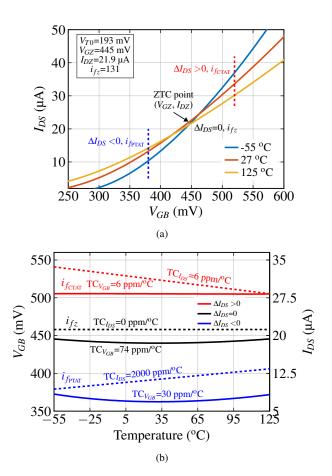

Fig. 1. (a) ZTC condition for a standard NMOS transistor in a 0.13- $\mu$ m CMOS process. (b) In solid line,  $V_{GB}(T, \Delta I_{DS} = I_{DS} - I_{DZ})$  with the right amount of thermal drift  $TC_{I_{DS}}$  applied into the MOS transistor. In dashed line, the bias currents with the needed thermal drift  $TC_{I_{DS}}$ .

approach proposed in [17] at the cost of increased area (using very low aspect ratio (W/L), i.e., very large transistor length).

#### **II. MOSFET ZTC CONDITION REVIEW**

In a MOSFET, the ZTC condition for the drain current follows from the mutual cancellation of the mobility and threshold voltage dependencies on temperature, which occurs at a particular MOSFET gate-to-bulk voltage bias. The bestknown simplified model for this gate-to-bulk voltage at ZTC condition, which was initially proposed by [18] and then deeply explored in [16] and [10], is given by

$$V_{GZ} = V_{T0}(T_0) + nV_{SB} - \alpha_{V_{T0}}T_0 \tag{1}$$

$$J_{DZ} = \frac{I_{DZ}}{(W/L)} = \frac{\mu_n(T_0)T_0^2 C'_{ox}}{2n} \alpha_{V_{T0}}^2$$

(2)

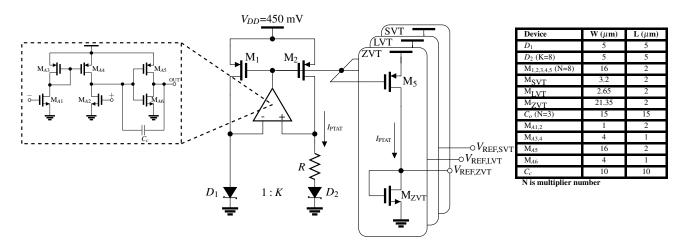

Fig. 2. Proposed 0.45-V CMOS voltage reference schematic circuit.

where  $T_0$  is the room temperature,  $V_{T0}(T_0)$  is the threshold voltage at room temperature, *n* is the slope factor,  $V_{SB}$  is the source-bulk voltage,  $\alpha_{V_{T0}}$  is the thermal coefficient of the threshold voltage (stressing that  $V_T$  decreases with *T*),  $\mu_n(T_0)$ is the low field mobility at room temperature,  $C'_{ox}$  is the oxide capacitance per unit of area and  $\frac{W}{L}$  is the transistor aspect ratio. The  $J_{DZ}$  can be defined as ZTC normalized drain-current and one can readily conclude that  $V_{GZ}$  and  $J_{DZ}$  are only dependent on device fabrication processes.

Fig. 1 (a) shows the drain current of a long-channel NMOS transistor in saturation as a function of the gate-bulk voltage  $(V_{GB})$ , simulated over temperatures ranging from -55 to 155 °C in standard 0.13- $\mu$ m CMOS. The ZTC operation point can be seen to be around  $V_{GB} \approx 445$  mV for a transistor with  $V_T$  = 193 mV and  $L = 1 \mu$ m. From the same Fig. 1 (a), looking at the vertical dotted lines, it can be observed that if the bias point is not exactly at ZTC, the  $V_{GB}$  or  $I_D$  has a nearly linear PTAT or CTAT behavior depending on its value, which can be expressed by series expansion around  $V_{GZ}$  as:

$$V_{GB}(T) = V_{GZ} - \left(\frac{\beta_z \Delta I_D}{I_{SQ} \frac{W}{L}}\right) T$$

(3)

where  $\Delta I_D = I_D - I_{DZ}$  indicates how far from ZTC operating point the transistor is biased and  $\beta_z$  is defined as the ZTC slope [10], [18].

To eliminate the first order temperature drift close to the ZTC, a drain current  $I_D$  with a suitable temperature coefficient  $TC_{PTAT}$  should be applied, i.e., it is needed to find out the forward inversion level  $(i_{f0})$  in which, once  $TC_{PTAT}$  is applied, the  $V_{GB}$  associated to this  $i_{f0}$  becomes less sensitive to temperature variations. As detailed in [10], this is equivalent, indeed, to change the reference voltage  $V_{REF}$  achieving ZTC condition, as highlighted in (4) and (5), or in other words, to re-configure the same circuit so that to obtain a different, first-order temperature independent, reference voltage  $V_{REF}$ .

$$V_{REF} = V_{T0} + n\phi_{t0} \left[ \sqrt{1 + i_{f0}} - 2 + \log \left( \sqrt{1 + i_{f0}} - 1 \right) \right] \quad (4)$$

$$\frac{|\alpha_{V_{T0}}|q}{nk} = \left[\frac{TC_{PTAT}T_0}{2} - \left(\frac{\alpha_{\mu} + 2}{2}\right)\right] \left(\frac{i_{f0}}{\sqrt{1 + i_{f0}} + 1}\right) \quad (5)$$

$$+ \left[\sqrt{1 + i_{f0}} - 2 + \log\left(\sqrt{1 + i_{f0}} - 1\right)\right]$$

where  $\phi_{t0}$  is the thermal voltage at room temperature, k is the Boltzmann constant, q is the elementary electric charge, and  $i_{f0}$  is defined as the ZTC forward inversion level for an associated  $TC_{PTAT}$ . Note that  $i_{f0}$  is related to  $i_{fPTAT}$  and  $i_{fCTAT}$  in Fig. 1(b) and  $V_{REF}$  can be set up based on both parameters,  $V_{T0}$  and  $TC_{PTAT}$ .

#### III. VOLTAGE REFERENCE ANALYSIS AND DESIGN

The design of a 0.3-1.2V voltage reference based on the approach revised in the previous Section and featuring a Schottky-diode based PTAT current reference for low voltage operation is proposed in the following subsections.

#### A. Schottky-diode based PTAT Current Reference

To achieve low-voltage operation, a low power PTAT current is generated using the forward voltage difference of two Schottky diodes operated under different current densities by a current mirror. Fig. 2 shows the schematic diagram of the PTAT current reference where a two-stage operational amplifier topology was chosen to increase the loop gain so that to enhance power supply rejection (PSR). The PTAT current analysis is given in [19], and leads to the following well known expression of the thermal drift:

$I_{PTAT} = I_0 (1 + TC_{PTAT} (T - T_0))$ (6)

where

$$I_{0} = \frac{n\phi_{t0}\log(K)}{R_{0}} \therefore TC_{PTAT} = \frac{1}{T_{0}\left[1 + \alpha_{1}(T - T_{0})\right]^{2}}$$

(7)

$R_0$  is poly resistance at room temperature,  $\alpha_1$  is its first order temperature dependence and *K* is ratio area between  $D_2$  and  $D_1$ .

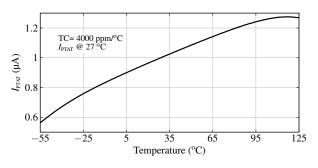

Fig. 3. Simulated PTAT current source temperature dependence.

TABLE I SIMULATED PERFORMANCE OF THE VOLTAGE REFERENCE

| Process                               |      | 0.13-µm*                   |       |  |  |  |

|---------------------------------------|------|----------------------------|-------|--|--|--|

| Temp. Rage (°C)                       | -    | $-55 \leftrightarrow 125$  |       |  |  |  |

| $V_{DD}$ (V)                          | (    | $0.45 \leftrightarrow 1.2$ |       |  |  |  |

| Transistor Type                       | SVT  | LVT                        | ZVT   |  |  |  |

| $\overline{V_{REF}}$ † (mV)           | 312  | 237                        | 51    |  |  |  |

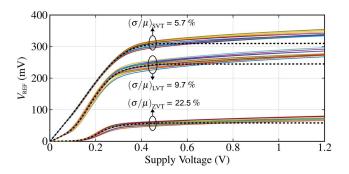

| $\overline{V_{REF}}$ $\mu/\sigma$ (%) | 5.7  | 9.7                        | 22.5  |  |  |  |

| LS (V/100mV)                          | 3.55 | 3.9                        | 1.5   |  |  |  |

| $TC_{eff}$ <sup>†</sup> (ppm/°C)      | 214  | 372                        | 953   |  |  |  |

| PSR @ DC † (dB)                       | -28  | -27.5                      | -36.8 |  |  |  |

| Power <sup>⊕</sup> (µW)               |      | 5.9                        |       |  |  |  |

$\oplus$  @( 27 °c,  $V_{DD,MIN}$ ); \* Simulation results; † Process and Mismatch (1000 runs)

#### B. Circuit Analysis and Design

The complete schematic of the proposed voltage reference is also shown in Fig. 2, and includes a low supply PTAT current reference biasing three diode-connected NMOS transistors operated close to their ZTC bias points. Using this topology it is possible to generate the needed amount of current temperature dependence  $TC_{PTAT}$  in order to compensate the first order temperature drift as described by (3) and discussed at Section II. The PTAT current reference by counterbalancing the CTAT behavior of the ZTC vicinity results a first order temperature compensation and provides a voltage reference given by (4) and (5).

The reference voltages are obtained directly from the gatebulk voltages ( $V_{GS}=V_{REF}$ ) of M<sub>SVT</sub>, M<sub>LVT</sub> and M<sub>ZVT</sub>. Based on (4)-(6), i.e., after generated the bias current with a defined  $TC_{PTAT}$  and found out the  $i_{f0}$ , each diode-connected transistor in Fig. 2 can be properly designed and their aspect ratio can be obtained by the procedure reported in [14]. In particular, transistor aspect ratio ( $\frac{W}{L}$ ) can be expressed as a function of its inversion level  $i_f$  [20] in (8) as:

$$\left(\frac{W}{L}\right) = I_D(T_0) \left(\mu_n(T_0)C'_{ox}n\frac{\phi_{t0}^2}{2}i_{f0}\right)^{-1}$$

(8)

which can be simplified as

$$\left(\frac{W}{L}\right) = \frac{2nI_0}{C_{ox}} \left(\frac{TC_{PTAT}}{2|\alpha_{V_{T0}}|} - \frac{\alpha_{\mu}}{T_0}\right)^2 \tag{9}$$

in strong inversion.

#### C. Simulation Results

Using a 0.45 V supply voltage, the voltage reference is simulated under the temperature range from -55 to 125  $^{\circ}$ C

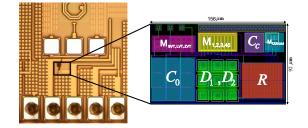

Fig. 4. Micrograph of the proposed 0.45 V voltage reference.

Fig. 5. Supply voltage dependence of 15 measured samples (solid), and typical voltage reference (dashed).

in order to predict the following performance parameters: PTAT current ( $I_{PTAT}$ ) and reference voltages ( $V_{REF}$ ), effective temperature coefficients (10),

$$TC_{eff} = \frac{V_{REF_{max}} - V_{REF_{min}}}{(T_{max} - T_{min})V_{REF(T_0)}}$$

(10)

line sensitivity (11),

$$LS = \frac{V_{REF(V_{DD}=1.8V)} - V_{REF(V_{DD}=0.45V)}}{(1.8V - 0.45V)V_{REF(V_{DD}=0.45V)}}$$

(11)

power supply rejection (PSR) and power consumption. The same expressions are used in section IV. Fig. 3 shows the PTAT current reference temperature dependence, which was designed for an 1  $\mu$ A nominal value at 27 °C and a temperature coefficient *TC* of 4000 ppm/°C. As can be noted, the PTAT current temperature dependence is not linearly constant for entire temperature range, and decreases at high temperatures, specially above 90 °C. The proposed circuits simulated results are summarized in Table I which will be compared against its measured performances. Each performance metric presented in Table I represents the median value of 1000 Monte Carlo runs.

#### **IV. MEASUREMENTS RESULTS**

The proposed circuit was designed and fabricated in a standard 0.13- $\mu$ m CMOS process. Fig. 4 shows the chip photo and its layout, which occupies a total silicon area of 0.014 mm<sup>2</sup>. Measurements were performed using a Keysight 4156C Semiconductor Parameter Analyzer for DC sweep, and a Tenney Jr. thermal chamber for temperature control. A total of 15 chips were packaged and measured. Their supply voltage dependence at room temperature is shown in Fig. 5 and proves to be compatible with simulated normalized standard deviation

4

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS

#### TABLE II

PERFORMANCE COMPARISON BETWEEN THE PROPOSED CIRCUIT AND MICROPOWER SUB-1 V STATE-OF-THE-ART VOLTAGE REFERENCES

| Parameter                               | This Work |       |       | st                 |                    |         |         |           | T         |          |         |

|-----------------------------------------|-----------|-------|-------|--------------------|--------------------|---------|---------|-----------|-----------|----------|---------|

|                                         | SVT       | LVT   | ZVT   | [21] <sup>st</sup> | [22] <sup>st</sup> | [23]    | [24]    | [25]      | [26]      | [27]     | [28]    |

| Process (µm)                            | 0.13      |       |       | 0.09               | 0.5                | 0.032   | 0.6     | 0.5       | 0.18      | 0.4      | SIMOX   |

| Temp. Rage (°C)                         | 0 - 85    |       |       | 5 - 100            | 5 - 70             | 0 - 125 | 0 - 100 | -40 - 125 | -40 - 140 | 27 - 125 | 20 - 80 |

| $V_{DD}$ (V)                            | 0.3-1.2   |       |       | 0.5                | 1.2                | 0.9     | 0.98    | 0.95      | 0.85      | 0.84     | 0.6     |

| $V_{\text{REF}}$ (mV)                   | 306.8     | 241.8 | 56.9  | 251                | 400                | 545     | 603     | 628       | 500       | 518      | 530     |

| LS (%/V)                                | 13        | 18    | 31.1  | 3                  | 1.4                | -       | 3.6     | -         | 4.4       | 0.1      | -       |

| TC (ppm/°C)                             | 81.5      | 24.2  | 114   | 263                | 107                | 962     | 15      | 17        | 33        | 116      | 37.7    |

| PSR @ 100 Hz (dB)                       | -29       | -28.3 | -34.7 | -                  | -                  | -       | -44     | -         | -         | -        | -       |

| Power (µW)                              | 4.12      |       |       | 450                | 59.4               | 12.6    | 17.6    | 10        | 9         | 4.6      | 100     |

| Area (mm <sup>2</sup> )                 | 0.014     |       |       | 0.02               | N/A                | 0.016   | 0.24    | 1.09      | -         | 0.1      | 0.06    |

| FoM ( $^{\circ}C^{3}/W \times mm^{2}$ ) | 3.87      | 6.34  | 3.88  | 0.0038             | -                  | 0.080   | 0.158   | 0.147     | -         | 0.18     | 0.016   |

<sup>st</sup> Schottky-diode-based <sup> $\oplus$ </sup> @( 27 °C V<sub>DD</sub> = 0.45V),<sup>‡</sup> @(27 °C, V<sub>DD</sub> = 0.45V to 1.2V) <sup>†</sup> @(V<sub>DD</sub> = 0.45V)

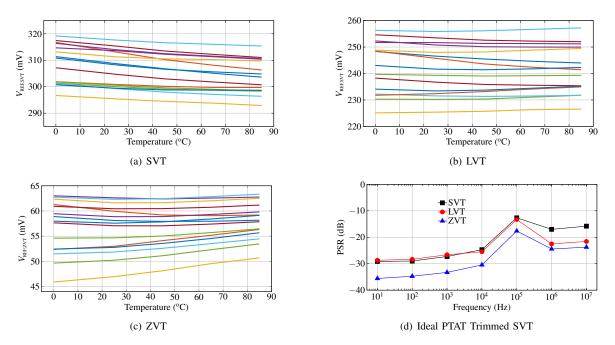

Fig. 6. Measured temperature dependence proposed voltage references @  $V_{DD} = 0.45$  V of untrimmed (a) SVT, (b) LVT and (c) ZVT. (d) Measured PSR @  $V_{DD} = 1.2$  V.

$(\sigma/\mu)$  of the reference voltage estimated from 1000 Monte Carlo simulations.

Fig. 6 shows the measured temperature dependence of the three outputs of the proposed voltage reference. To delivery a reasonable estimation of the circuit yield, the statistical benchmarking proposed in [29] is adopted here. Roughly speaking, [29] suggests to include confidence level and interval errors whenever experimental characterization over a limited number of samples is performed. Since only 15 measured samples are considered here, a 75% confidence level is considered in postmeasurement statistical analysis. Based on this approach, an output reference voltage (SVT, LVT, ZVT), with a mean value in the interval of  $\mu_{SVT} = (304.6, 309.0)$  mV and a standard deviation for different samples in the same batch in the interval  $\sigma_{SVT} = [5.827, 9.101] \text{ mV}, \ \mu_{LVT} = [238.91, 244.75] \text{ mV}$  and  $\sigma_{LVT} = [7.845, 12.25] \text{ mV}, \mu_{LVT} = [238.9, 244.7] \text{ mV} \text{ and } \sigma_{LVT}$ = [7.845, 12.25] mV,  $\mu_{ZVT}$  = [55.51, 58.37] mV and  $\sigma_{ZVT}$  = [3.83, 5.991] mV, respectively, have been reported.

The power supply voltage rejection (PSR) is shown in Fig 6 (d). Even though presenting a relatively high LS, around  $11.9 \sim 33.6 \%/V$ , it could be significantly reduced by regulating its  $V_{DD}$  using a sub-0.5 V supply voltage reference.

In Tab.II, the performance of the proposed circuit are compared with other pn- and Schottky-diode-based sub-1 V voltage references in the literature. It is worth being observed that the mean and standard deviation of the other references in the table have been calculated in the conventional way. The LS and TC values in Tab.II are the central value of mean interval; similar procedure done for  $V_{REF}$ . While the minimum supply voltage for the LVT version is comparable to [21], the ZVT output presented here starts to operate above 0.3V supply. The proposed topology was designed to optimize power consumption, consuming more than  $10 \times$  less power than previous Schottky-diode-based implementations (At 0.45V  $V_{DD}$ , measured chips consume in average between 3.8  $\mu$ W at 0°C and 7  $\mu$ W at 85°C). The LVT output shows a smaller *TC*. In addition, our reference circuit occupies the lower silicon area. The overall performance of our voltage reference can be evaluated using a Figure of Merit (FoM) [30]:

$$FoM = \frac{(T_{MAX} - T_{MIN})^2}{TC \times Power \times Area} \times \frac{1}{10^{15}}$$

(12)

and the proposed circuit presents one of the best FoM performance among others Schottky-diode based, low voltage references considered for comparison.

#### V. CONCLUSION

A voltage reference circuit operated under the MOSFET ZTC condition at 0.45 V has been proposed in this paper. The circuit generates three voltage references by biasing three MOS transistors with different threshold (standard- $V_T$ , low- $V_T$  and zero- $V_T$ ) under the ZTC condition, sharing the same current reference core. The proposed circuit has been designed in a standard 0.13- $\mu$ m CMOS process. Based on measurement results on 15 samples, three voltage references ranging from 47.66 up to 317 mV nominal voltages have been obtained, achieving a best measured TC of 73 ppm/°C over the whole 0 to 85 °C temperature range with a power consumption more than 10× less than previous Schottky-based implementations.

#### REFERENCES

- D. M. Colombo, G. Wirth, and S. Bampi, "Sub-1 V band-gap based and MOS threshold-voltage based voltage references in 0.13 μm cmos," *Analog Integrated Circuits and Signal Processing*, vol. 82, no. 1, pp. 25–37, 2015.

- [2] M. Seok, G. Kim, D. Blaauw, and D. Sylvester, "A Portable 2-Transistor Picowatt Temperature-Compensated Voltage Reference Operating at 0.5 V," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 10, pp. 2534–2545, Oct 2012.

- [3] A. C. de Oliveira, D. Cordova, H. Klimach, and S. Bampi, "A 0.12–0.4 V, Versatile 3-Transistor CMOS Voltage Reference for Ultra-Low Power Systems," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 11, pp. 3790–3799, Nov 2018.

- [4] I. Lee, D. Sylvester, and D. Blaauw, "A Subthreshold Voltage Reference With Scalable Output Voltage for Low-Power IoT Systems," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 5, pp. 1443–1449, May 2017.

- [5] Q. Dong, D. Blaauw, and D. Sylvester, "A 114-pW PMOS-only, trimfree voltage reference with 0.26% within-wafer inaccuracy for nW systems," in 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), June 2016, pp. 1–2.

- [6] A. C. de Oliveira, D. Cordova, H. Klimach, and S. Bampi, "Picowatt, 0.45–0.6 V Self-Biased Subthreshold CMOS Voltage Reference," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 12, pp. 3036–3046, Dec 2017.

- [7] D. Albano, F. Crupi, F. Cucchi, and G. Iannaccone, "A Sub-kt/q Voltage Reference Operating at 150 mV," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 8, pp. 1547–1551, Aug 2015.

- [8] I. Filanovsky, B. Bai, and B. Moore, "A CMOS voltage reference using compensation of mobility and threshold voltage temperature effects," in *Circuits and Systems, 2009. MWSCAS '09. 52nd IEEE International Midwest Symposium on*, Aug 2009, pp. 29–32.

- [9] J. Jiang, W. Shu, and J. S. Chang, "A 5.6 ppm/°C Temperature Coefficient, 87-dB PSRR, Sub-1-V Voltage Reference in 65-nm CMOS Exploiting the Zero-Temperature-Coefficient Point," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 3, pp. 623–633, March 2017.

- [10] P. Toledo, "MOSFET Zero-Temperature-Coefficient (ZTC) Effect Modeling and Analysis for Low Thermal Sensitivity Analog Applications," Master's thesis, Universidade Federal do Rio Grande do Sul, DOI: 10.13140/RG.2.1.2965.9286, sep 2015.

[11] Y. Wenger and B. Meinerzhagen, "A stable CMOS current reference based on the ZTC operating point," in 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), June 2017, pp. 273–276.

5

- [12] M. Alioto, Enabling the Internet of Things from Integrated Circuits to Integrated Systems, 1st ed. Springer, 2017.

- [13] J. Martino, V. Mesquita, C. Macambira, V. Itocazu, L. Almeida, P. Agopian, E. Simoen, and C. Claeys, "Zero Temperature Coefficient behavior for advanced MOSFETs," in 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Oct 2016, pp. 785–788.

- [14] D. Cordova, P. Toledo, H. Klimach, E. Fabris, and S. Bampi, "0.5 V supply voltage reference based on the MOSFET ZTC condition," in 2015 28th Symposium on Integrated Circuits and Systems Design (SBCCI), Aug 2015, pp. 1–7.

- [15] P. Toledo, H. Klimach, D. Cordova, S. Bampi, and E. Fabris, "Selfbiased CMOS current reference based on the ZTC operation condition," in 2014 27th Symposium on Integrated Circuits and Systems Design (SBCCI), Sept 2014, pp. 1–7.

- [16] —, "MOSFET ZTC Condition Analysis for a Self-biased Current Reference Design," *The Journal of Integrated Circuits and Systems*, vol. 10, no. 2, pp. 103–112, 2015.

- [17] D. Cordova, A. C. de Oliveira, P. Toledo, H. Klimach, S. Bampi, and E. Fabris, "A sub-1 V, nanopower, ZTC based zero-VT temperaturecompensated current reference," in 2017 IEEE International Symposium on Circuits and Systems (ISCAS), May 2017, pp. 1–4.

- [18] I. Filanovsky and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits," *Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactions on*, vol. 48, no. 7, pp. 876–884, Jul 2001.

- [19] R. Baker, CMOS: Circuit Design, Layout and Simulation, 2nd ed. Wiley-IEEE, 2005.

- [20] C. Schneider and C. Galup-Montoro, CMOS Analog Design Using All-Region MOSFET Modeling, 1st ed. Cambridge University Press, 2010.

- [21] P. Kinget, C. Vezyrtzis, E. Chiang, B. Hung, and T. Li, "Voltage references for ultra-low supply voltages," in *Custom Integrated Circuits Conference*, 2008. CICC 2008. IEEE, Sept 2008, pp. 715–720.

- [22] D. Butler and R. Jacob Baker, "Low-voltage bandgap reference design utilizing Schottky diodes," in *Circuits and Systems*, 2005. 48th Midwest Symposium on, Aug 2005, pp. 1794–1797 Vol. 2.

- [23] A. J. Annema, P. Veldhorst, G. Doornbos, and B. Nauta, "A sub-1V bandgap voltage reference in 32nm FinFET technology," in 2009 IEEE International Solid-State Circuits Conference - Digest of Technical Papers, Feb 2009, pp. 332–333.

- [24] K. N. Leung and P. K. T. Mok, "A sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 4, pp. 526–530, Apr 2002.

- [25] J. Doyle, Y. J. Lee, Y.-B. Kim, H. Wilsch, and F. Lombardi, "A CMOS subbandgap reference circuit with 1-v power supply voltage," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 1, pp. 252–255, Jan 2004.

- [26] A. Boni, "Op-amps and startup circuits for CMOS bandgap references with near 1-V supply," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 10, pp. 1339–1343, Oct 2002.

- [27] H. Banba, H. Shiga, A. Umezawa, T. Miyaba, T. Tanzawa, S. Atsumi, and K. Sakui, "A CMOS bandgap reference circuit with sub-1-V operation," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 5, pp. 670–674, May 1999.

- [28] M. Ugajin and T. Tsukahara, "A 0.6-V voltage reference circuit based on Σ-V<sub>TH</sub> architecture in CMOS/SIMOX," in 2001 Symposium on VLSI Circuits. Digest of Technical Papers, June 2001, pp. 141–142.

- [29] H. Schmid and A. Huber, "Measuring a Small Number of Samples, and the 3v Fallacy: Shedding Light on Confidence and Error Intervals," *IEEE Solid-State Circuits Magazine*, vol. 6, no. 2, pp. 52–58, Spring 2014.

- [30] A. C. de Oliveira, D. Cordova, H. Klimach, and S. Bampi, "Picowatt, 0.45-0.6 v Self-Biased Subthreshold CMOS Voltage Reference," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 12, pp. 3036–3046, Dec 2017.