Doctoral Dissertation Doctoral Program in Energy Enginering (31.th cycle)

# On-line Junction Temperature Estimation of SiC Power MOSFETs

Fausto Stella

\* \* \* \* \* \*

#### **Supervisors**

Prof. Gianmario Pellegrino, Supervisor Prof. Eric Armando, Co-supervisor

| NoDerivative Works 4.0 International  | ative Commons License, Attribution - Noncommercialal: see www.creativecommons.org. The text cial purposes, provided that credit is given to |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| · · · · · · · · · · · · · · · · · · · | and organisation of this dissertation constitute<br>t compromise in any way the rights of third<br>he security of personal data.            |

|                                       | Fausto Stella<br>Turin, May 2, 2019                                                                                                         |

|                                       |                                                                                                                                             |

## Summary

The ability to monitor the junction temperature of power devices during the operation of a power converter will be a key enabler towards higher performance and reliability of power electronics. Starting from the well-known dependency of the  $R_{ON}$  with the junction temperature of SiC power MOSFETs, innovative solutions are proposed in order to obtain a high-dynamic estimation of the junction temperature on board of a real converter. After the initial commissioning of the power module performed directly in the field, the device temperature is real-time observed during current controlled operation of the converter. Furthermore, this technique provides precious information about the state of health of the power modules. A proof of concept test rig and a 3-phase custom inverter, designed of for Formula SAE Electric have been designed, built and tested to validate the proposed solution. The results of the thesis demonstrate the effectiveness and feasibility of the proposed methodology, in terms of extra performance and augmented reliability of the power modules. Additional studies on lifetime prediction strategies are ongoing.

## Acknowledgements

I am infinitely beholden to my supervisor, Prof. Gianmario Pellegrino, for his invaluable support, expert advice and for helping me numerous time through the complex process of completing my doctoral degree. I am equally grateful to my cosupervisor, Prof. Eric Armando for his fantastic expertise and indispensable input that helped steer my research in the right direction on countless occasions. I am truly thankful to my beloved family and dear friends for supporting me throughout my doctorate.

"The history of science shows that theories are perishable. With every new truth that is revealed we get a better understanding of Nature and our conceptions and views are modified."

Nikola Tesla

## Contents

| Li | st of            | Table   | es e      | XI   |

|----|------------------|---------|-----------------------------------------------|------|

| Li | $\mathbf{st}$ of | Figur   | ·es                                           | XII  |

| 1  | Intr             | oduct   | ion                                           | 3    |

|    | 1.1              | -       | e of the Thesis                               |      |

|    | 1.2              | Publis  | shed Papers                                   | . 6  |

| 2  | Jun              | ction ' | Temperature Measurement and Estimation        | 7    |

|    | 2.1              | Direct  | t Measurements Techniques                     |      |

|    |                  | 2.1.1   | Physical Sensors                              |      |

|    |                  | 2.1.2   | Optical Sensors                               |      |

|    | 2.2              |         | ect Measurement Techniques                    |      |

|    |                  | 2.2.1   | Model Based Estimate                          |      |

|    |                  | 2.2.2   | TSEPs Parameters                              |      |

|    |                  |         | 2.2.2.1 Low Calibrated Current Injection      |      |

|    |                  |         | 2.2.2.2 Turn-ON Delay                         |      |

|    |                  |         | 2.2.2.3 Turn-OFF Delay                        |      |

|    |                  |         | 2.2.2.4 Saturation Current                    |      |

|    |                  |         | 2.2.2.5 di/dt                                 |      |

|    |                  |         | 2.2.2.6 High Current Injection                |      |

|    |                  |         | 2.2.2.7 TSEPs Conclusions                     |      |

|    |                  | 2.2.3   | Proposed Technique Based on $V_{ON}$ Sampling | . 15 |

| 3  | Pro              | of of C | Concept Demonstrator                          | 17   |

|    | 3.1              | Power   | r Modules Under Test                          | . 18 |

|    | 3.2              | Regen   | nerative Test Operation                       | . 20 |

|    | 3.3              |         | ayout                                         |      |

|    |                  | 3.3.1   | Control Board                                 | . 23 |

|    |                  | 3.3.2   | Driver Boards                                 | . 24 |

|    |                  | 3.3.3   | Power Board                                   | . 26 |

|    |                  | 3.3.4   | Heatsink with Resistors and Inductors Load    | . 28 |

|   |            | $3.3.5  V_{ON}$ Measurement System                                    |

|---|------------|-----------------------------------------------------------------------|

|   | 3.4        | EMI Aspects                                                           |

|   |            | 3.4.1 High dv/dt Related Problems                                     |

|   |            | 3.4.2 dv/dt Analysis                                                  |

| 4 | Res        | ults from POC Demostrator 3                                           |

|   | 4.1        | Commissioning Test                                                    |

|   |            | 4.1.1 Commissioning Test Description                                  |

|   |            | 4.1.2 Difference between $\theta_J$ and NTC Measurement               |

|   |            | 4.1.3 Data Manipulation                                               |

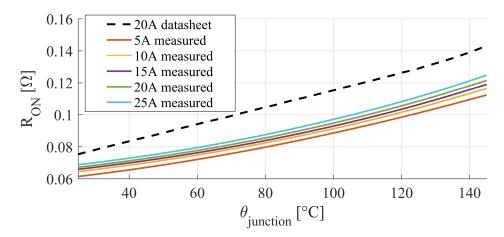

|   |            | 4.1.4 Measured vs Datasheet $R_{ON}$                                  |

|   | 4.2        | On-line Junction Temperature Estimation                               |

|   | 4.3        | Closed-Loop Temperature Control                                       |

|   | 4.4        | Validation of the Proposed Technique                                  |

|   |            | 4.4.1 Thermal Camera Validation                                       |

|   |            | 4.4.2 Comparison with an Adjacent Thermistor 5                        |

|   |            | 4.4.3 Insensitivity of Commissioning to the NTC Placement 50          |

|   |            | 4.4.4 Commissioning Test Repeatability 5                              |

|   | 4.5        | Comparison Between Dies from Different Manufacturers 5                |

|   | 4.6        | Conclusion                                                            |

|   |            | 4.6.1 Limitations of the Proposed Test Rig 69                         |

|   |            | 4.6.2 Other Considerations                                            |

| 5 | Pro        | gnostics 6                                                            |

|   | 5.1        | Review of Power Devices Prognostics 6                                 |

|   | 5.2        | Modified Commissioning Test 6                                         |

|   | 5.3        | Accelerated Aging of the Compoent                                     |

|   | 5.4        | Effect of Aging on Temperature Estimation After 15,000 Cycles Aging 7 |

|   | 5.5        | Direct Prognostics                                                    |

|   | 5.6        | Considerations About the Proposed Methodology                         |

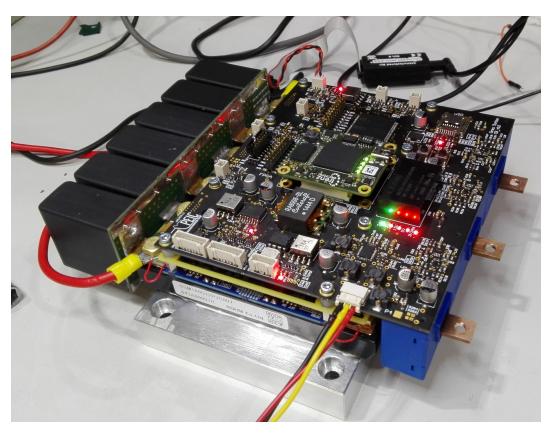

| 6 | <b>3-P</b> | H SiC Inverter for Student Formula Electric 79                        |

|   | 6.1        | Description of the Race Vehicle                                       |

|   |            | 6.1.1 AMK Motor Drive Package                                         |

|   |            | 6.1.2 Key Regulations of Formula SAE Competitions 8                   |

|   | 6.2        | New SiC MOSFET Inverter for Formula SAE 8                             |

|   |            | 6.2.1 Mechanical Layout                                               |

|   |            | 6.2.2 3-Phase Power Modules                                           |

|   |            | 6.2.3 Driver Board Design                                             |

|   |            | 6.2.4 Control Board Design                                            |

|   |            | 6.2.5 Capacitor Boards Design                                         |

|   |            | 6.2.6 Auxiliary Power Supplies 10                                     |

|   |     | 6.2.7    | V <sub>ON</sub> Measurement System                       | 107 |

|---|-----|----------|----------------------------------------------------------|-----|

|   | 6.3 | Firmw    | are Description                                          | 114 |

|   |     | 6.3.1    | FPGA Code                                                | 114 |

|   |     | 6.3.2    | Microcontroller Code                                     | 115 |

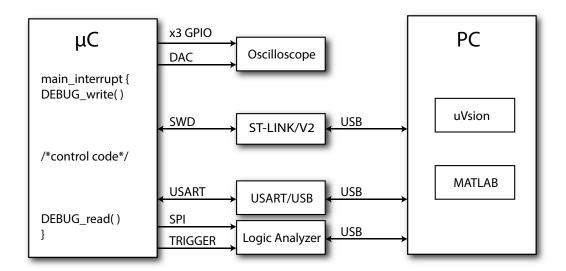

|   |     | 6.3.3    | Debug and Acquisition Tool                               | 117 |

| 7 | Res | ults for | r the 3-phase Inverter Prototype                         | 121 |

|   | 7.1 | Comm     | issiongin Test                                           | 122 |

|   |     | 7.1.1    | Commissioning Test Description                           | 122 |

|   |     | 7.1.2    | Pulse Sequence on Axis "a" Positive                      | 122 |

|   |     | 7.1.3    | Phase Hexagon                                            | 123 |

|   |     | 7.1.4    | Deviation of $\theta_J$ Respect to Hot Plate Temperature | 124 |

|   |     | 7.1.5    | Effect of Antiparallel Diodes                            | 128 |

|   |     | 7.1.6    | Parameters Dispersion                                    | 131 |

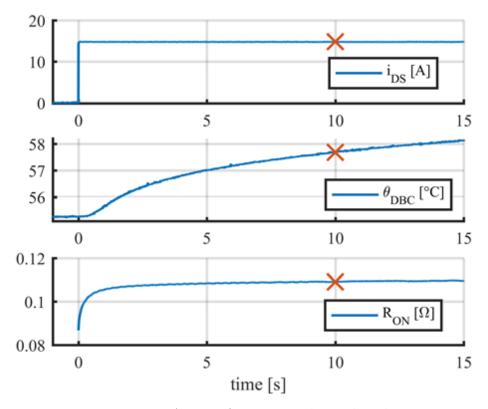

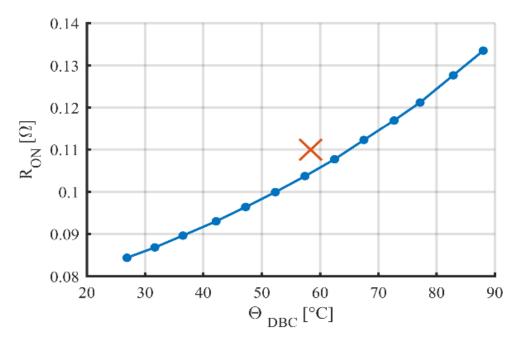

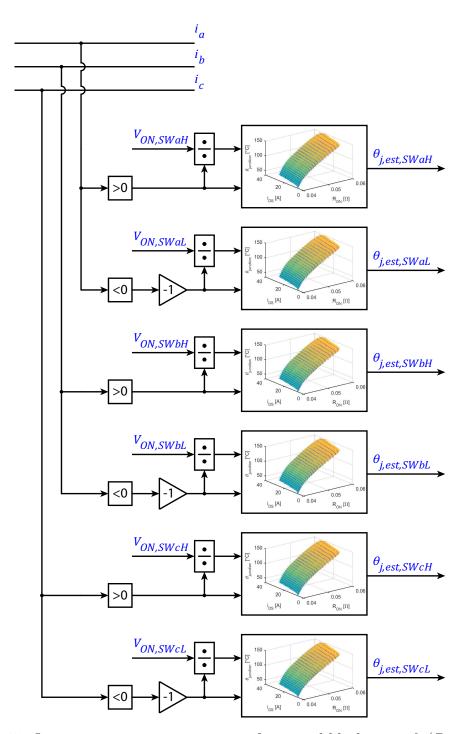

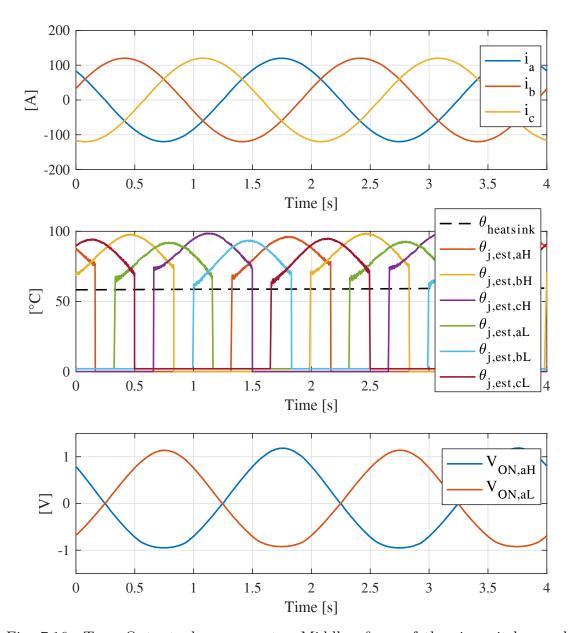

|   | 7.2 | Online   | Temperature Estimation                                   | 132 |

|   |     | 7.2.1    | Online Temperature Estimation Results                    | 134 |

|   |     | 7.2.2    | Online Temperature Estimation Considerations             | 135 |

| 8 | Cor | clusion  | ns .                                                     | 137 |

|   | 8.1 | Prospe   | ect Applications                                         | 138 |

|   | 8.2 | _        | Work                                                     |     |

## List of Tables

| 2.1 | Composition of the $R_{ON}$ of a 600 V MOSFET [47]                | 13  |

|-----|-------------------------------------------------------------------|-----|

| 3.1 | Power Module, type#1 (from datasheet)                             | 20  |

| 3.2 | Power Module, type#2 (from datasheet)                             | 20  |

| 3.3 | STGAP1S main features                                             | 25  |

| 3.4 | Electrolytic capacitor.                                           | 27  |

| 3.5 | Film capacitor                                                    | 27  |

| 3.6 | Ceramic capacitor                                                 | 28  |

| 3.7 | Ferrite Inductor.                                                 | 28  |

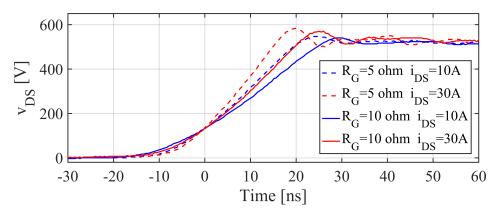

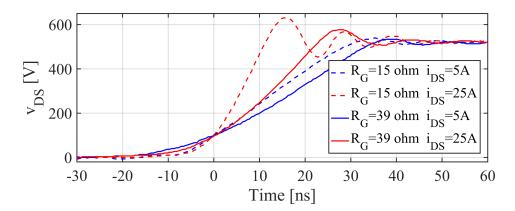

| 3.8 | Summary results collected dv/dt test. Maximum dv/dt for the two   |     |

|     | modules under test, measured at different values of drain current | 35  |

| 6.1 | IPM motor model: DD5-14-10-POW                                    | 82  |

| 6.2 | AMK inverter power ratings                                        | 84  |

| 6.3 | Power Module BSM180D12P3C007                                      | 91  |

| 6.4 | Capacitor: MKP1848C62090JP4                                       | 102 |

| 6.5 | Capacitor: 3640AC224KAT3A                                         | 102 |

| 7.1 | Test "a positive": sampling instances                             | 124 |

## List of Figures

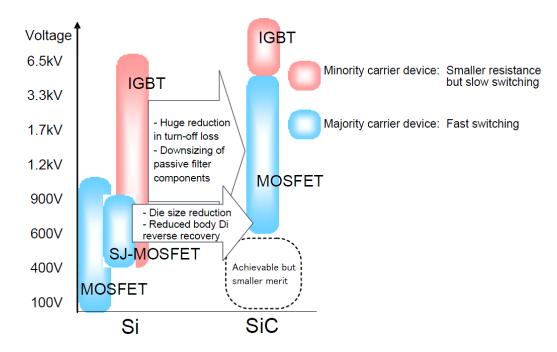

| 1.1  | Si vs SiC devices: areas of use and possible benefits [3]               | 4  |

|------|-------------------------------------------------------------------------|----|

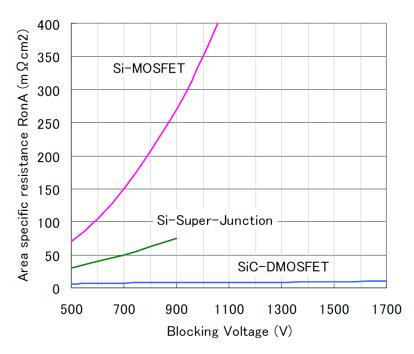

| 1.2  | Si vs SiC devices: $R_{ON}$ at various breakdown voltages. [3]          | 5  |

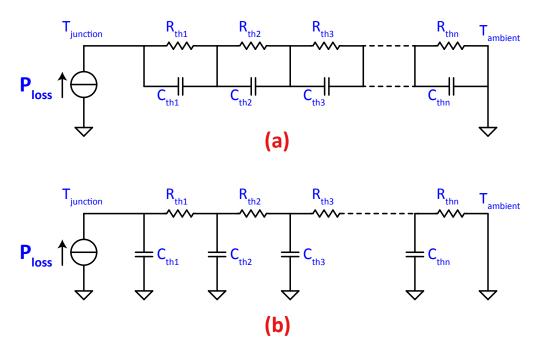

| 2.1  | Thermal RC models: (a) Foster network. (b) Cauer network                | 10 |

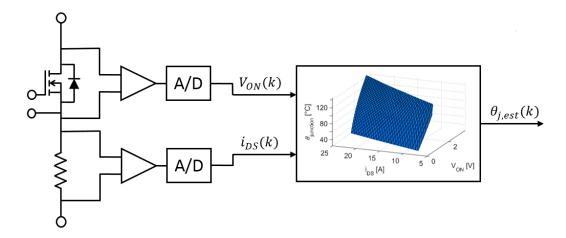

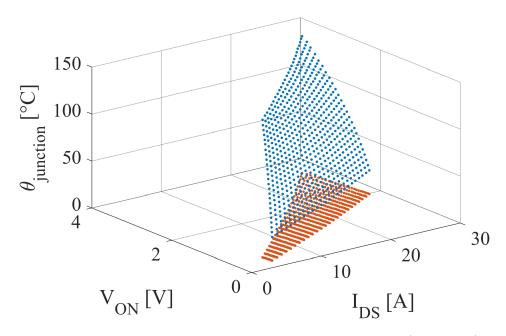

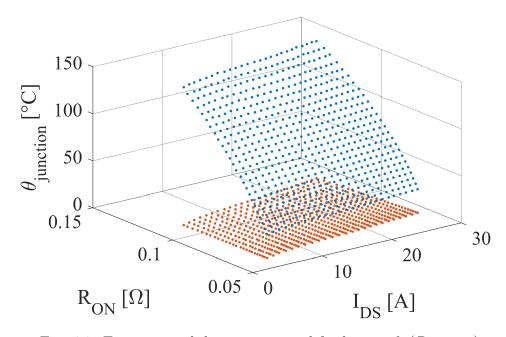

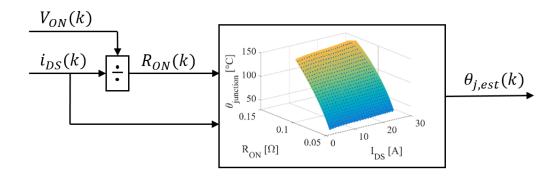

| 2.2  | Temperature estimator functional block using $\theta_J(V_{ON}, i_{DS})$ | 16 |

| 3.1  | Proof of concept demonstrator                                           | 17 |

| 3.2  | Power module package                                                    | 18 |

| 3.3  | Layout of power module (courtesy of Vishay Semiconductor Ital-          |    |

|      | iana). In green the two internal local capacitors. In blue the internal |    |

|      | NTC thermistor (label "Th"), for measurement of case temperature.       | 19 |

| 3.4  | Control schematic. LEG1 is open-loop controlled while LEG2 is used      |    |

|      | in closed-loop current control                                          | 21 |

| 3.5  | Schematic diagram of the proposed setup: red quantities are mea-        |    |

|      | sured online                                                            | 22 |

| 3.6  | Overview of the proposed setup                                          | 23 |

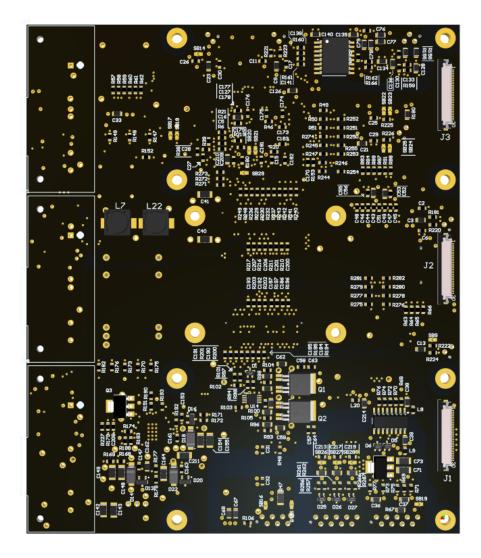

| 3.7  | Overview of the control board                                           | 24 |

| 3.8  | Overview of the driver board                                            | 25 |

| 3.9  | Overview of the driver board                                            | 26 |

| 3.10 | Heatsink with four heating resistors (two on the left side and two      |    |

|      | on the right side) and the inductive load composed of eight ferrite     |    |

|      | inductors. The two additional cooling fans are on the back of the       |    |

|      | heatsink (not visible in figure)                                        | 29 |

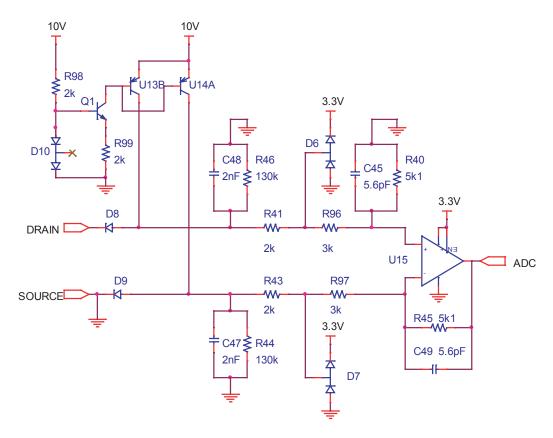

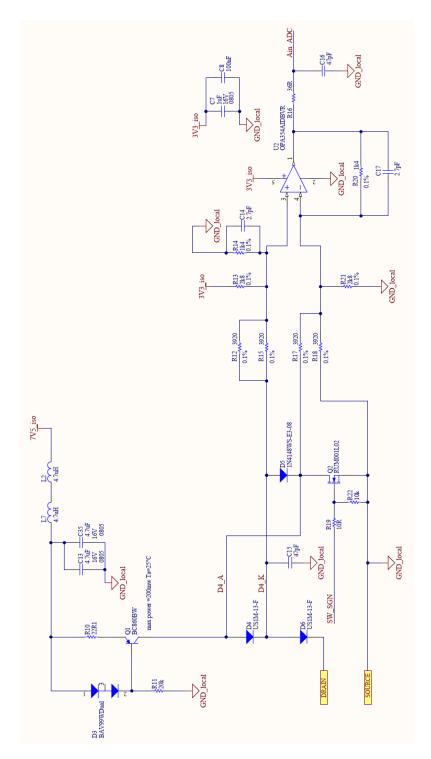

| 3.11 | Schematic of the analog conditioning stage dedicated to the $V_{ON}$    |    |

|      | measurement                                                             | 30 |

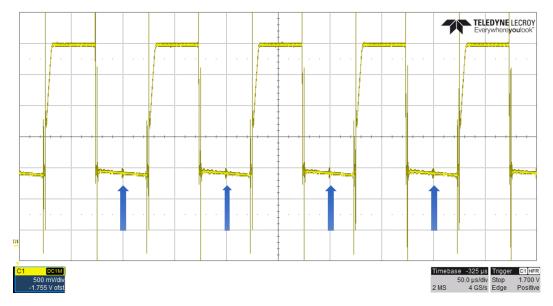

| 3.12 | Detail of the PCB board with the two diodes very close to eachother.    | 32 |

| 3.13 | Input voltage to the A/D converter. $V_{A/D}$ =500 mV/div t=50 µs/div   | 32 |

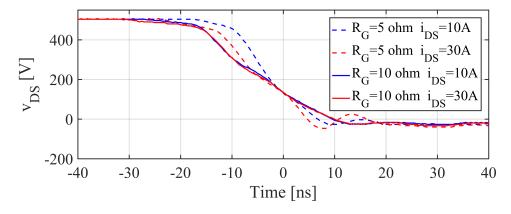

| 3.14 | Module#1 turn-OFF, behavior of $v_{DS}$ for different values of gate    |    |

|      | resistor                                                                | 34 |

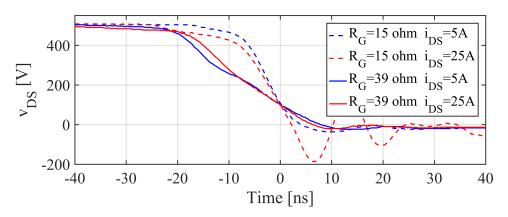

| 3.15 | Module#2 turn-OFF, behavior of $v_{DS}$ for different values of gate    |    |

|      | resistor                                                                | 34 |

| 3.16 | Module#1 turn-ON, behavior of $v_{DS}$ for different values of gate re- |    |

|      | sistor.                                                                 | 34 |

| 3.17        | Module#2 turn-ON, behavior of $v_{DS}$ for different values of gate re-                     |          |

|-------------|---------------------------------------------------------------------------------------------|----------|

|             |                                                                                             | 35       |

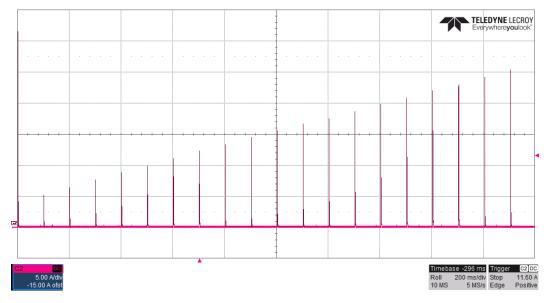

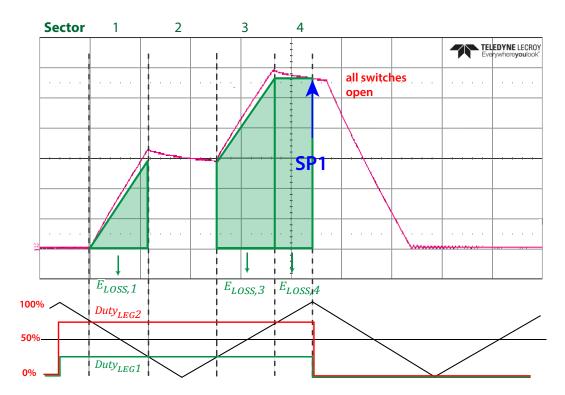

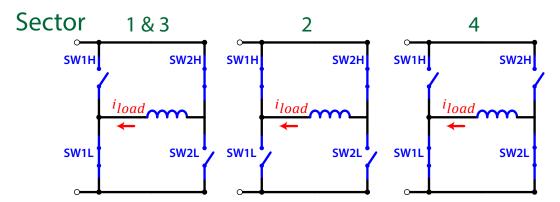

| 4.1         | Impulsive current test for mapping the MOSFET under test. The                               |          |

|             | current pulses are equally distributed in time, one pulse every 100                         |          |

|             | ms. The current pulses are of growing amplitude from 1 A up to the                          | 0.0      |

| 4.0         | SWIE /                                                                                      | 38       |

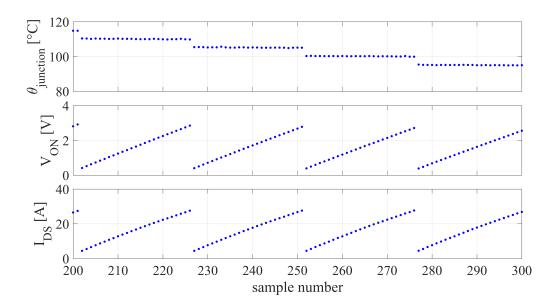

| 4.2         | Results of the commissioning: 28 current and voltage values per                             | ~ ~      |

| 4.0         | •                                                                                           | 36       |

| 4.3         | Top: load current during the current pulse test at 28 A. ( $i_SW1L=5$                       |          |

|             | A/div t=20 μs/div.) Bottom: corresponding reference duty cycles                             | 4 -      |

|             | 0                                                                                           | 41       |

| 4.4         |                                                                                             | 42       |

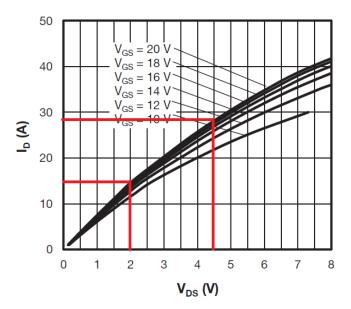

| 4.5         | Typical Drain-to-Source current output characteristics at $\theta_J = 150 ^{\circ}\text{C}$ | 10       |

| 1.0         | \                                                                                           | 42       |

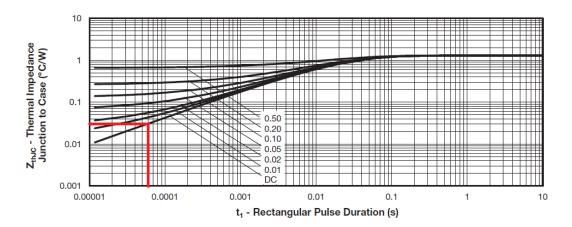

| 4.6         | Maximum thermal impedance Junction-to-Case Characteristic (cour-                            | 16       |

| 1 7         | · · · · · · · · · · · · · · · · · · ·                                                       | 43       |

| 4.7         | 0 0 0 010 000                                                                               | 44<br>44 |

| 4.8         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                     | 44       |

| 4.9         | Measured values of $R_{ON}$ as a function of junction temperature. The                      |          |

|             | black dashed line represents the $R_{ON}$ provided in the datasheet while                   | 45       |

| 4.10        | 1 011                                                                                       | 40<br>46 |

| 4.10        | **************************************                                                      | 47       |

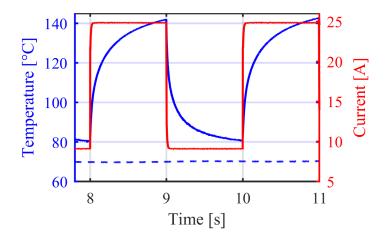

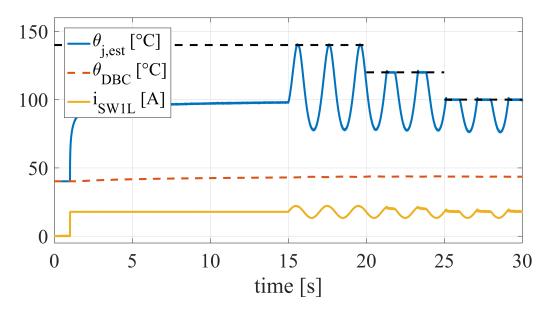

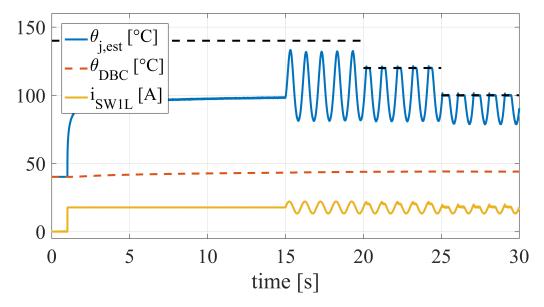

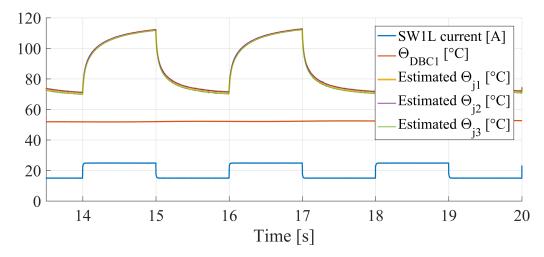

|             | On-line estimation of SW1L junction temperature (blue), with square-                        | 41       |

| 4.12        | wave load current (red). Dashed blue line: DBC substrate tempera-                           |          |

|             |                                                                                             | 47       |

| <i>4</i> 13 | On-line estimation of SW1L junction temperature (blue), at different                        | ±1       |

| 1.10        | load currents (red). Dashed blue line: DBC substrate temperature,                           |          |

|             |                                                                                             | 48       |

| 4.14        |                                                                                             | 49       |

|             | Online junction temperature limitation, duty-cycle LEG1=0% (SW1L                            |          |

|             |                                                                                             | 50       |

| 4.16        | Online junction temperature limitation, duty-cycle LEG1=0% (SW1L                            |          |

|             |                                                                                             | 50       |

| 4.17        | Online junction temperature limitation, duty-cycle LEG1=50% (SW1L                           |          |

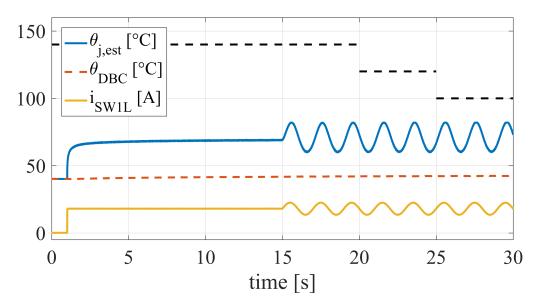

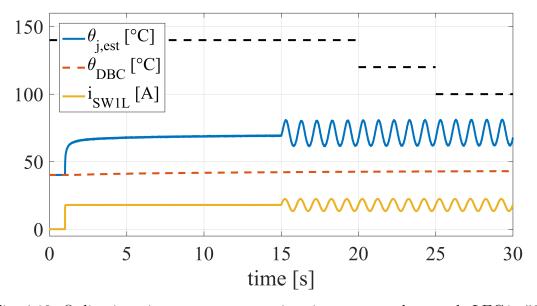

|             |                                                                                             | 51       |

| 4.18        | Online junction temperature estimation, average duty-cycle LEG1=50%                         |          |

|             |                                                                                             | 51       |

| 4.19        |                                                                                             | 53       |

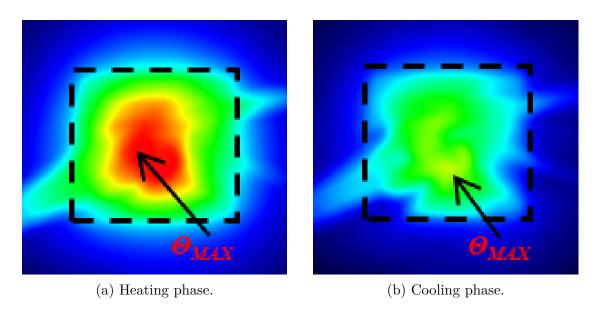

| 4.20        | Thermal image of the chip SW1L. The black dashed line indicate the                          |          |

|             | die area                                                                                    | 54       |

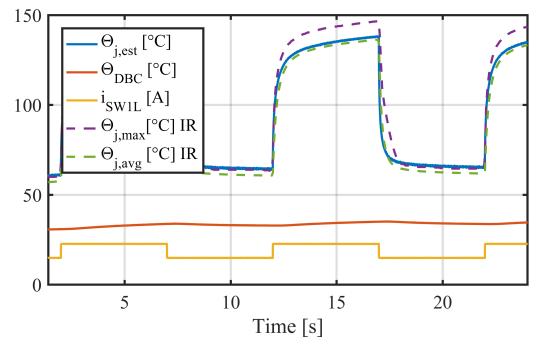

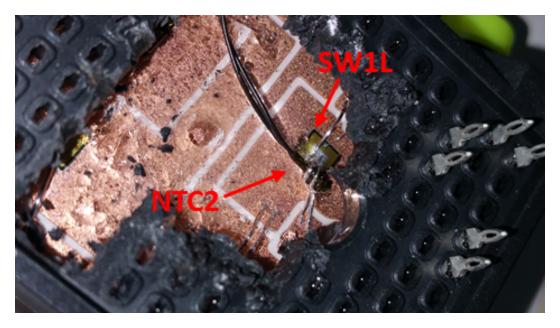

| 4.21 | Validation with IR camera: comparison estimated temperature (blue) and measured temperature (dashed). Maximum and average measurements are supported to the comparison of the comparison estimated temperature (blue) and measured temperature (dashed). |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.00 | surements are reported                                                                                                                                                                                                                                   |

| 4.22 | Placement of NTC2 thermistor under the bonding wires of the die                                                                                                                                                                                          |

| 4.00 | under test                                                                                                                                                                                                                                               |

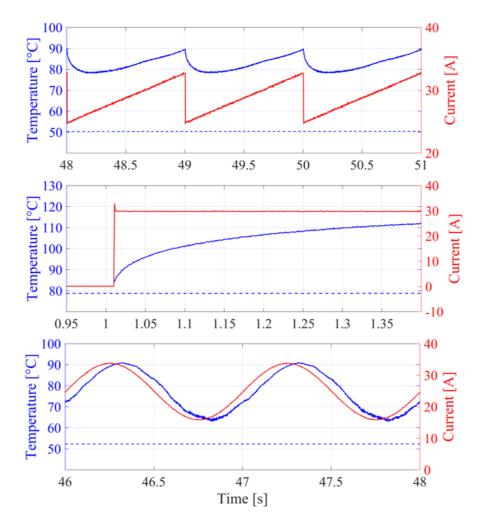

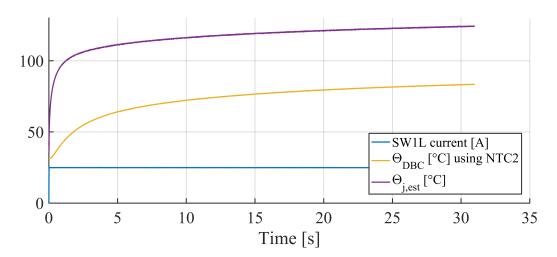

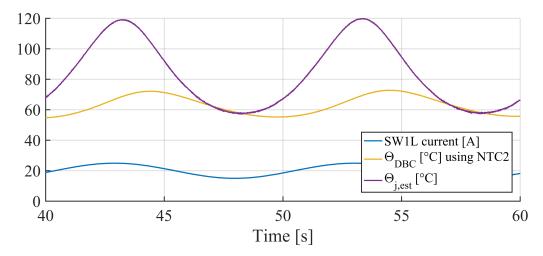

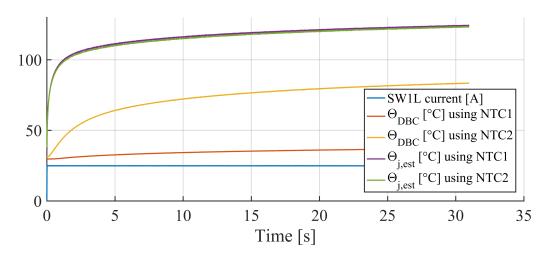

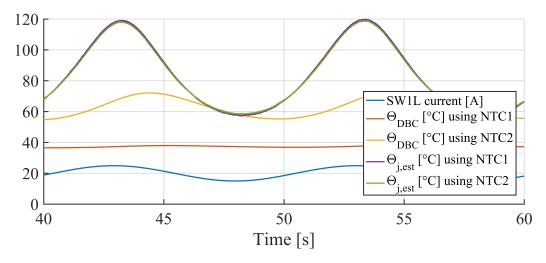

| 4.23 | Current step of 25 A. Comparison between junction temperature es-                                                                                                                                                                                        |

| 4.24 | timate and direct-contact measurement with NTC2 AC current at 0.1 Hz superimposed to 20 A DC. Comparison between junction temperature estimate and direct-contact measurement with                                                                       |

|      | NTC2.                                                                                                                                                                                                                                                    |

|      | Junction temperature estimation during a current step of 25A                                                                                                                                                                                             |

|      | Junction temperature estimation with sinusoidal current reference.                                                                                                                                                                                       |

| 4.27 | Temperature estimation using three different look-up-tables, made                                                                                                                                                                                        |

| 4.00 | during three different tests                                                                                                                                                                                                                             |

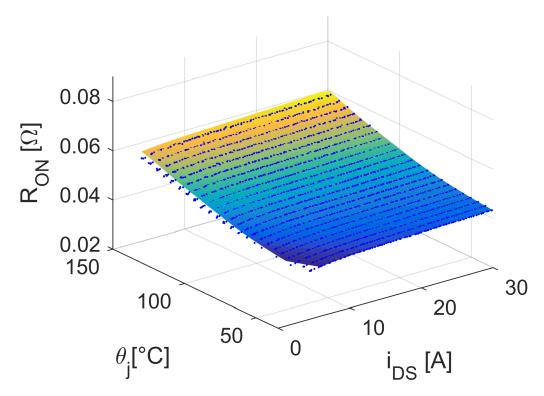

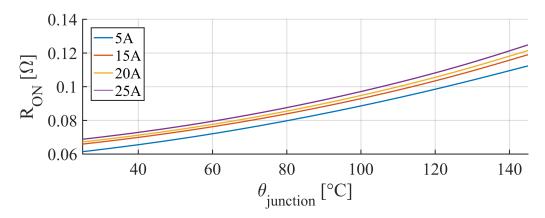

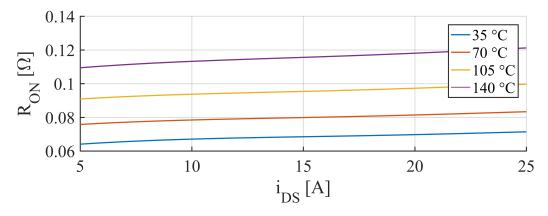

| 4.28 | Measured $R_{ON}$ as a function of junction temperature and current for module#1                                                                                                                                                                         |

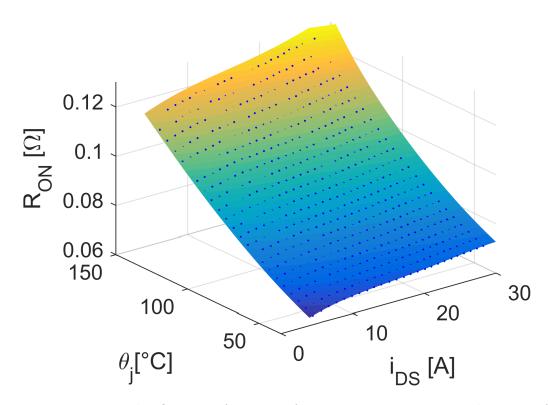

| 4.29 | Measured RON as a function of junction temperature and current                                                                                                                                                                                           |

|      | for module#2                                                                                                                                                                                                                                             |

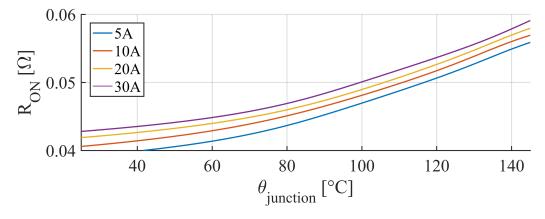

| 4.30 | Measured values of $R_{ON}$ as a function of $\theta_J$ for module #1                                                                                                                                                                                    |

| 4.31 | Measured values of $R_{ON}$ as a function of $\theta_J$ for module #2                                                                                                                                                                                    |

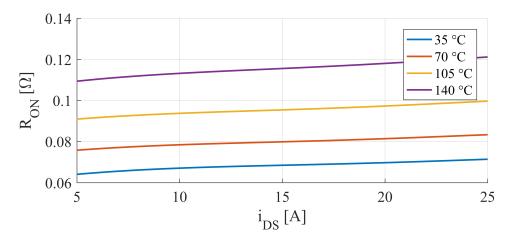

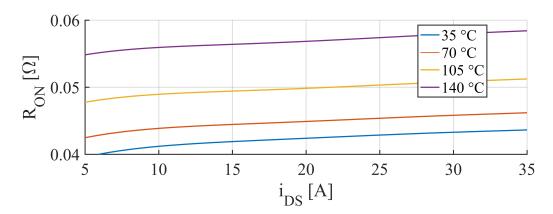

| 4.32 | Measured values of $R_{ON}$ as a function of $i_{DS}$ for module#1                                                                                                                                                                                       |

| 4.33 | Measured values of $R_{ON}$ as a function of $i_{DS}$ for module #2                                                                                                                                                                                      |

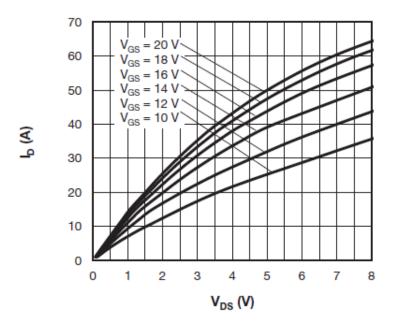

| 4.34 | Typical drain to source current output characteristics at $\theta_J = 25$ °C                                                                                                                                                                             |

|      | for module#2                                                                                                                                                                                                                                             |

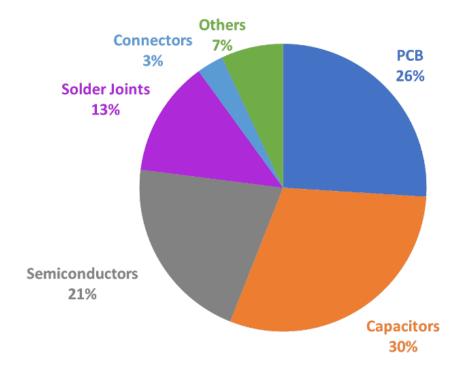

| 5.1  | Failure distribution among major components [55]                                                                                                                                                                                                         |

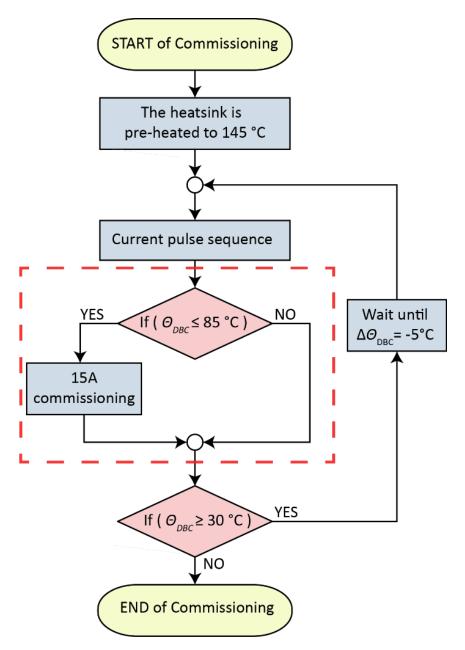

| 5.2  | Commissioning test flowchart. The dashed red box indicates the additional task dedicated to life state assessment for prognostics                                                                                                                        |

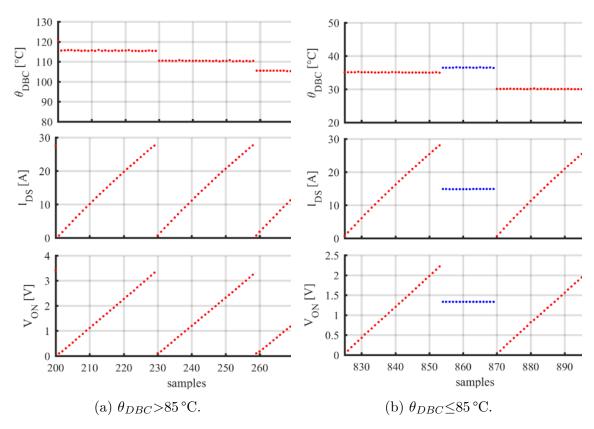

| 5.3  | Advanced commissioning test, with additional test (blue dots)                                                                                                                                                                                            |

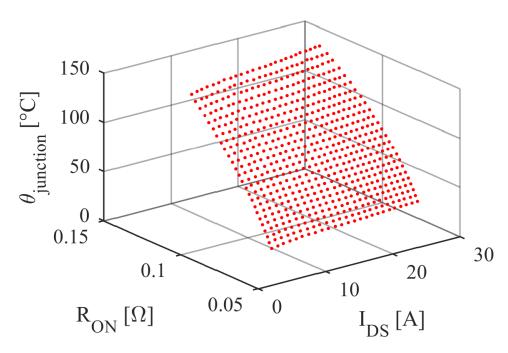

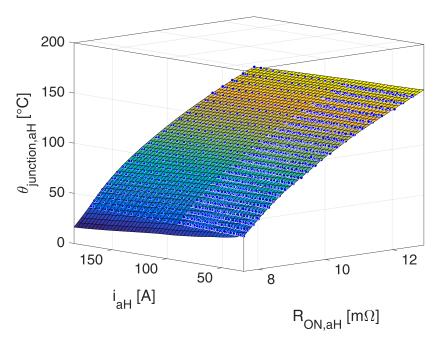

| 5.4  | Pulse current test results $\theta_J(R_{ON}, i_{DS})$                                                                                                                                                                                                    |

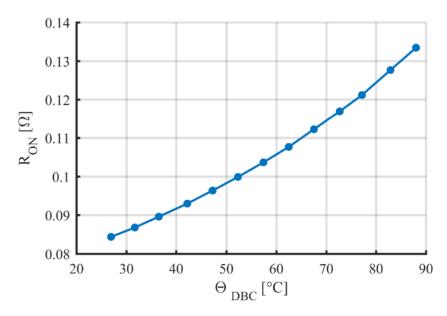

| 5.5  | $R_{ON}(\theta_{DBC}, i_{DS}=15 \text{ A})$ from 15A-test commissioning, representative of the healthy module                                                                                                                                            |

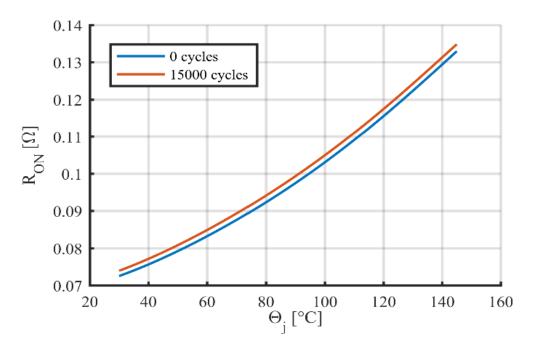

| 5.6  | $R_{ON}(\theta_J, i_{DS} = 15 \mathrm{A})$ before and after 15,000 cycles aging                                                                                                                                                                          |

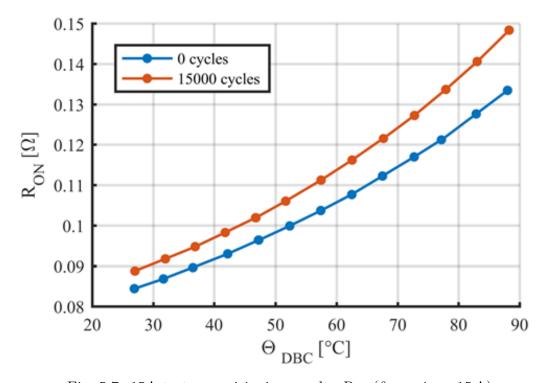

| 5.7  | 15A-test commissioning results $R_{ON}(\theta_{DBC}, i_{DS}=15 \text{ A})$                                                                                                                                                                               |

| 5.8  | Junction temperature estimation after 15,000 cycles aging. The orange line is the estimation of the junction temperature using the original LUT measured at the beginning of the life of the module.                                                     |

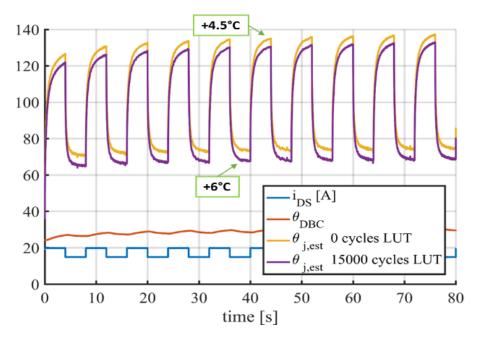

|      | The purple line is the estimation of the junction temperature using                                                                                                                                                                                      |

| 5.0  | the new LUT measured after the aging of the module                                                                                                                                                                                                       |

| 5.9  | 15A-test after 15,000 thermal cycles. $R_{ON}(\theta_{DBC}, i_{DS}=15 \text{ A})$ after 0 thermal cycles vs 15 A-test after 15,000                                                                                                                       |

| 5.10 | thermal cycles                                                                                                                                                                                                                                           |

| 6.1  | Previous version of the Squadra Corse prototype race car                                                                                                                                                                                                 |

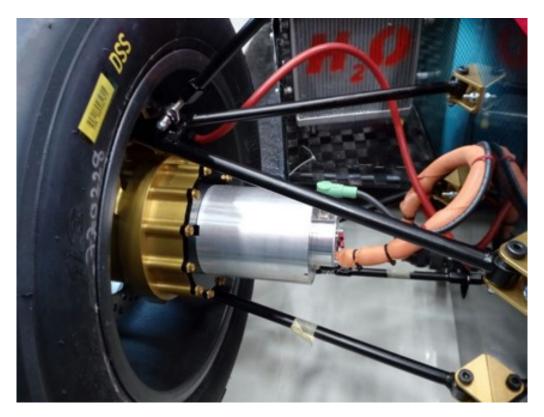

|      |                                                                                                                                                                                                                                                          |

| 6.2  | One of the motorized wheels                                                                              | 81   |

|------|----------------------------------------------------------------------------------------------------------|------|

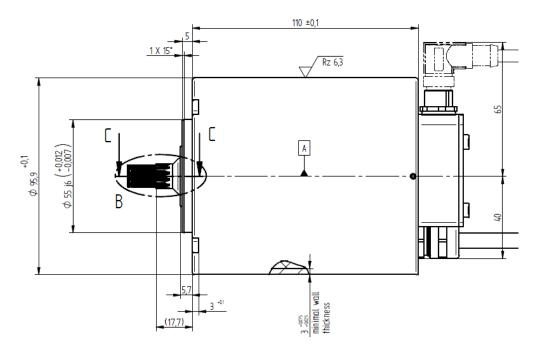

| 6.3  | Mechanical drawing of AMK motor model: DD5-14-10-POW                                                     | 82   |

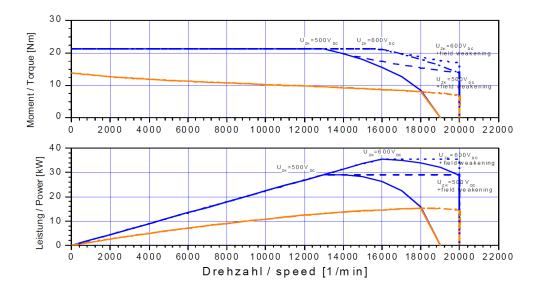

| 6.4  | Maximum Torque (top) and power (bottom) versus speed character-                                          |      |

|      | istics at maximum current and different DC-link voltage values                                           | 83   |

| 6.5  | Commercial inverter produced by AMK                                                                      | 85   |

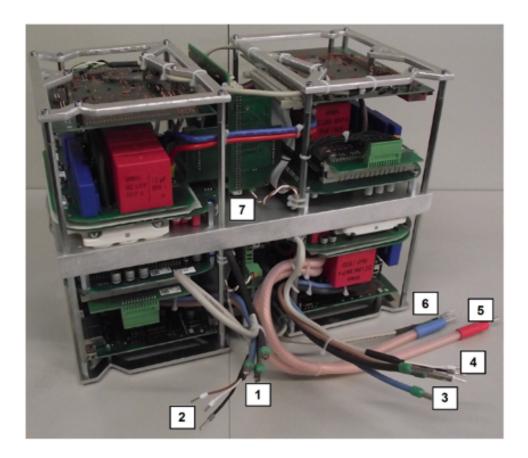

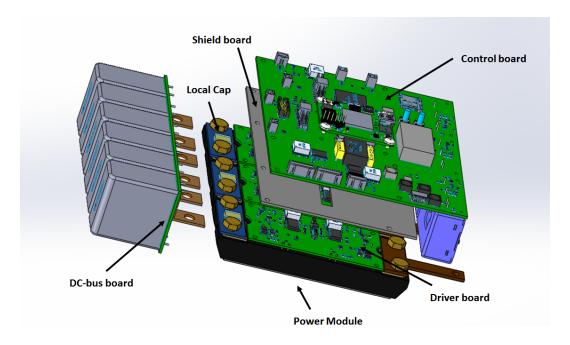

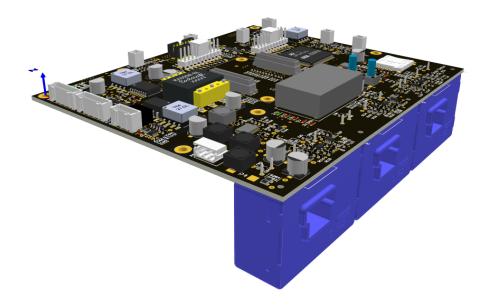

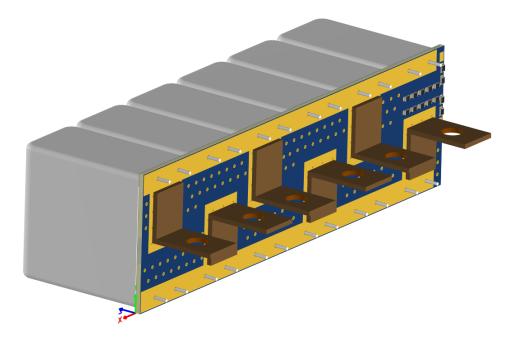

| 6.6  | Assembly of the power converter                                                                          | 87   |

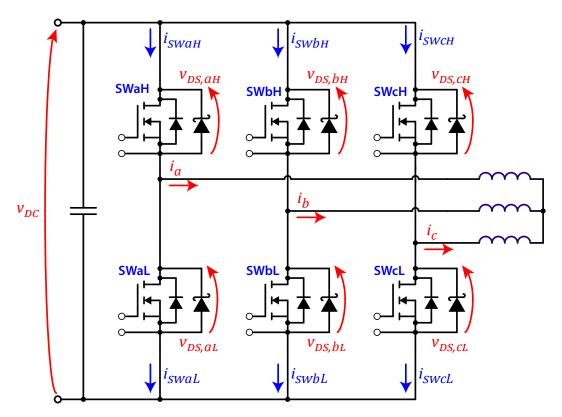

| 6.7  | Inverter schematic. Red quantities are measured online                                                   | 88   |

| 6.8  | Exploded view of the power converter                                                                     | 89   |

| 6.9  | Mechanical drawing of the inverter (dimensions in mm)                                                    | 90   |

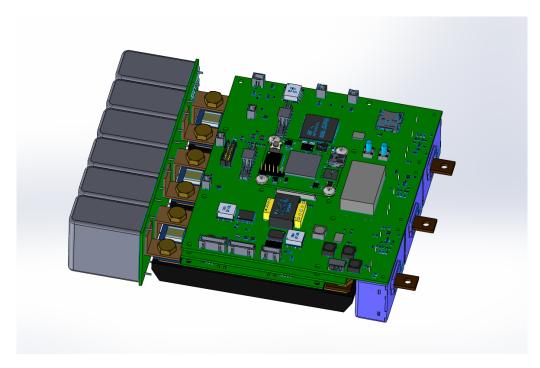

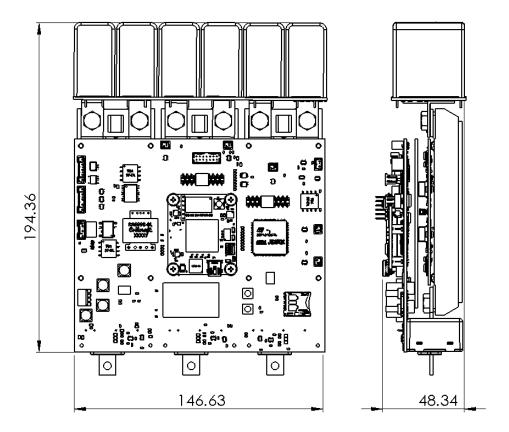

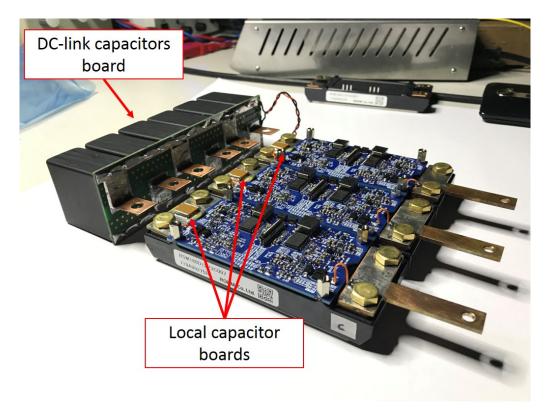

| 6.10 | SiC power module model:BSM180D12P3C007                                                                   | 91   |

| 6.11 | Internal layout of the power module                                                                      | 92   |

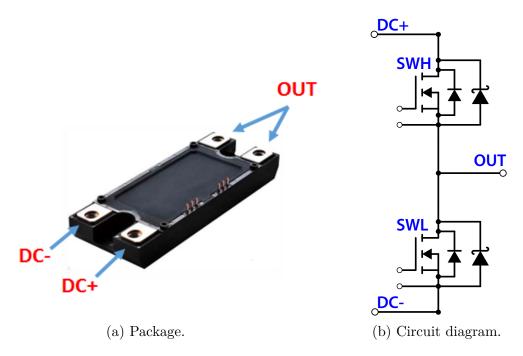

| 6.12 | Driver board, both sides                                                                                 | 93   |

| 6.13 | Power modules, driver board, local capacitor board and output busbar                                     | . 94 |

| 6.14 | Control board with current transducers                                                                   | 95   |

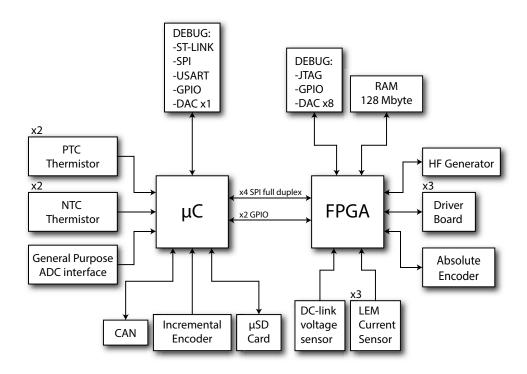

|      | Control board functional diagram                                                                         | 95   |

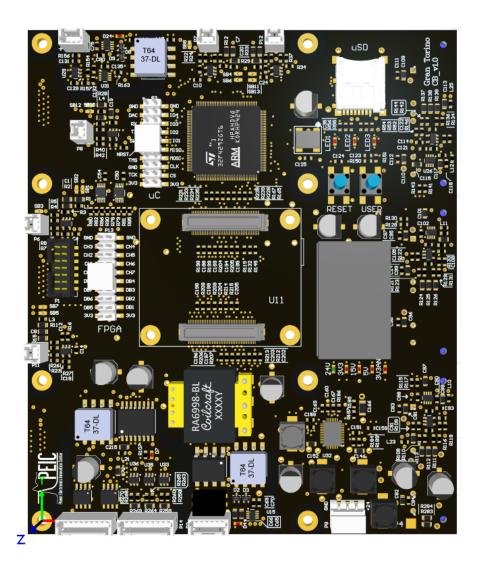

| 6.16 | Control board top side                                                                                   | 98   |

| 6.17 | Control board bottom side                                                                                | 99   |

| 6.18 | DC-link capacitors board                                                                                 | 100  |

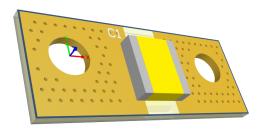

| 6.19 | Local capacitor board                                                                                    | 101  |

| 6.20 | Power module, driver boards, local capacitor boards, output busbar                                       |      |

|      | and capacitor board                                                                                      | 101  |

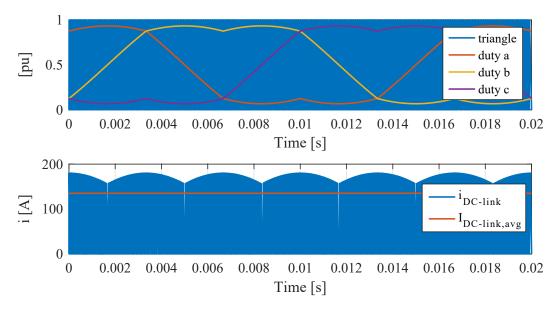

| 6.21 | $I_{\text{rms}}$ DC-link capacitors. $(i_{phase,pk}=180 \text{ A}, \cos(\theta)=1, V_{phase,ref,pu}=1).$ | 104  |

| 6.22 | Detail of Fig. 6.21                                                                                      | 104  |

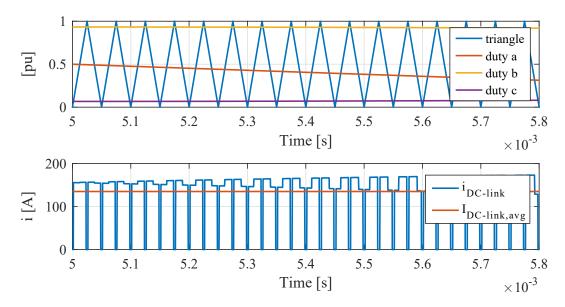

| 6.23 | $I_{RMS}$ in the DC-link capacitors at different value of $cos(\theta)$ and $V_{phase,ref}$              | .105 |

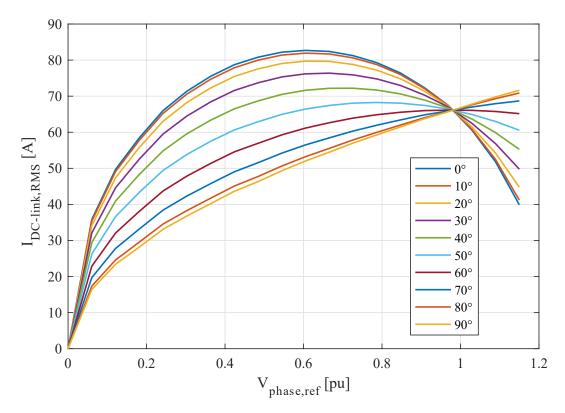

| 6.24 | Auxiliary power supplies functional diagram                                                              | 107  |

| 6.25 | Schematic $V_{ON}$ measurement system                                                                    | 108  |

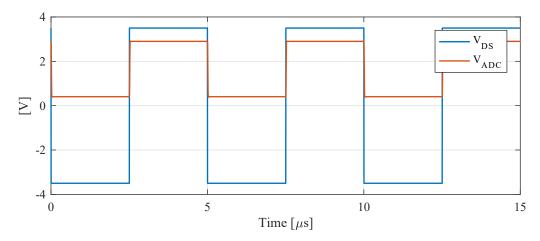

| 6.26 | Spice simulation of the $V_{ON}$ measurement system response at 100 kHz                                  |      |

|      | switching frequency                                                                                      | 111  |

|      | Detail of Fig. 6.26. (Left) down-front. (Right) up-front                                                 | 111  |

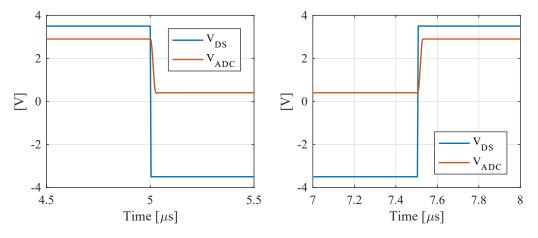

|      | Bode diagram of the $V_{Ain\ ADC}/V_{DS}$ response                                                       | 112  |

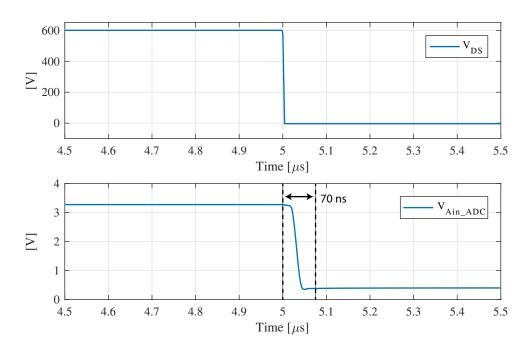

|      | $v_{DS}$ step changed from 600 V to -3.5 V                                                               | 112  |

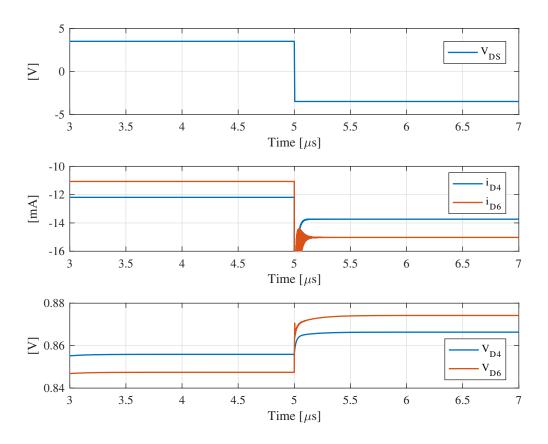

| 6.30 | Currents in D4 and D6 before and after a step variation of $v_{DS}$                                      | 113  |

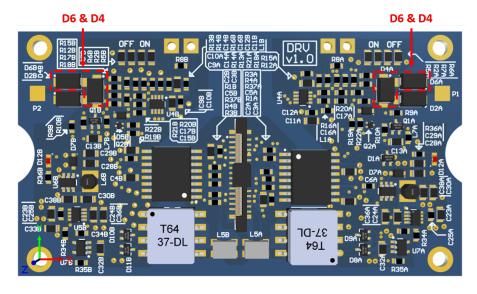

| 6.31 | Diodes D4 and D6 in close proximity                                                                      | 113  |

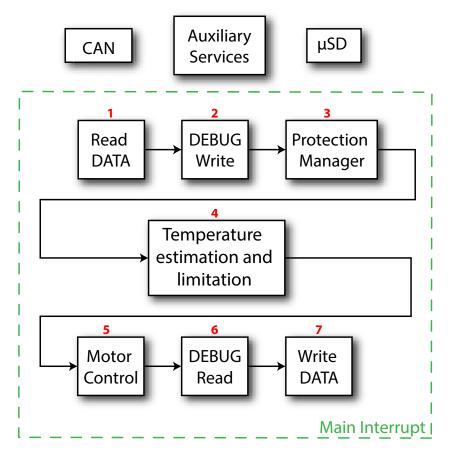

| 6.32 | Flowchart description of the control task executed by the MCU. The                                       |      |

|      | control task executed at each interrupt is enclosed in a green dashed                                    |      |

|      | line.                                                                                                    | 117  |

|      | DEBUG interface functional diagram                                                                       | 119  |

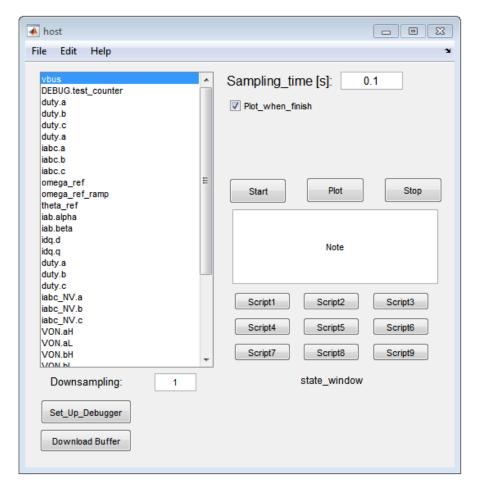

| 6.34 | DEBUG GUI MATLAB                                                                                         | 120  |

| 7.1  | Power converter overview. The provisional heatsink is a block of                                         |      |

|      | aluminium.                                                                                               | 121  |

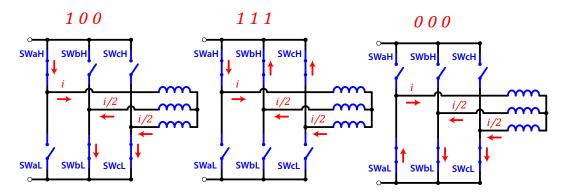

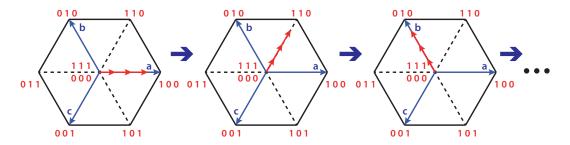

| 7.2  | First hexagon: switches state                                                                            | 123  |

| 7.3          | Current pulses of growing amplitude on each of the six axis of the                   |     |

|--------------|--------------------------------------------------------------------------------------|-----|

|              | phase hexagon.                                                                       | 123 |

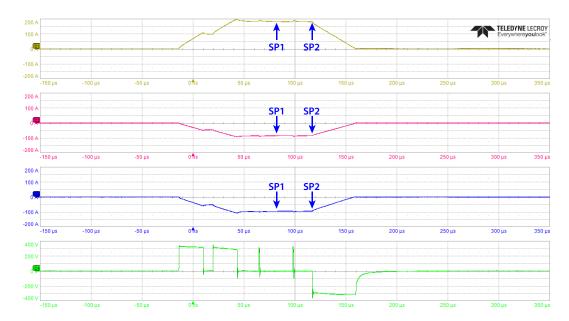

| 7.4          | Commissioning test. Starting from the top: $i_a$ (50 A/div), $i_b$ (50 A/div)        |     |

|              | $i_c$ (50 A/div) and $V_{ab}$ (100 V/div). (t=50 $\mu$ s/div)                        | 124 |

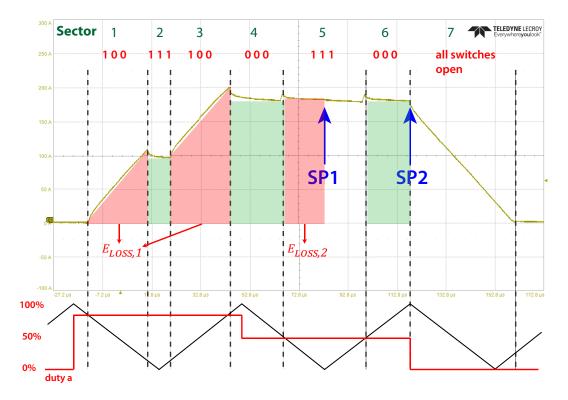

| 7.5          | Top: current pulse of phase "a" during the commissioning test ( $i_a=50 \text{ A}$ ) |     |

|              | t=22 μs/div). Bottom: reference duty cycle phase "a" and triangular                  |     |

|              | carrier.                                                                             | 126 |

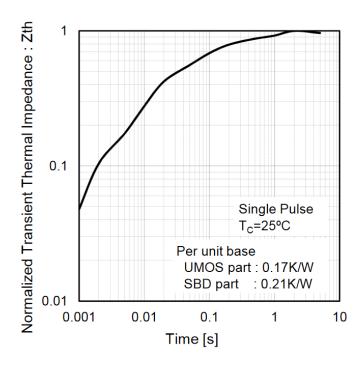

| 7.6          | Normalized transient thermal impedance (from the datasheet)                          | 127 |

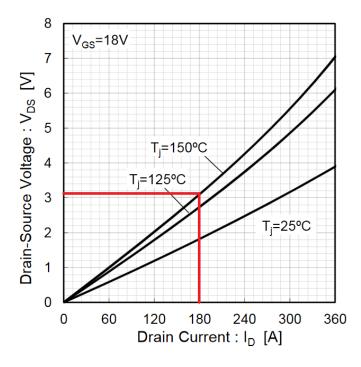

| 7.7          | Drain-Source voltage vs Drain Current (from the datasheet)                           | 127 |

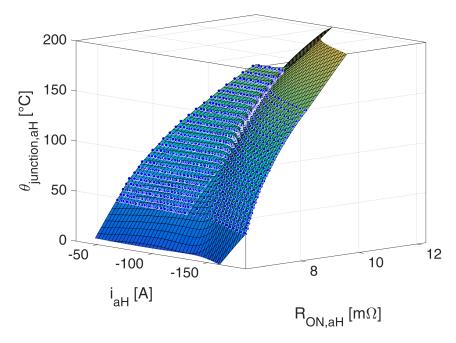

| 7.8          | Map of the switch SWaH for $i_{SWaH} > 30$ A obtained from the current               | 121 |

| 1.0          | pulse test                                                                           | 129 |

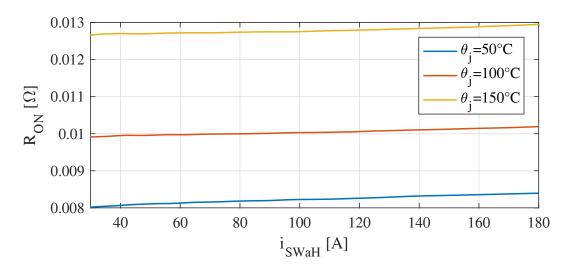

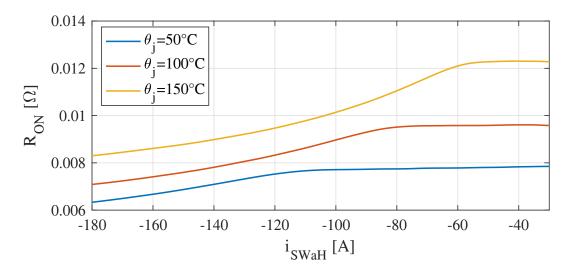

| 7.9          | $R_{ON}$ as a function of current for $i_{SWaH} > 30 \mathrm{A.}$                    | 129 |

|              | $R_{ON}$ as a function of eartern for $t_{SWaH} > 00$ M                              | 130 |

|              | Map of the switch SWaH for $i_{SWaH}$ <-30 A obtained from the current               | 100 |

| 1.11         | pulse test                                                                           | 130 |

| 7 10         |                                                                                      | 131 |

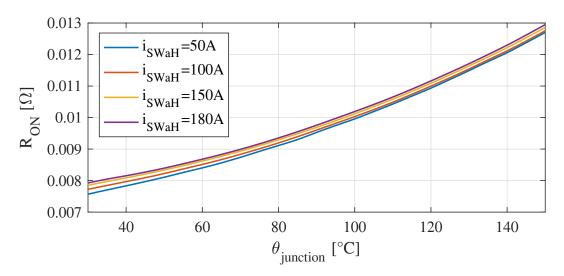

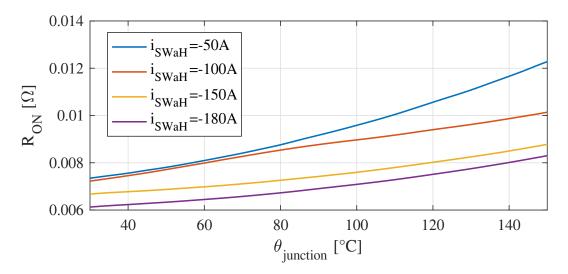

|              | $R_{ON}$ as a function of current for $i_{SWaH} < -30 \mathrm{A.}$                   |     |

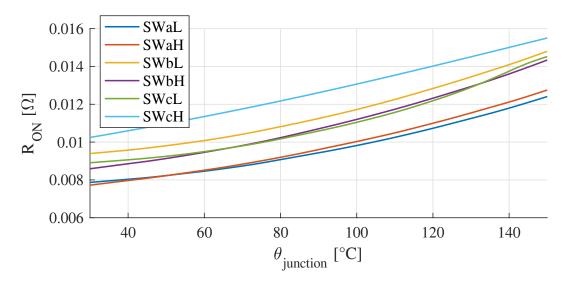

|              | $R_{ON}$ as a function of $\theta_J$ for switch SWaH                                 | 131 |

| 1.14         | $R_{ON}$ as a function of $\theta_J$ . Comparison between all the switches,          | 100 |

| <b>-</b> 1 - | $i_{DS}$ =180 A                                                                      | 132 |

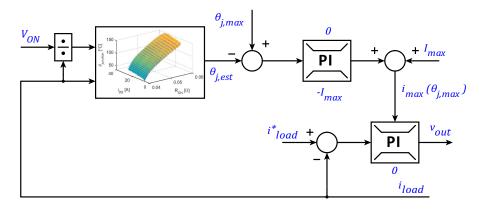

|              | Junction temperature estimator functional block using $\theta_J(R_{ON}, i_{DS})$     | 133 |

| 7.16         | Top: Output phase currents. Middle: $\theta_{J,est}$ of the six switches and         |     |

|              | measured heatsink temperature. Bottom: $V_{ON}$ of SWaH and SWaL.                    | 135 |

| 7.17         | Internal layout of the power module. Red dashed line indicates the                   |     |

|              | two metallized areas.                                                                | 136 |

## List of Abbreviations

ADC Analog to Digital Converter

API Application Program Interface

DAC Digital to Analog Converter

DBC Direct Bonded Copper substrate

DMA Direct Memory Access

FMC Flexible Memory Controller

FPGA Field Programmable Gate Array

FPU Floating Point Unit

GPIO General-Purpose Input/Output

GUI Graphical User Interface

IC Integrated Circuit

IR Infrared Radiation

MCU MicroController Unit

POC Proof Of Concept

SOA Safe Operating Area

SPI Serial Peripheral Interface

SPICE Simulation Program with Integrated Circuit Emphasis

SVM Space Vector Modulation

SWD Serial Wire Debug

TSEP Thermo-Sensitive Electrical Parameter

USART Universal synchronous and asynchronous receiver-transmitter

## Chapter 1

### Introduction

The first studies on Silicon-Carbide (SiC) semiconductors began in 1955, when the first methodologies for growing a pure crystal were presented [1]. At the time SiC was more popular than Si and Ge. However, due to the difficulty in obtaining high purity grade wafer, the SiC was abandoned until the 70'. In 1978 Tairov and Tsvetkov made the first high purity SiC wafer. In 1987 a new process for obtaining high purity SiC wafers at low temperature was developed. Cree launched the first commercial SiC LED and SiC wafer, respectively in 1989 and 1991. In the early 2000's the first SiC diodes became available on the market. In 2011 Cree launched the first commercial 1200 V SiC MOSFET [2].

Fig. 1.1 summarizes the main areas of use of the power semiconductor technologies today available on the market.

For many years, Si IGBT has been the traditional choice for power electronic applications, where high breakdown voltages and high currents are required. It has been widely used in power electronic application such as AC motor drives, UPS, power conversion for renewable energy(wind and solar). The IGBT has been developed in the 1980s and since that it has been continually improved [4]. Nowadays, IGBT devices continue to be used widely despite the number of studies pointing out the advantages of SiC MOSFETs over IGBTs [5], [6].

In IGBT devices low conduction resistances and high breakdown voltages are achieved by injecting minority carriers into the drift region. However, when the device is turned-OFF the minority carriers takes time to recombine, thus generating a "slow" commutation with a tail current.

In contrast, Silicon MOSFETs are devices based on majority carriers that permit to achieve high speed commutations. However, they have lower breakdown voltages and higher conduction resistances. During the year the Si MOSFET technology has been continuously improved and taken to its limits with the introduction of the Sisuper-junction MOSFET. Fig. 1.2 shows the area specific resistance as a function of the blocking voltage. Si MOSFETs and Si super junction MOSFETs are only available for breakdown voltages up to 900 V. In turn, they are not suitable for

Fig. 1.1: Si vs SiC devices: areas of use and possible benefits [3].

medium and high power applications. Compared to Si, SiC has ten times the dielectric breakdown field strength. In turn, high voltage SiC power MOSFETs are feasible. SiC MOSFETs combine the desirable characteristics of IGBT and Si MOSFET.

SiC MOSFETs devices offer a series of advantages compared to their silicon counterparts. They permit to achieve lower conduction and switching losses, higher operating temperatures, higher breakdown voltages, better thermal stability and better thermal conductivity [7], [8]. SiC diodes are now widely used in high efficiency applications while the SiC MOSFETs still have obstacles in terms of market penetration. Nearly a decade after the introduction of the 1200 V SiC MOSFET, its application is still armed by the high price of the devices and by many unsolved challenges such us: high dv/dt, EMI emission [9], reliability, reduced surge capability [10], reduced thermal inertia and non standard gate drivers. SiC technology is critical to realizing the next generation of high efficiency power electronic converters. SiC devices permit to realize extremely compact and efficient power applications. In the last years a wide range of SiC MOSFET power modules has hit the market, making SiC semiconductors more competitive. The main advantages in using a power module respect to discrete devices are the higher power density, the easier heat extraction, the lower part count, the optimized layout (parasitics reduction) and higher reliability. Due to the low thermal inertia and to the high power density, accurate thermal management is mandatory to ensure reliability and take full advantage of new SiC devices and modules.

Fig. 1.2: Si vs SiC devices:  $R_{ON}$  at various breakdown voltages. [3].

#### 1.1 Scope of the Thesis

The aim of this thesis is to provide a methodology to estimate the junction temperature of SiC power MOSFET modules implementable in hard switching industrial converters. An H-bridge proof of concept power converter and a three phase high power density inverter have been built to demonstrate the feasibility of the proposed methodology. Moreover, the presented methodology with minor modifications can be used for evaluating the health state of the power devices.

Section 1.2 contains the list of the published papers during the PhD program. Papers labelled as (c) and (g) concern the sensorless control of syncronous reluctance motor drives fed by matrix converter, with focus on the compensation of the converter voltage errors. This work is the result of a collaboration with the University of Nottingham, that the author visited for a semester. The initial plan was to investigate the SiC MOSFET matrix converter and to compare its performance with a Si IGBT counterpart. Such initial plan was later modified due to the non availability of both matrix converters. Although a consistent amount of time was dedicated to this activity, this is not reported in this thesis for the sake of clarity and brevity.

#### 1.2 Published Papers

#### Journal papers:

- (a) **F. Stella**, G. Pellegrino, E. Armando and D. Daprà, "Online Junction Temperature Estimation of SiC PowermosfetsThrough On-State Voltage Mapping," in IEEE Transactions on Industry Applications, vol. 54, no. 4, pp. 3453-3462, July-Aug. 2018. doi: 10.1109/TIA.2018.2812710

- (b) **F. Stella**, O. Olanrewaju, Z. Yang, A. Castellazzi, G. Pellegrino, Experimentally validated methodology for real-time temperature cycle tracking in SiC power modules, Microelectronics Reliability, Volumes 88–90, 2018, Pages 615-619, ISSN 0026-2714, https://doi.org/10.1016/j.microrel.2018.07.072.

- (c) **F. Stella**, A. Yousefi-Talouki, S. Odhano, G. Pellegrino and P. Zanchetta, "An Accurate Self-Commissioning Technique for Matrix Converters Applied to Sensorless Control of Synchronous Reluctance Motor Drives," in IEEE Journal of Emerging and Selected Topics in Power Electronics. doi: 10.1109/JESTPE.2018.2851142

#### Conference papers:

- (d) F. Stella, G. Pellegrino, E. Armando and D. Daprà, "Advanced testing of SiC power MOSFET modules for electric motor drives," 2017 IEEE International Electric Machines and Drives Conference (IEMDC), Miami, FL, 2017, pp. 1-8. doi: 10.1109/IEMDC.2017.8002314

- (e) F. Stella, G. Pellegrino and E. Armando, "Coordinated On-line Junction Temperature Estimation and Prognostic of SiC Power Modules," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, 2018, pp. 1907-1913. doi: 10.1109/ECCE.2018.8557850

- (f) **F. Stella**, G. Pellegrino, E. Armando and D. Daprà, "On-line temperature estimation of SiC power MOSFET modules through on-state resistance mapping," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, 2017, pp. 5907-5914. doi: 10.1109/ECCE.2017.8096976

- (g) A. Yousefi-Talouki, F. Stella, S. Odhano, L. de Lilo, A. Trentin, G. Pellegrino and P. Zanchetta, "Sensorless control of matrix converter-fed synchronous reluctance motor drives," 2017 IEEE International Symposium on Sensorless Control for Electrical Drives (SLED), Catania, 2017, pp. 181-186. doi: 10.1109/SLED.2017.8078421

## Chapter 2

## Junction Temperature Measurement and Estimation

The main methods to estimate and to measure the junction temperature are presented in this chapter.

#### 2.1 Direct Measurements Techniques

#### 2.1.1 Physical Sensors

The junction temperature of a semiconductor can be measured using a thermosensitive material that can be put in direct contact or in proximity to the die. In power electronic, thermistor and thermocouples are widely used. Most of the power modules already integrate an internal thermistor, however only one thermistor per module is usually present. The embedded thermistor can only measure the temperature of the DBC without being able to give any information about the junction temperature. In literature, many solutions were presented where the temperature sensor is placed in direct contact with the chip [11], [12] and [13]. The direct contact permits the transfer of thermal energy from the device under test to the probe thus measuring the temperature with a high level of accuracy. However, this energy transfer affects the temperature of the device under test modifying the thermal transfer path. Depending on the dimensions and on the type of contact between the probe and the device a delay and an attenuation of the temperature measurement have to be expected due to the probe thermal inertia. It is possible to adopt ultra small thermocouples with an external diameter of less than a millimetre as shown in [14], [15] and [15]. These extra small thermocouples can be glued directly on the chip surface, however the precision is low and the dynamic response is not good. Another solution is to use microprobes that thanks to their small dimension do not alter the thermal capacitance of the measured system [16]. Microprobes permit to achieve a good level of precision and a high level of dynamic. Placing a thermal sensor in direct contact with the chip may cause insulation problems, thus compromising the reliability of the device. In many cases, the greater reliability obtained thanks to the knowledge of the junction temperature, is not sufficient to compensate the lower reliability due to the presence of the sensor.

#### 2.1.2 Optical Sensors

An alternative method to directly measure the junction temperature of a semiconductor is to take advantage of the correlation between the optical proprieties of a material and its temperature. Different optical proprieties have been presented in literature like laser deflection [17], [18], luminescence, Raman spectroscopy [19], refraction index [20], thermoreflectance [21]. Dealing with the power electronics the preferred choice is the observation of the infrared radiation. The use of the IR camera permits to thermally map the whole chip surface so that is possible to detect the presence of local hotspots [22], [23], [24]. The temperature gradient across the device is not negligible and can reach tens of degrees depending on the semiconductor technology, the chip dimensions and the load conditions. Techniques like the laser deflection permit to measure the temperature distribution inside the die. However, there are drawbacks, like the necessity to provide visual access to the die inside the module. To make the chip visible from the optical system is necessary to remove the dielectric gel and depending by the adopted technique, the surface of the die need to be treated (e.g. IR thermography requires the surface to be black painted to obtain accurate measurements). In many cases no high voltage operations can be made. Moreover, any modification to the package can affect the working conditions of the chip. An alternative solution is to place optical fibers in direct contact with the surface of the chip without removing the dielectric. However, optical fibers only allow a local temperature measurement, without being able to give any information about the temperature gradient across the chip. Most of the optical methods require a considerable amount of hardware and computational time. To conclude, optical methods, compared to other methodologies have important advantages, however their use is mostly limited to a laboratory environment. Thanks to their precision and reliability, optical methods are often used to validate temperature estimation techniques, like the ones that rely on electro-thermal models or on TSEPs.

#### 2.2 Indirect Measurement Techniques

#### 2.2.1 Model Based Estimate

Thermal models are powerful tools, that can be used for real-time junction temperature estimation or during the design phase of a converter. For single chip devices, a typical thermal model is usually represented using a Cauer network Fig. 2.1(b) or a Foster network Fig. 2.1(a). The Cauer network reflects the real device structure with thermal capacitances and intermediary thermal resistances. Each layer of the power module can be represented with an RC model (chip, chip solder, substrate, and base plate). The Cauer network nodes are connected to the ground by a capacitor that represent the thermal capacitance of the layer. Each node of the network represents the temperature of the intermediate layers. The Cauer network however, is computationally complex to implement compared to the Foster network. The Foster network is composed by a series of resistors and capacitors connected in parallel, however the individual RC no longer represents the layer sequence. The network nodes have no correlation with the physical structure of the device. In fact the Foster network is a mathematical representation of the device and it has nothing to do with its physical representation. Usually, the datasheet of a device provides the transient thermal curve, from with is possible to obtain the R and C parameters of the Foster network. However, to have a precise model, the Foster network elements have to be computed experimentally. One way to do that is to measure the cooling thermal transient of the device. The analytical expression of a Foster network can be easily written in time domain (2.1) or in Laplace domain (2.2), where  $Z_{th}$  is the transient thermal impedance.

$$Z_{th}(t) = \sum_{i=1}^{n} R_i \cdot (1 - e^{-\frac{t}{R_i \cdot C_i}})$$

(2.1)

$$Z_{th}(t) = \frac{k_1}{s + p_1} + \frac{k_2}{s + p_2} + \dots \frac{k_n}{s + p_n}$$

(2.2)

$$k_i = \frac{1}{C_1}, \quad p_i = \frac{1}{R_i \cdot C_i}$$

(2.3)

Typically a power module includes more than one device (e.g. MOSFETs and the antiparallel diodes) that contributes to the total heat generation. The cross coupling effect can be taken into account by adding negative RC components to the Foster network [25] and [26]. With the aging of the component there is a degradation of the thermal path and the thermal network needs to be updated. In [27] the thermal model is updated with the aging of the component. The thermal resistance is supposed to increase linearly with the aging of the component. Although thermal capacitance is also affected by the aging of the component, its variation is significantly less than that in thermal resistance and in many cases its variation can be neglected.

Other factors can affect the thermal path. E.g. in case of liquid heatsink the thermal path depends on the flow rate of the coolant. Though the thermal path of the component is known, it is still necessary to compute the power losses of the device. The device datasheet provides the conduction and the switching losses measured under precise working conditions. E.g. The switching losses of a MOSFET depend on the gate resistance, the junction temperature, the commutated voltage and the commutated current. It is not trivial to compute the power losses when the working condition are different from those reported in the datasheet. "Hybrid" solutions where thermal networks and other methods are used conjointly to increase the accuracy of the temperature estimation. In [26] a thermal network model and a TSEP are used conjointly.

Fig. 2.1: Thermal RC models: (a) Foster network. (b) Cauer network.

#### 2.2.2 TSEPs Parameters

TSEPs (Temperature Sensitive Electrical Parameters) based methods are one of the most promising way for estimating the junction temperature in power semi-conductors [28]. Depending on the type of semiconductor different TSEPs can be used, in this section the analysis is mainly focused on N-channel power MOSFETs, however most of this techniques can be used also for IGBTs and diodes.

#### 2.2.2.1 Low Calibrated Current Injection

A few mA current is injected into the device and the voltage drop caused by the current is measured. This is one of the most used methods because thanks to the low current injection the device self heating is negligible. This TSEP is commonly used in power electronic where most of the devices have a PN junction. For MOSFETs, it is possible to inject a calibrated current between source and drain when the semiconductor is commanded open. This permit to measure the threshold

voltage of the body diode that presents a good sensitivity with the temperature [29], [30] and [31]. An alternative solution is to inject a low current between drain and source while the MOSFET is in ON state and then to measure the variation of the conduction resistance with the temperature [29]. However, due to the power MOSFETs low ohmic resistance, the voltage drop is extremely small and hardly measurable.

#### 2.2.2.2 Turn-ON Delay

The delay between the gate voltage signal imposed by the gate driver and the start of conduction of the device can be measured and used as a TSEP. This method can be applied to MOSFETs and IGBTs [32],[33], [34]. Different implementations are possible. E.g. In [35]  $V_{GE}$  and  $i_{CE}$  of an IGBT are monitored using two digital to analog converters. The  $V_{GE}$  rise, triggers a 100 MHz counter that is stopped when the collector current reaches a predefined level. In this example the delay time is around 1500 ns with a temperature sensitivity of 2 ns/°C. The turn-ON delay differently from the turn-OFF delay is not affected by the device current. For wide bandgap devices like SiC MOSFETs, the turn-ON delay time can be few tens of ns, in turn the time variations are hardly measurable. One solution is to slow down the commutations by increasing the gate resistance. However, this can result in an unacceptable loss of efficiency.

#### 2.2.2.3 Turn-OFF Delay

Similarly to the turn-ON delay, also the turn-OFF delay can be used as a TSEP [35] and [36]. Differently from the turn-ON delay, this method depends on the currents in the device before the switching. In [36] the junction temperature of a SiC MOSFET (rated 1200 V and 24 A) is estimated by measuring the turn-OFF delay. When the gate resistance is zero the sensitivity of the methodology is only 0.02 ns/°C, making the temperature estimation impossible. To increase the sensitivity the commutation has to be slowed down. In [36] the gate driver resistance is increased to  $150/300~\Omega$ , thus increasing the sensitivity by a factor of about 30/60. However, this cause also an increase of the switching losses. The proposed method uses an improved gate driver that slows down the turn-OFF only when the temperature estimation is needed. Power devices have thermal time constants of hundreds of ms, in turn it is not necessary to estimate their junction temperature at every commutation.

#### 2.2.2.4 Saturation Current

There is a well know dependency of the electron mobility with the temperature [37], so that is possible to use the saturation current as a TSEP [38], [39], [40], [41].

The MOSFET/IGBG is commanded close with a  $V_{GS}/V_{GE}$  that is slighter higher than the threshold voltage and the resulting saturation current  $(i_{DS}/i_{CE})$  is measured. This method, unlike others, is easy to implement because it does not require to measure currents in a very short timescale. However it can not be used during the normal operations of a converter. In turn, alternative solutions have been developed. In [42] the saturation current of a SiC MOSFET is dynamically measured. During the turn-ON the device go trough a saturation region.  $i_{DS}$  and  $V_{GS}$  are measured during the turn-ON commutation, this permits to obtain an estimation of the junction temperature during the normal converter operations. This solution can be used in hard switching converter, however it is necessary to measure voltages and currents in a very short timescale.

#### 2.2.2.5 di/dt

The turn-ON commutation current slope can be measured and used as a TSEP [33], [35], [31]. This technique can be used with converters operating under hard switching conditions. However, it requires to measure commutation currents in a very short timescale.

#### 2.2.2.6 High Current Injection

During the conduction state of the device, its current and its voltage drop  $(v_{DS} \text{ in case of MOSFET or } v_{CE} \text{ in case of IGBT}) \text{ can be measured. For a fixed}$ current, the  $V_{ON}$  of the device depends on its junction temperature. However, the correlation between the voltage drop and the junction temperature is not linear. This TSEP can be used for IGBTs [43], [44] and for MOSFETs [45], [31]. In [45] a Si MOSFET DC/DC hard switching converter is presented. The  $V_{ON}$  and the  $i_{DS}$ of each MOSFETs are measured during the normal operations of the converter and the conduction resistance  $R_{ON}$  is computed. The obtained  $R_{ON}$  is then compared to a look-up table and used to estimate the junction temperature. According to [46]  $R_{ON}$  is antiproportional to the mobility of electrons  $\mu_n$ . The relation between the  $R_{ON}$  and the temperature is expressed in (2.4), (2.5) and (2.6), where q is the elementary charge,  $N_D$  is the donor concentration and T is the temperature in Kelvin. Equation (2.6) shows that the  $R_{ON}$  variation with the temperatue can be represented using an exponential equation. However this is just an approximated model where the resistance of the channel is neglected, a good model should also take into account the variation of the ON-state resistance with the current. A SiC MOSFET compared to a Si MOSFET will present a smaller sensitivity of  $R_{ON}$ with the temperature. In the particular case shown in [45] the exponent of the equation is equal to 2.6 however this value can change depending on the MOSFET characteristics.

$$R_{ON} \propto \frac{1}{q\mu_n(T)N_D} \tag{2.4}$$

$$\mu_n(T) = \mu_n(300K) \left(\frac{T}{300K}\right)^{-x}$$

(2.5)

$$R_{ON} \propto \left(\frac{T}{300K}\right)^x \tag{2.6}$$

In [45] the dependency of the  $R_{ON}$  with the temperature is neglected and only the variation of the resistance with the temperature is considered, this decrease the precision of the estimation. As shown in Table 2.1 the  $R_{ON}$  is composed by the sum of different resistances, and only the n<sup>-</sup>-layer follows the temperature dependency shown in (2.6). The impact of the other resistances is small if compared to the resistance of the n<sup>-</sup>-layer, however the other resistances have a different thermal coefficient. Moreover, the different components of the device can be at different temperatures. E.g. The bonding wires during the normal operations of the device are likely to be at lower temperature respect to the junction and their resistance will vary according to the temperature with a coefficient that depends on the material. It is not enough to just measure the  $R_{ON}$  to estimate the junction temperature, it is necessary to have a look-up table that permits to correlate the two quantities. Usually the datasheet of the component provides  $R_{ON}(T)$ , however this value is usually based on the worst case scenario and the temperature estimation can became extremely inaccurate. An alternative solution is to characterize the component with the use of dedicated equipment like a curve tracer and then to place the component in the converter. This solution is not practical and the variation of the contact resistance due to the mounting process can lead to errors (few m $\Omega$  are enough to have tens of degrees of error on temperature estimation).

Table 2.1: Composition of the  $R_{ON}$  of a 600 V MOSFET [47].

| Package              | 0.5 %  |

|----------------------|--------|

| Source Layer         | 0.5~%  |

| Channel              | 1.5 %  |

| Accumulation Layer   | 0.5~%  |

| n <sup>-</sup> Layer | 96.5 % |

| Substrate            | 0.5~%  |

#### 2.2.2.7 TSEPs Conclusions

The main TSEPs have been analysed, however other solutions are feasible. TSEPs based techniques can be used conjoint with a thermal model to increase

precision and reliability. Temperature estimation by TSEPs is today the most promising way to carry out measurements on packaged devices. Most of the described techniques have been developed in a laboratory environment and they are not suitable to be implemented on a commercial application. This thesis is focused on the estimation of the junction temperature for commercial applications. To estimate the junction temperature two problems need to be solved:

- TSEP measurement.

- TSEP calibration.

Measuring voltages and currents in a very short timescale can be challenging. This is the case of TSEP techniques that require to measure turn-OFF delays, turn-ON delays and current slopes (di/dt). For "slow" devices like IGBTs under certain conditions is possible to measure these quantities. However, in wide bandgap devices it is not realistic to suppose to measure currents and voltages that vary in tens of nanosecond with a discretization of less than one nanosecond. These measures are very sensitive to the parasitics and require the use of dedicated laboratory equipments like oscilloscopes and measurements probes. A possible work around is to slow down the commutations of the device, the drawback is the loss of efficiency that in most of the cases is unacceptable. Alternatively, the commutation can be slowed down only when the estimation of the junction temperature is needed as shown in [36]. This requires to design custom gate drivers and to modify the modulator. E.g. If the commutation is slowed down the death time need to be increased.

Techniques based on the injection of a low calibrated current do not require to measure currents and voltages in a very short timescale. This techniques can be used with IGBTs and diodes during the forward conduction or with MOSFETs during the interdiction state to measure the threshold voltage of the body diode. However, in most of switching converters, it is not possible to inject a calibrated current in the device during the normal operations. E.g. In a two level switching converter using power MOSFETs, it is not possible to inject a calibrated current between source and drain during the interdiction state of the device (the device is subject to the full DC-link voltage).

Techniques that require the measure of the saturation current can be used during the commutation of the device or during the conduction state. The first solution can be implemented in hard switching converters but like the previous solutions requires to measure currents and voltages in a very short timescale. The second solution require to set a small voltage between gate and the source and then to measure the saturation current, this solution is not implementable in a classical two level converter.

Techniques that require to measure the voltage drop during the conduction of a high current are feasible with regards to the acquisition time. They can be used during the normal operations of a switching converter. To obtain a temperature estimation is necessary to calibrate the estimator, depending on the used technique the process can be more or less complex. TSEPs that have a linear temperature dependency are easier to calibrate, because they require to test the device only in a limited number of points.

Usually, the calibration process is carried out in a controlled environment with the use of calibrated equipments. To obtain a precise temperature estimation every device needs to be calibrated separately.

TSEPs are often compared in terms of sensitivity [28], [31], however in the author's opinion these comparisons can be misleading. E.g. measuring a voltage with an error of 1% can be easy if the measurement window is on the order of µs but can be hard if the measurement window is on the order of ns. In turn, the main TSEPs based techniques have not been compared in terms of sensitivity.

#### 2.2.3 Proposed Technique Based on $V_{ON}$ Sampling

The main objective of this thesis is the junction temperature estimation for SiC power MOSFET modules with focus on industrial applications (power switching converters, either DC/AC or DC/DC). The proposed technique was present in [48], [49]. It utilizes the ON-state voltage measurement with high current injection illustrated in the section earlier. Starting from such well know TSEP based technique, normally used in a laboratory environment, innovative solutions are proposed in order to be able to obtain a reliable estimation of the junction temperature also in a real case scenario.

After an initial commissioning of the power module performed directly on the converter, the look-up table  $\theta_J(I_{DS}, V_{ON})$  is built. This is then used for the on-line estimation and limitation of the junction temperature.

The strengths of the proposed methodology are:

- The TSEP calibration can be run directly on the converter without additional laboratory equipment like oscilloscopes and curve tracers.

- The hardware modifications are minor and easy to implement.

- The additional circuitry is low cost and off the shelf.

- Temperature detection does not affect the operation of the converter.

- Temperature detection has a fast dynamic response and high sampling rate.

- No complex computation is required.

Fig. 2.2 represents the principle of operation of the proposed  $V_{ON}$  based technique.

Fig. 2.2: Temperature estimator functional block using  $\theta_J(V_{ON},i_{DS})$ .

## Chapter 3

## **Proof of Concept Demonstrator**

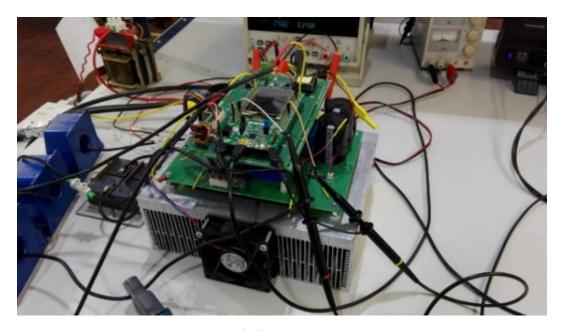

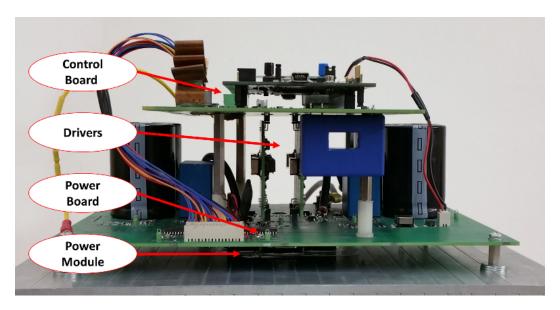

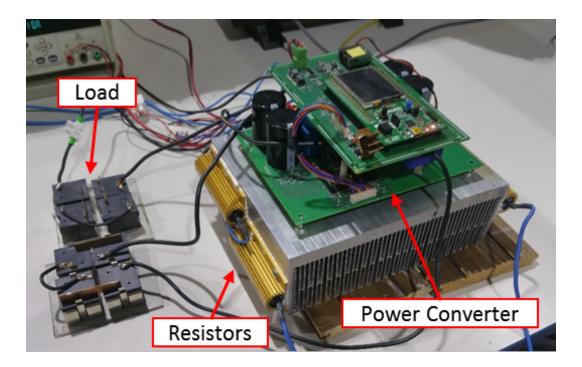

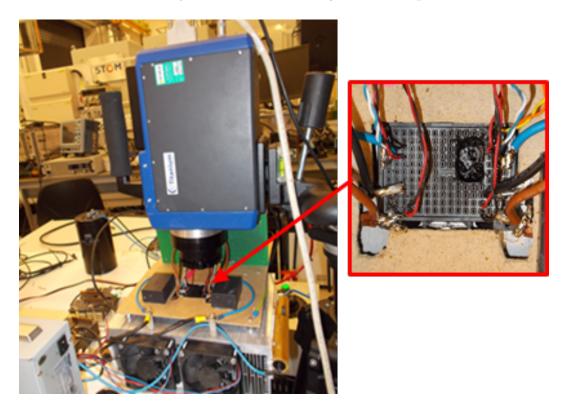

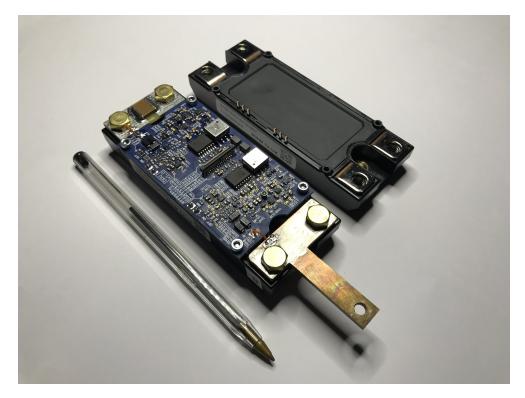

Fig. 3.1: Proof of concept demonstrator.

To validate the proposed methodology a proof of concept test rig has been designed. The converter shown in Fig. 3.1 makes use of a power module containing four SiC MOSFETs connected in H-bridge configuration. The power module operates under hard switching conditions and the junction temperature of one of the four MOSFETs is on-line estimated at every PWM period. The demonstrator permits to validate the proposed methodology while emulating real working conditions.

#### 3.1 Power Modules Under Test

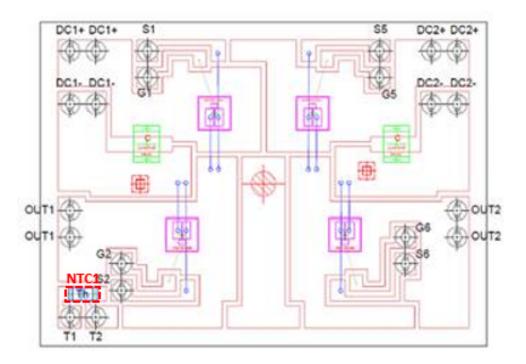

Four SiC power MOSFETs are contained in a custom "emipak-2B" package, produced by Vishay, shown in Fig. 3.2. The internal layout of the power module is shown in Fig. 3.3. The four MOSFETs are in purple. The blue label "Th" indicates the embedded NTC sensor used to measure the DBC temperature, here labelled NTC1. The two internal capacitors added to minimize the power loop stray inductance are depicted in green.

Like in most of the semiconductors used for power electronic applications, the source signal pins are separated from the source power pins. The same package with the same configuration is provided by Vishay with dies made by different manufacturers. Two different dies from two different manufacturers have been tested in this thesis.

Fig. 3.2: Power module package.

Fig. 3.3: Layout of power module (courtesy of Vishay Semiconductor Italiana). In green the two internal local capacitors. In blue the internal NTC thermistor (label "Th"), for measurement of case temperature.

The ratings of the two power modules under test are reported in Table 3.1 and Table 3.2. Both modules have a nominal breakdown voltage of 1200 V and a maximum junction temperature of 175 °C. The maximum allowable DC current for a case temperature of 80 °C is 26 A for module#1 and 19 A for module#2. The typical conduction resistance for a current of 20 A and a junction temperature of 25 °C is 71 m $\Omega$  for module#1 and 78 m $\Omega$  for module#2. The  $R_{ON}$  for a drain current of 20 A and a junction temperature of 25 °C is 105 m $\Omega$  for module#1 and 103 m $\Omega$  for module#2. Even if the nominal current of the two modules is similar the dies have been made by different producers that use a different manufacturing process. The two dies show a different variation of the  $R_{ON}$  with the temperature as shown in Section 4.5. Furthermore the two dies have different switching characteristics as shown in Section 3.4.2.

Table 3.1: Power Module, type#1 (from datasheet).

| Rated Current (T <sub>case</sub> =80°C)                      | 26 A             |

|--------------------------------------------------------------|------------------|

| Breakdown Voltage                                            | 1200~V           |

| $ m R_{ON}(	heta_j{=}25^{\circ}C,I_{DS}{=}20A)$              | $71 m\Omega$     |

| $\mathrm{C_{internal}}$                                      | $2 \times 47 nF$ |

| Maximum Junction Temperature                                 | 175 °C           |

| $C_{iss} (V_{DS} = 400 V, f = 1 MHz)$                        | $1700 \ pF$      |

| ${ m C_{oss}}~({ m V_{DS}}{=}400{ m V},~{ m f}{=}1{ m MHz})$ | $130 \ pF$       |

| $C_{rss} (V_{DS} = 400 V, f = 1 MHz)$                        | 25 pF            |

Table 3.2: Power Module, type#2 (from datasheet).

| Rated Current (T <sub>case</sub> =80°C)                               | 19 A             |

|-----------------------------------------------------------------------|------------------|

| Breakdown Voltage                                                     | 1200~V           |

| $ m R_{ON}(	heta_j{=}25^{\circ}C,I_{DS}{=}20A)$                       | $78 \ m\Omega$   |

| $C_{internal}$                                                        | $2 \times 47 nF$ |

| Maximum Junction Temperature                                          | $175~^{\circ}C$  |

| ${ m C_{iss}} \; ({ m V_{DS}}{=}1000  { m V},  { m f}{=}1  { m MHz})$ | 950 pF           |

| $C_{oss} (V_{DS} = 1000 V, f = 1 MHz)$                                | 80 pF            |

| $C_{rss} (V_{DS} = 1000  V,  f = 1  MHz)$                             | 7.6 <i>pF</i>    |

#### 3.2 Regenerative Test Operation

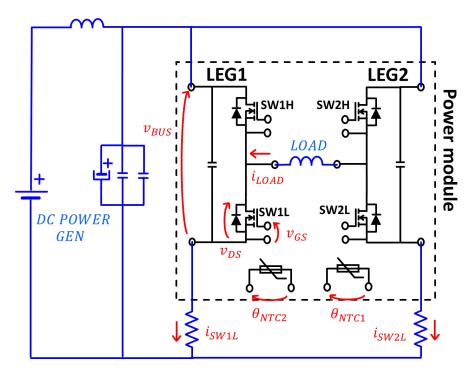

The schematic of the power section of the proposed test rig is shown in Fig. 3.5. The internal part of the power module is represented in black while external connections and components are represented in blue. The quantities shown in red are measured online at each PWM period.  $\theta_{NTC1}$  represents the measure of the embedded NTC thermistor while  $\theta_{NTC2}$  represents the measure of a second thermistor that has been added to validate the proposed junction temperature estimation technique as explained in Section 4.4.2. The MOSFET SW1L is fully monitored to estimate its junction temperature, it will be called also the **switch under test**. The voltage drop  $(v_{DS})$  during the conduction state and the voltage between gate and source  $(v_{GS})$  of the switch under test are measured for each PWM cycle. The bus voltage  $(v_{BUS})$ , the load current  $(i_{LOAD})$  and the switches currents  $(i_{SW1L})$  and  $i_{SW2L}$  are also measured.  $i_{LOAD}$  is measured through a closed loop hall sensor while  $i_{SW1L}$  and  $i_{SW2L}$  are measured through two shunt resistors that permit to achieve a higher measurement bandwidth. Due to the presence of the power module internal

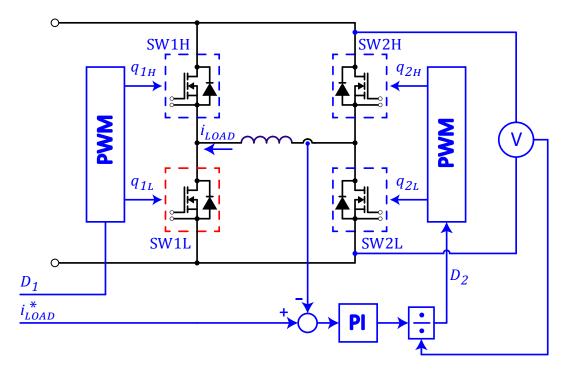

capacitance, the shunt resistors can't measure exactly the current in the switches especially during the commutations. However when the turn-ON transitory is over, the current flowing in the internal capacitances respect to the current flowing in the shunt resistors is negligible. The power module is connected in H-bridge configuration and it is supplying a purely inductive load. The current in the LOAD is closed-loop controlled by LEG2 while LEG1 is open loop controlled at a fixed duty-cycle to emulate a constant voltage source. The control schematic is shown in Fig. 3.4.

The average current in the switch under test is:

$$I_{SW1L} = I_{LOAD} (1 - D_1) (3.1)$$

The instantaneous current in the switch under test is:

$$i_{SW1L}(t) = i_{LOAD} \cdot q_{1L} \tag{3.2}$$

This configuration permits to mimic real operating conditions while absorbing from the DC-link just a fraction of the output power. The DC power source needs to provide only the losses of the system, this permits to test high current power modules without the need of an expensive high current power supply. Moreover this configuration permits to do some considerations on the efficiency of the system by measuring only the input power to the DC-link.

Fig. 3.4: Control schematic. LEG1 is open-loop controlled while LEG2 is used in closed-loop current control.

Fig. 3.5: Schematic diagram of the proposed setup: red quantities are measured online.

# 3.3 3D Layout

Fig. 3.6 shows the 3D-layout of the test rig. From top to bottom, the control board, the two driver boards, the power board, the power module and part of the heatsink are visible. The heatsink is better visible in Fig. 3.1. This arrangement was chosen to keep the gate driver circuitry and the measurement circuitry as close as possible to the pins of the power module. In turn, this layout minimizes the parasitic inductance of the gate-driver circuitry.

Fig. 3.6: Overview of the proposed setup.

#### 3.3.1 Control Board

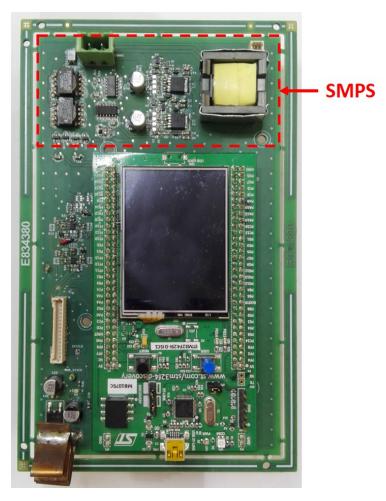

The control board houses the development board STM32F429-Discovery by STMicroelectronics. The development board comes with the STM32F429ZI microcontroller, embedding an ARM M4-core with clock frequency up to 180 MHz. This microcontroller is meant for industry applications. The Discovery board houses also a 64 Mbit SDRAM memory used as a buffer during PC communications and a debugger/programmer interface (ST-LINK/V2) provided by STMicroelectronics. The choice of using a development board permitted to save time and money when designing the PCB. The control board houses the closed-loop Hall effect current transducer used to closed-loop control  $i_{LOAD}$  as shown in Fig. 3.5. The signal coming from the current sensor and the embedded NTC1 are sampled using the ADCs of the microcontroller.

A 100 kHz SWPS (Switched Mode Power Supply) is used to supply an high frequency bus. Such high frequency bus provides insulated power supply to the gate-drive circuitry and to the measurement systems.

Fig. 3.7: Overview of the control board.

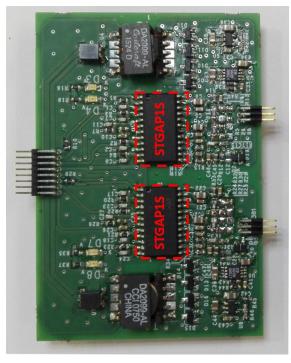

#### 3.3.2 Driver Boards

Two driver boards, one for each leg of the module are present. Each driver board contains two independent STGAP1S gate drivers. The STGAP1S is a isolated, single gate-driver with a output current capability of 5 A and common mode transient immunity of  $50\,\mathrm{kV/\mu s}$ . The driver output is rail-to-rail and can provide negative voltages. The SiC MOSFETs under test are driven by a  $V_{GS}$  ranging  $+20\,\mathrm{V}$  and  $-5\,\mathrm{V}$ . The device can be programmed and monitored through an SPI line. Advanced protections are available such as two level turn-OFF, Miller clamp, desaturation detection, 2-level turn-OFF,  $v_{DS}$  over voltage protection. The ability to program via SPI the protection threshold levels can be useful when different devices are tested. E.g. When a different power module is tested, it is possible to modify the level of intervention of the desaturation protection. Insulated supply is provided by the HF SMPS as said.

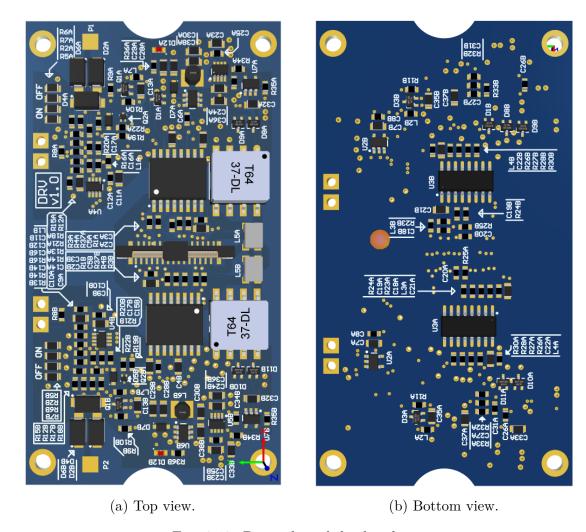

(a) Top view.

(b) Bottom view.

Fig. 3.8: Overview of the driver board.

Table 3.3: STGAP1S main features.

| Maximum isolation working voltage | 1500 V          |

|-----------------------------------|-----------------|

| Maximum transient overvoltage     | 4000 V          |