Doctoral Dissertation Doctoral Program in Computer and Control Engineering (31<sup>th</sup>cycle)

# Digital Design Techniques for Dependable High Performance Computing

By

Sarah Azimi

\*\*\*\*\*

#### Supervisor(s):

Prof. Luca Sterpone

#### **Doctoral Examination Committee:**

Prof. Fernanda.Lima Kastensmidt., Referee, Università federale del Rio Grande do Sul

Prof. Luis.Entrena, Referee, Università Carlos III

Prof. Otmane.Ait Mohamed, University of Concordia

Prof. Monica. Alderighi, Istituto di Astrofisica Spaziale

Prof. Stefano.Di Carlo, Politecnico di Torino

Politecnico di Torino

2019

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Sarah Azimi 2019

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). To my Mum and Dad, the hidden strength behind my every success.

### Acknowledgements

I would like to acknowledge all the people who support me and encourage me to accomplish my Ph.D thesis.

Many thanks goes to Prof. Luca Sterpone for providing me the opportunity to pursue my research activity in the CAD group and for his great support and generous help over the three pleasant years of my Ph.D. I would like to thank Dr. Boyang Du for his fundamental support during my research activity. I also would like to thank all the people I had the chance to have the collaboration with, specially David Merodio Codinacs From European Space Agency for all his support during my Ph.D. I also acknowledge Prof. Matteo Sonza for his fruitful encouragement during my Ph.D program. I would like to thank all my colleague in the CAD group and Lab3 for all the pleasant time we spent together.

Special thanks goes to Mariangela Saracco for her great support and effort in all the steps.

### Acknowledgements

- To my Mum and Dad who scarify their lives to give me a better life.

- To Luca, my best friend, who taught me about dreams and how to catch them.

- To Samira, my sister, who taught me that the light is always there.

- To Hannah, whose brought joy and hope to our lives.

- To Boyang who showed me how it feels to have the support of a brother.

- To Antonio who reminds me how lucky I am.

- To CAD & Reliability Group which provides me the opportunity to grow and build a bright future.

- To Lab3 which ties my life with amazing people.

### Abstract

The overall goal of my doctoral research activity is oriented in development of high performance computing design techniques for high reliability of digital circuits. One of the most critical environment aspect that could reduce the reliability of modern VLSI technologies used for high performance computing is radiation. When a set of radiation particle interact within the electronic systems by an exchange of energy, several kinds of effects can be observed. The impact of radiation effects on electronic devices can cause a misbehavior on the functionality of the circuit. In order to apply strategies and techniques to tolerate these faults and errors, these effects must be analyzed in details. Considering high frequency and smaller size of recent technologies, the sensitivity of High Performance Computing toward radiation is expected to be higher. Therefore, having more resilient mitigation technologies is more relevant and necessary, which is the focus of my research activity.

Radiation-induced effects can lead different effects depending on the location and time of the incident. If the effects of radiation incident lasts for a short period of time, it is known as a transient fault. While, if the effects last for a longer duration, it is known as a permanent fault. Therefore, my PhD dissertation is divided into two main parts. The first part as the main part is dedicated to the transient fault, mostly focusing on Single Event Transient while the second part is dedicated to the more permanent fault such as Micro Single Event Latch-up and Total Ionizing Dose.

Considering Single Event Transient as the golden part of my research, it covers different phases of this phenomena from the generation until the mitigation. The first phase is dedicated to the physical modeling of these effects and evaluating the impact of the radiation environment profile on the generated SET pulse. The second phase is devoted to develop tools and algorithms for analyzing and predicting the behavior of the effected device. As a last phase, the developed physical model and performed analysis have been the golden keys to propose an efficient mitigation solution for

robustness of the developed system against this phenomena. The proposed mitigation solution has been knows as the first method able to filter Single Event Transient pulses with zero-timing overhead. These methodologies have been applied to modern High Performance Computing technologies with high frequency and smaller size which lead to more critical condition for Single Event Transient effect.

This comprehensive proposed flow for analyzing and mitigating Single Event Transient has been applied to several industrial projects such as EUCLID space mission project with the goal of monitoring the dark space which the lunch planned for 2020 carrying by European Space Agency. The developed SET analysis and mitigation work-flow has been part of the handbook *Space Product Assurance Techniques for Radiation Effects Mitigation in ASICs and FPGAs handbook*, published by European Space Agency. Moreover, the developed set of tools has been known as the *Best EDA Tool for improving design automation for integrated circuits and systems* by IEEE Council on Electronic Design Automation.

However, as a part of my research activity, not only I focused on the Transient effects, but I dedicated the second part of my dissertation to the evaluation of permanent effects such as Single Event Latch-up and total Ionizing Dose. The second effect I focused on is Single Event Latch-up which is one of the major reliability concerns for VLSI device applied in safety critical applications. The reduction of the circuit feature size and operating voltage levels are leading to a new kind of latch-up called micro Single Event Latch-up. Single Event Latch-up tends to occur near the input/output terminals of logic gates while micro Single Event Latch-up may occur at various locations between layers. One of my main research contribution is to propose a first 3D model for describing the 3D physical layout description of the design including the interconnection resources and logic versatile. This 3D layout description leads to analyze the sensitivity of the sub-micron circuitry to Micro Single Event Latch-up phenomena with respect to the layout, depth, size and density of the design. This methodology is considered as the first one applicable to large industrial designs.

Bench-marking technologies are becoming increasingly attractive since their configuration memory is almost immune to Single Event Upset. However, applied in mission critical application, especially long term missions, the FPGA devices are subject to cumulative ionizing damage, known as Total Ionizing Dose. Total Ionizing Dose may affect the FPGA, causing performance degradation and eventually

permanent damage. Therefore, I dedicated part of my research activity to propose a physical model of Total Ionizing Dose effect in order to analyze the Total Ionizing Dose effect on recent modern technologies.

## **Table of contents**

| Li | st of l | Figures       |                                                   | xiii |

|----|---------|---------------|---------------------------------------------------|------|

| Li | st of ' | <b>Fables</b> |                                                   | XX   |

| 1  | Intr    | oductio       | n on Radiation Effect on Modern VLSI Technologies | 1    |

|    | 1.1     | Radiat        | ion characteristics                               | 3    |

|    | 1.2     | Moder         | n VLSI Technologies                               | 6    |

|    |         | 1.2.1         | Field Programmable Gate Array                     | 6    |

|    |         | 1.2.2         | GPGPU                                             | 9    |

|    |         |               |                                                   |      |

| I  | Sin     | gle Ev        | ent Transient                                     | 12   |

| 2  | Basi    | ic Mech       | anism of Single Event Transient                   | 14   |

|    | 2.1     | From 1        | radiation particle to voltage pulse               | 14   |

|    |         | 2.1.1         | Basic mechanism of Single Event Transient         | 15   |

|    |         | 2.1.2         | SET life-cycle inside the device                  | 16   |

| 3  | Ana     | lysis of      | Single Event Transient                            | 18   |

|    | 3.1     | SET C         | haracterization                                   | 18   |

|    |         | 3.1.1         | Electrical SET Injection                          | 19   |

|    |         | 3.1.2         | SET propagation characterization                  | 20   |

|   |     | 3.1.3    | SET characterization test setup on Flash-based FPGAs      | 22 |

|---|-----|----------|-----------------------------------------------------------|----|

|   |     | 3.1.4    | SET characterization test setup on SRAM-based FPGAs       | 31 |

|   |     | 3.1.5    | Research advancements on SET characterization             | 40 |

|   | 3.2 | On the   | prediction of SETs                                        | 40 |

|   |     | 3.2.1    | SET physical dynamic simulation model                     | 41 |

|   |     | 3.2.2    | SET prediction methodology                                | 45 |

|   |     | 3.2.3    | Prediction of SET on Flash-based FPGAs                    | 47 |

|   |     | 3.2.4    | Research advancement on the prediction of SETs            | 48 |

|   | 3.3 | Single   | Event Transient Analyzer - SETA                           | 50 |

|   |     | 3.3.1    | SET behavior in combinational logic                       | 51 |

|   |     | 3.3.2    | SET behavior in routing interconnections                  | 52 |

|   |     | 3.3.3    | Integration of SETA with commercial tools                 | 53 |

|   |     | 3.3.4    | SETA on Flash-based FPGAs                                 | 57 |

|   | 3.4 | Evalua   | tion of Transient Errors in GPGPUs                        | 59 |

|   |     | 3.4.1    | The proposed environment                                  | 61 |

|   |     | 3.4.2    | Fault tolerance design methods on GPGPU                   | 67 |

|   |     | 3.4.3    | Experimental results                                      | 77 |

|   | 3.5 | Conver   | rgence Single Event Transient Analyzer - CSETA            | 84 |

|   |     | 3.5.1    | SET pulse behavior at convergence point                   | 84 |

|   |     | 3.5.2    | Integration of CSETA with commercial tools                | 87 |

|   |     | 3.5.3    | C-SETA on Flash-based FPGAs                               | 90 |

|   |     | 3.5.4    | Research advancement on Single Event Transient Analyzer . | 93 |

| 4 | Мін | action ( | of Single Event Transient                                 | 94 |

| 4 |     | 0        |                                                           |    |

|   | 4.1 |          | Gate mitigation                                           | 95 |

|   |     | 4.1.1    | SET propagation analysis                                  | 96 |

|   |     | 4.1.2    | Netlist filter mitigation insertion                       | 97 |

5

|      | 4.1.3     | Physical implementation                                           |

|------|-----------|-------------------------------------------------------------------|

|      | 4.1.4     | Guard Gate Mitigation on Rad-Hard RTG4 Flash-based FPGAs101       |

| 4.2  | SET M     | Itigation by adding Charge Sharing logics on Flash-based          |

|      | FPGA      |                                                                   |

|      | 4.2.1     | Proposed design flow                                              |

|      | 4.2.2     | Experimental results                                              |

|      | 4.2.3     | Research advancement on mitigation of Single Event Transient112   |

| Indu | ıstrial A | Application 114                                                   |

| 5.1  | Radiat    | ion Test: Ultra High Energy Heavy Ion Test Beam on Xilinx         |

|      | Kintex    | -7 SRAM-based FPGA                                                |

| 5.2  | Backg     | round                                                             |

| 5.3  | Device    | and Design Under the Test                                         |

| 5.4  | Monito    | oring setup                                                       |

| 5.5  | UHE H     | Heavy Ion beam                                                    |

| 5.6  | Radiat    | ion Test Data                                                     |

|      | 5.6.1     | Error rate analysis                                               |

|      | 5.6.2     | Observation of SEMU                                               |

| 5.7  | EUCL      | ID Space Mission                                                  |

|      | 5.7.1     | What is EUCLID?                                                   |

|      | 5.7.2     | Analysis of EUCLID original EUCLID netlist sensitivity to<br>SET  |

|      | 5.7.3     | Mitigating the EUCLID design netlist                              |

|      | 5.7.4     | Analysis of EUCLID mitigated netlist sensitivity to SET phenomena |

| II | Fr    | om Tr     | ansient to Permanent                                  | 137   |

|----|-------|-----------|-------------------------------------------------------|-------|

| 6  | Mic   | ro Singl  | le Event Latch-up                                     | 139   |

|    | 6.1   | From S    | SEL to Micro SEL                                      | . 140 |

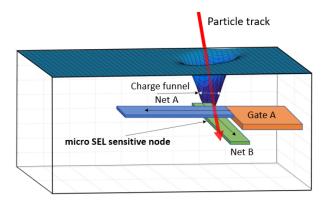

|    |       | 6.1.1     | Micro Single Event Latch-up Analysis                  | . 142 |

|    |       | 6.1.2     | Experimental Results                                  | . 147 |

|    |       | 6.1.3     | Research advancement on Micro Single Event Latch-up . | . 150 |

| 7  | Tota  | ıl Ionizi | ng Does                                               | 152   |

|    | 7.1   | The de    | eveloped environment                                  | . 153 |

|    |       | 7.1.1     | Background on Versatile architecture                  | . 154 |

|    |       | 7.1.2     | Total Ionizing Dose (TID) Heatmap generation          | . 155 |

|    |       | 7.1.3     | Hitlist generation                                    | . 157 |

|    |       | 7.1.4     | SDF Instrumentation                                   | . 159 |

|    |       | 7.1.5     | Simulation Execution                                  | . 159 |

|    | 7.2   | Experi    | mental Results                                        | . 160 |

|    |       | 7.2.1     | Experimental Setup                                    | . 162 |

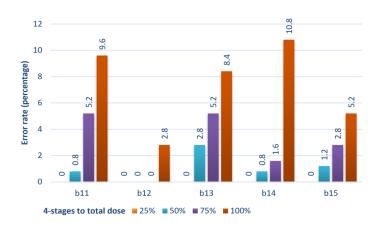

|    |       | 7.2.2     | Error Rate Reports                                    | . 164 |

|    |       | 7.2.3     | Research advancement on Total Ionizing Does           | . 165 |

| Re | feren | ices      |                                                       | 167   |

| Ар | pend  | lix A R   | Research Achievements                                 | 174   |

# **List of Figures**

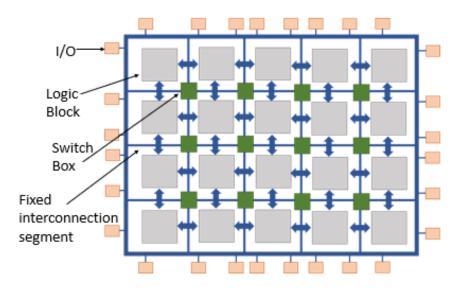

| 1.1 | FPGA General Architecture                                                                                                                                                                   | 7  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

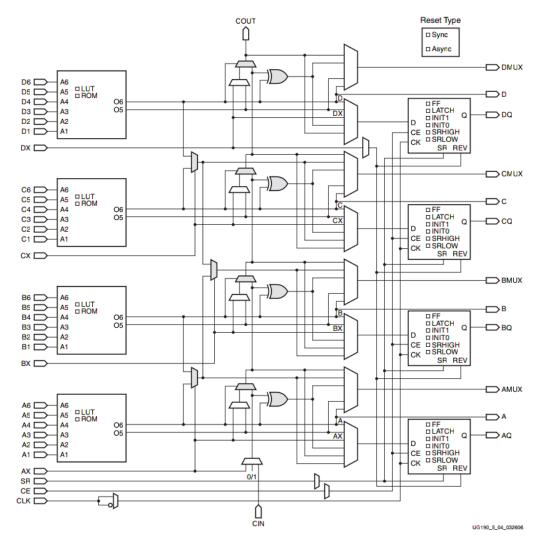

| 1.2 | Logic Block (SLICEL) diagram from Virtex-5 device of Xilinx                                                                                                                                 | 8  |

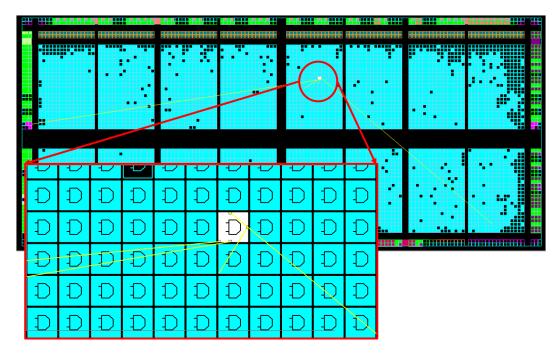

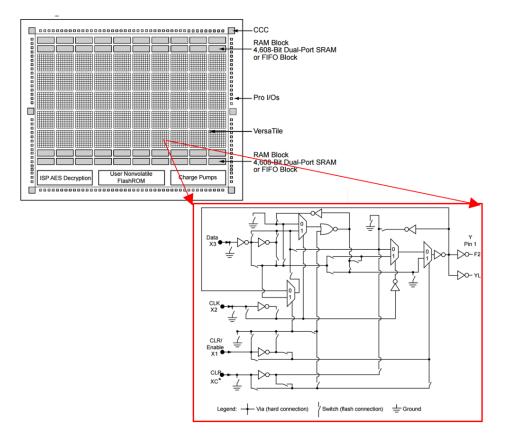

| 1.3 | A routed design mapped on ProASIC3 from Microsemi                                                                                                                                           | 9  |

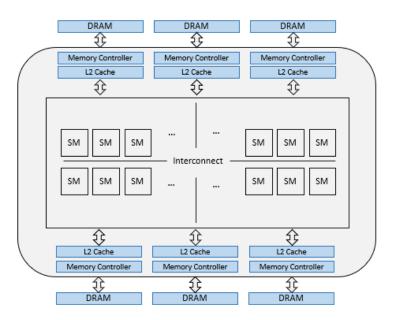

| 1.4 | Contemporary GPU architecture                                                                                                                                                               | 10 |

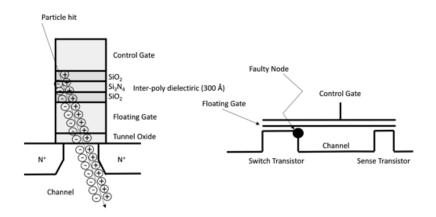

| 2.1 | Floating gate transistor layout in the 130 nm Flash-based FPGA and the correspondent sensitive node generating transient pulses                                                             | 15 |

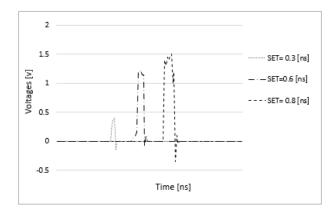

| 2.2 | Examples of transient pulses generated by our electrical fault injec-<br>tion platform and mimic heavy ions radiation particles hitting the<br>sensitive nodes of a 130nm Flash-based FPGAs | 16 |

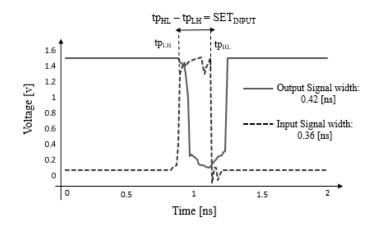

| 2.3 | Propagation of SET pulse through an Inverter with an input transition of 0-1-0                                                                                                              | 17 |

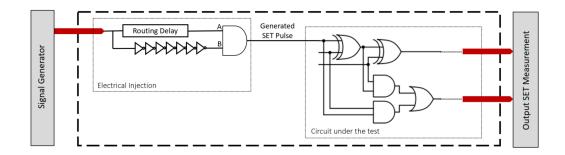

| 3.1 | The developed logic scheme of internal injection generation                                                                                                                                 | 20 |

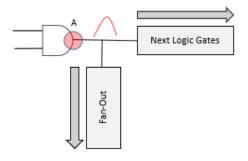

| 3.2 | A Logic sensitive node and the two observability methods: towards next logic gates and toward fan-out                                                                                       | 21 |

| 3.3 | Scheme of internal electrical pulse generator                                                                                                                                               | 22 |

| 3.4 | Logical scheme of the test- scenario 1                                                                                                                                                      | 24 |

| 3.5 | An overview of the placement layout- Scenario 1                                                                                                                                             | 25 |

| 3.6 | Propagation Induced Pulse Broadening- Scenario 1 (Source SET = 3.5 ns)                                                                                                                      | 25 |

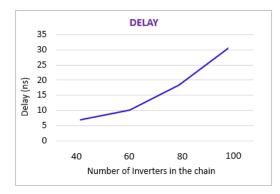

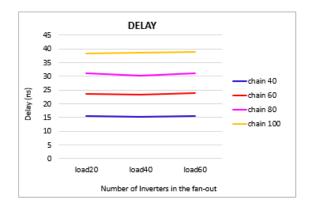

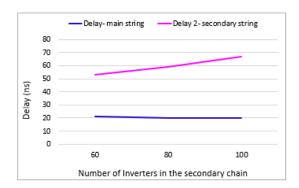

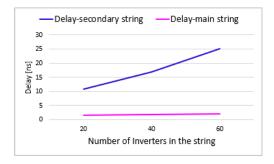

| 3.7 | Inverter chain delay- Scenario 1                                                                                                                                                            | 26 |

| 3.8  | Logical scheme of the test- Scenario 2                                                                                       | 26 |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | An overview of the placement layout- Scenario 2                                                                              | 27 |

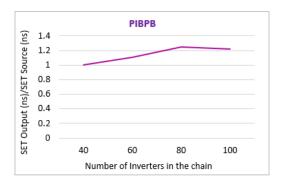

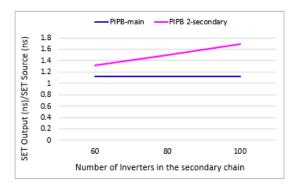

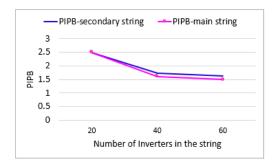

| 3.10 | Propagation Induced Pulse Broadening(PIPB)- Scenario 2 (Source<br>SET = 3.5 ns)                                              | 27 |

| 3.11 | Inverter chain delay- Scenario 2                                                                                             | 28 |

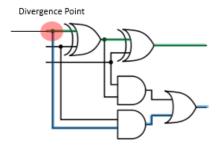

| 3.12 | Logical scheme of full adder by SET in the divergence point                                                                  | 28 |

| 3.13 | Conceptual scheme- third scenario                                                                                            | 29 |

| 3.14 | PIPB report- third scenario (Source SET = 3.5 ns)                                                                            | 29 |

| 3.15 | Delay report- third scenario                                                                                                 | 30 |

| 3.16 | Logical scheme of full adder affected by SET in the convergence point                                                        | 30 |

| 3.17 | Conceptual scheme- fourth scenario                                                                                           | 31 |

| 3.18 | PIPB report- fourth scenario (Source SET = $3.5 \text{ ns}$ )                                                                | 31 |

| 3.19 | Delay report- fourth scenario                                                                                                | 32 |

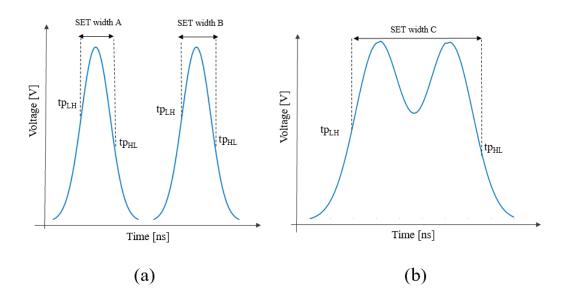

| 3.20 | An example of SET propagated through two convergence paths and generating: two independent SET pulse (a) and C-SET pulse (b) | 32 |

| 3.21 | Overview of the global analysis methodology for SRAM-based FPGAs                                                             | 34 |

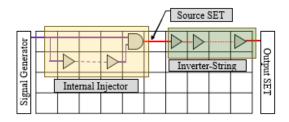

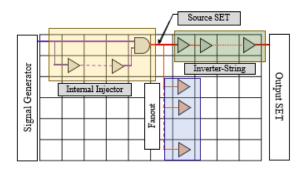

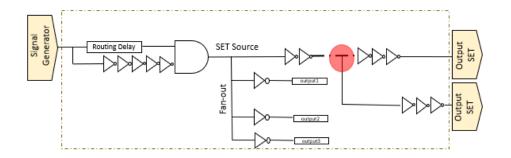

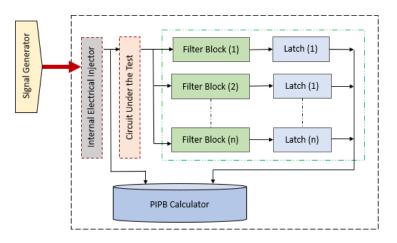

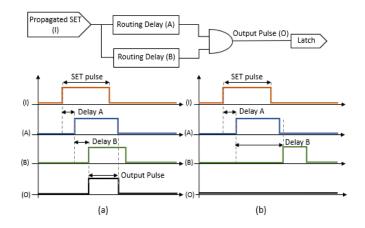

| 3.22 | Scheme of the SET pulse measurement circuit                                                                                  | 35 |

| 3.23 | Simulation results for injecting SET of 0.2 ns to a chain of 100 INVs                                                        | 37 |

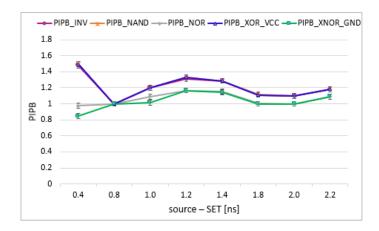

| 3.24 | Propagation pulse broadening for inverting gates- each chain in-<br>cludes 100 gates                                         | 38 |

| 3.25 | Propagation pulse broadening for non-inverting gates                                                                         | 38 |

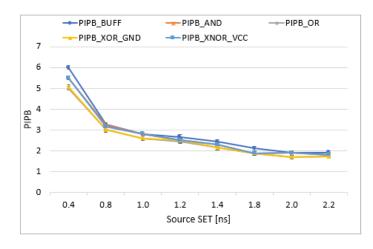

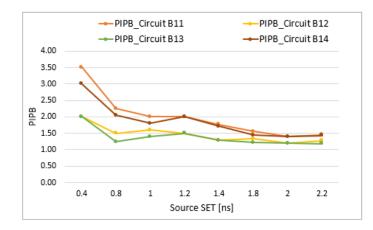

| 3.26 | Propagation pulse broadening for circuit benchmarks implemented<br>on SRAM-based FPGAs                                       | 40 |

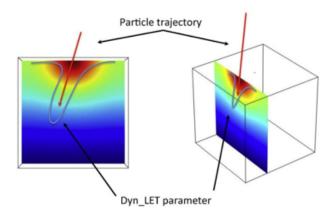

| 3.27 | An example of dynamic LET form on a generic empty layout in 2D and 3D                                                        | 42 |

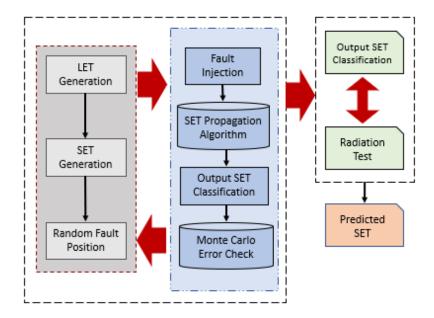

| 3.28 | The flow of the developed SET prediction method                                                                              | 45 |

| 3.29 | The flow of the developed SET prediction method                                                                              | 46 |

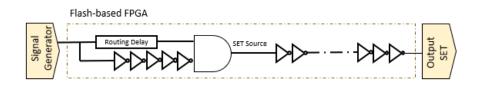

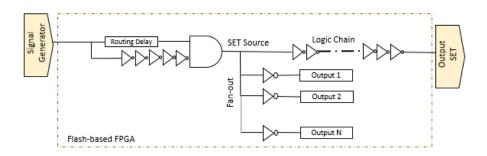

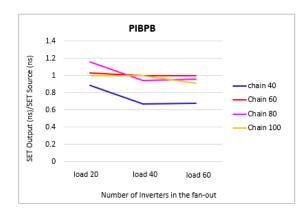

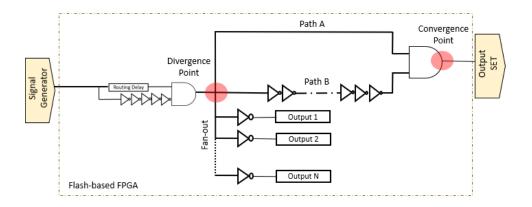

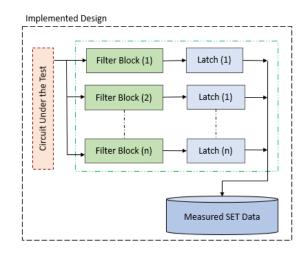

| 3.30 | Global scheme of the generated test setup                                                                                    | 47 |

| 3.31 | Scheme of the SET pulse measurement circuit.                                                                                                                                                                                                  | 48 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

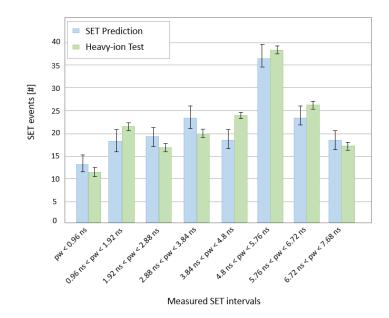

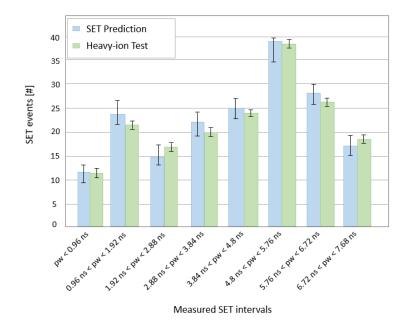

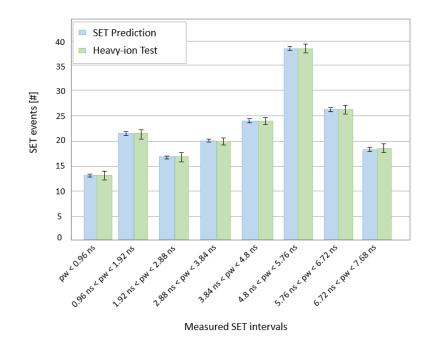

| 3.32 | Comparison between the SET prediction model and the heavy-ion test results. Standard error deviation at 10%                                                                                                                                   | 49 |

| 3.33 | Comparison between the SET prediction model and the heavy-ion test results. Standard error deviation at 1%.                                                                                                                                   | 49 |

| 3.34 | Comparison between the SET prediction model and the heavy-ion test results. Standard error deviation at 0.1%.                                                                                                                                 | 50 |

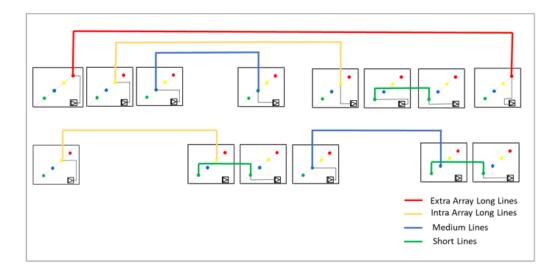

| 3.35 | The device routing topology of the Microsemi ProASIC3 family                                                                                                                                                                                  | 52 |

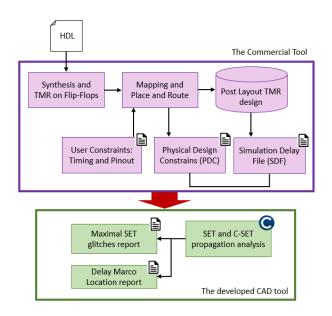

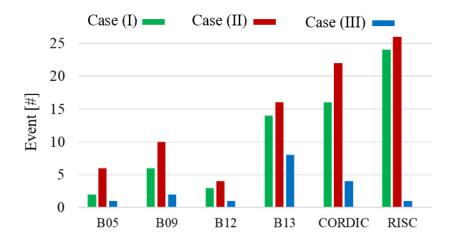

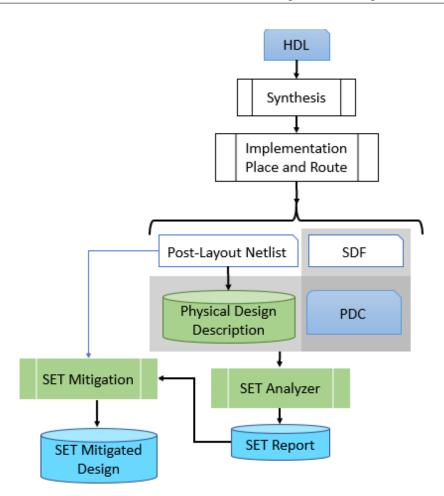

| 3.36 | The developed analysis flow for the accurate evaluation of SET effects on SoC implemented on Flash-based FPGA                                                                                                                                 | 54 |

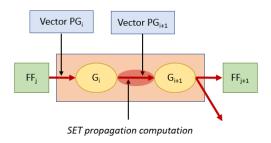

| 3.37 | The SET propagation approach: a voltage vector $PG_i$ is transformed<br>in a new vector $PG_{i+1}$ , considering the gate $G_i$ , the subsequent gate<br>$G_{i+1}$ and the routing segment between two logic gates                            | 55 |

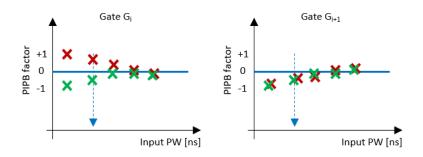

| 3.38 | The main core of the Propagation Induced Pulse Broadening (PIPB) calculation for the involved gates gate $G_i$ and the following gate $G_{i+1}$ (red X is representing the worst condition while green x is representing the best condition). | 56 |

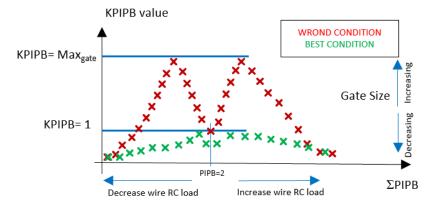

| 3.39 | Representation of the cumulative (KPIPB) on a generic couple of gates considered in a pulse traversing computation(red X is representing the worst condition while green x is representing the best condition).                               | 57 |

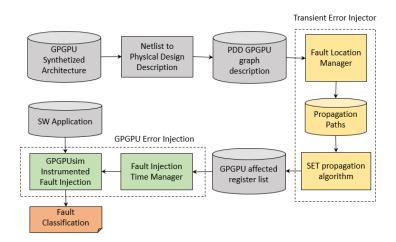

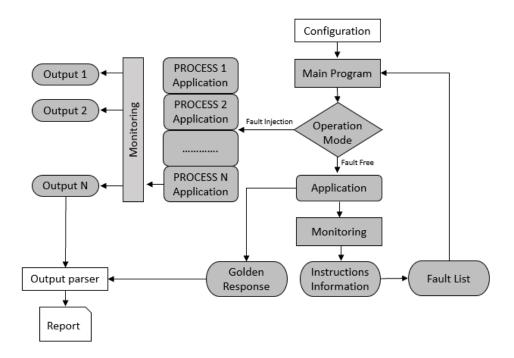

| 3.40 | The flow of the developed simulation-based fault injection for tran-<br>sient errors analysis on GPGPUs                                                                                                                                       | 62 |

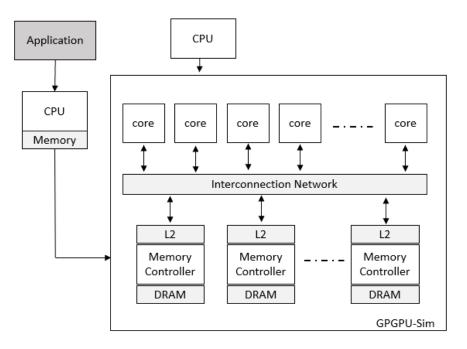

| 3.41 | GPGPU-sim modeled system.                                                                                                                                                                                                                     | 64 |

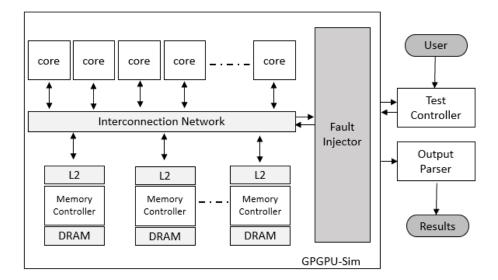

| 3.42 | Soft-error injection tool integration in the GPGPU-sim simulator                                                                                                                                                                              | 65 |

| 3.43 | Soft-error injection tool integration in the GPGPU-sim simulator                                                                                                                                                                              | 66 |

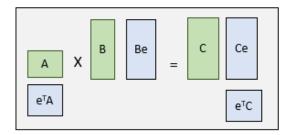

| 3.44 | The matrix multiplication kernel algorithm.                                                                                                                                                                                                   | 69 |

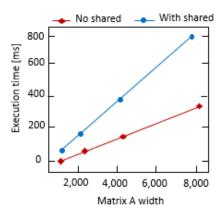

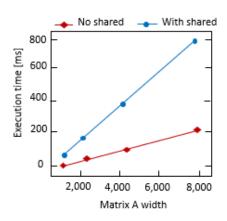

| 3.45 | Matrix product implementation comparison with and without using<br>the shared memory. The developed algorithm is using the shared<br>memory thus getting an improvement in performances.                                                      | 70 |

|      | memory mus gening an improvement in performances                                                                                                                                                                                              | 70 |

| The algorithm of matrix multiplication with DWC                                                                                                                                                   | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The algorithm of Matrix Multiplication with TMR-kernel                                                                                                                                            | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Additional buffers scheme needed for the check-sums for the matrix product ABFT method.                                                                                                           | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

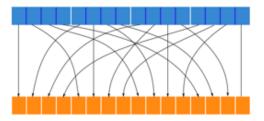

| Scheme of the shuffle operation on the FF network to the auxiliary network done in the global memory buffers                                                                                      | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FFT host algorithm executed on the share memory                                                                                                                                                   | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FFT propagation kernel algorithm executed on the shared memory .                                                                                                                                  | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The comparison of the FFT implementation with and without using the shared memory.                                                                                                                | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

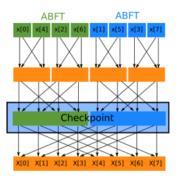

| The check-pointing scheme adopted integrating the ABFT algorithm.                                                                                                                                 | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The FFT algorithm with the ABFT mean based check pointing                                                                                                                                         | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

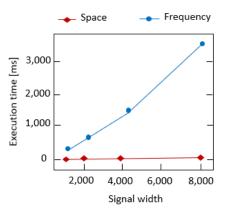

| Comparison of the execution times of the Sobel operator imple-<br>mented in Frequency (blue line) and in space (red line)                                                                         | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

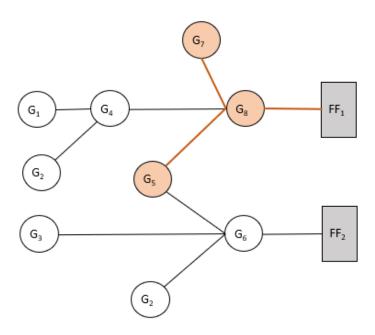

| An example of loical cone outputs                                                                                                                                                                 | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Single streaming processor SET sensitivity overview for injecting 1000 SET pulses.                                                                                                                | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

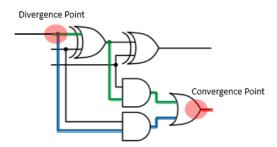

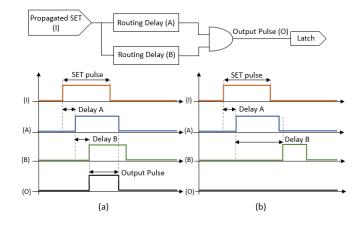

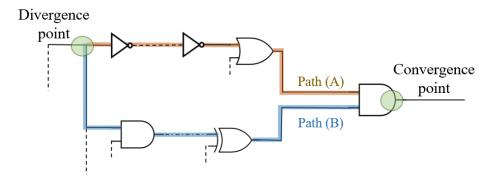

| An example of SET encountering the divergence point and conver-<br>gence point.                                                                                                                   | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

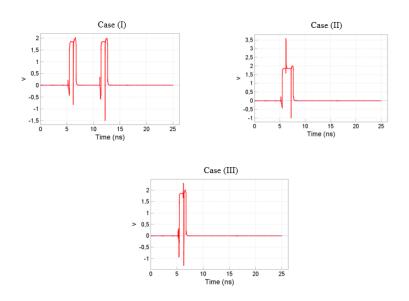

| Outcome of SET at the convergence point- C-SET                                                                                                                                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Correlation between maximum width of C-SET and Difference of delays between two paths.                                                                                                            | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

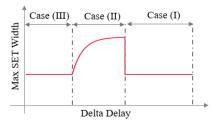

| Scheme of developed flow for accurate analysis of C-SET                                                                                                                                           | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The pseudo code for the identification of the SET width and ampli-<br>tude in a post layout circuit.                                                                                              | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

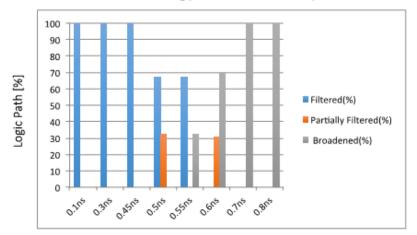

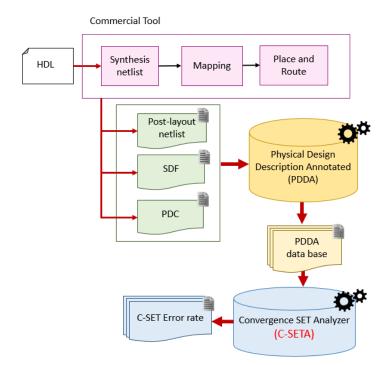

| Classification of C-SET in terms of criticality.                                                                                                                                                  | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

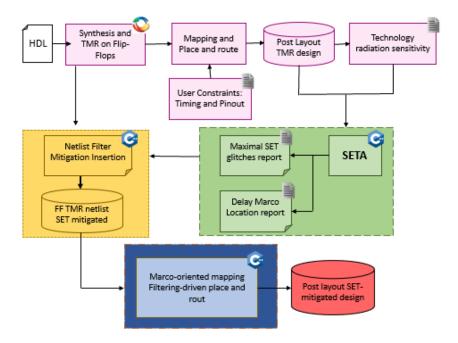

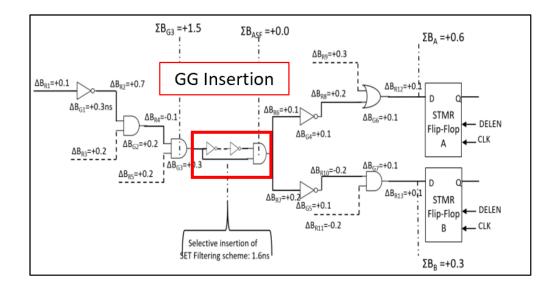

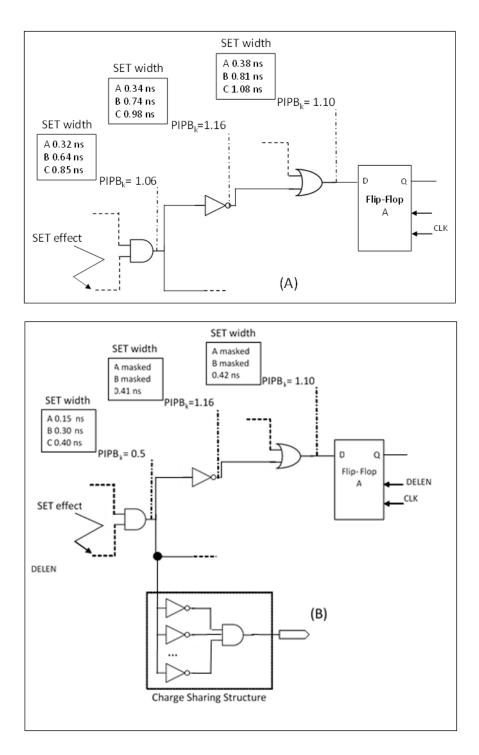

| The Overview of the SET-aware mitigation flow including the SET propagation analysis, the Netlist filter mitigation insertion and the marco-oriented mapping and filtering-driven place and route | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                   | The algorithm of Matrix Multiplication with TMR-kernel.          Additional buffers scheme needed for the check-sums for the matrix product ABFT method.          Scheme of the shuffle operation on the FF network to the auxiliary network done in the global memory buffers          FFT host algorithm executed on the share memory          FFT propagation kernel algorithm executed on the shared memory          The comparison of the FFT implementation with and without using the shared memory.          The check-pointing scheme adopted integrating the ABFT algorithm.          The FFT algorithm with the ABFT mean based check pointing.          Comparison of the execution times of the Sobel operator implemented in Frequency (blue line) and in space (red line).          An example of loical cone outputs.           An example of SET encountering the divergence point and convergence point.           Outcome of SET at the convergence point- C-SET.           Correlation between maximum width of C-SET and Difference of delays between two paths.           Scheme of developed flow for accurate analysis of C-SET.           The pseudo code for the identification of the SET width and amplitude in a post layout circuit.           The overview of th |

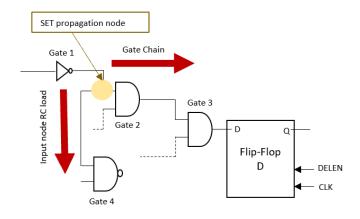

| 4.2  | The SET propagation method including the PIPB computation onthe propagation node.97                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

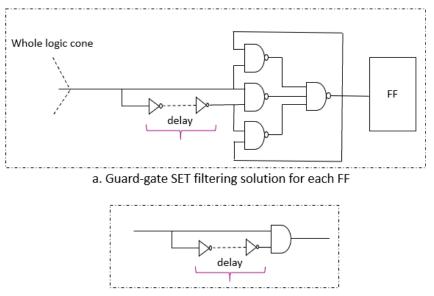

| 4.3  | Traditional Flip-Flop based guard-gate and SET-Filtering solution(a)compared to the SET-filtering scheme inserted by the netlist insertion mapper on logic gates shared by logic cones(b) |

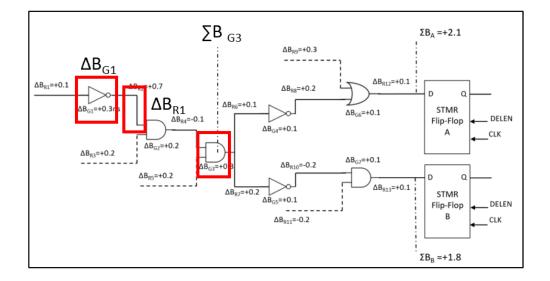

| 4.4  | An example of the netlist mitigation algorithm as a first phase on<br>a circuit portion: the calculation of the broadening coefficients in<br>nanoseconds                                 |

| 4.5  | Application of the netlist mitigation algorithm second phase to a circuit portion: the insertion of the filtering scheme on the shared logic path                                         |

| 4.6  | The global placement implementation algorithm                                                                                                                                             |

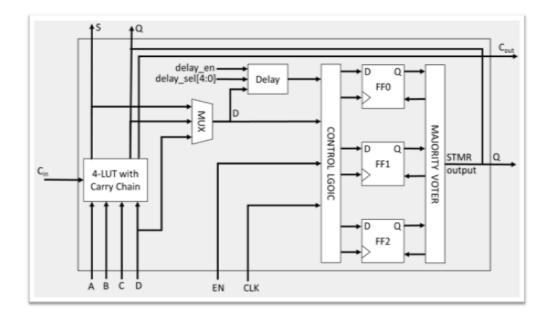

| 4.7  | The functional block diagram of logic element of the RTG4 Flash-<br>based FPGA family                                                                                                     |

| 4.8  | Overview of the developed flow including SET analysis and charge sharing mitigation                                                                                                       |

| 4.9  | The charge sharing mitigation algorithm for Flash-based FPGAs 107                                                                                                                         |

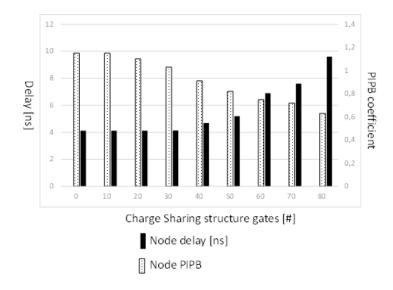

| 4.10 | Charge sharing number of gates per logic nodes with respect to the routing delay and PIPB coefficient                                                                                     |

| 4.11 | The key concept of the Charge Sharing mitigation algorithm 110                                                                                                                            |

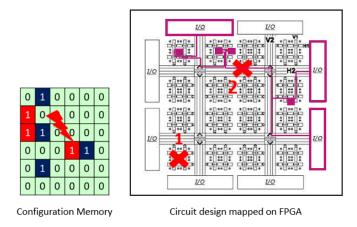

| 5.1  | SEU in configuration memory may corrupt circuit design mapped<br>on FPGA                                                                                                                  |

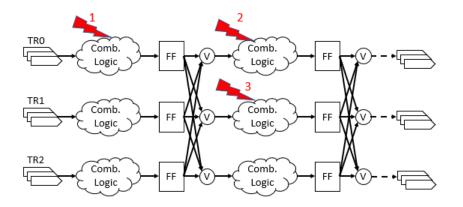

| 5.2  | SEUs in configuration memory affects different copies of logic path<br>in XTMR implementation                                                                                             |

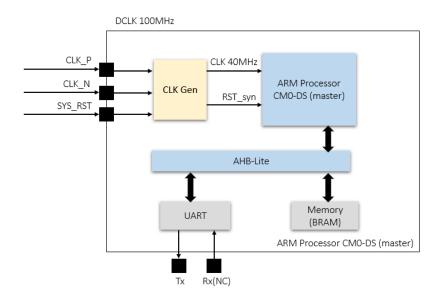

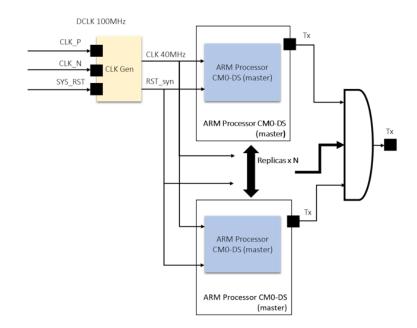

| 5.3  | Original ARM-based SoC used as benchmark circuit                                                                                                                                          |

| 5.4  | Replication scheme of ARM-based SoC for increasing device uti-<br>lization                                                                                                                |

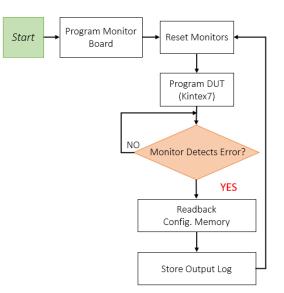

| 5.5  | Monitor flow with the Host PC application                                                                                                                                                 |

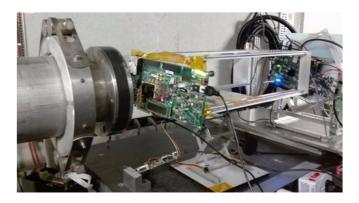

| 5.6  | board and beam setup for alignment                                                                                                                                                        |

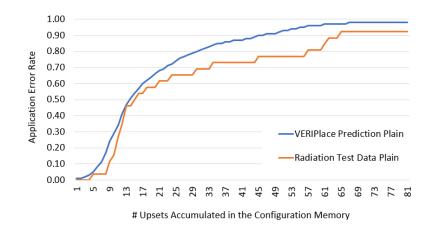

| 5.7  | VERI_Place error rate comparison with radiation test data for plain version                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------|

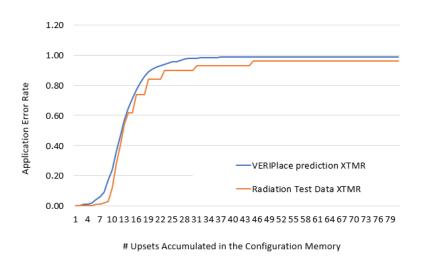

| 5.8  | VERI_Place error rate comparison with radiation test data for XTMR version                                                             |

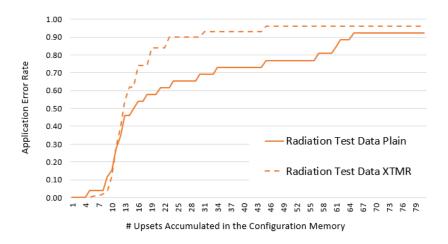

| 5.9  | VERI_Place error rate comparison between the Plain and XTMR version collected during radiation test                                    |

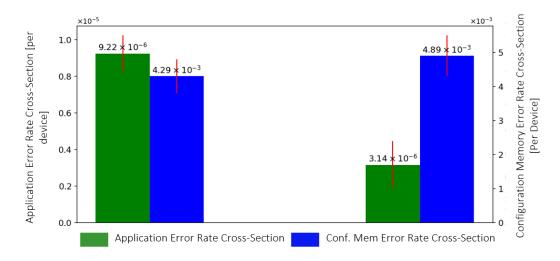

| 5.10 | Application and configuration memory error-rate cross-section com-<br>parison for Plain and XTMR versions                              |

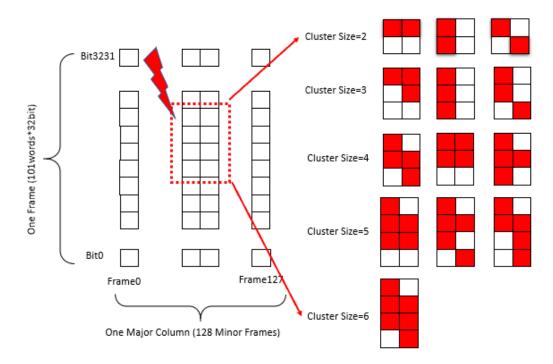

| 5.11 | Cluster (SEMU) patterns observed during radiation test                                                                                 |

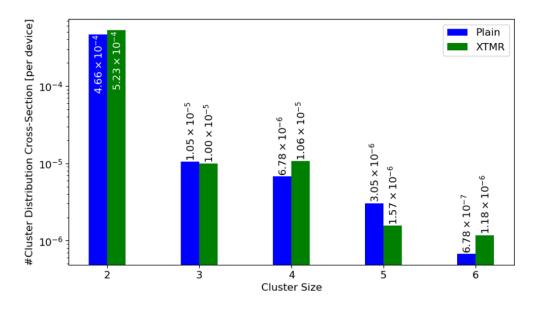

| 5.12 | Cluster distribution cross-section of different cluster sizes 126                                                                      |

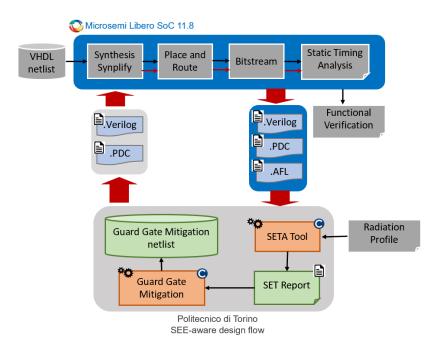

| 5.13 | The EDA adapted flow integrates both commercial tool (Micsosemi Libero Soc 11.8) and the SET analysis and mitigation flow 130          |

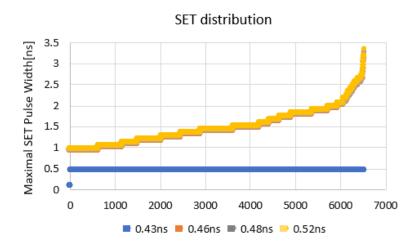

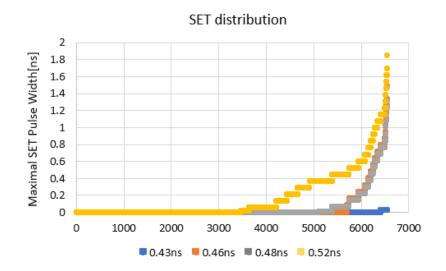

| 5.14 | The SET distribution obtained on the original EUCLID netlist 132                                                                       |

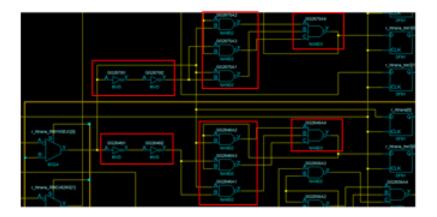

| 5.15 | An example of Gaurd-Gate automation insertion on a portion of the EUCLID design                                                        |

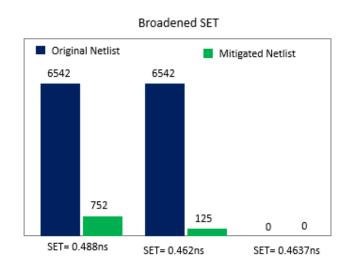

| 5.16 | The SET distribution obtained on the Mitigated EUCLID netlist 135                                                                      |

| 5.17 | A comparison of SET distribution between the original netlist and the mitigated netlist                                                |

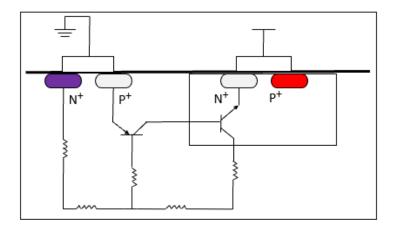

| 6.1  | Electrical effect generating a SEL effect                                                                                              |

| 6.2  | Overview of the basic mechanisms generating a micro SEL effect<br>on the output of a gate                                              |

| 6.3  | The intra-metal layer micro-SEL effect between routing segment.<br>The evidenced red routes represents the affected net                |

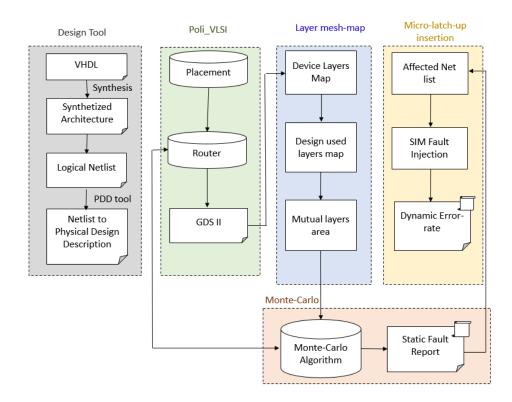

| 6.4  | OVerview of the global analysis methodology for micro-latch up consisting on the layer mesh-map and the micro-SEL insertion tool . 143 |

| 6.5  | A Pseudo-code overview of the developed latch-up analysis environ-<br>ment                                                             |

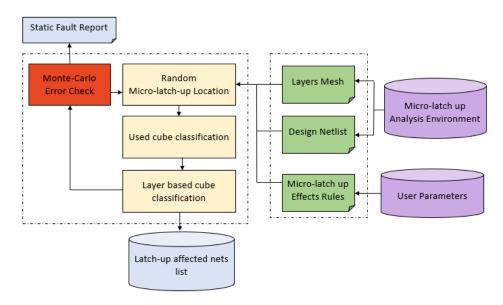

| 6.6  | The flow of the developed Monte Carlo Error Rate Analysis 145                                                                          |

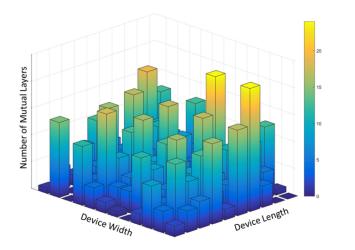

| 6.7  | Mutual layer distribution in terms of are width and length for bench-<br>mark B14 version F                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

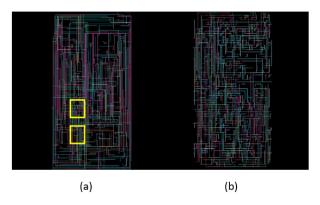

| 6.8  | Metal Layers 1 and 2 for the B14 implementation with routing congestion F(a) and routing congestion A(b)                                                         |

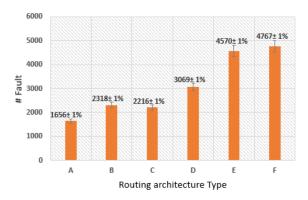

| 6.9  | Monte Carlo fault report for the different B14 Physical placement<br>and routing with statistical error rate bar at 1%                                           |

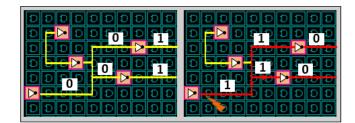

| 6.10 | $\mu$ SEL fault simulation instrumentation method                                                                                                                |

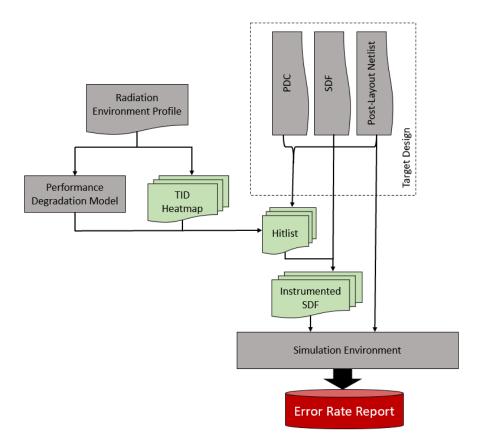

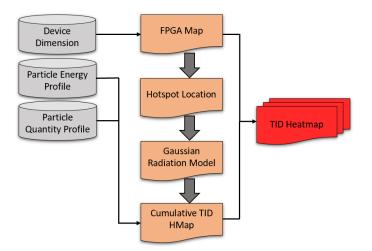

| 7.1  | The flow of the developed TID analysis environment                                                                                                               |

| 7.2  | VersaTile in Microsemi ProASIC Flash-based FPGA [1] 155                                                                                                          |

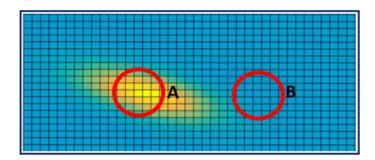

| 7.3  | Heatmap generation considering TID distribution: The area A repre-<br>sent a high density TID region, while area B is representing a TID<br>not affecting region |

| 7.4  | Block diagram of TIC Heatmap generation                                                                                                                          |

| 7.5  | Algorithm for generation Hitlist                                                                                                                                 |

| 7.6  | Algorithm for generation of instrumented SDF                                                                                                                     |

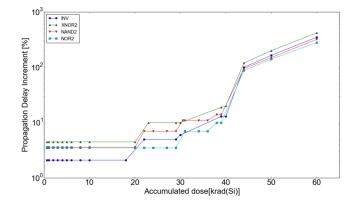

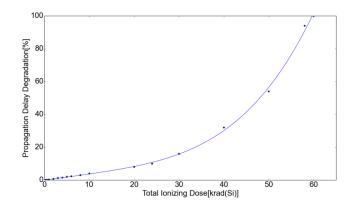

| 7.7  | Performance degradation for different types of gates [2]                                                                                                         |

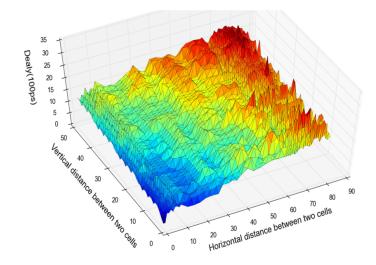

| 7.8  | Net propagation delay with respect to Manhattan distance between<br>net source and destination(X distance and Y distance separated) 163                          |

| 7.9  | Performance degradation coefficient model for routing net 164                                                                                                    |

| 7.10 | Error rate results of the selected ITC99 bench-mark with respect to different percentage for TID                                                                 |

## **List of Tables**

| 3.1  | Generated SET using internal electrical injection                                                      |

|------|--------------------------------------------------------------------------------------------------------|

| 3.2  | Benchmark area utilization                                                                             |

| 3.3  | Benchmark critical path resources                                                                      |

| 3.4  | $t_{pHL}$ and $t_{pLH}$ for each Inverter                                                              |

| 3.5  | Propagation behavior                                                                                   |

| 3.6  | Routing topology organization on ProASIC3 devices                                                      |

| 3.7  | Characteristic of the original benchmark circuits                                                      |

| 3.8  | Sensitivity report of the selected circuits for injection of 5000 SET pulses lower than 1 ns           |

| 3.9  | Matrix multiplication application results fault injection results 81                                   |

| 3.10 | Fast Fourier transform application fault injection results 82                                          |

| 3.11 | Fast Fourier transform application fault injection results 83                                          |

| 3.12 | Characteristics of the original benchmark circuits                                                     |

| 3.13 | Comprehensive SET sensitivity using static analysis tool- 5000 SET pulses lower than 1 ns are injected |

| 4.1  | Characteristics of the implemented circuits                                                            |

| 4.2  | SET fault simulation results                                                                           |

| 4.3  | Characteristics of the original benchmark circuits                                                     |

| 4.4  | Comprehensive Flip-Flop SET sensitivity using the static analysis tool111                              |

| 4.5 | SET fault injection wrong answers comparison                                                                                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 4.6 | Timing and area overhead for each method                                                                                        |

| 5.1 | Resource utilization for Plain and XTMR Version of ARM-based<br>SoC on Kintex-7                                                 |

| 5.2 | Comparison with Test Result of Lower Energy Beam on Kintex-7 . 127                                                              |

| 5.3 | Circuit Resources of the EUCLID netlist by type                                                                                 |

| 5.4 | Timing resources of the EUCLID netlist                                                                                          |

| 5.5 | Single Event Transient Analysis for SET Ranging from 0.43 sn to 0.52 ns representing the number of Flip-Flops for each case 131 |

| 5.6 | Timing analysis for three iteration of Guard-Gate mitigation tool 134                                                           |

| 5.7 | Area Over-head Report for Three Iteration of Guard Gate Mitigation<br>Tool                                                      |

| 5.8 | Circuit Resources for the Mitigation Netlist                                                                                    |

| 6.1 | Routing Architecture Characteristic                                                                                             |

| 6.2 | Dynamic error rate report                                                                                                       |

| 7.1 | Benchmark circuits characteristics                                                                                              |

### Chapter 1

# Introduction on Radiation Effect on Modern VLSI Technologies

Nowadays, electronic devices are used in a growing number of applications, starting from personal computers and entertainment market to large-scale business frameworks such as automobiles and satellites. Each application has its own requirements. However, they are considered as mission critical applications if they are involved in a huge amount of money or human lives. When electronic devices, in particular digital circuits are used in mission critical applications, dependability of theses devices is becoming an important issue. Dependability can be defined as the potential to tolerate faults happening due to environmental features, leading to the possible failure of the entire system. Misbehavior of the internal component of a system which is known as fault can propagate until the output of the system and become an error. Finally, if the generated error produced a misbehavior in the functionality of the system, the system is facing a failure [3]. Therefore, strategies and techniques are needed to tolerate faults and errors. In order to provide the most sufficient fault tolerant techniques, faults and errors themselves need to analyzed and studied in details. These faults and errors can be introduced both from the user side or the surrounding environment. One of the main environment aspect that can reduce the reliability of modern technologies specially when they are used in mission critical application is radiation.

When a set of radiation particle interact within the electronic systems by an exchange of energy, several kinds of effects can be observed. The impact of radiation

effects on electronic devices can cause a misbehavior on the functionality of the circuit. In order to apply strategies and techniques to tolerate these faults and errors, these effects must be analyzed in detail. Considering high frequency and smaller size of recent technologies, the sensitivity of High Performance Computing toward radiation is expected to be higher. Therefore, having more resilient mitigation technologies is more relevant and necessary, which is the focus of my research activity.

Radiation-induced effects can lead different effects depending on the location and time of the incident. If the effects of radiation incident last for a short period of time, it is known as a transient fault. While if the effects last for a longer duration, it is known as a permanent fault. Therefore, my PhD dissertation is divided into two main parts. The first part as the main part is dedicated to the transient fault, mostly focusing on Single Event Transient while the second part is dedicated to the permanent fault such as Micro Single Event Latch-up and Total Ionizing Dose. Considering Single Event Transient as the golden part of this dissertation, my research covers different phases of this phenomenon from the generation until the mitigation. Chapter 1 of this dissertation is dedicated to the elaboration of radiation effect on the modern technologies while chapter 2 is dedicated to the basic mechanism of Single Event Transient, evaluating the SET life-cycle inside the device. The thesis continues in chapter 3 by developing environments and setups for performing characterizations of SET pulses in different devices, development of tools and algorithms for analyzing and predicting the behavior of SET in the effected device. The performed analysis have been the golden keys to propose an efficient mitigation solution for robustness of the developed system against this phenomenon elaborated in chapter 4. The proposed mitigation solution has been known as the first method able to filter Single Event Transient pulses with zero-timing overhead. These methodologies have been applied to modern High Performance Computing technologies with high frequency and smaller size which leads to more critical condition for Single Event Transient effect.

This comprehensive proposed flow for analyzing and mitigating Single Event Transient has been applied to several industrial projects such as EUCLID space mission project with the goal of monitoring the dark space with the lunch planned for 2020 carrying by European Space Agency which is the focus of chapter 5. The developed SET analysis and mitigation work-flow has been part of the handbook *Space Product Assurance Techniques for Radiation Effects Mitigation in ASICs and*  FPGAs handbook, published by European Space Agency. Moreover, the developed set of tools has been known as the Best EDA Tool for improving design automation for integrated circuits and systems by IEEE Council on Electronic Design Automation.

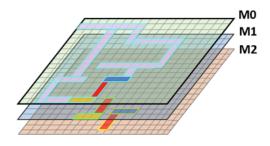

However, as a part of my research activity, not only I focused on the Transient effects, but I dedicated the second part of my dissertation to the evaluation of permanent effects such as Single Event Latch-up and total Ionizing Dose. Chapter 6 focuses on Single Event Latch-up which is one of the major reliability concerns for VLSI device applied in safety critical applications. The reduction of the circuit feature size and operating voltage levels are leading to a new kind of latch-up called micro Single Event Latch-up. Single Event Latch-up tends to occur near the input/output terminals of logic gates while micro Single Event Latch-up may occur at various locations between layers. One of the main research contributions of this dissertation is to propose a first 3D model for describing the 3D physical layout description of the design including the interconnection resources and logic versatile. This 3D layout description leads to analyze the sensitivity of the sub-micron circuitry to Micro Single Event Latch-up phenomena while considering the layout, depth, size and density of the design. This methodology is considered as the first one applicable to large industrial designs.

Bench-marking technologies are becoming increasingly attractive since their configuration memory is almost immune to Single Event Upset. However, applied in mission critical application, especially long-term missions, the FPGA devices are subject to cumulative ionizing damage, known as Total Ionizing Dose. Total Ionizing Dose may affect the FPGA, causing performance degradation and eventually permanent damage. Therefore, chapter 7 is dedicated to propose a physical model of Total Ionizing Dose effect in order to analyze the TID effect on recent modern technologies.

### **1.1 Radiation characteristics**

Radiation can be defined as a set of particles that are interacting within the device, transferring their energy to the device and creating several effects. In space, there are several kinds of radiation particles that can easily move in the space environment and interact within the electronic devices, such as: energetic electrons, protons, alpha particles, and heavy-ion particles [4] [5]. Some of these particles such as heavy ions

have a really high energy which are able to overcome the package protection of the chip and produce faults. While, other particles such as alfa particles are with lower energy which reduce the probability of passing through the shielding of the device. However, if these particles are generated inside the device as an interaction of high energy particles with the silicon of the device, they are capable of producing faults.

When an electronic device is exposed to radiation, several kinds of effects can be observed which is dependent to several factors. First of all, generated effects depends on the feature of radiation environment and particles such as the energy of the particle and the incident angel. On the other side, the triggered effects depends on the material of the device that the particle is going though. Considering different material, Linear Energy Transfer (LET) of the particle which is defined as the energy of the particles transferred to the material is different. The LET value plays an important roles in the computation of error rates for electronic system components. In the studies of radiation effects on electronic devices, LET is usually expressed in units of  $MeVcm^2/mg$  of the material, typically silicon, which is representing the lost energy of the particle to the material per unit path length ( $MeVcm^2/cm$ ) divided by the density of the material  $mg/cm^3$ .