Doctoral Dissertation Doctoral Program in Electronics Engineeing (31st cycle)

# Performance Optimization of Memory Intensive Applications on FPGA Accelerator

### Arslan Arif

\* \* \* \* \* \*

#### Supervisor

Prof. Luciano Lavagno, Supervisor

#### **Doctoral Examination Committee:**

Prof. Jordi Cortadella Fortuny, Referee, Universitat Politecnica de Catalunya, Spain

Prof. Frederic Petrot, Referee, Universite Grenoble Alpes, France

Prof. Paolo F. M. Ienne Lopez, Ecole Polytechnique Federale de Lausanne, Switzerland

Prof. Mihai T. Lazarescu, Politecnico di Torino, Italy

Prof. Alex Yokovlev, Newcastle University, England

Politecnico di Torino February 28, 2019

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

Arslan Arif

Turin, February 28, 2019

### Summary

Hardware accelerators are a fundamental part of modern high performance computing (HPC) systems due to their performance capabilities. The two most commonly used accelerators are GPUs and FPGAs. Despite the easier programmability and better memory performance of GPUs, generally FPGAs perform equally well for computationally challenging applications while dramatically reducing the energy consumption. Furthermore, with the availability of high level synthesis (HLS), the use of FPGAs has become easier. This makes them an excellent candidate for modern HPC systems. This dissertation describes my research work done in the field of electronic design automation with the major focus on optimizing memory intensive applications modeled using high level language for FPGAs. This work can be split into two parts, one dealing with manual memory optimization while other advocates the use of automated algorithms to select and optimize the best application-specific cache layout.

The first part covers the manual optimization of a realistic smart city application. The application implements two image processing algorithms in OpenCL language which computes velocity and density of vehicles on urban streets in real time. Several different implementations of these memory hungry algorithms are considered. The results show that using suitable optimizations and HLS optimization directives, FPGAs can produce results with performance similar to a GPU with an order of magnitude less energy consumption.

The second part of the dissertation starts by observing that custom data caches implemented on FPGAs are only useful if their layout is in accordance to their data access pattern. In this work, we present a tool, PEDAL (Pattern Evinced Determination of Appropriate Layout), that can automatically tune the custom data caches based on analyzing address traces. PEDAL uses artificial intelligence algorithms to detect the pattern of each array and then design the optimal cache for that pattern. The comparison of the results of PEDAL with the exhaustive search of cache configurations and cache designed through a state-of-the-art algorithm from the literature proves that it can produce better configurations in less time.

### Acknowledgements

First and foremost, I would like to thank Allah Almighty for all His blessings bestowed upon me. Without His will, I would not have made it this far. It is His blessing that I am able to complete my research project. It was He who provided me enough courage and strength to take on this challenge, accomplish it and make every hurdle easy for me.

I attribute myself lucky to have such a wise and kind supervisor and mentor, Prof. Luciano Lavagno, who was available to me in every hour of consultation and need. His expertise, patience, demeanor, and tolerance are some of the qualities for which I am thankful to him. He made this task as easy for me as was possible. He was always there to address my work-related as well as other general queries even with his extremely busy schedule.

Besides, I would also like to thank all the faculty members and researchers from the department of electronics and telecommunications (DET) at Politecnico di Torino, especially Prof. Mihai Teodor Lazarescu, who supported me in many ways during the course of my PhD. I would also like to take this opportunity to acknowledge the support of my group mates (past and present) at the Highlevel synthesis group at Polito, especially Liang Ma and Fahad bin Muslim. The discussions with them have always been extremely rewarding and I learned a lot from them.

My immense thankfulness goes for my family members including my parents, siblings and others for their unconditional support and prayers. This goes without saying that my wife Anum has a huge contribution in my degree.

Finally, I am extremely thankful to the higher education commission (HEC) Pakistan for funding my doctorate at the Politecnico di Torino. This is a great initiative by the government of Pakistan to create a pool of high quality researchers who can ultimately contribute to the prosperity of the nation. I find myself more equipped after my PhD to contribute to this goal.

I would like to dedicate this thesis to my loving parents

# Contents

| Li | List of Tables |                                                           |    |

|----|----------------|-----------------------------------------------------------|----|

| Li | st of          | Figures                                                   | X  |

| 1  | Intr           | roduction                                                 | 1  |

|    | 1.1            | FPGA based heterogeneous computing system                 | 2  |

|    | 1.2            | Problem Statement                                         | 3  |

|    | 1.3            | Contributions                                             | 4  |

|    | 1.4            | Organization of the thesis                                | 5  |

| 2  | Het            | erogeneous Systems                                        | 7  |

|    | 2.1            | Heterogeneous System Architecture                         | 7  |

|    |                | 2.1.1 Graphics Processing Units                           | 8  |

|    |                | 2.1.2 Field Programmable Gate Arrays                      | 9  |

|    |                | 2.1.3 ECOSCALE                                            | 9  |

|    | 2.2            | High Level Synthesis                                      | 12 |

|    |                | 2.2.1 High-level synthesis based Design Space Exploration | 13 |

|    | 2.3            | Open Computing Language                                   | 15 |

| 3  | Sma            | art City Application                                      | 17 |

|    | 3.1            | Application                                               | 18 |

|    | 3.2            | Related Work                                              | 20 |

|    | 3.3            | Algorithms                                                | 22 |

|    |                | 3.3.1 Background Subtraction                              | 22 |

|    |                | 3.3.2 Lucas Kanade Algorithm                              | 25 |

|    |                | 3.3.3 Implementation Model                                | 28 |

|    | 3.4            | Constraints                                               | 31 |

|    | 3.5            | Optimizations                                             | 31 |

|    |                | 3.5.1 Memory-related optimizations                        | 31 |

|    |                | 3.5.2 Computational optimization                          | 34 |

|    | 3.6            | Implementations                                           | 38 |

|    |                | 3.6.1 CPU                                                 | 39 |

|    |       | 3.6.2   | GPU                                     | 39 |

|----|-------|---------|-----------------------------------------|----|

|    |       | 3.6.3   | FPGA                                    | 40 |

|    |       | 3.6.4   | Performance and energy comparison       | 45 |

| 4  | Cac   | he Arc  | chitecture and Tuning                   | 49 |

|    | 4.1   | Relate  | d Work                                  | 50 |

|    | 4.2   | Archit  | ecture                                  | 52 |

|    |       | 4.2.1   | Direct-Mapped Cache                     | 54 |

|    |       | 4.2.2   | Set-Associative Cache                   | 56 |

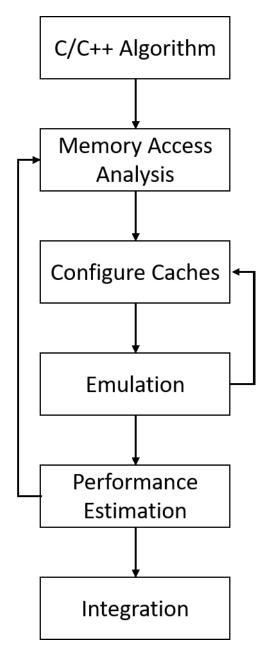

|    | 4.3   | Memo    | ry Access Patterns                      | 58 |

|    |       | 4.3.1   | Sequential access                       | 60 |

|    |       | 4.3.2   | Overlapping access                      | 61 |

|    |       | 4.3.3   | Non-unit stride                         | 62 |

|    |       | 4.3.4   | Window / neighbour                      | 63 |

|    |       | 4.3.5   | Random                                  | 64 |

|    | 4.4   | Cache   | Tuning using Heuristics                 | 64 |

|    |       | 4.4.1   | Heuristics in Literature                | 65 |

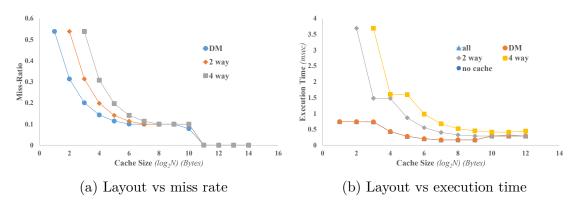

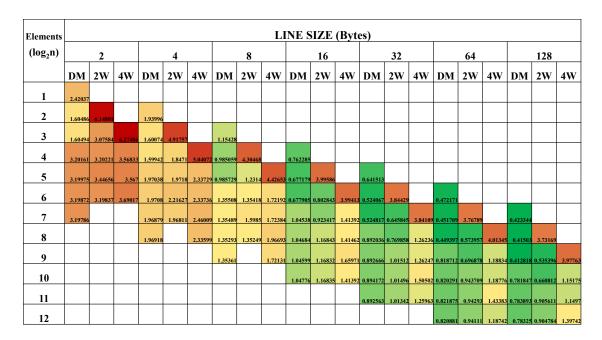

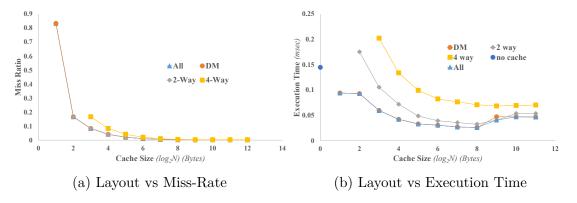

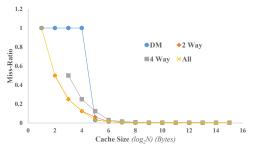

|    |       | 4.4.2   | Experimental Results                    | 66 |

|    | 4.5   | PEDA    |                                         | 69 |

|    |       | 4.5.1   | Algorithm                               | 70 |

|    |       | 4.5.2   | Pattern Recognition using Random Forest | 73 |

|    | 4.6   | Test ca | ase Implementations                     | 73 |

|    |       | 4.6.1   | Face Detection                          | 74 |

|    |       | 4.6.2   | Digit Recognition                       | 75 |

|    |       | 4.6.3   | Spam Filter                             | 75 |

|    |       | 4.6.4   | 3D-Rendering                            | 76 |

|    |       | 4.6.5   | Optical Flow I                          | 76 |

|    |       | 4.6.6   | Optical Flow II                         | 77 |

| 5  | Con   | clusio  | ns and Future Work                      | 79 |

|    | 5.1   | Conclu  | isions                                  | 79 |

|    | 5.2   |         | e Work                                  | 80 |

| No | omer  | clatur  | e                                       | 81 |

| Bi | bliog | graphy  |                                         | 82 |

# List of Tables

| 3.1 | Target FPGAs and boards                                             | 41 |

|-----|---------------------------------------------------------------------|----|

| 3.2 | Kernel Execution time and Resource Utilization for Basic Design     | 41 |

| 3.3 | Kernel Execution time and Resource Utilization for Design with Line |    |

|     | Buffer                                                              | 43 |

| 3.4 | Kernel Execution time and Resource Utilization for Design with cal- |    |

|     | culation reuse                                                      | 43 |

| 3.5 | Kernel Execution time and Resource Utilization for Design with      |    |

|     | piece-wise linear approximation                                     | 44 |

| 3.6 | Total Resource Utilization for Virtex 7                             | 45 |

| 3.7 | Total Resource Utilization for UltraScale+ (AWS-EC2)                | 46 |

| 3.8 | Power Consumption per Frame for Background Subtraction              | 46 |

| 3.9 | Power Consumption per Frame for Lucas Kanade Algorithm              | 47 |

| 4.1 | Results for Face Detection algorithm                                | 74 |

| 4.2 | Results for Digit Recognition algorithm                             | 75 |

| 4.3 | Results for Spam Filtering algorithm                                | 76 |

| 4.4 | Results for 3D rendering algorithm                                  | 77 |

| 4.5 | Results for Optical Flow algorithm                                  | 77 |

| 4.6 | Results for Lucas Kanade algorithm                                  | 78 |

# List of Figures

| 2.1  | A Typical Heterogeneous System Architecture                        |

|------|--------------------------------------------------------------------|

| 2.2  | FPGA Architecture                                                  |

| 2.3  | Hierarchical partitioning (tasks, memory, communication) of an HPC |

|      | application in ECOSCALE platform [27]                              |

| 2.4  | Platform and Memory Model of OpenCL                                |

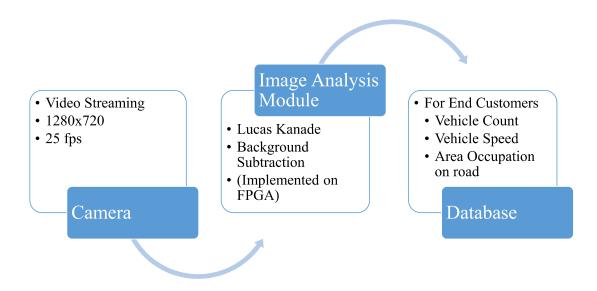

| 3.1  | Application Overview                                               |

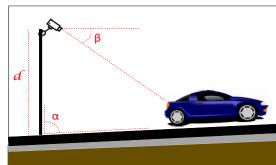

| 3.2  | Camera view                                                        |

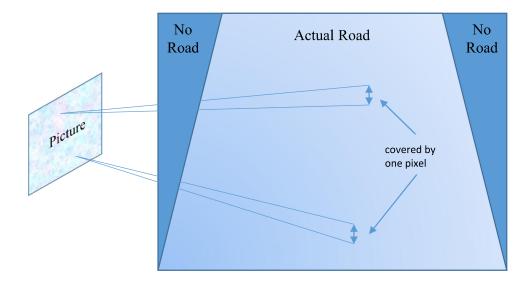

| 3.3  | Video Frame vs Ground reality                                      |

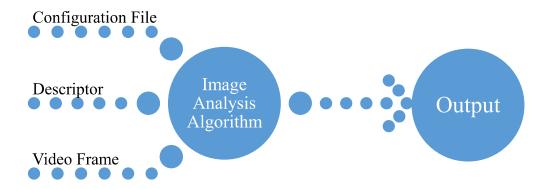

| 3.4  | General Workflow of Image Analysis module                          |

| 3.5  | Sample Frame                                                       |

| 3.6  | Output of the Background Subtraction Algorithm [64]                |

| 3.7  | Output of Background Subtraction                                   |

| 3.8  | Altera's Implementation of Lucas Kanade Algorithm [52] 26          |

| 3.9  | Lucas Kanade's Disparity Map                                       |

|      | Output of Lucas Kanade Algorithm                                   |

| 3.11 | Decentralized Model                                                |

| 3.12 | Centralized Model                                                  |

|      | From decentralized to centralized architecture                     |

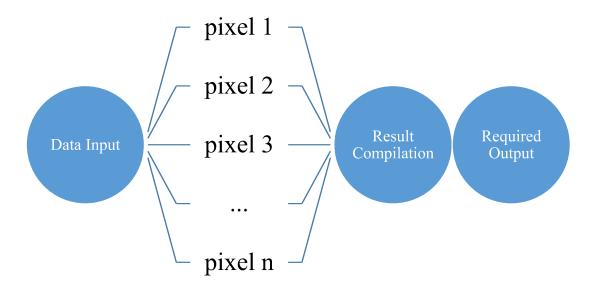

| 3.14 | Overview of parallelism in image processing Algorithms             |

|      | Example for burst access of data from DRAM                         |

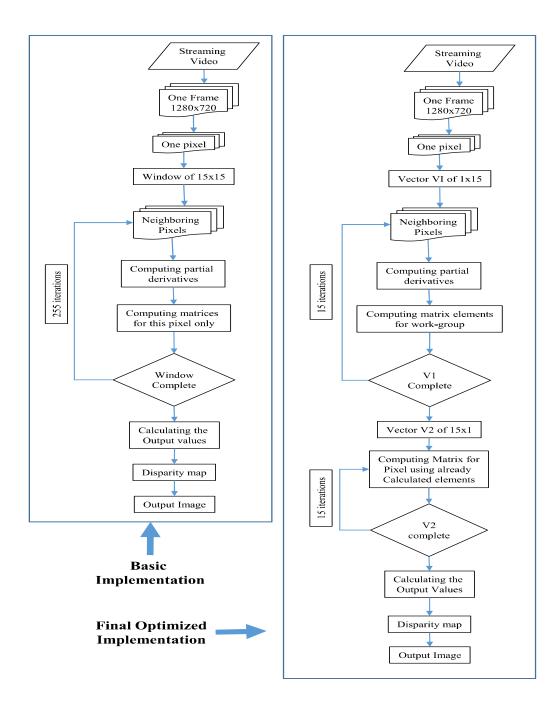

|      | Flowchart for KNP                                                  |

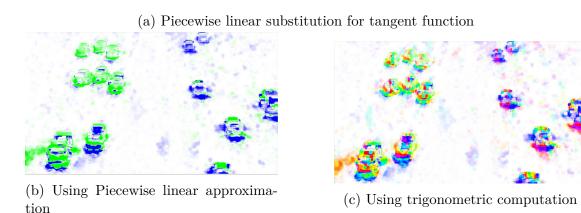

| 3.17 | Difference between two outputs for Lucas Kanade Algorithm 38       |

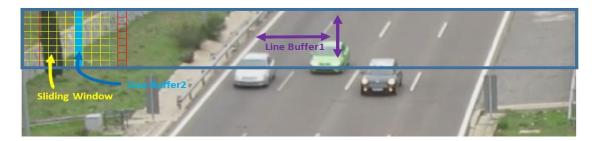

| 3.18 | Line Buffers for Lucas Kanade                                      |

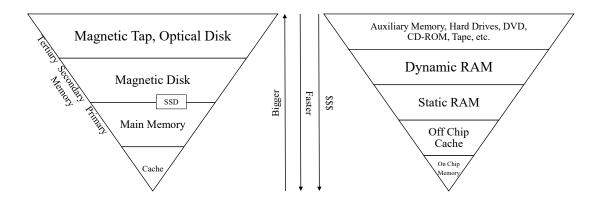

| 4.1  | A comparison of hardware memories                                  |

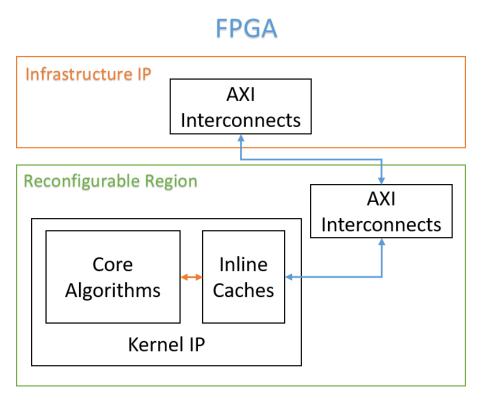

| 4.2  | Inline cache                                                       |

| 4.3  | Design flow with caches                                            |

| 4.4  | Diagram of a two-way set-associative cache                         |

| 4.5  | Different types of memory access patterns                          |

| 4.6  | Execution Time for Sequential Memory accesses                      |

| 4.7  | Pareto-optimal configurations for sequential memory accesses 61    |

| 4.8  | Execution Time for Overlapping Memory accesses                     |

| 4.9  | Pareto-Optimal configurations for Overlapping access 62            |

| 4.10 | Execution Time for Stride Memory accesses (Stride of 8 elements). | 63 |

|------|-------------------------------------------------------------------|----|

| 4.11 | Pareto-Optimal configurations for Stride access                   | 64 |

| 4.12 | Execution Time for Window Memory accesses                         | 65 |

| 4.13 | Pareto-Optimal configurations for 4x4 Window access               | 65 |

| 4.14 | Heuristic for cache layout                                        | 67 |

| 4.15 | Results for applying heuristics to Different access patterns      | 68 |

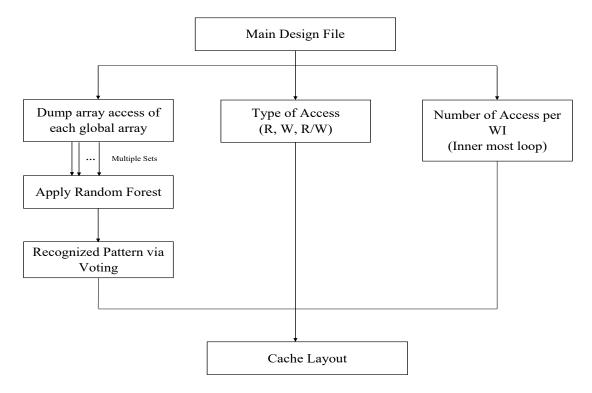

| 4.16 | Design flow of proposed method (PEDAL)                            | 70 |

| 4.17 | PEDAL Algorithm                                                   | 71 |

# Chapter 1

### Introduction

In the modern day world, the level of automation in the industry is constantly reaching new horizons. Both industry and the society at large are increasingly exploiting machine learning (ML), artificial intelligence (AI), Internet of Things (IoT) and Big Data applications. This in turn will make high performance computing the core of almost every industry. In order to yield this level of productivity, modern electronic devices are not only enhanced to perform multitasking, but are also required to do it in real time. Moore's law is reaching its end, mostly due to economic reasons, because only a few companies can afford to pay the exponentially increasing mask costs, and even increasing per-transistor costs. Thus the only approach to keep improving performance to the level required by the above mentioned application, with a reasonable energy cost, is to move some of the software load to dedicated heterogeneous architectures, where the heaviest parts are accelerated in hardware.

The main purpose to employ heterogeneous systems is to obtain the required performance for computationally expensive applications while achieving better energy efficiency [32], [46]. These systems generally consists of a multicore CPU along with various kinds of (typically programmable) accelerators. General purpose graphical processing units (GPGPUs) are traditionally used as accelerators as they provide the highest performance, albeit with a staggering energy-per-operation cost. The main issue with GPU based heterogeneous systems is that they are inefficient in terms of power consumption. In contrast to that, field programmable gate arrays (FPGAs) provide considerable performance while only consuming a fraction of energy as compared to GPUs. Hence, FPGAs are a strong competitor of GPUs for modern high performance computing (HPC) systems.

Although the computational capabilities of FPGA-based heterogeneous systems are very high, these systems require optimal data handling techniques in order to be effective. The main challenge in optimizing these systems is handling the memory bottleneck. This occurs when the data processing speed of the system is greater than the speed at which memory is able to provide (or, less frequently,

store) data. This is due to the fact that traditional CPU caches, which gives the programmer the illusion of a huge, yet very fast flat memory space, are not available for the portion of the computation that is offloaded to the FPGA. Thus the designer himself is responsible to optimize the HW memory architecture. The time required to fetch data and make it available for processing should be (by Amdahl's law) comparable with the processing frequency to obtain optimal results. The amount of data modern applications are dealing with ranges from hundreds of megabytes to terabytes. Therefore, this data needs to be stored in larger memories (DRAM or even Flash) which are slower to access. These memory accesses are costly not only in terms of time but also in terms of power and energy consumption. Moreover, as we discussed before, any delay in availability of data, also increases the computational time.

Now we conclude from the above discussion that memory is the major bottle-neck for HPC systems. There is no point in optimizing the computations without optimizing the data as we cannot achieve high computational throughput if we do not have the data to process. In this work we focus on a HW design methodology which starts from a C/C++ specification, where the memory access model reflects modern CPU architecture, and hence it is not typically suited for HW implementation. Hence the first thing that we need to optimize is memory accesses. The work presented in this dissertation considers memory hungry and computationally expensive applications as test cases and our results validate our hypothesis that without optimizing the data transfer for on chip design, state-of-the-art high-level synthesis tools fail to work. We have provided manual and automated solutions to improve the availability of data for applications.

# 1.1 FPGA based heterogeneous computing system

As discussed above, high performance computing requires sophisticated hardware and software resources. The performance of a processor can no longer be increased, since the early 2000's, by simply increasing its clock frequency, due to power reasons[9]. Moreover, traditional processor parallelism, in the form of superscalarity or hyper-threading, has also long reached its limits. Finally, multi-core processors are very energy-ineffficient due to the fetch-decode-execute cycle and the very general-purpose datapath and memory architecture that they offer. Therefore, it is a general consensus that heterogeneous systems are needed to provide the required performance in this regard.

Modern computing devices should have the capability to process large amounts of data. Extraction and categorization of vast amounts of data requires expensive and sophisticated software. For example, in the field of image processing, processing the live feed for even a single camera requires a dedicated central processing unit (CPU) [28]. This need of more performance requires computer accelerators. The most commonly used computer accelerator in this domain is the Graphical Processing Unit (GPU). GPUs provide higher memory bandwidth, higher floating point throughput and a more favorable architecture for data parallelism than processors. Due to these properties, they are used in modern high performance computing (HPC) systems as accelerators [74]. However, the main drawback of HPC systems based on GPU accelerators is that they consume large amount of power [25].

To overcome the power inefficiency of GPU-based HPC systems, modern field programmable gate arrays (FPGAs) can be used. FPGA devices require less operating power and energy per operation while providing reasonable processing speed as compared to GPUs [54]. When comparing them with multi-core CPUs, especially with regards to data center applications, it was observed that the performance gap keeps widening between the two. In summary, FPGAs are known to be more energy efficient than both CPUs and GPUs [69]. Moreover, FPGAs are well known for their reconfigurability as well as their energy efficiency. Acknowledging these capabilities, Microsoft, Baidu and Amazon now also use FPGAs as accelerators rather than GPUs in their data centers [53].

FPGAs are, however, complex to program. Hardware description languages (HDL) such as Verilog or VHDL are commonly used for this task. Most of the modern applications are developed in high level languages and it requires a lot of effort on the designer's end to define corresponding modules. Moreover, designer cannot explore many micro-architectural options using these low level languages due to long design and verification cycles.

To counter the issue of programming in low level HDL languages, designers now focus on high-level synthesis (HLS). HLS promises to generate register transfer logic (RTL) directly from algorithms written in high level languages e.g C, C++, OpenCL or SystemC. Moreover, HLS tools provide a number of directives to facilitate the designer in exploring different micro architectural solutions. Thus, we can say that HLS provides the capability to program FPGAs through the use of high-level languages, consequently reducing the design time debugging and analysis [50, 23].

#### 1.2 Problem Statement

The discussion above concluded that off chip memory accesses are expensive. They are not only expensive in terms of execution time, but also in terms of power and energy consumption. Moreover, if memory accesses are not optimized, then even other operations cannot be scheduled for efficient execution.

For example, in the simple case of vector addition, the only operation is a sum of two numbers. But if the data is stored in external DRAM, then it needs to

fetch the required elements from both the arrays, then it will perform addition and after that it will write the result back to the global memory. This means that in order to pipeline its computation with an Initiation Interval of 1 (i.e. starting a new elementwise addition every clock cycle) the global memory interface needs to support three operations (2 reads and 1 write) per clock cycle. This is very hard to sustain, even with modern DDR3 and DDR4 interfaces, for more than one such vector addition kernel on an FPGA (and a modern FPGA can support thousands of such computations in parallel). This quickly leads to saturation of the memory interface, and requires more efficient access techniques, that will be explored in this thesis. Thus the overall performance of the code degrades. If, hypothetically, we could make the whole data available on chip, then the operations in the work-items can be executed more efficiently. However, data can be copied on chip beforehand only for small applications, while for memory intensive applications involving image processing or machine learning, this option is not always feasible. Therefore we need to have a compromise between the two options to find the most optimal point.

In this thesis, the main focus is to improve the performance of a code which is memory bound, i.e. which requires a large amount of data transfer between external DRAM and silicon chip. The optimization can be application specific i.e. manually annotating the source code for fetching the memory in an appropriate way, or can be automatic, i.e. by using a tool to optimally implement this fetching for the designer.

In the first portion of the thesis, we want to optimize a real time application which is memory bound manually. The application implements two image processing algorithms on live video streaming of high definition (HD) quality (1280x720) at a rate of 25 frames per second. The main goal is to achieve real time video processing which requires a data transfer of more than 1.5 gigabytes (GB) per frame in unoptimized form.

The second part of the research considers the use of some *plug and play* application-specific caches to make the life easier for designer. The main aim of this work is to find an automated way to optimally choose the parameters for these caches, so that they can be used for any application without virtually any designer's effort.

#### 1.3 Contributions

In this thesis, the focus of the research is to optimize memory bound applications for FPGAs. As discussed in section 1.2, the work is divided into two major sections. One section deals with the manual optimization of highly memory bounded application while the other section proposes a tool to find optimal cache layouts. All of the work is done for FPGA applications written in high level languages, such as C/C++ or OpenCL.

In the first portion of the thesis, a realistic smart city application is optimized

for real time processing. The application processes incoming live video streams from the cameras to get velocity and density information for traffic on roads. It uses two image processing algorithms, Optical Flow and Background Subtraction that are computationally as well as memory expensive. The challenge of their real time implementation is met using GPUs and FPGAs, which were not feasible without accelerators. A very large design space was explored for multi architectural solutions and then the best solution, with respect to the end-user constraints (a company providing smart city infrastructure) was selected. All of the optimization done in this regard are explained in Chapter 3. These optimizations, although are application specific, can also be utilized with other memory hungry applications. The comparison of both accelerators shows that FPGAs are more suitable in terms of power and energy consumption than both CPUs and GPUs. High-level synthesis (HLS) with manual code optimizations is used to get the desired FPGA hardware and performance from GPU-optimized OpenCL code. Finally, the whole application is verified using Amazon Web Service (AWS) machines with FPGAs for functional verification and performance analysis. The final proposed design was able to process live video feed from roads for detection of number of vehicles and their speed.

The second part of the dissertation focuses on finding the application specific custom data cache configuration automatically. It discusses the architecture of an inline cache from the literature that reduces the programmer effort to optimize global memory (DRAM) accesses for any out-of-the-box code. This cache architecture previously needed manual intervention to find the most appropriate layout based on the application. This work first applies one of the best known generalpurpose heuristic cache sizing algorithms that was developed in the literature to find the optimal cache configuration. The results of this algorithm are compared with exhaustive search to adapt the cache to different memory access patterns. The results show that this heuristics can result in very sub-optimal configurations in all cases. Therefore, this work presents a tool to find the optimal cache configuration for each array mapped to DRAM. Using PEDAL, the configuration to obtain the best cache configuration for a specific application is automatically selected based on data access pattern. The results are verified using different applications and benchmarks. The cache architecture, layouts and data access patterns are discussed in detail in Chapter 4. It also discusses the tuning heuristic and algorithms and compares the performance of both of them.

### 1.4 Organization of the thesis

This thesis presents a collection of the work done in the field of electronic design automation (EDA) for FPGAs using high-level synthesis (HLS) with an emphasis on designs with efficient off-chip memory accesses. The work is divided into two

major portions and their organization is as under:

- Chapter 2 discusses Heterogeneous Systems and their architectures. It also explains their advantages and disadvantages. Moreover it also provides some introduction about high level synthesis (HLS) and the OpenCL programming platform.

- Chapter 3 discusses a video processing application which was co-designed in cooperation with Acciona, a Spanish company providing smart city solutions, in the context of an H2020 European project, and which was optimized by me for FPGA implementation. This chapter discusses in detail two commonly used video processing algorithms, their implementation and results generated by them to help the traffic flow. This chapter also includes the optimization carried out in order to achieve the required performance of 25 frames per second.

- Chapter 4 explains the architecture for custom inline data caches designed to be synthesized for FPGAs. It also discusses an automated algorithm that tunes the cache to obtain the best layout for the application under consideration. The effectiveness of the algorithm is tested against heuristics for different applications and benchmarks.

- Chapter 5 concludes the work. It also states the possible work which can be done in this field in future.

### Chapter 2

# Heterogeneous Systems

High-Performance Computing and data-intensive applications, such as Machine Learning, Artificial Intelligence, and big data processing, are becoming more and more common both in large data centers and on embedded platforms. Thus, while the processing speed of, e.g., Neural Network training or database sorting, remains a primary concern, energy consumption is quickly gaining importance. Homogeneous hardware architectures, e.g., multi-core general purpose Xeon processors, no longer meet the heaviest computation requirements especially from the point of view of energy efficiency [33].

A heterogeneous system refers to a system comprising of several different processors and cores. Such multi-core architectures offer high performance along with better power efficiency by not only using additional processor cores but by using specialized hardware called *accelerators* to handle certain computationally challenging portions of the applications. Thus, heterogeneous systems that cluster together different types of processors and hardware, such as CPU-GPU or CPU-FPGA, are able to achieve the best performance/cost/energy trade-offs for computationally-intensive parallel algorithms [71].

### 2.1 Heterogeneous System Architecture

As discussed before, a single core processor cannot provide the required performance for modern applications. Multicore processors have shown some promise in this field. As the name suggest, multicore processors are a number of processors packed in a single chip. They are able to show task and data level parallelism using parallel programming libraries [74], i.e OpenMP or MPI. These multicore processors still cannot beat the advantage we can obtain from system with hardware accelerator support, neither in terms of performance, nor in terms of energy efficiency.

Simple Xeon processor based systems are not as efficient as currently available

systems with accelerator support. A key point to keep in mind here is that these accelerators do not operate in stand alone fashion but they rely on traditional processors to manage them. CPUs are responsible to initiate the accelerators and upload and download the data as required by them [14], [30]. This make the heterogeneous systems more powerful as they take benefit from computationally advanced accelerators while the scheduling is done by multi-purpose central processing unit.

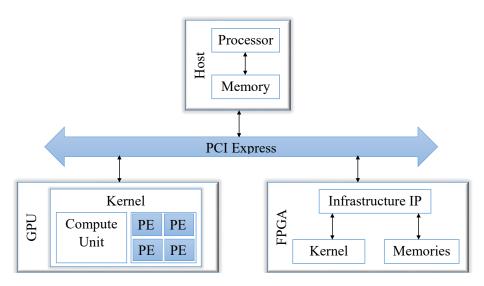

The accelerators used in such heterogeneous systems may be GPUs, FPGAs or a combination of both. In the terminology of heterogeneous system architecture, the multi-core processor is typically called a *host* while the hardware platforms used to accelerate certain portions of the applications are called *devices*. A typical heterogeneous system is shown in Fig. 2.1. The various important components of such a heterogeneous system are described here briefly.

Figure 2.1: A Typical Heterogeneous System Architecture

#### 2.1.1 Graphics Processing Units

As the name suggest, graphical processing units were originally designed to handle the advancement in field of graphics. The interest for GPUs or GPGPUs (general purpose graphical processing units) in the field of high performance computing developed after 2007, when NVIDIA introduced parallel programming framework, CUDA. CUDA (Compute Unified Device Architecture) is a parallel programming framework, designed for programming GPU based heterogeneous systems.

GPUs mainly consists of several processing elements which execute the kernel in parallel manner. These streaming processors are generally multicore and have

several components including ALUs (Arithmetic Logic Units), load/store units, caches etc. They execute the kernel code in SIMD (Single Instruction Multiple Data) fashion, which means that streaming microprocessors implement the same set of instruction to different data. In GPUs more emphasis is on data operations instead of data control and caching and hence their caches are smaller as compared to CPUs. GPUs also have their own device memory of few gigabytes [14].

GPUs do not operate in stand alone fashion. They always act as co-processor with CPUs, where CPU acts as a *host* and GPU acts as a *device*. Host is responsible for environment setting and data management for the device and they are connected through PCI-Express bus as shown in Fig. 2.1.

#### 2.1.2 Field Programmable Gate Arrays

The primary use of FPGAs was to implement discrete logic. Currently, recognizing their abilities and potential, their application is expanded to a variety of fields ranging from embedded systems to high performance computing systems [14]. Modern FPGAs provide a great alternative to GPUs in the field of high performance computing. The main issue with the GPUs is their energy inefficiency [25] which makes the case for FPGAs even strong. FPGAs can provide same amount of computational abilities while consuming a fraction of power. The application specific architecture of FPGAs reduces the need of multiplexing which provides great energy saving. Similarly hardwired control logic eliminates a lot of control instructions and is also a major reason for energy efficiency of FPGAs.

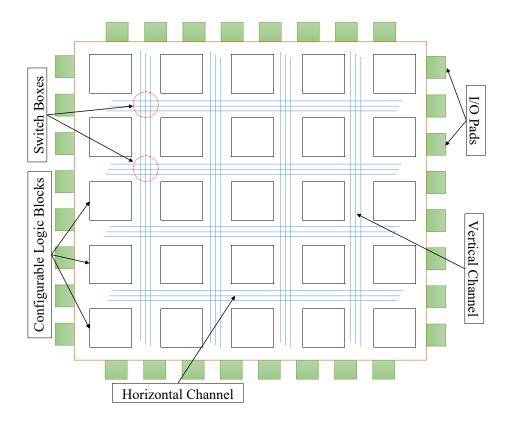

Unlike GPUs the architecture of an FPGA is not fixed, but can be customized according to the requirements of the application. A typical FPGA consists of logic blocks, memory blocks and DSP slices each surrounded by programmable interconnects as shown in Fig. 2.2. The interconnects among different logic and memory blocks of FPGAs are programmable, which provide a lot of flexibility to its architecture. Similarly, the I/O blocks are also not fixed and can be programmed according to the application.

The flexible FPGA architecture where provide a lot of opportunities to the designer on one end, it also posses some challenges for designers to optimally configure the architecture. Therefore, designers need to have good knowledge of the hardware and corresponding configurations in order to obtain good results. This problem is however resolved by the use of HLS (section 2.2) and languages like OpenCL (section 2.3).

#### 2.1.3 ECOSCALE

Many HPC centers are operating around the globe. Some of them are implemented using CPUs only while others have accelerator support in them as well. Previously the trend was to use GPUs in data centers but currently acknowledging

Figure 2.2: FPGA Architecture

the capabilities of FPGA, some of the major data centers in world like Microsoft, Amazon, Baidu are also using FPGAs rather than GPUs [53].

There are certain HPC servers that target to provide an energy-efficient architecture by sharing numerous reconfigurable accelerators. In order to provide a scalable approach, the architecture should be tailored to the needs of the HPC applications as well to the characteristics of the hardware platform. ECOSCALE (Energy-efficient heterogeneous COmputing at exaSCALE) is a project under the H2020 European research framework. The main goal of this project is to provide a hybrid MPI+OpenCL programming environment, a hierarchical architecture, a runtime system and middleware, and a shared distributed reconfigurable FPGA based acceleration [27].

ECOSCALE offers a hierarchical heterogeneous architecture with the purpose of achieving exascale performance in an energy-efficient manner. It proposes to adopt two key architectural features in order to achieve this goal: UNIMEM (Unified Memory) and UNILOGIC (Unified Logic). UNIMEM was first proposed by the EUROSERVER project [26] and provides efficient uniform access, including low-overhead ultra-scalable cache coherency, within each partition of a shared Partitioned Global Address Space (PGAS). UNILOGIC, which is first being proposed

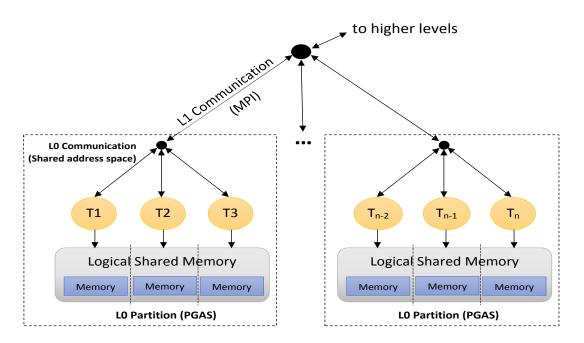

Figure 2.3: Hierarchical partitioning (tasks, memory, communication) of an HPC application in ECOSCALE platform [27]

by ECOSCALE, extends UNIMEM to offer shared partitioned re-configurable resources on FPGAs. The proposed HPC design flow, supported by implementation tools and a run-time software layer, partitions the HPC application design into several nodes. These nodes communicate through a hierarchical communication infrastructure as shown in Figure 2.3. Each Worker node (basically, an HPC board) includes processing units, programmable logic, and memory. Within a PGAS domain (several Worker nodes), this architecture offers shared partitioned re-configurable resources and a shared partitioned global address space which can be accessed through regular load and store instructions by both the processors and the programmable logic. A key goal of this architecture is to be transparently programmable with a high-level language like OpenCL.

ECOSCALE targets to provide an energy-efficient architecture by sharing numerous reconfigurable accelerators. In order to provide a scalable approach, the ECOSCALE architecture should be tailored to the needs of the HPC applications as well to the characteristics of the hardware platform.

### 2.2 High Level Synthesis

The main hindrance in exploiting the potential of FPGAs was the tedious job of coding them in hardware description languages. The use of FPGAs is now very convenient thanks to high level synthesis (HLS). Generation of quality register transfer level (RTL) from high level specifications is a great achievement in electronic design automation. Previously, HLS designs were considered inefficient, but after the recent development in designing tools and availability of different synthesis directives, it is gaining the interest of designers. It not only reduces the designer's efforts but also provides fast design cycles by minimizing the manual effort.

Designing a suitable hardware requires a number of steps to be followed in specific order. Most of the hardware design projects start from an executable model of high level language. This model is generally developed to verify the behaviour of the task to be performed. This model is tuned and tested at different stages to verify the correct functionality of the model. Once tested and verified, then this model goes under a number of steps before it takes form of an actual hardware implementation. The final architecture is then described in the form RTL, generally written in VHDL or Verilog. There are certain drawbacks of this process, including long design and verification cycles and manual nature of the process. High level synthesis tools can automate this whole process into an error free path from abstraction to RTL generation.

Some of the major advantages provided by high level synthesis are:

- Automates the whole process from abstract level design to RTL generation

- Accelerated design times

- Provides directives to explore the whole design space just by small modifications

- Debugging the algorithm is much easier and less time consuming

- Allows high level of portability between different platforms

- In most of the cases designers do not need to worry about detail architectures, i.e. clocks, design hierarchy, processes etc.

- Modules once synthesized can be reused more effectively

The reduction in design efforts allows the designer to freely focus on their main design functionality and care less about implementation details. These details are automatically tuned by the tool according to the design specifications and hardware selected. Another major advantage as stated above is the portability among different platforms. This also means that designer can switch between the hardware to choose the best according to his needs.

#### 2.2.1 High-level synthesis based Design Space Exploration

Modern FPGAs, such as the Stratix from Altera and the Virtex, UltraScale families from Xilinx, offer to the designer millions of Configurable Logic Blocks (CLBs) and Flip-Flops, megabytes of on-chip the Block RAM (BRAMs), hundreds of multiply-and-accumulate units (DSPs), and many other dedicated hardware blocks, including ARM Cortex processors [80]. Moreover, very recent design flows from both Altera/Intel and Xilinx promise software-like development for applications that are entirely written in a high-level language, like C, C++ or OpenCL, and are then compiled and synthesized for heterogeneous CPU-FPGA platforms. In particular, parallel languages that were originally developed to program GPUs, can now be used to program heterogeneous platforms such as PCs with FPGA boards, or Zyng platforms which include a multi-core CPU and a large FPGA [66].

However, the expected performance is typically not achieved by simply recompiling, via High-Level Synthesis for an FPGA target, an algorithm that was originally written for execution on a CPU or GPU. This is because the CPU or GPU architectures are fixed, hence most compiler decisions are local and relatively simple, such as intra-basic block scheduling or peephole optimizations. However, in an FPGA the architecture is adapted to the application, rather than the application to the architecture. While this can achieve much better optimization levels, it also implies that many more high-level decisions must be made during synthesis. HLS tools are able to automatically implement these decisions, but even their latest generations need to be directed to do so by a human or by a (very time-consuming) Design Space Exploration tool.

While the optimizations performed by a CPU or GPU compiler are considered excellent when they speed up execution by a factor of 2, the following HLS techniques can dramatically optimize the execution time of algorithms on FPGAs even by orders of magnitude. Most of them apply to loops, which are a major source of concurrency in high-level code and some languages, such as OpenCL, explicitly state that some loops can be arbitrarily parallelized, because iterations do not depend on each other:

1. Loop pipelining starts new iterations of a source code loop before the previous ones are completed. It is one of the best options for loop optimization in HLS, since it usually boosts the performance at a very low cost [29, p. 61]. The number of clock cycles between successive loop iteration starts (inverse of the throughput) is also called the "Initiation Interval" of the pipeline (in the best case, it can be one clock cycle). It is fully decoupled from the time it takes to complete one iteration, the pipeline "latency". Usually, memory or data dependencies between successive iterations ("loop-carried dependencies") are the bottlenecks that increase the initiation interval. Several other synthesis techniques, e.g., array partitioning or loop interchange [43], can be applied to ameliorate this problem.

- 2. Loop unrolling creates multiple copies of the loop body to be executed fully in parallel. In some cases it can achieve even more performance than by means of pipelining, but typically at a huge resource (i.e., area) cost. A loop can be fully or partially unrolled and in both cases the maximum performance can be achieved only by means of array partitioning and may require arithmetic evaluation restructuring (e.g., adder tree balancing) [29, p. 51]. In OpenCL (similar to CUDA), the loop over work groups can be unrolled arbitrarily by definition. Thus, like on a GPU, the performance on an FPGA can be increased by instantiating multiple work groups until the computing or routing resources, or its memory bandwidth are saturated [66, 49]

- 3. Exploiting on-chip memory. Most modern FPGAs integrate thousands of independent BRAMs on chip for a total of many MBs of storage. Accesses to these memories are both much faster in terms of latency and much more parallelizable than those to off-chip memories [78]. Many algorithms, especially the memory-intensive ones that are addressed in this article, achieve the best acceleration only by moving frequently-accessed data that reside in off-chip memories into on-chip BRAMs (or another kind of FPGA memory called LUTRAMs). As mentioned above, on-chip memories that are not carefully optimized by using partitioning directives can often become bottlenecks, because of the limited number of access ports that they offer. While on a GPU the maximum number of concurrent accesses to independent addresses (and the meaning of "independent") is fixed by the GPU architect, on an FPGA it must be carefully chosen by the designer, because more parallelism often implies a higher cost. Memory partitioning or memory reshaping according to user directives or to automated analysis of access patterns of a given algorithm can dramatically increase the memory bandwidth and achieve a much higher level of concurrency.

- 4. Optimizing global memory interfaces. Other methods to improve performance include instantiating multiple DRAM access ports or increasing their bit width.

On a GPU, the global memory interface subsystem receives memory read or write requests from the threads or work items that are executing on its compute units, and *coalesces* these requests whenever possible, in order to match both the available memory word size and bus burst transfer capabilities. For example, 16 accesses to adjacent properly aligned 32-bit integer array elements can be grouped *automatically at runtime* into a single 512-bit memory read, or to a burst of 4 128-bit memory reads, depending on the DRAM interface width.

On an FPGA, these groupings must be performed manually and at compile time, which requires a lot of design and tool usage expertise.

### 2.3 Open Computing Language

Open Computing language or *OpenCL* is a parallel programming framework based on C99 and C++11 which support parallel programming model. It is widely used for programming heterogeneous and multicore platforms [34], [68]. As the name suggests, it is an open source standard which is maintained by Khronos Group. The main advantage offered by OpenCL is execution portability. It allows to run the same design accross different platforms with few modifications.

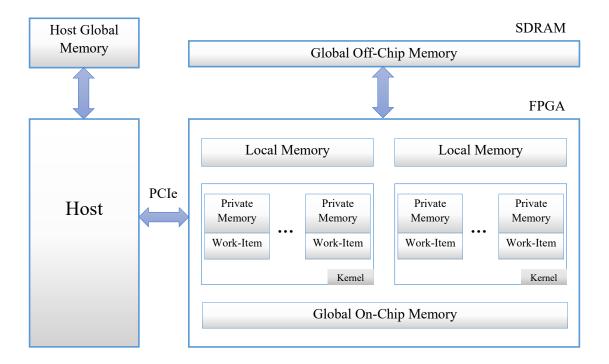

Figure 2.4: Platform and Memory Model of OpenCL

Some definitions/terminologies used by OpenCL model are shown in ifg. 2.4 and defined as under:

- **Host:** It is a (multi-core) processor, which is responsible for setting up the environment and managing tasks on the *device*.

- **Device:** Device is the word that represents the hardware accelerator in the system

- **Kernel:** It is the computationally expensive piece of code that is designed to run on the *device*.

- Compute Unit (CU): An OpenCL device can implement multiple copies of same design, called compute units.

- Work-items & work-groups: Concurrent implementations of kernel body are termed as work-items and a collection of these work items is called work groups. The designer can choose the size of work-items per work-group.

- Global Memory: It the shared memory between all the work-groups. It is the slowest device memory to access and have the size order of a few gigabytes (GB).

- Local Memory: This is a private memory of each work group, which means it is shared by all the work items within that work-group. It is faster than global memory.

- **Private Memory:** It the smallest, but fastest memory to access in the whole model. It is the private memory of each work-item and generally use to store some temporary variables.

It should be noted that memory management in OpenCL is done explicitly i.e. by moving data from host memory to global memory to local memory and then back. To ensure memory consistency and provide better synchronization within a workgroup, if needed, OpenCL also provides the concept of *barriers* [81].

# Chapter 3

# **Smart City Application**

Cities are seeing massive urbanization worldwide, thus increasing the pressure on infrastructure to sustain private and public transportation. Adding intelligence to traditional traffic management and city planning strategies is essential to preserve and even improve quality of life for citizens under this enormous increase of population. Traffic causes increased delays, thus reducing the opportunity for city dwellers to earn money by performing productive activities. It also poses health hazards due to pollution and accidents. Several public and private entities (ranging from public transportation providers, to city planners, to traffic light control, to taxi and car sharing providers, to individual drivers) can profit from the widespread availability of real-time information about traffic flows. Part of the work described in this chapter has been previously published in "Performance and energy-efficient implementation of a smart city application on FPGAs" [8].

This application can improve traffic-related problems in modern continuously growing cities based on the information provided by the citizens and/or extracted by monitoring their habits. Various methodologies and sensors can be used to achieve this goal.

This application will provide cost-effective and scalable real time analysis of traffic in cities that can then be harnessed by other smart city services and applications (e.g. intelligent traffic management tools) in order to reduce traffic-related impacts on the quality of life of citizens. Videos obtained from cameras can provide reliable information about the traffic flow on roads. The basic idea, as shown in Fig. 3.1. is that the cameras acquire the images, which are then processed using image-processing algorithms. After that, the data is stored in a database and accessed on demand.

Figure 3.1: Application Overview

### 3.1 Application

The main goal of the application described in this work is to extract data from video surveillance cameras and make it available to different services. The objective is to provide real-time information which can be used to optimize, for example the street lighting and traffic light systems installed in cities. The application will analyze the images recorded by the cameras installed in cities and will apply a set of algorithms in order to detect the presence of people and vehicles and to compute the density of traffic at each specific location.

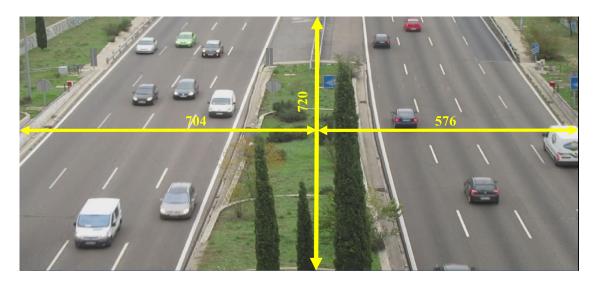

- (a) Camera view of the road

- (b) Road Parameters w.r.t camera

Figure 3.2: Camera view

For this purpose, cameras are installed on roads (Fig. 3.2a). Their parameters like height from ground, angle of elevation etc. and road parameters like width, etc.

are already assumed to be available for processing, as shown in Fig. 3.2b, together with other constants like the minimum value for detecting a change of speed.

Figure 3.3: Video Frame vs Ground reality

In most places, cameras cannot be positioned directly above a road. Most of the times they will have a prospective view, as shown in Fig. 3.2a. So we need input values to map the road with respect to the camera pixels. We need three types of information.

- 1. Whether a pixel covers a road area

- 2. How much area each pixel covers

- 3. How much distance each pixel covers in the direction of the camera

The presence or absence of the road allows us to apply the algorithm only on the part of the camera frame that we are interested in and hence save computational resources. The area value is used to find the percentage of the road occupied by moving objects. Finally the distance is used to compute the velocity of the vehicles. All of them can be calculated from camera resolution, aperture, focal length and height over the road. Another important thing to note here is that, as we move away from the camera, the distance represented by one pixel increases. Therefore, the distance value for each pixel is different. It is calculated once for each stationary camera and then used repeatedly to save time and computational resources.

Fig. 3.4 shows the general work-flow of the image analysis module in detail. Two configuration files containing road and camera parameters are used as inputs,

Figure 3.4: General Workflow of Image Analysis module

in addition to the image to be analyzed. This module can be instantiated, as many times as needed, once for each descriptor that is desired, so that it is possible to detect many kinds of objects at the same time.

#### 3.2 Related Work

A lot of work has been carried out on smart cities in the last 20 years [2]. For some reviewers smart cities are still confusing [4]. Definitions range from information and communication technology (ICT) networks in city environments [3]; to various ICT attributes in a city [7]. Some relate the term with indexes like the level of education of citizens or in terms of financial security etc. [5] while others thinks about it in terms of urban living labs [39]. All of these implications are alternative schools of thought and most researchers point towards the complexity and scale of the smart city domain [6].

The monitoring of roads for security and traffic management purposes is one of the main topics in this domain. Modern smart cities measure the traffic so that they can optimize the utilization of the roads and streets by taking actions which can improve traffic flow. Video-based approaches have been researched to monitor the flow of vehicles in order to obtain rich information about vehicles on roads (speed, type of vehicle, plate number, color etc.) [15].

Vision-based traffic monitoring applications have seen many advances thanks to several research projects that were aimed at improving them. In 1986, the European automotive industry launched the PROMETHEUS European Research Program [75]. It was a pioneer project which intended to improve traffic efficiency and reduce road fatalities [72]. Later, the Defense Advanced Research Projects Agency introduced the VSAM project to create an automated video understanding technology which can be used in urban and battlefield surveillance applications of

the future [20]. Within this structural framework, a number of advanced surveillance techniques were demonstrated in an end-to-end testbed system which included tracking from moving and stationary camera platforms and real-time moving object detection as well as multi-camera and active camera control tracking techniques. The cooperative effort of these two pioneering projects remained active for about two decades. As a result, new European frameworks evolved to cover a variety of visual monitoring systems for road safety and intelligent transportation. In the early 2000s, the ADVISOR project was implemented successfully to spot abnormal user behaviors and develop a monitoring system for public transportation [47, 48, 24].

There are several methods which can extract and classify raw images of vehicles. These methods are chiefly feature-based and require hand-coding for detection and classification of specific features of each kind of vehicle. Tian et al. [70] and Buch et al. [15] surveyed some of these methods. In the fields of intelligent transportation systems and computer vision, intelligent visual surveillance plays a key role [84]. An important early task is foreground detection, which is also known as background subtraction. Many applications such as object recognition, tracking, and anomaly detection can be implemented based on foreground detection. [82] [73].

An application was proposed in the Artemis Arrowhead Project [36] that can detect patterns of pedestrians and vehicles. According to the authors, based on this information, the application can also extract a set of parameters such as the density of vehicles and people, the average time during which the elements remain stationary, the trajectories followed by the objects, etc. Subsequently, these parameters are offered as a service to external parties, such as public administrations or private companies that are interested in using the data to optimize the efficiency of existing systems (e.g., traffic control systems or streetlight management) or develop other potential applications that can take advantage of them (e.g., tourism or security).

Many existing systems, which are concerned about privacy of the citizens, employ some sort of censorship so that human or AI users are not able to see and inadvertently recognize any person in the camera footage. This can be done either in the form of a superimposed black box, which blocks out the eyes or face of the person, masking each person in each frame or blocking images of certain places altogether [11, 51, 58, 59, 61, 65]. However, this approach cannot achieve full privacy. Most of the time we do not require any sort of information related to individuals while working with applications related to computer vision. Thus, the developer should be aware of the information being collected either advertently or inadvertently and of what are the real requirements for the application. [17]

### 3.3 Algorithms

To extract the required information from the video stream, two image processing algorithms are applied. One is the background subtraction algorithm, while other is Lucas Kanade Algorithm for optical flow. A sample frame from one of the cameras is shown in fig 3.5. The image is split into two portions to separate the information on two road recorded in one frame. These information is passed to the algorithm in the configuration file for separate calculations.

Figure 3.5: Sample Frame

#### 3.3.1 Background Subtraction

Algorithm 1 is based on a background subtraction and object tracking method. One popular implementation was made available by Laurence Bender et al. as part of the SCENE package [63], available in the Sourceforge repository (Fig. 3.6). The algorithm performs motion detection principle by calculating the change in corresponding pixel values with respect to the reference stationary background. The portion of the road where movement is detected gives an idea about the amount of traffic. Moreover, the algorithm also constantly updates the reference background image (in case a moving object is now at rest).

Scene is an open source multiplatform computer vision framework that performs background subtraction and object tracking using algorithms based on neural networks and fuzzy classification rules. It was mainly designed as a toolkit for the rapid development of interactive art projects that explore dynamics of complex environments (for example public spaces).

Scene defines five different model implementations if OpenCL for background subtraction. They are

- Simple Gaussian

- Fuzzy Gaussian

- Mixture of Gaussian

- Adaptive Self-Organizing Map (SOM)

- Fuzzy Adaptive Self-Organizing Map (SOM)

Figure 3.6: Output of the Background Subtraction Algorithm [64]

Our chosen algorithm takes four frames (images) as input, including the reference stationary background, the frame under the consideration, the preceding frame and the succeeding frame. For each pixel, it performs a weighted difference on the corresponding pixels of three consecutive frames. If this difference is zero, it implies that there is no movement in the corresponding pixel, hence no update is needed for the total moving area or the reference background. On the other hand, non-zero values corresponds to some change in the consecutive video frames around the pixel. The value can be a positive or a negative number according to the direction of movement with respect to the camera. If the absolute of this value is larger than the threshold set for movement detection and some change is also detected in the current frame pixel w.r.t. the reference background, then the global accumulator of the moving area is updated by adding the area of the road occupied by the current pixel. If the weighted difference is less than the threshold

for N-1 frames, then the algorithm updates the reference background pixel with the current pixel. N is the minimum number of frames required to declare the pixel to be part of the stationary background. The value of N can be set according to the application.

#### Algorithm 1 Background Subtraction algorithm

**Require:** Four grayscale images  $image_{-1}$ ,  $image_0$ ,  $image_1$  and  $image_{bg}$  & Count array

**Ensure:**  $image_{out}$ , Updated  $image_{bq}$  and Count array & Total Area with Movement

```

1: for j = 0 to HEIGHT - 1 do

2:

for i = 0 to WIDTH - 1 do

PIX = (j * WIDTH) + i

3:

lat = 0

4:

if PIX is on ROAD then

5:

center \leftarrow PIX

6:

left \leftarrow PIX - 10

7:

right \leftarrow PIX + 10

8:

lat \leftarrow Abs(sum of weighted difference of left, right and center pixels of

9:

all three images)

10:

end if

if (lat < threshold) & (Count[PIX] \geq N) then

11:

image_{bq}[center] \leftarrow image_0[center]

12:

else

13:

Count[PIX]++

14:

15:

if ((image_0[center] - image_{bq}[center] > Background threshold) & (lat > lat)

16:

threshold)) then

image_{out}[center] \leftarrow image_0[center]

17:

Increment Area with Movement

18:

else

19:

image_{out}[center] \leftarrow 0

20:

end if

21:

end for

22:

23: end for

```

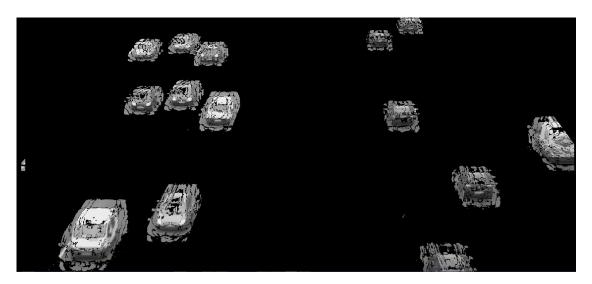

As described above, the algorithm needs three consecutive frames and a reference stationary background image to distinguish between moving and stationary objects. After the computation of one set of frames, the next frame is fed to the kernel and the oldest one is removed from the set. The result is shown in Figure

#### 3.7.

Here the static areas are detected as background and converted to black, while pixels where movements have been detected are shown as gray-scale pixels of the original frame. We also compute the portion of the road that is occupied by moving objects. In this set of frames, it is equal to  $11.2m^2$  on the side where traffic is coming towards the camera, and it is  $6.55m^2$  on the side where traffic is moving away from the camera.

Figure 3.7: Output of Background Subtraction

# 3.3.2 Lucas Kanade Algorithm

Since the background subtraction module can only find the area occupied by moving objects on the roads, another method is needed to measure the velocity of vehicles, based on the Lucas Kanade algorithm for optical flow [42]. An implementation of the Lucas Kanade's Optical Flow algorithm developed by Altera [52] in OpenCL with a 52x52 window size is shown in Fig. 3.8.

A window size of NxN means that the optical flow for one pixels is computed with respect to the neighboring N/2 pixels on each side of that pixel i.e. the pixel under consideration is in the center of a matrix of pixels having (N+1) rows and columns. For each pixel in the window, a partial derivative with respect to its horizontal  $(I_x)$  and vertical  $(I_y)$  neighbors is computed. The size of the window is a compromise between true negative and false positive change detection. Therefore it should be chosen by an expert with respect to area covered by each pixel and other parameters. In this paper we uses a 15x15 window.

A pyramidal implementation [12] is used to refine the optical flow calculation

and the iterative Lucas-Kanade Optical flow computation is used for the core calculations. For each pixel, computed partial derivatives within the window and the difference among the pixel values in the current and next frames are used to calculate the velocity of each moving object (it is zero if the area covered by the pixel is stationary). The magnitude is the speed of the object whereas the sign shows whether it moves towards the camera or away from it.

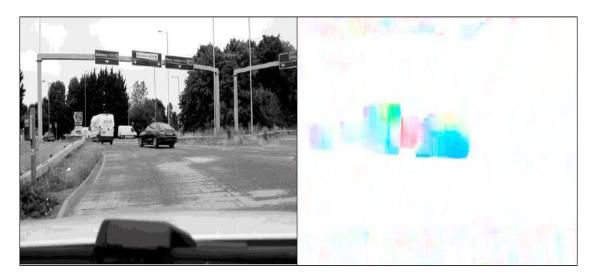

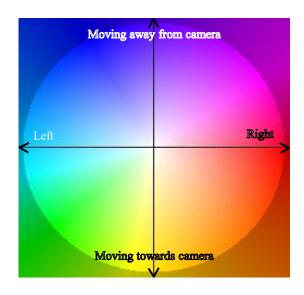

Figure 3.8: Altera's Implementation of Lucas Kanade Algorithm [52]

In our implementation of the Lucas-Kanade Algorithm (Algorithm 2), for each set of calculations, we need two consecutive image frames and a set of input parameters depending on the road conditions and camera angles. Similar to Background subtraction, each new frame replaces the older one. The optical flow is computed for all the pixels of the image (in this case for a 1280x720 resolution). Two images using 8 bits per pixel are compared with a window size of 15. Moreover, the obtained values are mapped to a single color representing both relative velocity and direction, as shown in figure 3.9. The graphical output from these images is shown in Fig. 3.10. The stationary regions are represented by white pixels, while moving objects are mapped to colors according to their speed and direction.

To calculate the average velocity of traffic with the Optical Flow algorithm one needs to know the distance between the camera and the recorded objects. In order to avoid expensive and complex solutions for a real time depth measurement, an approximation for calculating the distance corresponding to each pixel of the image is used based on static camera parameters, such as road plane inclination, camera orientation and field of view. For the current frame as reference. The average velocity coming towards the camera is about 118km/h while the velocity moving away is -67km/h.

## Algorithm 2 Lucas-Kanade algorithm

28: end for

```

Require: two frames of images image_0 and image_1 and other coefficients

Ensure: v_{\text{opt}}

1: for j = 0 to HEIGHT - 1 do

for i = 0 to WIDTH - 1 do

3:

G_{2\times 2} \leftarrow 0

b_{2\times 1} \leftarrow 0

4:

for w_j = -w_y to w_y do

5:

\mathbf{for}\ w_i = -w_x\ \mathbf{to}\ w_x\ \mathbf{do}

6:

center \leftarrow Pos(i + w_i, j + w_i)

7:

left \leftarrow Pos(i + w_i - 1, j + w_i)

8:

right \leftarrow Pos(i + w_i + 1, j + w_i)

9:

up \leftarrow Pos(i + w_i, j + w_i - 1)

10:

down \leftarrow Pos(i + w_i, j + w_j + 1)

11:

im_{\text{val}}^0 \leftarrow image_0[center]

12:

im_{\mathrm{val}}^{1} \leftarrow image_{1}[center]

13:

\delta I \leftarrow d(im_{\text{val}}^0, im_{\text{val}}^1)

14:

im_{\text{left}}^0 \leftarrow image_0[left]

15:

im_{\mathrm{right}}^{0} \leftarrow image_{0}[right]

16:

\begin{split} I_x &\leftarrow (im_{\mathrm{right}}^0 - im_{\mathrm{left}}^0)/2 \\ im_{\mathrm{up}}^0 &\leftarrow image_0[up] \end{split}

17:

18:

im_{\text{down}}^0 \leftarrow image_0[down]

19:

I_y \leftarrow (im_{\text{down}}^0 - im_{\text{up}}^0)/2

20:

G \leftarrow G + g_{2\times 2}(I_x, I_y)

21:

b \leftarrow b + f_{2 \times 1}(\delta I, I_x, I_y)

22:

end for

23:

end for

24:

G \leftarrow \text{inverse}(G)

25:

v_{\text{opt}}[j][i] \leftarrow G \times b

26:

end for

27:

```

We can also find the speed in any specific lane of the road, by dividing the pictures in separate lanes instead of two parts as we did in Fig. 3.5. This can be achieved, if required, by minor adjustments in the input configuration file.

Figure 3.9: Lucas Kanade's Disparity Map

Figure 3.10: Output of Lucas Kanade Algorithm

# 3.3.3 Implementation Model

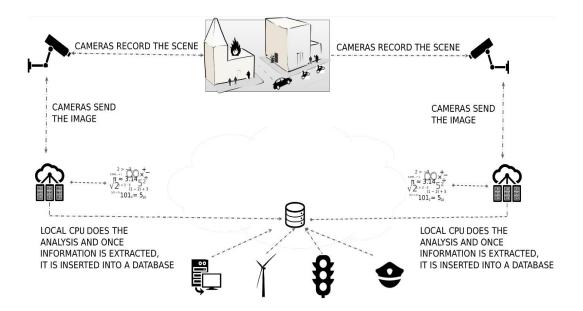

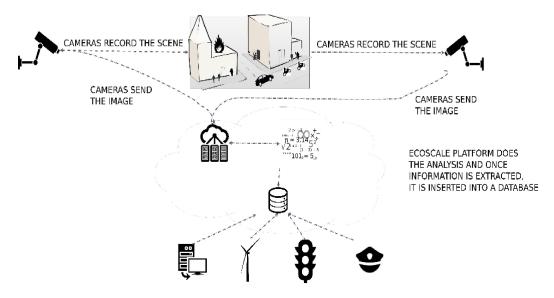

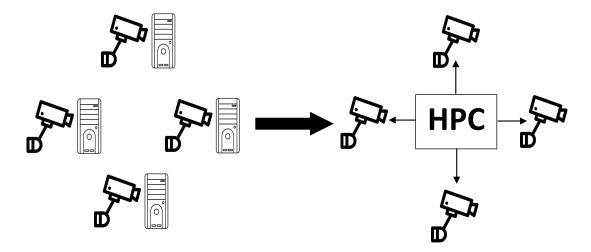

Two types of implementation are possible for this system on the basis of the location of computational and storage units. One is decentralized, where each camera has its own processing unit. The other is centralized, where all the processing by a set of closely situated cameras is done on one single server.

#### Decentralized Architecture

Figure 3.11: Decentralized Model

Fig. 3.11 represents the decentralized architecture version of the application. Due to the high computational requirements, a dedicated CPU would be needed for each camera installed in the monitored scenario. Once the image (which must be processed in real time) is captured, the pre-processing unit associated to that camera processes the signal for detecting the elements present in the image. Afterwards, it sends a picture with some meta-data to the central processing unit in which all of the information is processed and stored to be offered to the customers within a cloud architecture.

#### Centralized Architecture

On the other hand, Fig. 3.12 depicts an architecture in which one processing unit is used by a number of cameras. The idea is to combine the processing unit with the central database where all the data is offered to the customer. This means that no camera has a dedicated processing unit attached, which dramatically increases the amount of data to be processed centrally in real time.

After analyzing both options, the second alternative is considered more appropriate because of the costs of implementation, application software management, maintenance costs to resolve hardware failures, improved safety etc. In Figure 3.13, the scheme for the proposed solution is presented. A major factor for choosing a

STAKEHOLDERS RECEIVE THE INFORMATION VIA WEB SERVICE

Figure 3.12: Centralized Model

Figure 3.13: From decentralized to centralized architecture

centralized system would be the achievable energy efficiency by using latest generation FPGA devices, which are very power-efficient but too expensive to be deployed in a decentralized architecture.

# 3.4 Constraints

However, the use of cameras poses some disadvantages. The first major draw-back is the breach of privacy. Citizens usually feel uncomfortable and insecure when their movements are being monitored and they tend to oppose any such system. To overcome this disadvantage, the end users of our application are not given the raw data. Rather they are provided with only the result of the processing of the images recorded by the cameras. This ensures both the protection of personal information and the value of data.

Note that, in our implementation of the application, the processed images or data extracted from them contain no personal information, thus we can safely say that we have achieved the objective of personal data integrity and we are not forwarding any sort of personal or privileged information to any third party.

Another difficulty in the use of such systems is the huge effort required to compute and process data by image analysis algorithms. For instance, cameras should be deployed every 50 meters or so in order to obtain a density that can provide complete information for a city. A big city with an urban area of  $360km^2$  would require the use of about 100,000 active cameras. This can be supported only by extreme parallel computing techniques.

This issue is resolved by the use of centralized architecture. Moreover the computational power is provided by the ECOSCALE platform, whose architecture is discussed in Chapter 2. Therefore, we can say that the application can be implemented in real world.

# 3.5 Optimizations

Most of the operations carried out in image processing are pixel-based, with no or very few dependencies on other pixel output values. This provides a very good basis for a parallel implementation of image processing algorithms that work on each pixel either simultaneously or in a pipelined fashion (Fig. 3.14). In this way we can reduce the frame processing time and hence we can achieve a real time processing frequency, which is about 25fps for the target application.

Several optimization that we performed on the code to make it optimal for FPGA design are explained below.

# 3.5.1 Memory-related optimizations

In the context of memory-related key issues and observations, it has to be stated that the most important aspect that affects performance is the data I/O to and from the host as well as the hardware accelerators. The highest I/O bandwidth can be achieved by using streams and DMA controllers. This approach though

Figure 3.14: Overview of parallelism in image processing Algorithms

has one critical restriction, requiring that the data have to be stored in contiguous memory space, which is not always possible. In this application, the kernels are generated using OpenCL which only supports memory mapped interfaces. As a result streams cannot be utilized. Hence, we require other methods and coding examples that make the memory mapped interface as efficient as possible. In the ideal scenario it can achieve comparable bandwidth to the streaming case, i.e. only two times slower. These methods can be categorised as follows:

- Inferring memory bursts

- Utilizing the maximum bus width

- Eliminating unnecessary memory accesses

## **Inferring Memory Bursts**

As mentioned above OpenCL kernels do not support streaming interfaces, they support the AXIIite and AXI master interfaces. The AXImaster interface supports memory bursts of up to 256 words on the Ultrascale+ FPGAs.

Subsequently, in order for the kernel to infer memory bursts, the code has to be written in certain ways, which the tool can identify and produce the correct interface that accesses the memory using bursts. The first way is the usage of a function defined for this purpose  $async\_work\_group\_copy()$  and the second is to read the data into local or private memory, which is using BRAMs in the FPGA,

inside a for loop. The async\_work\_group\_copy() function is defined for OpenCL language and transfer data between global and local (work group) memory only. It cannot transfer data for private memory. The maximum burst size supported is 256 words per burst. The following code segment (Fig. 3.15) describes how bursts can be inferred using a pipelined for loop.

Figure 3.15: Example for burst access of data from DRAM

#### Utilization of maximum Bus width

Another really important optimization is the utilization of the maximum bus width. In our case that is 128bits which is restricted by the host HP ports that are used for communication between the processing system and the programmable logic. In order for the kernel to have a 128-bit data width, the arguments must use vector data types, e.g. float4, int4 etc. This allows the most efficient utilization of the PS-PL bandwidth as it utilizes the full width of the HP ports.

#### Eliminating Unnecessary Memory Accesses

The previous two subsections provide I/O optimization that are platform and technology specific and always affect performance. Here, we present memory-related optimization that is application specific and concern mainly the minimization of the DDR memory accesses.

Based on the source code description of an algorithm, it is not possible for the platform to recognize whether the application accesses the same data multiple times from the DDR memory or not. Hence, depending on the application, it highly recommended to increase the usage of temporary buffers (BRAMs) or temporary registers, that store data inside the PL to be further processed, since this can significantly improve the performance as it reduces DDR accesses. For example in the case of image filter applications, line buffers can be used to store the lines or pixels required for the filter. A 3x3 filter requires 9 memory accesses per result. If the data are stored in line buffers the same operation requires only 1 memory access as the data are already stored in BRAMs.

# 3.5.2 Computational optimization

In this subsection we provide a summary of source code optimization that were implemented to generate an efficient hardware accelerator module that will eventually lead to a cost-effective application execution. These guidelines are principally split into the following sections.

- Loop pipeling and unrolling

- Array partitioning

- Minimization of operations using temporary registers

- Division using constants

- Reusing the calculations

- Piecewise Linear approximation

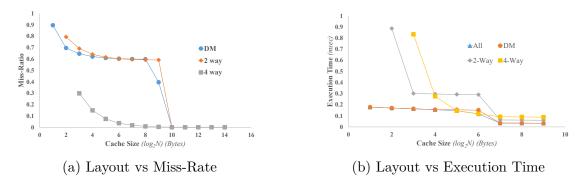

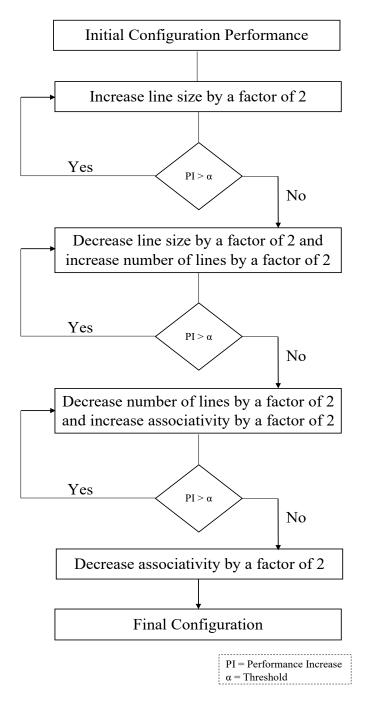

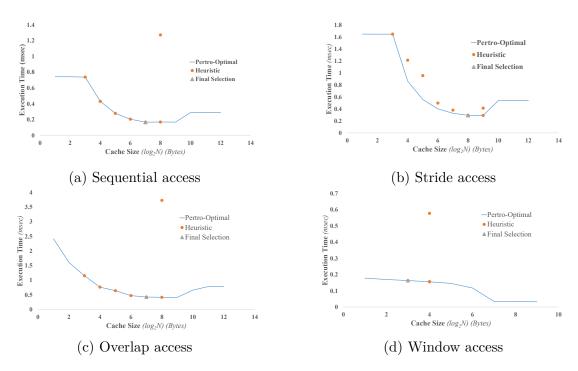

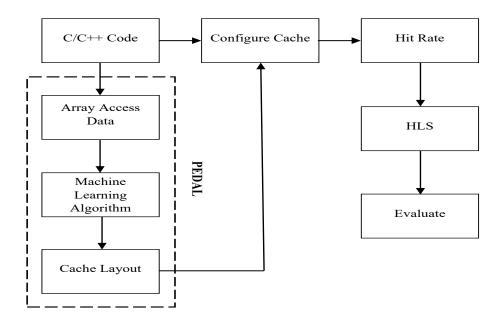

#### Loop pipelining and unrolling