# $\label{eq:Doctoral Dissertation} Doctoral \ Program \ in \ Electronic \ and \ Telecommunication \ Engineering \ (30^{th} cycle)$

# Design and testing of CMOS radiation detectors for High Energy Physics Experiments

By

#### Serena Panati

\*\*\*\*\*

#### **Supervisors:**

Angelo Rivetti, Supervisor Michele Goano, Co-Supervisor

#### **Doctoral Examination Committee:**

Michela Greco, University of Turin Gianluca Traversi, University of Bergamo

Politecnico di Torino 2018

#### **Declaration**

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Serena Panati 2018

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

Said the straight man to the late man "Where have you been?" "I've been here and I've been there and I've been in between"

#### **Abstract**

In recent years, the study and the development of novel architectures and technologies to improve performance of silicon pixel detectors became a pivotal node for High Energy Physics (HEP) experiments. Their extremely tight constraints of spatial resolution, low power dissipation, speed, granularity, signal-to-noise ratio and radiation hardness, led the scientific community to continuously research new solutions to satisfy newer and more stringent requirements. In this context, the two main categories of detectors technologies have been represented by Hybrid Pixel Detectors (HPDs) and Monolithic Active Pixel Sensors (MAPS).

Traditionally, HPDs constitute the more widespread technology for particle pixel detectors: due to their excellent characteristics, they are adopted for the inner layers of the most of current main HEP experiments. However, on the other side, the relatively novel monolithic sensors technology became recently more and more interesting as leading replacing technology due to its improved radiation hardness and the lower material budget and cost with respect to HPDs.

In this thesis an introduction to these technologies will be carried out and some related research results will be shown.

In Chapter 1 Hybrid Pixel Detectors technology will be described, with an additional part dedicated to some literature examples about HEP experiments which adopted this kind of sensors for their inner layers. This chapter acts as an introduction to the CHIPIX65 (*CHIp for PIXel detector in a 65 nm process*) prototype shown in Chapter 3 and to the Phase-Locked Loop described in Chapter 5.

In Chapter 2 MAPS (Monolithic Active Pixel Sensors) technology will be introduced, from the early prototypes based on 3-T and 4-T architecture until the last examples of monolithic sensors implemented inside more recent particle detectors upgrades. This part is preparatory to Chapter 5, where the MATISSE prototype is described both to the development and to the testing point of view.

Chapter 3 is dedicated to CHIPIX65 project and the development of a novel prototype of an 65 nm CMOS HPD: realized in collaboration of some INFN Italian groups, this is the first example of HPD fully developed in a sub-micron CMOS technology. Starting with a short introduction to architecture and readout modes, this chapter shows some important testing results presented in Strasbourg during an IEEE MIC-NSS Conference talk in 2016.

Chapter 4 is fully dedicated to a low-noise and compact Phase-Locked Loop (PLL) built in the same 65 nm CMOS technology. After some theoretical and introductory sections, the prototype will be described and test results provided.

Chapter 5 is fully dedicated to the development and test of a prototype of MAPS, called MATISSE (*Monolithic AcTIve pixel SenSor Electronics*). Developed by INFN groups of Turin and Padua, University of Trento and TIFPA, it is an example of a fully-depleted monolithic active sensor. Here, some sensor and readout electronics will be described, followed by some tests. These results have been presented during a poster session in Atlanta during the IEEE MIC-NSS Conference in 2017.

Appendices will cover some follow-up topics related to the previous sections.

Appendix A summarizes radiation effects on silicon devices, both total dose and heavy-ions effect: this section is useful to referring to all the parts related to radiation hardness tests of described prototypes.

Appendix B outlines some practical guidelines about Process Design Kit (PDK) of a given technology process. Indeed, before starting the design of any ASIC device, a PDK needs to be provided by the foundry, installed and configured in order to allow to work with.

Appendix C is dedicated to some theoretical issues on oscillator phase noise, which represent a huge subject in Phase-Lock Loop theory; however, since it is not covered by the analysis and tests on the PLL prototype, it has been chosen to put this part separately to Chapter 4.

## **Contents**

| Li | st of l | Figures       |             |                                | XV  |

|----|---------|---------------|-------------|--------------------------------|-----|

| Li | st of ' | <b>Fables</b> |             |                                | xxi |

| 1  | Hyb     | rid pixe      | el detector | s                              | 1   |

|    | 1.1     | Introdu       | uction to h | ybrid pixel detectors          | 1   |

|    |         | 1.1.1         | Some exa    | amples                         | 4   |

|    |         |               | 1.1.1.1     | FPix2                          | 4   |

|    |         |               | 1.1.1.2     | Topix v4                       | 6   |

|    |         |               | 1.1.1.3     | TimePix3                       | 8   |

|    |         |               | 1.1.1.4     | VELOpix                        | 9   |

| 2  | Mor     | olithic       | pixel dete  | ctors                          | 13  |

|    | 2.1     | Introd        | uction to m | nonolithic pixel detectors     | 13  |

|    |         | 2.1.1         | Generalia   | a                              | 13  |

|    |         |               | 2.1.1.1     | Early architectures: 3T and 4T | 14  |

|    |         | 2.1.2         | Some exa    | amples                         | 17  |

|    |         |               | 2.1.2.1     | LePix                          | 17  |

|    |         |               | 2.1.2.2     | ALPIDE                         | 18  |

| 3  | The     | СНІРІ         | X65 nroje   | ct                             | 2.1 |

x Contents

|   | 3.1  | Backgr   | round and motivation                                         |

|---|------|----------|--------------------------------------------------------------|

|   |      | 3.1.1    | RD53 collaboration                                           |

|   |      | 3.1.2    | CHIPIX65 project                                             |

|   | 3.2  | The CI   | HIPIX65 demonstrator                                         |

|   |      | 3.2.1    | Analog Architecture                                          |

|   |      | 3.2.2    | Region digital architecture                                  |

|   |      |          | 3.2.2.1 Pixel data acquisition and synchronization 31        |

|   |      |          | 3.2.2.2 Operation modes                                      |

|   |      |          | 3.2.2.3 Readout                                              |

|   |      |          | 3.2.2.4 Chip configuration, End of Column readout and I/O 33 |

|   |      |          | 3.2.2.5 SLVS drivers and padframe                            |

|   |      | 3.2.3    | Bias network and monitoring                                  |

|   | 3.3  | Test re  | sults                                                        |

|   |      | 3.3.1    | Calibration DAC and monitoring ADC                           |

|   |      | 3.3.2    | Synchronous front-end                                        |

|   |      |          | 3.3.2.1 Calibration voltage scans                            |

|   |      |          | 3.3.2.2 Threshold voltage scans                              |

|   |      | 3.3.3    | Asynchronous front-end                                       |

|   | 3.4  | Conclu   | sions                                                        |

| 4 | Phas | se locke | d-loops 49                                                   |

| • |      |          | •                                                            |

|   | 4.1  |          | action to phase-locked loops                                 |

|   |      | 4.1.1    | History and applications                                     |

|   | 4.2  | Phaselo  | ock-loop fundamentals                                        |

|   |      | 4.2.1    | Working principle                                            |

|   |      |          | 4.2.1.1 Noise suppression                                    |

Contents xi

|   | 4.3 | Buildir  | ng blocks o | design and implementation              | 53 |

|---|-----|----------|-------------|----------------------------------------|----|

|   |     | 4.3.1    | Voltage (   | Controlled Oscillator (VCO)            | 53 |

|   |     | 4.3.2    | Phase det   | tector (PD)                            | 53 |

|   |     |          | 4.3.2.1     | Multiplier phase detector              | 53 |

|   |     |          | 4.3.2.2     | EXOR phase detector                    | 56 |

|   |     |          | 4.3.2.3     | JK-FF phase detector                   | 57 |

|   |     |          | 4.3.2.4     | Phase and frequency detector           | 60 |

|   | 4.4 | Jitter . |             |                                        | 63 |

|   |     | 4.4.1    | Timing ji   | tter                                   | 63 |

|   |     |          | 4.4.1.1     | Different kind of jitter               | 64 |

|   | 4.5 | The pro  | ototype .   |                                        | 65 |

|   |     | 4.5.1    | Design a    | nd implementation                      | 65 |

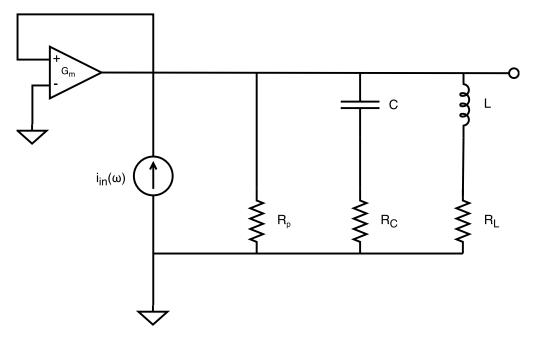

|   |     |          | 4.5.1.1     | LC-Voltage Controlled Oscillator       | 67 |

|   |     |          | 4.5.1.2     | Frequency and Phase Detector           | 68 |

|   |     |          | 4.5.1.3     | Charge pump PD                         | 69 |

|   |     |          | 4.5.1.4     | Frequency Divider                      | 72 |

|   |     |          | 4.5.1.5     | Output Driver                          | 72 |

|   |     | 4.5.2    | Test resu   | lts                                    | 75 |

|   |     | 4.5.3    | N-cycle j   | itter performance                      | 77 |

|   |     |          | 4.5.3.1     | Total Ionizing Dose (TID) test results | 78 |

|   | 4.6 | Conclu   | isions      |                                        | 84 |

| 5 | The | MATIC    | SE protot   | Almo                                   | 85 |

| 3 |     |          | •           | •                                      |    |

|   | 5.1 |          |             | motivation                             | 85 |

|   | 5.2 |          |             | ent                                    |    |

|   |     | 5.2.1    | State of t  | he art                                 | 88 |

**xii** Contents

|          |             | 5.2.2          | The MATISSE sensor                    |

|----------|-------------|----------------|---------------------------------------|

|          | 5.3         | Front I        | End Electronics                       |

|          |             | 5.3.1          | Pinout description                    |

|          |             | 5.3.2          | Pixel matrix                          |

|          |             | 5.3.3          | End of Column                         |

|          |             | 5.3.4          | Readout management signals and timing |

|          |             | 5.3.5          | Programming                           |

|          |             |                | 5.3.5.1 Procedure                     |

|          |             | 5.3.6          | Voltage supply and analog bias        |

|          |             | 5.3.7          | Readout modes                         |

|          |             |                | 5.3.7.1 Diode reset                   |

|          |             |                | 5.3.7.2 Standard mode                 |

|          |             |                | 5.3.7.3 Test pulse mode               |

|          |             |                | 5.3.7.4 Fixed pixel mode              |

|          | 5.4         | Tests .        |                                       |

|          |             | 5.4.1          | Data Acquisition System               |

|          |             | 5.4.2          | Power consumption                     |

|          |             | 5.4.3          | Test pulse linearity                  |

|          |             | 5.4.4          | Noise measurements                    |

|          |             | 5.4.5          | <sup>55</sup> Fe irradiation tests    |

|          |             | 5.4.6          | Storage time                          |

|          | 5.5         | Conclu         | isions                                |

| <b>A</b> | Dad!        | la <b>ti</b> a | ffeets on ciliagn devices             |

| A        |             |                | ffects on silicon devices 131         |

|          | <b>A.</b> 1 | Dose u         | nits                                  |

|          | A 2         | Total Γ        | Dose Effects 132                      |

| Contents | xiii |

|----------|------|

|----------|------|

|    | A.3                                 | Heavy-   | Ion Effect | s                                                        | 133 |

|----|-------------------------------------|----------|------------|----------------------------------------------------------|-----|

|    | A.3.1 Types of Single Event Effects |          |            | Single Event Effects                                     | 133 |

|    |                                     |          | A.3.1.1    | SEU                                                      | 133 |

|    |                                     |          | A.3.1.2    | MBU                                                      | 134 |

|    |                                     |          | A.3.1.3    | SEFI                                                     | 134 |

|    |                                     |          | A.3.1.4    | SET                                                      | 134 |

|    |                                     |          | A.3.1.5    | SED                                                      | 134 |

|    |                                     |          | A.3.1.6    | SHE                                                      | 135 |

|    |                                     |          | A.3.1.7    | SEL                                                      | 135 |

|    |                                     |          | A.3.1.8    | SESB                                                     | 135 |

|    |                                     |          | A.3.1.9    | SEB                                                      | 135 |

|    |                                     |          | A.3.1.10   | SEGR                                                     | 136 |

|    |                                     |          | A.3.1.11   | SEDR                                                     | 136 |

|    |                                     | A.3.2    | Mitigatio  | n Techniques                                             | 136 |

| В  | Proc                                | ess Desi | ign Kit (P | DK) installation and maintenance                         | 141 |

| C  | Phas                                | se noise |            |                                                          | 145 |

|    |                                     | C.0.1    | Oscillator | r phase noise: general theory                            | 145 |

|    |                                     |          | C.0.1.1    | Background and definitions                               | 146 |

|    |                                     |          | C.0.1.2    | Excess phase impulse response model                      | 149 |

|    |                                     |          | C.0.1.3    | Transformation of phase to voltage                       | 150 |

|    |                                     |          | C.0.1.4    | Phase noise sideband power prediction                    | 150 |

|    |                                     |          | C.0.1.5    | Sources of cyclostationary noise                         | 151 |

|    |                                     |          | C.0.1.6    | Output phase noise with multiple noise source prediction | 152 |

| Re | feren                               | ces      |            |                                                          | 153 |

## **List of Figures**

| 1.1 | Section of a generic hybrid pixel detector                                                                                                                                                                     | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Flip-chip technique                                                                                                                                                                                            | 3  |

| 1.3 | ToPix v4 close-up.                                                                                                                                                                                             | 6  |

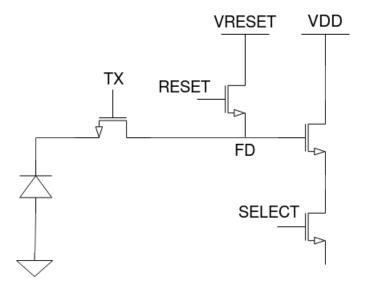

| 2.1 | The 3T MAPS architecture                                                                                                                                                                                       | 14 |

| 2.2 | The 4T MAPS architecture                                                                                                                                                                                       | 15 |

| 2.3 | A general scheme for a Monolithic Active Pixel Sensor                                                                                                                                                          | 16 |

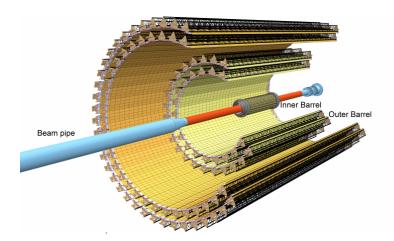

| 2.4 | Inner Tracking System section; inner and outer barrel are highlighted (image via [1])                                                                                                                          | 19 |

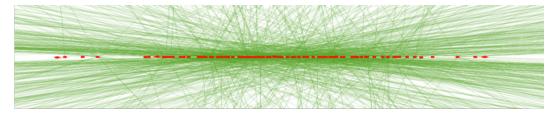

| 3.1 | HL-LHC pileup graphic simulation                                                                                                                                                                               | 21 |

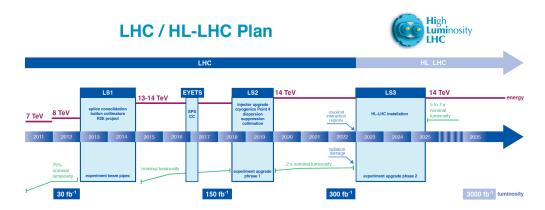

| 3.2 | Roadmap of HL-LHC Project                                                                                                                                                                                      | 22 |

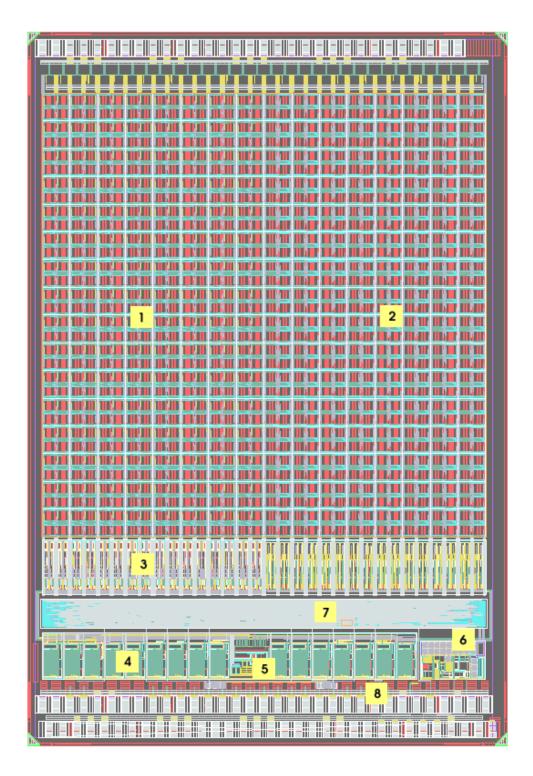

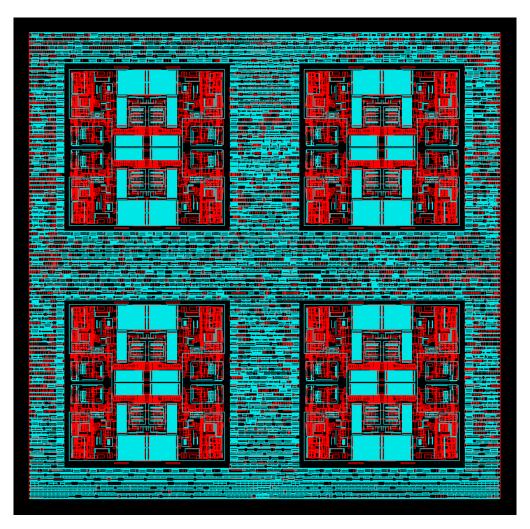

| 3.3 | CHIPIX65 demonstrator layout                                                                                                                                                                                   | 26 |

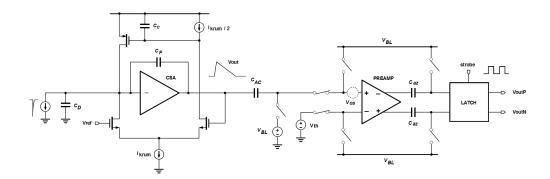

| 3.4 | Schematic view of the synchronous front-end. From left: Krummenacher feedback charge-sensitive amplifier, AC coupling and track-and-latch voltage comparator with auto-zeroing obtained with the OOS technique | 28 |

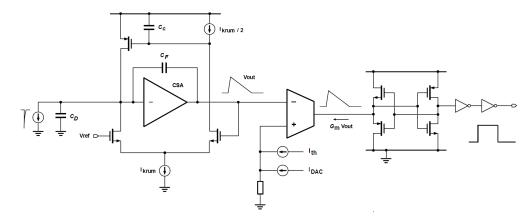

| 3.5 | Schematic view of synchronous front-end chain. From left: Krummenacher feedback charge-sensitive amplifier, voltage-to-current transconductor and fast current comparator.                                     | 29 |

xvi List of Figures

| 3.6  | Pixel region ( $4\times4$ pixel) layout. As it is possible to see, each pixel region contains $2\times2$ analog islands (sixteen analog front-ends) with                                                             |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | a common digital logic architecture                                                                                                                                                                                  | 30 |

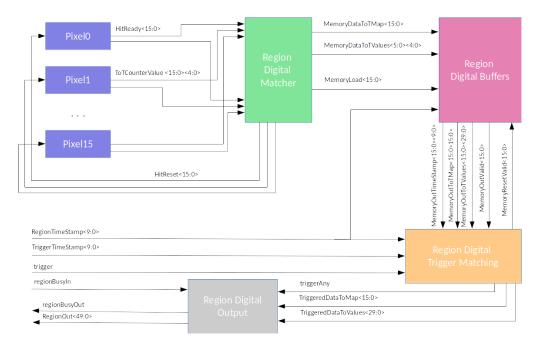

| 3.7  | Digital architecture functional scheme                                                                                                                                                                               | 31 |

| 3.8  | Output packet scheme                                                                                                                                                                                                 | 32 |

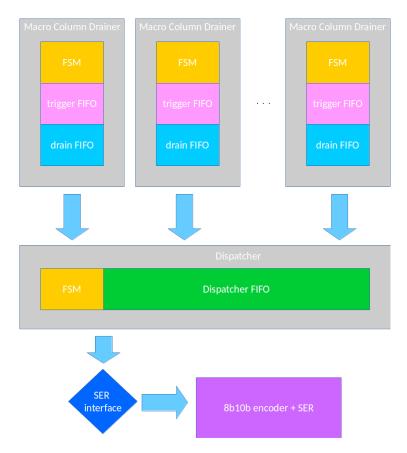

| 3.9  | Macro Column Drainers readout flow                                                                                                                                                                                   | 34 |

| 3.10 | SPI packet division                                                                                                                                                                                                  | 35 |

| 3.11 | Drivers and SLVS pads                                                                                                                                                                                                | 35 |

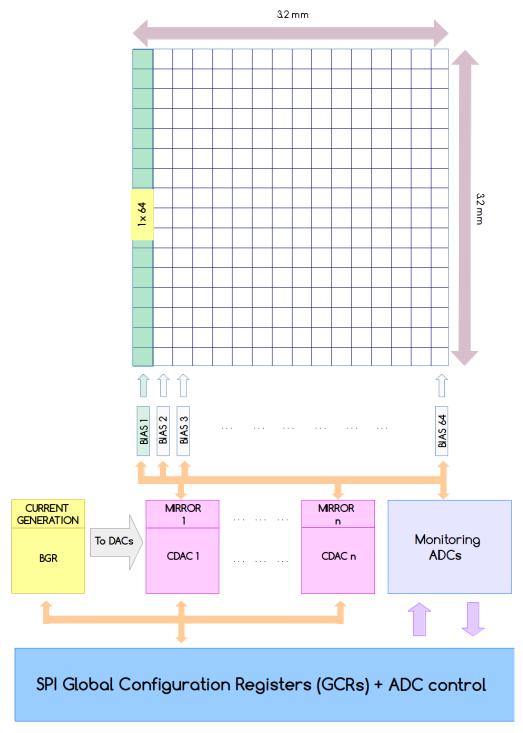

| 3.12 | Block scheme depicting monitoring network and bias                                                                                                                                                                   | 37 |

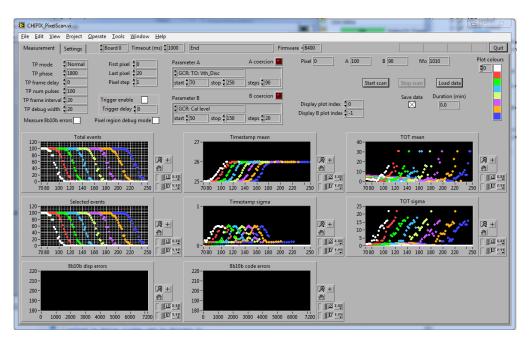

| 3.13 | LabVIEW interface for data acquisition                                                                                                                                                                               | 38 |

| 3.14 | Test setup at the INFN Torino laboratory.                                                                                                                                                                            | 39 |

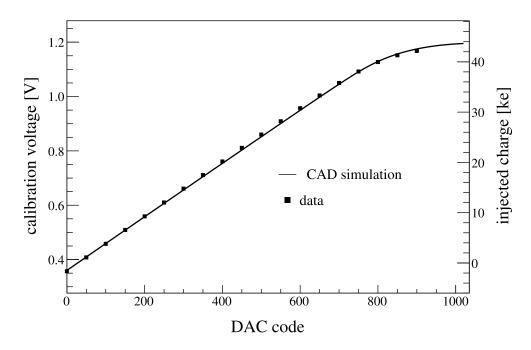

| 3.15 | Test results and CAD simulation data of calibration DAC (plot via [2]).                                                                                                                                              | 40 |

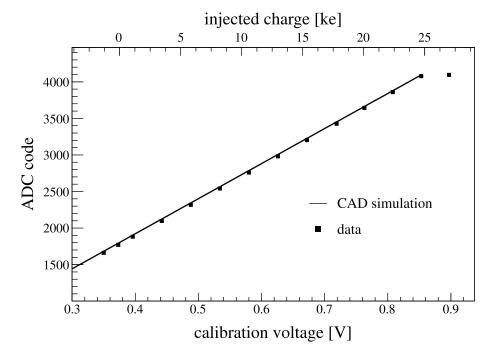

| 3.16 | Test results and CAD simulation data of monitoring ADC (plot via [2])                                                                                                                                                | 40 |

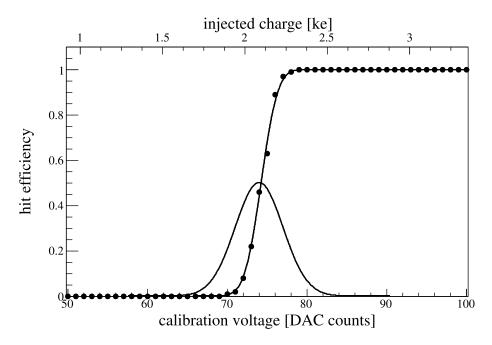

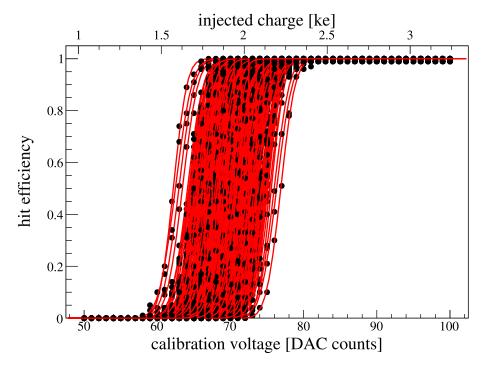

| 3.17 | Charge scan measurements; fit by using a sigmoid error function (plot via [2])                                                                                                                                       | 41 |

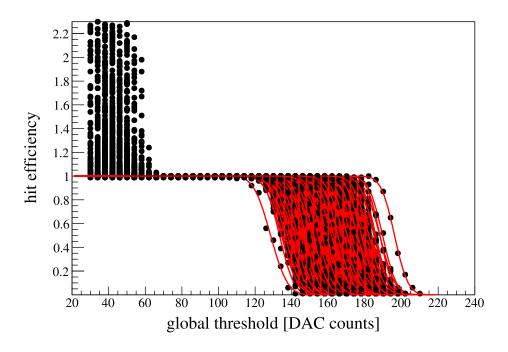

| 3.18 | Synchronous front-end: calibration voltage scan for all the pixel (plot via [2])                                                                                                                                     | 42 |

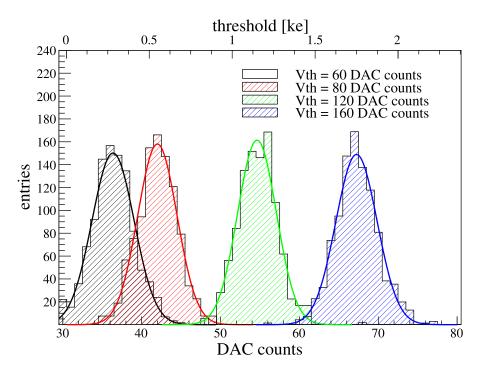

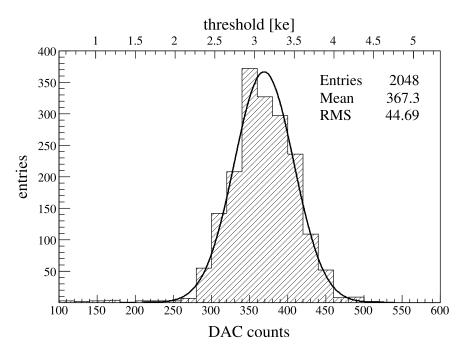

| 3.19 | Synchronous front-end: effective threshold measurement distribution for different values of fixed global threshold (plot via [2])                                                                                    | 43 |

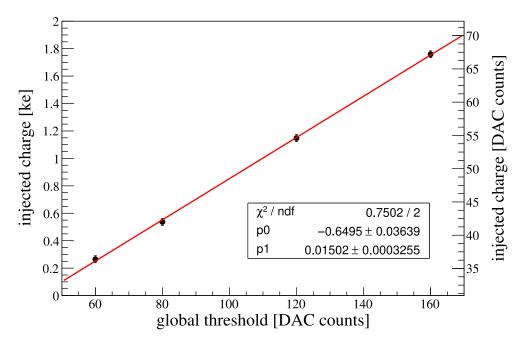

| 3.20 | Global threshold expressed in DAC counts vs injected charge with linear fit (plot via [2])                                                                                                                           | 43 |

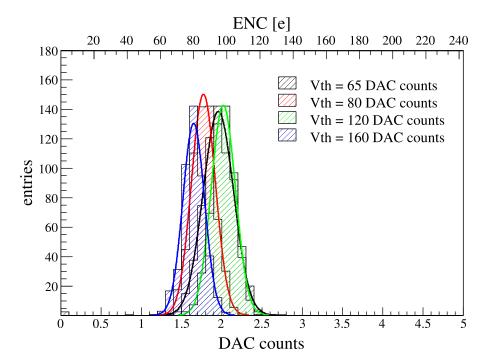

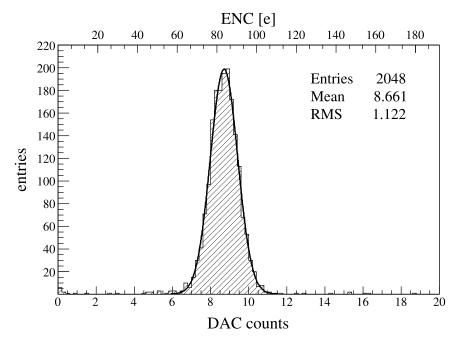

| 3.21 | Synchronous front-end Equivalent Noise Charge (ENC) measurements for some different fixed global threshold values. All the pixels in the array use a minimum common threshold (equal to $\sim 250~\text{e}^-$ ) [2]. | 44 |

| 3.22 | Fixed-charge scan curves (plot via [2])                                                                                                                                                                              | 45 |

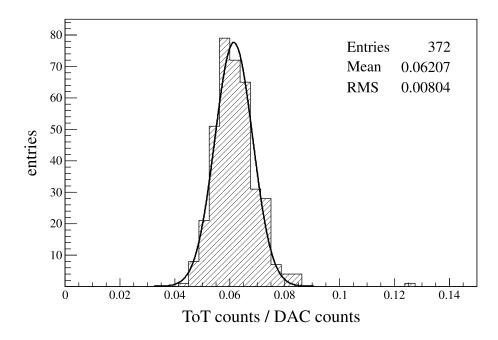

| 3.23 | ToT linearity for a single pixel (plot via [2])                                                                                                                                                                      | 45 |

| 3.24 | ToT slopes distribution (plot via [2])                                                                                                                                                                               | 46 |

List of Figures xvii

| 3.25 | Distribution of effective threshold measured for different values of                                                                                                              |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | fixed global threshold for the asynchronous front-end (plot via [2])                                                                                                              | 47 |

| 3.26 | Equivalent Noise Charge (ENC) values measured for different values of fixed global threshold for the asynchronous front-end (plot via [2]).                                       | 47 |

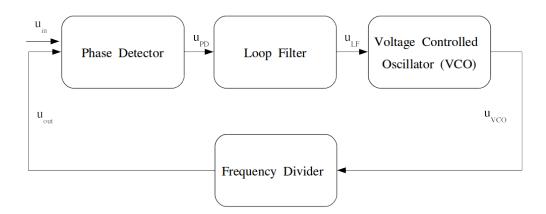

| 4.1  | A basic phase-locked loop scheme                                                                                                                                                  | 51 |

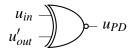

| 4.2  | EXOR phase detector scheme                                                                                                                                                        | 56 |

| 4.3  | EXOR phase detector waveforms. a) Zero-phase case. b) Case with a positive phase $\theta_e$                                                                                       | 56 |

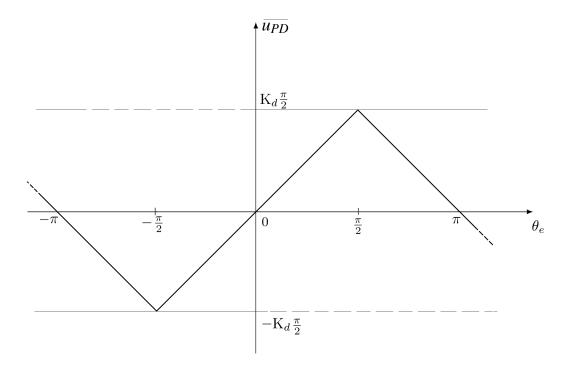

| 4.4  | EXOR phase detector averaged output signal versus phase: case with $u_{in}$ and $u'_{out}$ symmetrical square waveforms                                                           | 57 |

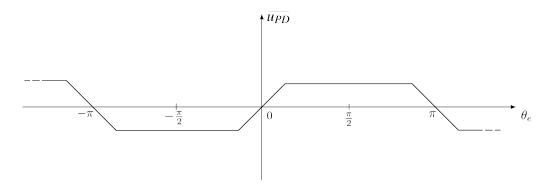

| 4.5  | EXOR phase detector averaged output signal $u_{PD}$ versus phase: case with $u_{in}$ and $u'_{out}$ asymmetrical square waveforms. It is possible to see a clipped curve behavior | 58 |

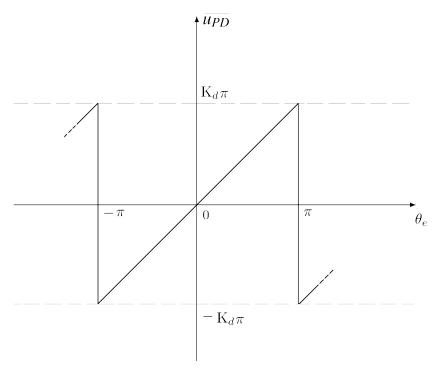

| 4.6  | JK-flip flop phase detector scheme                                                                                                                                                | 58 |

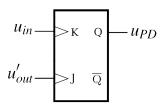

| 4.7  | JK-flip flop phase detector waveforms. a) Zero-phase case. b) Case with a positive phase $\theta_e$                                                                               | 58 |

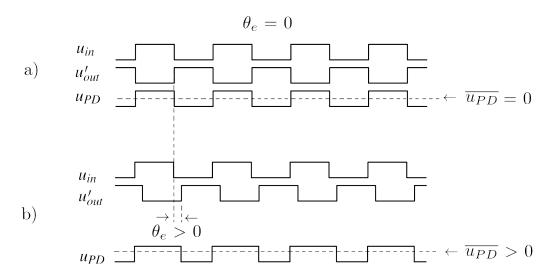

| 4.8  | EXOR phase detector averaged output signal versus phase: in this case, in contrast with the previous ones, the asymmetry between input signals does not produce clipping          | 59 |

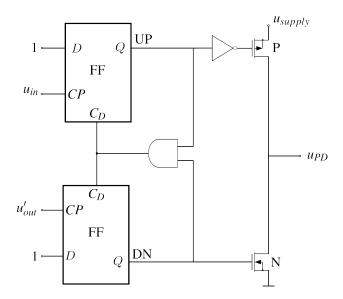

| 4.9  | Phase-Frequency detector general scheme                                                                                                                                           | 60 |

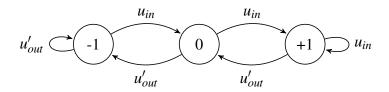

| 4.10 | PFD state machine. State variations are rising-edge defined                                                                                                                       | 61 |

| 4.11 | PFD phase detector waveforms. a) Zero-phase case. b) Case with a positive phase $\theta_e$ . c) Case with a negative phase $\theta_e$                                             | 61 |

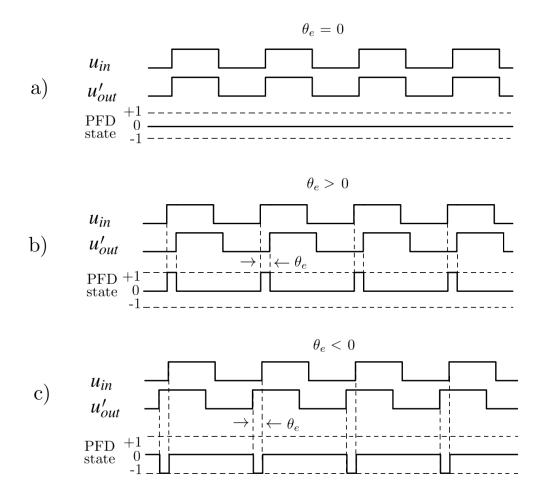

| 4.12 | PFD average of $u_d$ ; here are depicted values for phase error values greater than $2\pi$ and smaller than $-2\pi$ as well                                                       | 62 |

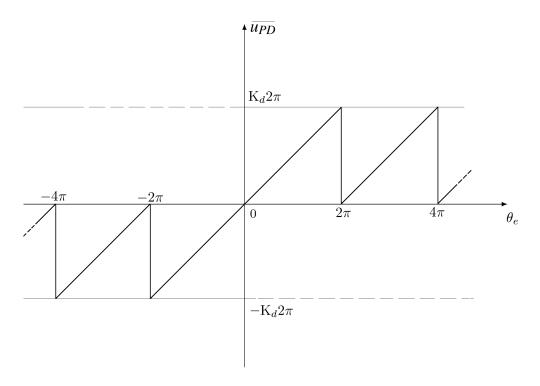

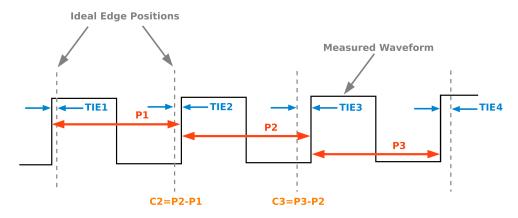

| 4.13 | Different measurement of jitter. Dotted vertical lines represent ideal positions of the edges of a jitter-free clock-like signal                                                  | 64 |

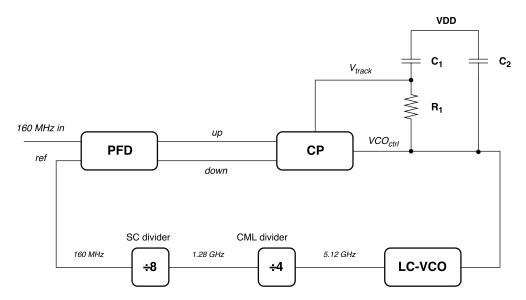

| 4.14 | PLL general and simplified schematic                                                                                                                                              | 66 |

xviii List of Figures

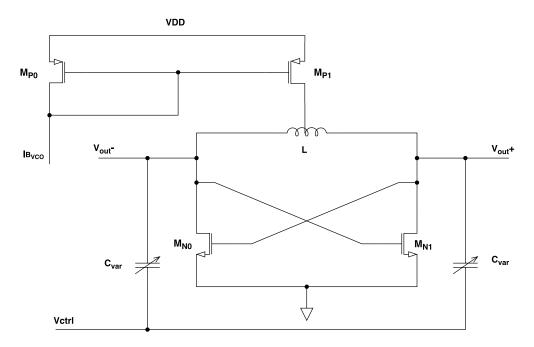

| 4.15 | VCO general schematic                                                                                                                                         | 66 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

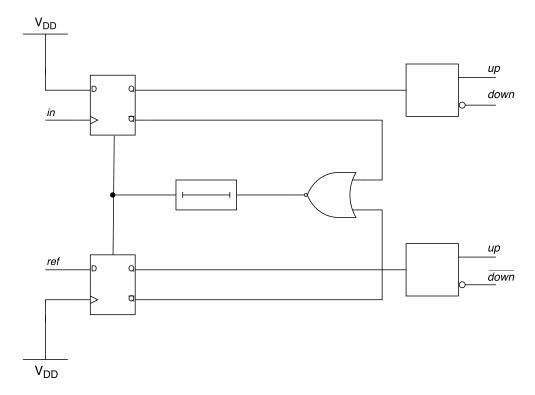

| 4.16 | Phase and frequency detector scheme                                                                                                                           | 68 |

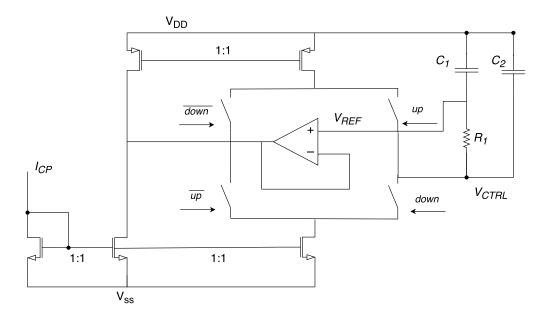

| 4.17 | Charge-Pump circuit schematic                                                                                                                                 | 69 |

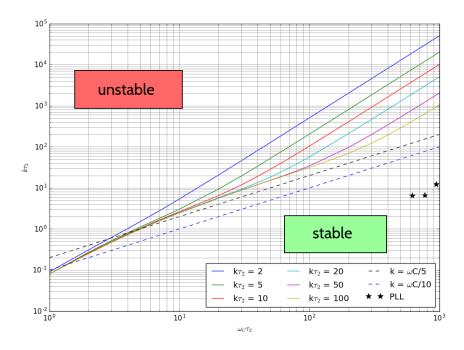

| 4.18 | Stability limits (third order loop) for different values of <i>b</i> : values above the curve depict unstable loops while values below represent stable loops | 71 |

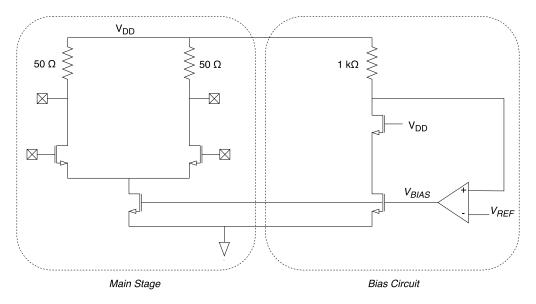

| 4.19 | Output driver schematic                                                                                                                                       | 72 |

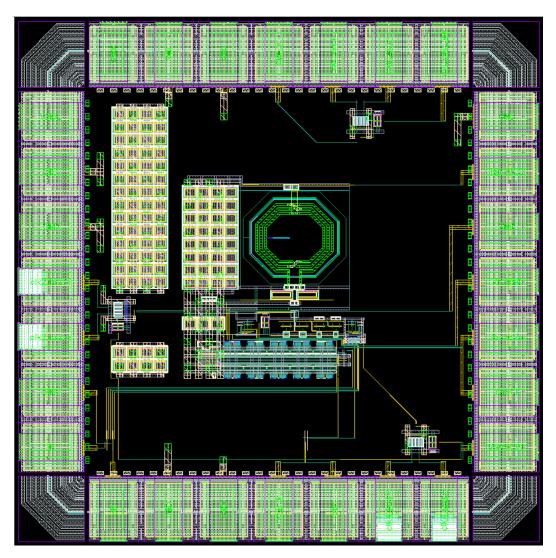

| 4.20 | ECAD schematic view of the layout of the circuit                                                                                                              | 74 |

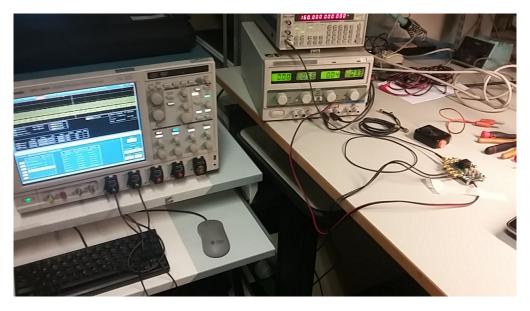

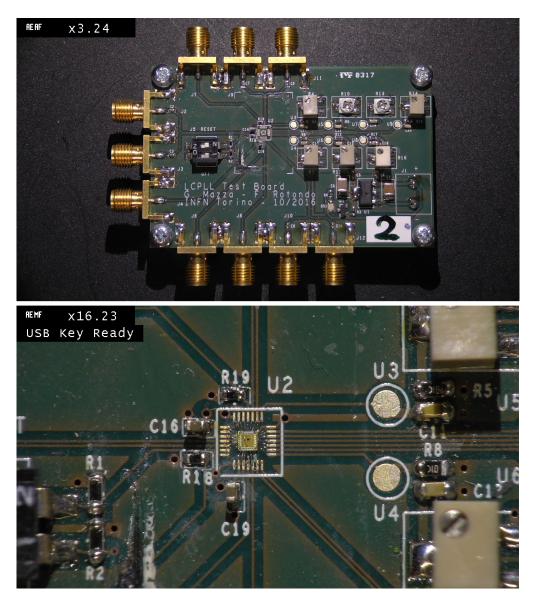

| 4.21 | Test setup in Torino (Electronic Laboratory)                                                                                                                  | 75 |

| 4.22 | The PLL PCB board with a PLL on it                                                                                                                            | 76 |

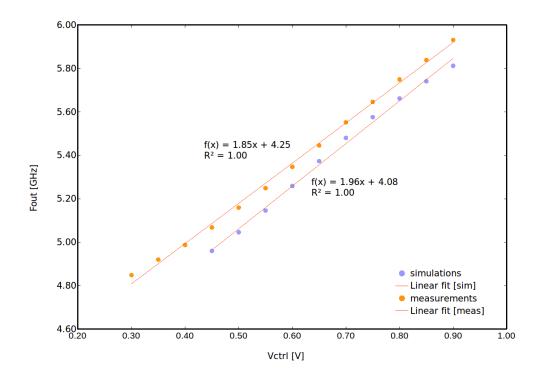

| 4.23 | VCO transfer function: simulation vs measurement data                                                                                                         | 77 |

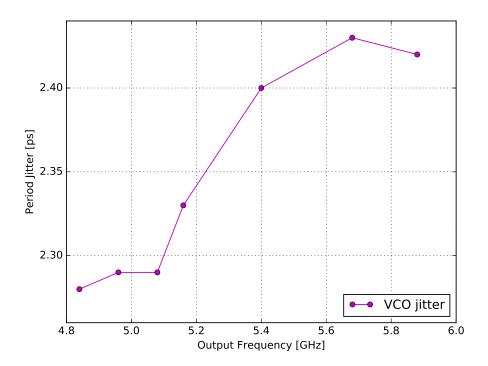

| 4.24 | VCO period jitter                                                                                                                                             | 78 |

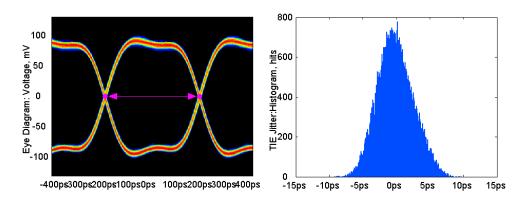

| 4.25 | Eye diagram of the $F_{VCO}$ output (1.28 GHz)                                                                                                                | 78 |

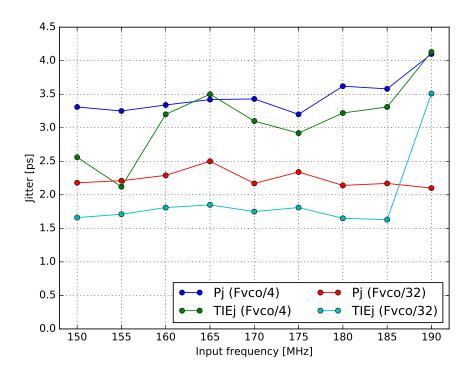

| 4.26 | PLL jitter measurements                                                                                                                                       | 79 |

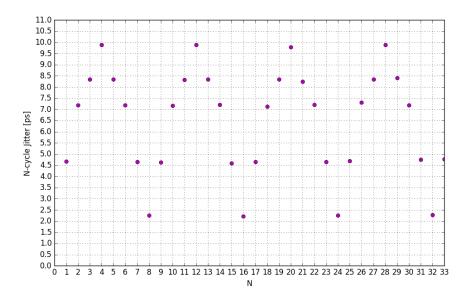

| 4.27 | Peridicity of the N-cycle jitter vs N number                                                                                                                  | 79 |

| 4.28 | A picture of the X-ray facility at INFN Padova                                                                                                                | 80 |

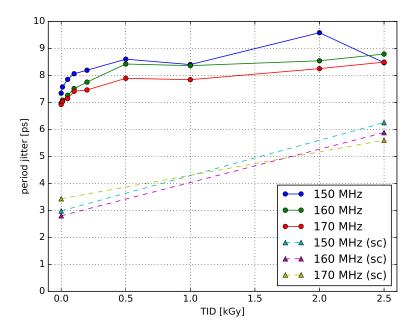

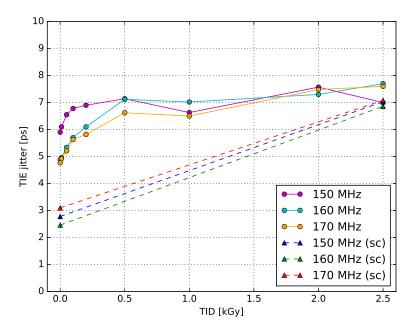

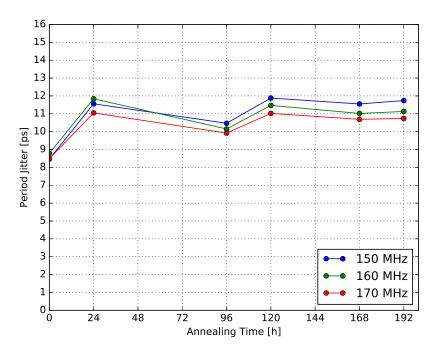

| 4.29 | Jitter levels vs total ionizing dose                                                                                                                          | 81 |

| 4.30 | Annealing measurements                                                                                                                                        | 82 |

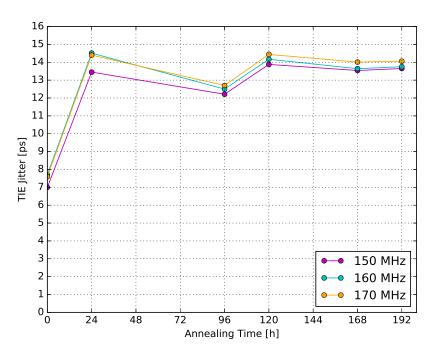

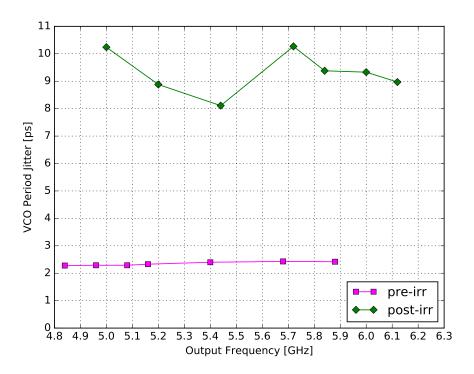

| 4.31 | Pre and post irradiation periodic jitter measurements                                                                                                         | 83 |

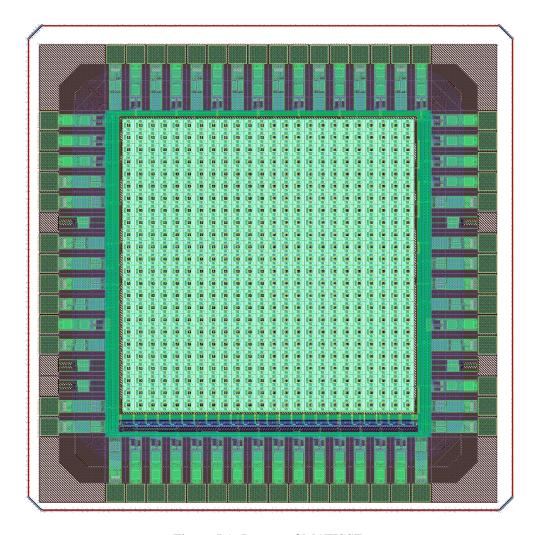

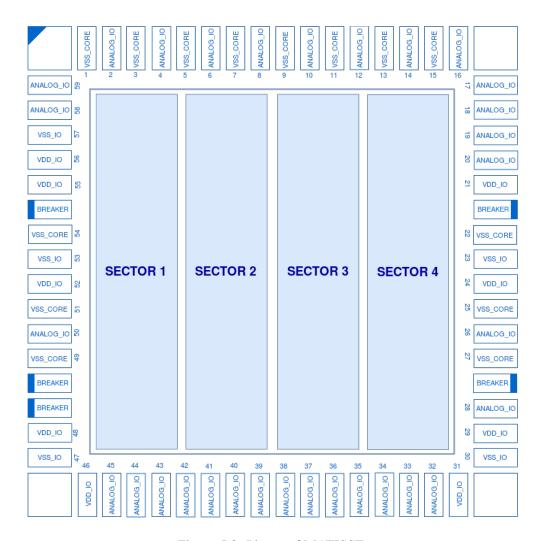

| 5.1  | Layout of MATISSE                                                                                                                                             | 86 |

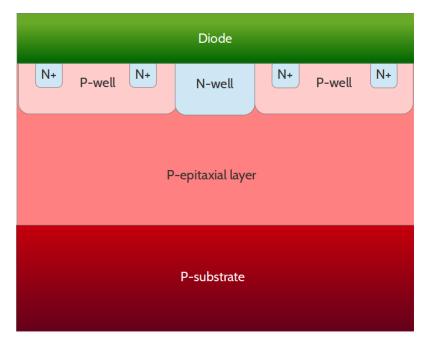

| 5.2  | Cross section of a fully-depleted sensor (via [3])                                                                                                            | 88 |

| 5.3  | Section of a Tower Jazz 180 nm MAP sensor (image via [1])                                                                                                     | 89 |

| 5.4  | Cross section of an imaging sensor with a fully-depleted epitaxial                                                                                            |    |

|      | layer (via [4])                                                                                                                                               | 89 |

List of Figures xix

| 5.5              | Cross-section of an optical sensor developed on a fully-depleted substrate, with a back-side and front-side pn-junction. In this picture, p-regions highlighting and labels are added for a better clarity with respect to the patent one [5] |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.6              | Cross-section of a fully-depleted monolithic sensor developed in a p-type substrate, with n-type electrodes and back-side junction (via [6])                                                                                                  |

| 5.7              | Cross section of the monolithic double-sided processed sensor of                                                                                                                                                                              |

| 3.7              | MATISSE92                                                                                                                                                                                                                                     |

| 5.8              | Pinout of MATISSE                                                                                                                                                                                                                             |

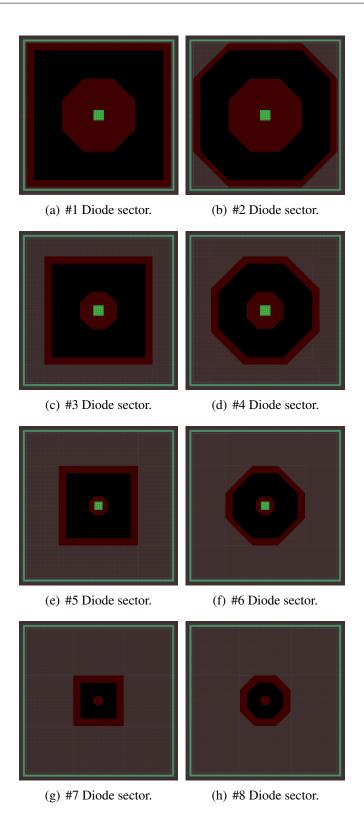

| 5.9              | Diode sectors' different sizes and shapes                                                                                                                                                                                                     |

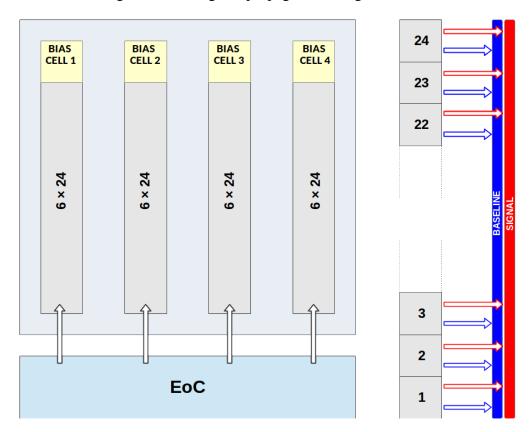

| 5.10             | Readout of MATISSE                                                                                                                                                                                                                            |

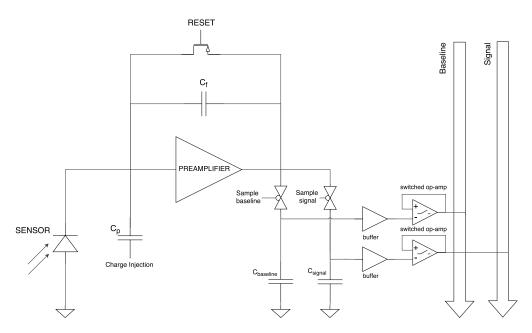

| 5.11             | MATISSE front-end electronics schematic                                                                                                                                                                                                       |

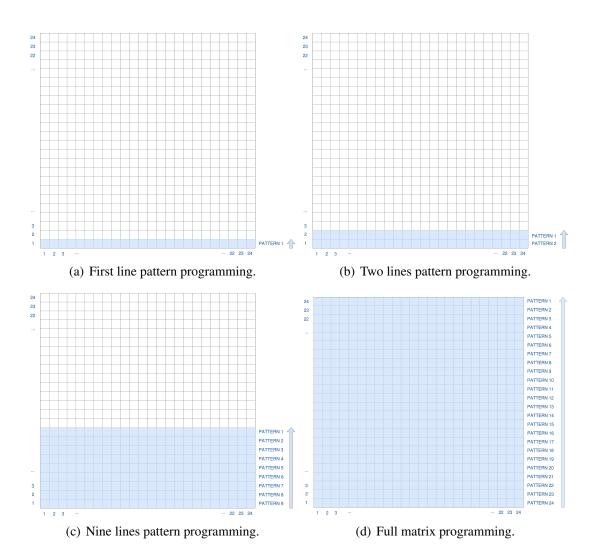

| 5.12             | Matrix programming sequence                                                                                                                                                                                                                   |

| 5.13             | Diode reset                                                                                                                                                                                                                                   |

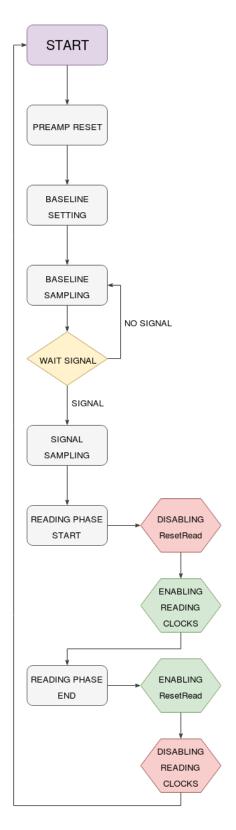

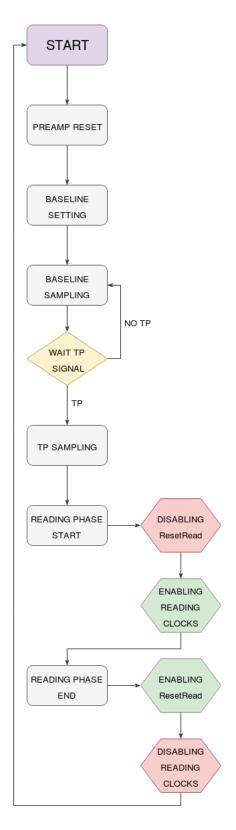

| 5.14             | Standard mode readout flow of MATISSE                                                                                                                                                                                                         |

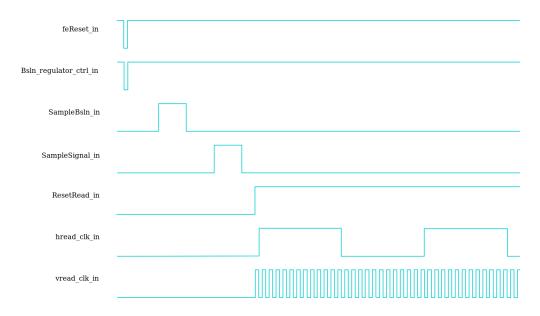

| 5.15             | Standard mode                                                                                                                                                                                                                                 |

| 5.16             | Test pulse mode readout flow of MATISSE                                                                                                                                                                                                       |

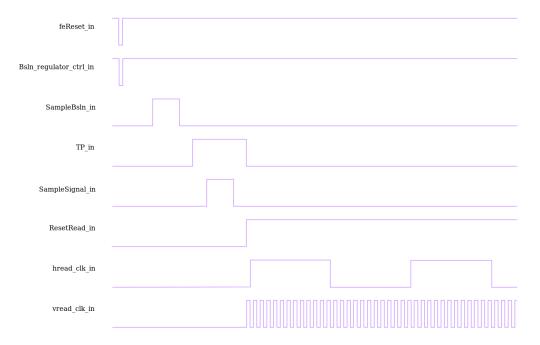

| 5.17             | Test pulse mode                                                                                                                                                                                                                               |

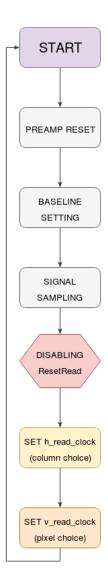

| 5.18             | Fixed pixel mode readout flow of MATISSE                                                                                                                                                                                                      |

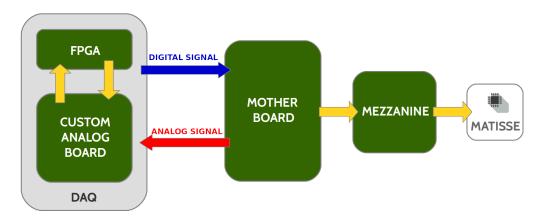

| 5.19             | Schematic view of the DAQ used for MATISSE tests                                                                                                                                                                                              |

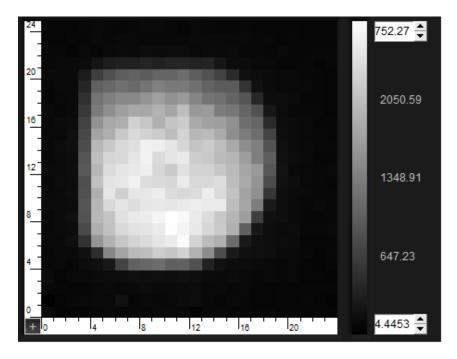

| 5.20             | An example of an online matrix view with a laser spot reconstruction built with the C++/ROOT software interface (plot via [7]) 118                                                                                                            |

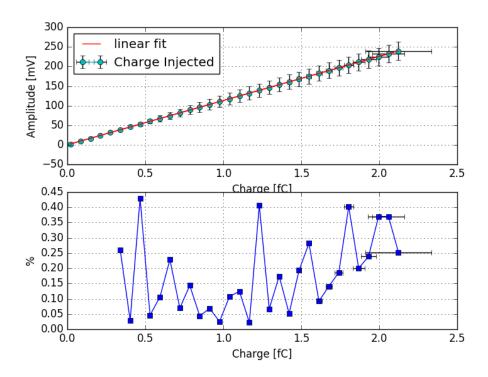

| 5.21             | Test pulse linearity                                                                                                                                                                                                                          |

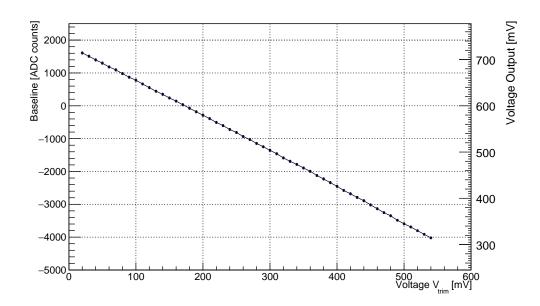

| 5.22             | Baseline regulation plot                                                                                                                                                                                                                      |

| 5.23             | Jitter measurements by mean of the automatic data acquisition with DAQ[8] (Fig. 5.23(a)) and by mean of the oscilloscope (Fig. 5.23(b)) 122                                                                                                   |

| 5 24             | <sup>55</sup> Fe peak                                                                                                                                                                                                                         |

| J.∠ <del>T</del> | 10 pour                                                                                                                                                                                                                                       |

xx List of Figures

| 5.25 | Irradiation test of the MATISSE using a <sup>55</sup> Fe source. Each plot corresponds to the results of a matrix sector (plot via [7]) 124 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 5.26 | Irradiation test of the MATISSE using a <sup>55</sup> Fe source. Each plot corresponds to the results of a matrix sector (plot via [7]) 124 |

| 5.27 | Storage time results (plot via [7])                                                                                                         |

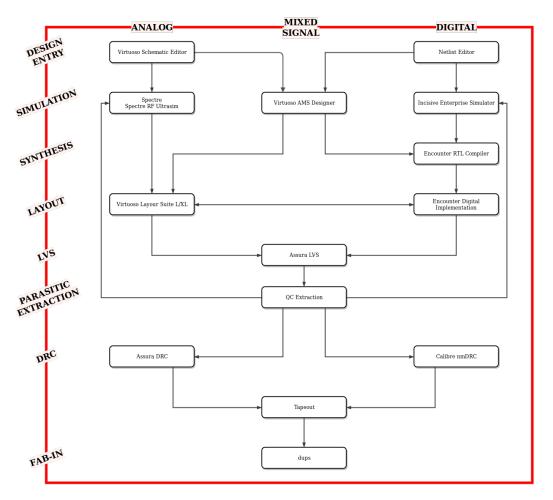

| B.1  | EDA design flow example for Cadence <sup>©</sup> tools                                                                                      |

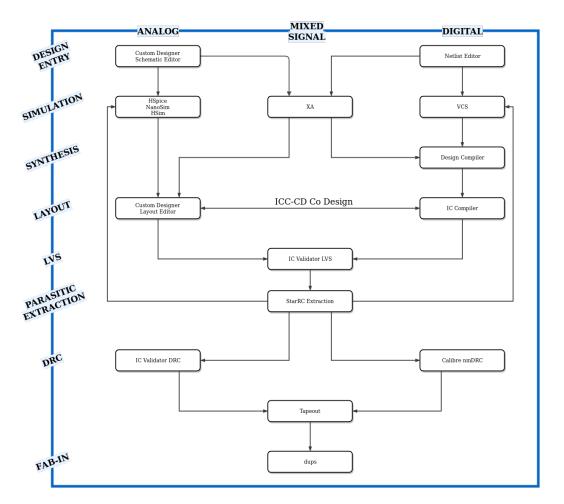

| B.2  | EDA design flow example for Synopsys <sup>©</sup> tools                                                                                     |

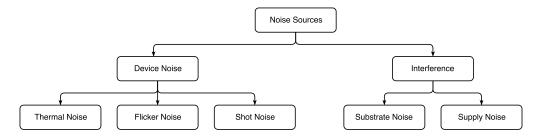

| C.1  | Noise sources                                                                                                                               |

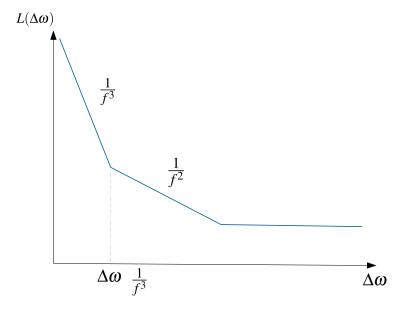

| C.2  | Phase noise vs frequency offset of the carrier                                                                                              |

| C.3  | A typical RLC oscillator scheme                                                                                                             |

## **List of Tables**

| 1.1 | Advantages and disadvantages of HPDs                 | 4  |

|-----|------------------------------------------------------|----|

| 1.2 | FPix2 parameters summary                             | 5  |

| 1.3 | ToPix v4 parameters summary                          | 7  |

| 1.4 | Timepix3 parameters summary                          | 9  |

| 1.5 | VELOPix parameters summary.                          | 10 |

| 2.1 | LePix parameters summary                             | 18 |

| 2.2 | ALPIDE parameters summary                            | 20 |

| 3.1 | Main requirements for the detectors among LHC Phases | 22 |

| 3.2 | Summary of the characteristics of the prototype      | 25 |

| 3.3 | Digital architecture performances summary            | 33 |

| 3.4 | SPI configuration commands                           | 36 |

| 4.1 | Possible states for the PDF                          | 60 |

| 4.2 | LC-VCO PLL summarized parameters                     | 73 |

| 4.3 | Average period/TIE jitter values                     | 75 |

| 5.1 | MATISSE parameter summary                            | 87 |

| 5.2 | Top side pads                                        | 95 |

| 5.3 | Right side pads                                      | 96 |

xxii List of Tables

| 5.4  | Bottom side pads                               |

|------|------------------------------------------------|

| 5.5  | Left side pads                                 |

| 5.6  | Readout modes                                  |

| 5.7  | Digital clock values                           |

| 5.8  | Evaluation for timing for readout              |

| 5.9  | Evaluation of timing for programming           |

| 5.10 | Voltage supply values                          |

| 5.11 | Bias current values                            |

| 5.12 | Bias voltage values                            |

| 5.13 | Digital input values                           |

| 5.14 | Power dissipation measurements (table via [7]) |

| A.1  | SEE overview                                   |

| Α.1  | SEE OVERVIEW                                   |

| A.2  | Applicability of SEE to circuit types          |

| A.3  | Common mitigation techniques for SEE           |

## **Chapter 1**

## Hybrid pixel detectors

#### 1.1 Introduction to hybrid pixel detectors

The development of LHC detectors, where remarkable speed and radiation hardness constraints are required, has promoted an astound growth of the Hybrid Pixel Detectors (HPDs)[9]. From the point of view of fabrication, even though very similar to microstrip detectors' ones, HPDs show an higher segmentation by splitting the original strip structure into small parts called, indeed, *pixels*.

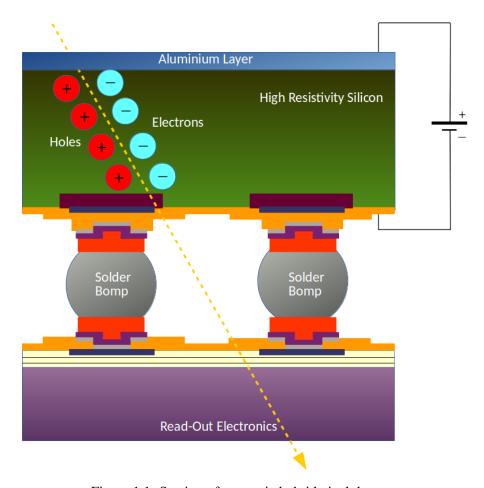

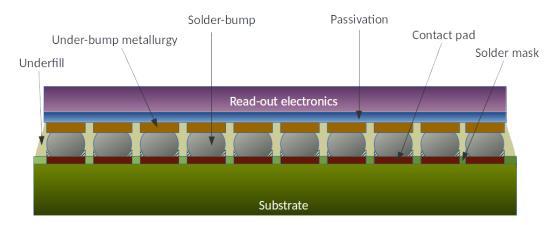

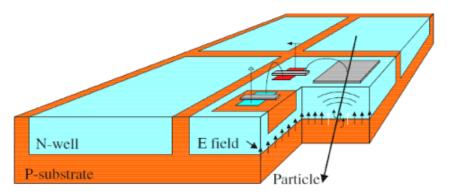

Detecting sensors and their front-end electronics chip belong to two different pieces and they are processed and optimized separately [10]. Usually, the read-out electronics is developed in some commercial CMOS process, which facilitates huge and low-cost production. In order to extract the signal from the front-end, some ancillary logic is needed with organizing and off-chip transmission purposes. These logic parts generally are not distributed along the pixel matrices but they are concentrated all together and put close to the chip. On the other hand, detecting sensor is generally developed with high-resistivity silicon but also other materials are considered, such as diamond [11]. The solding with these two parts is achieved by means of the flip-chip bonding technique [12] where the mechanical and electrical connection between the two is established by some small solder balls (gold, indium or other metals are utilized). The connectivity between sensor and front-end electronics must be vertical in order to allow them to stay very close (10-20  $\mu$ m). Furthermore, the pixel size must match with the size of its corresponding electronics. This proximity

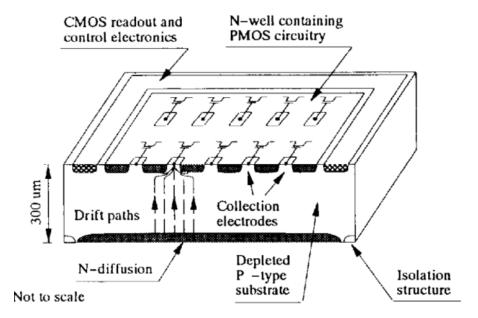

Figure 1.1: Section of a generic hybrid pixel detector.

may cause some issues which need some special attention during the design phase:

- spurious signals due to high-frequency signals on the electronics detected on the metalization of the pixel. This phenomenon may be contained by reducing the coupling capacitance between digital lines and sensor and by utilizing low-swing logic (such as LVDS);

- destructive sparks due to static voltage (e.g. bias voltages) on the edges or front-side of the sensor may damage the front-end electronics. For this reason, some specific structures (*guardrings*) are utilized with the aim to confine the high voltage parts on the sensor's backside.

The small dimension of the sensing unity - the pixel - represents the main characteristic of HPDs. Actually, each pixel is fabricated with a thin silicon layer ( $\approx 300 \ \mu m$ ) and occupies a small area ( $\approx 10^{-4} \ cm^2$ ). Thanks to the low capacitance ( $\approx 0.2$ -

0.4 pF), HPDs stand out for low noise and fast signal shaping.

Common noise values are around  $200 e^-$  for 40 MHz operating frequencies; a good choice of detection threshold (i.e.  $10 \sigma$  noise) may ensure that noise fluctuations do not cross the threshold, maintaining a full efficiency at the same time with an extremely low probability to incur in spurious hits [13].

Additionally, a good Signal-To-Noise Ratio (SNR) implies for the detector the needed robustness for remarkable loss of signal. Even though the huge complexity

Figure 1.2: Flip-chip technique.

of interconnections and functionalities, HPDs allows an excellent resolution of the acquired signals, this entails an high power dissipation (by approximately few hundreds mW/cm<sup>2</sup>), more material for the active areas and larger pixels' size since more space for readout circuitry is needed.

A solution can be found into taking advantages by material sensors with thin active depth, such as GaAs, CdZnTe or diamond, which are, however, characterized by meager collection of the charge; alternatively, silicon sensors which may be degraded by radiation and thus reduce the charge collection due to carriers' trapping phenomena. Furthermore, the small dimension of the pixel leads to small reverse depletion current (in the order of  $0.1~\mu\text{A/cm}^2$ ): this allows operation after irradiation due to reduced noise. This makes HPDs the appropriate detector for harsh radiation environment.

HPDs have demonstrated their worth in the field of huge HEP detector, where the need to cover square meters of sensitive area with millions of channels for extremely intense particle fluxes occurs. Their characteristics and the freedom to choose the sensitive material makes them a preferred technology also in other fields, such as

medical diagnostics [14].

| Advantages                                                                                     | Disadvantages                                                                                                                                  |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| high space and time resolution<br>speed<br>radiation hardness<br>non-ambiguous 3D measurements | extra material (due to the flip-chip)<br>high power dissipation<br>high costs (solding)<br>two different foundry processes<br>(sensor and FEE) |

Table 1.1: Advantages and disadvantages of HPDs.

#### 1.1.1 Some examples

As said before, HPDs represent the main detector tipology for High Energy Physics experiments. Following, a round-up of some readout chips based on HPDs.

#### 1.1.1.1 FPix2

FPix2 [15] is the rad-hard chip developed for the BTeV experiment at Fermilab [16]. BTeV was proposed for the CZero interaction region of the Tevatron [17] and it was intended to collect data from a pixel vertex detector by reconstructing vertices and tracks for each beam crossing. The detector requirements pertain in particular to the extreme radiation hardness (≈ 3Mrad/year), to be SEE tolerant and to the capability to sustain very high leakage currents. Radiation hardness techniques has been implemented in order to accomplish to this crucial requirement [18]. Furthermore, given the Tevatron time between proton-antiproton interactions (132 ns), the FPix2 needed to be designed to guarantee no data losses due to the readout deadtime. In addition to that, enough bandwidth is needed in order to collect all the data (since the trigger needs all pixel data each crossing) and a high-speed zero suppression system to manage the high data quantity. The vertex detector was intended to be made of sensors arrays perpendicular to the direction of the beam.

Built in a commercial CMOS 250 nm, the pixel matrix is composed by  $22 \times 128$  pixels; the pixel size is  $50 \times 400 \ \mu\text{m}^2$ . The chip needs just 2.5 V supply and ground signal, since all the other ones (current and voltages bias, thresholds) are on-chip generated by some DACs. For the I/O interface, FPix2 is equipped with standard

| Parameter               | Value                         |

|-------------------------|-------------------------------|

| CMOS technology process | 250 nm                        |

| Pixel size              | $50\times400~\mu\mathrm{m}^2$ |

| Matrix array            | 22×128 pixels                 |

| I/O interface           | LVDS                          |

| Voltage Supply          | 2.5 V                         |

Table 1.2: FPix2 parameters summary.

#### LVDS protocol.

As said before, all the pixels are read and their data readout each beam crossing. All the pixel hits are sent, every readout period, to a Pixel Data Combiner Board on a FPGA located far off the collision ( $\approx$ 10 meters). A 140 Mbps serial link is used to send off-chip all the data using a point-to-point serial way. In order to modulate the required bandwidth by the section of the detector (from the closest to the further from the collision), the output serial link can be programmed in four different modes.

The pixel unit cell consists in a continuous-time-filter amplifier with a 3-bit flash ADC, composed by eight comparators and some digital circuitry to encode the output of the ADC and store the data related to the hits. This last information is preserved until a signal coming from the EoC allows to transmit them to the output interface. The data word sent on a core output-bus is 23-bit long and it is made of the 7-bit row number, the 3-bit ADC value plus thirteen bits added by the EoC (a 5-bit column number and an 8-bit time-stamp, also called the BCO number); data from 1<sup>st</sup> to 13<sup>th</sup> bit cannot be zero: for this reason the numbers of 22 columns are encoded on five bits by using binary code without zeroes in lowest positions. The data are then serialized and sent off-chip [18].

A synchronization/status word is used to synchronize the chip with the data combiner board which checks its correctness as well: the readout is performed column by column in a round-robin way. The output of the chip is managed using Low Voltage Differential Signaling (LVDS) and consists in a clock signal and in a programming number corresponding to the position of the chip with respect to the collision point: it can be 1, 2, 4 or 6 respectively from the further to the closest to collision position; thus, each number corresponds to a different internal readout clock frequency (1 to 5.8 MHz, 2 to 11.7 MHz, 4 to 23.3 MHz, 6 to 35 MHz); this frequency derives by the

transfer bit rate divided by the word size (24 bit) and the number of active data links. Data output clock and readout clock are originated from a 70 MHz internal clock. The equality between the time required to send data off chip and time required to readout is guaranteed by the relationship between the number of data links used and internal readout clock: one clock period is needed to send off chip one word.

#### 1.1.1.2 Topix v4

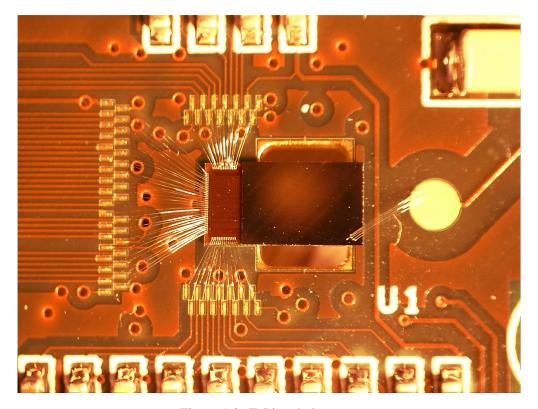

Figure 1.3: ToPix v4 close-up.

In the framework of the Micro Vertex Detector of PANDA [19] experiment, ToPix v4 ASIC [20] has been developed for the readout of the silicon hybrid pixel detectors. Designed in a commercial 130 nm CMOS process, the prototype shows a 640 pixel matrix organized in 8 columns; the die size is 6 mm ×3 mm.

While the full chip should be consisted into a 116×110 pixel matrix arranged in 55 double columns, with four full column controllers and a Chip Control Unit (CCU), whose purpose is to multiplex data from the column controllers to the GBT chip by mean of a 320 Mb/s serial link, the prototype consists into a smaller matrix of

just 640 pixels organized in four double columns with different size arrangements (the two central ones are  $2 \times 128$  pixels, while the other ones are  $2 \times 32$  pixels; this allows to analyze issues of the data transmission in very long on-chip lines) with a simplified CCU and with a dedicated time stamp circuitry with a 160 MHz frequency for time arrival measurements. In order to measure released energy, a ToT technique is implemented: in such a way, Topix v4 is able to return information about time, position and energy of the incoming particle. The readout chain is based on a 4.9 fF

| Parameter               | Value                                |

|-------------------------|--------------------------------------|

| CMOS technology process | 130 nm                               |

| Pixel size              | $100 \times 100 \ \mu \text{m}^2$    |

| Active area             | $11.4 \times 11.6 \text{ mm}^2$      |

| Maximum input charge    | 50 fC                                |

| Power consumption       | $< 800 \text{ mW/cm}^2$              |

| Preamplifier noise      | $< 32 \text{ aC } (200 \text{ e}^-)$ |

| Time resolution         | 6.25 ns (1.8 ns rms)                 |

| Input clock frequency   | 160 MHz                              |

| Maximum hit rate        | $6.1 \times 10^6 \text{/cm}^2$       |

| dE/dx measurement       | ToT, 12 bits dynamic range           |

| Total ionizing dose     | < 100 kGy                            |

Table 1.3: ToPix v4 parameters summary.

feedback preamplifier with a constant current discharge circuit and a comparator. Detection of the comparator output falling and rising edges and their storing of time-stamps into two 12 bit registers is managed by a digital control unit. Then, a dedicated bus distributes the time reference to all columns. A time-over-threshold technique is used for the measure of the charge released in the detector by the particle: since a capacitor discharges linearly, the difference between the two edges of this pulse of the comparator is related to the integrated charge released into the detector by the incident particle. Once this information is stored, a busy signal by mean of a fast-OR chain is propagated along the columns; the column controller enables the writing of the address and the data of the hit pixel. Since the logic is asynchronous, the 160 MHz clock is not propagated to all the pixel of the array. For a better calibration of the threshold of the comparator and for pixel masking purposes, a configuration register is provided: its configuration values are uploaded during the time preceding the phase dedicated to pixel data collecting by using the time

stamp bus. The time stamp propagation is improved by mean of some techniques, such as pre-emphasis, Gray encoding and differential transmission on the bus, which can be demanding in terms of RC delay even though the low values of capacitance and resistance. A 32 word FIFO is connected to each double column readout buses; the CCU performs the readout of those FIFOs and sends out the data with a 320 Mb/s SLVS serial link. For what concerns the I/O, on the top and bottom of the die some test pads and analog bias are located; all the pads of the digital interface are differential and put on the right side. In order to test the radiation tolerance of the chip ToPix v4 prototype has been irradiated up to 100 kGy of TID and under several ions type in order to check SEE hardness. Detailed report could be found in [20].

#### 1.1.1.3 TimePix3

Timepix3 is the enhanced version of Timepix [21][22]. Designed by CERN, NIKHEF (Netherlands) and University of Bonn (Germany), it is based on a CMOS 130 nm process. Similarly to Timepix [23] (which indeed is based on a CMOS 250 nm process), it consists in a  $256 \times 256$  matrix with a 55  $\mu$ m pitch in both directions. It is capable to provide time to arrival (ToA), Time-Over-threshold (ToT) or event/photon counting measurement (called PC). Differently to Timepix, it is able to perform ToA and ToT or PC or iToT (integral ToT) at the same time.

Timepix3 can operate in two main modes: ToT with ToA or PC with iToT.

In the first mode, each pixel is able to record 10 bits for the ToT and 18 bits for the ToA. A 40 MHz reference clock is used to sample the most significant 14 bits, while the last 4 bits are measured by mean of a VCO (Voltage Controlled Oscillator) inside the pixel matrix. In the second mode, a 14 bit register is used to store the integrated values of the ToT during a period determined by an external shutter signal; another 10 bits register is implemented to store the number of hits. A different requirement between Timepix and Timepix3 is the monotonicity of the input charge vs ToT up to 300k holes (positive charge).

The readout can be performed in two ways as well. The first is a classical sequential shutter period readout. The last one is a data-driven mode readout: when a pixel is hit, the chip sends off chip a 48 bits string. Pixel are then gathered together in  $2\times4$  pixels groups which may be called "superpixel". Each superpixel group has a dedicated VCO which generates a 640 MHz local clock, used for ToA measurements

| Parameter                    | Value                             |

|------------------------------|-----------------------------------|

| CMOS technology process      | 130 nm                            |

| Matrix                       | $256 \times 256$ pixels           |

| Pitch                        | $55\mu\mathrm{m}$                 |

| Analog FEE Area              | $55 \times 13.5 \ \mu \text{m}^2$ |

| Detector Capacitance         | min 25 fF                         |

|                              | typ 50 fF                         |

|                              | max 100 fF                        |

| Polarity of the signal       | positive and negative             |

| Monotonicity of the ToT      | up to $300 \text{ kh}^+$          |

| Leakage current              | from -5 nA to 20 nA               |

| Jitter and mismatch of ToA   | 1.56 ns resolution compatibility  |

| Amplitude linearity          | not required                      |

| Time to peak                 | 25 ns target                      |

| Noise and threshold mismatch | 90 electrons                      |

| Power consumption            | 12 μW/pixel                       |

| On pixel equalization DACs   | 4 bit                             |

Table 1.4: Timepix3 parameters summary.

up to 1.56 ns. This architecture is able to optimize the bandwidth since the expected maximum hit rate is of 40 Mhits/s·cm<sup>-2</sup>. Furthermore, the front-end electronics is based on a single threshold discriminator and charge preamplifier with a Krummenacher feedback. Other features which enable Timepix3 to be optimized for power pulsing tests (dynamic wake-up/shut-down) needed for large systems and essential for LINAC requirements.

#### **1.1.1.4 VELOpix**

VELOPix[24] ASIC is the chosen chip for VErtex LOcator (VELO)[25] at LHCb. Based on the Timepix3 [22] architecture, the 256×256 pixel array is organized in 128 double columns; each column contains 64 super pixel (2×16 pixels each) and each super pixel connects to 8 digital front-end connected to the analog front-end by mean of the output of the discriminator. Each double column has a data buffer and a finite state machine with communication purposes placed which consist into EoCs. Each super pixel is equipped with the same digital and full-custom analog circuitry integrated in a digital-on-top fashion.

| Parameter               | Value                                      |

|-------------------------|--------------------------------------------|

| CMOS technology process | 130 nm                                     |

| Layout size             | $14\times55 \mu\mathrm{m}^2$               |

| C det                   | 50 fF                                      |

| Minimum threshold       | 500 e <sup>-</sup> , 5-bit threshold DAC   |

| Dead time               | 400 ns for 16 ke <sup>-</sup> input charge |

| Maximum leakage current | 12 nA                                      |

| Noise (simulation)      | 60 e <sup>-</sup>                          |

Table 1.5: VELOPix parameters summary.

The motivation of the choice of a  $2\times4$  size superpixel is related to the opportunity of packing an sharing data in order to reduce the data rate of 30%. A preamplifier with a Krummenacher feedback and a discriminator give rise to the analog front end, specifically developed for electrons collection; a global threshold is utilized for all pixels. On the other hand, the digital parts show some synchronization circuitry and a linear feedback shift register (LFSR) with a 62 counts range: this pseudo random counter could be programmed for event counting purposes, in a ToT configuration or as a smaller binary counter (with pseudo-randomized values, easily readable with a lookup table); 8 digital front ends arrange a super pixel logic. A ToT threshold logic is dedicated to accept or reject hit values based on a comparison between ToT and a digital programmable threshold. ToT technique is utilized internally into the pixel and the same programmable digital value is shared in the same superpixel. Thus, differelly to Timepix3, VELOPix does not provide charge information. Time resolution is 16 times less accurate with respect to Timepix3 (25 ns) and the on pixel memory for time measurement is smaller (9 bits instead 14). The periphery is nodebased [26] and a second memory is dedicated in order to increase the throughput packet from one packet every three clock cycle to just only one clock cycle. Four 160 MHz clocked parallel data channels characterize each half periphery: this leads to a 1.28 Gpackets/s ( $2 \times 4 \times 160$  MHz).

At the end of the data path, four serializer and drivers with a data rate of 5.12 Gbps are implemented. From a 320 MHz clock, with a DLL (Delay-Locked Loop), sixteen different clock are derived and generated on-chip. This generates 128-bit frame each 40 MHz/output link with a data stream of 5.12 Gbps (320 MHz  $\times 16$ ); each frame is composed by 30 bit: 4 bits for the header and a parity bit every packet.

Radiation tolerance is implemented both for total ionizing dose effects and against

single event effects. NMOS transistors inside the preamplifier are equipped with enclosed layout. All state or configuration registers, clock muxes, clock gates, FSMs show a triple modular redundancy protection. Event data coming from pixel does not have protection due to missing area for additional flip-flops. Clearly, radiation protection increases considerably the total chip area.

## **Chapter 2**

### Monolithic pixel detectors

#### 2.1 Introduction to monolithic pixel detectors

#### 2.1.1 Generalia

Monolithic Active Pixel Detectors (MAPS) [27][28] were conceived in early 90s as a leading technology for camera sensors development. At that time requirements on noise, speed and leakage were somehow less stringent and the main aim was the detection of visible light (i.e. for consumer devices such as commercial cameras). Due to the initial limitations and poor performance of their original architecture, several improvement and different implementations were considered during the next years in order to richly enhance their performance.

However, until the beginning, some key strengths of MAPS were clear [29][30]:

- they are developed in a standard commercial CMOS technology: this leads simplification of the process for wide cheap production of sensors;

- no bonding necessary (or other types of connections): sensor and front end electronics are in the same piece of silicon and thus produced in the same process;

- possibility to develop smaller pixels with several functionalities integrated in the front end electronics together with the sensor;

- they have low power dissipation;

- radiation robustness can be obtained with deep submicron processes;

- random accessibility to the pixel array;

- massively parallel and high speed analog to digital readout;

- limited readout I/O requirements.

Nowadays they are extensively utilized into everyday technological devices (cams, mobile phones, computers, web-cams, toys, security tools) and they are considered as working technology for particle detectors in HEP.

#### 2.1.1.1 Early architectures: 3T and 4T

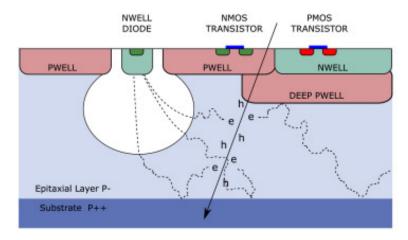

Figure 2.1: The 3T MAPS architecture.

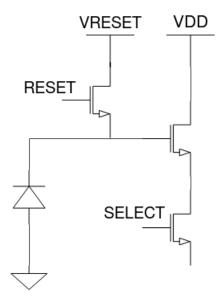

The simplest structure of a MAPS consist in just three transfors (Figure 2.1): one is implemented as reset for the FD node on the photodiode; a second is utilized as switch for readout line selection and the third is the input for a source follower outside the pixel, used as current source and common to all the column. For efficiency reasons the preferred type of transistor are nMOS with p-substrate.

The diode allows a quite good radiation hardness [31][32] and a rather fast time for collecting charge.

Figure 2.2: The 4T MAPS architecture.

The working mode for this kind of sensors is the so-called *rolling-shutter* mode: pixel array is readout in parallel one line at once by activating the SELECT transistor an then resetting the floating node FD node to a VRESET voltage. In the majority of structures, the charge collection is performed by diffusion and this makes these structures limited in speed. Furthermore, radiation hardness is fairly reduced by the minority carriers lifetime. Nevertheless, deep n-well structures [33][34][35] may guarantee better speed performance. The 3T architecture was used for some projects of particle detecting sensors [32][36][37][38] and it was well known and tested. The 4T MAPS pixel structure with pinned diode and stitching is shown in Fig. 2.2. The two major differences with respect to the 3T structure are:

- a forth transistor in series between FD and the pinned photodiode; with the appropriate timing this transistor is able to transfer the charge from the photodiode to the FD, in this way establishing a in-pixel Correlated Double Sampling (CDS)[39], thus easing reset noise removal (which usually represents the main cause of noise).

- the pinned photodiode represents the key element of the imaging instruments: its structure is fairly close to the base bipolar transistor, with an additional p+ implants on the top of the structure n-well/p-sub; some recent studies [40][41] analyzes its performance during irradiation.

Figure 2.3: A general scheme for a Monolithic Active Pixel Sensor.

In recent years, the development of new silicon detectors in HEP became crucial due to the stringent requirements such as speed, radiation tolerance, time and space resolution, high rate capability and cost lead scientists to put more effort on study and investigation of new adequate solutions. As mentioned before, with the aim to overcome the original structure issues, several improvements [42] of the 3T/4T architecture made MAPS attractive and suitable for High Energy Physics experiments. With respect to HPDs, MAPS fulfill excellently all the requirements pertinent to the quality of the data collection and also an extremely low material budget (since sensor and front end electronics are integrated on the same piece of silicon and no bonding or soldering is needed), easy assembly and low production cost (since they can be produced in a commercial CMOS process). In addition to that, since the connection between the detector and the collection node usually introduces some parasitic capacitance, MAPS exhibit low detector capacitances (on the order of fFs), which means the possibility to working in a low power mode.

### 2.1.2 Some examples

#### 2.1.2.1 LePix

LePix [43] has been developed in a CMOS process 90 nm with a mid-resistive substrate. Besides traditional charge collection by diffusion, depletion by drift is here possible and it is eased by high values of resistivity: the process on which LePix is based provides an above 500  $\Omega$ ·cm resistivity substrate, which makes possible to deplete the substrate by using low voltages ( $\approx$ 100 V).

The importance of this opportunity lies in some reasons: the possibility to use very low voltages for drift depletion, thanks to doping level much higher than the traditional MAPS, allows lower power dissipation of the detector system. In addition to that, advanced processes (such as 90 nm or smaller) facilitate reduction of dead area and ease high speed transmission, which represent two main constraints of new generation of particle detectors.

In LePix architecture the collection electrode is built by means of a 2D array of n-well diffusion inserted in a p-substrate. The n-well diffusion also contains the readout circuit, where the nMOS transistors are arranged into a p-well inside the initial n-well, thus originating a triple well configuration.

The detector matrix is composed by  $32\times32$  pixel with a 50  $\mu$ m pitch. Four sectors of  $8\times32$  pixels implement different input devices:

- sector 1: thin oxide pMOS transistors

- sector 2: thin oxide pMOS transistors (bigger than sector 1)

- sector 3: thick oxide pMOS transistors

- sector 4: nMOS transistors

As expected, transistors in sectors 1 and 2 show higher values of gate leakage while neither transistors in sector 3 nor the nMOS transistors experience this issue. On the other hand, nMOS input transistor exhibits a large parasitic capacitance.

In addition to that, two matrices have been designed in order to implement different sizes of collection nodes (but identical in the other parts): very small, in order to minimize the intrinsic capacitance and fairly larger; tests show that in the first case a smaller size of the electrode leads to an increase of the electric field.

Another difference is the way to reset the pixels: the first 16 rows are reset by

| Parameter        | Value                      |

|------------------|----------------------------|

| Process          | 90 nm                      |

| Pixel array      | 32×32 pixels               |

| Dimensions       | $50\times50~\mu\text{m}^2$ |

| Integration time | programmable               |

| Readout          | double-sampling serial     |

Table 2.1: LePix parameters summary.

applying a reset signal to the reset transistor in each pixel, leading this way an active reset mode. The lower 16 rows, instead, are reset with a diode which absorbs the pixel leakage, generating a sort of continuous reset mode. An embedded capacitor allows test pulse to rows 1 and 17. Power supply is set at 1.2 V for both analog and digital parts, even if their power are separated; CMOS 1.2 V logic is implemented for all the signals. To allow reverse bias of the substrate, a guard ring is inserted. The analog readout is double-sampling serial: at the begin and at the end of the programmable integration time, each pixel's analog voltage level is sampled and the difference between the two is then stored: this value corresponds to the signal plus the integrated leakage current. Even though this readout mode is very similar to the traditional rolling shutter, it differs in the outer and simultaneous storing of the pixel information. For this reason, a peripheral line connects all the pixel and manages the pixels' signal collection. Electrical and irradiation tests have been extensively done [44] [45] [46] [47].

#### **2.1.2.2 ALPIDE**

ALICE experiment at CERN is currently through an upgrade which involves the development of a new Inner Tracking System [48] [49] [50] [51]. Based on seven concentric cylindric layers of MAPS, it will cover an area of 10 m<sup>2</sup> and it will be installed during the second long shutdown (2019-2020).

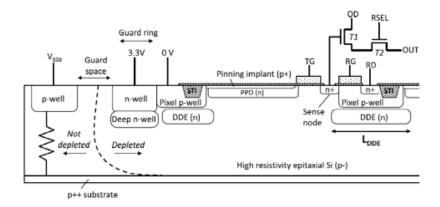

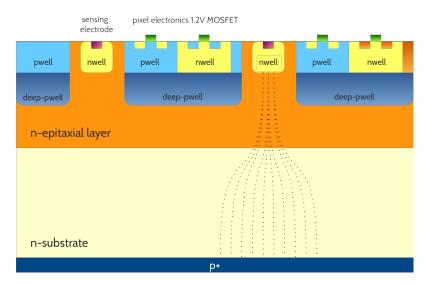

Monolithic Active Pixel Sensor will be produced in a TowerJazz 180 nm process with six metal layers available and the additional small deep p-well structure, which allows the implementation of full CMOS structures inside the pixel circuitry [52]. High resistive epitaxial layers (more than 1 k $\Omega$ ·cm) represent a crucial node for a better charge collection [53] [54]. During the years several prototypes have been

Figure 2.4: Inner Tracking System section; inner and outer barrel are highlighted (image via [1]).

developed to fulfill geometry, power consumption and radiation hardness constraints until the full-scale submission of the final ALPIDE chip in 2014.

ALPIDE chip [55] [55] is arranged by  $512 \times 1024$  pixel array and its dimension is  $1.5 \times 3$  cm<sup>2</sup>, with a pixel area of  $28 \times 28 \ \mu\text{m}^2$ .

The readout [56] is binary with an in-pixel hit discrimination and the low-power front-end is continuously active: hit data information can thus be discriminated and sent to a multiple event memory continuously with a trigger latency of some microseconds. However, memory strobing may also be done within long and steady periods in order to perform non-stop data recording. Hit pixel information is thus sent from matrix to the periphery by mean of an in-matrix sparsification circuit with an asynchronous and hit-driven combinatorial circuitry constituted by a priority encoder every double column. From periphery, data are serialized and then delivered off the detector by mean of a high-speed link. Irradiation tests show a detection efficiency of the sensor above 99%, a space resolution of  $\approx 5\mu$ m and a fake hit rate lower han  $10^{-5}$ . Other details on test may be found in [3].

| Parameter                           | Value                                                                           |

|-------------------------------------|---------------------------------------------------------------------------------|

| Process                             | 180 nm                                                                          |

| Sensor thinckness                   | [inner barrel] 50 $\mu$ m                                                       |

|                                     | [outer barrel] 100 $\mu$ m                                                      |

| Dimensions                          | $1.5\times3$ cm <sup>2</sup>                                                    |

| Pixel array                         | 512×1024 pixels                                                                 |

| Pixel area                          | $28\times28~\mu\text{m}^2$                                                      |

| Spatial resolution                  | [inner barrel] 5 $\mu$ m <sup>2</sup>                                           |

|                                     | [outer barrel] $10 \ \mu \text{m}^2$                                            |

| Event-time resolution               | ≈2 µs                                                                           |

| Power density                       | [inner barrel] 300 mW/cm <sup>2</sup>                                           |

|                                     | [outer barrel] 100 mW/cm <sup>2</sup>                                           |

| Detection efficiency                | >99%                                                                            |

| TID radiation hardness              | [inner barrel] 2700 krad                                                        |

|                                     | [outer barrel] 100 krad                                                         |

| NIEL radiation hardness             | [inner barrel] $1.7 \cdot 10^{-13} \text{ MeV} \cdot \text{n}_{eq} \text{cm}^2$ |

|                                     | [outer barrel] $10^{-12} \text{ MeV} \cdot \text{n}_{eq} \text{cm}^2$           |

| Fake hit rate per pixel and readout | $\ll 10^{-6}$                                                                   |

Table 2.2: ALPIDE parameters summary.

## **Chapter 3**

## The CHIPIX65 project

## 3.1 Background and motivation

A new frontier of particle physics is represented by the High-Luminosity Large Hadron Collider (LHC) at CERN which should be operational by 2025.

Figure 3.1: HL-LHC pileup graphic simulation.

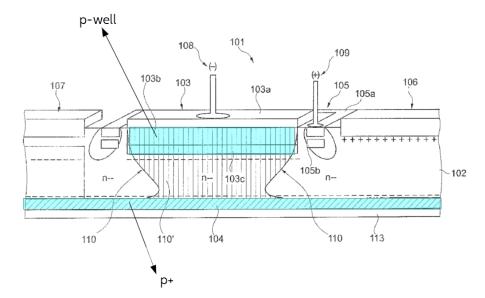

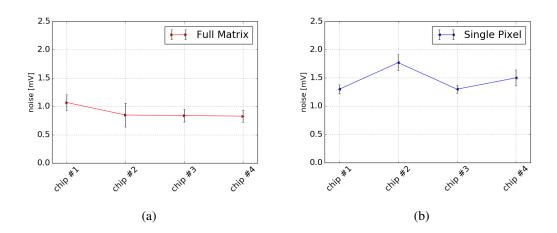

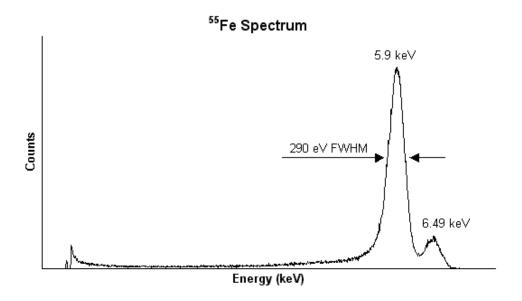

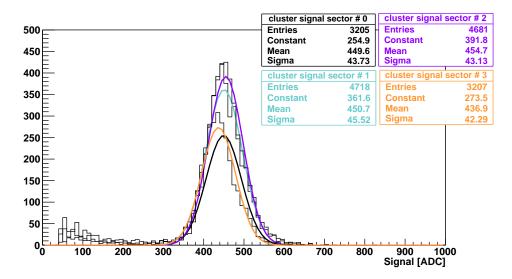

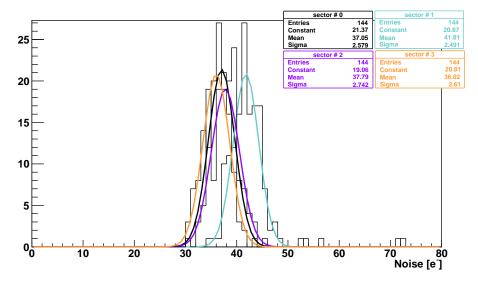

The aim of this huge project is to increase the LHC performances in order to extend the possibility of discoveries in high energies physics field. The main target is to obtain a ×10 higher luminosity with respect to the current one. Luminosity can characterize the collider because it is proportional to the number of particle collisions happened in a given time. The more elevated is the luminosity, the more particle collision data are collected, the more the accelerator is performing. A higher luminosity collider will allow more accurate studies of new particles and rare processes: HL-LHC will be able to generate 15 million of Higgs processed in a year with respect to the 1.2 million (2011-2012)[57].