Doctoral Dissertation Doctoral Program in Physics (30<sup>th</sup>cycle)

# Neuromorphic Systems based on Memristive Devices

From the material science perspective to bio-inspired learning hardware

By

Daniele Conti

\*\*\*\*\*

Supervisor(s):

Prof. Fabrizio C. Pirri, Supervisor Prof. Carlo Ricciardi, Co-Supervisor Politecnico di Torino, Department of Applied Science and Technology, Torino, Italy

#### ii

#### **Doctoral Examination Committee:**

**Prof.** Roberto Verucchi, Referee, CNR-IMEM, Institute of Materials for Electronics and Magnetism, Trento, Italy

**Prof. Ettore Vittone**, Referee, University of Torino, Department of Physics, Torino, Italy

**Prof. Dario Daghero**, Politecnico di Torino, Department of Applied Science and Technology, Torino, Italy

**Prof.** Daniele Ielmini, Politecnico di Milano and IU.NET, Department of Electronics, Informations and Bioengineering, Milano, Italy

**Prof. Riccardo Zecchina**, Bocconi University, Department of Decision Sciences, Milano, Italy; Politecnico di Torino, Institute of Condensed Matter Physics and Complex Systems, Torino, Italy

> Politecnico di Torino 2018

### Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Daniele Conti 2018

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to everyday life dreamers, to simple people that silently continue to explore ways of improving the world with their knowledge, while doing their job. Don't stop, find the way, build the opportunity and start with action. Future belongs to day-dreamers.

### Acknowledgements

I would like to acknowledge my supervisor, Prof. Fabrizio C. Pirri, and my cosupervisor, Prof. Carlo Ricciardi, for making me available their knowledge and precious experience, for the meaningful discussions we had in these three years of science and exploration of physics and technology. Thank you for having been my mentors along the way.

I would like to acknowledge Prof. Riccardo Zecchina, for having introduced me to such an exciting topic that stays at the frontier of physics, technology, computer science and biology.

I would like to acknowledge Prof. Giacomo Indiveri and his group, together with Doct. Sabina Spiga, Stefano Brivio and their colleagues at CNR-Agrate, for the excellent time I had in a top class environment such as Zuerich and the high quality research we did all together.

I would like to acknowledge my colleagues, Cecilia Giovinazzo, Gianluca Milano, Vittorio Fra and Davide Scaiola, for sharing with me both excitement and frustration typical of research. They helped me in growing both as a person and as a researcher. I am proud of the scientific exploration we did together.

I would like to acknowledge the people I collaborated with during my research activities: Samuele Porro, Krishna Rajan, Denis Perrone and many others, that made everyday life run nicely.

I would like to acknowledge the PhD in physics board, together with its coordinator, Prof. Arianna Montorsi, with which I collaborated so proficiently during my representative activities.

I would like to acknowledge the PhD students for all the good moments we shared together and, in particular, Lucrezia Ravera, with which we created AperiDISAT. In conclusion, I would like to say thanks to my family that, following all of my choices, always found the way to give me good advice and stay close to me. Thank you.

#### Abstract

Hardware computation is facing in the present age a deep transformation of its own paradigms. Silicon based computation is reaching its limit due to the physical constraints of transistor technology. As predicted by the Moore's law, downscaling of transistor dimensions doubled each year since the 60s, leading nowadays to the extreme of 16-nm channel width of the present state-of-the-art technology. No further improvement is possible, since laws of physics impose a different electrical behavior when lower dimensions are attempted. Multiple solutions are then envisaged, spanning the range from quantum computing to neuromorphic computing.

The present dissertation wants to be a preliminary study for understanding the opportunities enabled by neuromorphic computing based on resistive switching memories. In particular, brain inspires technology and architecture of new generation processors because of its unique properties: parallel and distributed computation, superposition of processing and memory unit, low power consumption, to cite only some of them. Such features make brain particularly efficient and robust against degraded data, further than particularly suitable to process and store in memory new information. Despite many research projects and some commercial products are already proposing brain-like computing processors, like spiNNaker or IBM's Bluenorth, they only mimic the brain functioning with standard Silicon technology, that is inherently serial and distinguish between processing and memory unit. Resistive switching technology on the other hand, would allow to overcome many of these issues, enabling a far better match between biological and artificial neuromorphic computation.

Resistive switching are, generally speaking, Metal-Insulator-Metal structures able to change their electrical conductance as a consequence of the history of applied electric signal. In such sense, they behave exactly as synapses do in a biological neural networks. For this reason, resistive switching when modeled as memristor, i.e. memory-resistor, can act as artificial synapses and, moreover, are particularly suitable to be interfaced with artificial Silicon neurons that are designed to replicate the biological behavior when excited with electric pulses. Anyhow, from the technological standpoint, there is still no standard on the design and fabrication of resistive switching, so that multiple structure and materials are investigated.

In this dissertation, it is reported an analysis of multiple resistive switching devices, based on various materials, i.e.  $TiO_2$ , ZnO and HfO, and device architectures, i.e. thin film and nanostructured devices, with the scope of both characterizing and comprehending the physics behind resistive switching phenomena. Furthermore, numerical simulations of artificial spiking neural networks, embedding Silicon neurons and HfO-based resistive switching are designed and performed, in order to give a systematic analysis of the performances reached by this new kind of computing paradigm.

## Contents

| Lis | st of H          | Figures                                       | xi |

|-----|------------------|-----------------------------------------------|----|

| Lis | st of 7          | Tables                                        | XX |

| 1   | Intro            | oduction                                      | 1  |

|     | 1.1              | Motivations                                   | 1  |

|     | 1.2              | Resistive Switching and Memristor             | 4  |

|     | 1.3              | Spiking Neural Network                        | 10 |

|     | 1.4              | Dissertation Outlook                          | 14 |

| 2   | Exp              | erimental                                     | 17 |

|     | 2.1              | Device Fabrication                            | 17 |

|     |                  | 2.1.1 $TiO_2$ Nanotubes Array                 | 17 |

|     |                  | 2.1.2 $TiO_2$ thin film devices               | 18 |

|     |                  | 2.1.3 ZnO thin film devices                   | 19 |

|     |                  | 2.1.4 HfO devices                             | 20 |

|     | 2.2              | Material Characterization                     | 21 |

| 3   | TiO <sub>2</sub> | 2 based resistive switching                   | 22 |

|     | 3.1              | $TiO_2$ Nanotubes Array                       | 22 |

|     |                  | 3.1.1 $TiO_2$ NTA structural characterization | 23 |

|   |     | 3.1.2    | $TiO_2$ NTA electrical characterization   | 28 |

|---|-----|----------|-------------------------------------------|----|

|   |     | 3.1.3    | Conclusions                               | 32 |

|   | 3.2 | $TiO_2$  | Thin Film                                 | 33 |

|   |     | 3.2.1    | Material Characterization                 | 35 |

|   |     | 3.2.2    | Electrical Characterization               | 39 |

|   |     | 3.2.3    | Conclusion                                | 42 |

| 4 | ZnC | based    | resistive switching                       | 44 |

|   | 4.1 | ZnO T    | hin Films                                 | 44 |

|   |     | 4.1.1    | Material Characterization                 | 45 |

|   |     | 4.1.2    | Electrical Characterization               | 51 |

|   |     | 4.1.3    | Conclusions                               | 57 |

| 5 | Men | nristive | Neuromorphic Systems                      | 59 |

|   | 5.1 | STDP     | and Fusi Learning                         | 61 |

|   | 5.2 | HfO R    | esistive Switching                        | 63 |

|   |     | 5.2.1    | Characterization                          | 63 |

|   |     | 5.2.2    | Modeling                                  | 66 |

|   |     | 5.2.3    | Memristor implications to Neural Networks | 67 |

|   | 5.3 | Neuro    | morphic hardware architecture             | 68 |

|   | 5.4 | Netwo    | rk                                        | 71 |

|   |     | 5.4.1    | Neurons Populations                       | 71 |

|   |     | 5.4.2    | Synaptic Connections                      | 72 |

|   |     | 5.4.3    | Perceptron                                | 73 |

|   |     | 5.4.4    | Linear Synapses Network                   | 79 |

|   |     | 5.4.5    | Fast Dynamic Memristive Network           | 85 |

|   |     | 5.4.6    | Slow Dynamic Memristive Network           | 90 |

ix

|    | 5.5         | Conclusions                            | 94  |

|----|-------------|----------------------------------------|-----|

| 6  | Con         | clusions                               | 96  |

| Re | feren       | ces                                    | 101 |

| Ар | pend        | ix A Fast Dynamics Resistive Switching | 111 |

|    | A.1         | Modeling                               | 113 |

| Ар | pend        | ix B Parameters Investigation          | 116 |

|    | <b>B</b> .1 | Unbounded Calcium Current              | 117 |

|    | B.2         | Bounded Calcium Current                | 117 |

|    | B.3         | Dynamic Calcium Current                | 118 |

|    | B.4         | Homeostatic Principle                  | 118 |

|    | B.5         | Double Calcium Bands                   | 119 |

# **List of Figures**

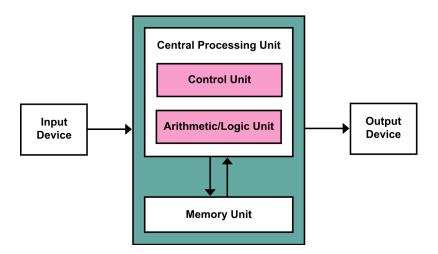

| 1.1 | Von Neumann Architecture                                                                                                                                                                                                                                                                                                                                                                                       | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

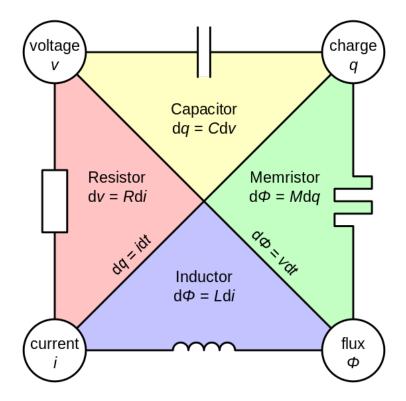

| 1.2 | Definition of the memristor from symmetric reasoning                                                                                                                                                                                                                                                                                                                                                           | 7  |

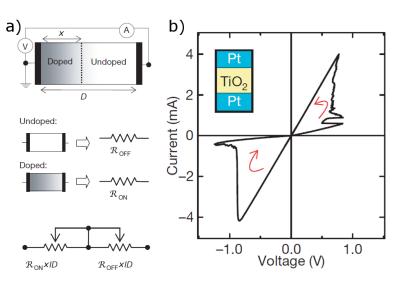

| 1.3 | HP Labs model of $TiO_2$ -based memristor                                                                                                                                                                                                                                                                                                                                                                      | 10 |

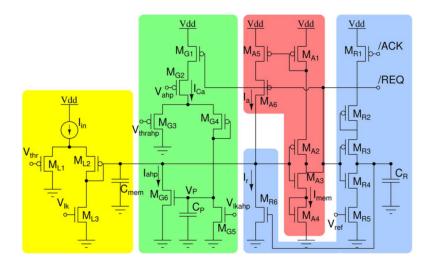

| 1.4 | Schematics of Integrate and Fire Neuron.                                                                                                                                                                                                                                                                                                                                                                       | 12 |

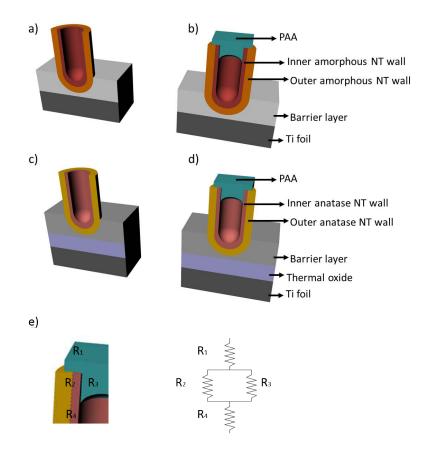

| 3.1 | 3D drawing of the $TiO_2$ NTA samples, representing the multilayer<br>structure of the nanotubes. Panels a) and b) show as-grown material<br>without and with partially conformal PAA coating. Panels c) and<br>d) show corresponding annealed NTA structure, highlighting insur-<br>gence of thermal oxide as intermediate layer. Panel e) shows the<br>equivalent electric circuit schematics for the device | 24 |

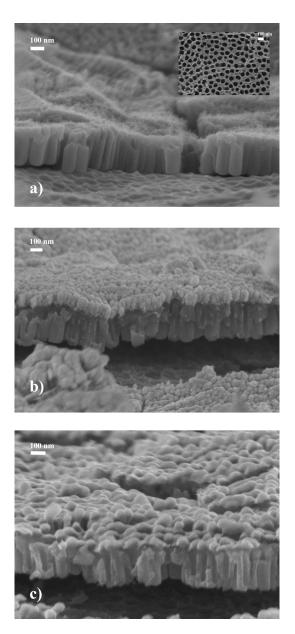

| 3.2 | FESEM characterization of NTA samples in top view, inset of panel<br>a), and cross-section. Panel a), as grown material. Panel b), Pt<br>coated NTA. Panel c), PAA coated NTA. PAA coating creates a<br>homogeneous layer partially filling the tube cavities                                                                                                                                                  | 26 |

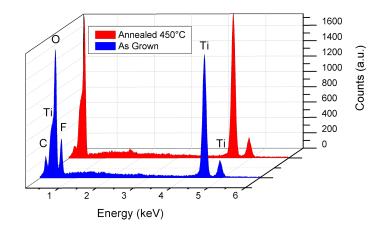

| 3.3 | EDX characterization of NTA samples. As-grown material shows typical peaks of Carbon and Fluorine (blue trace), while only Tita-<br>nium and Oxygen are present in annealed sample (red trace)                                                                                                                                                                                                                 | 27 |

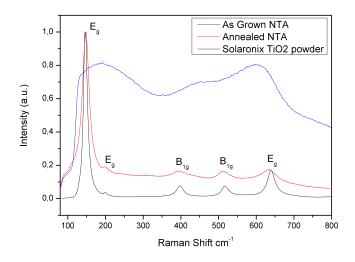

| 3.4 | Raman spectroscopy of as-grown (blue trace), and annealed (red trace) NTA devices. For comparison, it is reported Raman spectroscopy for commercial $TiO_2$ powder                                                                                                                                                                                                                                             | 27 |

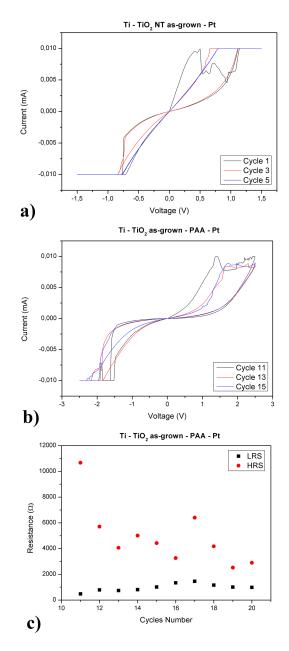

| tive switching behavior. Panel c), resistance states for $PAA/Pt$ device, measured at $V = 0.1V$ , for the first ten                                                                                                           | 29                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| representative cycles for $Ti/TiO_2 - ann/Pt$ device.<br>re qualitatively representative cycles for $Ti/TiO_2$ –<br>device showing resistive switching behavior. Panel<br>states for the $Ti/TiO_2/PAA/Pt$ device, measured at | 31                                                                                                                                                                                                                                                                                                               |

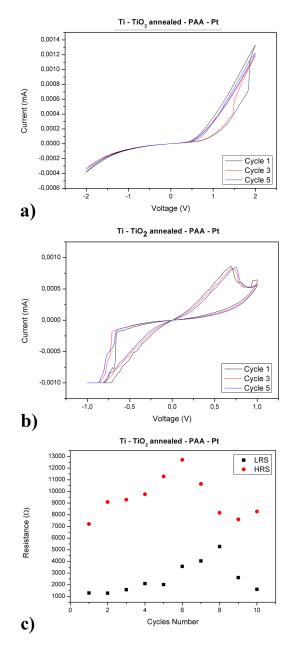

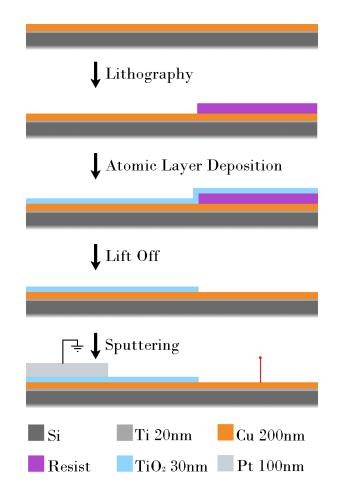

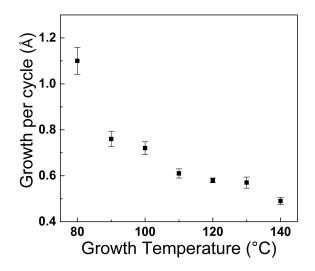

| •                                                                                                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                               |

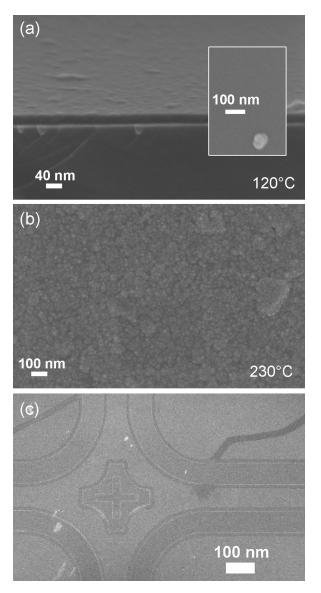

| (inset) of material deposited at 120°C. Panel b), top<br>ial deposited at temperature of 230°C. Panel c), top                                                                                                                  | 36                                                                                                                                                                                                                                                                                                               |

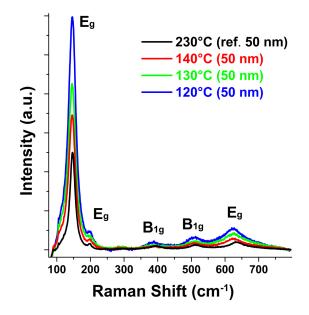

|                                                                                                                                                                                                                                | 37                                                                                                                                                                                                                                                                                                               |

| leasured peaks, as reported in table 3.2, are typical of                                                                                                                                                                       | 38                                                                                                                                                                                                                                                                                                               |

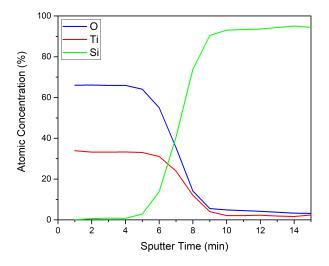

| ofile of $TiO_2$ thin film device deposited at $120^{\circ}C.$ 3                                                                                                                                                               | 39                                                                                                                                                                                                                                                                                                               |

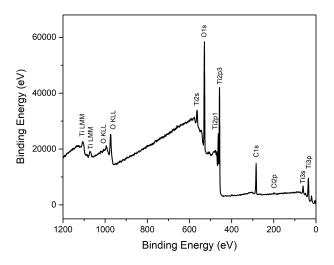

| ls of $TiO_2$ thin film device deposited at $120^{\circ}C.$ 4                                                                                                                                                                  | 40                                                                                                                                                                                                                                                                                                               |

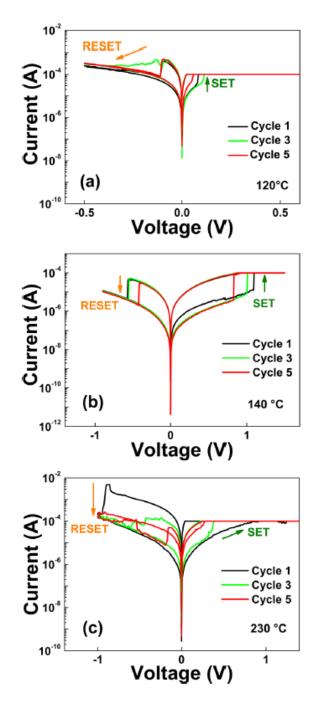

| different temperatures. Three representative cycles able bipolar resistive switching behavior for devices                                                                                                                      | 41                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                | racterization of annealed NTA devices. Panel a), three<br>representative cycles for $Ti/TiO_2 - ann/Pt$ device.<br>we qualitatively representative cycles for $Ti/TiO_2$ –<br>device showing resistive switching behavior. Panel<br>states for the $Ti/TiO_2/PAA/Pt$ device, measured at<br>the first ten cycles |

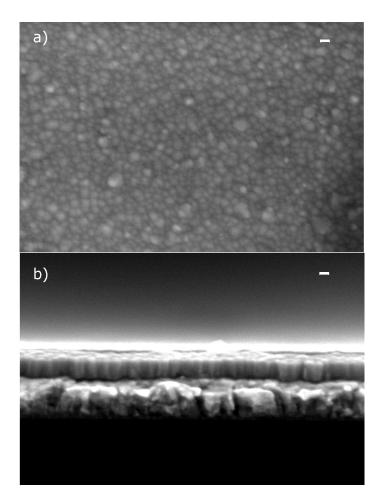

| 4.1 | FESEM characterization of ZnO - 50 nm sample deposited on Si/Ta/Pt substrate. Panel a), top-view. Panel b), cross-section. In both the cases, images are acquired at 500k magnification while the scale bar is 20 nm.                                                                                                                                                                                                                                                                                                                                                                                                      | 46 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

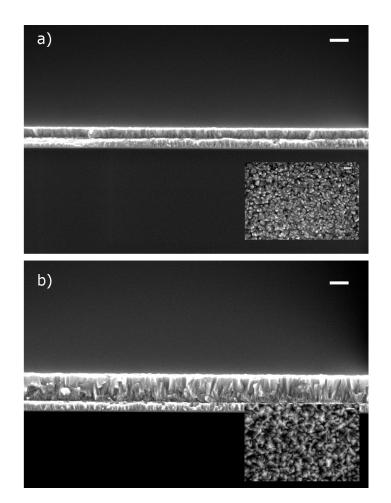

| 4.2 | FESEM characterization of ZnO samples. Panel a), ZnO - 100 nm<br>layer as observed in cross section with SEM at 100k magnification,<br>the shown scale bar is 200 nm. Panel a) inset, ZnO - 100 nm layer<br>as observed in top view with SEM at 250k magnification, the shown<br>scale bar is 100 nm. Panel b), ZnO - 250 nm layer as observed in<br>cross section with SEM at 100k magnification, the shown scale bar<br>is 200 nm. Panel b) inset, ZnO - 250 nm layer as observed in top<br>view with SEM at 250k magnification, the shown scale bar<br>is 100 nm. Panel b) inset, ZnO - 250 nm layer as observed in top | 47 |

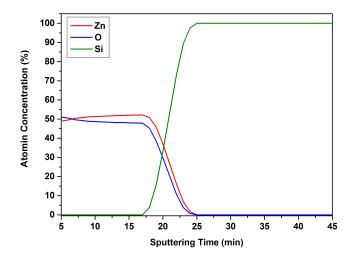

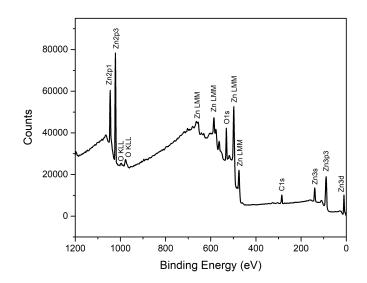

| 4.3 | XPS depth profile of ZnO-based MIM memristive devices, at ZnO film thickness of 100 nm as reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48 |

| 4.4 | XPS core levels spectrum of ZnO-based MIM memristive devices, at ZnO film thickness of 100 nm as reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |

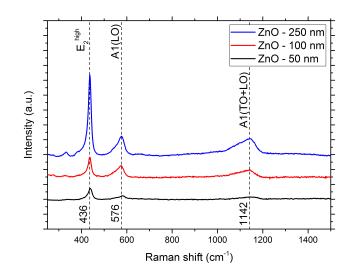

| 4.5 | Raman spectroscopy of ZnO samples at 50 nm thickness (black trace), 100 nm thickness (red trace), 250 nm thickness (blue trace) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49 |

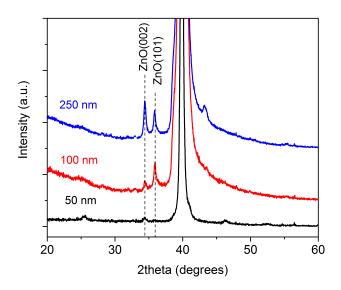

| 4.6 | XRD spectra of ZnO-based MIM memristive devices, at the different ZnO film thickness of 50 nm, 100 nm, and 250 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50 |

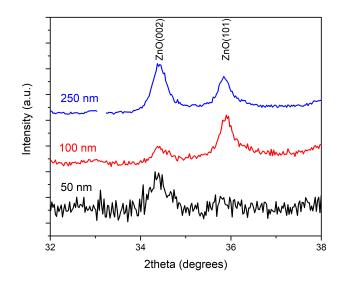

| 4.7 | XRD spectra detail of ZnO-based MIM memristive devices, at the different ZnO film thickness of 50 nm, 100 nm, and 250 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50 |

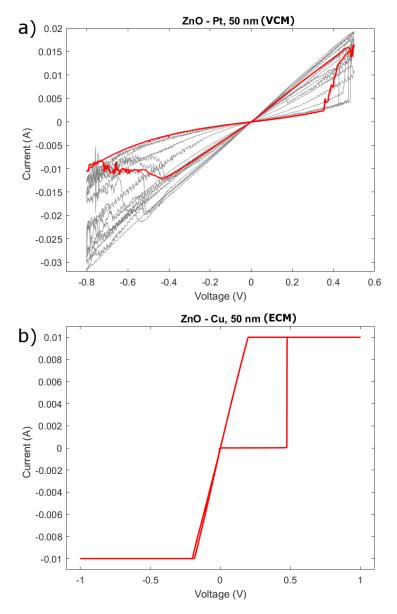

| 4.8 | Electrical characterization for ZnO - 50 nm samples. Panel a), volt-<br>age sweep cycles for ZnO/Pt sample showing bipolar resistive switch-<br>ing behavior; representative cycle is reported in red. SET transition<br>is observed in positive voltage polarity, RESET transition is ob-<br>served in negative voltage polarity. Panel b), voltage sweep cycle<br>for ZnO/Cu sample. Dielectric breakdown is observed in positive<br>polarity and irreversibly shortcut the davies                                                                                                                                       | 52 |

|     | polarity and irreversibly shortcut the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52 |

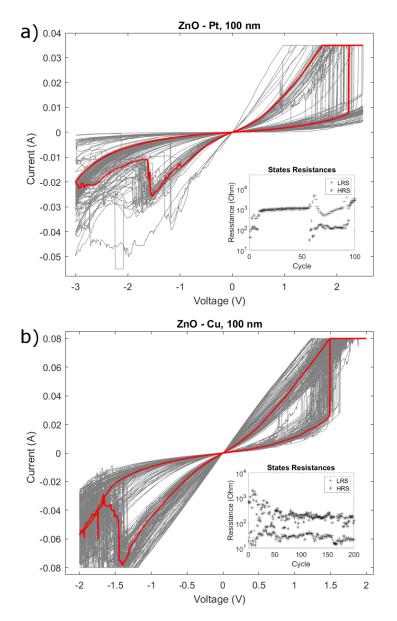

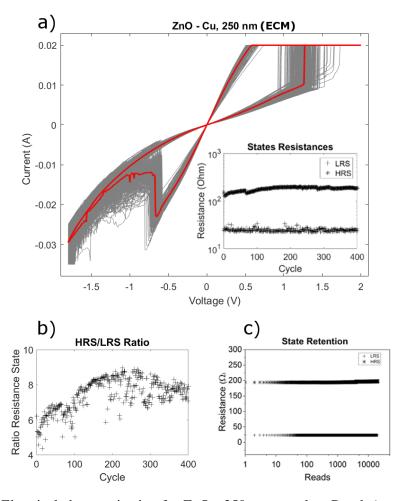

4.9 Electrical characterization for ZnO - 100 nm samples. Panel a), voltage sweep cycles for ZnO/Pt sample showing bipolar resistive switching behavior; representative cycle is reported in red. High failure rate is observed. SET transition is observed in positive voltage polarity, RESET transition is observed in negative voltage polarity. Panel a) inset, resistance states measured at V = 0.1V for 100 cycles. Panel b), voltage sweep cycles for ZnO/Cu sample showing bipolar resistive switching behavior; representative cycle is reported in red. SET transition is observed in positive voltage polarity, RESET transition is observed in negative voltage polarity. Panel b) inset, resistance states measured at V = 0.1V for 100 cycles. . . . . . 54 4.10 Electrical characterization for ZnO - 250 nm samples. Panel a), voltage sweep cycles for ZnO/Cu sample showing stable and repeatable bipolar resistive switching behavior; representative cycle is reported in red. SET transition is observed in positive voltage polarity, RESET transition is observed in negative voltage polarity. Panel a) inset, resistance states measured at V = 0.1V for 400 cycles. Panel b), resistance states ratio computed for 400 cycles. Panel c), retention measurements for LRS and HRS, measured with V = 0.1V,

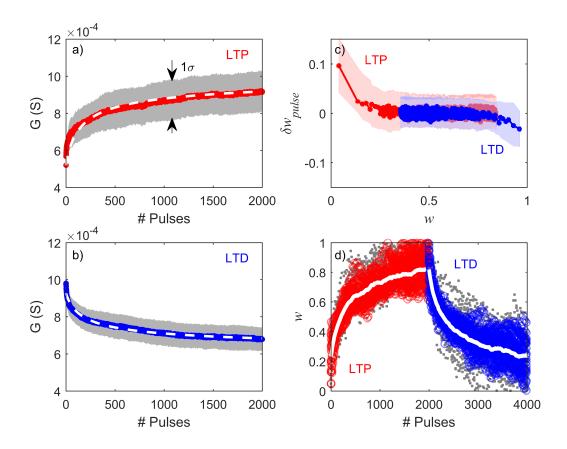

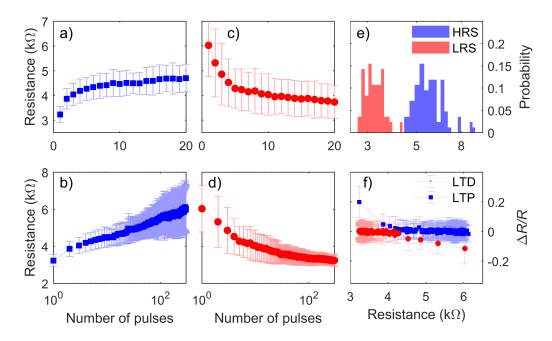

| 5.2 | RRAM representative conductance evolution as a function of the                                                                                   |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | number of pulses from 1 to 2k pulses for LTP (a) and LTD (b):                                                                                    |    |

|     | symbols correspond to the average of 50 experimental curves; dashed                                                                              |    |

|     | lines are the fitting curves. Grey shaded regions correspond to $1\sigma$                                                                        |    |

|     | variability. (c) Conductance change driven by one pulse as a function                                                                            |    |

|     | of the initial resistance for both LTP and LTD, in red and blue                                                                                  |    |

|     | respectively. (d) Comparison of tens of weight evolution as obtained                                                                             |    |

|     | from device and simulations including pulse-to-pulse variability for                                                                             |    |

|     | LTP (from pulse 1 to 2000) and LTD (from pulse 2000 to 4000).                                                                                    |    |

|     | Grey small filled symbols are experimental data and large empty                                                                                  |    |

|     | symbols corresponds to the simulated data. Thick white lines are the                                                                             |    |

|     | average of the simulated data                                                                                                                    | 65 |

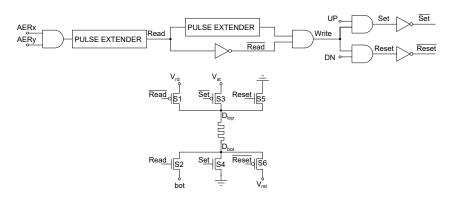

| 5.3 | A memristor synapse. <i>AERx</i> and <i>AERy</i> are the select signals used to access the synapse. The node marked <i>bot</i> will be connected |    |

|     | to a sensing circuit that sets the node voltage to Vrdb. UP and                                                                                  |    |

|     | DN are inputs to the synapse that determine if the conductance                                                                                   |    |

|     | of the memristor should be increased or decreased. $V_{st}$ and $V_{rst}$                                                                        |    |

|     | are the voltages applied across the memristor when increasing and                                                                                |    |

|     | decreasing its conductance, respectively                                                                                                         | 69 |

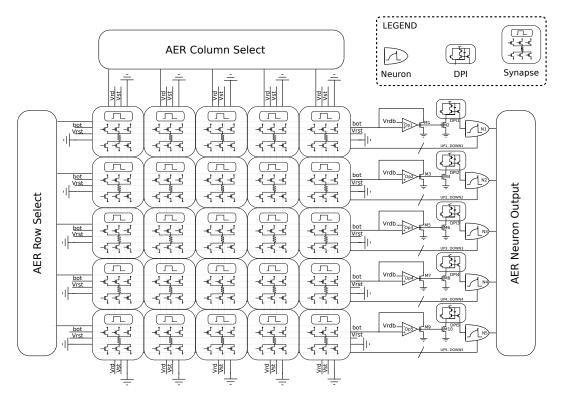

| 5.4 | A neuromorphic system implementing the proposed learning ar-                                                                                     |    |

|     | chitecture. The AER Row and Column select modules generate                                                                                       |    |

|     | the AERx and AERy signals, shown in Figure 5.3, to access each                                                                                   |    |

|     | synapse. The AER Neuron output module communicates the spikes                                                                                    |    |

|     | generated by the neurons to the configured target                                                                                                | 70 |

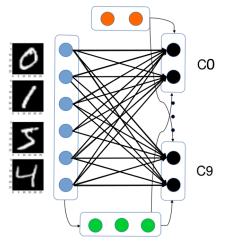

| 5.5 | Architecture of the complete network adopted in the learning task.                                                                               |    |

|     | Four different neurons population are represented in different colors.                                                                           |    |

|     | IP is represented in blue and inputed with MNIST digits as repre-                                                                                |    |

|     | sented in the picture. InhP is represented in green, TP in orange, OP                                                                            |    |

|     | in black. IP and OP, IP and InhP as well as InhP and OP are fully                                                                                |    |

|     | connected, but for sake of clearness, only the first set of edges is                                                                             |    |

|     | shown in the picture. Only synaptic connections represented with                                                                                 |    |

|     | thicker lines are plastic. TP and OP are connected one to one when                                                                               |    |

|     | a digit belonging to the specific class is presented                                                                                             | 72 |

|     |                                                                                                                                                  |    |

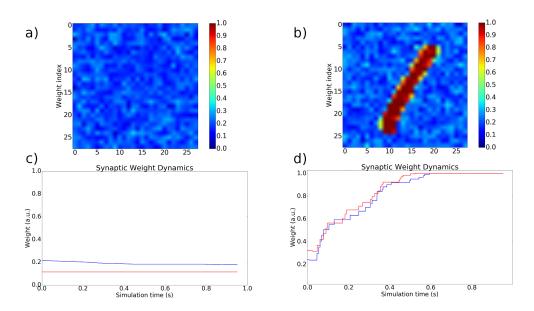

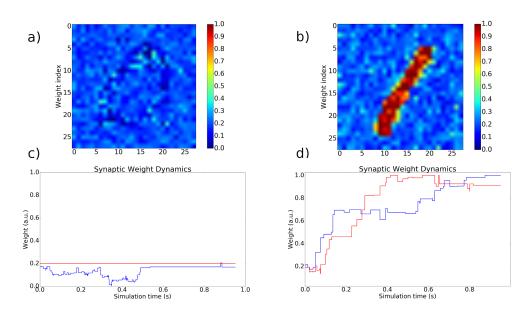

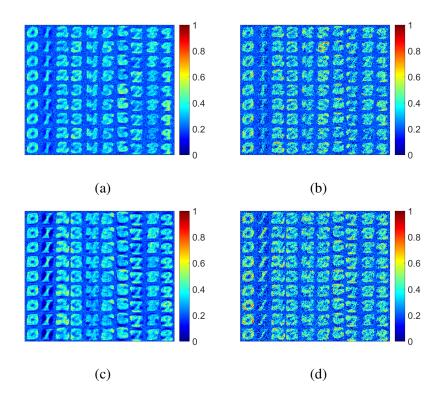

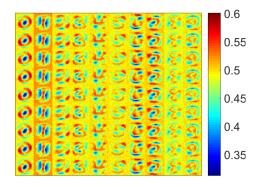

- 5.6 Panel a), synaptic weights after a single 0 digit presented for 900 ms. Panel b), synaptic weights after a single 1 digit presented together with teacher signal. Panels c) and d), dynamics of weights in the former two cases respectively. Blue traces correspond to weight excited by both digits, while red traces correspond to weight excited only by digit 1. Traces make evident LTD process, when the only input is shown, and LTP process when teacher signal is applied. The narrow relative variation in weight for LTD is due to an already high value of initialized resistance, that brings dynamics toward saturation. 75

- 5.7 Panel a), synaptic weights, including device variability, after a single 0 digit presented for 900 ms. Panel b), synaptic weights, including device variability, after a single 1 digit presented together with teacher signal. Panels c) and d), dynamics of weights in the former two cases respectively. Blue traces correspond to weight excited by both digits, while red traces correspond to weight excited only by digit 1. Traces make evident LTD process, when the only input is shown, and LTP process when teacher signal is applied. The device variability is evident in the noisy and non-monotonic dynamics.

76

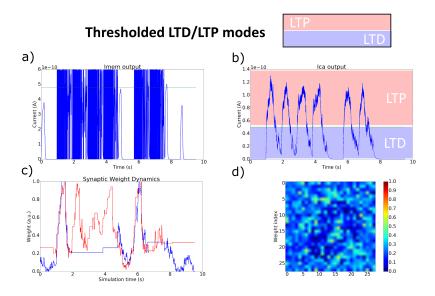

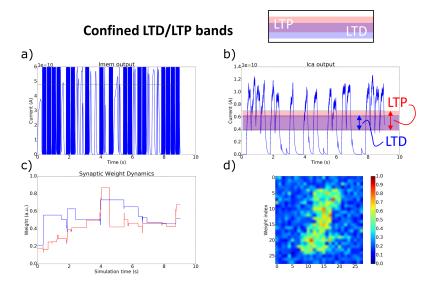

| 5. | Example of perceptron learning dynamics with confined $I_{Ca}$ bands                                                                                                                                                          |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | when 30 input digits are presented. Panel a), output neuron mem-                                                                                                                                                              |    |

|    | brane current. Low frequency corresponds to digit 0 presented. High                                                                                                                                                           |    |

|    | frequency corresponds to digit 1 presented together with teacher                                                                                                                                                              |    |

|    | signal applied. Panel b), output neuron Calcium current acts as a low                                                                                                                                                         |    |

|    | pass filter of membrane current. Regions for LTD and LTP are high-                                                                                                                                                            |    |

|    | lighted. Panel c), dynamics of weights during learning. Blue trace                                                                                                                                                            |    |

|    | corresponds to weight excited by both digits, red trace corresponds                                                                                                                                                           |    |

|    | to weight excited only by digit 1. Confined $I_{Ca}$ bands allow for slow                                                                                                                                                     |    |

|    | dynamics of weights that do preserve acquired features. Panel d),<br>weight map after 30 digits presented.                                                                                                                    | 78 |

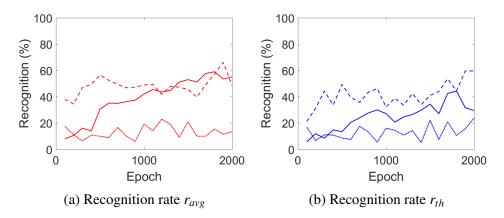

| 5. | Recognition rate $r_{avg}$ , panel a) red lines, and $r_{th}$ , panel b) blue lines, computed for 10 synaptic states available (dotted line), 100 states (dashed line) and 1000 states (solid line) in a 2000 training images |    |

|    | simulation                                                                                                                                                                                                                    | 81 |

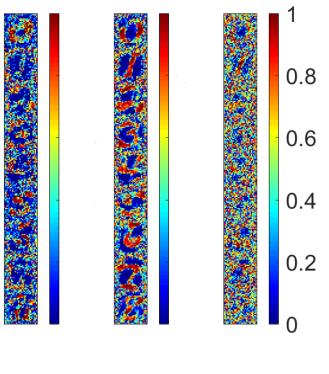

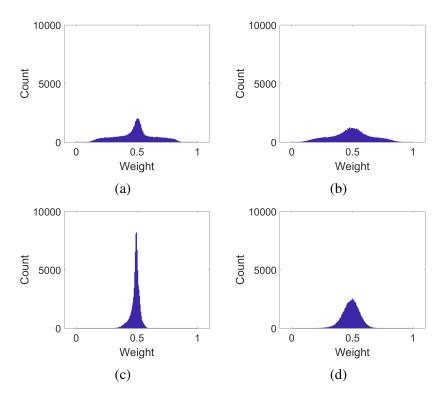

| 5. | Weightmaps obtained after 2000 training images simulations for<br>network embedding linear synapses. Panel a), 10 states available,<br>Panel b) 100 states available, Panels c) 1000 states available 8                       | 82 |

| 5. | Weight distributions obtained after 2000 training images simulations<br>for network embedding linear synapses. Panel a), 10 states available,<br>Panel b) 100 states available, Panels c) 1000 states available 8             | 82 |

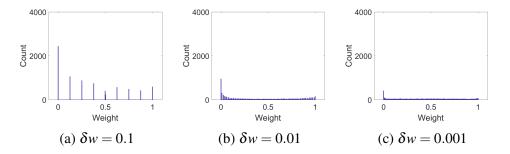

| 5. | Recognition rate $r_{avg}$ , panel a) red lines, and $r_{th}$ , panel b) blue lines, computed for 100 synaptic states available (dashed line) and 1000 states (solid line) in a 20000 training images simulation.             | 83 |

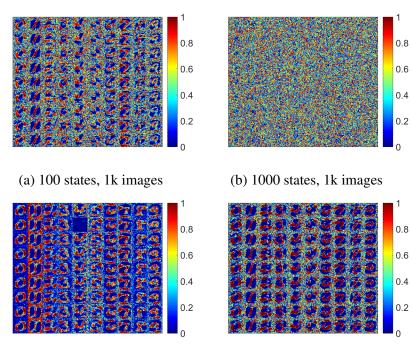

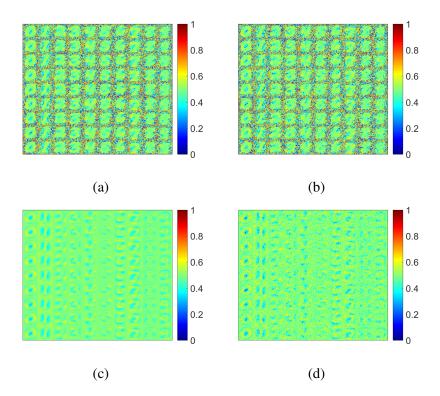

| 5. | Weightmaps obtained after 1000, Panel a) and b), and 20000, Panel c) and d), training images simulations for network embedding linear synapses. Panel a) and c), 100 states available, Panel b) and d), 1000 states available | 84 |

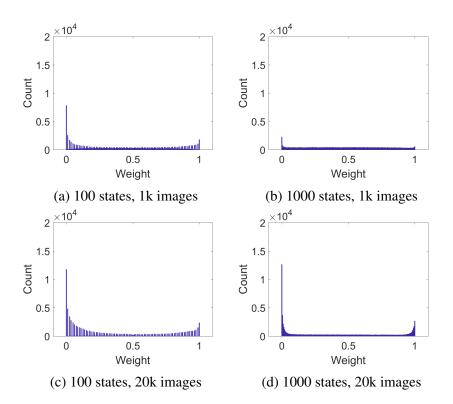

| 5. | Weight distributions obtained after 1000, Panel a) and b), and 20000,<br>Panel c) and d), training images simulations for network embedding<br>linear synapses. Panel a) and c), 100 states available, Panel b) and           |    |

|    | d), 1000 states available                                                                                                                                                                                                     | 85 |

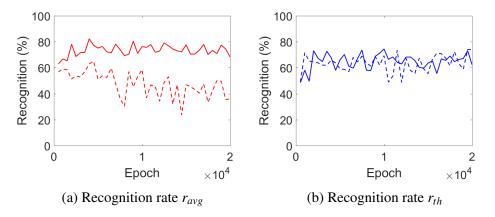

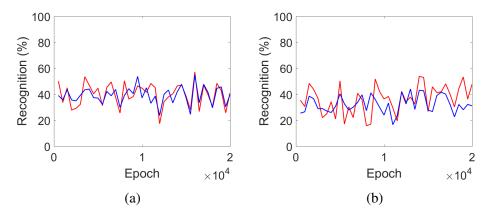

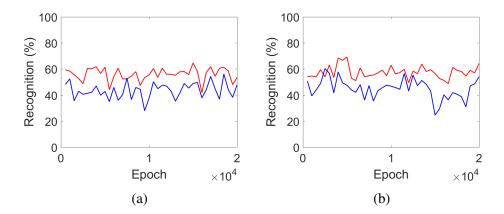

| 5.16 | Panel a), recognition rate achieved by PPS1 memristive network<br>with parameters as specified in tables 5.3 and 5.5, without device<br>variability. Performance are computed as $r_{avg}$ (red line) and $r_{th}$ (blue<br>line) across 20k training epochs. Panel b), recognition rate achieved<br>by memristive network with parameters as specified in 5.5 with<br>device variability. Performance are computed as $r_{avg}$ (red line) and<br>$r_{th}$ (blue line) across 20k training epochs | 87 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.17 | Weight distributions obtained after 1000, Panel a) and b), and 20000,<br>Panel c) and d), training images simulations for network embedding<br>resistive switching synapses. Panel a) and c) report simulations not<br>accounting for device variability, Panel b) and d) report simulations<br>accounting for device variability.                                                                                                                                                                 | 88 |

| 5.18 | Comparison between features maps of synaptic weights for network without device variability, panel a) and c), and network with device variability, panels b) and d). Maps are reported after 1000 epochs, panel a) and b), and after 20000 epochs, panel c) and d).                                                                                                                                                                                                                                | 89 |

| 5.19 | Panel a), recognition rate achieved by PPS2 memristive network<br>with parameters as specified in tables 5.3 and 5.5, without device<br>variability. Performance are computed as $r_{avg}$ (red line) and $r_{th}$ (blue<br>line) across 20k training epochs. Panel b), recognition rate achieved<br>by memristive network with parameters as specified in 5.5 with<br>device variability. Performance are computed as $r_{avg}$ (red line) and<br>$r_{th}$ (blue line) across 20k training epochs | 90 |

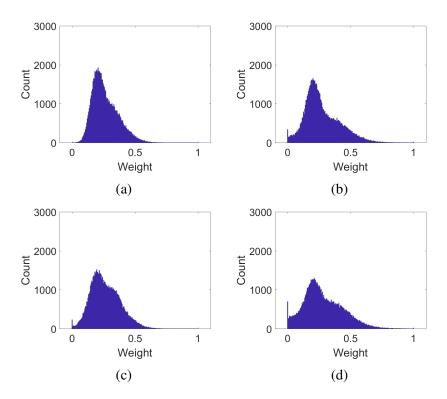

| 5.20 | Weight distributions obtained after 1000, Panel a) and b), and 20000,<br>Panel c) and d), training images simulations for network embedding<br>resistive switching synapses. Panel a) and c) report simulations not<br>accounting for device variability, Panel b) and d) report simulations<br>accounting for device variability                                                                                                                                                                  | 92 |

| 5.21 | Comparison between features maps of synaptic weights for network without device variability, panel a) and c), and network with device variability, panels b) and d). Maps are reported after 1000 epochs, panel a) and b), and after 20000 epochs, panel c) and d).                                                                                                                                                                                                                                | 93 |

| 5.22        | Weightmap of synaptic weights for network without device variabil-<br>ity after 20000 training images presented. False colors map has been<br>rescaled in a narrow range in order to put in evidence discriminative<br>features acquired                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.1         | Representative resistance evolution as a function of the number of pulses from 1 to 50 pulses and from 1 to 300 pulses starting from LRS and HRS for LTD (blue, a and b) and LTD (red, c and d), respectively. Panel e), distribution of resistance values for HRS and LRS obtained after 300 LTD and LTP spikes. Panel f), dependence of the 1-spike normalized resistance change as a function of the pre-spike resistance value. Symbols reports the average among tens of experimental curves acquired on a single device and error bars corresponds to one sigma standard deviation                                                                                                                                                                                                                                                                                                                      |

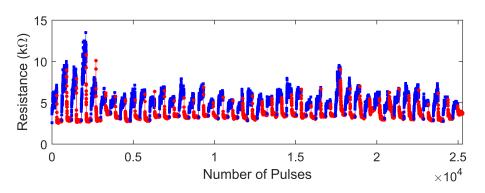

| A.2         | Representative endurance test over LTD (blue squares) and LTP (red circles)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

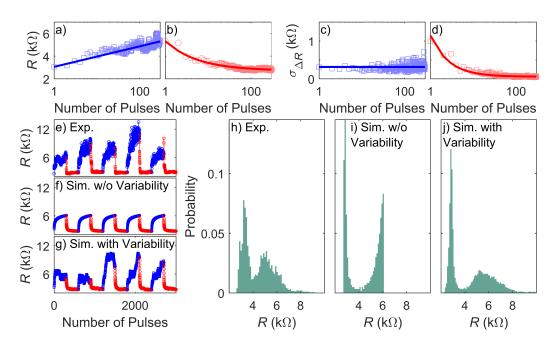

| A.3         | Fitting and simulation of the HfO <sub>2</sub> memristors. Panel a) and b), representative LTD and LTP processes respectively (symbols, the experimental results and lines, fitting according to equation A.1. Panels c) and d), standard deviation of resistance variation per pulse $\Delta R$ for LTD and LTP respectively. Representative switching cycles: experimental, panel e), simulated without variability, panel f), and simulated with pulse to pulse variability, panel g). Resistance values histograms obtained with tens of cycles: experimental, panel h), simulated without variability, panel i) and simulated with pulse to pulse variability, panel i) and simulated with pulse to pulse variability, panel i) and simulated with pulse to pulse variability, panel i) and simulated with pulse to pulse variability, panel i) and simulated with pulse to pulse variability, panel j). |

| <b>B</b> .1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.6         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## **List of Tables**

| 3.1 | NTA devices electrical performances summary.                                                                                              | 32  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | $TiO_2$ Raman peaks center comparison                                                                                                     | 38  |

| 3.3 | $TiO_2$ Raman peaks FWMH comparison                                                                                                       | 39  |

| 3.4 | $TiO_2$ thin film electrical performances summary                                                                                         | 42  |

| 4.1 | ZnO devices electrical performances summary: exhibited LRS, HRS and ratios.                                                               | 55  |

| 4.2 | ZnO devices electrical performances summary: voltage ranges for SET and RESET transitions.                                                | 55  |

| 5.1 | Pulse Parameter sets adopted for electrical characterization of RS devices.                                                               | 64  |

| 5.2 | Values of the fitting parameters for the general synaptic weight<br>evolution and for the modeling of the device variability for both LTD |     |

|     | and LTP                                                                                                                                   | 67  |

| 5.3 | Parameters adopted in the memristive network                                                                                              | 80  |

| 5.4 | Thresholds adopted for $I_{mem}$ and $I_{Ca}$ in the doubled LTD band net-                                                                |     |

|     | work                                                                                                                                      | 80  |

| 5.5 | Thresholds adopted for $I_{mem}$ and $I_{Ca}$ in the doubled LTD band network.                                                            | 87  |

| A.1 | Pulse Parameter sets adopted for electrical characterization of RS devices.                                                               | 111 |

| A.2 | Averages and standard deviations values of the fitting parameters for |     |

|-----|-----------------------------------------------------------------------|-----|

|     | the general resistance evolution and for the modeling of the device   |     |

|     | variability for both LTD and LTP                                      | 115 |

### Chapter 1

### Introduction

### **1.1 Motivations**

Artificial intelligence, (AI), has became one of the most prominent topic in technology, able to agglomerate around itself wide segments of society that in the past usually remained disaggregated with respect to the development of science. Indeed, the scientific community devotes huge efforts in the understanding of basic principles of learning, both from the biologic and computational perspective, and its development in real-world application. Their results are constantly monitored by the industry world, that from applications into the production process up to management of new services, are progressively integrating autonomous robot and machine learning algorithms into their businesses. Interestingly, also the general public is enthusiastically following the success reached by scientists and engineers, developing in parallel to the technological progress a common thought interrogating itself about the ethical and moral implications of artificial intelligence. It may sound almost natural nowadays thinking about robots helping us side by side in our daily life, but still it is an astonishing result getting real day after day. AI signs milestones more and more frequently, winning world championship of chess (IBM's Deep Blue, May 1997), obtaining super-human performance in pattern recognition (IJCNN Competition, 2011, [1]), recently winning he strategy based Go championship with a self-teaching AI (DeepMind & Google's AlphaGo, March 2016). Tools that allow for direct interactions with machine through natural language are widespread, from mobile-phones (Apple's Siri), computers (Microsoft's Cortana), personal assistance

at home (Amazon's Alexa). The latest technology pops up from automotive industry and regards self-driving cars. This is a step further in the realization of the over-mentioned Internet of Things (IoT), constituted by network of devices able to sense stimuli from the real world, communicate among each-other and actuate in order to accomplish specific tasks. Devices in the internet of things are requested to operate autonomously in remote areas, where in principle, electric power could not be sufficiently available and remote control cannot be feasible. Nonetheless, device activity needs to be desirably efficient, avoiding failures in task performances. In order to accomplish such a demanding requirement, devices must be compact, power efficient, optimized from the algorithmic standpoint and, above all, *smart*.

Smart devices must be able to process information gathered from the environment and perform predictions about its dynamic. Such a prior information is then evaluated to take decisions leading to the successfully accomplished task. In principle, it is a particularly power demanding activity and it may be hardly implemented on remote devices, that nowadays are indeed constantly communicating with servers where computation is performed. This leads, just as examples, to delays in response to stimuli, approximated analysis due to incomplete data, suffer from connection failures... local computation would solve many of these limitations, struggling on the other hand with the limited computational power.

Such an important challenge brought the scientific community to investigate further machine learning algorithms and device architectures, looking for inspiration from nature. The most effective example of extreme computational power, combined with power efficiency, is undoubtedly the human brain.

The human brain has astonishing capabilities with a limited amount of resources. We are able to perform task characterized by a high level of complexity, such as recognizing faces in very corrupted environment, as well as sounds, communicate with multiple languages, define complex activity strategies based on external dynamic variables. All of this with a more efficient power consumption, [2]. Brain has developed in its evolution an highly parallelized architecture completely different from the Von Neumann one, that stays at the basis of computers. Von Neumann architectures requires the computation unit (ALU) and the memory unit to be distinguished inside the central processing unit (CPU), [3], see figure 1.1.

Within brain, such a distinction is not existing anymore and the computation unit is merged with the memory unit, through synapses. The neural network is indeed built out of about  $10^{11}$  neurons, each of them generating an average of  $10^4$

Fig. 1.1 Von Neumann Architecture

connections with other neurons in the cortex, [4]. These are dynamic connections, i.e. synapses, that emerge or disappear according to the network functioning. Moreover, their efficacy evolves in time according to the task performed, shaping what we call memory, [5]. From this perspective, synapses are both the processing unit of our brain, whose information is transmitted across neurons that acts as center of integration, and the center where memory is stored. It is the neurons activity itself that allows synaptic strength to change in time, according to a learning rule named spike-timing dependent plasticity, (STDP), [6–9]

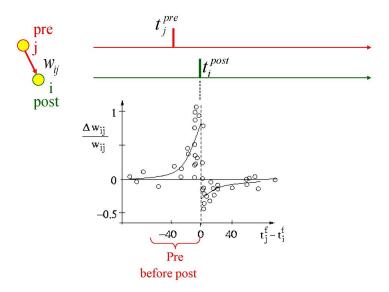

According to STDP, the time-correlation between the firing activity of pre-synaptic neurons and post-synaptic neuron is responsible for potentiating or depressing the synapse efficacy. Specifically, if a post-synaptic spike follows in time a pre-synaptic spike, synapse strengthen its efficacy proportionally to their delay. Vice-versa, if post-synaptic spike comes earlier that the pre-synaptic spike, i.e. the spikes are anti-correlated in time, the synapse becomes depressed. In this way, information processing happens locally in time and space, i.e. only when spikes occur at the level of single synapse, and in parallel, thus for multiple synapses at the same time. Both features are particularly desirable for algorithms embedded on independent smart devices.

Because of all of these features expressed by the human brain functioning, the scientific community began to investigate it also from the robotics and computer science perspective. A new emergent technology seems to be particularly promising for the realization of artificial neural network in hardware, called resistive switchings.

### **1.2 Resistive Switching and Memristor**

Resistive switching are devices able to perform a reversible transition in their resistivity according to the variation of an external variable, like temperature, pressure, magnetic field, voltage, [10]. Among the many physical mechanisms involved with different material, the resistive switching addressed in this dissertation are only those involving as control variable the applied voltage. Huge investigation in the field comes from micro-electronics companies. Indeed more-than-Moore technologies are of paramount importance in companies outlook, since the current transistor based technology is reaching its physical limit, [11]. The Moore's law, [12], empirically defined in 1965, by Gordon Moore, founder of Intel, stated that the micro-processors complexity doubles every 18 months. Taking in account that the chip board remains nearly constant, the Moore's law imply a constant doubling of chip density. Since its definition, Moore's law has been taken as growth target for all electronic components producers, pushing the technology process toward optimized Metal-Oxide-Semiconductor (MOS) fabrication with lower and lower channel size. From the 60s, the channel dimension of CMOS stepped from microns to the 32 nm currently implemented in standard commercial laptops. Further research scales down this reference dimension to 20 nm, touching the extreme limit of 16 nm, [13]. It is the limit imposed by physics to Moore's law, since below this dimension, the silicon doping allowing the functioning of MOS as logic gates cannot be guaranteed anymore to be equivalent for all the nodes, i.e. being the doping process intrinsically stochastic, the number of doping atoms in the channel cannot be tuned and lead to a higher failure rate of single nodes in operative conditions. From this scenario comes the pressure laying behind the investigation of resistive switching technology. Indeed, different physical mechanisms would allow a further scale down of chip components dimensions primarly for random access memories fabrication (RAM). Particularly attractive from this standpoint appear to be magnetoresistances (MRAM) [14], based on spintronics, phase change memories (PRAM), [15], and, more recently, resistive switching (ReRAM), [16, 17]. Resistive switching phenomenon is observed with a large varieties of devices characterized by different architectures, metal-insulator-metal (MIM) layers or nanostructures, different materials, like transition metal oxides [18], transitional metal dichalcogenides [19], graphene-based structures [20], organic compounds [21], colloids [22]. Among them, binary oxides, like TiO<sub>2</sub> [23], Ta<sub>2</sub>O<sub>5</sub> [24], ZnO [25], HfO [26], WO<sub>3</sub> [27], NiO [28], appears to

be particularly promising for ReRAM applications. Mechanisms laying behind the resitive switching phenomenon in MIM architecture are still under deep investigation [29], but can classified in two major areas, i.e. valence change memories (VCM) and electro-chemical memories (ECM), [16]. The former mechanisms involves the presence of defects in the transition metal oxide matrix in the form of oxygen vacancies. The absence of one oxygen atom in the lattice (that often is amorphous or polycrystalline) creates a locally positive charged that is unstably occupied by electrons, in order to respect the neutrality principle. The positively charged oxygen vacancies thus are subject to external electric field imposed through the application of a voltage to the two electrodes of the MIM structure and drifts through the lattice. A distinction at this stage is done, identifying interface-type mechanism, [30, 31], and filamentary mechanisms [32], depending on the characteristics of the material adopted as insulator. With interface resistive switching, the insulator layer can be observed to contain a sublayer under-stoichiometric with respect to the whole lattice. Its resistance thus would be lower than the stoichiometric sub-layer and the whole structure would act as the series of two resistances. Under the effect of external electric field and with proper lattice properties, the interface between the two layers could move, reaching the opposite electrode from the one where voltage is applied. As soon as the whole lattice is homogeneously under-stoichiometric, the MIM device switches from a high resistance state (HRS) to a low resistance state (LRS). In filamentary RS on the other hand, rather than a moving interface, the movement of oxygen vacancies is favored withing a tiny region of the lattice that thus assumes locally a lower stoichiometry, [33]. The difference between the two mechanisms is strongly dependent on the lattice properties, as it is determined by the potential barriers height and distribution encountered by oxygen vacancies while drifting.

The second major subset of RS accounts for electro-chemical memories. ECM require the presence of an electro-migrating metal element as one of the two electrodes adopted for the MIM structure, like Ag or Cu, [34]. In ECM, when positive voltage is applied to the electro-migrating electrode, redox reaction happens at the interface between metal and insulator, leading to anodic dissolution of metallic cations subject to the electric field drift. Depending on the ion mobility within the insulator matrix, they will reach the opposite electrode creating a so called Conductive Filament (CF). CF is a metallic shortcut, cone-shaped, between the two electrode and through the insulating material, usually few tens of nm in diameter [35].

In both mechanism, the phenomenon is reversible when opposite polarity voltage is

applied and imposes drift toward the electrode of origin. When the LRS is reached in fact, the electronic current transport dissipates energy under form of heat, respecting the Joule law. Above a certain threshold thus, the CF can be interrupted and the newly generated ions (both vacancies in the case of VCM and metal ions in case of ECM) are drifted backward from the grounded electrode.

An optimized resistive switching reaches good repeatability in switching, cycle to cycle endurance and state retention. Companies' objective is the production of ReRAM featuring these quality measures comparable to the present transistor-based technology.

In 2008, the interest of the scientific community was awakened by results from HP labs. The group of Strukov and William in fact, published a description of  $TiO_2$  based MIM resistive switching modeled as a memristor, [36].

Memristor, literally the contraction of the terms memory and resistor, was postulated by Leon Chua in 1971 as the fourth missing fundamental circuit element, together with resistor, capacitor and inductor, [37]. He proceeded from symmetrical reasoning, comparing the constitutive equations of the three elements,

$$dv = R di$$

$$dq = C dv$$

$$d\phi = L di$$

(1.1)

together with the definition of charge and magnetic flux as:

$$q = \int i \, dt \tag{1.2}$$

$$\phi = \int v \, dt$$

Observing the previous set of equations, graphically depicted in figure 1.2, it emerges that all the constitutive equations derive from the relation between two of the fundamental quantities v, i, q and  $\phi$ , but no relation exists between charge and magnetic flux. Chua in [37] demonstrate that such a relation can exists for a passive element, whose constitutive equation can be written as:

$$\phi = f(q)$$

$$d\phi = M(q) dq$$

(1.3)

where M(q) is the so called *memristance*.

Fig. 1.2 Definition of the memristor from symmetric reasoning

Notice that one can always take the time derivative of such a constitutive equation, obtaining:

$$\begin{cases} v(t) = \frac{df(q)}{dq} i(t) = M(q) i(t) \\ \frac{dq}{dt} = i(t) \end{cases}$$

(1.4)

Some observation is important already at this stage about the memristor definition. First of all, the memristor is intrinsically a non-linear element, since if M(q)would be constant, integrating the constitutive equation would lead to the case of linear resistor. Moreover, the quantity  $\phi$  involved in the constitutive equation comes from the Lenz's law, that states the existence of an electromotive force, i.e. a voltage, induced by the time variation of magnetic flux. This is certainly true in the case of an inductor, where a coil generates a magnetic field, but it is not necessarily implied in the case of a memristor, as it will be clarify in the next of this dissertation. Indeed,  $\phi$  should be considered not as a magnetic flux, but only as the integral of voltage in time, and for this reason it will be called, as in the most recent literature, *voltage momentum*, [38].

Memristor is an element with memory, i.e. its memristance value depends on the quantity of charged that passed through the element under the effect of the applied voltage in time. Thus, the history of the applied signal determines the resistance state of the device.

As last consideration at this stage, from the equation 1.4 it can obtained that the memristor fingerprint is an hysteresis loop pinched at the origin of axis, as the one shown in figure 1.3.

In 1976, the memristor definition was generalized to non ideal cases by Leon Chua and Sung M. Kang, introducing a so called *state variable* collecting all other dependencies of the memristance different from charge, [39]. The new obtained set of equation becomes then, in terms of voltage momentum and charge:

$$\begin{cases} \phi = f(q, x(t)) \\ \frac{dx(t)}{dt} = g(x, i) \\ \frac{dq(t)}{dt} = i \end{cases}$$

(1.5)

and in terms of voltage and current:

$$\begin{cases} v(t) = M(q, x(t)) \ i(t) \\ \frac{dx(t)}{dt} = g(x, i) \end{cases}$$

(1.6)

where g(x,i) is the dynamic functional relation that specifies the evolution in time of the state variables controlling the memristor and specifies the whole physics involved. Examples of such variables could be the internal temperature, the applied electric field, defect concentration etc., depending on the system under test. As it can be noticed, the memristor is described as a non-linear dynamic systems. In 2008, HP labs scientists, Dmitri B. Strukov and Stanley R. Williams published in Nature for the first time the description of a resistive switching, based on  $TiO_2$ and with MIM architecture, as a memristor, titling the paper "The missing memristor found", [36]. In that case, they provided a simple model of interface-type resistive switching, with a separation between region rich in positively charged dopant, i.e. oxygen vacancies, and region poor of dopant, i.e. stoichiometric metal oxide, see figure 1.3. Application of the external bias imposes a drift of the region boundary, modeled as state variable of the system. Thus, considering the total thickness of the device *D* and the dopant mobility  $\mu_V$ , they write the dynamic equation of the system as the series of two resistances:

$$v(t) = \left(R_{ON}\frac{x(t)}{D} + R_{OFF}\left(1 - \frac{x(t)}{D}\right)\right)i(t)$$

$$\frac{dx(t)}{dt} = \mu_V \frac{R_{ON}}{D}i(t)$$

(1.7)

That yields for what concerns the state variable dynamics:

$$x(t) = \mu_V \frac{R_{ON}}{D} q(t) \tag{1.8}$$

The impact of such a paper on the scientific community was incredibly high, since boosted renovated research on a field that since 1976 was stuck to purely theoretical results, without any experimental counterpart. On the contrary, from that moment on, huge scientific effort is devoted to the investigation of the physical mechanism behind the resistive switching devices, together with their theoretical modeling in the framework of Chua's formalism.

From the perspective of neuromorphic systems, memristors offer particularly favorable features to mimic synapse functioning. In fact, synapse is a junction between two nodes of a circuit and it is in charge to transfer a weighted information depending on its relevance for accomplishing a task. Relevance then is gathered via *experience*, if we are talking from a biology perspective, or through what the network has learned during its training phase, talking from the computer science standpoint. Indeed, while learning synapses change their synaptic weight, i.e. their efficacy, according to the signal they observe and then preserve that change. At the

Fig. 1.3 HP Labs model of *TiO*<sub>2</sub>-based memristor.

very same level, memristor reaches a resistance state, mathematically formalized by its state variable, depending on the history of signals applied and then preserves memory of it. It means that, within a network, signals in the form of electric current can be weighted by the internal resistance of memristors while being transferred to other nodes. In the extreme cases, a highly insulating memristor is equivalent to an open circuit and the information is not transferred, while a memristor in conductive state lets the information be transferred without attenuation.

Memristors, in the experimental form of resistive switching, can be reasonably investigated as synaptic element of hardware neural network to be embedded in future smart devices.

### **1.3 Spiking Neural Network**

Hardware devices designed specifically for machine learning purposes are usually referred to as hardware neural networks (HNN). Since the end of the past century, together with the faster development of deep neural networks in software simulations, HNN received great attention because of their inherent advantages with respect to the traditional computing technologies. Indeed, state of the art neural networks, such as convolutional neural networks (CNN) and recurrent neural networks (RNN) are particularly computational demanding. Moreover, NN are intrinsically parallel in the computing architecture, but higher complexity of electronic systems is required when transferred on a serial computing architecture.

HNN then are particularly desirable for several properties: *speed*, specialized hardware are optimized for learning tasks, outperforming standard technologies; intrinsically hardware-embedded *parallel* computing allows for improved computational power and speed on the one side and, on the other, it provides a particularly robust infrastructure against system failures and *degradation*. Indeed, serial architectures are particularly vulnerable to *fail-stop* operations, mainly because of lack of redundancy. On the contrary, neural networks are extremely tolerant to single connection failures as well as noise, and rather than stopping, they continue to operate with reduced performances. All of these characteristics make HNN of considerable advantage for the development of smart and remote technologies, [40].

If the number of advantages for HNN is considerable, a still large number of challenges must be faced by HNN designers. The most prominent regards the network topology, whose high connection degree could result in a complex pattern of connectivity to be transferred in silicon. Moreover, hardware technology could potentially introduce further variability to the one accounted in the normal function of learning. Another important fact is the non-linearity of activation function required by learning algorithm, that for digital technology could require complex and power-angry control circuits.

The complete landscape of HNN different implementations thus is still variegated and accounts for multiple solution dealing with the aforementioned problems. They include digital, analog, hybrid solutions, optical solutions, FPGA (Field Programmable Gate Array) based solutions, VLSI (Very Large Scale Integration) solutions.

Among those, neuromorphic Spiking Neural Networks (SNN) are gathering more and more interest for many reasons. First they are *event-based* networks, where computation happens only when an event, i.e. an electric (often differential) signal is inputed to the network sensors. It allows to save power and speed up performances. Moreover, they allow for bio-inspired learning algorithms implementation, such as the one currently recognized by the neuroscience community as at the basis of brain functioning, i.e. STDP.

Spiking Neural Networks convert the input stimulus into a train of Poisson spikes, with frequency directly proportional to input intensity, e.g. in the case of image recognition, pixel brightness is converted with direct proportionality into spiking trains of certain frequency. Nodes of the SNN are then Integrate&Fire (I&F) neurons, which receive input in form of current and accumulate it until a pre-defined threshold

is reached. When the threshold is reached, the I&F neuron emits an output spike that is forwarded in the network.

The state-of-the-art I&F neuron was developed in 2009 by Indiveri et al. with analogue VLSI technology embedding 21 metal-oxide-semiconductor field effect transistors (MOSFET) working in the subthreshold domain and capacitors, [41, 42]. Its schematics is reported in figure 1.4.

Fig. 1.4 Schematics of Integrate and Fire Neuron.