Doctoral Dissertation Doctoral Program in Electronic Engineering (30<sup>th</sup>cycle)

# High Performance Computing via High Level Synthesis Xilinx FPGA

By

## Mehdi Roozmeh

\*\*\*\*\*

#### Supervisor(s):

Prof. Luciano Lavagno

#### **Doctoral Examination Committee:**

Prof. Roberto Passerone, Referee, University of TrentoProf. Davide Quaglia, Referee, University of VeronaProf. E.F, University of...Prof. G.H, University of...Prof. I.J, University of...

Politecnico di Torino 2018

## Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Mehdi Roozmeh 2018

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my loving parents

## Acknowledgements

First of all I appreciate the given opportunity to study and educate in Politecnico di Torino, during my PhD course in the Department of Electronics and Telecommunications (DET) I met great and outstanding people which is impossible to name all, but I offer my sincerest gratitude to all who helped me to complete my study and find my future path.

Secondly, I would like to express my sincere gratitude to my advisor Prof. Luciano Lavagno for the continuous support of my Ph.D study and related research, for his patience, motivation, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my PhD study.

Last but not least, my love goes to my parents and sister for the inspiration I draw from them during my life.

Mehdi Roozmeh 2018, Torino

#### Abstract

As more and more powerful integrated circuits are appearing on the market, more and more applications, with very different requirements and workloads, are making use of the available computing power. This thesis is in particular devoted to High-Performance Computing applications, where those trends are carried to the extreme. In this domain, the primary aspects to be taken into consideration are (1) performance (by definition) and (2) energy consumption (since operational costs dominate over procurement costs). These requirements can be satisfied more easily by deploying heterogeneous platforms, which include CPUs, GPUs and FPGAs to provide a broad range of performance and energy-per-operation choices. In particular, as we will see, FPGAs clearly dominate both CPUs and GPUs in terms of energy, and can provide comparable performance.

An important aspect of this trend is of course design technology, because these applications were traditionally programmed in high-level languages, while FPGAs required low-level RTL design. The OpenCL(Open Computing Language) developed by the Khronos group enables developers to program CPU, GPU and recently FPGAs using functionally portable (but sadly not performance portable) source code which creates new possibilities and challenges both for research and industry <sup>1</sup>.

FPGAs have been always used for mid-size designs and ASIC prototyping thanks to their energy efficient and flexible hardware architecture, but their usage requires hardware design knowledge and laborious design cycles. Several approaches are developed and deployed to address this issue and shorten the gap between software and hardware in FPGA design flow, in order to enable FPGAs to capture a larger portion of the hardware acceleration market in datacenters. Moreover, FPGAs usage in data-centers is growing already, regardless of and in addition to their use as

<sup>&</sup>lt;sup>1</sup>Both Intel and Xilinx provide software development kit(SDK) to support high level synthesis using the OpenCL programming language

computational accelerators, because they can be used as high performance, low power and secure switches inside data-centers.

High-Level Synthesis (HLS) is the methodology that enables designers to map their applications on FPGAs (and ASICs). It synthesizes parallel hardware from a model originally written C-based programming languages .e.g. C/C++, SystemC and OpenCL. Design space exploration of the variety of implementations that can be obtained from this C model is possible through wide range of optimization techniques and directives, e.g. to pipeline loops and partition memories into multiple banks, which guide RTL generation toward application dependent hardware and benefit designers from flexible parallel architecture of FPGAs.

Model Based Design (MBD) is a high-level and visual process used to generate implementations that solve mathematical problems through a verified set of IP-blocks. MBD enables developers with different expertise, e.g. control theory, embedded software development, and hardware design to share a common design framework and contribute to a shared design using the same tool. Simulink, developed by Matlab, is a model based design tool for simulation and development of complex dynamical systems. Moreover, Simulink embedded code generators can produce verified C/C++ and HDL code from the graphical model. This code can be used to program micro-controllers and FPGAs. This PhD thesis work presents a study using automatic code generator of Simulink to target Xilinx FPGAs using both HDL and C/C++ code to demonstrate capabilities and challenges of high-level synthesis process. To do so, firstly, digital signal processing unit of a real-time radar application is developed using Simulink blocks. Secondly, generated C based model was used for high level synthesis process and finally the implementation cost of HLS is compared to traditional HDL synthesis using Xilinx tool chain.

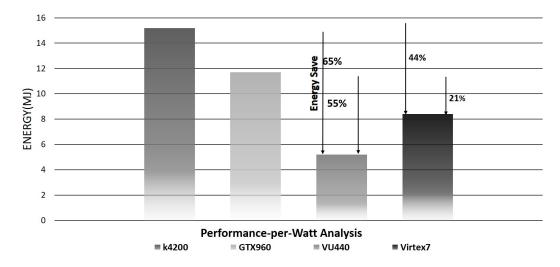

Alternative to model based design approach, this work also presents an analysis on FPGA programming via high-level synthesis techniques for computationally intensive algorithms and demonstrates the importance of HLS by comparing performance-per-watt of GPUs(NVIDIA) and FPGAs(Xilinx) manufactured in the same node running standard OpenCL benchmarks. We conclude that generation of high quality RTL from OpenCL model requires stronger hardware background with respect to the MBD approach, however, the availability of a fast and broad design space exploration ability and portability of the OpenCL code, e.g. to CPUs and GPUs, motivates FPGA industry leaders to provide users with OpenCL software development environment which promises FPGA programming in CPU/GPU-like fashion. Our experiments, through extensive design space exploration(DSE), suggest that FPGAs have higher performance-per-watt with respect to two high-end GPUs manufactured in the same technology(28 nm). Moreover, FPGAs with more available resources and using a more modern process (20 nm) can outperform the tested GPUs while consuming much less power at the cost of more expensive devices.

## Contents

| Li | List of Figures x |                                             |    |  |

|----|-------------------|---------------------------------------------|----|--|

| Li | st of [           | Tables xi                                   | ii |  |

| 1  | FPG               | GA - Field Programmable Gate Arrays         | 1  |  |

|    | 1.1               | An example of a modern FPGA-based platform  | 4  |  |

|    | 1.2               | FPGA Architecture                           | 6  |  |

|    |                   | 1.2.1 Configurable Logic Blocks             | 6  |  |

|    |                   | 1.2.2 DSP Slice                             | 8  |  |

|    |                   | 1.2.3 Memory Resources                      | 9  |  |

|    | 1.3               | HDL - Hardware Description Languages        | 3  |  |

|    | 1.4               | Contributions and Motivations:              | 5  |  |

| 2  | HLS               | S - High Level Synthesis                    | .7 |  |

|    | 2.1               | State Of The Art                            | 7  |  |

|    | 2.2               | High Level Synthesis and Model Based Design | 3  |  |

|    | 2.3               | High Level Synthesis and OpenCL Model       | 6  |  |

|    | 2.4               | Xilinx SDAccel Development Environment      | 8  |  |

|    |                   | 2.4.1 Concepts of Application Host Code     | 0  |  |

|    |                   | 2.4.2 Static Region                         | 0  |  |

|    |                   | 2.4.3 Programmable Region                   | 81 |  |

|   |                            | 2.4.4                                                                      | Off-chip to On-chip Interface Optimization                                 | 33                                                                                             |

|---|----------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   |                            | 2.4.5                                                                      | On-chip optimization                                                       | 40                                                                                             |

|   | 2.5                        | Design                                                                     | Space Exploration and HLS                                                  | 45                                                                                             |

|   |                            | 2.5.1                                                                      | DSE of Multi-Core RTL via OpenCL Synthesis                                 | 46                                                                                             |

| 3 | HPO                        | C - High                                                                   | Performance Computing                                                      | 53                                                                                             |

|   | 3.1                        | Platfor                                                                    | m and Underlying Hardware                                                  | 53                                                                                             |

|   |                            | 3.1.1                                                                      | GPU                                                                        | 54                                                                                             |

|   |                            | 3.1.2                                                                      | High Bandwidth Memory(HBM):                                                | 61                                                                                             |

|   |                            | 3.1.3                                                                      | FPGA                                                                       | 63                                                                                             |

|   | 3.2                        | Applic                                                                     | ations                                                                     | 63                                                                                             |

|   |                            | 3.2.1                                                                      | Join Operation                                                             | 63                                                                                             |

|   |                            | 3.2.2                                                                      | Frequency Modulated Continuous Wave (FMCW) Radar                           | 72                                                                                             |

|   |                            |                                                                            |                                                                            |                                                                                                |

| 4 | -                          |                                                                            | ntion and Performance-per-Watt Analysis of HPC Applica<br>GA-GPU Platforms | -<br>79                                                                                        |

| 4 | -                          | s on FP                                                                    |                                                                            | 79                                                                                             |

| 4 | tion                       | s on FP<br>FFT-ba<br>Impler                                                | GA-GPU Platforms<br>ased Digital Signal Processing Unit of Radar           | <b>79</b><br>80                                                                                |

| 4 | <b>tion</b><br>4.1         | s on FP<br>FFT-ba<br>Impler                                                | GA-GPU Platforms ased Digital Signal Processing Unit of Radar              | <b>79</b><br>80<br>85                                                                          |

| 4 | <b>tion</b><br>4.1         | s on FP<br>FFT-ba<br>Impler<br>tion or                                     | GA-GPU Platforms<br>ased Digital Signal Processing Unit of Radar           | <b>79</b><br>80<br>85<br>86                                                                    |

| 4 | <b>tion</b><br>4.1         | s on FP<br>FFT-ba<br>Impler<br>tion on<br>4.2.1                            | GA-GPU Platforms<br>ased Digital Signal Processing Unit of Radar           | <b>79</b><br>80<br>85<br>86                                                                    |

| 4 | <b>tion</b><br>4.1         | s on FP<br>FFT-ba<br>Impler<br>tion on<br>4.2.1<br>4.2.2                   | GA-GPU Platforms<br>ased Digital Signal Processing Unit of Radar           | <b>79</b><br>80<br>85<br>86<br>90                                                              |

| 4 | <b>tion</b><br>4.1<br>4.2  | s on FP<br>FFT-ba<br>Impler<br>tion on<br>4.2.1<br>4.2.2<br>4.2.3          | GA-GPU Platforms<br>ased Digital Signal Processing Unit of Radar           | <b>79</b><br>80<br>85<br>86<br>90<br>93                                                        |

| 5 | tions<br>4.1<br>4.2<br>Con | s on FP<br>FFT-ba<br>Impler<br>tion on<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | GA-GPU Platforms<br>ased Digital Signal Processing Unit of Radar           | <ul> <li>79</li> <li>80</li> <li>85</li> <li>86</li> <li>90</li> <li>93</li> <li>97</li> </ul> |

# **List of Figures**

| 1.1  | 28 nm Xilinx Virtex7 FPGA                                      | l |

|------|----------------------------------------------------------------|---|

| 1.2  | Major share holders of FPGA market                             | 2 |

| 1.3  | U.S. FPGA Market by application                                | 2 |

| 1.4  | Asian Pacific FPGA Market by application                       | 3 |

| 1.5  | Top view of data center                                        | ł |

| 1.6  | Xilinx Ultrascale+ Platform Schem                              | 5 |

| 1.7  | Top View of FPGA fabric architecture                           | 7 |

| 1.8  | Slice of CLB                                                   | 3 |

| 1.9  | Slice of DSP                                                   | ) |

| 1.10 | True Dual-Port Data Flows for a RAMB3 10                       | ) |

| 1.11 | Comparison of 7 Series FPGA                                    | 1 |

| 1.12 | STRATIX® 10 FPGAs developed by Intel                           | 2 |

| 1.13 | Graphical Presentation of full adder in different HDL level 14 | ł |

| 2.1  | High level synthesis flow                                      | 3 |

| 2.2  | Scheduling and Binding                                         | ) |

| 2.3  | Control Extraction and IO port Sequencing                      | 2 |

| 2.4  | OpenCL platform and memory model                               | 5 |

| 2.5  | SDAccel CPU/GPU-Like development environment                   | 3 |

| 2.6  | Programmable Device Block Diagram                              | ) |

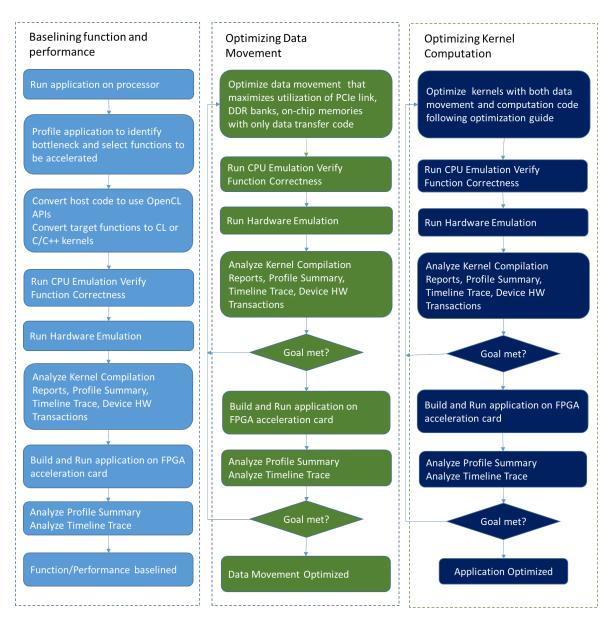

| Block Diagram of Example Xilinx SDAccel Platform                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                           | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                           | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

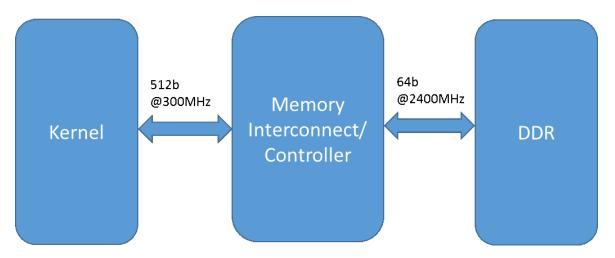

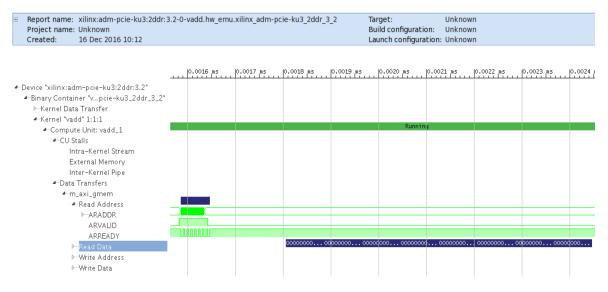

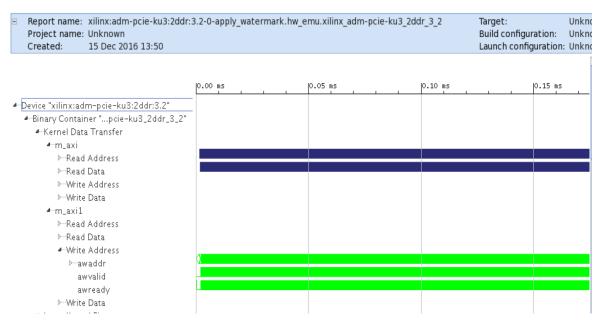

| Device-Hardware-Transaction Timing Diagram                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

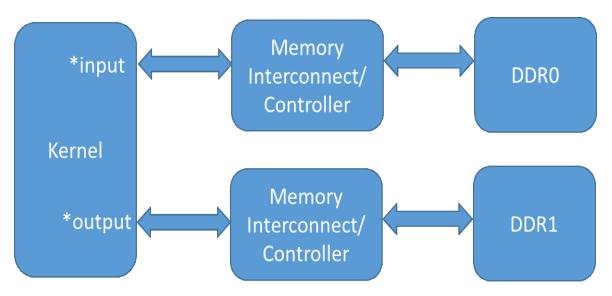

| Off-chip Memory With Two Separaeted Banks                                 | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Device Hardware Transaction                                               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

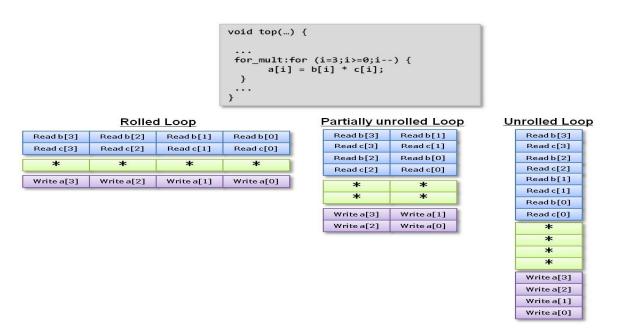

| Loop Unrolling                                                            | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

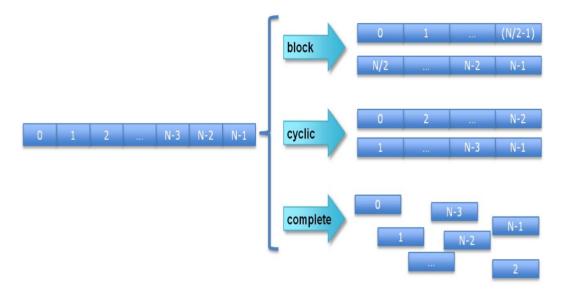

| Array Partitioning                                                        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

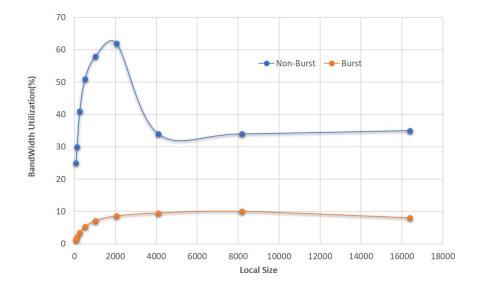

| Off-Chip bandwidth utilization vs on-chip memory size                     | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

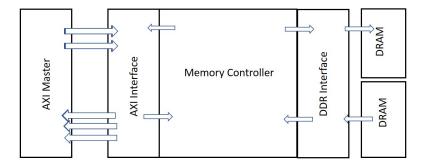

| AXI memory controller diagram                                             | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Design Space Exploration Flow of Multi Kernel OpenCL Models               | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

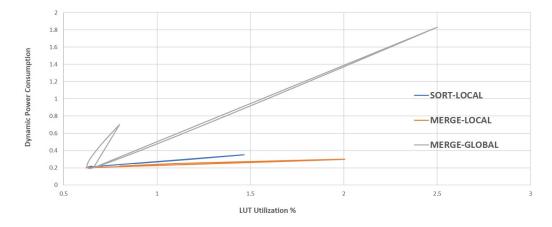

| Dynamic power consumption versus LUT utilization                          | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

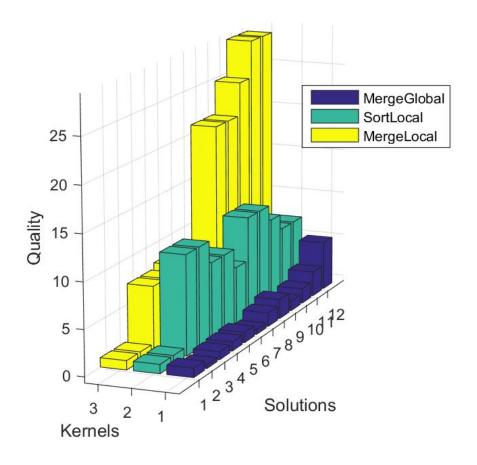

| Quality of generated RTL by SDAccel for three kernels used in the sorting |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| network                                                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

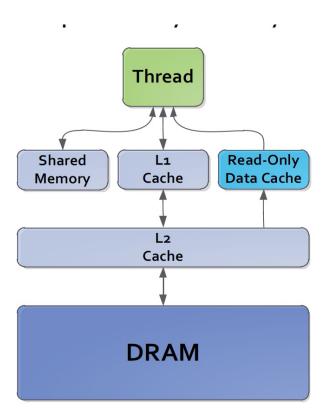

| Streaming Multi Processor of Kepler architecture                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Kepler Memory Hierarchy                                                   | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Streaming Maxwell's Multiprocessors                                       | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

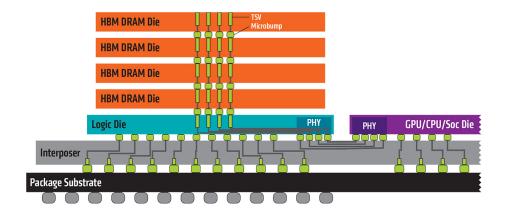

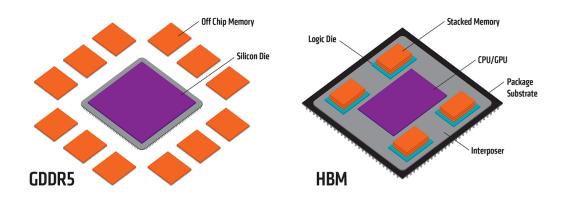

| Stack of Memory Chips                                                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| НВМ                                                                       | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

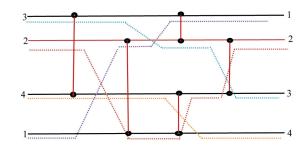

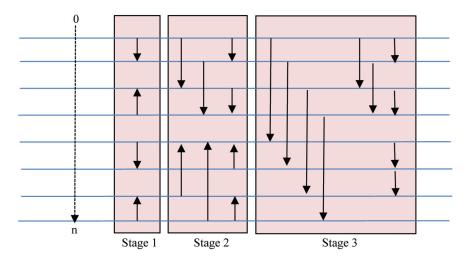

| Illustration of a simple sorting network                                  | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bitonic sort network with 8 inputs (N=8). It operates in 3 stages, it     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| has a depth of 6 (steps) and employs 24 comparators                       | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

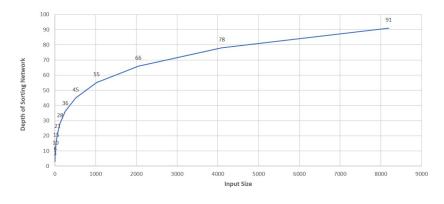

| Depth of Sorting network : $D(N) = \frac{log_2 N.(log_2 N+1)}{2}$         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

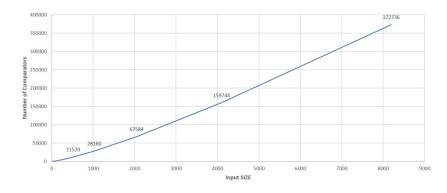

| Number of Comparators : $C(N) = \frac{N.log_2N.(log_2N+1)}{4}$            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

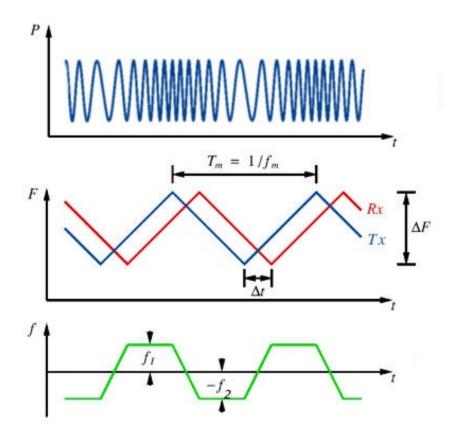

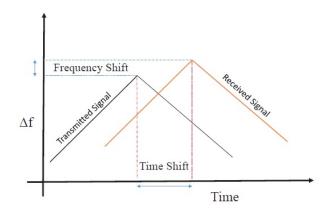

| FMCW radar signal analysis                                                | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

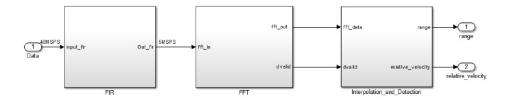

| Simulink Top model of FMCW                                                | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                           | Device Hardware TransactionLoop UnrollingArray PartitioningOff-Chip bandwidth utilization vs on-chip memory sizeAXI memory controller diagramDesign Space Exploration Flow of Multi Kernel OpenCL ModelsDynamic power consumption versus LUT utilizationQuality of generated RTL by SDAccel for three kernels used in the sorting<br>networkStreaming Multi Processor of Kepler architectureKepler Memory HierarchyStreaming Maxwell's MultiprocessorsStack of Memory ChipsHBMIllustration of a simple sorting networkBitonic sort network with 8 inputs (N=8). It operates in 3 stages, it<br>has a depth of 6 (steps) and employs 24 comparators.Depth of Sorting network : $D(N) = \frac{log_2N.(log_2N+1)}{2}$ Number of Comparators : $C(N) = \frac{N.log_2N.(log_2N+1)}{4}$ FMCW radar signal analysis |

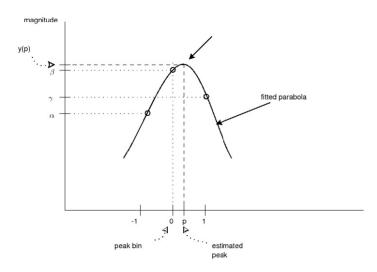

| 3.12 | Estimation improvement by Interpolation                                             | 73 |

|------|-------------------------------------------------------------------------------------|----|

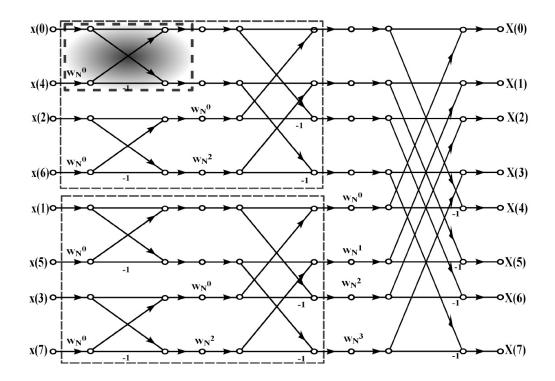

| 3.13 | Signal flow graph for radix-2, 8-point in place FFT computations                    | 75 |

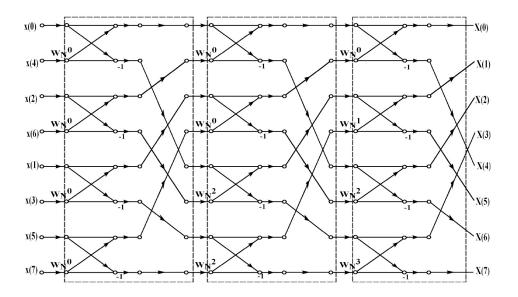

| 3.14 | Signal flow graph for radix-2, 8-point FFT computations                             | 77 |

| 4.1  | Operation of FMCW Doppler Radar                                                     | 80 |

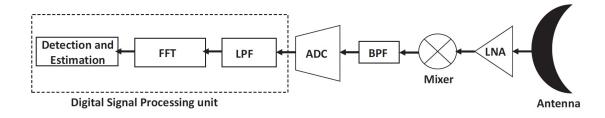

| 4.2  | FMCW Radar receiver architecture                                                    | 81 |

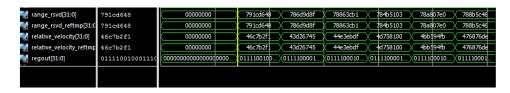

| 4.3  | RTL simulation of FMCW model generated in ISE Simulator (ISim)                      | 82 |

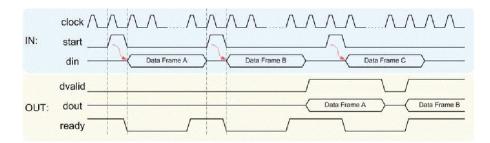

| 4.4  | Timing diagram of streaming Simulink FFT from HDL library                           | 82 |

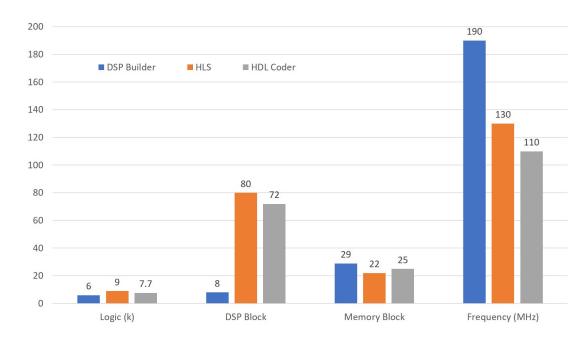

| 4.5  | Comparison of synthesis result of streaming FFT IP using three different approaches | 83 |

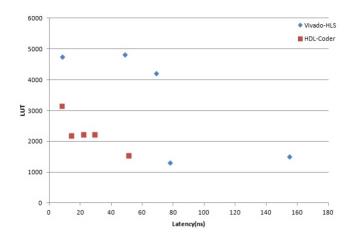

| 4.6  | HDL and C based design space exploration of FIR subsystem (LUT Utilization)         | 84 |

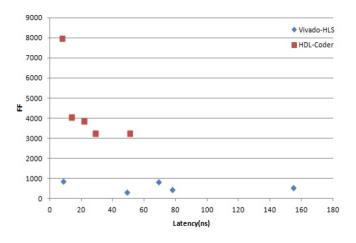

| 4.7  | HDL and C based design space exploration of FIR subsystem (FF Utilization)          | 84 |

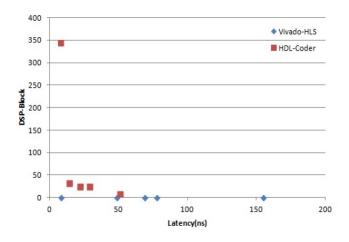

| 4.8  | HDL and C based design space exploration of FIR subsystem (DSP Utilization)         | 85 |

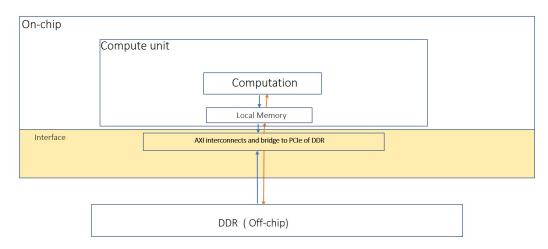

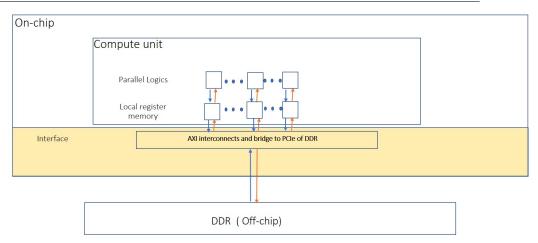

| 4.9  | Memory model of single compute unit                                                 | 87 |

| 4.10 | Fine-grained memory model of compute unit                                           | 88 |

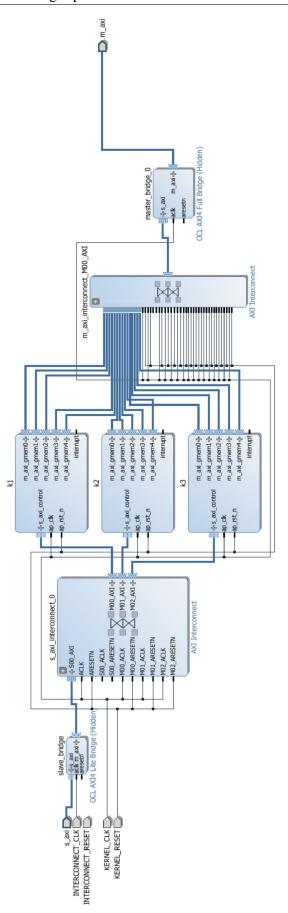

| 4.11 | Top-level block diagram with 3 OpenCl kernel instances, generated by SDAccel.       | 89 |

| 4.12 | Output of nvidia-smi dmon command line                                              | 91 |

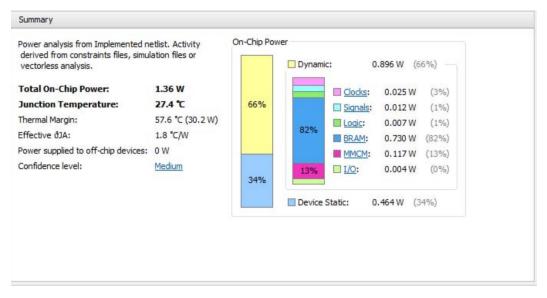

| 4.13 | Vivado Power Analysis                                                               | 92 |

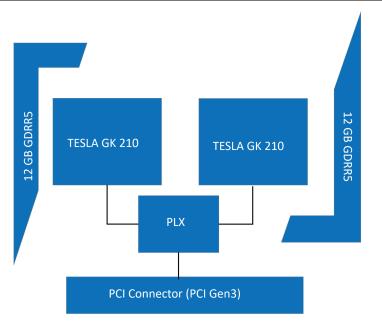

| 4.14 | Tesla K80 Block Diagram                                                             | 94 |

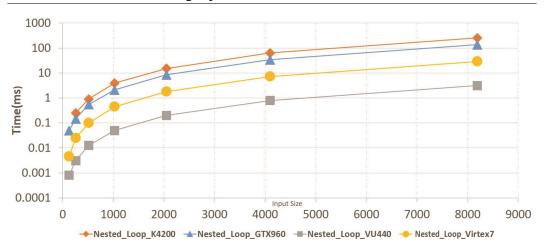

| 4.15 | Performance comparison of nested-loop join versus data size                         | 95 |

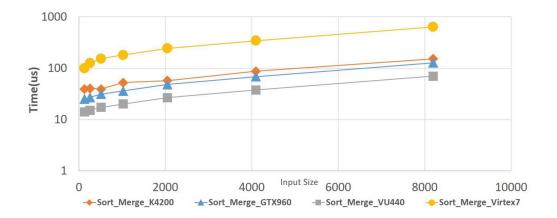

| 4.16 | Performance comparison of sort-merge join versus data size                          | 95 |

| 4.17 | Performance-per-watt compassion of FPGA vs GPU                                      | 97 |

## **List of Tables**

| 1.1 | 7 Series FPGA Family comparison                                    | 10 |

|-----|--------------------------------------------------------------------|----|

| 2.1 | Loop Level Optimizations                                           | 40 |

| 2.2 | Array Optimization                                                 | 40 |

| 2.3 | SDAccel off-chip to on-chip transfer analysis                      | 47 |

| 3.1 | Release sequence of NVIDIA GPUs micro-architecture                 | 54 |

| 3.2 | NVIDIA GPUs L1, L2 and register file size(Sizes are in KB)         | 58 |

| 3.3 | Comparison of Kepler and Maxwell architecture                      | 59 |

| 3.4 | Comparison of GDDR5 and HBM                                        | 62 |

| 3.5 | Computation Accuracy of FMCW RADAR                                 | 74 |

| 3.6 | Specification of Modeled FMCW Radar with FFT of 2048               | 74 |

| 4.1 | FFT Implementation for Radar DSP Unit HLS-IP vs. HDL Coder .       | 81 |

| 4.2 | Comparison of implementation cost for different radar blocks using |    |

|     | HLS                                                                | 81 |

| 4.3 | Full Radar DSP Unit Implementation HLS vs. HDL Coder               | 81 |

| 4.4 | Specification of tested Platforms                                  | 93 |

| 4.5 | Performance and energy analysis of Nested_Loop Join                | 96 |

| 4.6 | Performance and energy analysis of Sort_Merge Join                 | 96 |

## Chapter 1

# FPGA - Field Programmable Gate Arrays

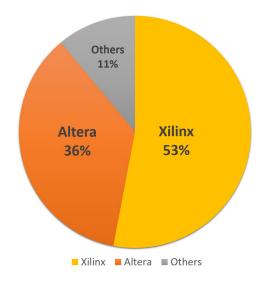

Field programmable arrays(FPGA) consists of arrays of gates that can be programmed and reconfigured by a designer. Hardware description languages (VHDL/Verilog) are widely used to model a design in a bit and cycle accurate way and map them to FPGA via various available synthesis tools to generate functionally verified bit-stream in an automated flow[1, 2]. Although, multiple companies share FPGA's market, but Intel(after acquisition of Altera in 2016) and Xilinx are two major competitors. Even though Intel cannot be underestimated especially when it comes to their technology and capital, this work focuses on Xilinx tools and technology. Xilinx is the market leaders of FPGAs with 18-months technology lead. Its products are aimed to meet requirements of various workloads coming from different domains[3, 4], figure 1.2 suggests that more than 50% of FPGA market belongs to Xilinx programmable platforms.

Figure 1.1 28 nm Xilinx Virtex7 FPGA

Figure 1.2 Major share holders of FPGA market

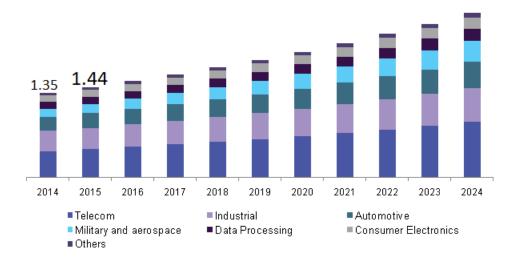

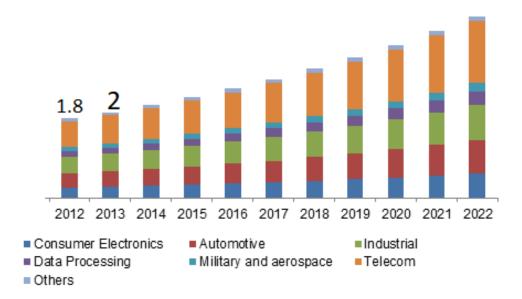

As technology world is shifting toward a huge ramp driven by 5G communication, Artificial intelligence(AI) and Internet of Things(IoT), the demand of high performance computing and efficient-energy solutions are growing and this makes FPGA more suitable to be used as the core of embedded electronic systems. However, complexity of FPGA is growing day by day, but FPGAs development environment improvement in recent years made developers to consider them as a cost optimized and high performance devices, Figures 1.3 and 1.4 demonstrate increasing growth of FPGA deployment in USA and Asian pacific markets, overall annual market value of FPGA is estimated around 7 billion USD by the end of 2022 [5–7].

Figure 1.3 U.S. FPGA Market by application, 2014-2024(USD Bilion)

Figure 1.4 Asian Pacific FPGA Market by application, 2014-2024 (USD Bilion)

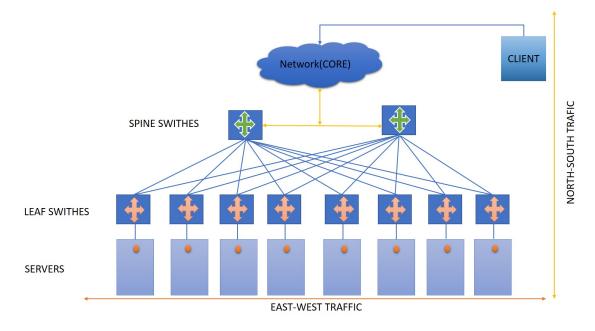

Moreover, previously most of the traffics in the INTERNET were between client and data-centers which is known as north-south traffic in data-center terminology, nowadays, 80 percent of the total traffic belongs to east-west traffic which is the internal communications within a data-center [8], figure 1.5 shows top view of data center architecture. This fact increases FPGA deployment in data centers mainly because of the FPGAs flexibility that can be configured as high-performance switches inside data centers structures without outside standards concern coming from client side[9].

Figure 1.5 Top view of Data center

In the rest of this chapter, FPGAs are discussed both from hardware and software perspective which are fundamentals to understand and perform successful software and hardware co-design targeting FPGAs.

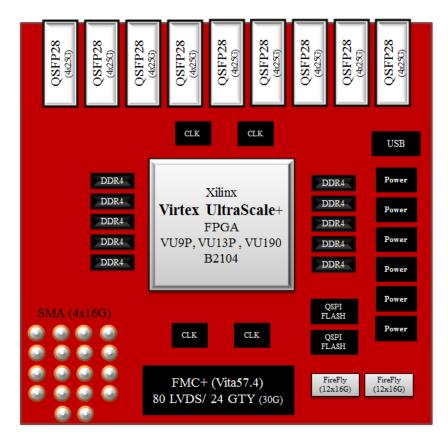

### **1.1** An example of a modern FPGA-based platform

FPGAs, like any other integrated circuit, are mounted on boards (and often racks of boards) to create a complete electronic system. To give an idea of the power and possibilities of modern FPGA-based platforms, we will consider a very recent example board, shown in figure 1.6. HTG-9200 from HiTech Global is powered by the latest generation Xilinx Virtex Ultrascale+(16nm) FPGA. This modern platform is suitable, for example, for high performance optical networking applications since it has nine QSFP28<sup>1</sup> ports and two separate DDR4 high-performance DRAM banks(using a total of 10 memory chips).

<sup>&</sup>lt;sup>1</sup>Quad Small Form-Factor Pluggable is a high-performance and low-power Ethernet connectivity solution for data center and high performance computing. These transceivers come in various types supporting 40 G and 100 G Ethernet.

The HTG9200 is considerably more powerful than most FPGA boards that are deployed today. However, it is a clear example of an ongoing trend to replace ASICs with FPGAs for any application domain that require the latest technologies, but cannot afford to design an ASIC due to the Non-Recurrent Engineering cost. Design costs for the 14 nm technology node are estimated by various industry sources to be around 300M\$ per design, and mask costs are most likely comparable. This means that several million integrated cicuits must be sold to recover the NRE costs. For this reason, and due to the ability to upgrade the hardware in situ, FPGAs are becoming the preferred platform for a growing number of applications, ranging from automotive (ADAS in particular), to telecom, military, aerospace, and recently even data centers. In the latter case, FPGAs are not competing with ASICs but with GPUs, and can offer comparable performance at a fraction of the energy-per computation cost, as we will show later in this thesis.

As we discussed, a key motivation of FPGAs is to keep design costs low. This is achieved first and foremost by reducing the verification costs dramatically, since their reprogrammability ensures that there is no need to get the first implementation completely bug-free. Designs can be reloaded at will, and debugging on the FPGA itself is much easier than on an ASIC.

Moreover, recent design technology advances, in particular High-Level Synthesis, have enabled a dramatic paradigm shift in terms of how FPGAs (and ASICs) are designed. As we will demonstrate in this thesis, HLS tools enable the designer to achieve high-quality implementations in a fraction of the time required by traditional HDL-based methodologies working at the Register Transfer level. The Quality of Results of RTL can even be surpassed by HLS-based solutions, thanks to the broader design space (e.g. the tradeoffs between pipelining and resource consumption, or the exploration of memory architectures) that is afforded by HLS. This motivates us to conduct an extensive research on different FPGA programming approaches and report our experiment results in this dissertation.

Figure 1.6 Xilinx Ultrascale+ Platform Scheme

## **1.2 FPGA Architecture**

FPGAs are capable to serve as an accelerator for the wide range of applications ,moreover, new technologies shape and develop FPGA platforms day by day to meet customer and market needs. Modern FPGAs consist of millions of logic cells and switches which are programmable. This chapter studies the key components of FPGA chip and provide the numerical report of available resources for each component in 7 series Xilinx FPGAs(28 nm).

#### **1.2.1** Configurable Logic Blocks

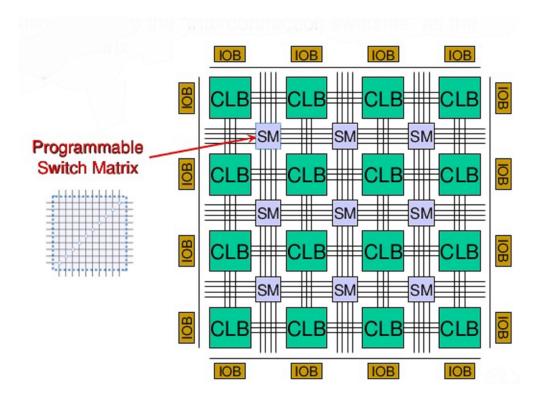

Figure 1.7 presents top view of FPGA fabric composed of arrays of configurable logic blocks(CLB) and switches.

Figure 1.7 Top View of FPGA fabric architecture

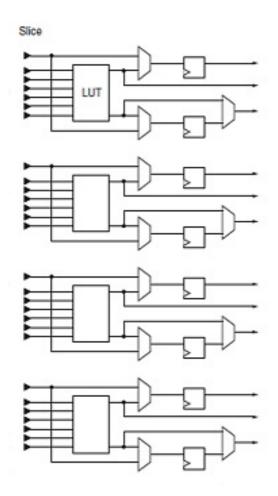

CLBs are the key component in Xilinx FPGAs and each has pair of slices, figure 1.8 shows simplified graphical presentation of one slice with 6-input look-up tables(LUT), fast adders and registers. Logical,arithmetic,memory and shift register functions can be implemented using these slices [10].

Figure 1.8 Slice of CLB

### 1.2.2 DSP Slice

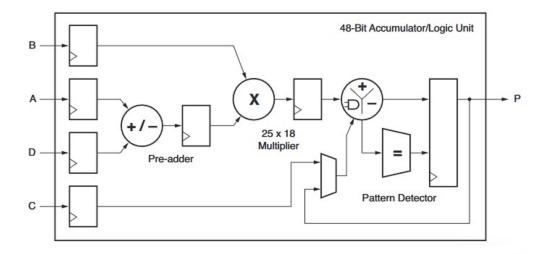

Xilinx FPGAs provide slices of DSP that are designed to implement vast number of binary multipliers and adders used in DSP applications. Figure 1.9 provides insight to DSP slice architecture used in 7series Xilinx FPGAs, implementation of DSP algorithms using DSP slices enhance speed and efficiency of FPGA device within a small size and flexible hardware [11].

Figure 1.9 Slice of DSP

#### 1.2.3 Memory Resources

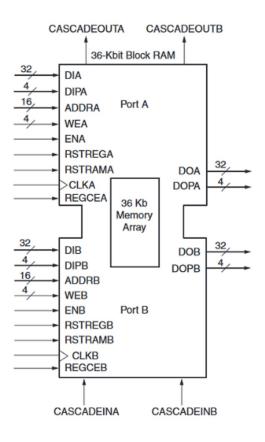

Available on-chip memory is essential for high performance computing, however, LUTs in FPGAs can be used as distributed RAM across FPGA device, but dedicated blocks of RAM in FPGAs are the main resource of on-chip memory (fig 1.10). Dual 36 Kb block RAM can be configured as a 64K x 1 (when cascaded with an adjacent 36 Kb block RAM),32K x 1, 16K x 2, 8K x 4, 4K x 9, 2K x 18, 1K x 36, or 512 x 72 in simple dual-port mode [12].

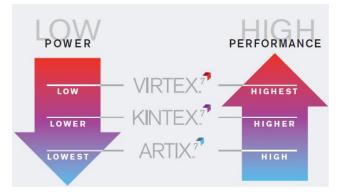

In order to address performance and power requirement of different applications, Xilinx FPGAs are divided into three main families, table1.1 reports available resources for each family member, however, they have similar architecture, but performance and power metrics of each device is different mainly because of available resource and external memory band-width.

| MAXIMUM CAPABILITY | ARTIX      | KINTEX    | VIRTEX    |

|--------------------|------------|-----------|-----------|

| LOGIC CELLS        | 215K       | 478K      | 1,955K    |

| BLOCK RAM          | 13 Mb      | 34 Mb     | 68 Mb     |

| DSP SLICES         | 740        | 1,920     | 3,600     |

| MEMORY INTERFACE   | 1,066 Mbps | 1,866 Mbs | 1866 Mbps |

Table 1.1 7 Series FPGA Family comparison

Figure 1.10 True Dual-Port Data Flows for a RAMB36

Figure 1.11 draws a comparison between three family members of Xilinx, each can be deployed based on application requirements. VIRTEX with maximum number of logic cells is designed for high performance applications, while ARTIX provides users with low power devices, moreover, KINTEX devices are manufactured to offer best performance-per-cost FPGAs to designers.

Figure 1.11 Comparison of 7 Series FPGA

#### **INTEL FPGA Devices**

However, Xilinx FPGAs are dominant in programmable logic market, but Altera FPGAs are also powerful devices with multiple classes that can offer costumers various performance, power and cost solutions to addressee different applications requirements. Additionally, reports in [13] suggest higher core performance of Intel FPGAs with respect to Xilinx UltraScale devices manufactured in 20 nm technology using ten different test bench targeting Intel and FPGA devices. Following lines briefly introduce five different FPGA classes produced by Intel which are currently closest competitor to Xilinx and may gain larger portion of FPGA market thanks to Intel investment and support[14].

#### **STRATIX®**

The Stratix® Series of FPGAs and SoC FPGAs are designed for the most demanding systems where performance is paramount. Stratix 10, figure 1.12, is the flagship of Intel configurable device. Manufactured on Intel 14 nm Tri-Gate technology, Stratix 10 will offer industry-leading capacity, performance, and architectural innovation for the most challenging computing, signal-processing, and software-defined networking applications.

Figure 1.12 STRATIX® 10 FPGAs developed by Intel

#### Arria®

The Arria® Series of FPGAs and SoC FPGAs deliver a **balance of performance and power efficiency**. Arria 10 FPGAs and SoC FPGAs are the latest product within the Arria family. Arria 10 at 20 nm has a unique combination of speed, DSP performance, capacity and power efficiency, and are the only **20 nm** FPGA to integrate an embedded processor system.

#### MAX®

The MAX® Series of programmable logic devices features a **non-volatile** architecture and offers a **low cost and low power configurable logics**. MAX devices are widely used for **general-purpose and power-sensitive** designs in a wide variety of market segments to perform functions that include **I/O expansion, interface bridging, power management, and FPGA configuration control**.

#### **Cyclone**®

The Cyclone® Series of FPGAs and SoC FPGAs are optimized for **low-cost**, **high-volume systems**. Cyclone V deliver capacity, performance, and IP ideal for the majority of embedded applications used in the **industrial and automotive markets**.

#### **Enpirion**®

The Enpirion® product line offers the industry's **most compact, energy-efficient, and sophisticated DC-DC converters** for meeting the power requirements of FP-GAs. When power rails demand programmable **on/off, fast transient response and extra-low noise** devices they are the winner candidate.

#### **1.3 HDL - Hardware Description Languages**

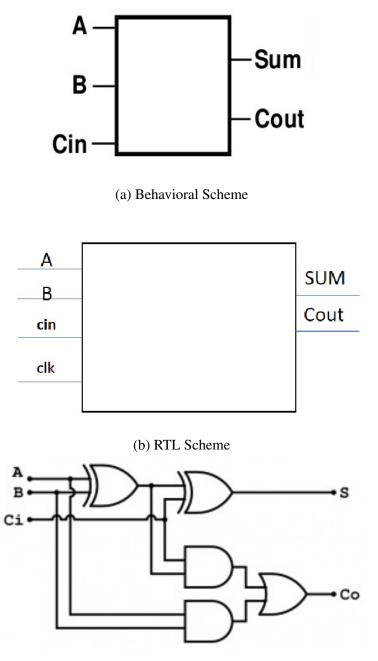

Hardware Description Language(HDL) is used to model digital electronic system, in other words, any digital electronic component such as registers, memories and switches can be modeled in HDL. VHDL/Verilog are common HDL languages in industry which support designing at three main levels of abstraction, although, designing digital electronic circuits can be done both using top-down and bottom-up approach, but the latter method is almost obsolete because of modern digital circuit complexity. Three different levels of HDL are shown in figure1.13 and described below.

- Behavioral Level: enable hardware designers to model whole algorithm starting from top level, each block consists of sequential function and tasks with defined inputs and outputs. In this level designers are focused on behavior and performance of the algorithm and only when behavioral level is verified, designers can develop underlying digital circuits of algorithm using register transfer level abstraction.

- Register-Transfer Level (RTL): In this level designers can model digital circuits at resister level using cycle accurate timing. Technically, RTL code can be used by synthesis tools in order to generate gate-level model from algorithm.

- Gate Level: The lowest level of abstraction is gate level which can be used to implement digital algorithm on silicon after placement and routing stage which can be done automatically by modern synthesis tools.

(c) Gate Level Presentation

Figure 1.13 Graphical Presentation of full adder in different HDL level

### **1.4 Contributions and Motivations:**

The rest of this dissertation presents a study on the high-level synthesis (HLS) methodology for high performance computing applications (HPC) using two different approaches. To do so, firstly, this work discusses high-level synthesis, Model Based Design (MBD) and parallel computing that helps to provide the necessary background for analyzing the conducted experiments in this work. The main motivation behind this study relies on the importance of high performance and low power hardware to address the ever-growing demand for energy efficient platforms. Hence, the experiments are designed to examine Xilinx high-level synthesis tool chain in an analytical manner using various type of C based model (e.g. C, SystemC and OpenCL) for DSP and data base applications.

As the first stage of this PhD course, Simulink is used to develop a real-time application of digital signal processing unit of frequency modulated continuous wave (FMCW) radar. The top level model is used to generate functionality verified C and HDL based model in customizable fashion. Thereupon, the Xilinx synthesis tool chain is used to map automatic generated codes on FPGAs. Although, the results suggest that C based FPGA programming consumes less resources for performing the same amount of computation, performance hungry part of the DSP algorithm is substituted with SystemC IP that can be integrated within Simulink environment and be used to realize parallel RTL. The results of this study are discussed in more detail in chapters three, four and [15].

The growing trend towards heterogeneous platforms is crucial to meet time and power consumption constraints for high-performance computing applications. The OpenCL parallel programming language and framework enable programming CPU, GPU and recently FPGAs using the same source code. This eases software developers to implement applications on various devices supported by heterogeneous HPC platforms. This work presents two very different FPGA implementations of a database join operation, one using a direct O(n2) algorithm, and the other using a bitonic sort network to speed up the join operation. Comparison of performance and energy consumption for both FPGA and GPUs is provided which suggests an average of 40% performance-per-watt improvement by using an FPGA instead of a GPU. Extensive analysis and discussions related to these experiments are presented in chapters two, three and [16, 17] Even though, MBD offers faster development cycle with respect to code based model due to early stage verification and coarse-grained subsystem integration, the available design space is much larger in latter case thanks to low level exposure capabilities. This leads the quest for the best implementation towards design space exploration (DSE) analysis of OpenCL models. The proposed DSE technique, discussed in the next chapter and demonstrated in the chapter four, offers careful design space exploration by considering on-chip and off-chip sources of parallelism. Additionally, power estimation based on the area utilization enables exploration of design space at a faster pace.

## Chapter 2

## **HLS - High Level Synthesis**

Technically speaking, High Level Synthesis(HLS) is automated flow which transforms C based model algorithm to register transfer level (RTL) that can be used to program FPGAs. Current Xilinx HLS tools chain supports C/C++, systemC and OpenCL as source code and generates high quality RTL based on design constraints and optimization directives provided by a designer [18, 19].

### 2.1 State Of The Art

Design complexity of electronic devices is growing day by day and manufacturing optimized hardware requires strong technology and knowledge to address the need of wide range of computational intensive workloads such as artificial intelligence(AI) and digital signal processing applications. Companies like Intel and NVIDIA manufacture parallel fixed-architecture GPUs which can be programmed by software developers using parallel programming languages such as OpenCL and CUDA. Moreover, the growing trend toward hybrid platform is crucial to meet time and power constraints of ever-evolving high performance computing applications.

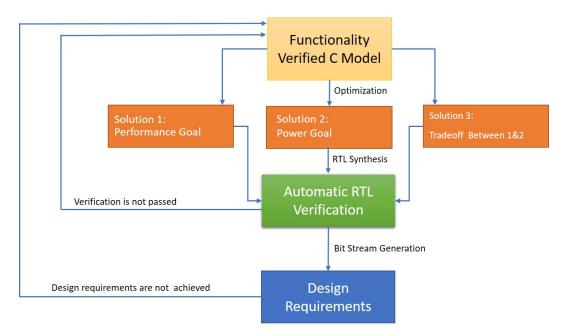

Recent studies suggest that FPGAs have performance and power consumption advantage over GPUs thanks to technology advancement in FPGA manufacturing and development environment improvement which shortened the gap between hardware and software layer[20, 17]. Algorithms can be developed and verified at system level within the same frame work as CPU/GPU, this automated flow and FPGAs inherent reconfigurable parallel architecture result in high performance and low power hardware which can be tuned and adopted according to design constraints during design cycles (figure 2.1).

Figure 2.1 High level synthesis flow

High level synthesis enables designers with minimum hardware experience to program modern FPGAs through sophisticated tool chain that supports application development for FPGA starting from pure software level. Next section covers high level synthesis principles and optimization techniques which are used in this work to generate desirable RTL micro-architecture from higher abstraction layer. **High Level Synthesis Principles:**

In this part of the thesis techniques and terminologies of Xilinx tool chain are explained using user manual and optimization instructions. The codes and figures are derived from Xilinx documentation which are prepared to introduce their product in a most advantageous form. However, each section refer to related document, it would be helpful to mention that the information of the rest of this section are obtained from [21–25].

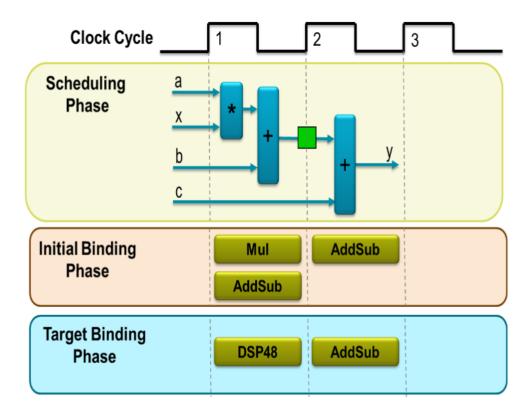

Scheduling and binding are the processes at the heart of high level synthesis. The code below is used to explain theses process [24].

```

int foo(char x, char a, char b, char c) {

char y;

y = x*a+b+c;

return y

}

```

**Scheduling:** Scheduling is the process that HLS decides in which clock cycle operations should occur. This depends on the clock frequency, timing information of the target FPGA, and any additional optimization directives.

**Binding:** In this stage of high level synthesis, the tool determines which hardware resources implement each scheduled operation.

The scheduling phase section of figure 2.2 depicts this step. The multiplication and the first addition are performed in the first clock cycle. The next clock cycle executes the second addition. The green square in this figure indicates when an on-chip memory is written. The maximum number of scheduled operation in one clock cycle depends upon the clock period and the operation execution time. Faster FPGA can complete all above computations in one clock cycle, conversely, slower FPGAs may take more clock cycles.

Figure 2.2 Scheduling and Binding

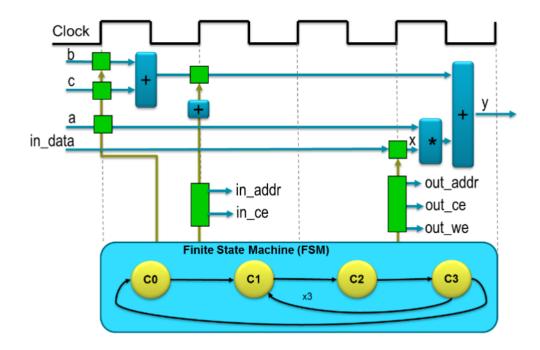

Specific information about FPGA target device is needed to decide which resource is the most optimized solution for each implementation. Multiplication and addition can be implemented by DSP48 resource which is the high performance and power-efficient unit in FPGA architecture [24]. Final step of high level synthesis is extraction and implementation of control logic and I/O ports. The simple C code below is used to clarify this process with more details. Generated RTL by HLS runs the logics inside the loop three times, high level synthesis tools produces a Finite State Machine (FSM) in the hardware design to complete these operations.

```

void foo(int in[3], char a, char b, char c, int out[3]) {

int x,y;

for(int i = 0; i < 3; i++) {

x = in[i];

y = a*x + b + c;

out[i] = y;

}

}</pre>

```

Figure 2.3 illustrates final scheduled design and generated FSM by HLS which is described below in more details.

- The C0 is the first state of FSM which is followed by C1, C2 and C3. The full sequence of states are :C0,{C1, C2, C3},{C1,C2,C3},{C1,C2,C3}, C0.

- The variables only once require the addition of the *b* and *c*. This operation pulls outside the (for-)loop and performed in the state *C0*. Each time the design enters state *C3* it reuses the operation result.

- The data for *in* is returned from the block-RAM in state *C*2 and stored as variable *x*.

- The data from port *a* is read with other values to perform the calculation. The first *y* output is generated and the FSM ensures that the correct address and control signals are generated to store this value outside the block.

- The design then returns to state *C1* to read the next value from the array/block-RAM *in*.

- This process continues until all output is written.

• The design then returns to state *C0* to read the next values of *b* and *c* to start the process all over again.

Figure 2.3 Control Extraction and IO port Sequencing

### 2.2 High Level Synthesis and Model Based Design

Model Based Design environments (MBDEs), such as Simulink, are becoming more widespread as they expand their capabilities of synthesizing efficient hardware and software from high-level algorithmic models. They find applications in very important areas such as digital signal processing (DSP), telecommunications, and control systems. MBDEs allow modeling of complex algorithms and systems at a very abstract level, using pre-defined primitive micro and macro blocks (e.g. adders, multipliers, multiplexers, FIR filters, FFTs). The designer can thus focus on defining the best algorithm without caring for tedious low level implementation details. Such details can be introduced later in the design flow via automated model-to-model translation, including both direct mapping and sophisticated hardware and software synthesis algorithms, or through a user-directed refinement process.

One of the major advantages of MBD tools is that they let the designer verify and validate abstract golden models against their design specifications. The designer can then use these models to generate code targeting either a specific embedded processor for software implementation, or a register transfer level (RTL) description for hardware synthesis. The process of generating software code or the RTL hardware description is normally assisted by the designer by providing constraints and directives. Algorithmic design provides a much better scope for power, area and performance optimizations as compared to what can be achieved at lower levels. MBD also greatly eases the verification task by allowing one to re-use already verified macro blocks and more importantly by letting the designer use the same verified golden reference model throughout the complete design, verification and implementation flow.

State of the art MBD tools used in the industry can generate very efficient and optimized software code for different target processors, by using information about the target processor architecture. But hardware implementation essentially entails the generation of a cycle accurate RTL model from very abstract block level models that have no notion of clock cycles. Hence the set of choices is much broader, and the normal direct translation strategy used for software implementation is likely to fail. Current MBD tools, such as Simulink from the Mathworks, can generate a very limited set of hardware implementations starting from a given model. In other words, they have limited capabilities to explore the hardware design space starting from a single model, due to reasons that are described more with detail in the next sections.

This is particularly true in the case of complex blocks like a Fast Fourier Transform (FFT), a Discrete Cosine Transform (DCT) or a Viterbi decoder, which are normally represented as Simulink macro blocks.

Simulink models can be also translated to RTL description for hardware synthesis through a tool called HDL Coder. Efficient hardware implementation starting from an abstract model generally requires effective design space exploration (DSE) from a single model. HDL Coder, however, has limited capabilities in this regard, especially when it comes to complex algorithms like FFT, DCT, and Viterbi decoders. Each HDL coder block is mapped to a few micro-architectures, e.g. fully sequential and fully pipelined, which provide only a few design points, such as minimum area or maximum throughput. Many of the architectural trade-offs that are essential for optimized hardware implementation, such as independent definition or throughput and latency, or the choice of memory parallelism and architecture, may even need to be performed manually, by changing the source model every time. This changing of model defies one of the main purposes of model-based design, by requiring different models for different implementations, and hence making the design process long and tedious.

Simulink has a rich library of components that can be used to model systems and algorithms from many different domains. In Simulink libraries, the components are arranged in groups known as blocksets, for example the DSP-blockset that can be used to model DSP algorithms. Simulink libraries are extensible through a mechanism known as S-functions. It provides a component modeling paradigm in which the functionality (algorithm) as well as the interaction with other components can be represented in a well-defined way. The S-functions can be written in C, FORTRAN, or MATLAB, as required.

Simulink comes integrated with a tool called Real Time Workshop (RTW). RTW is a set of code generators known as target language compilers (TLC) that can translate a Simulink model to C/C++. Each TLC can be optimized to generate code for a different processor or platform. Embedded Real Time (ERT) coder is one of these TLCs, which is optimized to generate software code for embedded applications. It can generate floating and fixed point code. **Part of this work presents a study on high level synthesis and the legacy code generated by RTW and HDL coder which can be divided into three main sections:**

- 1. Modeling and validation of digital signal processing unit of specific type of RADAR used in automotive industry via Simulink which will be described in chapter 3.

- 2. Generation of SystemC-based FFT IP with fully pipelined stages to be substituted with Simulink C model. The data flow and analysis of FFT algorithms are explained in chapter3.

- 3. Comparison of high level and RTL synthesis using HDL and C-based Simulink IPs is reported in chapter 4.

Alternative to model based design approach, in the next section, new programming framework is discussed that can target heterogeneous platforms equipped with CPU, GPU and FPGA devices. OpenCL(Open Computing Language) is supported by industry leaders to program various hardware accelerators within the same framework using close-to metal optimization options.

# 2.3 High Level Synthesis and OpenCL Model

The OpenCL Programming model has been developed by the Khronos group to overcome the hurdles of programming multi-core and heterogeneous compute platforms. OpenCL enables programmers to develop both close-to-the metal and portable software. Although, OpenCL is a high-level programming language, it provides a low-level abstraction layer that can expose significant architectural aspects of the target hardware, such as massive parallelism and the memory hierarchy. The CPU/GPU based platforms generally have a fixed architecture. While this makes programming easier and compilation times much faster, it is also a limitation because it reduces both the energy efficiency and the on-chip ("local" in OpenCL terms) memory access bandwidth with respect to an FPGA.

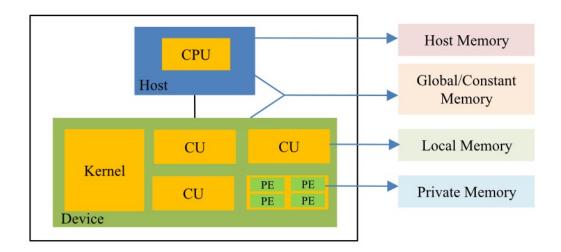

Figure 2.4 OpenCL platform and memory model

An OpenCL device consists of compute units (CU), each further divided into processing elements (PE) as shown in Fig 2.4. Several concurrent executions of the kernel body (called work-items) take place on multiple processing elements. The work-items are further grouped into work-groups, which are being executed by compute units. The memory is broadly divided into host (i.e. CPU) memory and device (i.e. GPU or FPGA) memory. The device memory is further divided into private memory (specific to each work-item), local mem- ory (shared by all the work-items in a work-group) and a global/constant memory (shared by all the work-groups). Access to global memory is the slowest (since it typically resides in external

DRAM) while private memory is the fastest (since it is typically allocated to register files), while local memory often resides in on-chip SRAM. Global memory however, is the largest in size while private memory is the smallest. The OpenCL memory model is also shown in figure 2.4. The work-items that compose an OpenCL kernel can be executed in an out-of order manner, in order to ensure high performance on a variety of platforms with different numbers of CUs [26]. Thus, the OpenCL standard uses a three-level synchronization and collaboration model. The execution order of different kernels is completely determined by the host code, either by calling them sequentially, or by using synchronization callbacks that notify the host code when a given kernel has completed execution. The execution of different work-groups within a kernel is completely unsynchronized, thus they must read and write different areas of global memory, and they cannot cooperate in any manner. Finally, the programmer can use explicit barriers to ensure local and global memory consistency for work-items within a work-group.A barrier represents a checkpoint within a workgroup. All the work-items belonging to that work-group must reach it before any of them can proceed beyond it.

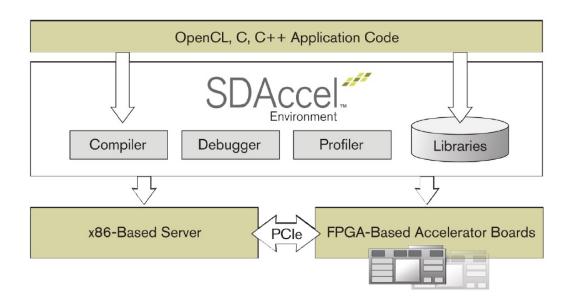

# 2.4 Xilinx SDAccel Development Environment

The new Xilinx SDAccel<sup>TM</sup> Development Environment provides high performance application developers the dedicated FPGA-based hardware and software tool chain. SDAccel offers a fast, micro and macro architecture optimized compiler that makes efficient use of on-chip FPGA resources; a well-known software-development flow with an Eclipse<sup>TM</sup>-based Integrated Design Environment (IDE) for software development, profiling, and verification, which provides a CPU/GPU-like work environment; and dynamic reconfigurable accelerators optimized for different high performance applications that can be swapped in and out on the fly for a CPU/GPU-like run-time environment[22, 27].

Figure 2.5 SDAccel CPU/GPU-Like development environment

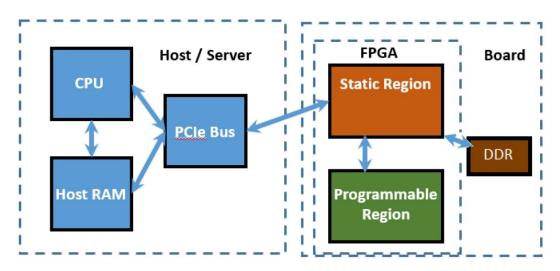

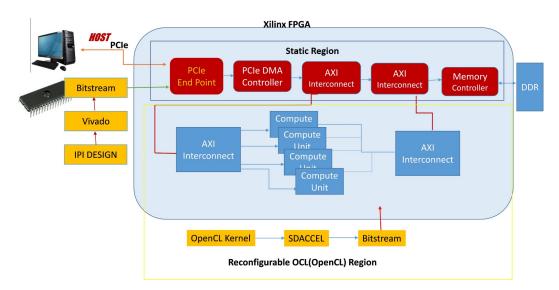

OpenCL defines hierarchical memory model that is common between all vendors and can be applied to all OpenCL applications. Global, local and private memories are the main layers of this hierarchy. SDAccel maps them to the FPGA platform as external DRAMs, BRAMs, and register. SDAccel allows even finer-grained exploitation of the on-chip memory architecture of FPGAs by using directives such as on-chip global memory, multiple AXI buses for kernel global arrays, and partitioned local arrays, which enable a designer to finetune the memory architecture and adapt the RTL architecture to the application, rather than the application to the GPU architecture[16].

The Xilinx® SDAccel OpenCL boards are PCIe® based accelerator cards that plug into a standard PCIe slot in x86\_64 host or server type architectures.