## POLITECNICO DI TORINO Repository ISTITUZIONALE

#### An Analytical Approach for the Design of Class-E Resonant DC-DC Converters

#### Original

An Analytical Approach for the Design of Class-E Resonant DC-DC Converters / Bertoni, Nicola; Frattini, Giovanni; Massolini Roberto, G.; Pareschi, Fabio; Rovatti, Riccardo; Setti, Gianluca. - In: IEEE TRANSACTIONS ON POWER ELECTRONICS. - ISSN 0885-8993. - STAMPA. - 31:11(2016), pp. 7701-7713. [10.1109/TPEL.2016.2535387]

Availability:

This version is available at: 11583/2696621 since: 2020-02-05T22:26:37Z

Publisher:

Institute of Electrical and Electronics Engineers Inc.

Published

DOI:10.1109/TPEL.2016.2535387

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# An Analytical Approach for the Design of Class-E Resonant DC-DC Converters

Nicola Bertoni, *Student Member, IEEE*, Giovanni Frattini, Roberto G. Massolini, Fabio Pareschi, *Member, IEEE*, Riccardo Rovatti, *Fellow, IEEE*, and Gianluca Setti, *Fellow, IEEE*

Abstract—We present a new approach to design resonant dcdc converters, that allows to achieve both a more accurate implementation and a simpler architecture, by reducing the number of required passive components. The approach is applied to a class-E topology, and it is based on the analytic solution of the system of differential equations regulating the converter evolution. Our technique is also capable of taking into account the most important circuit non-idealities. This represents an important breakthrough with respect to the state-of-the-art, where class-E circuit analysis is based on strong simplifying assumptions, and the final circuit design is achieved by means of numerical simulations after many time-consuming parametric sweeps. The developed methodology is dimensionless, and the achieved design curves can be de-normalized to easily get the desired circuit design. Measurements on two different prototypes confirm an extremely high adherence to the developed mathematical approach.

Index Terms—Resonant dc-dc converters, Class-E converters.

#### I. Introduction

NE of the most important recent trends in the design of dc-dc switching power converters is the increase in their operating frequency, which has nowadays reached the VHF range (30-300 MHz) [1]–[4]. There are, in fact, several advantages connected to a very high switching frequency. Two of them are noteworthy: first, better transient performance and bandwidth can be achieved; second, constraints on the values of passive reactive elements are relaxed and, in general, smaller and less expensive components are required. This allows to increase the converter power density and supports the ultimate goal of adopting air-core magnetic components small enough to be embedded into a fully integrated solution.

Unfortunately, the design of a VHF switching power converter poses several challenges. In particular, the main issue is the converter efficiency, since switching losses are increasing with the switching frequency [1]. To solve the impasse, resonant class-E dc-dc converters were introduced [5], [6], exploiting the so-called *soft switching* technique.

Manuscript received Mmmm dd, yyyy; revised Mmmm dd, yyyy.

N. Bertoni, F. Pareschi and G. Setti are with the Department of Engineering, University of Ferrara, 44122 Ferrara, Italy. F. Pareschi and G. Setti are also with the Advanced Research Center on Electronic Systems, University of Bologna, 40125 Bologna, Italy (e-mail: nicola.bertoni@unife.it; fabio.pareschi@unife.it; gianluca.setti@unife.it).

R. Rovatti is with the Department of Electrical, Electronic, and Information Engineering, University of Bologna, 40136 Bologna, Italy, and also with the Advanced Research Center on Electronic Systems, University of Bologna, 40125 Bologna, Italy (e-mail: riccardo.rovatti@unibo.it).

G. Frattini and R. Massolini are with Texas Instruments Italia, 20089 Rozzano, Italy (e-mail: giovanni.frattini@ti.com; roberto.massolini@ti.com).

Roughly speaking, they embed a resonant circuit that shapes the voltage across the semiconductor switching device in such a way that it naturally reaches zero immediately before the instant in which the switch is turned on [7], allowing current to start flowing. Additionally, it is possible to impose that the voltage goes to zero smoothly, *i.e.*, with zero time derivative.

These two conditions are known respectively as zero voltage switching (ZVS) and zero voltage derivative switching (ZVDS), and satisfying them produces a reduction of the voltage-current product of the switching device at turn on instants, lowering (ideally, down to zero) the energy-loss-per-cycle, with beneficial effects also in terms of electromagnetic interference (EMI) mitigation and stress reduction on switching devices.

While the classical procedure for resonant converter design relies on heavy simplifying assumptions, here we propose a novel approach where the exact dynamics of the system is taken into consideration. By solving the system of ordinary differential equations (ODE) regulating the converter behavior, and by considering the converter operating at steady state condition as in [8]–[10], we develop a mathematical framework which makes possible a fast and accurate circuit design.

In addition to the obvious advantage of achieving a less approximate design without resorting to circuit-level simulations, the ability of considering non-simplified dynamics allows to eliminate circuit elements, such as bulky RF choke inductors, high-Q filters or tuned matching network conventionally introduced to justify model simplifications. This has a tremendous impact on circuit size and complexity and allows us to apply our approach to an extremely lightweight class-E architecture that can be configured either as an isolated or non-isolated topology.

Some preliminary results, limited to the case of ideal circuit components, were reported in [11], where we presented an initial study of the ODE-based approach. A first dc-dc converter prototype has been designed and described in [12]. Here, with respect to [11], [12], we present three additional steps:

- we include the most important circuit non-idealities and parasitic elements in the model. This allows us to obtain an almost perfect match between the expected circuit behavior and the actual measurements, and to make this procedure extremely useful for circuit designers;

- we introduce a suitable normalization that makes the circuit design independent of the values of voltages, currents and switching frequency. We also provide general design curves that allow any designer to immediately solve the

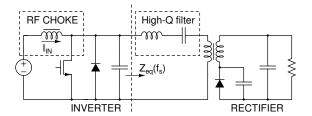

Fig. 1. Classical isolated class-E dc-dc converter design taken from [13], where we highlighted the RF choke inductor and the LC high-Q filter connecting the inverter and the rectifier stages.

converter design problem by simply de-normalizing the general solution;

we validate the improved methodology by implementing two new circuit prototypes. The almost perfect match between theoretical and measured waveforms in both circuits confirm the validity of the design tool and opens new optimization possibilities in class E dc-dc converter design.

The paper is organized as follows. Section II reviews the state-of-the-art design methodology of class-E dc-dc converters and introduces the resonant topology considered in this paper. In Section III we develop the framework for the exact circuit analysis. Then, in Section IV our design approach is explained, and used for achieving general design curves in Section V. The implementation of the two prototypes is presented in Section VI and, finally, we draw the conclusion.

#### II. CLASS-E DC-DC CONVERTERS

Class-E dc-dc converters were first introduced in the early 80s to take advantage of the radio frequency (RF) design techniques in high-frequency dc-dc power conversion, aiming to move from the common single power source scenario to low power, small size, distributed power modules [5], [6], [13]. The key point was to increase efficiency at high speed of operation by moving from rectangular pulse waveforms to sinusoidal-like ones.

#### A. Conventional class-E converter design approach

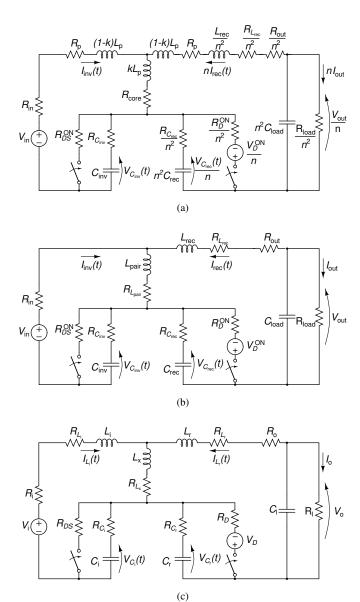

All class-E dc-dc converter topologies are based on two fundamental building blocks, a class-E inverter [7], [14] and a rectifying stage [15]–[18], usually connected together by means of an LC filter that acts as impedance matching network. A very common topology used for isolated converters is represented in Fig. 1 (taken from [13]).

The inverter stage is basically a class-E amplifier working at frequency  $f_s$ , and loaded with a non-resistive network designed to properly shape the voltage across the transistor and achieve optimal operation, *i.e.*, ZVS and (possibly) ZVDS conditions. More specifically, the inverter design is achieved by assuming the equivalent input impedance  $Z_{eq}(f_s)$  of the rectifier as load. The resonant rectifier (*i.e.*, a rectifier properly connected with reactive elements) makes the final ac/dc conversion. Its design is achieved by approximating the input voltage as a sinusoidal tone at the converter working frequency  $f_s$ . To ensure both the aforementioned assumptions,

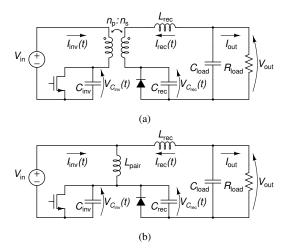

Fig. 2. Schematic of the considered converter. (a): isolated topology; (b): non-isolated topology.

allowing the actual circuit behavior to match the approximated one, the inverter and rectifier are connected by means of a high-Q LC filter, ensuring both an impedance matching (from the inverter point of view) and harmonics filtering (from the rectifier point of view). A large RF choke inductor is also commonly employed to ensure that the simplifying assumption of a constant current power source is actually satisfied.

In this way, the whole converter design can be readily obtained taking advantage of well-known RF techniques [13].

In recent years, research efforts have been focused on the investigation of different inverter and rectifier topologies [19]–[24] to increase efficiency or reduce device stress. As an example, the  $\phi_2$  converter [19] was introduced to decrease the peak level of the MOS switch drain-source voltage. A few contributions also tried a mathematical formalization of the converter analysis aiming to reduce the circuit complexity by removing unnecessary reactive elements such as the RF choke inductor [25]. However, the achieved accuracy is always limited by the aforementioned sinusoidal approximation, that makes necessary the presence of the LC filter, and causes appreciable differences between the theoretical circuit evolution and the actual one. Consequently, a simulation-based tuning of circuit parameters is needed to identify the optimal operating point.

#### B. Proposed circuit description

The schematic of the circuit we consider is shown in its isolated and non-isolated configuration in Fig. 2(a) and 2(b), respectively. In both cases, we indicate the input voltage with  $V_{\rm in}$ , the output voltage with  $V_{\rm out}$ , and we assume a resistive load  $R_{\rm load}$ , with load current given by  $I_{\rm out} = V_{\rm out}/R_{\rm load}$ . Like any class-E dc-dc converter, the circuit can be separated into an inverter and a rectifying stage, connected together either by a coupling transformer or by a pairing inductance  $L_{\rm pair}$ .

Note that the two schematics of Fig. 2 represent only the "core" of a class-E dc-dc converter. Actually, two sub-circuits required to obtain the complete scheme used in practice are not considered.

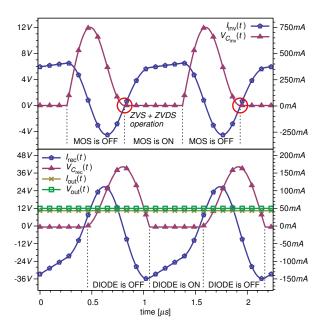

Fig. 3. Example of current and voltage signals waveforms for the inverter, featuring ZVS and ZVDS (top plot), and for the rectifier (bottom plot) in an isolated converter topology example.

The first one is a gate driver circuit for the MOS switch. With respect to this, it is worth noticing that in practical cases the most common approach is to embed a self-resonant gate driver circuit with the aim of improving energy efficiency [26]. In this paper, to maintain focus on the main contribution, we decided to simply assume that the oscillation frequency is regulated by an external clock generator, which turns ON and OFF the MOS switch at frequency  $f_s$  with duty-cycle D.

The second sub-circuit is the load regulator. In class-E dcdc converters, ZVS and ZVDS are achieved only for a specific optimal operating point, i.e., for a given  $R_{load}$  or equivalently a given output power. To preserve ZVS and ZVDS with a variable load, an on-off control [25], [27] is typically employed. Without entering into details, this approach allows the converter only to be in an off state (where the output voltage is maintained constant by  $C_{load}$ ) or to work in the optimal operating point. Under this assumption, the converter design is achieved considering the maximum output power, i.e., the minimum  $R_{\rm load}$ , and the ratio between the actual output power and the maximum one is set by the ON/OFF ratio. Again, to maintain our paper focused on its main contribution and simplifying the presentation as much as possible, in this paper we do not consider the on-off control, and we design the circuit according to the maximum output deliverable power.

An example of the typical circuit waveforms of the dcdc converter of Fig. 2(a), designed accordingly to the proposed methodology, can be observed in the SPICE simulation waveforms of Fig 3. The picture includes the voltage  $V_{C_{\rm inv}}(t)$  and the current  $I_{\rm inv}(t)$  at the inverter side, and the voltage  $V_{C_{\rm rec}}(t)$  and the current  $I_{\rm rec}(t)$  at the rectifier side. The (almost constant due to  $C_{\rm load}$ ) output voltage  $V_{\rm out}$  and output current  $I_{\rm out}$  are also shown; note that, accordingly to the schematic of Fig. 2, and considering a zero average current flowing through the output capacitor in steady-state condition,  $I_{\rm out}$  can be

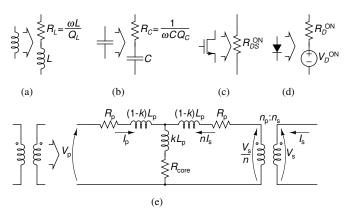

Fig. 4. Equivalent circuits used to model real devices. (a): inductors; (b): capacitors; (c): MOS switch (ON state); (d): diode (ON state); (e): transformer. MOS switch and diode in the OFF state are modeled as open circuits.

expressed as a function of the mean value of  $I_{rec}(t)$  as:

$$I_{\text{out}} = -\langle I_{\text{rec}}(t) \rangle$$

(1)

It is worth stressing that the desired ZVS and ZVDS operation conditions have been perfectly ensured, as  $V_{C_{\mathrm{inv}}}(t)$  smoothly crosses the zero level at the MOS turn-ON instant.

#### III. ODE-BASED CIRCUIT ANALYSIS

#### A. Non-idealities modeling

To develop an accurate mathematical model for the dc-dc converters of Fig. 2, for every device (with the exception of  $C_{\rm load}$ ) we consider a very simple equivalent circuit that includes non-idealities and parasitic effects as summarized in Fig. 4.

More specifically, for inductors and capacitors we use the classical equivalent circuit for lossy reactive components operating at angular frequency  $\omega_s=2\pi f_s$  of Fig. 4(a) and 4(b) respectively. The value of the series resistances is linked to the quality factors  $Q_L$  and  $Q_C$  by

$$Q_L = \frac{\omega_s L}{R_L}, \quad Q_C = \frac{1}{\omega_s C R_C}$$

(2)

Conversely,  $C_{\rm load}$  is not part of a resonating circuit, but its role is just to limit oscillations in the output voltage  $V_{\rm out}$  as much as possible. Therefore, we will adopt in the following a common assumption for all dc-dc switching converters and replace the  $R_{\rm load}$  and  $C_{\rm load}$  network with an ideal dc voltage source  $V_{\rm out}$ .

Active devices (i.e., the MOS switch and the rectifying diode) are modeled as switches that can be either in a completely ON or OFF state. When ON, the MOS switch is replaced by a reasonably small  $R_{DS}^{\rm ON}$  resistance as shown in Fig. 4(c), and by an open circuit while OFF. When the diode is ON, we observe a forward voltage drop that has a weak dependence on the diode current. To model this effect, we replace the diode with an ideal voltage source  $V_D^{\rm ON}$  and a (small) series resistance  $R_D^{\rm ON}$  as in Fig. 4(d). When in the OFF state, we assume that the diode is equivalent to an open circuit. Note that parasitic capacitances on both the MOS switch and the diode, that may be relevant in particular in their OFF state,

Fig. 5. Equivalent schematic circuits of the converter topologies of Fig. 2, including parasitic device modeling. (a): isolated topology, referring all elements at the secondary side of the transformer to the primary side; (b): non-isolated topology; (c): schematic and notation used to analyze both topologies.

have not been explicitly modeled. In fact, for typical values of the external capacitors  $C_{\rm inv}$  and  $C_{\rm rec}$  these parasitic effects can be considered as masked or conveniently absorbed by them; this is a very common assumption in almost all class-E design approaches, and we adopted it here as well.

Finally, the transformer is modeled with the standard equivalent circuit of Fig. 4(e) [28], where all the elements are referred to the primary side and an ideal transformer with turns ratio  $n=n_{\rm s}/n_{\rm p}$  couples the secondary side. The total inductance  $L_{\rm p}$  seen at the primary side is split into a magnetizing inductance  $kL_{\rm p}$  and two leakage inductances  $(1-k)L_{\rm p}$  by means of the coupling coefficient k. The equivalent circuit also includes a resistance  $R_{\rm core}$  mainly modeling energy loss in the magnetic core, and two resistances  $R_{\rm p}$  modeling wire turns losses.

When replacing all devices of Fig. 2 with the equivalent of Fig. 4, we get the two schematics of Fig. 5(a) and Fig. 5(b). In the figure we have also included two additional resistances  $R_{\rm in}$  and  $R_{\rm out}$  to model other possible circuit losses (e.g., current sensing resistors, a non-ideal voltage source, etc.) and, in the isolated topology, we have replaced all elements at the secondary side of the transformer (i.e.,  $L_{\rm rec}$ ,  $C_{\rm rec}$ ,  $C_{\rm load}$ ,  $R_{\rm load}$ ,  $R_{\rm out}$  and the rectifying diode) with the corresponding equivalent ones at the primary side.

The differences between the circuits of Fig. 5(a) and Fig. 5(b) are very limited. Since the aim of this paper is to analyze both converter topologies, the most convenient approach is to introduce the schematic of Fig. 5(c). The notation of the new circuit is simplified with respect both to that of Fig. 5(b) and of Fig. 5(a) to allow an easier mathematical analysis, and a few elements have been removed by considering series connections. More formally, the new notation is achieved by setting

$$\begin{split} V_{\rm o} = & \begin{cases} V_{\rm out}/n \\ V_{\rm out} \end{cases}, \ C_{\rm l} = & \begin{cases} n^2 C_{\rm load} \\ C_{\rm load} \end{cases}, \ R_{\rm l} = & \begin{cases} R_{\rm load}/n^2 \\ R_{\rm load} \end{cases}, \\ I_{\rm o} = & \begin{cases} nI_{\rm out} \\ I_{\rm out} \end{cases}, \ I_{L_{\rm r}}(t) = & \begin{cases} nI_{\rm rec}(t) \\ I_{\rm rec}(t) \end{cases}, \ R_{\rm o} = & \begin{cases} R_{\rm out}/n^2 \\ R_{\rm out} \end{cases}, \\ L_{\rm r} = & \begin{cases} (1-k)L_p + L_{\rm rec}/n^2 \\ L_{\rm rec} \end{cases}, \ R_{L_{\rm r}} = & \begin{cases} R_p + R_{L_{\rm rec}}/n^2 \\ R_{L_{\rm rec}} \end{cases}, \\ V_{C_{\rm r}}(t) = & \begin{cases} V_{C_{\rm rec}}(t)/n \\ V_{C_{\rm rec}}(t) \end{cases}, \ C_{\rm r} = & \begin{cases} n^2 C_{\rm rec} \\ C_{\rm rec} \end{cases}, \ R_{C_{\rm r}} = & \begin{cases} R_{C_{\rm rec}}/n^2 \\ R_{C_{\rm rec}} \end{cases}, \\ V_{\rm D} = & \begin{cases} V_{D}^{\rm ON}/n \\ V_{D}^{\rm ON} \end{cases}, \ R_{D} = & \begin{cases} R_{D}^{\rm ON}/n^2 \\ R_{D}^{\rm ON} \end{cases}, \ L_{\rm x} = & \begin{cases} R_{\rm p} \\ L_{\rm pair} \end{cases}, \\ R_{L_{\rm x}} = & \begin{cases} R_{\rm core} \\ R_{L_{\rm pair}} \end{cases}, \ L_{\rm i} = & \begin{cases} (1-k)L_{\rm p} \\ 0 \end{cases}, \ R_{L_{\rm i}} = & \begin{cases} R_{\rm p} \\ 0 \end{cases}, \end{split}$$

where the first line refers to Fig. 5(a), and the second one to Fig. 5(b), and by defining for both cases  $V_{\rm i}=V_{\rm in},\,R_{\rm i}=R_{\rm in},\,R_{DS}=R_{DS}^{\rm ON},\,C_{\rm i}=C_{\rm inv},\,R_{C_{\rm i}}=R_{C_{\rm inv}},\,I_{L_{\rm i}}(t)=I_{\rm inv}(t)$  and  $V_{C_{\rm i}}(t)=V_{C_{\rm inv}}(t).$

#### B. Converter analysis

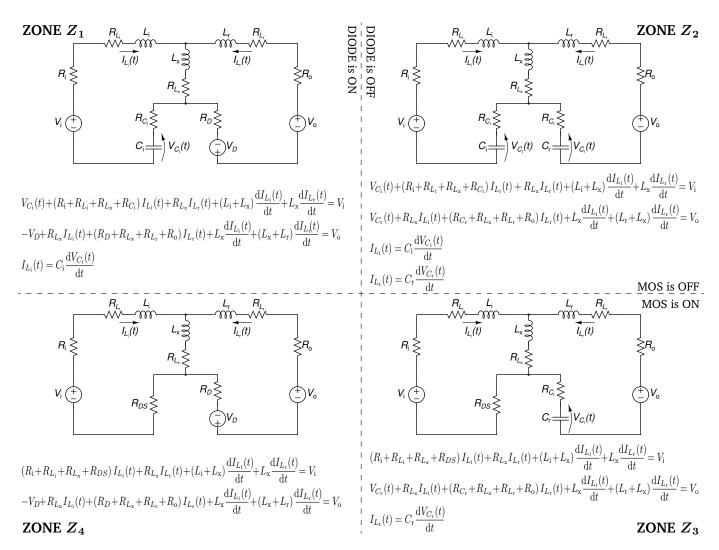

By modeling the MOS switch and the rectifying diode as devices that can be only in an ON or an OFF state, the analysis of the circuit of Fig. 5(c) can be achieved by considering separately the four different configurations determined by the possible ON/OFF combinations of the state of the two devices. We denote them as *zones*, referred to with  $Z_j$ ,  $j=1,\ldots,4$ . The schematic associated to each zone is depicted in Fig. 6.

The four circuits of Fig. 6 have been obtained as follows. The MOS switch is OFF in  $Z_1$  and  $Z_2$ , where it is modeled as an open circuit. In  $Z_3$  and  $Z_4$  it is ON and replaced by  $R_{DS}$ , that it is assumed very small. Therefore,  $V_{C_i}(t)$  is vanishing, and the current  $I_{L_i}(t)$  is all flowing through the MOS, so that  $C_i$  has almost no effect and is not considered. Conversely, the rectifying diode is OFF in  $Z_2$  and  $Z_3$  and ON in  $Z_1$  and  $Z_4$  where, since  $R_D$  is small, we have  $V_{C_r}(t) \approx -V_D$  so that  $C_r$  can be assumed to have no influence on the circuit.

Fig. 6. Equivalent circuit models used for the converter analysis according to the four different zones. In  $Z_1$  and  $Z_2$  the MOS switch is OFF, and it is not taken into account; in  $Z_3$  and  $Z_4$  the MOS is ON and it is replaced by a  $R_{DS}$  resistance, while the  $C_r$  is not considered in the equivalent circuit. The rectifying diode is OFF in  $Z_2$  and  $Z_3$  and therefore it is removed from the equivalent circuit; in  $Z_1$  and  $Z_4$  the diode is ON, and it is modeled as a voltage source  $V_D$  and a resistance  $R_D$ , while  $C_i$  is not considered. In each zone the equivalent circuit is linear and its evolution is regulated by the differential equation system written below.

As previously explained, in all four cases the load network  $R_1 - C_1$  has been replaced by a constant voltage generator  $V_0$ .

The four achieved circuits are linear, and their evolution can be obtained by solving the four associated systems of linear ODEs, whose order ranges from 2 (in  $\mathbb{Z}_4$ ) to 4 (in  $\mathbb{Z}_2$ ), and which are reported below each schematic in Fig. 6. The evolution of the whole converter can then be obtained by ensuring the continuity of the capacitance voltages and of the inductor currents when switching from one zone to another one.

To express the results of our analysis in a more compact and useful form, we need to introduce a suitable normalization for all equations of Fig. 6. Let us consider current and voltage signals normalized respectively by  $I_{\rm o}$  and  $V_{\rm o}$ , and indicate them as function of the normalized time  $\theta=\omega_s t$ , that is:

$$i_{L_i}(\theta) = \frac{I_{L_i}(\theta/\omega_s)}{I_o}, \quad i_{L_r}(\theta) = \frac{I_{L_r}(\theta/\omega_s)}{I_o},$$

$$v_{C_i}(\theta) = \frac{V_{C_i}(\theta/\omega_s)}{V_o}, \quad v_{C_r}(\theta) = \frac{V_{C_r}(\theta/\omega_s)}{V_o}$$

(3)

Observing that  $R_{\rm l}=V_{\rm o}/I_{\rm o}$ , let us also introduce the five dimensionless parameters  $q_i,\,q_r,\,q_x,\,k_i$  and  $k_r$  defined by:

$$q_{i} = \frac{1}{\omega_{s}C_{i}R_{l}}, \ q_{r} = \frac{1}{\omega_{s}C_{r}R_{l}}, \ q_{x} = \frac{\omega_{s}L_{x}}{R_{l}}$$

$$k_{i} = \frac{L_{x}}{L_{i} + L_{x}}, \ k_{r} = \frac{L_{x}}{L_{r} + L_{x}}$$

(4)

We express the equivalent series resistances for the five reactive elements  $L_{\rm i}$ ,  $L_{\rm x}$ ,  $L_{\rm r}$ ,  $C_{\rm i}$  and  $C_{\rm r}$  exploiting the definition of the quality factors  $Q_{L_{\rm i}}$ ,  $Q_{L_{\rm x}}$ ,  $Q_{L_{\rm r}}$ ,  $Q_{C_{\rm i}}$  and  $Q_{C_{\rm r}}$  as in (2). Then, let us also define

$$g_{DS} = \frac{R_{l}}{R_{DS}}, \ g_{D} = \frac{R_{l}}{R_{D}}, \ g_{i} = \frac{R_{l}}{R_{i}}, \ g_{o} = \frac{R_{l}}{R_{o}}$$

(5)

so that  $g_{DS}$ ,  $g_D$ ,  $g_i$  and  $g_o$  play the role of quality factors for, respectively, the MOS switch, the rectifying diode, and the input and output node.

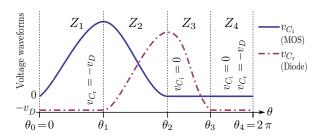

Fig. 7. Succession of zones considered in this paper.

Finally,  $\mu$  and  $v_D$  are the normalization of the input voltage and the diode forward voltage drop:

$$\mu = \frac{V_{\rm i}}{V_{\rm o}}, \ v_D = \frac{V_D}{V_{\rm o}} \tag{6}$$

The advantage of this approach is that the normalized system fully describes the circuit topology, and it is independent of the switching frequency and of the output voltage and power. Furthermore, let us introduce the two parameters  $m^{\rm ON}$  and  $d^{\rm ON}$ , with  $m^{\rm ON}=1$  ( $m^{\rm ON}=0$ ) when the MOS switch is ON (is OFF), and  $d^{\rm ON}=1$  ( $d^{\rm ON}=0$ ) when the rectifying diode is ON (is OFF). With these, the systems describing the evolution of the four zones can be written as in (7).

With this approach, the evolution of the circuit in a clock period can be easily described once the succession of zones is known. Despite a few different sequences can be observed, particularly in rather unpractical situations such as when the system is not in a steady-state condition, or when the considered quality factors of the components are extremely low, in all realistic cases the succession of zone is the one depicted in Fig. 7. For this reason, and since to consider a mathematical framework able to deal will all possible zone sequences would considerably complicate our design procedure without any real practical benefit, in the following we limit ourselves to consider this case only.

Mathematically, let us set the normalized time to  $\theta=\theta_0=0$  when the MOS switch is turned OFF while the diode is still ON. At this time instant, we can approximate  $v_{C_i}(0)=0$  and  $v_{C_r}(0)=-v_D$ , and we define  $i_{L_i}(0)=i_{L_i}^0$  and  $i_{L_r}(0)=i_{L_r}^0$ . Then,  $Z_1$  starts, followed by  $Z_2$ ,  $Z_3$  and  $Z_4$  as described in the following.

**Zone**  $Z_1$ : Let us refer to normalized currents and voltages in this zone with  $i_{L_i}^{(Z_1)}$ ,  $i_{L_r}^{(Z_1)}$ ,  $v_{C_i}^{(Z_1)}$  and  $v_{C_r}^{(Z_1)}$ . In this zone we can assume that  $v_{C_r}^{(Z_1)}(\theta) = -v_D$ , while the evolution of  $i_{L_i}^{(Z_1)}(\theta)$ ,  $i_{L_r}^{(Z_1)}(\theta)$  and  $v_{C_i}^{(Z_1)}(\theta)$  is regulated by (7) with  $m^{\rm ON}=0$  and  $d^{\rm ON}=1$ . The computation of the evolution

is reported in the Appendix; the result can be found in (A.2), and the three coefficients  $c_1$ ,  $c_2$  and  $c_3$  must be computed to satisfy the initial conditions

$$i_{L_{\rm i}}^{\,(Z_1)}(0)=i_{L_{\rm i}}^{\,\,0},\quad i_{L_{\rm r}}^{\,(Z_1)}(0)=i_{L_{\rm r}}^{\,\,0},\quad v_{C_{\rm i}}^{\,(Z_1)}(0)=0 \eqno(8)$$

The zone ends at  $\theta=\theta_1$ , that is defined as the normalized time instant in which the diode turns OFF. The value of  $\theta_1$  is computed by solving  $i_{L_{\rm r}}^{(Z_1)}(\theta_1)=0$ . **Zone Z\_2:** Here  $m^{\rm ON}=d^{\rm ON}=0$  and (7) is turned into a  $4^{\rm th}$  order system in the variables  $i_{L_{\rm i}}^{(Z_2)}(\theta),\,i_{L_{\rm r}}^{(Z_2)}(\theta),\,v_{C_{\rm i}}^{(Z_2)}(\theta)$

**Zone**  $Z_2$ : Here  $m^{\rm ON}=d^{\rm ON}=0$  and (7) is turned into a  $4^{\rm th}$  order system in the variables  $i_{L_{\rm i}}^{(Z_2)}(\theta),\,i_{L_{\rm r}}^{(Z_2)}(\theta),\,v_{C_{\rm i}}^{(Z_2)}(\theta)$  and  $v_{C_{\rm r}}^{(Z_2)}(\theta)$ , whose solution can be found in (A.4). The four coefficients  $c_1,\,c_2,\,c_3$  and  $c_4$  are computed by imposing the continuity of the current signals at  $\theta_1$

$$i_{L_{\rm i}}^{(Z_2)}(\theta_1) = i_{L_{\rm i}}^{(Z_1)}(\theta_1), \quad i_{L_{\rm r}}^{(Z_2)}(\theta_1) = i_{L_{\rm r}}^{(Z_1)}(\theta_1)$$

and by assuming

$$v_{C_{\mathbf{i}}}^{(Z_2)}(\theta_1) = v_{C_{\mathbf{i}}}^{(Z_1)}(\theta_1), \quad v_{C_{\mathbf{r}}}^{(Z_2)}(\theta_1) = -v_D$$

$Z_2$  ends at  $\theta_2=2\pi(1-D)$ , when the MOS switch is externally turned ON while the diode is still OFF. Note that, accordingly to the assumptions of Sec. II-B,  $\theta_2$  is actually a degree of freedom of the system, since D is not constrained but can be freely set.

**Zone**  $Z_3$ : Here  $m^{\rm ON}=1$  and  $d^{\rm ON}=0$ , and we can approximate  $v_{C_{\rm i}}^{(Z_3)}(\theta)=0$  independently of  $v_{C_{\rm i}}^{(Z_2)}$ , and include  $v_{C_{\rm r}}^{(Z_3)}$  in the pool of system variables along with  $i_{L_{\rm i}}^{(Z_3)}$  and  $i_{L_{\rm r}}^{(Z_3)}$ . The evolution given by (A.6), where the coefficients  $c_1$ ,  $c_2$  and  $c_3$  are given by imposing

$$i_{L_{i}}^{(Z_{3})}(\theta_{2}) = i_{L_{i}}^{(Z_{2})}(\theta_{2}), \quad i_{L_{r}}^{(Z_{3})}(\theta_{2}) = i_{L_{r}}^{(Z_{2})}(\theta_{2}),$$

$$v_{C_{r}}^{(Z_{3})}(\theta_{2}) = v_{C_{r}}^{(Z_{2})}(\theta_{2})$$

$$(9)$$

The zone  $Z_3$  ends at  $\theta_3$ , when the voltage  $v_{C_r}(\theta)$  turns negative and is able to switch the diode ON. Mathematically,  $\theta_3$  is the normalized time that solves  $v_{C_r}^{(Z_3)}(\theta_3) = -v_D$ .

**Zone**  $Z_4$ : Here both MOS switch and diode are ON, so  $m^{\rm ON}=d^{\rm ON}=1$ . We approximate  $v_{C_{\rm i}}^{(Z_4)}(\theta)=0$  and  $v_{C_{\rm r}}^{(Z_4)}(\theta)=-v_D$ , while the evolution of  $i_{L_{\rm i}}^{(Z_4)}(\theta)$  and  $i_{L_{\rm r}}^{(Z_4)}(\theta)$  is given by (A.8), where the coefficients  $c_1$ ,  $c_2$  are computed in accordance to the initial conditions

$$i_{L_{\rm i}}^{(Z_4)}(\theta_3) = i_{L_{\rm i}}^{(Z_3)}(\theta_3), \quad i_{L_{\rm r}}^{(Z_4)}(\theta_3) = i_{L_{\rm r}}^{(Z_3)}(\theta_3)$$

This zone ends at  $\theta = \theta_4 = 2\pi$ , when the MOS switch is turned OFF, and the system evolution starts again from  $Z_1$ .

$$\left(1-m^{\mathrm{ON}}\right)v_{C_{\mathrm{i}}}(\theta) + \left(\frac{1}{g_{\mathrm{i}}} + \frac{1-k_{i}}{k_{i}}\frac{q_{x}}{Q_{L_{\mathrm{i}}}} + \frac{q_{x}}{Q_{L_{\mathrm{x}}}} + \left(1-m^{\mathrm{ON}}\right)\frac{q_{i}}{Q_{C_{\mathrm{i}}}} + \frac{m^{\mathrm{ON}}}{g_{DS}}\right)i_{L_{\mathrm{i}}}(\theta) + \frac{q_{x}}{Q_{L_{\mathrm{x}}}}i_{L_{\mathrm{r}}}(\theta) + \frac{q_{x}}{k_{i}}\frac{\mathrm{d}i_{L_{\mathrm{i}}}(\theta)}{\mathrm{d}\theta} + q_{x}\frac{\mathrm{d}i_{L_{\mathrm{r}}}(\theta)}{\mathrm{d}\theta} = \mu$$

$$\left(1-d^{\mathrm{ON}}\right)v_{C_{\mathrm{r}}}(\theta) - d^{\mathrm{ON}}v_{D} + \frac{q_{x}}{Q_{L_{\mathrm{x}}}}i_{L_{\mathrm{i}}}(\theta) + \left(\frac{1}{g_{\mathrm{o}}} + \frac{1-k_{r}}{k_{r}}\frac{q_{x}}{Q_{L_{\mathrm{r}}}} + \frac{q_{x}}{Q_{L_{\mathrm{x}}}} + \left(1-d^{\mathrm{ON}}\right)\frac{q_{r}}{Q_{C_{\mathrm{r}}}} + \frac{d^{\mathrm{ON}}}{g_{D}}\right)i_{L_{\mathrm{r}}}(\theta) + q_{x}\frac{\mathrm{d}i_{L_{\mathrm{i}}}(\theta)}{\mathrm{d}\theta} + \frac{q_{x}}{k_{r}}\frac{\mathrm{d}i_{L_{\mathrm{r}}}(\theta)}{\mathrm{d}\theta} = 1$$

$$i_{L_{\mathrm{i}}}(\theta) = \frac{1}{g_{i}}\frac{\mathrm{d}v_{C_{\mathrm{r}}}(\theta)}{\mathrm{d}\theta} \quad (Z_{\mathrm{1}} \text{ and } Z_{\mathrm{2}} \text{ only}),$$

$$i_{L_{\mathrm{r}}}(\theta) = \frac{1}{g_{r}}\frac{\mathrm{d}v_{C_{\mathrm{r}}}(\theta)}{\mathrm{d}\theta} \quad (Z_{\mathrm{2}} \text{ and } Z_{\mathrm{3}} \text{ only})$$

In conclusion, the normalized analytic evolution of the converter in the considered clock period is then given by the piecewise solution

$$i_{L_{i}}(\theta) = i_{L_{i}}^{(Z_{k})}(\theta) \quad v_{L_{i}}(\theta) = v_{L_{i}}^{(Z_{k})}(\theta) i_{L_{r}}(\theta) = i_{L_{r}}^{(Z_{k})}(\theta) \quad v_{L_{r}}(\theta) = v_{L_{r}}^{(Z_{k})}(\theta)$$

(10)

with  $\theta_{k-1} \le \theta \le \theta_k$ ,  $k=1,\ldots,4$ ,  $\theta_0=0$  and  $\theta_4=2\pi$ , and which depends on the dimensionless parameters

$$\frac{\mu, D, i_{L_{i}}^{0}, i_{L_{r}}^{0}, k_{i}, k_{r}, q_{i}, q_{x}, q_{r},}{v_{D}, Q_{L_{i}}, Q_{L_{x}}, Q_{L_{r}}, Q_{C_{i}}, Q_{C_{r}}, g_{DS}, g_{D}, g_{i}, g_{o}}$$

(11)

Note that some of the above parameters are fixed by technological constraints (such as inductors and capacitors quality factors, as well as  $k_i$  and  $v_D$ ) or circuital ones (such as  $\mu$ ). Others are not constrained, and can be set to achieve the desired ZVS and ZVDS behavior. In particular, the parameters that can be easily tuned by a designer are  $q_i$ ,  $q_r$ ,  $q_x$  and  $k_r$ , representing the normalized value of  $C_i$ ,  $C_r$ ,  $L_x$  and  $L_r$ . Also the duty cycle D can be tuned for optimization purposes. Conversely, the values of  $i_{L_i}^0$  and  $i_{L_r}^0$ , despite unconstrained, are regulated by the circuit evolution.

#### IV. CIRCUIT DESIGN TECHNIQUE

From (10) one can get the converter design once behavioral constraints are expressed into a mathematical form.

• Stationary condition: it is achieved when:

$$i_{L_{\rm i}}(2\pi) = i_{L_{\rm i}}(0) = i_{L_{\rm i}}^{0}$$

(12)

$$i_{L_r}(2\pi) = i_{L_r}(0) = i_{L_r}^0$$

(13)

$$\frac{1}{2\pi} \int_{0}^{2\pi} i_{L_{\mathbf{r}}}(\theta) \,\mathrm{d}\theta + 1 = 0 \tag{14}$$

Equations (12) and (13) are used to ensure that the two current waveforms  $i_{L_{\rm i}}(\theta)$  and  $i_{L_{\rm r}}(\theta)$  are periodic waveforms<sup>1</sup>. Equation (14) derives from (1) under the assumption to compute the mean value of  $I_{\rm rec}(t)$  as its average value in a period, and considering the normalization introduced in (3). With (14) we ensure that the average current on  $C_l$  is zero, so that the average output voltage is unchanged justifying the assumption to replace it with an ideal voltage source.

• **ZVS:** the zero voltage switching is achieved by imposing:

$$v_{C_i}(\theta_2) = 0 \tag{15}$$

• **ZVDS:** the zero voltage derivative switching is achieved when  $dv_{C_i}(\theta)/d\theta = 0$  for  $\theta = \theta_2$ . Accordingly to (7), this is equivalent to ask that:

$$i_{L_i}(\theta_2) = 0 \tag{16}$$

Equations (12)-(16) represent a system of five (non-linear) equations in the seven (unconstrained) variables

$$D, i_{L_i}^0, i_{L_r}^0, k_r, q_i, q_x, q_r \tag{17}$$

<sup>1</sup>Note that a similar condition for  $v_{C_i}(\theta)$  and  $v_{C_r}(\theta)$  is not necessary, since it is always satisfied.

and, once solved, ensure that the designed converter features both ZVS and ZVDS behavior at its steady state. Furthermore, note that they are independent of the switching frequency  $f_s$ , which is required to denormalize the system according to (4) and represents an additional free design parameter.

Unfortunately, the solution of these equations cannot be achieved in closed form due to their non-linearity. Yet, they can be fed into any numerical solver (usually, a numerical optimization tool) to get, with minimal computational effort, the parameters values that ensure the desired behavior. The Wolfram Mathematica notebook software developed for solving the system (12)-(16) is available online<sup>2</sup> and as paper additional material.

Interestingly enough, despite the non-linearity, we always observed that the achieved equation system has a "good" behavior: under the assumption that a solution exists, only five degrees of freedom are required to satisfy the five constraints (12)-(16). Furthermore, in the most common case (in particular, in the ideal lossless system, i.e., when all quality factors are set to infinity and  $v_D = 0$ ), convergence of the numerical optimization tool is not an issue, and the selection of a proper initial point is required only for reducing the computation time. With respect to this, it is worth highlighting that the system has shown to be smooth, so the best candidate as initial point is the solution of another system whose design parameters (e.g.,  $\mu$ ,  $k_i$ , etc.) are similar to those of the considered one. As an example, the solution of the corresponding ideal lossless system is a good candidate as the initial point of a lossy system. This is the approach we followed in the two examples of Sec. VI.

Interestingly, from a mathematical point of view, only five among the unconstrained parameters in (17) are returned by the solver. This means that two parameters are actually degrees of freedom.

In the example provided is Sec. VI, aiming to optimize the the hardware implementation complexity of the converter, we fix the value of D and  $k_r$ . In fact, a 50% duty cycle clock is usually the simplest one to realize, while fixing  $k_r$  means setting the ratio between the inductances of the two inductors present in the circuit of Fig. 2(b) (or between the inductance of the inductor and the equivalent inductance and the transformer for the circuit in Fig. 2(a)). The latter may be extremely useful both in an off-the-shelf realization and in an integrated one, since the number of available inductors is usually much more limited with respect to the number of available capacitors.

Despite the one mentioned above is the optimization choice we made in this paper, it is worth stressing that other choices are possible and can be easily achieved. As an example, one may want to exploit the degrees of freedom to reduce the peak values of voltage or current on the active devices, so reducing their stress and improving reliability and/or reducing costs. Another option is to maximize the converter efficiency,  $\eta$  defined as the ratio between the power on the output load and the power required from the input source  $V_{\rm in}$ , that considering

<sup>&</sup>lt;sup>2</sup>see http://dcdc.signalprocessing.it

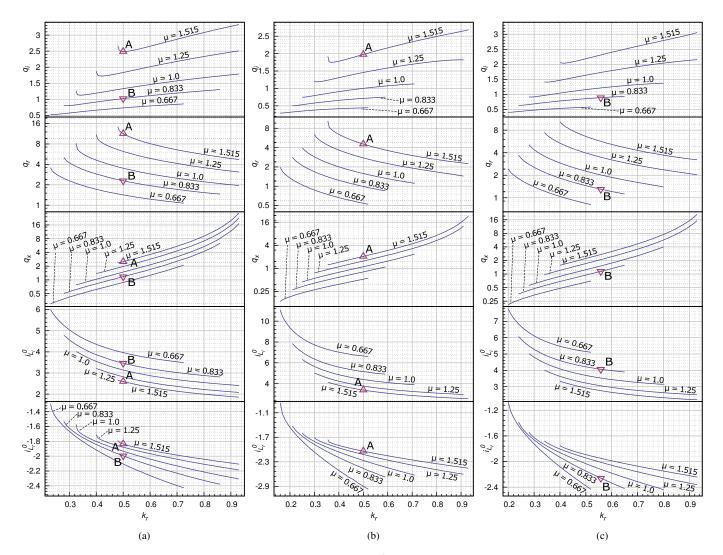

Fig. 8. Design curves for the dimensionless system. (a): for D=0.5,  $k_i=1$ ,  $v_d^{\rm ON}=0$  and all quality factors to infinity (i.e., a lossless system); (b): for D=0.5,  $k_i=1$ ,  $v_D=0.091$ ,  $Q_{L_{\rm i}}=\infty$ ,  $Q_{L_{\rm r}}=Q_{L_{\rm x}}=36$ ,  $Q_{C_{\rm i}}=Q_{C_{\rm r}}=28$ ,  $g_{DS}=162$ ,  $g_D=162$  and  $g_{\rm i}=g_{\rm o}=218$  (design example 1); and (c): for D=0.5,  $k_i=0.98$ ,  $v_D^{\rm ON}=0.058$ ,  $Q_{L_{\rm i}}=Q_{L_{\rm x}}=45$ ,  $Q_{L_{\rm i}}=47$ ,  $Q_{C_{\rm i}}=Q_{C_{\rm r}}=\infty$ ,  $g_{DS}=2700$ ,  $g_D=96$ ,  $g_{\rm i}=720$  and  $g_{\rm o}=56.5$  (design example 2). These design curves have been used in Sec. VI for the design of the two prototypes, whose working points have been identified by the markers A and B.

the normalization we introduced can be defined as

$$\eta = \frac{\int_0^{2\pi} i_{L_{\rm r}}(\theta) \,\mathrm{d}\theta}{\mu \int_0^{2\pi} i_{L_{\rm i}}(\theta) \,\mathrm{d}\theta}$$

(18)

Also in this case, to limit the complexity of this paper, we leave the detailed description of these optimized solutions to future contributions.

#### V. DESIGN CURVES

As observed in the previous section, the advantage of the proposed dimensionless analysis is that one can solve the system composed by (12)-(16) without any assumption on the real circuit parameters, thus obtaining general design curves. Then, a circuit designer can simply ensure the optimal working point by looking at the achieved dimensionless solution and denormalize it with the actual values of  $V_o$ ,  $I_o$  and  $f_s$ . In case

of an isolated topology, also the value of n has to be used in the denormalization process.

In this paper we limit ourselves to propose the three design curves sets of Fig. 8. The curves refer to the two design examples that will be considered in Sec. VI, and have to be interpreted as follows.

The plots report, from top to bottom, the values of  $q_i$ ,  $q_r$ ,  $q_x$ ,  $i_{L_i}^{\ 0}$  and  $i_{L_r}^{\ 0}$  that ensure both ZVS and ZVDS behavior at stationary condition, as a function of  $k_r$  and  $\mu$ , under the assumption that  $k_i$ , D and all other technological constrained parameters are fixed. Given the actual value of  $\mu$ , i.e., given the ratio between input and output voltage, and by looking at the design curves corresponding to the actual values of the parameters fixed by technological constraints, a designer can simply select a value of  $k_r$  of his/her choice, and immediately get  $q_i$ ,  $q_r$  and  $q_x$ . Then, given  $V_o$ ,  $I_o$  and  $f_s$ , by using (4) it is possible to get the values of  $C_i$ ,  $C_r$ ,  $L_x$  and  $L_r$  of the equivalent circuit of Fig. 5(c). In case of a non-isolated

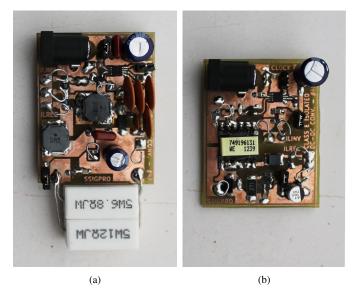

Fig. 9. Photograph of the designed prototypes. (a): 2.5 W non-isolated dc-dc converter; and (b): 500 mW isolated dc-dc converter.

topology, these values correspond directly to  $C_{

m inv},\,C_{

m rec},\,L_{

m pair}$ and  $L_{\rm rec}$ ; in case of an isolated topology,  $C_{\rm rec}$  and  $L_{\rm rec}$  are modified by the turns ratio value. In the next section, two design examples will be provided to better clarify the design procedure.

#### VI. PROTOTYPES DESIGN AND MEASUREMENTS

The proposed methodology is validated through the design, implementation and measurements of two dc-dc converters realized with off-the-shelves components. The first one has a non-isolated topology, a low switching frequency and it is built with low-quality inductors and capacitors. The second one is isolated, running at higher frequency and designed with highquality reactive elements. The pictures of the two prototypes are shown in Fig. 9(a) and Fig. 9(b), respectively. The design procedure is composed of two steps: the first design step is performed neglecting any kind of loss in the circuit in order to get, with the help of the design curves of Fig. 8(a), a first approximation of the component values, and consequently an indication of their parasitics. Then we take into account all circuit non idealities (diode voltage drop, inductor and capacitor quality factors etc.) to reach the final accurate design point by exploiting the design curves of Fig. 8(b) and Fig. 8(c).

**Design example 1.** Let us consider a 2.5 W non-isolated dc-dc converter, with  $V_{\rm in} = 5\,\mathrm{V}$  and  $V_{\rm out} = 3.3\,\mathrm{V}$  (so  $I_{\rm out}=0.76\,{\rm A}$  and  $R_{\rm load}=4.36\,\Omega$ ), operating at approximately  $500\,\mathrm{kHz}$ . The desired voltage ratio imposes  $\mu=1.515$ and, since it is a non-isolated topology, we have  $L_i = 0 \,\mathrm{H}$ and so  $k_i = 1$ . Let us also set the two additional constraints  $k_r=0.5$  (to achieve  $L_x=L_r$  and thus  $L_{

m pair}=L_{

m rec}$ ) and D=0.5 (i.e.,  $\theta_3=\pi$ ). If we initially assume that all circuit elements are ideal, i.e.,  $V_D^{\rm ON}=0$  and all quality factors equal to infinity, the solution of (12)-(16) is the point indicated with the marker "A" in Fig. 8(a) and it is given by:

$$q_i = 2.49, q_r = 11.3, q_x = 2.50, i_{L_i}^0 = 2.60, i_{L_r}^0 = -1.84$$

(19)

Then  $q_i$ ,  $q_r$ ,  $q_r$  and  $k_r$  can be denormalized using (4) to get

$$C_{\rm inv} = 29.4 \,\mathrm{pF}, \, C_{\rm rec} = 6.43 \,\mathrm{pF}, \, L_{\rm pair} = L_{\rm rec} = 3.47 \,\mu\mathrm{H}$$

Given a first approximation of circuit elements values, it is possible to get a realistic indication of their parasitics. For example, let us assume that we wish to design the converter with inductors that, in the range of a few  $\mu H$  and for the desired frequency, have  $Q_{L_{\rm x}}=Q_{L_{\rm r}}\approx 36.$  We desire to use standard ceramic capacitors with X7R dielectric, which have a quite low merit factor at the desired operating frequency, quantifiable in  $Q_{C_i} = Q_{C_r} \approx 28$ . Furthermore, we use a IRLML0030TR N-MOS transistor by International Rectifier, with  $R_{DS}^{\rm ON} \approx 27\,\mathrm{m}\Omega$  ( $g_{DS} \approx 162$ ) and a DB24307 Schottky barrier diode from Panasonic with  $V_D \approx 0.3 \, \mathrm{V}$  and  $R_D^{\rm ON} \approx 30\,{\rm m}\Omega$  ( $v_D=0.091$  and  $g_D\approx 145$ ). Finally, we add two  $20 \,\mathrm{m}\Omega$  current sensing resistors, with  $g_{\mathrm{i}} = g_{\mathrm{o}} \approx 218$ .

The design curves corresponding to these values have been computed and plotted in Fig. 8(b). The desired solution is the point with the marker "A", and it is given by

$$q_i = 1.97, q_r = 4.54, q_x = 2.06, i_{L_i}^0 = 3.38, i_{L_r}^0 = -2.04$$

that is remarkably different from (19), mainly due to the low quality factors of inductors and capacitors. This confirms how important is the consideration and the correct estimation of parasitics in this kind of converters. Denormalization leads to

$$C_{\text{inv}} = 37.0 \text{ pF}, C_{\text{rec}} = 16.1 \text{ pF}, L_{\text{pair}} = L_{\text{rec}} = 2.86 \mu\text{H}$$

For a more feasible solution, we exploit the last degree of freedom given by the oscillation frequency, noticing that by slightly increasing the  $f_s$  from 500 kHz to 649.6 kHz, we get

$$C_{\rm inv} = 28.5 \, {\rm pF}, \, C_{\rm rec} = 12.4 \, {\rm pF}, \, L_{\rm pair} = L_{\rm rec} = 2.2 \, \mu {\rm H}$$

In this way, we can use two inductors with a standard commercial values for  $L_{\rm pair}$  and  $L_{\rm rec}$ , while we can approximate  $C_{\mathrm{inv}} = 30\,\mathrm{pF}$  and  $C_{\mathrm{rec}} = 12.2\,\mathrm{pF}$  placing a few commercial capacitors in parallel.

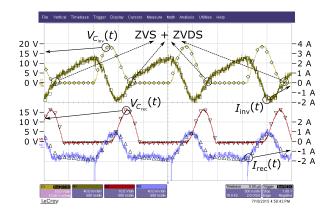

Output voltage and current measured from the prototype are in the expected range ( $V_{\text{out}} = 3.1 \,\text{V}$  and  $I_{\text{out}} = 680 \,\text{mA}$ ). Also the measured efficiency (59%) agrees with the theoretical one (58%) computed accordingly to (18). The measured waveforms for  $V_{C_{\rm inv}}(t),\,V_{C_{\rm rec}}(t),\,I_{\rm inv}(t)$  and  $I_{\rm rec}(t)$  are plotted in Fig. 10 (solid line), along with the theoretical ones computed with the developed model (marker points). As it can be noted, the matching is almost perfect; it is also possible to see a very good behavior in terms of both ZVS and ZVDS.

Design example 2. Let us consider a 500 mW isolated dcdc converter, with  $V_{\rm in}=5\,{\rm V},\,V_{\rm out}=12\,{\rm V}$  (so  $I_{\rm out}=41.7\,{\rm mA}$ and  $R_{\rm load} = 288 \,\Omega$ ), operating at approximately 1 MHz. Let us also assume a transformer turns ratio n = 2. By considering all the normalizations introduced in Sec. III, we have  $\mu = nV_{\rm in}/V_{\rm out} = 0.833$ . Here,  $k_i$  is given by the transformer coupling coefficient k (so ideally  $k_i = 1$ ), while  $k_r = k L_{

m p}/(L_{

m p} + L_{

m rec}/n^2)$  determines the relation between  $L_{\rm p}$  and  $L_{\rm rec}$ . As in the previous example, we can start with the assumption of ideal devices and  $k_r = 0.5$ , that leads from Fig. 8(a) (see marker "B") to

$$q_i = 2.49, \ q_r = 11.3, \ q_x = 2.50, \ i_{L_i}^{\ 0} = 2.60, \ i_{L_r}^{\ 0} = -1.84$$

(19)  $q_i = 1.03, \ q_r = 2.29, \ q_x = 1.18, \ i_{L_i}^{\ 0} = 3.46, \ i_{L_r}^{\ 0} = -1.99$  (20)

Fig. 10. Measured current and voltage waveforms for the 2.5 W non-isolated dc-dc converter prototype, compared with the expected theoretical ones (dark markers) computed with the proposed model.

$V_{C_{inv}}(t)$ ZVS + ZVDS 20 V 15 V 10 V 500 mA -250 mA -250 mA  $V_{c}(t)_{c}$ 40 V -500 mA 20 V--100 mA -50 mA -0 mA -50 mA -150 mA

Fig. 11. Measured current and voltage waveforms for the  $500\,\mathrm{mW}$  isolated dc-dc converter prototype, compared with the expected theoretical ones (dark markers) computed with the proposed model.

#### that is denormalized to

#### $C_{\rm inv} = 2.15 \,\mathrm{nF}, \, C_{\rm rec} = 241 \,\mathrm{pF}, \, L_{\rm p} = 13.5 \,\mu\mathrm{H}, \, L_{\rm rec} = 54.1 \,\mu\mathrm{H}$

The best fit for commercial transformer is a  $10.9 \,\mu\text{H}$  WE-FLEX transformer by Würth Elektronik, with coupling coefficient  $k \approx 0.98$  and quality factor  $\approx 45$ . Consequently, we use a smaller value also for the inductor, i.e.,  $L_{\rm rec}=33\,\mu{\rm H}$ with a quality factor  $\approx 47$ . Without any knowledge on how the transformer losses are divided into the  $R_{\rm core}$  and  $R_{\rm p}$ , we assume  $Q_{L_{\rm i}} \approx Q_{L_{\rm x}} \approx 45$ , while  $Q_{L_r} \approx 47$ . Furthermore,  $k_i \approx 0.98$  and  $k_r \approx 0.558$ . In this prototype we use ceramic capacitors with COG dielectric, that ensure extremely high performance  $(Q_{C_i} > 1000 \text{ and } Q_{C_r} > 1000)$  so that we can assume an infinite quality factor. We also use the same N-MOS as in the previous example (with here  $g_{DS} \approx 2700$ ), while the rectifying diode of our choice is a ES1B by Vishay, with  $V_D^{\rm ON} \approx 0.7 \, {\rm V}$  and  $R_D^{\rm ON} \approx 3 \, \Omega$  ( $v_D = 0.058$  and  $g_D \approx 96$ ). The design is completed with two current sensing resistors, a  $0.1\,\Omega$  at the primary side  $(g_{\rm i}\approx720)$  and a  $5.1\,\Omega$  at the secondary side ( $g_o \approx 56.5$ )

The solution of the system considering these technological constrained parameters can be found looking at the design curves of Fig. 8(c). Due to the high quality of the component used, this design leads to a solution (the marker point "B" in the figure) not very different from (20)

$$q_i = 0.910, q_r = 1.35, q_x = 1.16, i_{L_i}^0 = 3.97, i_{L_r}^0 = -2.23$$

that, by slightly increasing the operating frequency to  $f_s=1.25\,\mathrm{MHz}$ , is denormalized as

$$C_{\rm inv}\!=\!1.95\,{\rm nF},\,C_{\rm rec}\!=\!328\,{\rm pF},\,L_{\rm p}\!=\!10.9\,\mu{\rm H},\,L_{\rm rec}\!=\!33\,\mu{\rm H}$$

where we can approximate  $C_{\rm inv}=2\,{\rm nF}$  and  $C_{\rm rec}=330\,{\rm pF}$ . Measurements show  $V_{\rm out}=11.8\,{\rm V}$  and  $I_{\rm out}=40.3\,{\rm mA}$  with a 75% efficiency, that are very similar to the theoretically expected ones (12.0 V, 41.7 mA, 77%). Measured waveforms are plotted in Fig. 11 (solid lines) and compared with the ones computed according to the developed theoretical model (marker points). Also in this case the matching is extremely good.

#### VII. CONCLUSION

In this paper, a new approach for class-E dc-dc converter design has been proposed. Differently from the state-of-the-art approach, the proposed methodology is based on the *exact* circuit analysis, and does not need any strong simplifying assumptions such as the common sinusoidal approximation. Furthermore, the approach is capable of taking into account the most important circuit non-idealities, ensuring a very high adherence between the actual circuit evolution and the modeled one. A dimensionless approach also allows to achieve design curves that can be used to get in few seconds the optimized circuit design. As a proof of concept, two dc-dc converter prototypes are presented. Measurements confirm an almost perfect matching with the expected results.

### APPENDIX MATHEMATICAL FORMULATIONS OF SEC. III

A. Zone  $Z_1$

In  $Z_1$   $v_{C_{\rm r}}^{(Z_1)}$  is assumed constant. Eq. (7) is so reduced to a third order system in the tree variables  $i_{L_{\rm i}}^{(Z1)}$ ,  $i_{L_{\rm r}}^{(Z1)}$  and  $v_{C_{\rm i}}^{(Z_1)}$ . By properly rearranging all terms in (7), the system can be conveniently rewritten as

$$\frac{\mathrm{d}}{\mathrm{d}\theta} \begin{pmatrix} i_{L_{i}}^{(Z_{1})}(\theta) \\ i_{L_{r}}^{(Z_{1})}(\theta) \\ v_{C}^{(Z_{1})}(\theta) \end{pmatrix} = \underline{\underline{A}}^{(Z_{1})} \begin{pmatrix} i_{L_{i}}^{(Z_{1})}(\theta) \\ i_{L_{r}}^{(Z_{1})}(\theta) \\ v_{C}^{(Z_{1})}(\theta) \end{pmatrix} + \underline{\underline{B}}^{(Z_{1})} \tag{A.1}$$

where all elements of  $\underline{\boldsymbol{A}}^{(Z_1)} \in \mathbb{R}^{3 \times 3}$  and of  $\underline{\boldsymbol{B}}^{(Z_1)} \in \mathbb{R}^3$  can be retrieved by comparing (A.1) with (7) under the assumption that  $m^{\mathrm{ON}} = 0$  and  $d^{\mathrm{ON}} = 1$ . Even if it is not possible to provide a full mathematical demonstration, the matrix  $\underline{\boldsymbol{A}}^{(Z_1)}$  always features two complex conjugated eigenvalues  $-\sigma_0 \pm j\omega_0$  (with associated eigenvectors  $\underline{\boldsymbol{w}}_R \pm j\underline{\boldsymbol{w}}_I$ ) and a real negative one  $-\lambda_3$  (with associated eigenvector  $\underline{\boldsymbol{w}}_3$ ) that can be easily numerically computed. In this case, the solution of (A.1) in matricial form is given by (A.2). Note that three unknown coefficients  $c_1$ ,  $c_2$  and  $c_3$  are presents, and determined once the initial condition of the system is given.

$$\begin{pmatrix}

i_{L_{1}}^{(Z_{1})}(\theta) \\

i_{L_{1}}^{(Z_{1})}(\theta) \\

v_{C}^{(Z_{1})}(\theta)

\end{pmatrix} = \begin{pmatrix}

\underline{\boldsymbol{w}}_{R} \ \underline{\boldsymbol{w}}_{I} \ \underline{\boldsymbol{w}}_{3}

\end{pmatrix} \begin{pmatrix}

e^{-\sigma_{0}\theta} \cos(\omega_{0}\theta) & e^{-\sigma_{0}\theta} \sin(\omega_{0}\theta) & 0 \\

-e^{-\sigma_{0}\theta} \sin(\omega_{0}\theta) & e^{-\sigma_{0}\theta} \cos(\omega_{0}\theta) & 0 \\

0 & 0 & e^{-\lambda_{3}\theta}

\end{pmatrix} \begin{pmatrix}

c_{1} \\

c_{2} \\

c_{3}

\end{pmatrix} - \left(\underline{\boldsymbol{A}}^{(Z_{1})}\right)^{-1} \underline{\boldsymbol{B}}^{(Z_{1})} \tag{A.2}$$

$$\begin{pmatrix} i_{L_{1}}^{(Z_{2})}(\theta) \\ i_{L_{r}}^{(Z_{2})}(\theta) \\ v_{C_{1}}^{(Z_{2})}(\theta) \\ v_{C_{r}}^{(Z_{2})}(\theta) \end{pmatrix} = \begin{pmatrix} \underline{\boldsymbol{w}}_{R1} \ \underline{\boldsymbol{w}}_{I1} \ \underline{\boldsymbol{w}}_{R2} \ \underline{\boldsymbol{w}}_{I2} \end{pmatrix} \begin{pmatrix} e^{-\sigma_{1}\theta} \cos(\omega_{1}\theta) \ e^{-\sigma_{1}\theta} \sin(\omega_{1}\theta) & 0 & 0 \\ -e^{-\sigma_{1}\theta} \sin(\omega_{1}\theta) \ e^{-\sigma_{1}\theta} \cos(\omega_{1}\theta) & 0 & 0 \\ 0 & 0 & e^{-\sigma_{2}\theta} \cos(\omega_{2}\theta) \ e^{-\sigma_{2}\theta} \sin(\omega_{2}\theta) \end{pmatrix} \begin{pmatrix} c_{1} \\ c_{2} \\ c_{3} \\ c_{4} \end{pmatrix} - \left(\underline{\boldsymbol{A}}^{(Z_{2})}\right)^{-1} \underline{\boldsymbol{B}}^{(Z_{2})}$$

$$(A.4)$$

$$\begin{pmatrix}

i_{L_{1}}^{(Z_{3})}(\theta) \\

i_{L_{r}}^{(Z_{3})}(\theta) \\

v_{C_{r}}^{(Z_{3})}(\theta)

\end{pmatrix} = \begin{pmatrix}

\underline{\boldsymbol{w}}_{R} \ \underline{\boldsymbol{w}}_{I} \ \underline{\boldsymbol{w}}_{3}

\end{pmatrix}

\begin{pmatrix}

e^{-\sigma_{0}\theta} \cos(\omega_{0}\theta) & e^{-\sigma_{0}\theta} \sin(\omega_{0}\theta) & 0 \\

-e^{-\sigma_{0}\theta} \sin(\omega_{0}\theta) & e^{-\sigma_{0}\theta} \cos(\omega_{0}\theta) & 0 \\

0 & 0 & e^{-\lambda_{3}\theta}

\end{pmatrix}

\begin{pmatrix}

c_{1} \\

c_{2} \\

c_{3}

\end{pmatrix} - \left(\underline{\boldsymbol{A}}^{(Z_{3})}\right)^{-1}\underline{\boldsymbol{B}}^{(Z_{3})}$$

(A.6)

#### B. Zone $Z_2$

The system evolution is regulated by

$$\frac{\mathrm{d}}{\mathrm{d}\theta} \begin{pmatrix} i_{L_{1}}^{(Z_{2})}(\theta) \\ i_{L_{2}}^{(Z_{2})}(\theta) \\ v_{C_{1}}^{(Z_{2})}(\theta) \\ v_{C_{2}}^{(Z_{2})}(\theta) \end{pmatrix} = \underline{\boldsymbol{A}}^{(Z_{2})} \begin{pmatrix} i_{L_{1}}^{(Z_{2})}(\theta) \\ i_{L_{2}}^{(Z_{2})}(\theta) \\ v_{C_{1}}^{(Z_{2})}(\theta) \\ v_{C_{2}}^{(Z_{2})}(\theta) \end{pmatrix} + \underline{\boldsymbol{B}}^{(Z_{2})} \tag{A.3}$$

where  $\underline{A}^{(Z_2)} \in \mathbb{R}^{4 \times 4}$  and  $\underline{B}^{(Z_2)} \in \mathbb{R}^4$ . The matrix  $\underline{A}^{(Z_2)}$  has two couples of complex conjugates eigenvalues  $-\sigma_1 \pm j\omega_1$  (with associated eigenvectors  $\underline{w}_{R1} \pm j\underline{w}_{I1}$ ) and  $-\sigma_2 \pm j\omega_2$  (with associated eigenvectors  $\underline{w}_{R2} \pm j\underline{w}_{I2}$ ). The evolution of all normalized current and voltage signals is given by the sum of two damped sinusoidal tones, with angular frequency  $\omega_1$  and  $\omega_2$ , whose expression is given in (A.4).

#### C. Zone $Z_3$

The evolution here is regulated by a third order system as in  $Z_1$ , and it is described by

$$\frac{\mathrm{d}}{\mathrm{d}\theta} \begin{pmatrix} i_{L_{\mathrm{i}}}^{(Z_{3})}(\theta) \\ i_{L_{\mathrm{r}}}^{(Z_{3})}(\theta) \\ v_{C}^{(Z_{3})}(\theta) \end{pmatrix} = \underline{\boldsymbol{A}}^{(Z_{3})} \begin{pmatrix} i_{L_{\mathrm{i}}}^{(Z_{3})}(\theta) \\ i_{L_{\mathrm{r}}}^{(Z_{3})}(\theta) \\ v_{C}^{(Z_{3})}(\theta) \end{pmatrix} + \underline{\boldsymbol{B}}^{(Z_{3})} \tag{A.5}$$

with  $\underline{\underline{A}}^{(Z_3)} \in \mathbb{R}^{3 \times 3}$  and  $\underline{\underline{B}}^{(Z_3)} \in \mathbb{R}^3$ . Similarly to  $\underline{\underline{A}}^{(Z_1)}$ , also  $\underline{\underline{A}}^{(Z_3)}$  features two complex conjugated eigenvalues  $-\sigma_0 \pm j\omega_0$  (with associated eigenvectors  $\underline{\underline{w}}_R \pm j\underline{\underline{w}}_I$ ) and a real one  $-\lambda_3$  (with associated eigenvector  $\underline{\underline{w}}_3$ ). The evolution of the system is regulated by (A.6).

#### D. Zone $Z_2$

In  $Z_4$ ,  $v_{C_{\rm i}}^{(Z_4)}$  and  $v_{C_{\rm r}}^{(Z_4)}$  are constrained, and (7) is reduced to

$$\frac{\mathrm{d}}{\mathrm{d}\theta} \begin{pmatrix} i_{L_{1}}^{(Z_{4})}(\theta) \\ i_{L_{r}}^{(Z_{4})}(\theta) \end{pmatrix} = \underline{\boldsymbol{A}}^{(Z_{4})} \begin{pmatrix} i_{L_{1}}^{(Z_{4})}(\theta) \\ i_{L_{r}}^{(Z_{4})}(\theta) \end{pmatrix} + \underline{\boldsymbol{B}}^{(Z_{4})} \tag{A.7}$$

where  $\underline{A}^{(Z_4)} \in \mathbb{R}^{2 \times 2}$  and  $\underline{B}^{(Z_4)} \in \mathbb{R}^2$ . Since  $\underline{A}^{(Z_4)}$  has always two real negative eigenvalues  $-\lambda_1$  and  $-\lambda_2$  with

associated eigenvectors  $\underline{\boldsymbol{w}}_1$  and  $\underline{\boldsymbol{w}}_2$ , the evolution is simply given by:

$$\begin{pmatrix} i_{L_{\mathbf{i}}}^{(Z_{4})}(\theta) \\ i_{L_{\mathbf{r}}}^{(Z_{4})}(\theta) \end{pmatrix} = \left( \underline{\boldsymbol{w}}_{1} \ \underline{\boldsymbol{w}}_{2} \right) \begin{pmatrix} e^{-\lambda_{1}\theta} & 0 \\ 0 & e^{-\lambda_{2}\theta} \end{pmatrix} \begin{pmatrix} c_{1} \\ c_{2} \end{pmatrix} - \left( \underline{\boldsymbol{A}}^{(Z_{4})} \right)^{-1} \underline{\boldsymbol{B}}^{(Z_{4})}$$

$$(A.8)$$

#### REFERENCES

- J. Rivas, D. Jackson, O. Leitermann, A. Sagneri, Y. Han, and D. Perreault, "Design Considerations for Very High Frequency dc-dc Converters," in 2006 IEEE Power Electronics Specialists Conf., Jun. 2006, pp. 1–11.

- [2] J. Rivas, R. Wahby, J. Shafran, and D. Perreault, "New Architectures for Radio-Frequency DC-DC Power Conversion," *IEEE Trans. on Power Electron.*, vol. 21, no. 2, pp. 380–393, Mar. 2006.

- [3] R. Pilawa-Podgurski, A. Sagneri, J. Rivas, D. Anderson, and D. Perreault, "Very-high-frequency resonant boost converters," *IEEE Trans. Power Electron.*, vol. 24, no. 6, pp. 1654–1665, Jun. 2009.

- [4] D. Perreault, J. Hu, J. Rivas, Y. Han, O. Leitermann, R. Pilawa-Podgurski, A. Sagneri, and C. Sullivan, "Opportunities and Challenges in Very High Frequency Power Conversion," in 24th Annu. IEEE Applied Power Electronics Conf. and Expo. (APEC2009), Feb 2009, pp. 1–14.

- [5] R. Gutmann, "Application of RF Circuit Design Principles to Distributed Power Converters," *IEEE Trans. Ind. Electron. and Control Instr.*, vol. IECI-27, no. 3, pp. 156–164, Aug. 1980.

- [6] R. Redl, B. Molnar, and N. Sokal, "Class E Resonant Regulated DC/DC Power Converters: Analysis of Operations, and Experimental Results at 1.5 MHz," *IEEE Trans. Power Electron.*, vol. PE-1, no. 2, pp. 111–120, Apr. 1986.

- [7] N. Sokal and A. Sokal, "Class E-A new class of high-efficiency tuned single-ended switching power amplifiers," *IEEE J. Solid-State Circuits*, vol. 10, no. 3, pp. 168–176, Jun. 1975.

- [8] I. Batarseh, R. Liu, C. Lee, and A. Upadhyay, "Theoretical and experimental studies of the lcc-type parallel resonant converter," *Power Electronics, IEEE Transactions on*, vol. 5, no. 2, pp. 140–150, Apr 1990.

- [9] J. Lazar and R. Martinelli, "Steady-state analysis of the llc series resonant converter," in *Applied Power Electronics Conference and Ex*position, 2001. APEC 2001. Sixteenth Annual IEEE, vol. 2, 2001, pp. 728–735 vol.2.

- [10] M. Foster, H. Sewell, C. Bingham, D. Stone, D. Hente, and D. Howe, "Cyclic-averaging for high-speed analysis of resonant converters," *Power Electronics, IEEE Transactions on*, vol. 18, no. 4, pp. 985–993, July 2003.

- [11] N. Bertoni, G. Frattini, R. Massolini, F. Pareschi, R. Rovatti, and G. Setti, "A new semi-analytic approach for class-E resonant DC/DC converter design," in *Int. Symp. on Circuits and Systems (ISCAS)*, May 2015, pp.

- [12] N. Bertoni, G. Frattini, P. Albertini, F. Pareschi, R. Rovatti, and G. Setti, "A first implementation of a semi-analytically designed class-E resonant DC-DC converter," in *Int. Symp. on Circuits and Systems (ISCAS)*, May 2015, pp. 221–224.

- [13] M. Kazimierczuk and J. Jozwik, "Resonant DC/DC converter with class-E inverter and class-E rectifier," *IEEE Trans. Ind. Electron.*, vol. 36, no. 4, pp. 468–478, Nov. 1989.

- [14] M. Kazimierczuk and K. Puczko, "Exact analysis of class E tuned power amplifier at any Q and switch duty cycle," *IEEE Trans. Circuits and Syst.*, vol. 34, no. 2, pp. 149–159, Feb 1987.

- [15] R. Gutmann and J. Borrego, "Power combining in an array of microwave power rectifiers," *IEEE Trans. Microw. Theory Tech.*, vol. 27, no. 12, pp. 958–968, Dec 1979.

- [16] M. Kazimierczuk and J. Jozwik, "Class-E zero-voltage-switching and zero-current-switching rectifiers," *Circuits and Systems, IEEE Transac*tions on, vol. 37, no. 3, pp. 436–444, Mar 1990.

- [17] A. Ivascu, M. Kazimierczuk, and S. Birca-Galateanu, "Class E resonant low dv/dt rectifier," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 39, no. 8, pp. 604–613, Aug. 1992.

- [18] S. Birca-Galateanu and J.-L. Cocquerelle, "Class E half-wave low dν/dt rectifier operating in a range of frequencies around resonance," *IEEE Trans. Circuits and Syst I: Fundamental Theory and Applications*, vol. 42, no. 2, pp. 83–94, Feb 1995.

- [19] J. Rivas, O. Leitermann, Y. Han, and D. Perreault, "A very high frequency dc-dc converter based on a class φ<sub>2</sub> resonant inverter," *IEEE Trans. Power Electron.*, vol. 26, no. 10, pp. 2980–2992, Oct 2011.

- [20] J. Hu, A. Sagneri, J. Rivas, Y. Han, S. Davis, and D. Perreault, "High-frequency resonant sepic converter with wide input and output voltage ranges," *Power Electronics, IEEE Transactions on*, vol. 27, no. 1, pp. 189–200, Jan 2012.

- [21] J. Santiago-Gonzalez, K. Afridi, and D. Perreault, "Design of resistive-input class e resonant rectifiers for variable-power operation," in *Control and Modeling for Power Electronics (COMPEL)*, 2013 IEEE 14th Workshop on, June 2013, pp. 1–6.

- Workshop on, June 2013, pp. 1–6.

[22] A. Mediano and N. Sokal, "A class-E RF power amplifier with a flattop transistor-voltage waveform," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5215–5221, Nov. 2013.

- [23] A. Sagneri, D. Anderson, and D. Perreault, "Optimization of integrated transistors for very high frequency dc-dc converters," *Power Electronics, IEEE Transactions on*, vol. 28, no. 7, pp. 3614–3626, July 2013.

- [24] W. Inam, K. K. Afridi, and D. J. Perreault, "High efficiency resonant dc/dc converter utilizing a resistance compression network," in *Applied Power Electronics Conference and Exposition (APEC)*, 2013 Twenty-Eighth Annual IEEE, March 2013, pp. 1399–1405.

- [25] J. M. Burkhart, R. Korsunsky, and D. J. Perreault, "Design Methodology for a Very High Frequency Resonant Boost Converter," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1929–1937, Apr. 2013.

- [26] M. Madsen, J. Pedersen, A. Knott, and M. Andersen, "Self-oscillating resonant gate drive for resonant inverters and rectifiers composed solely of passive components," in *Applied Power Electronics Conference and Exposition (APEC)*, 2014 Twenty-Ninth Annual IEEE, March 2014, pp. 2029–2035.

- [27] Y. Lee and Y. Cheng, "A 580 khz switching regulator using on-off control," *Electronic and Radio Engineers, Journal of the Institution of*, vol. 57, no. 5, pp. 221–226, September 1987.

- [28] F. de Leon, A. Farazmand, and P. Joseph, "Comparing the T and  $\pi$ s equivalent circuits for the calculation of transformer inrush currents," *IEEE Trans. on Power Delivery*, vol. 27, no. 4, pp. 2390–2398, oct 2012.

Giovanni Frattini received the MS degree in electronic engineering (summa cum laude) from the University of Pavia, Italy, in 1997. The same year he joined STMicroelectronics in Milan, Italy, as an Analog Designer in the BCD technology R&D, where he worked on designing signal analog circuitry for smart power chips, data converters, HV linear and DC/DC power converters. In 2008 he joined National Semiconductor (which became part of Texas Instruments in 2011) to start and lead the R&D team in the Design Center in Milan, Italy,

driving the development of chips for different applications, including photovoltaics, ultrasound, LED driving, isolated power conversion, high frequency DC/DC converters. He is author or co-author of 18 papers and he holds 13 patents.

Roberto G. Massolini received the Laurea Degree in Electronic Engineering (summa cum laude) and the Ph.D. degree in Electronic and Electrical Engineering in 2004 and 2007 from the University of Pavia, Italy. During his Ph.D activity he consulted ST-Microelectronics in the field of Analog Mixed-Signal and digitally assisted ADC converters and developed multiple algorithm for ADC gain and offset correction. He joined National Semiconductor in 2008 (which became part of Texas Instruments in 2011) where he is in charge of circuit and magnetic

component design for different application such as high voltage power conversion for PV, High Frequency Switching Converter, advanced ZVS topology and low power DC-DC point of loads.

Fabio Pareschi (S'05-M'08) received the Dr. Eng. degree (with honours) in Electronic Engineering from University of Ferrara, Italy, in 2001, and the Ph.D. in Information Technology under the European Doctorate Project (EDITH) from University of Bologna, Italy, in 2007. He is currently an Assistant Professor in the Department of Engineering (ENDIF), University of Ferrara. He is also a faculty member of ARCES - University of Bologna, Italy. He served as Associate Editor for the IEEE Transactions on Circuits and Systems -

PART II (2010-2013). His research activity focuses on analog and mixed-mode electronic circuit design, statistical signal processing, random number generation and testing, and electromagnetic compatibility. He was recipient of the best paper award at ECCTD 2005 and the best student paper award at EMC Zurich 2005.

Nicola Bertoni (S'15) received the B.S. degree (cum laude) in information technology and the M.S. degree (magna cum laude) in electronic engineering and telecommunications in 2010 and 2013 respectively, from the University of Ferrara, Italy. He is currently with ENDIF, University of Ferrara, where he is working toward the PhD degree in electronic engineering. In 2015 he spent four months at the Institute for Systems Research, University of Maryland as a visiting scholar under the Italian "Young Researchers" program. His current research focuses

on analog and mixed mode circuit design for power electronics, statistical analysis and design of resonant converters. His other research interests include compressed sensing and low power biomedical applications.

Riccardo Rovatti (M'99-SM'02-F'12) received the M.S. degree in Electronic Engineering and the Ph.D. degree in Electronics, Computer Science, and Telecommunications both from the University of Bologna, Italy in 1992 and 1996, respectively. He is now a Full Professor of Electronics at the University of Bologna. He is the author of approximately 300 technical contributions to international conferences and journals, and of two volumes. His research focuses on mathematical and applicative aspects of statistical signal processing and on the application

of statistics to nonlinear dynamical systems. He received the 2004 IEEE CAS Society Darlington Award, the 2013 IEEE CAS Society Guillemin-Cauer Award, as well as the best paper award at ECCTD 2005, and the best student paper award at EMC Zurich 2005 and ISCAS 2011. He was elected IEEE Fellow in 2012 for contributions to nonlinear and statistical signal processing applied to electronic systems.

Gianluca Setti (S'89-M'91-SM'02-F'06) received the Ph.D. degree in Electronic Engineering and Computer Science from the University of Bologna in 1997. Since 1997 he has been with the School of Engineering at the University of Ferrara, Italy, where he is currently a Professor of Circuit Theory and Analog Electronics and is also a permanent faculty member of ARCES - University of Bologna, Italy. His research interests include nonlinear circuits, implementation and application of chaotic circuits and systems, electromagnetic compatibility, statisti-

cal signal processing and biomedical circuits and systems. Dr. Setti received the 2013 IEEE CAS Society Meritorious Service Award and co-recipient of the 2004 IEEE CAS Society Darlington Award, of the 2013 IEEE CAS Society Guillemin-Cauer Award, as well as of the best paper award at ECCTD 2005, and the best student paper award at EMC Zurich 2005 and at ISCAS 2011. He held several editorial positions and served, in particular, as the Editor-in-Chief for the IEEE TRANSACTION ON CIRCUITS AND SYSTEMSPART II (2006-2007) and of the IEEE TRANSACTION ON CIRCUITS AND SYSTEMSPART II (2008-2009). Dr. Setti was the Technical Program Co-Chair at ISCAS 2007, ISCAS 2008, ICECS 2012, BioCAS 2013 as well as the General Co-Chair of NOLTA 2006. He was a member of the Board of Governors of the IEEE CAS Society (2005-2008), served as its 2010 President, and he is a Distinguished Lecturer of CASS (2015-2016). He held several other volunteer positions for the IEEE and in 2013-2014 he was the first non North-American Vice President of the IEEE for Publication Services and Products.