Doctoral Dissertation Doctoral Program in Computer Engineering (29<sup>th</sup>cycle)

# Cross layer reliability estimation for digital systems

By

## **Alessandro Vallero**

\*\*\*\*\*

Supervisor(s):

Prof. Stefano Di Carlo, Supervisor

#### **Doctoral Examination Committee:**

Prof. Regis Leveugle, Referee, TIMA Grenoble

Prof. Marco Ottavi, Referee, University of "Rome Tor Vergata"

Prof. Ramon Canal, UPC Barcelona

Prof. Lorena Angel, TIMA Grenoble

Prof. Dimitris Gizopoulos, University of Athens

Politecnico di Torino 2017

## Declaration

I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

> Alessandro Vallero 2017

\* This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my grandparents who always open my mind toward new horizons

## Acknowledgements

I would like to acknowledge Prof. Stefano Di Carlo, at first. He made my Ph.D. a pleasant journey during which I had the chance to learn so many things from him, from both a professional and a human point of view. Secondly, I would like to thank my mother, Linda, and my sister, Greta. They supported me emotionally, even in very stressful moments. I acknowledge Computer Architecture Lab of University of Athens. It was a pleasure to work together. During my visiting you made me feel like at home. Thank you Prof. Dimitris Gizopoulos, Sotiris Tselonis, Manolis Kaliorakis, Athanasios Chatzdimitriou, Giorgos Papadimitriou. In addition, I would like to thank all the CLERECO partners with which I collaborated for my Ph.D. activities. I would also like to acknowledge my housemates, Ivan and Daniele, who suffered me for more than two long years! Finally, I thank all the guys of my lab at Politecnico di Torino (Lab 6) who always laughed at my jokes and contributed to create a pleasant atmosphere.

#### Abstract

Forthcoming manufacturing technologies hold the promise to increase multifuctional computing systems performance and functionality thanks to a remarkable growth of the device integration density. Despite the benefits introduced by this technology improvements, reliability is becoming a key challenge for the semiconductor industry. With transistor size reaching the atomic dimensions, vulnerability to unavoidable fluctuations in the manufacturing process and environmental stress rise dramatically. Failing to meet a reliability requirement may add excessive re-design cost to recover and may have severe consequences on the success of a product.

One of the open challenges for future technologies is building "dependable" systems on top of unreliable components, which will degrade and even fail during normal lifetime of the chip. Conventional design techniques are highly inefficient. They expend significant amount of energy to tolerate the device unpredictability by adding safety margins to a circuit's operating voltage, clock frequency or charge stored per bit. Unfortunately, the additional cost introduced to compensate unreliability are rapidly becoming unacceptable in today's environment where power consumption is often the limiting factor for integrated circuit performance, and energy efficiency is a top concern.

Attention should be payed to tailor techniques to improve the reliability of a system on the basis of its requirements, ending up with cost-effective solutions favoring the success of the product on the market. Cross-layer reliability is one of the most promising approaches to achieve this goal. Cross-layer reliability techniques take into account the interactions between the layers composing a complex system (i.e., technology, hardware and software layers) to implement efficient cross-layer fault mitigation mechanisms. Fault tolerance mechanism are carefully implemented at different layers starting from the technology up to the software layer to carefully

optimize the system by exploiting the inner capability of each layer to mask lower level faults.

For this purpose, cross-layer reliability design techniques need to be complemented with cross-layer reliability evaluation tools, able to precisely assess the reliability level of a selected design early in the design cycle. Accurate and early reliability estimates would enable the exploration of the system design space and the optimization of multiple constraints such as performance, power consumption, cost and reliability.

This Ph.D. thesis is devoted to the development of new methodologies and tools to evaluate and optimize the reliability of complex digital systems during the early design stages. More specifically, techniques addressing hardware accelerators (i.e., FPGAs and GPUs), microprocessors and full systems are discussed. All developed methodologies are presented in conjunction with their application to real-world use cases belonging to different computational domains.

# Contents

| List of Figures |                     |              | xi                               |   |   |      |   |      |  |

|-----------------|---------------------|--------------|----------------------------------|---|---|------|---|------|--|

| Li              | List of Tables xvii |              |                                  |   |   | xvii |   |      |  |

| No              | omen                | clature      |                                  |   |   |      | X | viii |  |

| 1               | Intr                | Introduction |                                  |   | 2 |      |   |      |  |

|                 | 1.1                 | Motiva       | ation                            | • |   | •    | • | 4    |  |

|                 | 1.2                 | Goals        |                                  | • |   |      | • | 7    |  |

|                 | 1.3                 | Structu      | ure of the thesis                |   |   |      |   | 9    |  |

| 2               | Dep                 | endabil      | ity of digital systems           |   |   |      |   | 12   |  |

|                 | 2.1                 | Depen        | dability                         | • |   |      | • | 12   |  |

|                 | 2.2                 | Reliab       | ility metrics of digital systems | • |   |      | • | 14   |  |

|                 |                     | 2.2.1        | Failure Rate                     | • |   |      | • | 15   |  |

|                 |                     | 2.2.2        | Failures In Time                 | • |   |      | • | 15   |  |

|                 |                     | 2.2.3        | Mean Time To Failure             | • |   |      | • | 15   |  |

|                 |                     | 2.2.4        | Mean Time To Repair              | • |   |      | • | 16   |  |

|                 |                     | 2.2.5        | Mean Time Between Failures       | • |   |      | • | 16   |  |

|                 |                     | 2.2.6        | Availability                     | • |   |      | • | 16   |  |

|                 |                     | 2.2.7        | Mean Workload To Failure         | • |   |      |   | 17   |  |

|   |      | 2.2.8         | Mean Instruction To Failure           | 17 |

|---|------|---------------|---------------------------------------|----|

|   | 2.3  | Depen         | dability threats                      | 17 |

|   |      | 2.3.1         | Faults                                | 17 |

|   |      | 2.3.2         | Errors                                | 20 |

|   |      | 2.3.3         | Failures                              | 21 |

|   | 2.4  | Soft er       | rors                                  | 23 |

|   | 2.5  | Depen         | dability enhancement techniques       | 26 |

|   |      | 2.5.1         | The traditional approach              | 28 |

|   |      | 2.5.2         | Cross-layer reliability enhancement   | 31 |

|   |      |               |                                       |    |

| 3 | Faul | lt tolera     | nce in autonomous FPGA-based systems  | 33 |

|   | 3.1  | Introdu       | action                                | 33 |

|   | 3.2  | State-c       | of-the-art                            | 35 |

|   | 3.3  | The pr        | oposed methodology                    | 37 |

|   |      | 3.3.1         | The proposed system architecture      | 37 |

|   |      | 3.3.2         | The proposed partitioning methodology | 39 |

|   |      | 3.3.3         | The proposed partitioning algorithm   | 41 |

|   | 3.4  | Experi        | mental results                        | 44 |

|   | 3.5  | Conclu        | usion                                 | 48 |

| 4 | GPG  | <b>PII Re</b> | liability evaluation                  | 49 |

| • | 4.1  |               |                                       | 50 |

|   | 4.2  |               | d works                               | 50 |

|   |      |               |                                       |    |

|   | 4.3  |               | outhern Islands AMD architecture      | 53 |

|   | 4.4  | SIFI at       | rchitecture and functionalities       | 54 |

|   |      | 4.4.1         | Fault injection engine                | 56 |

|   |      | 4.4.2         | ACE analysis engine                   | 57 |

|   | 4.5  | Experi    | mental results                                                                     | 59  |

|---|------|-----------|------------------------------------------------------------------------------------|-----|

|   |      | 4.5.1     | SIFI results                                                                       | 59  |

|   |      | 4.5.2     | A multi-faceted comparison of reliability between AMD and NVIDIA GPU architectures | 65  |

|   | 4.6  | Conclu    | usions                                                                             | 77  |

| 5 | A Ba | ayesian   | model for reliability evaluation of CPU-based systems                              | 80  |

|   | 5.1  | Introd    | uction                                                                             | 81  |

|   | 5.2  | Reliab    | ility analysis                                                                     | 83  |

|   | 5.3  | Experi    | mental results                                                                     | 89  |

|   |      | 5.3.1     | Framework implementation                                                           | 89  |

|   |      | 5.3.2     | Experiment setup                                                                   | 90  |

|   |      | 5.3.3     | Results                                                                            | 92  |

|   | 5.4  | Conclu    | usion                                                                              | 93  |

| 6 | Reli | ability ( | estimation of complex digital systems                                              | 95  |

|   | 6.1  | Introd    | uction                                                                             | 96  |

|   | 6.2  | Relate    | d works                                                                            | 98  |

|   |      | 6.2.1     | Architectural level reliability analysis                                           | 98  |

|   |      | 6.2.2     | Accounting for software effects in reliability analysis                            | 98  |

|   |      | 6.2.3     | Bayesian models for reliability estimation                                         | 99  |

|   | 6.3  | The pr    | oposed system level reliability framework                                          | 100 |

|   |      | 6.3.1     | Qualitative model of the system                                                    | 101 |

|   |      | 6.3.2     | Quantitative model of the system                                                   | 104 |

|   |      | 6.3.3     | Reasoning on the model of the system                                               | 108 |

|   | 6.4  | Integra   | ated tools framework                                                               | 109 |

|   |      | 6.4.1     | Technology Domain                                                                  | 109 |

|   |      | 6.4.2     | Hardware Domain                                                                    | 111 |

| Ap | pend  | ix A T    | he SER of future devices               | 175 |

|----|-------|-----------|----------------------------------------|-----|

| Re | feren | ces       |                                        | 160 |

| 8  | Con   | clusions  |                                        | 159 |

|    | 7.5   | Conclu    | sion                                   | 156 |

|    |       | 7.4.3     | From benchmarks to real applications   | 155 |

|    |       | 7.4.2     | Results and discussion                 | 151 |

|    |       | 7.4.1     | Experimental setup                     | 149 |

|    | 7.4   | Experin   | mental Results                         | 149 |

|    |       | 7.3.3     | Optimization algorithm                 | 144 |

|    |       | 7.3.2     | Definitions and notation               | 143 |

|    |       | 7.3.1     | Extremal optimization theory           | 142 |

|    | 7.3   | System    | optimization methodology               | 142 |

|    | 7.2   | System    | level modeling                         | 139 |

|    | 7.1   | Introdu   | ction                                  | 138 |

| 7  | Relia | ability o | ptimization of complex digital systems | 137 |

|    | 6.6   | Conclu    | sions                                  | 135 |

|    |       | 6.5.3     | Experimental Results                   | 119 |

|    |       | 6.5.2     | The validation framework               | 115 |

|    |       | 6.5.1     | The experimental setup                 | 113 |

|    | 6.5   | Results   |                                        | 113 |

|    |       | 6.4.4     | System Domain                          | 112 |

|    |       | 6.4.3     | Software Domain                        | 112 |

|    |       |           |                                        |     |

# **List of Figures**

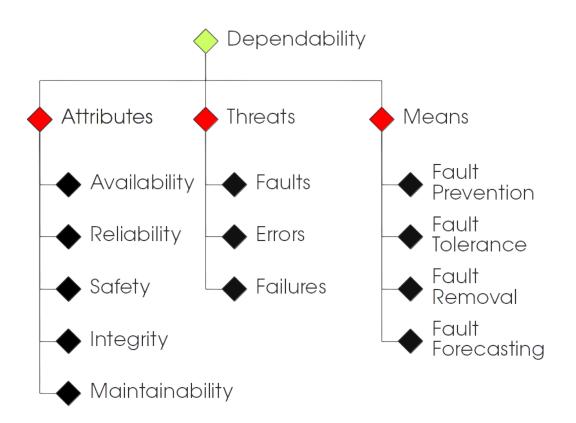

| 2.1 | All the aspects of dependability.                                                                                                                                                                                                                                            | 13 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

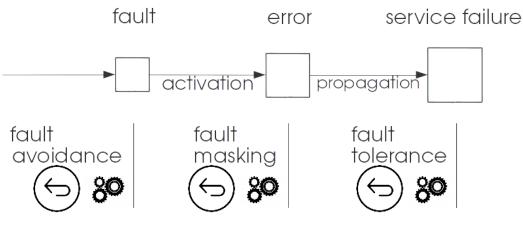

| 2.2 | The chain of dependability threats.                                                                                                                                                                                                                                          | 18 |

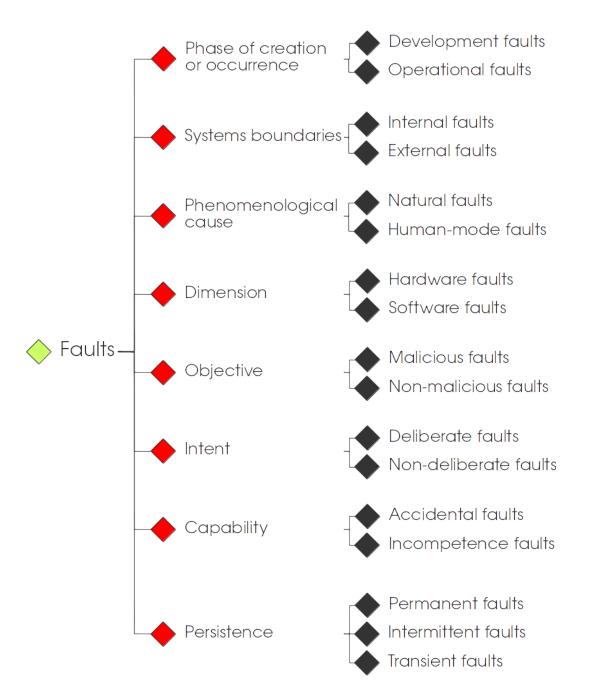

| 2.3 | Classification of faults.                                                                                                                                                                                                                                                    | 19 |

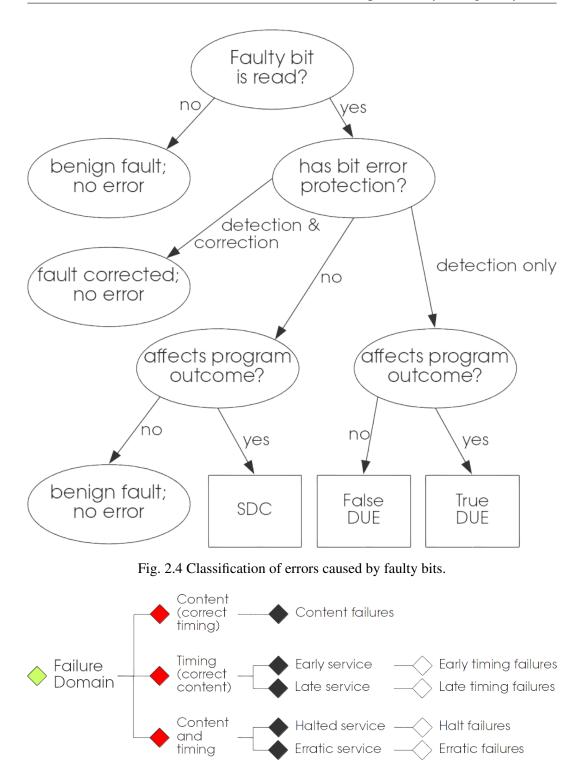

| 2.4 | Classification of errors caused by faulty bits                                                                                                                                                                                                                               | 22 |

| 2.5 | Failure modes of computing systems.                                                                                                                                                                                                                                          | 22 |

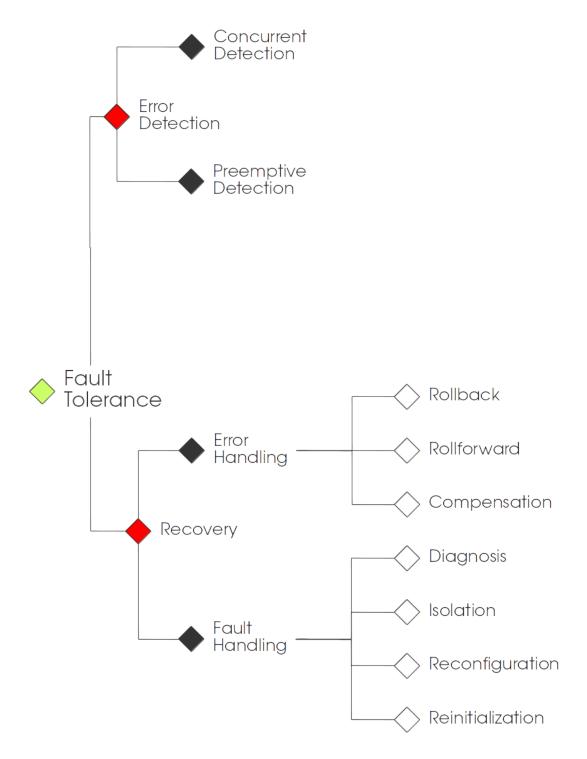

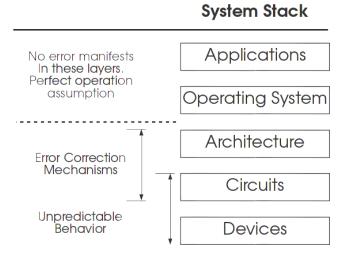

| 2.6 | The dependability enhancing mechanisms                                                                                                                                                                                                                                       | 27 |

| 2.7 | The conventional approach to enhance reliability usually targets one                                                                                                                                                                                                         |    |

|     | or two layers of the system.                                                                                                                                                                                                                                                 | 28 |

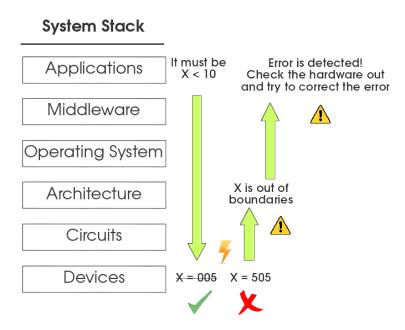

| 2.8 | Cross-layer information sharing and cooperation.                                                                                                                                                                                                                             | 31 |

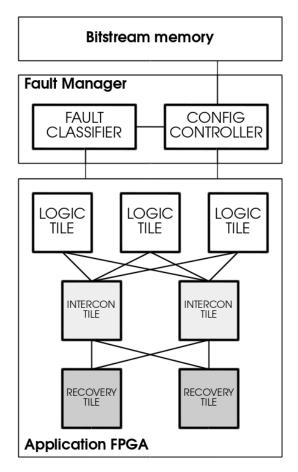

| 3.1 | The proposed system architecture (Source: [1])                                                                                                                                                                                                                               | 38 |

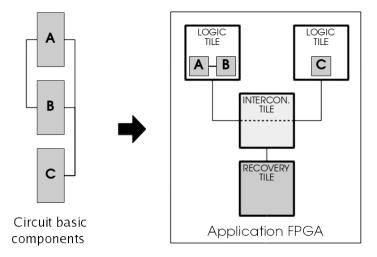

| 3.2 | Circuit basic components and tiles organization (Source: [1])                                                                                                                                                                                                                | 39 |

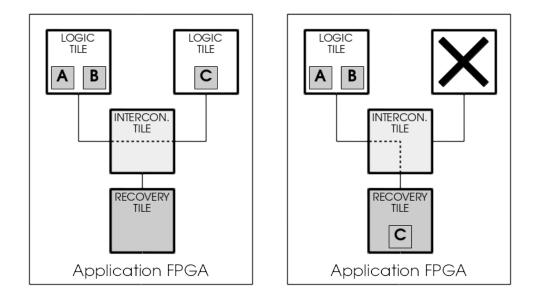

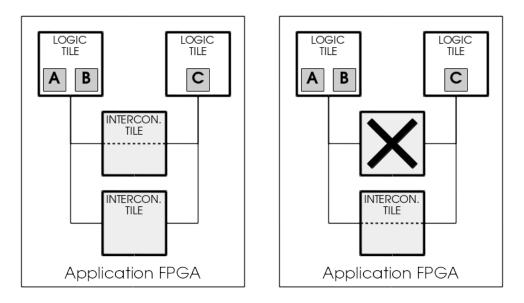

| 3.3 | The recovery strategies when a permanent faults occur. Fig 3.3a illustrates the relocation of the faulty logic tile into a recovery tile and the reconfiguration of the interconnection tile. Fig 3.3d shows how interconnections are reconfigured when a permanent fault is |    |

|     | detected inside the active interconnection tile (Source: [1])                                                                                                                                                                                                                | 42 |

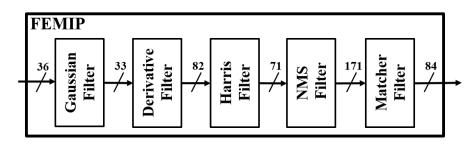

| 3.4 | FEMIP basic components (Source: [1])                                                                                                                                                                                                                                         | 45 |

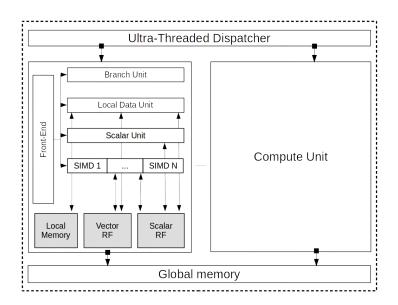

| 4.1 | Southern Islands AMD architecture.                                                                                                                                                                                                                                           | 53 |

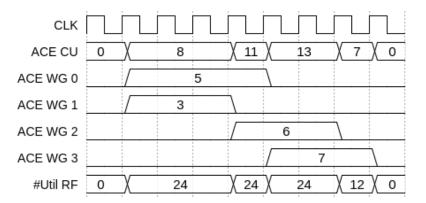

| 4.2  | An example of $ACE_{CU}$ timing diagram for a single CU. Considering $\#V_{RF} = 32$ and $\#kclk = 7$ , then $AVF = \frac{\frac{8+8+8+11+13+13+7}{32}}{7} = 0.3$ . If                                                                                           |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $#v_{wg} = 12 \text{ then } AVF_{Util} = \frac{\frac{8}{24} + \frac{8}{24} + \frac{8}{24} + \frac{11}{24} + \frac{13}{24} + \frac{13}{24} + \frac{7}{12}}{7} = 0.45 \dots \dots$                                                                                | 58 |

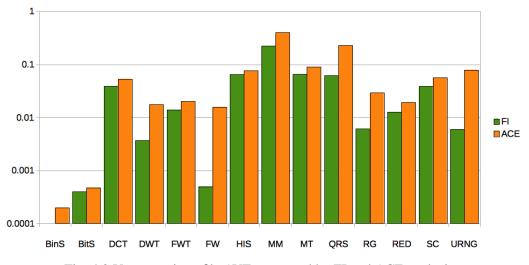

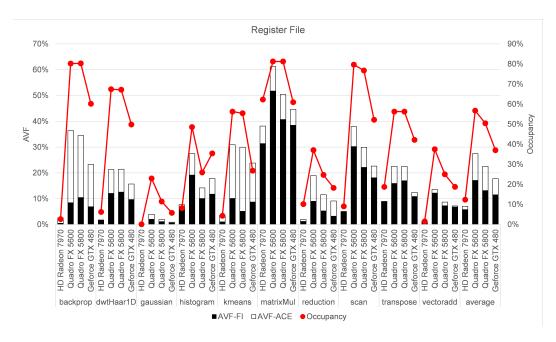

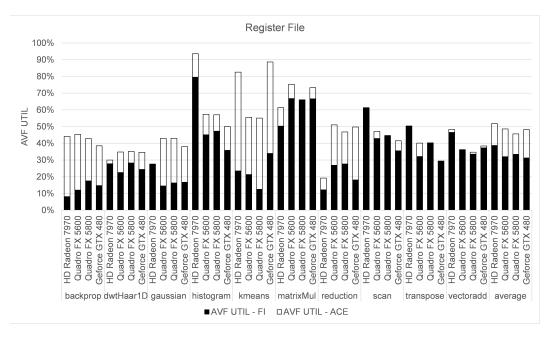

| 4.3  | Vector register file AVF computed by FI and ACE analysis                                                                                                                                                                                                        | 61 |

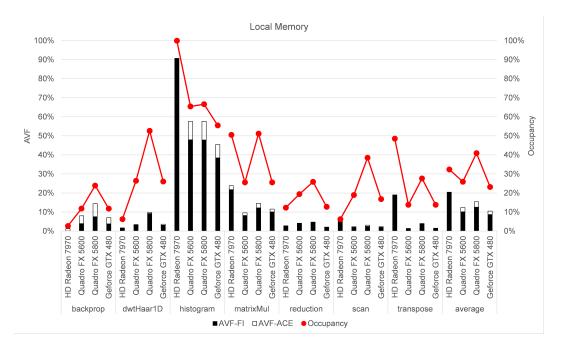

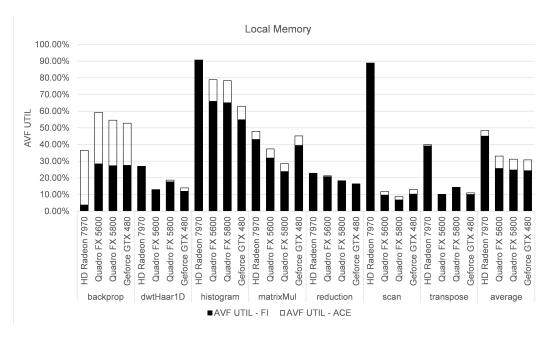

| 4.4  | Local memory AVF computed by FI and ACE analysis. The AVF is reported just for benchmarks using local memory.                                                                                                                                                   | 61 |

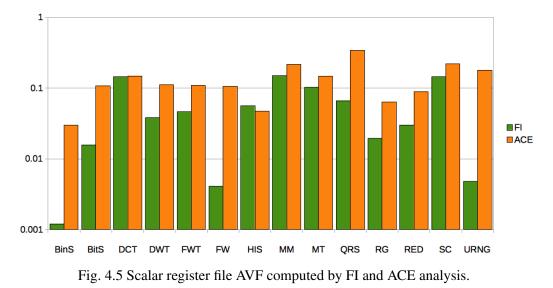

| 4.5  | Scalar register file AVF computed by FI and ACE analysis                                                                                                                                                                                                        | 62 |

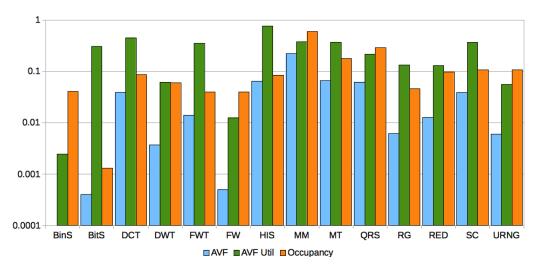

| 4.6  | The correlation between occupancy and AVF of the vector register file. The AVF Util is computed in order to decouple vulnerability and occupancy.                                                                                                               | 62 |

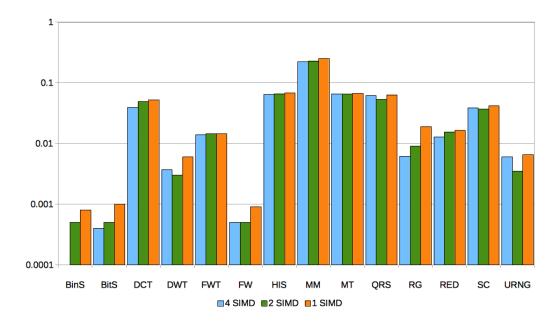

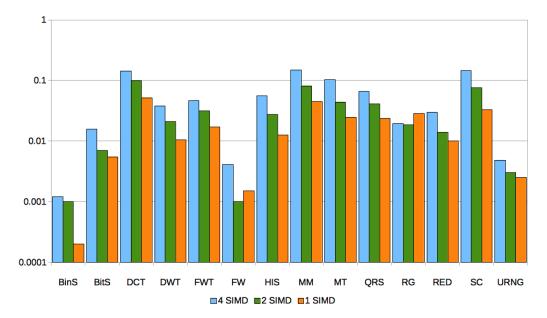

| 4.7  | Vulnerability comparison of vector register file changing the number of SIMD Units per CU.                                                                                                                                                                      | 64 |

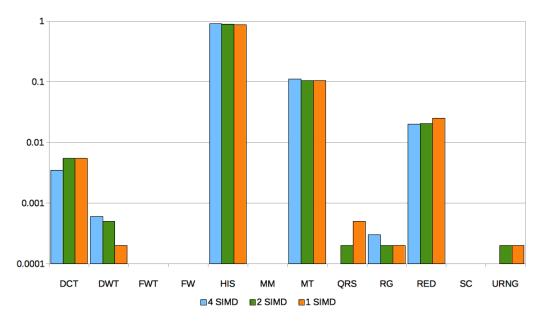

| 4.8  | Vulnerability comparison of local memory changing the number ofSIMD Units per CU.                                                                                                                                                                               | 64 |

| 4.9  | Vulnerability comparison of scalar register file changing the number of SIMD Units per CU.                                                                                                                                                                      | 65 |

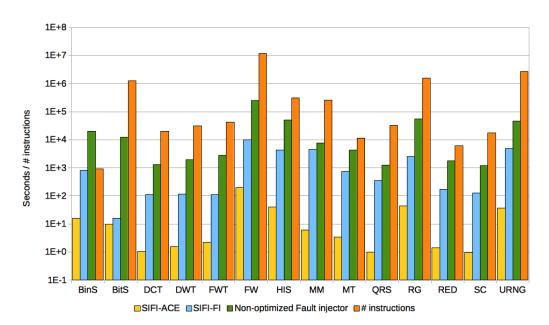

| 4.10 | SIFI timing performance. For each benchmark the figure reports the time required to estimate the vector register file AVF using ACE analysis, FI and non-optimized FI (10,000 injections using 8 cores) alongside the number of GPU instructions per simulation | 66 |

| 4.11 | AVF for Register File measured by FI and ACE analysis (Source: [2]).                                                                                                                                                                                            | 68 |

| 4.12 | AVF for Local Memory measured by FI and ACE analysis (Source:                                                                                                                                                                                                   |    |

|      | [2])                                                                                                                                                                                                                                                            | 69 |

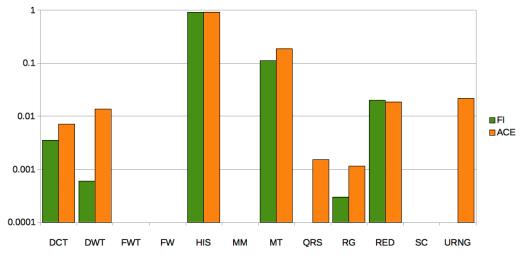

| 4.13 | AVF Util for Register File measured by FI and ACE analysis                                                                                                                                                                                                      | 70 |

| 4.14 | AVF Util for Local Memory measured by FI and ACE analysis                                                                                                                                                                                                       | 71 |

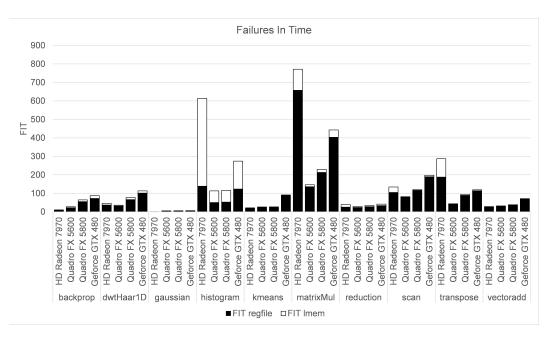

| 4.15 | Breakdown of Failures in Time rate using the AVF measurements from Fault Injection.                                                                                                                                                                             | 74 |

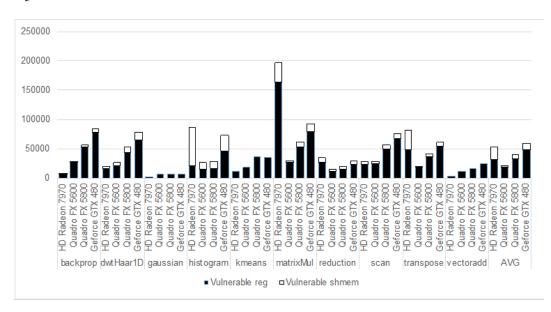

| 4.16 | Vulnerable resources in bits.                                                                                                                                                                                                                                   | 74 |

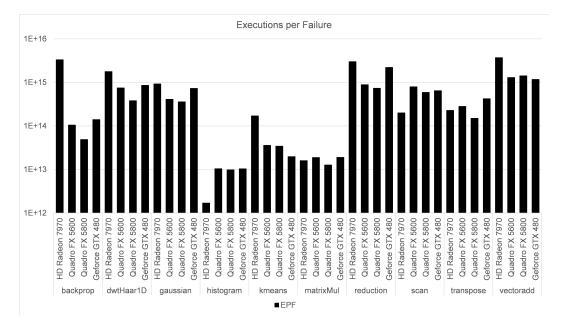

| 4.17 | Executions per Failure (EPF) (Source: [2]).                                                                                                                                                                                                                     | 75 |

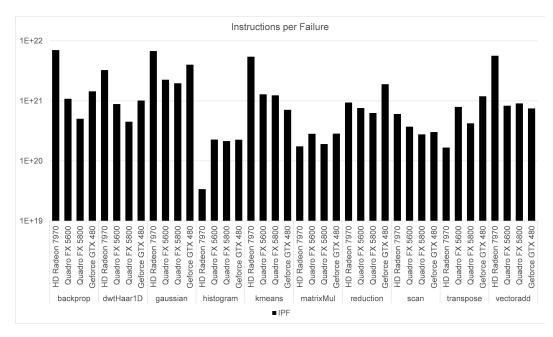

| 4.18 | Instructions per Failure (IPF)                                                                                                                                                                                                                                  | 77 |

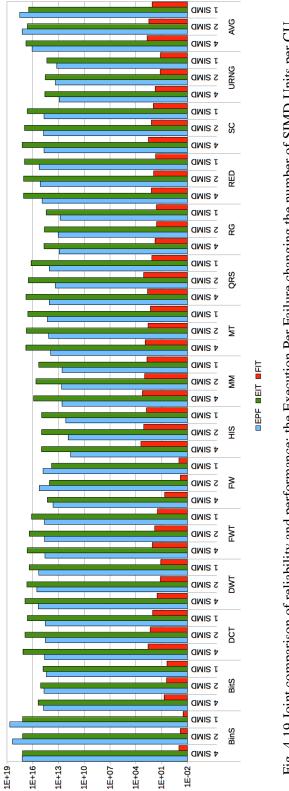

| 4.19 | Joint comparison of reliability and performance: the Execution Per<br>Failure changing the number of SIMD Units per CU                                                                                                                                                                                                                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

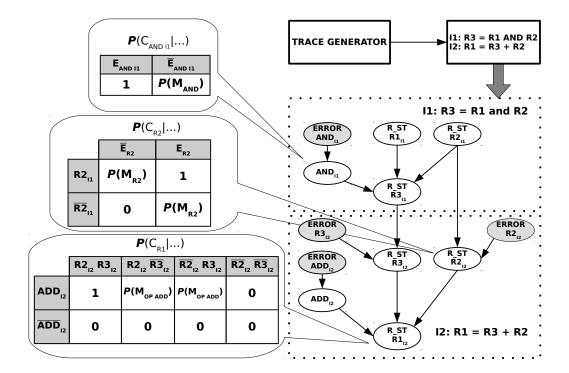

| 5.1  | Example of a bayesian network model for a simple sequence of two instructions (Source: [3])                                                                                                                                                                                                                                                                                                                                                                 |

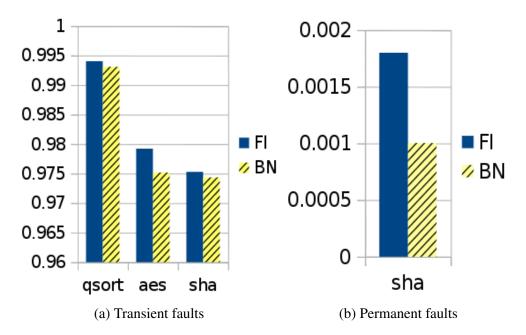

| 5.2  | Estimations of masking probability for both the Bayesian Network<br>and the Fault Injection approaches (Source: [3])                                                                                                                                                                                                                                                                                                                                        |

| 5.3  | Timing performance comparison of simulation time of a single trace<br>for both the Bayesian Network and the Fault Injection approaches.<br>Time is expressed in seconds (Source: [3])                                                                                                                                                                                                                                                                       |

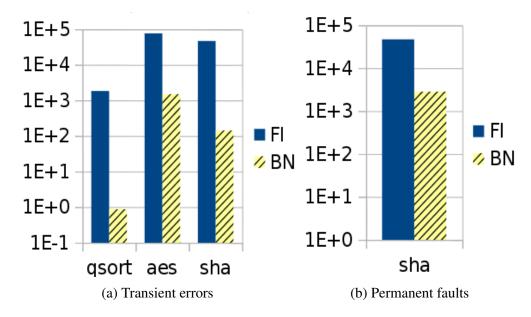

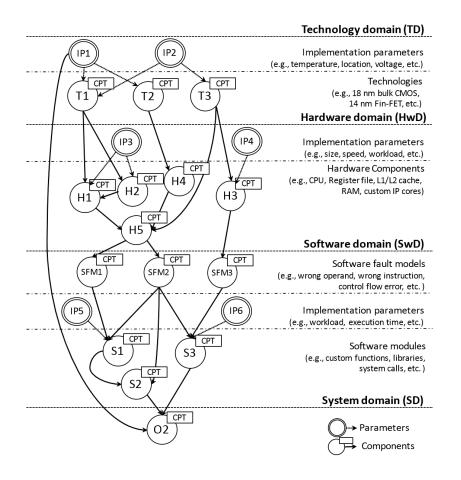

| 6.1  | The system stack: faults originate at the lower layer of the system stack and are either masked or propagated to the upper layer possibly resulting in a failure at system level (Source: [4])                                                                                                                                                                                                                                                              |

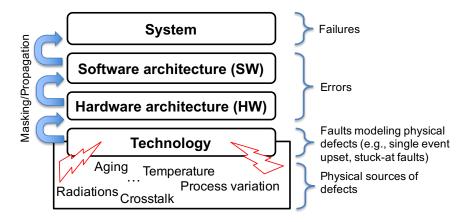

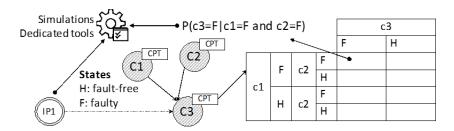

| 6.2  | System reliability estimation model. System components are mod-<br>eled by component nodes. The topology of the network provides<br>the qualitative description of the system. Conditional probability<br>tables (CPT) associated to each component node of the network<br>provide the quantitative description of the reliability of the system.<br>Parameter nodes model information required to compute the CPTs<br>of the component nodes (Source: [4]) |

| 6.3  | Example of CPT for node c3 (Source: [4])                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.4  | The error propagation policy from parents to child                                                                                                                                                                                                                                                                                                                                                                                                          |

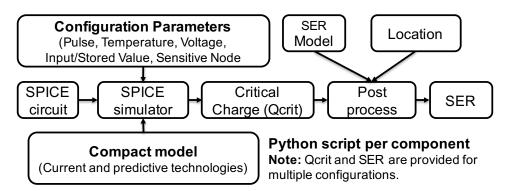

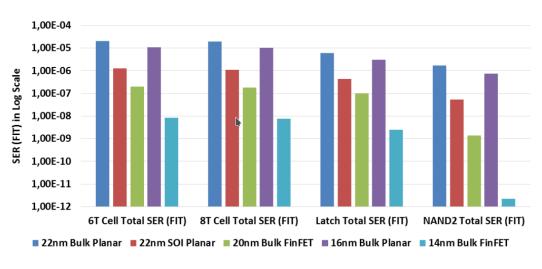

| 6.5  | Building blocks and technologies analyzed (Source: [4]) 110                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.6  | Technology Domain characterization workflow (Source: [4]) 110                                                                                                                                                                                                                                                                                                                                                                                               |

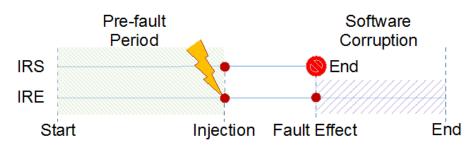

| 6.7  | IRE and IRS modes of GeFIN operation (Source: [4])                                                                                                                                                                                                                                                                                                                                                                                                          |

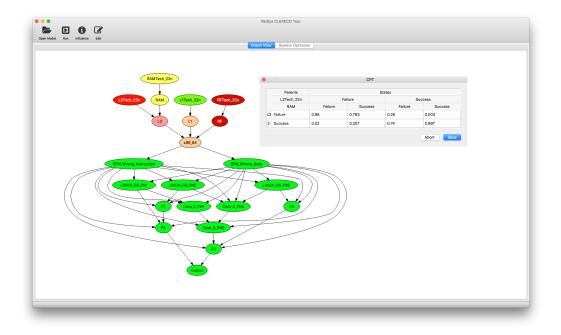

| 6.8  | System level reliability analyzer interface (Source: [4])                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.9  | Overview of the simulation and validation campaign                                                                                                                                                                                                                                                                                                                                                                                                          |

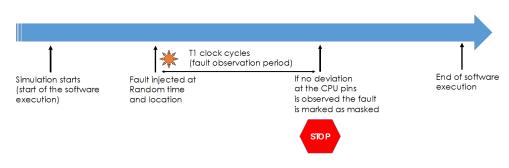

| 6.10 | RTRA-COP Injection timeline                                                                                                                                                                                                                                                                                                                                                                                                                                 |

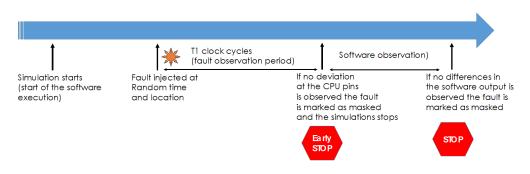

| 6.11 | RTRA-SOP Injection timeline                                                                                                                                                                                                                                                                                                                                                                                                                                 |

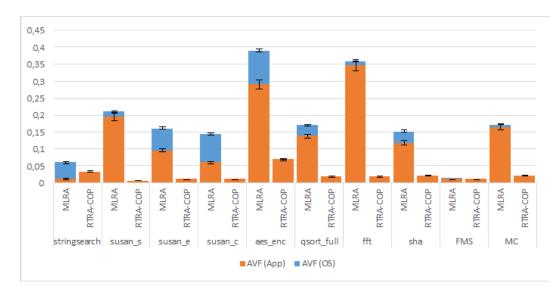

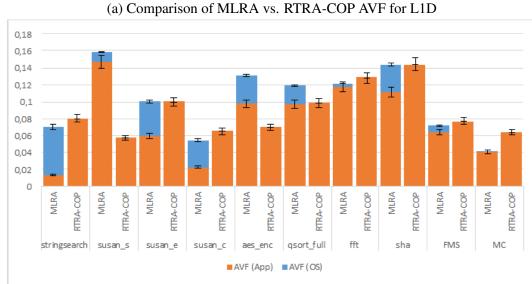

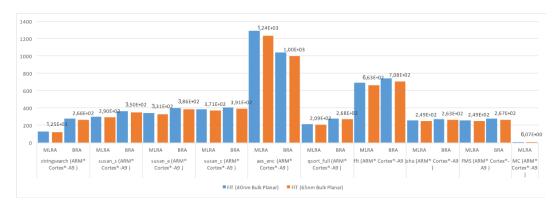

| 6.12 | Comparison of MLRA vs. RTRA-COP AVF estimation with 5% error margin and 99% confidence level. All benchmarks are executed on ARM Cortex <sup>®</sup> -A9 microprocessor models at the microarchitecture level (MLRA) and the RTL level (RTRA-COP)                                                                                                                                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

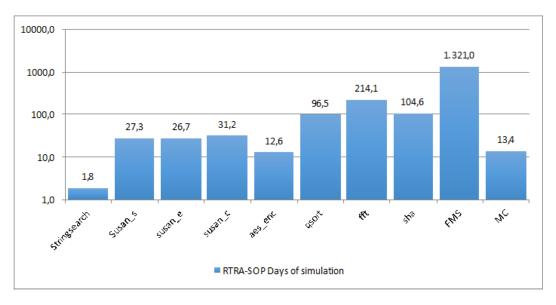

| 6.13 | CPU time in days of simulation to perform 680 injections for L1D<br>and 680 injections for RF using RTRA-SOP with T1 timer equal to<br>the duration of the program. Simulation time is provided in Days of<br>simulation using a logarithmic scale                                                                                                                                                                                                                      |

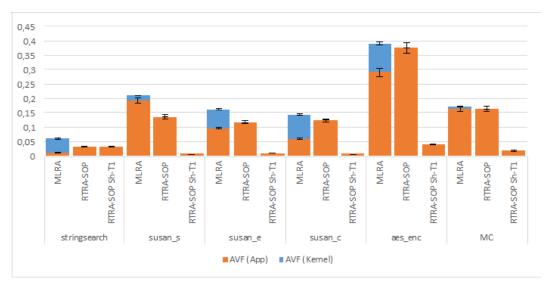

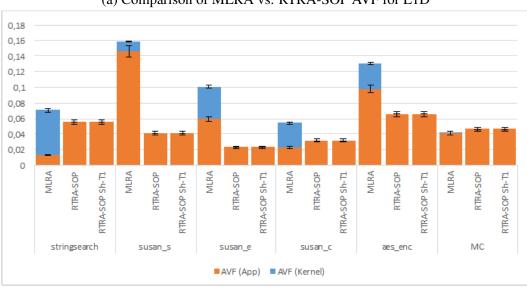

| 6.14 | Comparison of MLRA vs RTRA-SOP AVF esitmation. All bench-<br>marks are executed on the ARM Cortex <sup>®</sup> -A9 microprocessor RTRA-<br>SOP and RTRA-SOP sh-T1. In RTRA-SOP the T1 time is set to the<br>duration of the application, therefore all faults are simulated until<br>the end of the program execution. In RTRA-SOP sh-T1 only faults<br>that create differences at the CPU outputs in T1 clock cycles are<br>simulated until the end of the application |

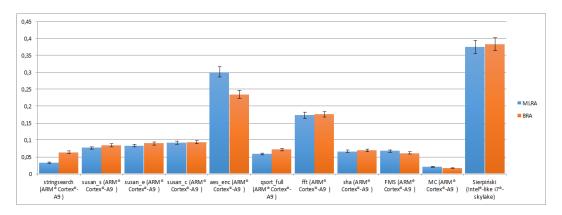

| 6.15 | AVF estimation comparison between MLRA and BRA. This is a full system AVF including contribution of RF, L1D, L1I, L2 and SQ 125                                                                                                                                                                                                                                                                                                                                         |

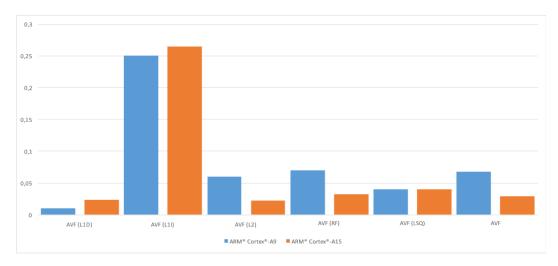

| 6.16 | Comparison of the AVF for two different ARM architectures running FMS: ARM Cortex <sup>®</sup> -A9 and ARM Cortex <sup>®</sup> -A15                                                                                                                                                                                                                                                                                                                                     |

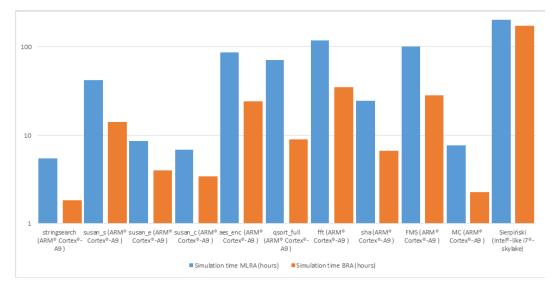

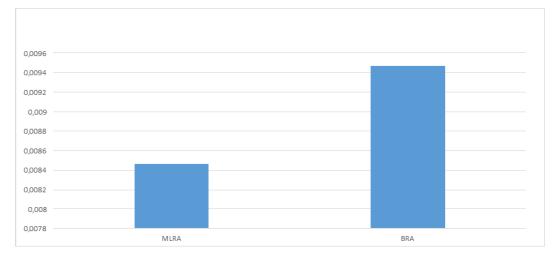

| 6.17 | Simulation time comparison between MLRA and BRA. Simulation time is provided in hours of simulation using a logarithmic scale 127                                                                                                                                                                                                                                                                                                                                       |

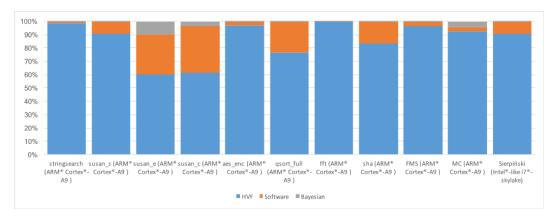

| 6.18 | Complexity distribution between the different layer                                                                                                                                                                                                                                                                                                                                                                                                                     |

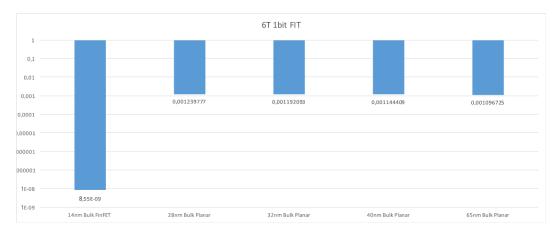

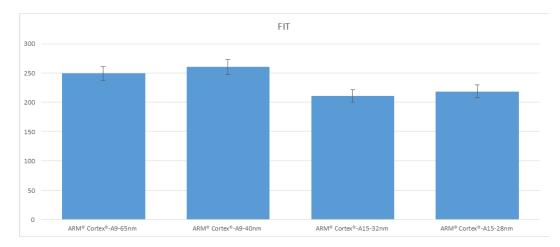

| 6.19 | 6T SRAM FIT/bit for the five fabrication technologies used in the considered microprocessor architectures                                                                                                                                                                                                                                                                                                                                                               |

| 6.20 | FIT rate for the applications executed on the ARM®Cortex®-A9 under two different technology nodes                                                                                                                                                                                                                                                                                                                                                                       |

| 6.21 | FIT rate for the Sierpinski application executed on the Intel <sup>®</sup> -like i7-skylake 14nm Bulk FinFET technology node                                                                                                                                                                                                                                                                                                                                            |

| 6.22 | Comparison of the FIT rate for FMS considering different micropro-<br>cessor architectures fabricated using different technology nodes 131                                                                                                                                                                                                                                                                                                                              |

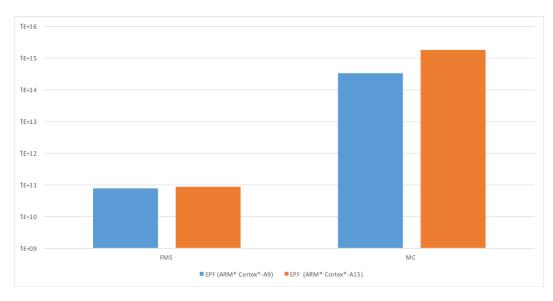

| 6.23 | EPF computed for FMS and MC on two different ARM architectures:<br>ARM Cortex <sup>®</sup> -A9 implemented with 65nm Bulk Planar CMOS<br>clocked at 800-MHz and ARM Cortex <sup>®</sup> -A15 implemented with<br>28nm Bulk Planar CMOS clocked at 2.5GHz. Results are plotted in<br>a logarithmic scale                                                                                                                                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

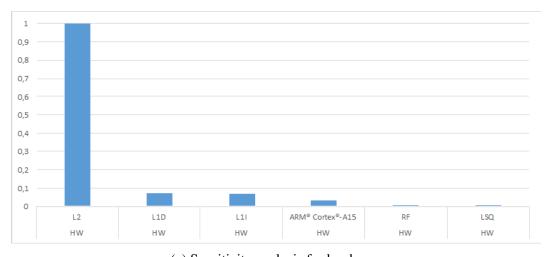

| 6.24 | Sensitivity analysis performed for FMS running on the ARM Cortex <sup>®</sup> -<br>A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

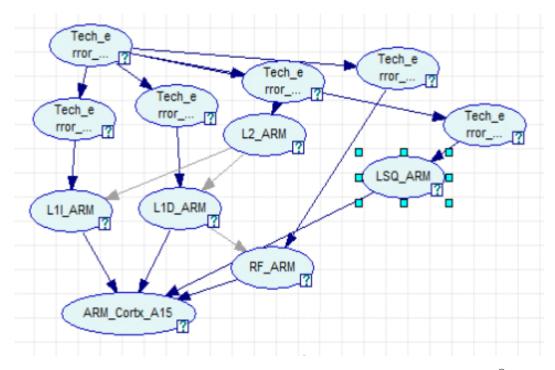

| 6.25 | Snapshot of Bayesian model of the hardware portion of the ARM Cortex <sup>®</sup> -A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

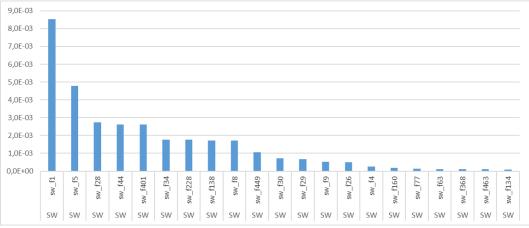

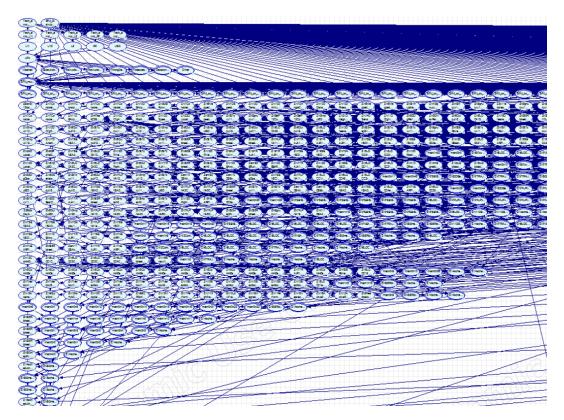

| 6.26 | Snapshot of the full FMS Bayesian model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

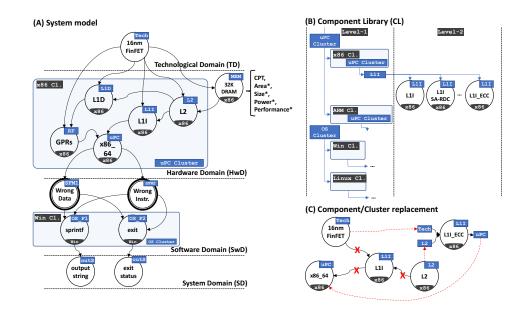

| 7.1  | System modeling. (A) <i>Bayesian model of the systems</i> : nodes are organized into domains and each node is characterized by a Conditional Probability Table (CP) plus a set of optional parameters (e.g., are, size, power, performance) that can be used during the optimization process, (B) <i>design alternatives</i> : for each component (node) or cluster of components different implementations are defined, thus forming a library of design alternatives, (C) <i>component replacement</i> showing how a component can be replaced with a different implementation in the model |

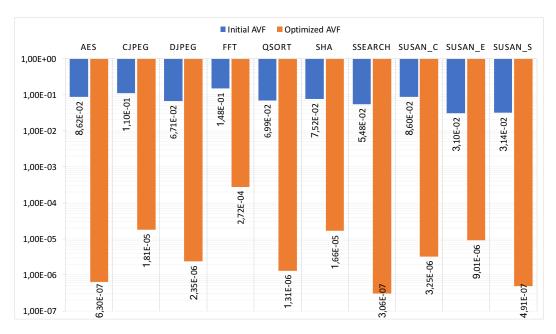

| 7.2  | AVF improvement (log scale) when optimizing for best reliability. $.152$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

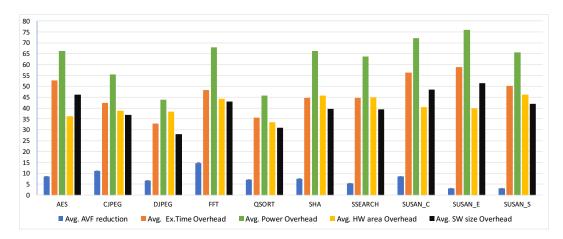

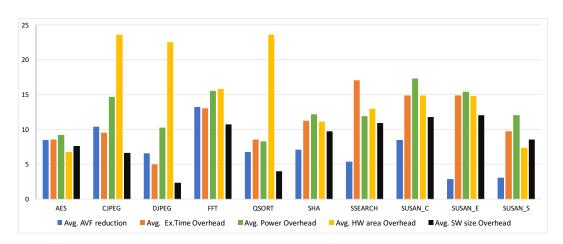

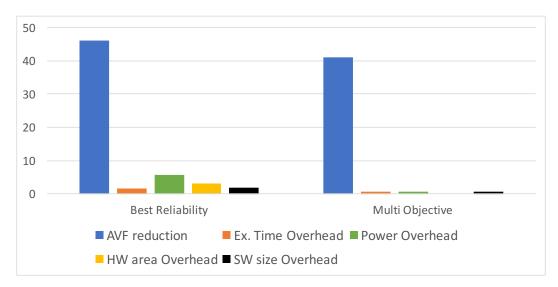

| 7.3  | Percentage improvement for all design dimensions when optimizing for best reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

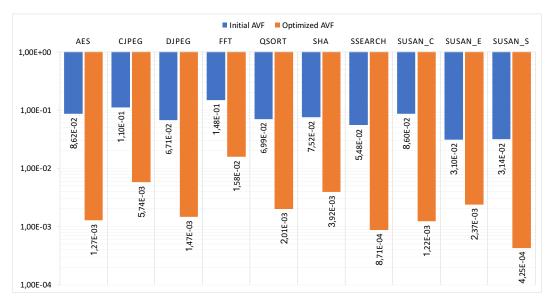

| 7.4  | AVF improvement (log scale) when optimizing for multiple objectives.153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.5  | Percentage improvement for all design dimensions when when opti-<br>mizing for multiple objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

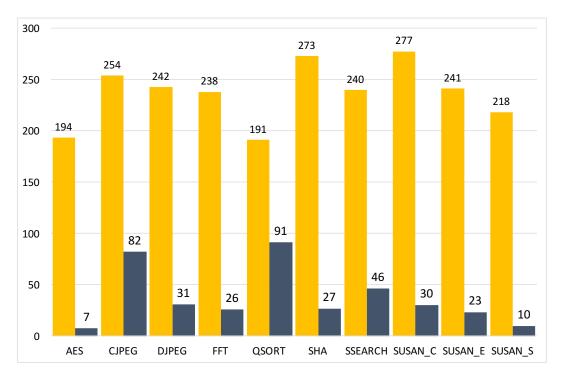

| 7.6  | Number of iterations before best solutions (500 iterations were simulated): optimization for best reliability (yellow bars) vs. optimization for multiple objectives (dark blue bars)                                                                                                                                                                                                                                                                                                                                                                                                         |

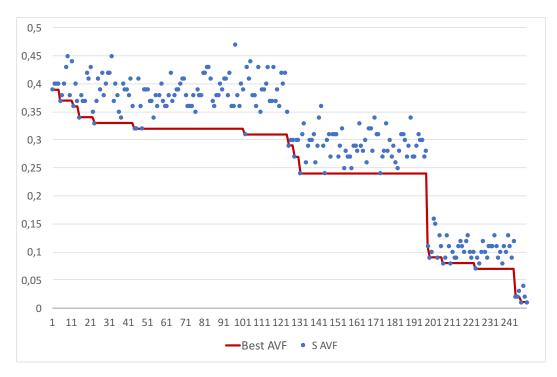

| 7.7  | AVF trajectory when optimizing the Sierpinski framework for best reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

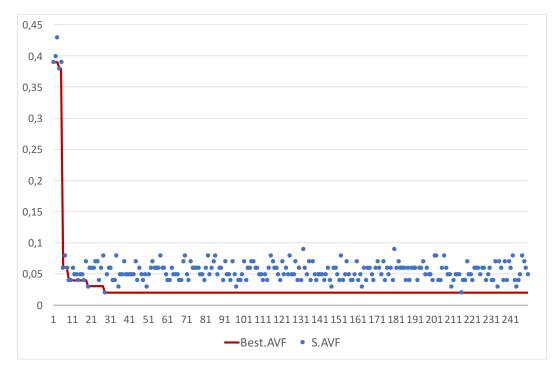

| 7.8 | AVF trajectory when optimizing the Sierpinski framework for multi-<br>ple objectives                                                |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| 7.9 | Percentage improvement for all design dimensions when optimizing the Sierpinski framework using the two optimization strategies 157 |

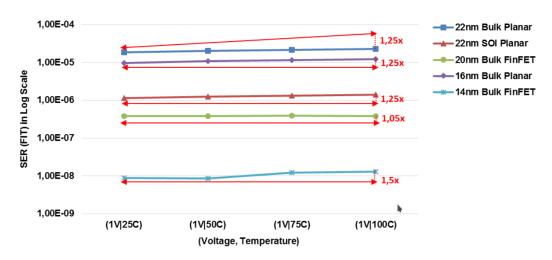

| A.1 | Technology comparison                                                                                                               |

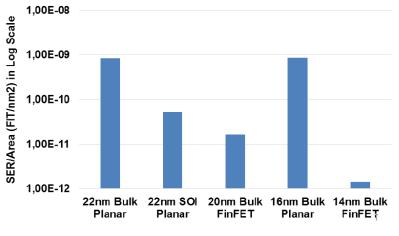

| A.2 | SERArea for a 6T SRAM cell                                                                                                          |

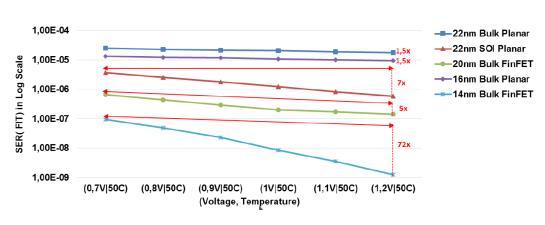

| A.3 | SER changing the voltage of a 6T SRAM cell                                                                                          |

| A.4 | SER changing the temperature of a 6T SRAM cell                                                                                      |

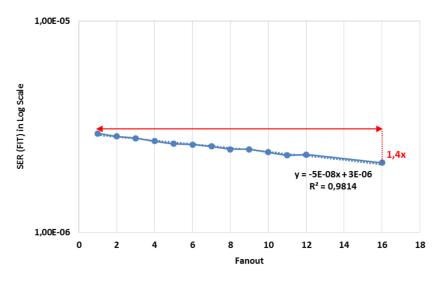

| A.5 | SER changing the fanout of a NOT logic gate                                                                                         |

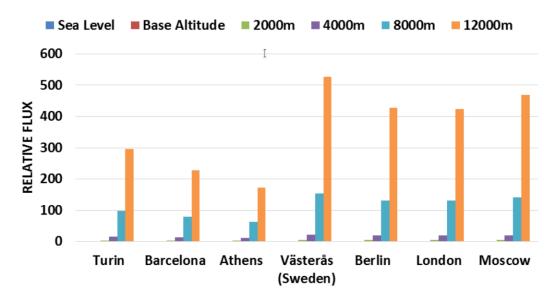

| A.6 | Relative neutron fluxes of different locations                                                                                      |

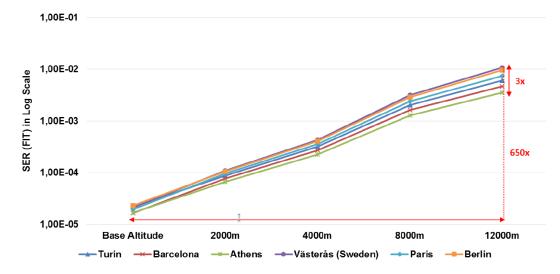

| A.7 | SERs depending on the Location and Altitude of a 6T SRAM Cell                                                                       |

|     | in 22nm Bulk Planar                                                                                                                 |

# **List of Tables**

| 3.1 | Resources requirements for <i>FEMIP</i> basic components                                                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Resources requirements for FEMIP tiles                                                                                                     |

| 3.3 | Resources requirements for H.264 video encoder tiles                                                                                       |

| 4.1 | CU details of the target GPU architecture                                                                                                  |

| 4.2 | Simulation time required to perform the reliability analysis 73                                                                            |

| 4.3 | Execution time and instructions of each benchmark                                                                                          |

| 5.1 | Marssx86-64 microprocessor model configuration                                                                                             |

| 6.1 | Example of SFMs taxonomy                                                                                                                   |

| 6.2 | Software Faulty Behavior Classifications                                                                                                   |

| 6.3 | Microprocessor architectures details                                                                                                       |

| 6.4 | Hardware configuration for the three considered microprocessor<br>architectures. It reports the size (#bits) of the main arrays considered |

|     | in the analysis                                                                                                                            |

| 6.5 | Complexity of the Bayesian Model required for BRA                                                                                          |

| 7.1 | Hardware fault tolerance techniques                                                                                                        |

| 7.2 | Software implemented fault tolerance techniques                                                                                            |

# Nomenclature

#### **Acronyms / Abbreviations**

- ACE Architectural Correct Execution

- AFTS Autonomous Fault-Tolerant Systems

- ASIC Application Specific Integrated Circuits

- AVF Architectural Vulnerability Factor

- *BN* Bayesian Network

- BRA Bayesian Reliability Analysis

- *CL* Component Library

- CPT Conditional Probability Table

- CPU Central Processing Unit

- CU Compute Unit

- DPR Dynamic Partial Reconfiguration

- DUE Detectable Unrecoverable Error

- EO Extremal Optimization

- *EPF* Execution Per Failure

- ES Embedded Systems

- FI Fault Injection

- FPGA Field Programmable Gate Array

- GPGPU General Purpose computing on Graphics Processing Units

- GPU Graphics Processing Unit

- HPC High Performance Computing

- HwD Hardware Domain

- *IPF* Instructions Per Failure

- IPH Injections Per Hour

- *IRE* Injection Runs up to the End

- *IRS* Injection Runs up to the Software level

- ISA Instruction Set Architecture

- MBU Multiple Bit Upset

- MLRA Microarchitectural Level Reliability Analysis

- OS Operating System

- PDF Probability Density Function

- RTL Register Transfer Level

- RTRA Register Transfer Reliability Analysis

- RTRA-COP RTRA CPU Observation Points

- RTRA-COP RTRA Software Observation Points

- SD System Domain

- SDC Silent Data Corruption

- SER Soft Error Rate

- SEU Single Event Upset

- SFB Software Faulty Behavior

| SFM  | Software Fault Model             |

|------|----------------------------------|

| SIMD | Single Instruction Multiple Data |

| SM   | Software Module                  |

| SUE  | System Under Evaluation          |

| SwD  | Software Domain                  |

| TD   | Technology Domain                |

| TMR  | Triple Modular Redundancy        |

TTM Time To Market

# About the author

Alessandro Vallero received his Bachelor of Science and Master of Science degree in Electronics Engineering from Politecnico di Torino (Italy), respectively, in 2008 and 2013. He also received his Master of Science in Electrical and Computer Engineering from University of Illinois at Chicago (US) in 2014.

Alessandro started his PhD in January 2013. His major interests are reliability analysis of digital systems and reconfigurable computing. During the PhD activity he contributed actively to the CLERECO

FP7 European project. Moreover he received a HiPEAC Collaboration grants to visit University of Athens (Greece) and collaborate to the development of reliability analaysis techniques for general purpose computing on GPUs.

## List of publications

This is the list of the papers that Alessandro published during its Ph.D.:

Di Carlo S.; Gambardella G.; Prinetto P.; Rolfo D.; Trotta P.; Vallero A. "A novel methodology to increase fault tolerance in autonomous FPGA-based systems", IEEE 20th International On-Line Testing Symposium (IOLTS), Platja d'Aro, Girona (ES), 7-9 July 2014. pp. 87-92.

- Di Carlo, S.; Vallero, A.; Gizopoulos, D.; Di Natale, G.; Gonzalez, A.; Canal, R.; Mariani, R.; Pipponzi, M.; Grasset, A.; Bonnot, F.; Reichenbach, F.; Rafiq, G.; Loekstad T. "Cross-layer early reliability evaluation: Challenges and promise", IEEE 20th International On-Line Testing Symposium (IOLTS), Platja d'Aro, Girona (ES), 7-9 July 2014. pp. 228-233.

- Di Carlo, S.; Vallero, A.; Gizopoulos, D.; Di Natale, G.; Grasset, A.; Mariani, R.; Reichenbach, F. "Cross-Layer Early Reliability Evaluation for the Computing cOntinuum", 17th Euromicro Conference on Digital System Design (DSD), Verona, IT, 27-29 Aug. 2014. pp. 199-205.

- Alessandro VALLERO, Alessandro SAVINO, Gianfranco POLITANO, Stefano DI CARLO (Politecnico di Torino - Italy), Sotiris TSELONIS, Nikos FOUTRIS, Manolis KALIORAKIS, Dimitris GIZOPOULOS (University of Athens - Greece), "A bayesian model for system level reliability estimation", 20th IEEE European Test Symposium.

- A.Vallero, A.Savino (Politecnico di Torino), S.Tselonis, N.Foutris, M.Kaliorakis (University of Athens), G.Politano (Politecnico di Torino), D.Gizopoulos (University of Athens), S.Di Carlo (Politecnico di Torino), "Bayesian Network Early Reliability Evaluation Analysis for both Permanent and Transient Faults", 21st IEEE International On-Line Testing Symposium.

- A.Vallero, S.Tselonis, N.Foutris, M.Kaliorakis, M. Kooli, A.Savino, G.Politano, A.Bosio, G. Di Natale, D.Gizopoulos, S.Di Carlo, "Cross-Layer Reliability Evaluation, moving from the Hardware Architecture to the System level: a CLERECO EU Project overview", Microprocessors and Microsystems, 2015.

- Vallero, A.; Savino, A.; Politano, G.; Di Carlo, S.; Chatzidimitriou, A.; Tselonis, S.; Kaliorakis, M.; Gizopoulos, D.; Riera, M.; Canal, R.; Gonzalez, A.; Kooli, M.; Bosio, A.; Di Natale, G. "Early Component-Based System Reliability Analysis for Approximate Computing Systems" 2nd Workshop On Approximate Computing (WAPCO), Prague, CZ, 20 Jan. 2016.

- A. Savino; S. Di Carlo; A. Vallero; G. Politano; D. Gizopoulos; A. Evans, "RIIF-2: Toward the next generation reliability information interchange format", 2016 IEEE 22nd International Symposium on On-Line Testing and Robust System Design (IOLTS).

- A. Vallero, A. Savino, G. Politano, S. Di Carlo, A. Chatzidimitriou, S. Tselonis, M. Kaliorakis, D. Gizopoulos, M. Riera, R. Canal, A. Gonzalez, M. Kooli, A. Bosio, G. Di Natale, "Cross-Layer System Reliability Assessment Framework for Hardware Faults" IEEE International Test Conference (ITC), 2016.

- Alessandro Vallero, Sotiris Tselonis, Dimitris Gizopoulos, and Stefano Di Carlo, "Microarchitecture Level Reliability Comparison of Modern GPU Designs: first findings" Performance Analysis of Systems and Software (ISPASS), 2017 IEEE International Symposium on.

- Alessandro Vallero, Dimitris Gizopoulos, and Stefano Di Carlo, "SIFI: AMD Southern Islands GPU Microarchitectural Level Fault Injector" 2017 IEEE 23nd International Symposium on On-Line Testing and Robust System Design (IOLTS) IEEE, 2017.

# Chapter 1

# Introduction

## **1.1 Motivation**

Information technology is at the core of our society and it relies completely on the design of electronic information processing systems. Today's computing is a true continuum that ranges from smartphones to mission-critical datacenter machines, and from desktops to automobiles. On aggregate, these computing devices represent a total addressable market approaching a billion processors a year, which is expected to explode to more than two billion per year before 2020.

The computing industry move towards the *computing continuum* means that the same key technologies and industrial players will act across all computing segments: airplanes, automobile, buildings, health instruments, smartphones, tablets, desktops, servers, datacenters, clouds, high-performance computing (HPC), etc. Therefore, in the near future we will see embedded systems (ES) with HPC performance and functionalities, HPC systems used in time and safety critical applications, cloud resources used with very different business models, etc.

For more than three decades, industry has evolved by roughly doubling the device density (and corresponding performance) every two years following Moore's law. However, future device integration technology is expected to dramatically reduce the device quality, and therefore the operational reliability of circuits: as the transistors and wires shrink, they show both larger differences in behavior although they are designed to be identical (device variability, manufacturing defects, aging), and higher susceptibility to transient and permanent faults (soft errors, wear-out). The great challenge for future technologies is building "dependable" systems on top of unreliable components, which will degrade and even fail during normal lifetime of the chip. Dependability is however not a quantitative term which is instead quantified by *reliability* (i.e., continuity of correct service), *availability* (i.e., readiness for correct service), *safety* (absence of catastrophic consequences on the user(s) and the environment), *maintainability* (i.e., ability to undergo modifications and repair). Reliability is the most often used concept in the industry and academia. Therefore, without loss of generality, the word reliability will be employed for the rest of the thesis when referring to all concepts related to dependability.

First studies addressing reliability with an engineering approach date back to World War II and they were mainly devoted towards understanding the behavior of electronic devices in presence of radiation. Alongside the military field, reliability for digital circuits found application in the space domain as well as in medical fields where radiation are involved. In recent years, as technology has progressed, new reliability issues started to manifest in consumer devices. In fact, from one side there was a reduction of cost associated to the production of digital devices benefiting of the shrinking of circuits thanks to technological improvements; from the other side reliability problems arose due to the manufacturing process and the dramatic shrinking of the feature sizes.

In the industrial domain, nowadays, reliability is a fundamental aspect when a new system is designed, as it influence its cost and success on the market. Some techniques can be adopted to improve reliability of a digital circuit, but they come at a price: they increase manufacturing and engineering cost. Moreover they usually have a negative impact on performance, power consumption and area of the designed products. Conventional design techniques expend significant amount of energy to tolerate the device unpredictability by adding safety margins to a circuit's operating voltage, clock frequency or charge stored per bit. However, the rising energy cost needed to compensate for increasing unpredictability are rapidly becoming unacceptable in today's environment where power consumption is often the limiting factor for integrated circuit performance, and energy efficiency is a top concern.

On one hand, if reliability was not taken into account, the designed system would be very cheap despite a short lifetime. As a result, nobody would buy it, or, even worse, the system would not be suitable to be employed as it would not meet the reliability requirements. On the other hand, if reliability led to an over-designed system, a system with many reliability improvements, the lifetime of this product would be excellent. However, the associated cost would grow exponentially alongside the system performance degradation, making this product not competitive with the others. In some cases, a negative return of investment would be unavoidable because of over-design.

Much attention should be payed to tailor techniques for reliability improvements on the basis of system needs, ending up with a cost-effective system successful on the market. Finding the right balance among system reliability, cost and performance is not an easy task and it usually takes some time during the different stages of the design, thus increasing the time-to-market of the product and the possibility to have a negative return of investment.

Implementing systems belonging to the computing continuum in this era, where low reliability threatens to end the benefits of feature size reduction, requires a holistic approach across different computing disciplines, across computing system layers and across computing market segments to have a unique reliability assessment methodology. The main goal of this thesis is to propose a framework addressing the problem of having an early, fast, and accurate evaluation of computing systems reliability to support design decisions for hardware and software reliability enhancing mechanisms in the system. Such a framework will contribute to the continuation of technology scaling benefits harnessing for several decades. Moreover, it will also enable the implementation of the computing continuum that societal services demand.

Cross-layer reliability is one of the most promising approach to reliability, leveraging the many commonalities between different application domains and computing disciplines in the next generation computing continuum. This methodology aims at providing a reliability analysis despite differences among application domains and computing systems by identifying their common aspects. It takes into account the abstraction layers a system is composed of (i.e., technology, hardware and software layers) and addresses their interaction. Consequently, resorting to a cross-layer approach for reliability estimation enables the exploration and optimization of the design space (performance, portability, energy efficiency, dependability, real-time responsiveness) across different domains.

The benefits of an early and accurate methodology to estimate the reliability of a system are many. First, a tool that yields early estimate allows designers to reduce the

time-to-market (TTM) of all products, enabling the fast turnaround of proliferation of computing systems tailored to customers' needs. Nowadays, sometimes the system must be re-designed several times in order to satisfy the target constraints because of a worst-case approach, posing a serious threat to the success of the product. Second, accurate reliability estimates allow developing the required cost- and energy-efficient reliability solutions at the hardware and software layers. Such solutions can be only developed if the expected reliability of the system can be quickly and accurately assessed: (a) at different stages of the design flow (from design concept and early design stages through first silicon validation and eventually during operation in the field), (b) considering the impact of all hardware and software components, and the different modes of operation (use cases) of the system. In detail, cross-layer reliability allows to identify the most efficient protection mechanisms at different system layers (technology, hardware architecture, software), thus exploiting the inner capability of each layer to mask lower level faults. For this purpose, cross-layer reliability design techniques need to be complemented with cross-layer reliability evaluation tools, able to precisely assess the reliability level of a selected design early in the design cycle. Accurate and early reliability estimates enable the exploration of the system design space and the optimization of multiple constraints such as performance, power consumption, cost and reliability. Finally, the development of a reliable and dependable product that employs mechanisms to detect and handle possible faults can reduce the overall life cycle cost.

Finally, targeting the entire emerging computing continuum is an ambitious challenge since it requires methodologies and models to analyze reliability issues belonging to different application fields and considering different components of systems with different complexity. Technology, hardware components (e.g., CPUs, GPUs, DSP, memories, peripherals, accelerators, interconnects), and software (systems and application) from different domains are to be addressed.

#### **1.2 Goals**

Traditionally, reliability estimation performed at different stages of the design cycle can lead to "worst-case" decisions and over-designed systems. While the required system reliability can be guaranteed, the cost of the employed reliability mechanisms (in terms or area, energy/power, performance and money) and the design time re-

quired for their integration and evaluation are both excessive. Moreover, standard reliability evaluation approaches strongly rely on massive and time-consuming simulations and/or fault injection campaigns, which are becoming a bottleneck with the increasing complexity of computing systems.

The ultimate goal of my Ph.D. program is the development of new methodologies and tools to evaluate and to optimize the reliability of complex digital systems, in the context of a cross-layer reliability design. In this way, reliability of computing systems can be evaluated at each stage of the design cycle fast and accurately, providing designers with a valuable support for reliability related decision-making process. As a result, improved cost-related characteristics (area, energy/power, and performance) and reduced TTM are also enabled.

The detailed objective of my Ph.D. are:

- To analyze the reliability of the different hardware components at different levels of detail (depending on the design phase), emphasizing the role that the interaction between hardware and software plays in the overall reliability figure of the system.

- To design flexible, fast, and accurate reliability evaluation methodologies and tools for the computing continuum. Offering a more accurate reliability estimation allows to lead system designers to suitable decisions at intermediate design stages, thus effectively reducing the reliability cost and the TTM, consequently impacting the overall life-cycle cost.

- To comprehensively support the reliability decision-making process in computing systems exploiting the proposed reliability evaluation frameworks (methodologies and tools) that leads to meet the reliability constraints of the system avoiding over-design.

- To validate and evaluate in detail the effectiveness of the proposed frameworks in real-world systems belonging to the computing continuum domains.

## **1.3** Structure of the thesis

An overview on reliability is presented in Chapter 2. In detail, at fist a definition of dependability, faults, errors and failures is given. Then, this chapter introduces the reliability metrics most commonly used when reliability is assessed. Finally, the dependability threats are discussed alongside the related protection mechanisms, focusing mainly on soft errors. This chapter also introduces the key concepts of cross-layer reliability. More specifically, the main advantages enabled by this approach are discussed and analyzed. It follows a deep analysis about the impact on reliability of all the layers a computing system is composed of and their interaction.

My Ph.D. activities covered several aspects of reliability, however they were all developed in the context of cross-layer reliability. In detail, my contribution ranges from reliability studies of hardware accelerators, GPUs, CPUs and digital systems.

Chapter 3 focuses on a methodology to enhance reliability leveraging reconfigurable computing. My contribution was the development of a new methodology to increase fault tolerance of FPGA-based autonomous systems by means of partial reconfiguration. The proposed methodology includes both a new FPGA-based system architecture and a floor planning strategy. Main improvements with respect to state-of-the-art solutions are the reduction (35x) of the required memory to store bitstreams (configurations of the FPGA) and the reduction (4x) of the recovery time, without any loss of performance and tolerating the same number of permanent faults.

A reliability framework for GPUs I developed to assess reliability fast and accurately is introduced in Chapter 4. This framework is based on the publicly available micro-architectural simulator Multi2Sim and it allows to analyze the reliability of applications running on the Southern Islands AMD GPU architecture. The framework allows designers to perform three different kinds of reliability analyses: fault injection, architecturally correct execution analysis and Instruction Correlation analysis. The GPU hardware structures that can be analyzed are: the vector register file, the scalar register file as well as the local data storage. Thanks to its flexibility, this framework can simulate different kinds of AMD GPU chips that differ on their architectural parameters. This enables to easily explore several design spaces and to understand their impact on the reliability, taking into account the executed workload (software application). Moreover, the framework was employed for an

extensive experimental campaign carried out in collaboration with the University of Athens to compare the reliability of AMD GPUs and NVIDIA GPUs. Results of the comparison are also reported and discussed in this chapter.

In Chapter 5, a methodology for cross-layer reliability evaluation of microprocessor based systems affected by soft errors and permanent faults is presented. This methodology takes into account the microprocessor architecture and the executed software along with their interaction at the Instruction Set Architecture level. In detail, it models the sequence of instructions executed by the microprocessor, and the hardware resources used for their execution in the form of a Bayesian Network that can be used to estimate the probability of fault propagation during the execution of the application. This methodology introduces several advantages with respect to current reliability evaluation approaches: a reduction of computation time (some orders of magnitude if compared to micro-architectural fault injection) and high accuracy (it provides results within 3% error margin with respect to results obtained with fault injection).

A methodology to evaluate the reliability of a complex system in the presence of soft errors, allowing the identification of the weakest components of the system is reported in Chapter 6. This approach is based on a Bayesian model of the system enabling a reliability analysis leveraging Bayesian reasoning. The Bayesian model follows the cross-layer paradigm. In details, in the proposed model, network nodes represent the system components, while arcs connecting nodes model relationships between the different system components. This Bayesian Network can be split into three distinct sub-networks, reflecting the main layers of the system: technology, hardware architecture and software. This chapter aims at describing how the model is built and which kind of reliability analysis can be performed resorting to this methodology. In addition, a detailed description of the tools and techniques employed to obtain numbers to populate the model at each system layer is given. Finally, a validation campaign for this methodology is carried out by comparing the obtained results against stat-of-the-art industrial workflows. The analysis concerns reliability assessment of benchmark systems as well as real-life systems belonging to the computing continuum. Chapter 7 introduces a design optimizer based on this Bayesian model. More specifically, the optimization algorithm as well as results are reported.

Finally Chapter 8 concludes the dissertation summarizing the key aspects related to reliability that have emerged and identifies the possible future works in this field.

# **Chapter 2**

# **Dependability of digital systems**

This section overviews basic dependability principles applied to digital systems. At first, the concept of dependability is introduced. The concepts and the taxonomy presented in Section 2.1 serve as the basis for the classification of reliability metrics explained in Section 2.2. Dependability threats and dependability enhancing mechanisms are analyzed in Section 2.3 and Section 2.5.

This thesis focuses mainly on reliability in presence of soft errors. For this reason, specific subsections are added to analyzes into details these aspects.

## 2.1 Dependability

The term "dependability" covers different aspects of a system, it represents the extent to which a system is expected to operate in compliance to its specifications. Dependability involves several attributes [5]:

- Availability: readiness for correct service.

- Reliability: continuity of correct service.

- **Safety:** absence of catastrophic consequences on the user(s) and the environment.

- Integrity: absence of improper system alterations.

- Maintainability: ability to undergo modifications and repairs.

Fig. 2.1 All the aspects of dependability.

Main dependability attributes, as well as dependability threats and means to improve dependability are shown in Figure 2.1. A definition of dependability threats is the following:

- Failure an event that occurs when the delivered service deviates from correct service. A service fails either because it does not comply with functional specification, or because this specification did not adequately describe the system function. Correct service is delivered when the service implements the system function [5]. Failures manifest at user domain.

- **Error** part of the total state of the system that may lead to its subsequent service failure. It is important to note that many errors do not reach the system's external state and thus do not cause a failure [5]. Errors manifest at informational domain.

- Fault adjudged or hypothesized cause of an error. A fault is active when it causes an error; otherwise it is dormant [5]. Faults manifest at the physical domain.

Among all the attributes of dependability introduced in Figure 2.1, this thesis focuses on reliability. Reliability is the property of a system to behave properly for a given period of time. In particular external agents, manufacturing processes as well as stress can impact reliability of systems, changing their functioning. From a theoretical point of view, reliability is defined as:

**Reliability** *Reliability is a function expressing the probability of a system to behave correctly, without any failure, in between a certain time interval* [0,t]*. There-fore, system reliability,* R(t)*, is the probability that the time to failure,* T*, is grater than t:*

$$R(t) = P\{T > t\}$$

where  $R(0) = 1$   $\lim_{t \to \infty} R(t) = 0$  (2.1)

The relation between reliability and failure is highlighted in Equation 2.2, where F(t) is the probability of a failure to happen before time *t*:

$$F(t) = 1 - R(t) = P\{T < t\}, \quad f(t) = \frac{\mathrm{d}F(t)}{\mathrm{d}t}$$

(2.2)

In fact, F(t) expresses the cumulative distribution function (CDF) of the failure distribution f(t), that is the probability distribution function (PDF) of the failures. When taking into account reliability constraints in the design of a system, fault models alongside their failure distribution should be studied at first.

## 2.2 Reliability metrics of digital systems

Reliability of digital systems can be measured according to different metrics. This section analyzes the main reliability metrics that are widely employed in state-of-the-art studies. In details, each metric can be computed at every stage of the system project, according to the needs of designers.

#### 2.2.1 Failure Rate

The failure rate is the frequency with which the system fails and it expresses the number of failures per unit of time. If the Failure Rate is assumed as constant it can be used to model the exponential distribution of failures and it is commonly indicated as  $\lambda$ . A formal definition of exponential distribution applied in the reliability field is discussed in Section 2.4.

#### 2.2.2 Failures In Time

Digital systems are usually characterized by very low failure rates, consequently another parameter derived from the failure rate is preferred: the Failures in Time (FIT). The FIT is the number of expected failures in a billion hours of system activity.

$$FIT = \lambda_{hours} \times 10^9 \tag{2.3}$$

The most common approach employed to evaluate the reliability of a digital system, expressed by  $FIT_S$ , consists of analyzing the FIT of each component of the system,  $FIT_{C_i}$ , individually and later combining them together according to:

$$FIT_S = \sum_{i}^{\# components} FIT_{C_i}$$

(2.4)

This formula can be employed when errors in each system component i are assumed as independent.

#### 2.2.3 Mean Time To Failure

Mean Time To Failure (MTTF) is the average time before the occurrence of a failure, that is the expected value E(T) of the failure distribution. It is strongly related to the system reliability:

$$MTTF = E(T) = \int_0^\infty t \, f(t) \, dt = \int_0^\infty R(t) \, dt$$

(2.5)

The MTTF is usually expressed in hours and it is a basic measure of reliability for non-repairable items. For non-repairable items with constant failure rate:

$$MTTF = \frac{1}{\lambda} \tag{2.6}$$

Finally, MTTF and FIT metrics are correlated as illustrated in Equation 2.7 (a mnemonic rule of the correlation between FIT and MTTF is that an MTTF of 1000 years translates into a FIT rate of 114 FIT):

$$MTTF(years) = \frac{10^9}{FIT \times 24 \,hours \times 365 \,days} \tag{2.7}$$

#### 2.2.4 Mean Time To Repair

Expresses the mean time to repair an error once it is detected. It therefore measures the service interruption. This time is determined by the repair and recovery mechanisms that a system is equipped with. It is a basic measure of the maintainability of repairable items.

#### 2.2.5 Mean Time Between Failures

The Mean Time Between Failure (MTBF) is the average time elapsing between two failures of a system. MTBF is computed as the sum of two distinct contributions: the Mean Time To Failure (MTTF) and the Mean Time To Repair (MTTR).

$$MTBF = MTTF + MTTR \tag{2.8}$$

In particular, MTTR applies only for repairable systems, systems which include repair mechanisms, in the other cases the MTBF is equal to MTTF.

#### 2.2.6 Availability

Ability of a system to be in state to perform a required function at a given instant of time or at any instant of time within a given time interval, assuming that the external

resources, if required, are provided [6].

$$Availability = \frac{MTTF}{MTTF + MTTR}$$

(2.9)

In conclusion, the smaller the MTTR the higher is the availability of the system.

#### 2.2.7 Mean Workload To Failure

It captures the average amount of work between two errors and is useful to compare the reliability of different workloads [7].

#### 2.2.8 Mean Instruction To Failure

It expresses the average number of committed instructions in a microprocessor between two errors [8].