# POLITECNICO DI TORINO VISHAY SEMICONDUCTOR ITALIANA

# Thermal dissipation improvement by new technology approach: study, development and characterization

Department of Applied Science and Technology

PhD in Physics XXVIII Cycle

#### Isabella Para

**Supervisors**

Prof. C.F. Pirri

Dott. L. Merlin

# Outline

| Chapter 1                                         | 1  |

|---------------------------------------------------|----|

| INTRODUCTION                                      | 1  |

| 1.1 Semiconductor wafer                           | 1  |

| 1.2 Wafer thinning techniques overview            | 4  |

| 1.1.1 Temporary bonding process and Taiko process | 10 |

| 1.3 Thesis objectives                             | 14 |

| 1.4 Thesis structure                              | 16 |

| References                                        | 17 |

| Chapter 2                                         | 19 |

| CLEANROOM AND SAMPLES                             | 19 |

| 2.1 Cleanroom                                     | 19 |

| 2.2 Samples                                       | 24 |

| 2.3 Samples Preparation                           | 27 |

| References                                        | 29 |

| Chapter 3                                         | 30 |

| THE PROCESS FLOW                                  | 30 |

| 3.1 Silicon Oxide Deposition                      | 30 |

| 3.1.1 Introduction                                | 30 |

| 3.1.2 Objective                                   | 31 |

| 3.1.3 Sputtering basic principle                  | 31 |

| 3.1.4 Equipment details and results               | 33 |

| 3.2 Photolithography                              | 35 |

| 3.2.1 Introduction                                | 35 |

| 3.2.2 Objective                                   | 38 |

| 3.2.3 Coating                                     | 39 |

| 3.2.4 Exposure                                    | 39 |

| 3.2.4.1 Overview                                  | 39 |

| 3.2.4.2 Experimental                              | 42 |

| 3.2.3 Development                     | . 46 |

|---------------------------------------|------|

| 3.2.4 Photolithography                | . 47 |

| 3.3 Deep Reactive-Ion Etching         | . 50 |

| 3.4 Barrier Seed Layer Deposition     | . 59 |

| 3.4.1 Introduction                    | . 59 |

| 3.4.2 Objective                       | . 61 |

| 3.4.3 Evaporation basic principle     | . 61 |

| 3.4.4 Equipment details and results   | . 63 |

| 3.5 Photoresist Lift-off              | . 64 |

| 3.5.1 Introduction                    | . 64 |

| 3.5.2 Objective                       | . 65 |

| 3.5.3 Lift-off basic principle        | . 65 |

| 3.5.4 Equipment details and results   | . 66 |

| 3.6 Copper Electroplating             | . 69 |

| 3.6.1 Introduction                    | . 69 |

| 3.6.2 Objective                       | . 69 |

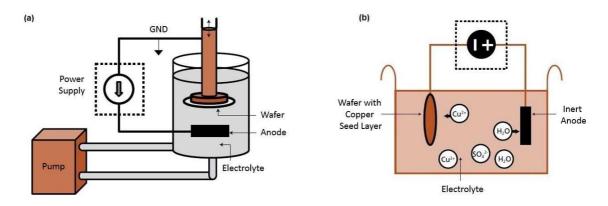

| 3.6.3 Electroplating basic principle  | . 70 |

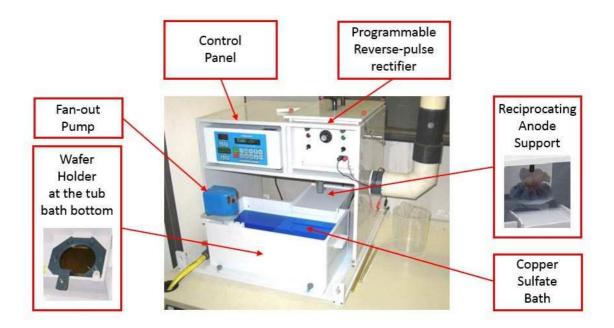

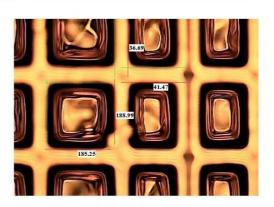

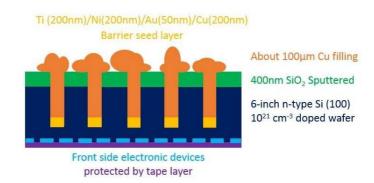

| 3.6.4 Equipment details and results   | . 71 |

| 3.7 Wafer Planarization               | . 73 |

| 3.8 Back Metal Deposition             | . 74 |

| 3.9 Process Flow Summary              | . 76 |

| References                            | . 77 |

| Chapter 4                             | . 82 |

| SECTION STUDY                         | . 82 |

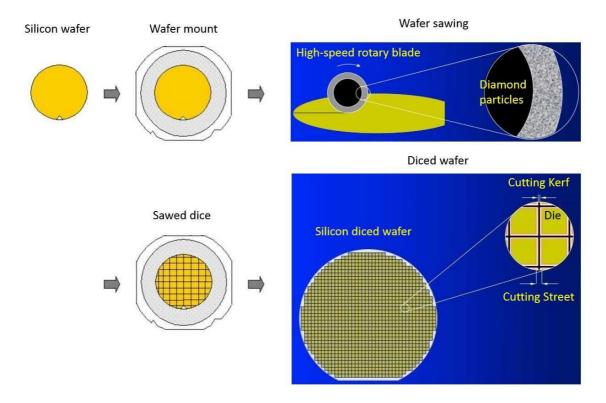

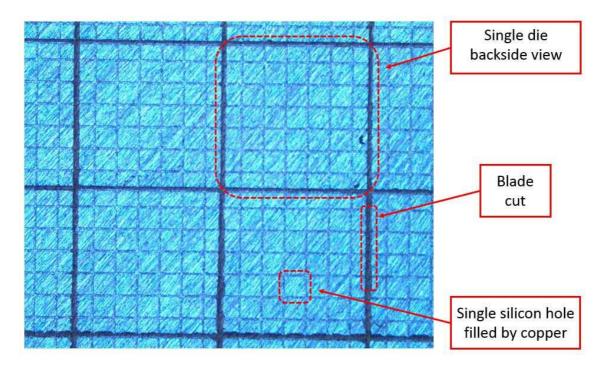

| 4.1 Wafer Dicing                      | . 82 |

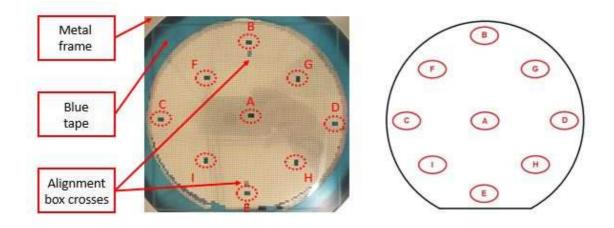

| 4.2 Sample Choice Criterion           | . 84 |

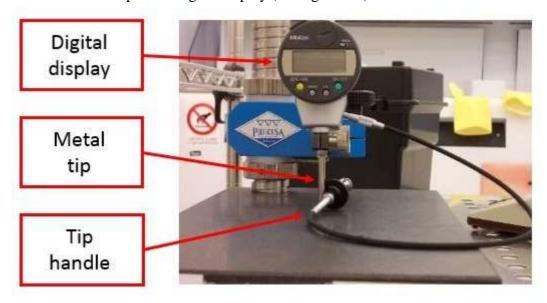

| 4.4 Thickness Measurements            | . 85 |

| 4.5 Resin Encapsulation               | . 85 |

| 4.6 Mechanical Grinding and Polishing | . 86 |

| 4.7 FESEM Samples preparation         | . 87 |

| 4.8 Results and discussion            | . 88 |

| References                             | 93  |

|----------------------------------------|-----|

| Chapter 5                              | 94  |

| DICE ASSEMBLY                          | 94  |

| 5.1 Assembly overview                  | 94  |

| References                             | 98  |

| Chapter 6                              | 99  |

| ELECTRICAL AND THERMAL                 | 99  |

| CHARACTERIZATION                       | 99  |

| 6.1 Electrical Characterization        | 99  |

| 6.2 Thermal Characterization           |     |

| References                             | 106 |

| Chapter 7                              | 107 |

| FAILURE ANALYSIS                       | 107 |

| 7.1 Failure analysis on assembled dice |     |

| 7.2 Forced dice degradation            | 109 |

| Chapter 8                              | 111 |

| CONCLUSIONS                            | 111 |

# Chapter 1

# **INTRODUCTION**

In this introductive Chapter, an overview of the semiconductor wafer and its thinning technique is reported. Afterwards it is presented an alternative approach to improve the performances of the electronic devices, which is the thesis' target. Finally, the last Section of the Chapter is dedicated to the description of the thesis structure and where it was conduct.

#### 1.1 Semiconductor wafer

In electronics, a wafer (also called a slice or substrate) is a thin slice of semiconductor material, such as a silicon crystal, used in the fabrication of integrated circuits and other micro-devices.

The wafer serves as the substrate for microelectronic devices built in and over the wafer and undergoes many microfabrication process steps such as doping or ion implantation, etching, deposition of various materials and photolithographic patterning.

Front-end-of-line (FEOL) processing refers to the formation of devices directly in the substrate. In order to enhance the performance of electronic devices, the raw wafer is engineered by the growth of an ultrapure, virtually defect-free, silicon layer through epitaxy. Once the epitaxial silicon is deposited, the crystal lattice becomes stretched somewhat, resulting in improved electronic mobility. In addition, epitaxial wafers over

bulk wafers offer mean of controlling the doping profile and epitaxial layers are generally oxygen and carbon free.

Since the epitaxial silicon layer is the layer of device fabrication, its thickness choice depends largely on the intended application. Moreover, raw wafer thickness is determined by the mechanical strength of the material used and by the slice diameter; the important thing is that the wafer must be thick enough to ensure a minimum of mechanical stability to support its own weight without cracking during handling and to avoid warping during high-temperature processing steps.

Single crystal silicon wafers are utilized for essentially all integrated circuits and many other semiconductor devices. To permit common processing equipment to be used in multiple device fabrication lines, it is essential for the wafer dimensions to be standardized [1].

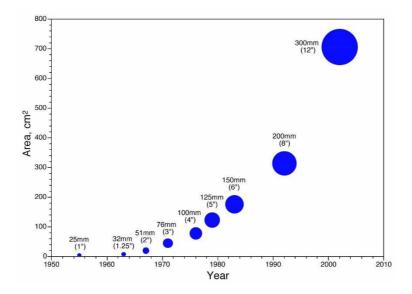

Fig. 1 Commercial silicon wafer size vs year trend [2].

Fig. 1 reports the time evolution in commercial silicon wafer size during last 60 years. The diameter has gradually increased to improve throughput and reduce cost but larger wafer diameters require thicker silicon to withstand wafer manufacturing.

| Diameter [mm] | Diameter [inch] | Thickness [μ] |

|---------------|-----------------|---------------|

| 25            | 1               | -             |

| 51            | 2               | 275           |

| 76            | 3               | 375           |

| 100           | 4               | 525           |

| 130           | 5               | 625           |

| 150           | 6               | 675           |

| 200 | 8  | 725 |

|-----|----|-----|

| 300 | 12 | 775 |

| 450 | 18 | 925 |

Tab. 1 Current commercial silicon wafer size [3].

Tab. 1 reports some values of production standard wafer sizes in case of silicon substrates.

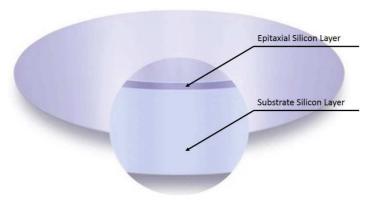

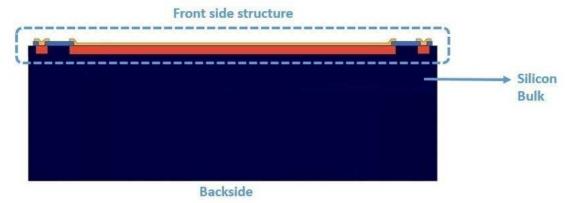

On the other hand, the epitaxial layer thickness strictly depends on the desired device, thus, it is always thinner than the bulk substrate (Fig. 2). It ranges from a few hundred Angstrom to several tenth of Microns. This means that the active region of a semiconductor device is limited at the surface, thus there is a large amount of unused material. This silicon bulk material excess acts only as a mechanical support during manufacturing process steps and causes heat increasing during the device operation. Thermal dissipation is an important issue in semiconductor manufacturing because the operation of a semiconductor device is sensitive to temperature. When the junction temperature exceeds its functional limit, semiconductor performance, life, and reliability can be significantly reduced.

Fig. 2 Typical silicon wafer substrate with the epitaxial layer [4].

In electronic field, the thermal resistance is a simplified parameter characterizing the devices thermal performances and it depends strongly on the wafer thickness. As mentioned before, the substrate region has no major electrical function and the thermal resistance of nearly all power chips can be significantly improved by thinning the wafer. The lower the thermal resistance, the better the thermal dissipation, thus the better performing devices.

In order to improve the thermal resistance, the thinning of the whole wafer at the back end, i.e., after the complete device processing on the front side, is strongly required. The final thickness depends on the designed package, that depends itself on the final customer application.

# 1.2 Wafer thinning techniques overview

The requirement of an increasing thickness of the wafers during processing and the contrasting interest of thinner silicon in powerchip applications makes thinning techniques more and more important.

Wafer thinning is the process of removing material from the backside of a wafer to a desired final target thickness [5].

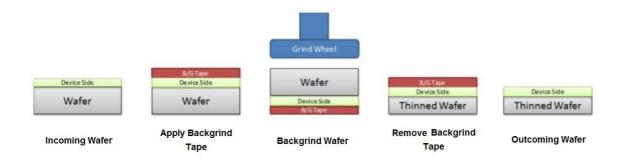

Because of its high thinning rate, mechanical grinding currently is the most common technique for wafer thinning especially in semiconductor and electronic manufacturing [6, 7, 8].

Conventional grinding is an aggressive mechanical process that utilizes a grind wheel to perform the material removal. These wheels are made by diamond grits embedded in a bonding matrix, which can be either metallic, vitrified or a resin. The main characteristic of a grinder wheel is its mesh, that is related to the density of diamond particles embedded and thus, with the size of these particles. The higher the mesh, the smaller the grit size, the smaller the roughness and the smaller the sub-surface damage (SSD).

The wafer is positioned on a porous ceramic rotating vacuum chuck with the backside of the wafer facing upwards (towards the grind wheel) (Fig. 3). Both the grind wheel and wafer chuck rotate during grind. Deionized water is jetted onto the work piece to provide cooling and wash away material particles generated during the grind. A grinding tape is applied to the front side of the wafer to protect the devices from being damaged during thinning.

The grind recipe dictates the spindle RPM, rate of material removal, and the final target thickness of the work piece.

Fig. 3 Conventional mechanical wafer grinding process flow sketch [6].

All commercially available grinding systems use a two-step process including a coarse grinding that performs the bulk of the material removal and a subsequent fine grinding. The first grinding step is performed with a rough grinding wheel (small mesh) in order to remove the bulk of the Si at high speed (in the order of a few  $\mu$ m per second). Yet, it causes deep SSD due to the brittle nature of the Si wafer in combination with the big grit size. This damage layer is typically confined to the first 30-20  $\mu$ m below the ground surface (Fig 4) [8]. A fine grinding step is then performed to remove this damaged layer created by the coarse grinding step and reduce surface roughness by means of grids with smoothest roughness than that ones used for the first step. This step provides a mirror like surface that is the final finish of the wafer backside.

Fine grinding step provide the highest wafer and die strength as the high grit wheel removes the most subsurface damage. As a rule, as the grit increases, the wafer strength and smoothness improves, while the wafer warpage and subsurface damage decreases.

However, there is a remaining defect band near the surface. Although the fine grinding is used to remove the SSD from the rough grinding, it also introduces its own damage, though in a much smaller range, normally a few microns deep or even below 1µm.

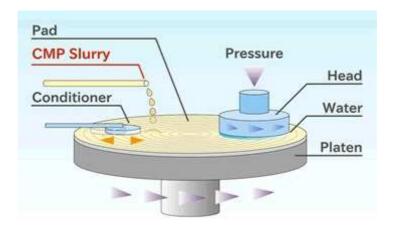

The residual defects cause stress in the thinned wafer, leading to an additional bow and often broken wafers during handling or further processing. This means that additional thinning is necessary to remove the remaining defect layer and surface roughness after mechanical grinding. This can be done by either chemical mechanical polishing (CMP), dry etching (ADP) or wet chemical etching.

Fig. 4 Sub-Surface Damage stack (top) and SEM image of cracks (fracture zone) introduced because of the rough grinding process (bottom) [8].

In CMP, abrasive chemical slurry is used with a polishing pad to perform material removal [7, 9, 10]. During CMP processes, a wafer is rotated about its axis while being pressed face-down by a carrier and a carrier film against a rotating polishing pad covered with colloidal silica slurry with specific chemical properties (Fig. 5). The abrasive slurry, plays an important role in the material removal mechanism in CMP. Microscopic observations of polished surfaces have shown that material removal in CMP occurs as a consequence of a combination of chemical reaction of the slurry chemicals with the wafer surface materials and the repeated sliding, rolling, or indentation of the abrasive particles against the wafer surface.

Fig. 5 Chemical Mechanical Polishing Process apparatus [10].

CMP provides greater planarization compared to mechanical grinding and low total thickness variation (TTV) values, however, it is considered a "dirtier" and more costly process. The thinning rate, however, reaches values of only a few micrometers per minute.

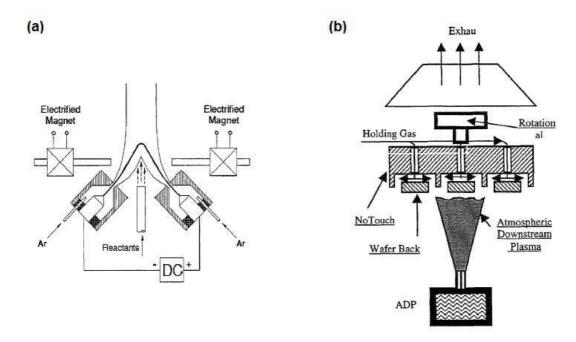

Atmospheric Downstream Plasma (ADP) processing utilize a magnetically controlled, inert gas, DC arc-plasma discharge [7, 11]. In the ADP source (Fig. 6a), two electrode units are directed upward and toward each other with an angle of about 90" between their axes. Each unit consists of an electrode placed inside a chamber with a water-cooled orifice. The orifice and electrode are located along the chamber axis so that the mainstream plasma gas (usually argon), when injected into the chamber, will exit through the orifice. When a dc field is applied between the two electrodes, a plasma arc is formed which exits the orifice of one electrode unit and enters the orifice of the other. The plasma is kept from the chamber walls by the flow of mainstream gas.

Fig. 6 (a) Schematic of the atmospheric downstream plasma source; (b) process chamber schematic of the Tru-Etch System [11].

External magnetic fields are used to direct the plasma jet parallel to the vertical symmetry axis of the combined electrode system. The vertical orientation of the plasma region creates a chimney effect and, when cold reactant gases are injected into the plasma region along its vertical axis, they are captured by the plasma. The reactant gases are heated, activated, and effectively decomposed in the plasma region which is far from the electrode units, therefore, chemical erosion of the plasma generators is eliminated. For silicon etching, tetrafluorocarbon (CF<sub>4</sub>) is used as a reactant.

The ADP source has been incorporated into the Tru-Etch series of wafer treatment systems. The system schematic is shown in Fig. 6b.

The ADP flow is directed up and stabilized with the magnetic fields. Because of the atmospheric pressure in the process chamber, the effluent gases move up due to natural convection and are effectively removed by an exhaust located at the top of the process. The wafers are placed in holders so that the wafer side to be etched is oriented down. The wafer holders are attached to a process carousel precisely moved by a computer controlled rotational drive.

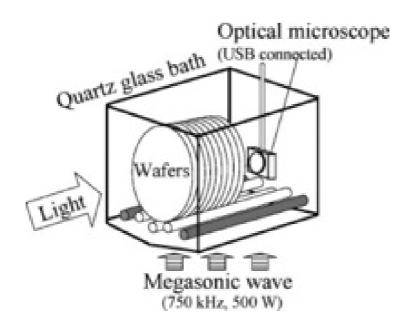

Another common thinning technique is wet chemical etching. The wafers can be immersed in a bath of etchant, which must be agitated to achieve good process control (Fig.7) [12,13]. The wafer front side must be protected by specific tape before the immersion. Megasonic agitation is commonly used with the chemical bath. An optical microscope serves as etching controller. This technique allows to simultaneously etching more than one wafer, thus it is the most widely used in mass production. KOH

is one the most commonly used silicon etch chemistry for micromachining silicon wafers. The KOH etch rate is strongly affected by the crystallographic orientation of the silicon and depends on the concentration of the KOH solution and temperature.

Fig. 7 Schematic drawing of a wet chemical etching bath [12].

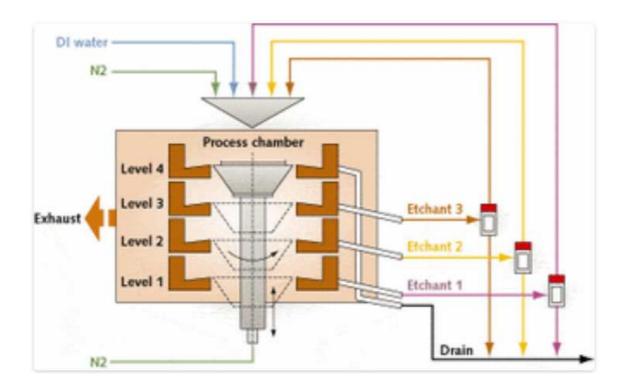

As an alternative to immersion, to etch one side of the wafer, is spin etching, in which a thin stream of an etching agent is moved periodically over the surface of the rotating wafer (Fig. 8) [7, 14].

The front surface of the wafer is protected either by additional layers or by applying special chucks that allow the processing of thin wafers without surface protection layers or tapes. The etching agents for silicon are mostly mixtures of HF and HNO<sub>3</sub>. The different mixtures allow different etching rates and are characterized by different selectivity, which may be important if different layers are involved.

The process chuck of the spin processor used to conduct the HF tests relies on Bernoulli's principle to fix the wafer at a constant distance from the chuck surface on a bed of nitrogen  $(N_2)$ . The wafer is held in place by six edge-contact-only pins that make contact at the wafer bevel with sufficient force to center the wafer on the  $N_2$  bed and hold it in place while the chuck rotates. The chuck rests in a process chamber, as depicted in the schematic drawing in Fig.8.

The process chamber can have up to four independent process levels, three of which dispense different process chemicals (or chemical blends) and one of which is dedicated to DI-water rinsing and nitrogen drying. The process chuck rotates clockwise or counterclockwise within the process chamber while the medium is dispensed. The

different chemistries are dispensed onto a spinning wafer at three dedicated process levels, allowing for tight process control and eliminating the risk of chemical cross-contamination.

Fig. 8 Schematic drawing of the spin-processor chamber [7].

Once the wafer reached the desired thickness and surface finishing, further production steps, such as backside contact formation, are needed. All these steps are affected by the wafer history, i.e., the processes that result in a sequence of layers on the wafer front side that generate different internal stresses on the wafer. In addition, thin wafers are very flexible, which is the biggest problem for conventional handling tools.

# 1.1.1 Temporary bonding process and Taiko process

Nowadays, in order to overcome handling issues, wafer thinning process in mass production is carried out using mainly two approaches, the temporary bonding and the so-called Taiko processes.

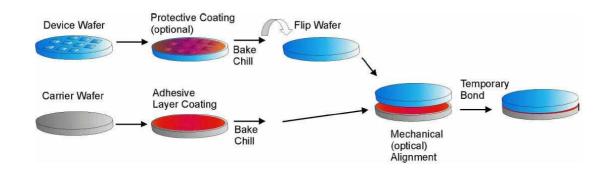

Temporary bonding process is an EV Group (Electron Vision Group) invention covered by United States Patent and Trademark Office [15].

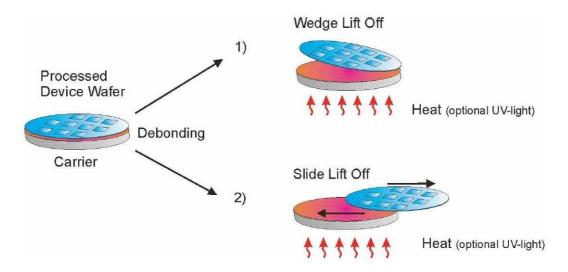

In the temporary bonding approach, the original thick and rigid device wafer is bonded onto a carrier wafer prior to the thinning step being performed.

The process for temporary wafer bonding is shown in Fig.9. The front side of the carrier wafer will be coated with the adhesive, and the wafer will undergo an initial bake to remove the solvent. The device wafer, after the application of a protective layer, will be brought into contact with the adhesive-coated carrier wafer under vacuum and pressure conditions [16, 17, 18, 19].

Fig. 9 Temporary bonding process flow [16].

Once the product wafer is temporarily bonded to the carrier wafer, which provides sufficient mechanical support, it is ready for mechanical grinding and next backside processing steps which generally may include, depending on the type of fabricated devices on the front side, lithography, DRIE etch, insulator/barrier deposition, CMP, metallization deposition, etc.

After completion of the backside processing steps, the thin device wafer can be released from the carrier wafer.

The most commonly used methods for debonding, depending on the kind of adhesive material employed, are represented in Fig.10. In the first method, the removable thermosets (the protecting coating of device wafer and the adhesive layer coating of the carrier wafer) can be completely decomposed at temperatures above 350°C in nitrogen atmosphere within 15 minutes without leaving any residue. Then the thinned wafer can be carefully removed from the carrier using a wedge-off motion. The second method involves heating the substrates uniformly to the debonding temperature (in most cases, typically above 200°C) while they are locked into a rigid frame with top and bottom heaters. Then, the wafers are slide apart in a controlled manner such that the wafers stay parallel to each other until completely apart.

Once the wafers are separated, the thin wafer is safety transferred to a single wafercleaning chamber, where the remaining adhesive is removed with an appropriate solvent.

This solvent is dispensed on the device wafer and allowed to soak for a period of time. During soaking, the solvent is agitated using a proprietary tool developed to better dissolve the polymer. As the polymer dissolves, the wafer is spun and sprayed with additional solvent to allow complete cleaning. A final high-speed spin is used to completely dry the wafer.

Fig. 10 Debonding methods [16].

The selection of a suitable temporary adhesive is the key to success. The major requirements of temporary adhesives are related to its process flow, thermal stability, chemical resistance, and mechanical strength.

Thermal stability of temporary adhesives relates to the ability of the material to resist decomposition and outgassing during exposure to high process temperatures over periods of time. The commonly reported modes of adhesive failure after exposure to high temperatures are the complete delamination of the thinned wafer from the carrier.

The adhesive must be resistant to a wide range of semiconductor chemicals that it will contact, from solvents and acids to plating solutions and cleaning agents.

Mechanical hardness and strength of the adhesive becomes important during the wafer thinning process and during permanent bonding, otherwise the thinned wafer will flex and prevent bonding.

Adhesives for the bonding process must have a good adhesion to a variety of semiconductor substrates and should possess adequate flow properties to flow into

structures on the front side of the device wafer to provide good bonding quality. In addition, the adhesives must be easy to apply and exhibit minimal total thickness variation (TTV) across wafers.

Finally, it must have a very gentle debond process imparting the least amount of stress on a fragile wafer.

The wafer carrier must also meet certain requirements like ability to align through the carrier and the adhesive and to be a non-contaminating material (the most diffused are silicon and glass). In addition, wafer carrier must have similar thermal expansion coefficient of device wafer, a diameter dimension able to support device wafer edge and it must have total thickness variation similar to the device wafer.

A temporary wafer bonding/debonding approach allows using standard wafer processing equipment for backside processing of thin wafers. A thin semiconductor wafer bonded to a carrier wafer resembles a thick semiconductor wafer in terms of geometrical and thermal properties. The bonded device wafer can be processed without the need for special thin wafer components.

The Taiko backgrinding process is a DISCO Corporation invention covered by United States Patent and Trademark Office [20].

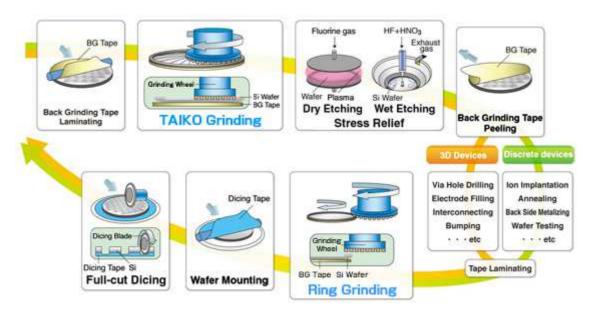

Fig. 11 Taiko Backgrinding process. [21]

In the Taiko approach, Fig.11, the front side of the wafer, with a plurality of devices, is covered with a proper material to protect the device front end during the subsequent processes. Then, the semiconductor backside is thinned removing the semiconductor material. However, the grinding wheel has a small diameter than the wafer one, and the

grinding process is done in a way that only the inner portion is thinned, whereas the rim edge of the background wafer has the original thickness of the wafer [22, 23].

Further backside processing steps, like wet and dry etching, can be performed and then the protective layer on the semiconductor wafer front end can be removed. Based on the semiconductor device typology the backside is processed to complete the device structure (implantation, thermal processes, metallization, etc...), managing the obtained thinner wafer.

Taiko approach allows to reduce the wafer thinning minimizing the wafer warpage and improving the semiconductor wafer strength. A comparison between conventional thinned wafer and Taiko grinded wafer, before edge removal, is shown in Fig.12. The thicker edge allows a self-support of the grinded wafer, while the conventional wafer shows a wide warpage. Different solutions for the removal of the thick ring are available, such as ring grinding, circle cut and direct dicing.

Fig. 12 Taiko wafer vs. conventional wafer. [23]

# 1.3 Thesis objectives

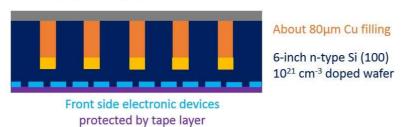

The main objective of this thesis project is to reduce the thermal resistance of the devices without reducing the wafer thickness but by exploiting the excess material as a heat sink.

The idea is to replace a large amount of silicon selectively removed by a local wafer thinning with a conductive material like copper. Therefore, the large amount of unused material, which would cause only heat increasing, becomes useful.

The first thesis goal is to develop a suitable process flow optimizing the parameters of each step and make it repeatable. The second thesis part is devoted to undergo the backside of the electrically good devices with the new process flow and hence compare thermal and electrical performances with those of standard good devices without a treated backside.

This new process flow offers the advantage of maintaining the wafer "self-support" and allow working with already existing technologies saving on both dedicated thinning technologies and handling technologies.

That concept is a completely new idea covered by United States Patent and Trademark Office [24]. Fig. 13 shows a drawing of a final new device section view compared with the final standard one. The front side structure belongs to a generic planar device and it is the same for new devices and the standard ones. The difference lies on the backside structure.

# Front side structure Silicon Bulk Copper

#### STANDARD DEVICE

**NEW DEVICE**

Fig. 13 Comparison between New and Standard devices' section view.

## 1.4 Thesis structure

The thesis is arranged into seven Chapters, the first one giving a brief introduction to the semiconductor wafers and thinning methods. This is followed by the purpose of the study as well as the outline of the thesis.

Chapter 2 deal with the environment in which the samples were processed, the cleanroom, and the description of the starting samples used during the thesis.

Chapter 3 presents the consolidated fabrication process flow in details.

Chapter 4 provides the section study characterization of the new process flow applied to semiconductor wafers.

Chapter 5 explains the assembly process flow of the manufactured devices.

Chapter 6 is devoted to the description of electrical and thermal characterization of new assembled devices.

Chapter 7 discusses the failure analysis results on new devices and the related root cause.

Chapter 8 presents the general conclusions together with a brief discussion of future work.

This work is the result of a collaboration among the Vishay Semiconductor Company of Borgaro Torinese (TO) and the Applied Science and Technology Department (DISAT) of the Politecnico di Torino.

All the process flow production and its characterization was performed mainly at Material and Microsystems Laboratory (Chilab) of the Politecnico di Torino, in Chivasso (TO) with the technological support of Trustech Innovation Technology at Techfab Laboratory, Chivasso (TO). The silicon wafers were supplied by Vishay Semiconductor Company of Borgaro Torinese (TO) as well as the back end processes, electrical and thermal characterization and failure analysis.

# References

[1] SEMI International Standards

http://ams.semi.org/ebusiness/standards/SEMIStandardDetail.aspx.

[2] Beloit College, Wisconsin

http://education.mrsec.wisc.edu/SlideShow/slides/computer/commercial\_wafer\_size.ht ml

[3] EE Times Newsletter

http://www.eetimes.com/document.asp?doc\_id=1169573

[4] Sun Edison Semiconductor

http://www.sunedisonsemi.com

[5] Melissa E. Grupen-Shemansky, "Method for thinning a semiconductor wafer" United States Patent US5268065, 1993

[6] Corwil Technology Corporation

http://www.corwil.com/SATS-CORblog/bid/331237/What-is-Wafer-Thinning

[7] Solid State Technology

http://electroiq.com/blog/2003/03/wafer-thinning-techniques-for-ultra-thin-wafers

[8] M. Nishiguchi et al., "Mass Production Back-Grinding/Wafer-Thinning Technology for GaAs Devices" IEEE Transactions on Components, Hybrids, and Manufacturing Technology, vol.13, no.3 (1990).

[9] Jianfeng Luo and David A. Dornfeld, "Material Removal Mechanism in Chemical Mechanical Polishing: Theory and Modeling" IEEE Transactions on Semiconductor Manufacturing, vol.14, no.2 (2001).

[10] ACG Asahi Glass

http://www.agc.com/english/products/products\_02.html

[11] Oleg Siniaguine, "Atmospheric Downstream Plasma Etching Of Si Wafers" Electronics Manufacturing Technology Symposium, 1998.

[12] H. Habuka et al., "Dominant Forces for Driving Bubbles in a Wet Cleaning Bath Using Megasonic Wave" Journal of Electrochemical Society, vol.157, no.6 (2010).

[13] M. Hendrix et al., "Advantages of Wet Chemical Spin-Processing for Wafer Thinning and Packaging Applications" International Electronics Manufacturing Technology Symposium, 2000.

[14] Micro Magazine

http://micromagazine.fabtech.org/archive/01/06/Archer.html

[15] E. Tallner, "Device for detaching a carrier from a semi-conductor disk" United States Patent US6792991B2, 2004.

[16] R. Puligadda et al., "High-Performance Temporary Adhesives for Wafer Bonding Applications" Material Research Society Symposium Proceedings, 2007.

- [17] J. Charbonnier, "Integration of a Temporary Carrier in a TSV Process Flow" Electronic Components and Technology Conference, 2009.

- [18] S. Pargfrieder "Temporary Bonding and DeBonding Enabling TSV Formation and 3D Integration for Ultra-thin Wafers" Electronics Packaging Technology Conference, 2008.

- [19] J. Hermanowski "Thin Wafer Handling Study of Temporary Wafer Bonding Materials and Processes" Suss Technical Publications, 2009.

- [20] S Yoshida et al., "Wafer Grinding Method" United States Patent US7462094B2, 2008.

- [21] Disco Technologies

http://www.disco.co.jp/eg/solution/library/taiko.html

- [22] A. Dhadda et al., "Processing of Ultrathin Wafers for Power Chip Applications" Electronics Packaging Technology Conference, 2012.

- [23] G. Klug, "Advanced Solutions for Ultra-Thin Wafers and Packaging" Microelectronics and Packaging Conference, 2009.

- [24] The patent about this topic is not still available online because the filing date was the 15th October 2015. The Serial No. assigned to this application is 14/884,090.

- C. Sanfilippo, L. Merlin, I. Para, G. Richieri "Local Semiconductor Wafer Thinning".

# **Chapter 2**

# **CLEANROOM AND SAMPLES**

This Chapter gives an overview of the specific environment in which the thesis samples were built, the cleanroom. Moreover, the focus will move to the detailed description of the raw starting samples used during the thesis project.

#### 2.1 Cleanroom

Product manufacturing takes place in a controlled environment called cleanroom. Cleanrooms are used in scientific research and practically every industry where small particles can adversely affect the manufacturing process. They vary in size and complexity, and are used extensively in industries such as semiconductor manufacturing, electronics, pharmaceuticals, biotech, medical device and life sciences, as well as critical process manufacturing common in aerospace, optics, military, department of energy and other critical manufacturing environments [1, 2].

A cleanroom is any given contained space where provisions are made to reduce particulate contamination and control other environmental parameters such as air flow rates and direction, pressurization, temperature, humidity and specialized filtration.

The concentration of pollutants such as dust, airborne microbes, aerosol particles, and chemical vapors must be under specified limits. People, process, facilities and

equipment inside a cleanroom also generate these contaminants, which must be continually controlled and removed from the air.

There are different kind of cleanrooms based on the kind of threated products and there are classified by how clean the air is.

The level to which these particles need to be removed depends upon the standards required [1, 3, 4].

The most frequently used standard is the U.S. General Service Administration's standards (known as Federal Standard 209E). The FS209E is a document that establishes standard classes of air cleanliness for airborne particulate levels in cleanrooms and clean zones.

In FS 209E, the number of particles equal to and greater than 0.5µm is measured in one cubic foot of air, and this count is used to classify the cleanroom.

However, as the need for international standards grew, the Internal Standard Organization (ISO) established a technical committee and several working groups to delineate its own set of standards.

The ISO 14644-1 standards classify a cleanroom by the number of particles per cubic meter equal to and greater than 0.1µm.

The two specifications does not match up because of the ISO 14644-1 is based on  $0.1~\mu m$  whereas FS 209E was based on  $0.5~\mu m$  (see Tab.1). FS 209E contains six classes, while the ISO 14644-1 classification system adds two cleaner standards and one dirtier standard. The "cleanest" cleanroom in FS 209E is referred to as Class 1; the "dirtiest" cleanroom is a class 100000. In ISO 14644-1 the "cleanest" cleanroom is a class 1 and the "dirtiest" a class 9. ISO class 3 is approximately equal to FS209E class 1, while ISO class 8 approximately equals FS209E class 100000.

| FED STD 209E |         |             | 0       |        | 0.1µm 0.2µm |              | 0.3µm  |      | 0.5µm    |        | 1µm     |        | 5µm    |      |

|--------------|---------|-------------|---------|--------|-------------|--------------|--------|------|----------|--------|---------|--------|--------|------|

|              |         |             |         | m3 ft3 | m3          | ft3          | m3     | ft3  | m3       | ft3    | m3      | ft3    | m3     | ft3  |

| SI           | ENG     | ISO CLASS 1 | 10      | 0.28   | 2           | 0.056        |        |      |          |        |         |        |        |      |

|              |         | ISO CLASS 2 | 100     | 2.8    | 24          | 0.67         | 10     | 0.28 | 4        | 0.1    |         |        |        |      |

| M1.5         | 1       | ISO CLASS 3 | 1000    | 28     | 237         | 6.7          | 102    | 2.8  | 35       | 0.9    | 8       | 0.2    |        |      |

| M2.5         | 10      | ISO CLASS 4 | 10000   | 283    | 2370        | 67           | 1020   | 28   | 352      | 9      | 83      | 2      |        |      |

| M3.5         | 100     | ISO CLASS 5 | 100000  | 2831   | 23700       | 671          | 10200  | 288  | 3520     | 99     | 832     | 23     | 29     | 0.8  |

| M4.5         | 1,000   | ISO CLASS 6 | 1000000 | 28316  | 237000      | 6711         | 102000 | 2888 | 35200    | 996    | 8320    | 235    | 293    | 8    |

| M5.5         | 10,000  | ISO CLASS 7 |         |        |             | - material o |        |      | 352000   | 9967   | 83200   | 2355   | 2930   | 82   |

| M6.5         | 100,000 | ISO CLASS 8 |         |        |             |              |        |      | 3520000  | 99674  | 832000  | 23559  | 29300  | 829  |

| ~            | 1000    | ISO CLASS 9 |         |        |             |              |        |      | 35200000 | 996743 | 8320000 | 235593 | 293000 | 8296 |

Tab. 1 Comparison between cleanroom standards FS 209E and ISO 14644-1 [3].

In the last years, Federal Standard 209E has not been an active specification but its terminology is still around. The main reason is the ISO 14644-1 cleanroom classification does not do much to identity the class. The Federal Standard 209E is more intuitive. For example, an ISO Class 6 shows 35200 particles at 0.5 µm per cubic meter of air, whereas the Federal Standard class 1000 (which is the equivalent of ISO class 6)

means 1000 particles at 0.5  $\mu$ m per cubic foot of air. Both FS 209E and ISO 14644-1 assume log-log relationships between particle size and particle concentration. For that reason, there is no such thing as zero particle concentration. Ordinary room air is approximately class 1000000 or ISO 9.

The key component to control the air cleaning is the High Efficiency Particulate Air (HEPA) filter that is used to trap particles that are 0.3 µm and larger in size [1, 3]. All of the air delivered to a cleanroom passes through HEPA filters, and in some cases where stringent cleanliness performance is necessary, Ultra Low Particulate Air (ULPA) filters are used.

HEPA (High Efficiency Particulate Air) filters have minimum efficiency of 99.97% at  $0.3~\mu m$  the Most Penetrating Particle Size (MPPS). This type of filter is usually used in ISO Class 5 (100) to ISO Class 8 (100000).

ULPA (Ultra Low Penetration Air) filters have a minimum efficiency of 99.9997 at 0.12  $\mu m$  MPPS. This type of filter is usually used in ISO Class 4 (10) to ISO Class 1.

In addition to the air filtration, the air flow should take into account too.

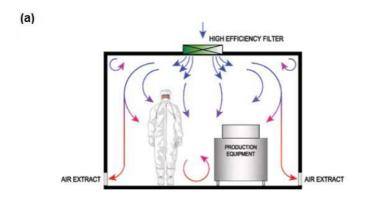

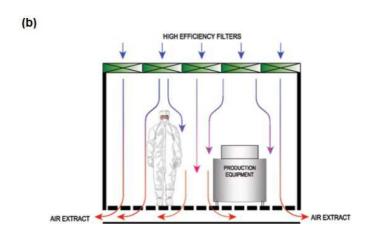

Two major types distinguish the methods of cleanroom ventilation: the turbulently ventilated flow and the unidirectional flow [3, 5]. Turbulently ventilated cleanrooms are also known as 'non-unidirectional'. Unidirectional flow cleanrooms were originally known as 'laminar flow' cleanrooms. The unidirectional type of cleanroom uses very much more air than the turbulently ventilated type, and gives a superior cleanliness. These two types of cleanroom are illustrated in Fig.1.

Fig. 2.1 Types of cleanroom; (a) Turbulently ventilated cleanroom; (b) Unidirectional flow cleanroom [5].

Figure 1a shows a turbulently ventilated room receiving clean filtered air through air diffused from the ceiling. This air mixes with the room air and removes airborne contamination through air extracts at the bottom of the walls. The air changes are normally equal to or greater than 20 per hour, this being much greater than that used in ordinary rooms, such as in offices. In this cleanroom, the contamination generated by people and machinery is mixed and diluted with the supply air and then removed.

Figure 1b shows the basic principles of the unidirectional flow room. High efficiency filters are installed across a whole ceiling (or wall in some systems) and they supply air. This air sweeps across the room in a unidirectional way at a speed of around 0.4 m/s (80 ft/min) and exits through the floor, thus removing the airborne contamination from the room. This system uses more air than the turbulently ventilated cleanroom, because of the directed air movement; it minimizes the spread of contamination about the room and sweeps it out through the floor.

Clean air devices, such as unidirectional benches or isolators, are used in both turbulently and unidirectional ventilated cleanrooms. These machines will give a localized supply of filtered air and enhances air conditions where required, e.g. at the area where the product is open to contamination.

ISO Class 1 through 5 are recommended to be unidirectional airflow designs, as well as ISO Class 6 through 9 are recommended to be non-unidirectional airflow designs.

Personnel selected to work in cleanrooms undergo extensive training in contamination control theory [1]. They enter and exit the cleanroom through airlocks, air showers and/or gowning rooms, and they must wear special clothing designed to trap contaminants that the skin and the body naturally generate. Depending on the room classification or function, personnel gowning may be as limited as lab coats and hairnets, or as extensive as fully enveloped in multiple layered bunny suits with selfcontained breathing apparatus like the human represented in Fig. 1. Cleanroom clothing is used to prevent substances from being released off the wearer's body and contaminating the environment. The cleanroom clothing itself must not release particles or fibers to prevent contamination of the environment by personnel. This type of personnel contamination can degrade product performance in the semiconductor and pharmaceutical industries and it can cause cross-infection between medical staff and patients in the healthcare industry for example. Cleanroom garments include boots, shoes, aprons, beard covers, bouffant caps, coveralls, face masks, frocks/lab coats, gowns, glove and finger cots, hairnets, hoods, sleeves and shoe covers. The type of cleanroom garments used should reflect the cleanroom and product specifications. Lowlevel cleanrooms may only require special shoes having completely smooth soles that do not track in dust or dirt. However, shoe bottoms must not create slipping hazards since safety always takes precedence. A cleanroom suit is usually required for entering a cleanroom. Class 10000 cleanrooms may use simple smocks, head covers, and booties. For Class 10 cleanrooms, careful gown wearing procedures with a zipped cover all, boots, gloves and complete respirator enclosure are required.

A white area and a gray area compose the cleanroom [6]. The white area is the clean ambient in which all the processes take place. The gray area has a low-level cleanroom class than the white area one and refers to the interim space between the surroundings and the white area. The pressure cascade ensures that contamination is limited and that no exterior air enters the white area. The service area is located in the gray area i.e. changing rooms and the servicing and repair of technical systems. A wall or a curtain separates the white and gray areas.

Since this thesis project involves scientific research related to semiconductor manufacturing processes, all the production steps were conducted in cleanrooms. In particular, the whole process flow (see Chapter 3, Section 8) was carried out at Chilab

and Techfab cleanrooms [7, 8]. They are equipped with a yellow area because yellow lighting is necessary during photolithography process (see Chapter 3, Section 2), in order to prevent unwanted exposure of photoresist to light of shorter wavelengths.

Three different areas compose these cleanrooms:

- ISO 14644 Class 5 (U.S Fed-Std 209D Class 100) yellow area validated facility (15 m<sup>2</sup>);

- ISO 14644 Class 6 (U.S Fed-Std 209D Class 1000) validated facility (45 m<sup>2</sup>);

- not classified gray area, but approximately a ISO 14644 Class 7 (U.S Fed-Std 209D Class 10000) as measured (90 m<sup>2</sup>).

During the sample transport from one cleanroom to another, the samples were properly sealed.

# 2.2 Samples

Starting thesis samples consists of a semiconductor wafers, as previously explained (Chapter 1 Section 1).

In order to test and subsequently fix the process flow settings, some monitor wafers were processed before the electrically good epi wafers. A monitor wafer is a slice of semiconductor for use in testing and controlling semiconductor fabrication lines and processes. Although monitor wafers are substantially the same as prime polished wafers with respect to cleanliness, and in some cases flatness, other specifications are generally less rigorous. The main difference between a monitor wafer and a prime polished wafer is the absence of the epi layer, thus without good devices on the front side. This allows a more cost-effective solution for non-critical wafer applications.

Prime polished epi wafers with front side devices were processed after the conclusion of the process flow settings.

Both monitor wafers and epi wafers used in the thesis project were 6-inch n-type silicon wafers with (100) lattice orientation. The bulk resistivity and the bulk doping were  $0.0035 \Omega$ .cm and  $10^{21} \text{ cm}^{-3}$  respectively.

Although the new process only involves the backside of a silicon wafer, any kind of electronic device can be present at the front side; it makes no difference if there is a diode, MOSFET, IGBT and other devices.

The electronic devices at the front side chosen as starting samples for the thesis project are standard planar power PiN diodes still in production. Standard planar power diodes availability and the related quantity of the electrical and thermal characterization data is the reason of this choice.

In power electronic circuits, planar power diodes are used mainly as power switches to regulate the duration of current flow; there are many types according to the desired application.

A diode is a two-terminal electronic component that conducts primarily in one direction thanks to the depletion process at the junction; it has low (ideally zero) resistance to the flow of current in one direction, and high (ideally infinite) resistance in the other. A power diode must be capable of controlling the flow of power to loads with low (ideally zero) power dissipation.

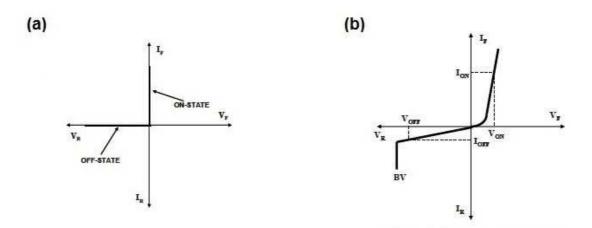

The three main electrical parameters that describe the diode behavior are the forward voltage drop, the leakage current and the breakdown voltage. The forward voltage drop is the voltage across the diode when it allows the current flow. The leakage current is the current value when the diode is inversely polarized. The breakdown voltage is the maximum reverse voltage that the diode can support before breaking.

An ideal diode should exhibit the current–voltage (i–v) characteristic shown in Fig. 2.2a. In the forward conduction mode, the first quadrant of operation in the figure, it should be able to carry any amount of current with zero on-state voltage drop. In the reverse blocking mode, the third quadrant of operation in the figure, it should be able to hold off any value of voltage with zero leakage current. An ideal device is able to sustain an infinite amount of potential in reverse bias, thus the breakdown voltage is infinite.

Fig. 2.2 Current-Voltage (I-V) characteristics (a) of an ideal diode and (b) of a typical real diode [9].

Further, the ideal rectifier should be able to switch between the on-state and the off-state, with zero switching time.

Neither of these components exhibits the ideal characteristics that are required in power circuits to prevent power dissipation.

Real diodes exhibit the i–v characteristics illustrated in Fig. 2.2b. They have a finite voltage drop ( $V_{ON}$ ) when carrying current on the on-state, leading to power loss during the conduction. They also have a finite leakage current ( $I_{OFF}$ ) when blocking voltage in the off-state, creating off-state power loss. Moreover, the breakdown voltage (BV) has a finite value.

The device must have a finite size in order to produce chips that go into packages, thus, it is necessary to surround the device cells with an edge termination. That area provides the transition from the interior of the chip to the edge of the die where it is separated from other chips by using a sawing operation. Cutting out the individual chips by using diamond-coated blades produces considerable damage to the semiconductor crystal. The damaged region must be kept separated from the active area of the chip where current flow transpires to avoid degradation of the device characteristics. This problem can be addressed by using special junction terminations around the edges of the power devices, so that the depletion regions of the high-voltage junctions do not intersect with the saw lanes where the damage is located.

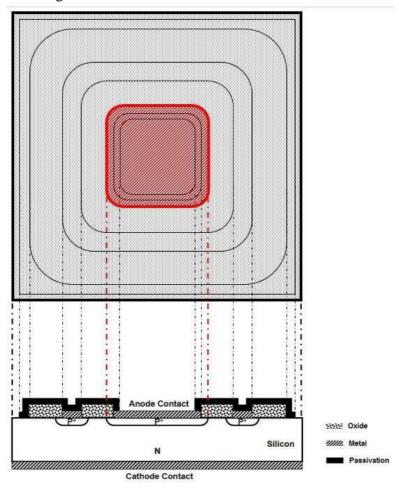

Fig. 2.3 Planar diode front view (upper) and section view (lower); active area and termination are highlighted respectively in red and grey.

In figure 2.3 a basic scheme of a generic planar PiN diode is presented; the upper square is the front view of a planar diode where have been highlighted two main areas: the active area (red) and the termination (grey). The sketch under the front view is the section view of a diode.

The active area is the central part of the device and is mainly responsible for the conduction of the device in direct bias polarization. The termination on the other hand works when the device is in reverse bias conditions. Its efficiency represents the ability of the device to reach the maximum breakdown voltage possible. The leakage current can originate both from the active area and from undesired effect in the termination.

The reverse blocking capability of a diode structure is limited by the design and performance of the edge termination. Many edge termination designs for power devices are still in use in semiconductor industries. The most common approach utilizes one or more floating field rings and field plates. In figure 2.3, there is illustrated an example with a generic planar power diode with singular ring configuration.

Numerical simulations have determined the optimum location of the floating field ring in a device. There are much kind of termination each one with its peculiar structure.

The external ring dimension and quantity depends on the desired electrical device performances. In fact, the major breakdown voltage is required; the major is the number of external rings. Depending on the desired and required Von, IOFF and BV the diode structure can change in active area dimensions, termination designs and so forth.

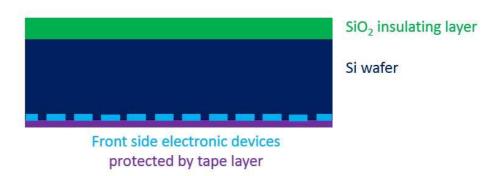

# 2.3 Samples Preparation

Once the whole front side process flow was accomplished, the wafers were taken from production line.

Before processing the epi wafers with the new process flow described in Chapter 3, the wafer front side was coated by a protective tape (Nitto BT-HR-100 [10]). This tape has a total 100µm thickness composed by 50µm thick adhesive layer and 50µm thick upper material. This material layer is able to resist to both high temperature (over 400°C) and chemicals used during the new process flow.

Further, the wafers have to be mechanically grinded and stress relief etched (see Chapter 1 Section 1) in order to start with a wafer thickness equal to standard wafer in production; this allows their direct comparison after the device assembly.

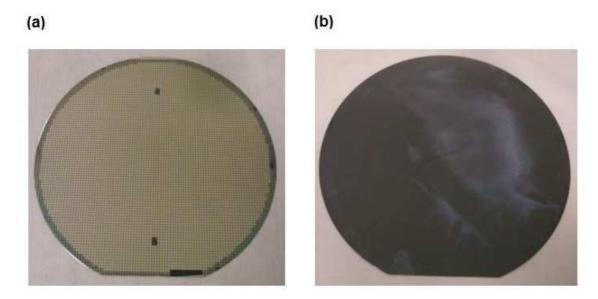

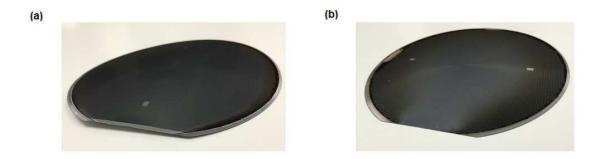

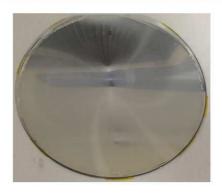

In figure 2.4 there is a typical front side view (a) and backside view (b) of the starting samples. Each small square distinguishable on the front side is a single device. The backside shows some surface staining due to chemical exposure during stress relief etching.

Chapter 2

Fig. 2.4 (a) Wafer front side with multiple devices; (b) wafer backside view with a chemical polishing staining.

## References

[1] Clean Air Technology Inc.

http://www.cleanairtechnology.com/cleanroom-classifications-class.php

[2] Coastwide Laboratories

$http://www.coastwidelabs.com/Technical\%\,20 Articles/Cleaning\%\,20 the\%\,20 Cleanroom. \\ htm$

[3] Clean Room Built and Performance – A division of AM Technical Solutions.

http://amclean roombuild.com/news/the-4-elements-of-clean room-design-certification-and-maintenance-part-1/

[4] Terra Universal – Critical Environment Solutions

http://www.terrauniversal.com/cleanrooms/iso-classification-cleanroom-standards.php

[5] Space Industries Ltd

http://www.spaceindustries.co.uk/cleanrooms/cleanroom-types.php

[6] Dussman Service

http://www.clean-room-cleaning-glossary.com/

[7] Materials and Microsystems Laboratory (Chilab)

http://www.chilab.polito.it/utilities.html

[8] Trustech Innovation Technology (TechFab)

http://www.trustech.it/a-private-laboratory-specialized-in-microenano-technologies

[9] Baliga che ho da Vishay! E altro Baliga trovato "The IGBT device – Physics, Design and Applications of the Insulated Gate Bipolar Transistor" author B. Jayant Baliga editor Elsevier

[10] Nitto Innovation for Customers

http://www.nitto.com/eu/en/products/

Chapter 3 The process flow

# **Chapter 3**

# THE PROCESS FLOW

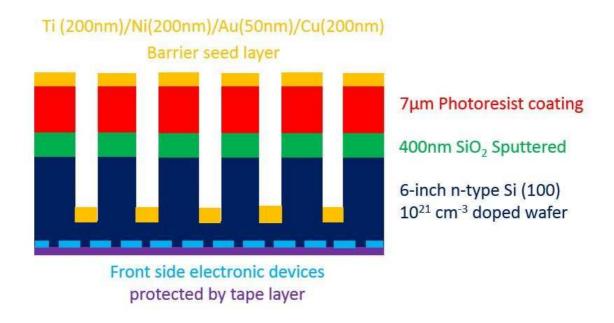

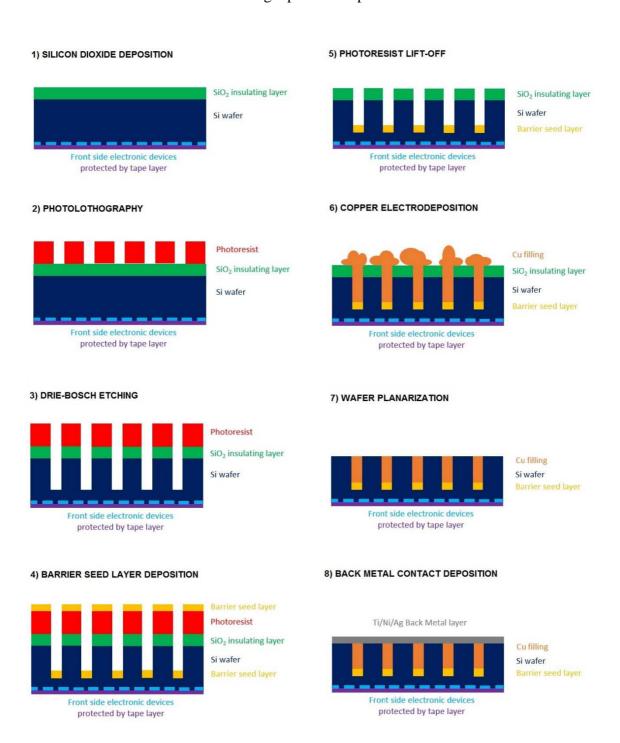

This Chapter is fully devoted to the detailed description of the whole final process flow designed in order to produce new and improved devices.

The next sections are each dedicated to an each step of the process in order to examine them in depth manner. The last session provides a summary of the set process flow.

# 3.1 Silicon Oxide Deposition

#### 3.1.1 Introduction

Silicon dioxide (SiO<sub>2</sub>) films have found applications in many areas, such as optics, electronics, tribology, etc [1, 2]. Silicon dioxide films are extensively used as low-index films in multilayer optical devices, scratch resistant coatings for plastic ophthalmic lenses and so on. In silicon microelectronics and power electronics, SiO<sub>2</sub> films are generally employed for diffusion masking and passivation or protection of silicon devices as well as gate oxide film formation in MOS capacitors [3].

The usual methods employed for forming silicon dioxide films involve oxidation of silicon at elevated temperatures (T > 900°C). However, the high-temperature processing

Chapter 3 The process flow

results in junction degradation. There are many low-temperature methods used in the preparation of SiO<sub>2</sub> films, such as evaporation, pyrolytic decomposition, plasma enhanced chemical vapor deposition, reactive sputtering and radio frequency (rf) magnetron sputtering. Film composition as well as deposition and post-deposition processing conditions strongly affect film microstructure, and, consequently, many of its macroscopic properties. A global optimization of the film properties and deposition conditions are necessary in preparing SiO<sub>2</sub> films for applications in a specific field [1, 2, 3]. The oxygen mixing confirms that the film properties of sputter-deposited films can be considerably improved to the same level as those of thermal oxide film [3].

# 3.1.2 Objective

In the present study, the first process flow step involves the deposition of a thin layer of silicon dioxide in order to electrically insulate the desired portion of the wafer surface during the final electroplating deposition. For this specific application, there is no need to have a silicon dioxide film with certain breakdown characteristics. In this case, this film must isolate selected parts of the underlying substrate in order to make effective the electroplating deposition and then it will be totally removed. Thus, it will not give any contribution to the final device working.

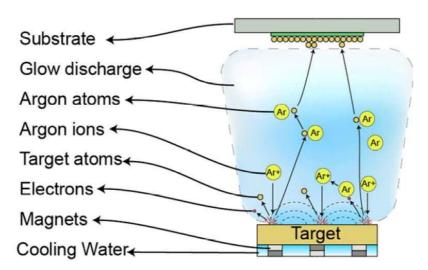

# 3.1.3 Sputtering basic principle

Silicon dioxide films were prepared by radiofrequency (rf) magnetron sputtering. Sputtering is a physical vapor deposition (PVD) process used for depositing materials onto a substrate, by ejecting atoms from such materials and condensing the ejected atoms onto a substrate in a high vacuum environment.

The basic process is as follows [4] and is shown in figure 3.1. Electrically neutral Argon atoms are introduced into a vacuum chamber at a pressure of 10<sup>-5</sup> to 10<sup>-6</sup> Torr. A DC voltage is placed between the target and substrate which ionizes Argon atoms and creates a plasma, hot gas-like phase consisting of ions and electrons, in the chamber. This plasma is also known as a glow discharge due to the light emitted. These Argon ions are now charged and are accelerated to the anode target. The forceful collision of these ions onto the target ejects target atoms into the space. These ejected atoms then travel some distance until they reach the substrate and start to condense into a film. Electrons released during Argon ionization are accelerated to the anode substrate, subsequently colliding with additional Argon atoms, creating more ions and free electrons in the process, continuing the cycle. As more and more atoms coalesce on the

substrate, they begin to bind to each other at the molecular level, forming a tightly bound atomic layer. One or more layers of such atoms can be created at will depending on the sputtering time, allowing for production of precise layered thin-film structures.

There are a number of ways to enhance this process. One common way to do this is to use what is known as a magnetron sputtering system. The main difference between this and a basic DC sputtering system described above is the addition of a strong magnetic field near the target area. This field causes traveling electrons to spiral along magnetic flux lines near the target instead of being attracted toward the substrate. The advantage of this is that the plasma is confined to an area near the target, without causing damages to the thin film being formed. In addition, electrons travel for a longer distance, increasing the probability of further ionizing Argon atoms. This tends to generate a stable plasma with high density of ions. More ions mean more ejected atoms from the target, therefore, increasing the efficiency of the sputtering process. The faster ejection rate, and hence deposition rate, minimizes impurities to form in the thin-film, and the increased distance between the plasma and substrate minimizes damage caused by stray electrons and Argon ions. A way to measure the target deposition rate is the sputtering yield. The sputtering yield is defined as the number of target atoms released per incident Argon ion with certain kinetic energy. For example, if two target atoms are released per collision with an Argon ion, the sputtering yield is two.

Fig. 3.1 The basic principles of a magnetron sputtering system [4].

To sputter conducting targets, a DC power supply is generally used. For insulating or semiconducting targets, an RF power supply is required with an automatic or manual impedance matching network between the power supply and the sputtering gun. The

magnetron sputtering guns are designed to work with any DC and RF power supplies for sputtering applications.

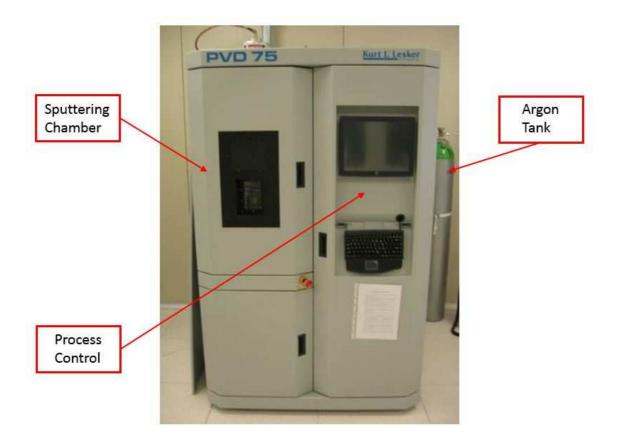

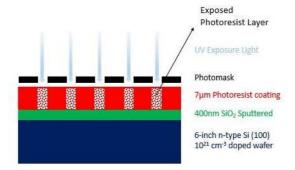

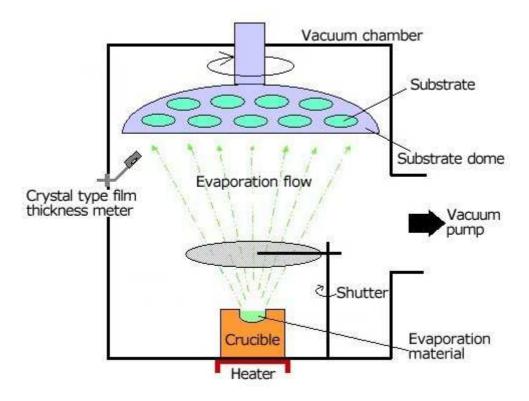

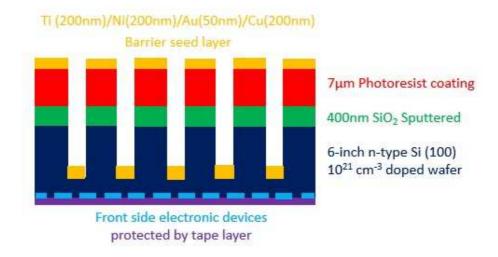

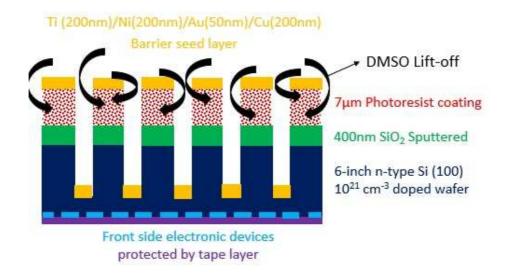

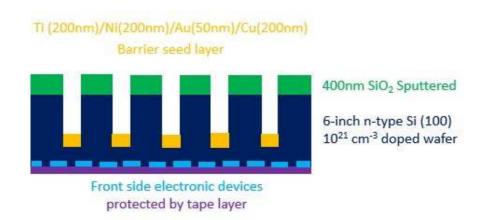

## 3.1.4 Equipment details and results

Silicon dioxide films were prepared by using a commercial RF magnetron sputtering system PVD 75 Pro Line Thin Film Deposition System (Kurt J. Lesker Company, England) available at TechFab, a Trustech Innovation Technology Laboratory, Chivasso (TO) (Fig. 3.2). The sputtering target was a 1 inch hot-pressed SiO<sub>2</sub> ceramic (99.995% purity) supplied by Superconductive Components, USA. The substrates employed were 6-inch n-type Si (100)  $10^{21}$  cm<sup>-3</sup> doped wafers supplied by Vishay Semiconductor Company of Borgaro Torinese (TO). The substrate was fixed directly above the target and a mechanical shutter was attached to it. An Argon/Oxygen (5%) gas mixture was introduced through a mass flow controller after the vacuum chamber was evacuated to about  $2x10^{-6}$  Torr. The RF power supply was set at 150W. The growth rate was about 1.8nm/min. Before deposition, the target was usually pre-sputtered for some minutes to remove any contaminants and eliminate any differential sputtering effects with 100W RF power. The whole process duration is a bit more than 4 hours per wafer.

Fig. 3.2 Commercial RF magnetron sputtering system PVD 75 (Kurt J. Lesker Company, England) available at TechFab, Chivasso (TO) used for silicon dioxide deposition [5].

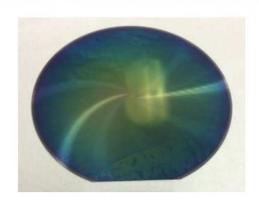

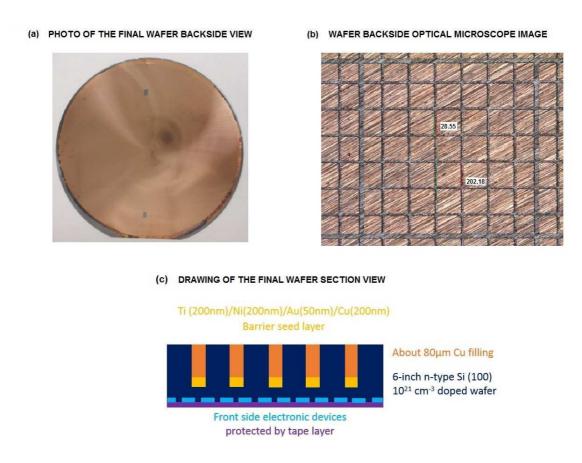

The final SiO<sub>2</sub> film thickness was 400nm. This thickness choice is due to the needed of an insulating layer that must also be thinner in order to permit a fast etching during DRIE process (see Section 3). The faster silicon dioxide plasma etching, the lower the damage at the hard mask. It is important that the hard mask will not be completely removed during DRIE etching. The reason will be understood in details in Section 3.5. Figure 3.3 shows the six-inch wafer backside view after the deposition of 400nm of silicon dioxide layer and the correspondent drawing of the section view. This sketch will be useful throughout the third Chapter (to note that the drawing is not in scale).

#### (a) PHOTO OF THE FINAL WAFER BACKSIDE VIEW

#### (b) DRAWING OF THE FINAL WAFER SECTION VIEW

Fig. 3.3 6-inch silicon wafer after  $SiO_2$  deposition; (a) Picture of the final wafer backside view; (b) Sketch of the final wafer section view not in scale.

# 3.2 Photolithography

### 3.2.1 Introduction

Photolithography is a fundamental process in modern semiconductor manufacturing to build the complex structures that make up a device, such as diodes and transistors, and the many wires that connect the millions of components of a circuit. Simple layers of thin films do not make a device. To create a device, layers of thin films have to be patterned, etched and coated. Photolithography combines these processes and can create millions of devices in batch [6, 7].

Photolithography steps are repeated at least 10 times, but more typically are done 20 to 30 times to make one circuit. Due to the large number of photolithography steps needed

in semiconductor manufacturing, this process typically accounts for about 30 percent of the cost of the total fabrication [6, 7].

Photolithography is an optical process of transferring geometric shapes on photomasks to the surface of a substrate. This technique generally involves stages as wafer cleaning, photoresist coating, soft backing, mask alignment, exposure, development, hard backing and post process cleaning.

A Photoresist useful for semiconductor device manufacturing, must exhibit several characteristics in addition to photosensitivity and acid resistance, they are listed below.

- Coating: must be able to form a thin, uniform, pinhole free film.

- Adhesion: adheres to the underlying substrate and does not lift off during subsequent processing.

- Sensitivity: must be sensitive to the wavelength of radiation utilized for exposure.

- Resolution: the ability to resolve the required minimum feature size being printed.

- Developing: must exhibit a significant difference in develop rate between the exposed and unexposed areas without pattern distortion.

- Process resistance: withstands plasma etch processes, high dose ion implantation, and wet etchants.

- Easy removal: must be removable by following processes.

- Thermal stability: must withstand bake processes without pattern distortion.

- Stability: the formulation must be stable enough to be stored for reasonable periods without requiring prohibitively difficult storage conditions.

- Safety: the material cannot present an acceptable health hazard.

Practical photoresists meeting above criteria are generally composed of three major components as follows.

- The polymer that is the backbone of the photoresist. Following exposure and developing the polymer is the major constituent of the patterned photoresist film.

- Photo active compound (PAC) which is the constituent of the photoresist that undergoes a reaction when exposed to light. The photoactive compound may be combined with the polymer.

- Solvent that keeps the photoresist in liquid form until after coating.

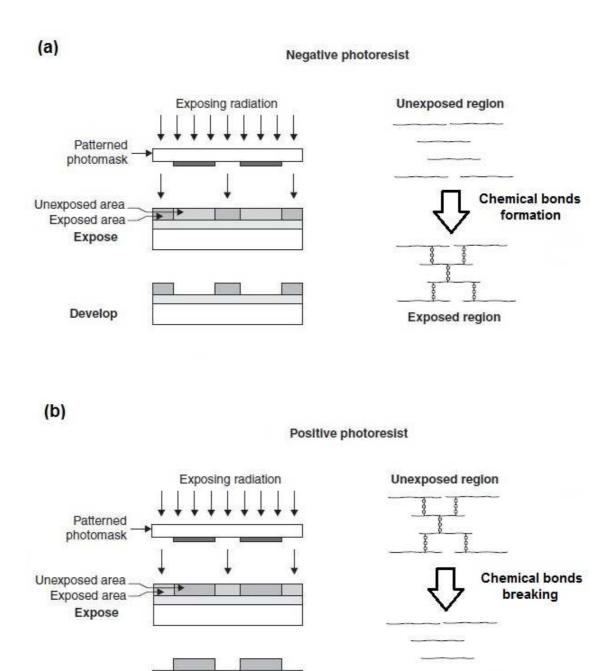

Photoresist may be classified as negative or positive photoresist.

• Negative photoresist: relatively developer soluble until exposed to light at which point the exposed portion exhibits decreased developer solubility.

• Positive photoresist: relatively developer insoluble until exposed to light at which point the exposed portion exhibits increased developer solubility.

Figure.3.4 illustrates negative and positive photoresist behavior during photolithography process. In case of negative photoresist, the light makes chemical bonds and the exposed parts will not be removed during developing. On the other hand, the light cause a bond breaking when a positive photoresist is exposed, thus the exposed parts will be removed during developing.

Fig. 3.4 Comparison between negative and positive photoresist; (a) photolithography process with a negative photoresist: only exposed parts survive; (b) photolithography process with a positive photoresist: only non-exposed parts remains on the substrate after developing [6].

**Exposed region**

# 3.2.2 Objective

Develop

The aim of this process step is to transfer the desired geometric pattern to a light sensitive thick polymer in order to further etch the silicon dioxide sputtered film and the below wafer substrate according to the chosen geometry.

The photoresist thickness required is related to the next etching step (described in next Section 3.3); in fact, this photoresist layer acts as a protective layer against subsequent plasma etching. During the plasma etching, it is important that the photoresist be not completely consumed.

## *3.2.3 Coating*

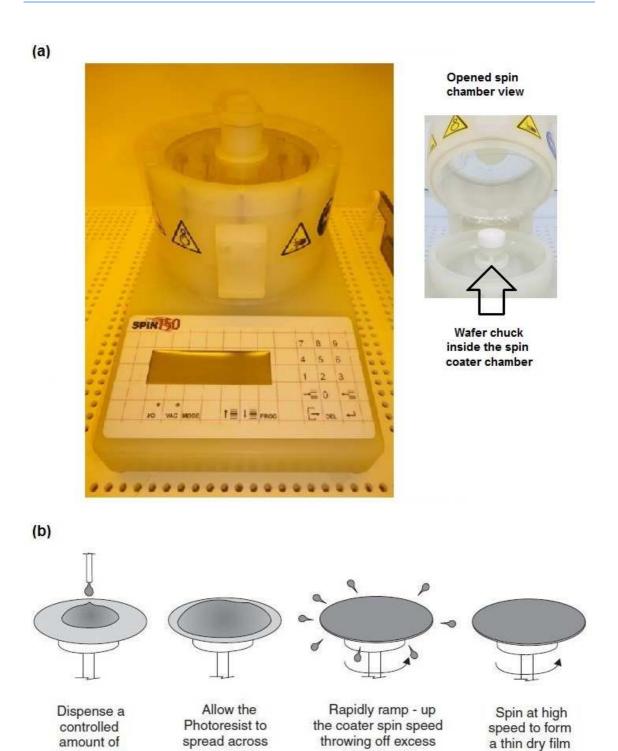

During the spin coating process, a controlled photoresist volume is dispensed onto the wafer substrate; then the wafer is spun at a high speed to produce a uniform, partially dried, photoresist film.

Before the photoresist coating, a wafer dehydration is required on 120°C hot plate for 5 min. Thick positive photoresist AZ9260 [8] was employed for coating purpose by SPS Spin 150 Spin Coater (SPS Europe) [9]. The equipment and the basic coating process are illustrated in figure 3.5a and 3.5b respectively.

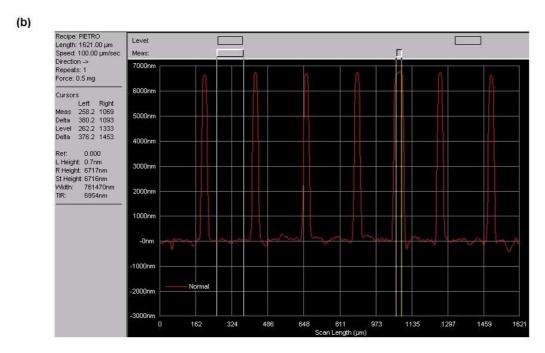

A controlled photoresist volume (about 20ml) was manually dispensed onto the center of the wafer. The coater offers a vacuum secured sample holder. The initial dispense was done with the wafer static. The photoresist is allowed to spread through the wafer rotating at a 500 RPM for 5s; then, the wafer is rapidly ramped up to a high spin speed, 2400 RPM, for 60s producing a uniformly layer with the desired thickness (from 7 up to  $10 \mu m$ ).

The spin coater bowl is properly designed to avoid the photoresist droplets splash back onto the wafer surface causing a non-uniform coat.

After the spin coating, the photoresist still contains too much solvent for a sufficient difference to exist in developing rates between the exposed and unexposed portion of the photoresist. In order to reduce the residual solvent level in the photoresist, a soft bake step is employed at 100°C hot plate for 10 min. Afterwards wafer hydration is required for about 1 hour – 1 hour and a half.

## 3.2.4 Exposure

### 3.2.4.1 Overview

Although photolithography experts have been predicting the end of optical lithography since the mid-eighties, optical lithography remains the methodology of choice for

patterning wafers in semiconductor manufacturing. The optical exposure of a wafer can occur through different techniques and tools.

The first commercially available exposure tool was the contact printer introduced in 1964.

A photomask containing a pattern for an entire wafer is brought into contact with the wafer to be patterned, hence the name contact printer.

Proximity printing system are very similar to contact printing systems with an illumination system that is typically more optimized for collimated light and a small gap introduced between the mask and wafer (5 up to  $20 \, \mu m$ ).

Fig. 3.5 (a) SPS Spin 150 Spin Coater used for photoresist coating with opened spin chamber view [10, 11]; (b) Photoresist spin coating process [6].

Photoresist

the wafer

of Photoresist

photoresist

Projection printers have mask-wafer separation distances measured in centimeters and utilize lens systems to focus the mask image onto the wafer. The mask image is reproduced at the same size on the wafer, thus there is one-to-one systems (1:1).

In a step and repeat system a reticle is used that contains the patterns for one or more chips but does not contain enough chip patterns to pattern a whole wafer in one exposure. The reticle pattern is exposed onto the wafer and then the wafer stage "steps" the width of a patterned area and exposes the wafer again. By stepping and exposing multiple times the entire wafer area can be patterned.

The step and scan system is similar to step and repeat system with the difference that moves wafer and lenses contemporary. The basic principle of step and scan is that lens system is stepped to a location in the wafer and then a slit image through the lens scans the reticle image onto the wafer.

The step-and-scan approach uses a fraction of a normal stepper field (for example, 25mm x 8mm), then scans this field in one direction to expose the entire 4 x reduction mask. The wafer is then stepped to a new location and the scan is repeated.

There are some non-optical alternatives in lithography based on the utilized source used for exposure step. Extreme Ultraviolet (EUV), X-ray Lithography (XRL), Electron beam systems, Ion projection lithography (IPL). As long as economical optical lithography alternatives exist, the industry will make the safe choice and stay with optical lithography.

Of course, there are maskless lithographic techniques based either on a charged particle maskless or optical maskless methods like zone plate array lithography (ZPAL), doppen lithography (DPL), multiaxis electron beam lithography (MAEBL), scanning electron beam lithography (SEBL), focused ion beam lithography (FIBL), interference lithography (IL), maskless optical projection lithography (MOPL), and so on. Therefore, these endeavors require expensive instrumentation and or controlled experimental environments and none of them can be considered as a fast cost effective prototyping tool for microfabrication [14].

### 3.2.4.2 Experimental

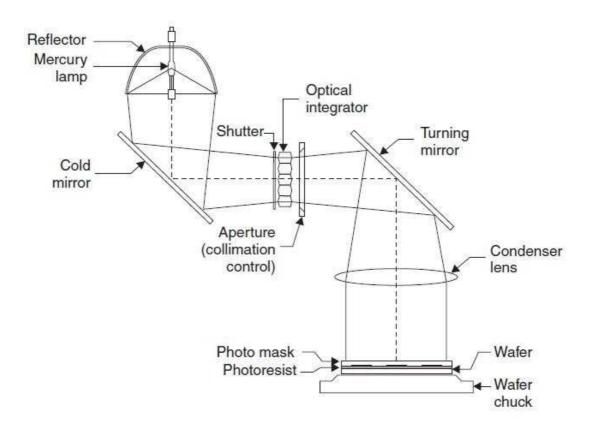

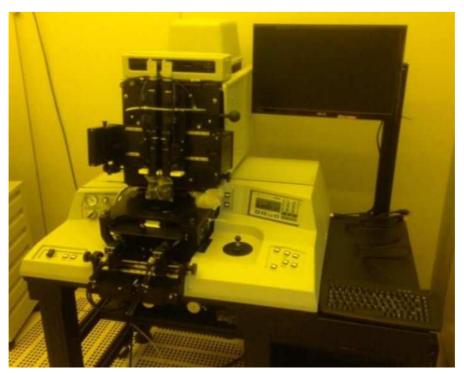

The adopted lithography technique in the thesis project is the optical exposure by the contact printer. The contact printer system is illustrated in figure 3.6 and consists of the following elements.

• A mercury arc lamp centered in a parabolic or ellipsoidal reflector to collect the lamp light and direct the light into the aligner optics. The mercury lamp emits light from an area a few mms across so the lamp acts like a point source.

- A cold mirror to redirect the light and provide wavelength filtration.

- A shutter to control the time the wafer is exposed to light.

- An optical integrator creates multiple light images that are then recombined to improve uniformity.

- An aperture to block divergent light rays outside a controlled area.

- A turning mirror to turn the light towards the wafer.

- A condenser lens to create parallel light rays.

- The photomask.

- The photoresist coater wafer.

Fig. 3.6 Contact printer drawing [6].

A vacuum chuck may be moved in two horizontal directions and also move up and down a controlled distance to bring the mask and wafer in and out of contact.

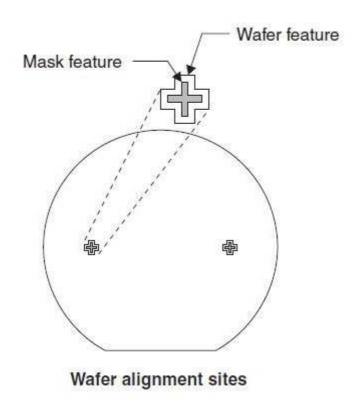

In order to expose the wafer, the photomask is loaded and rotationally aligned looking through the microscope. The rotational alignment insures the mask edges are parallel to the front of the aligner. The wafer is then manually loaded onto specific chuck aligning its flat side parallel to the front of the aligner.

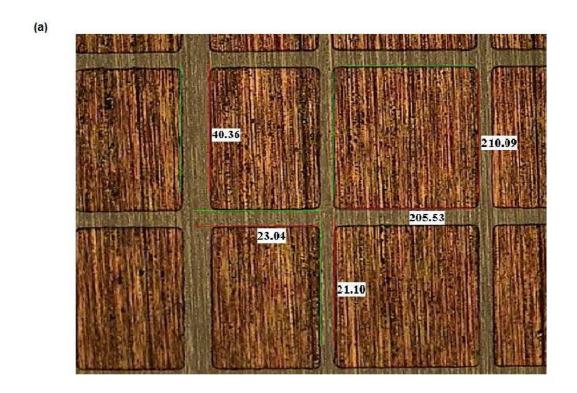

Since the wafer front side already has electrically good devices, there is a previous pattern on it, thus the alignment marks, which typically are crosses of boxes out toward both sides (see figure 3.7). It is necessary to pattern the back side of the wafer faithfully to the front side devices, hence the box crosses on the mask and the ones on the wafer will be properly designed. The cross set on the mask are smaller than the one on the wafer. If both crosses are centered in both sides of the wafer, the alignment is correct.

The wafer and mask must be separated during the alignment procedure so they may move independently. It is possible to put the mask and wafer in and out of contact several times during the alignment process.

Once alignment is achieved the wafer is brought up into contact with the mask and the shutter opens for a controlled time exposing the wafer.

Fig. 3.7 Alignment marks [6].

Figure 3.8 shows the NXQ4006 mask aligner [12] used for the exposure of the previously coated substrate. It supports Soft/Hard pressure contact and Vacuum contact printing. The system can also print in Manual Proximity mode. It can process partial and whole substrates up to 200mm (8-inch) diameter and can be optionally equipped

with Backside Alignment and UV Nano Imprint Lithography. This aligner permits setting the pressure of the contact mode.

In order to avoid any misalignment between the front side devices and the related backside pattern, the equipment was adapted in backside alignment mode. Moreover, the exposure process was performed in contact mode with an exposure time of 180s.

During the exposure process, UV light shines through the mask, which blocks light in chrome patterned areas and lets it transmit to other transparent blanks. The transmitted light falls onto the photoresist where the exposed areas are modified distinctly than that of the unexposed areas by photochemical reactions.

The photomasks are hence an integral component in the entire procedure and manufactured by industrial companies using highly precise techniques like electron beam lithography. Quality masks are generally very expensive and depending on the complexities of intended structure, several lithographic steps with several masks are needed for fabricating one structure resulting in escalating mask costs per design to thousands of euro.

Fig. 14 The NXQ Mask Aligner Equipment [13].

The photomask allows selective irradiation of resist on the wafer surface by blocking irradiation in selected areas; consist of opaque (non-transparent to given wavelengths) and blank (transparent) parts; in photolithography chrome, and quartz respectively. These masks used in photolithography to block resist exposure to UV radiation in

selected areas; consists of chrome opaque areas supported by high quality quartz plate transparent to UV radiation.

If a particle lands on a mask or reticle (the term reticle will be used to include both masks and reticles from this point forward) and the particle is larger than the minimum resolution of the exposure system, the particle will print on every wafer exposed with the reticle in question. Reticles are typically manufactured by patterning a chrome layer on one side of a glass plate. Particles falling on the un-patterned side of the reticle will generally be out of focus and not printed, therefore only the patterned side of the reticles is susceptible to particle induced defects. If a thin film is stretched over a frame a small distance above the patterned side of the reticle, any particle falling towards the patterned side of the reticle will be blocked from reaching the pattern and will be out of focus, this is what a pellicle does. Every mask has a set of alignment windows based on the used aligning equipment thus under specific rules.

## 3.2.3 Development

The selective removal of exposed or unexposed photoresist is made possible by resist developers. Consequently, desired patterns are formed in photoresist after the resist development.

Once an image is exposed into a photoresist layer, depending on the tone (negative or positive) of the photoresist, the develop process either dissolves the photoresist that has been exposed or the photoresist that has not been exposed. The developer needs to remove photoresist where removal is desired and have a low attack rate on the photoresist where dissolution is not desired. The developing process must also be chosen to avoid distortion in the resulting photoresist pattern.

Once exposed, the photoresist must be developed. Most commonly used photoresists use aqueous bases as developers. Development is undoubtedly one of the most critical steps in the photoresist process. The characteristics of the resist-developer interactions determine to a large extent the shape of the photoresist profile and, more importantly, the linewidth control.

The method of applying developer to the photoresist is important in controlling the development uniformity and process latitude. In the past, batch development was the predominant development technique. A boat of some 10-20 wafers or more are developed simultaneously in a large beaker, usually with some form of agitation. With the push towards in-line processing, however, other methods have become prevalent. During spin development wafers are spun, using equipment similar to that used for spin coating, and developer is poured onto the rotating wafer. The wafer is also rinsed and dried while still spinning. Spray development has been shown to have good results

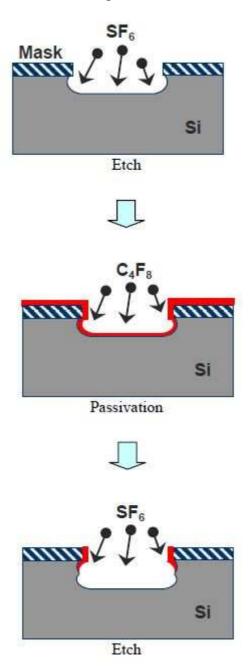

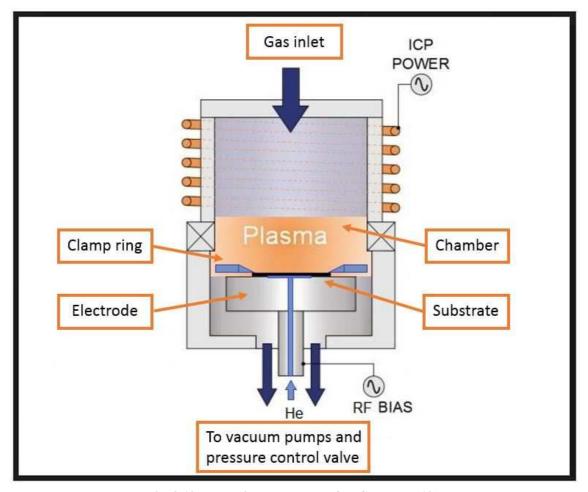

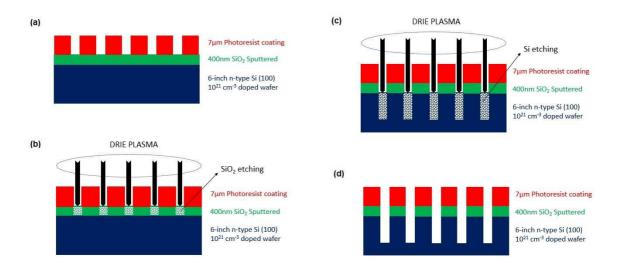

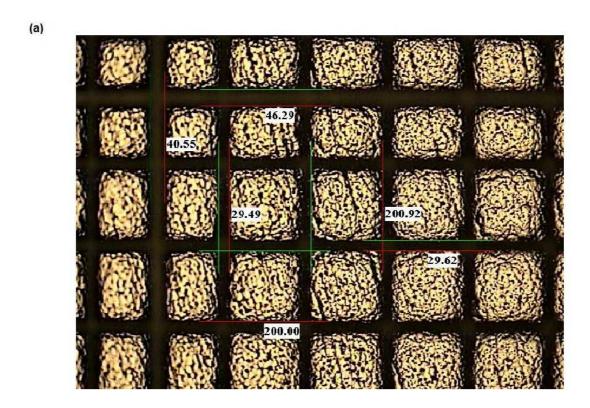

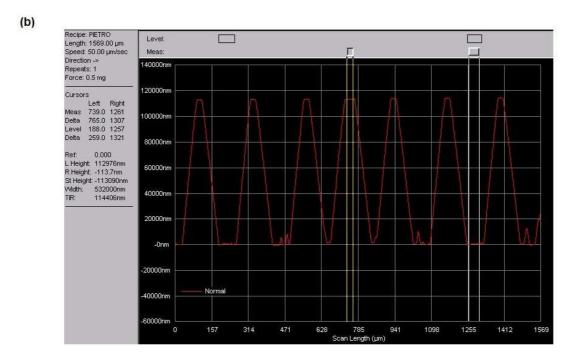

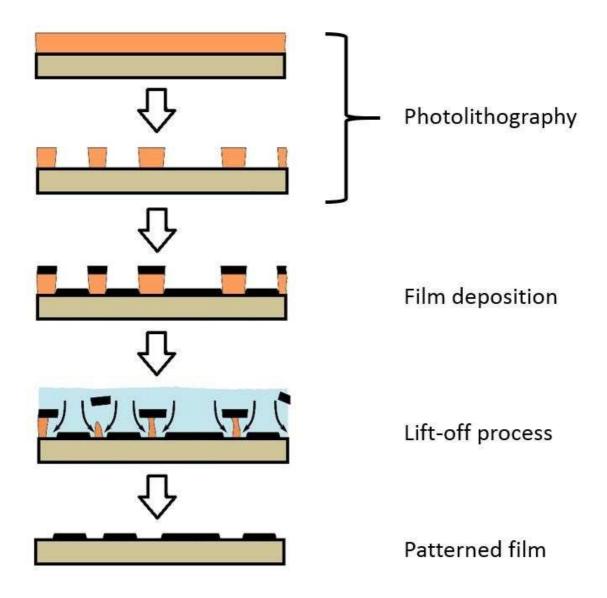

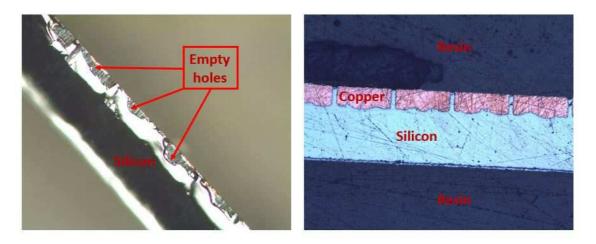

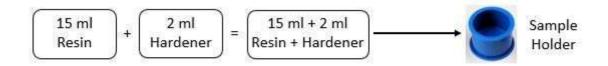

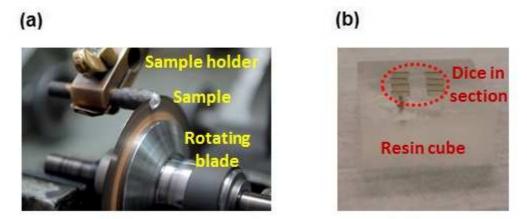

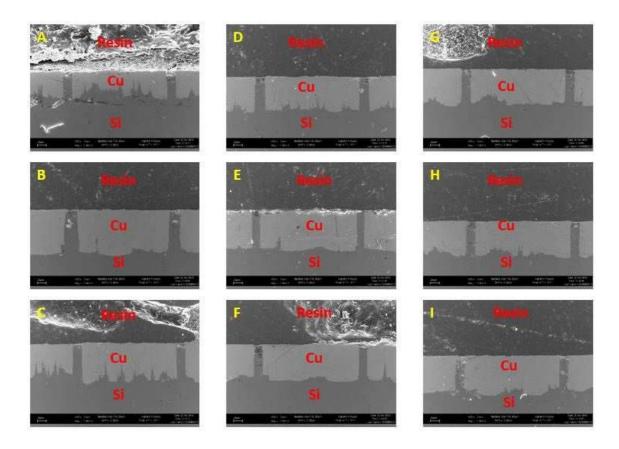

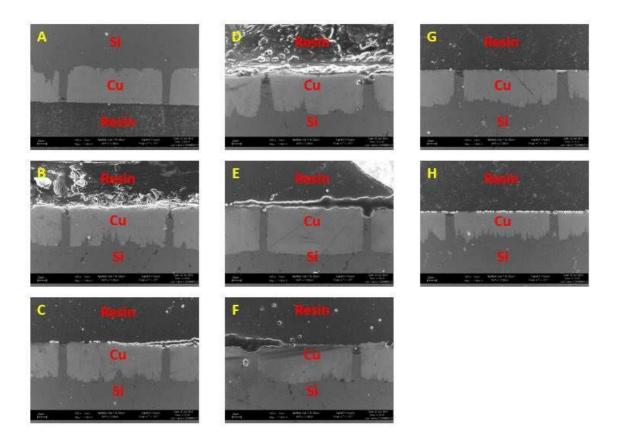

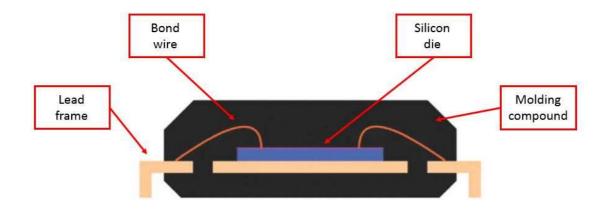

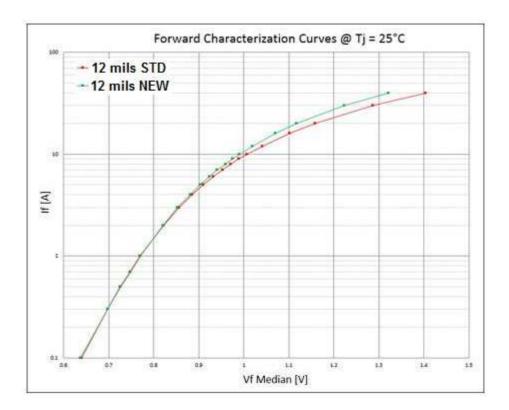

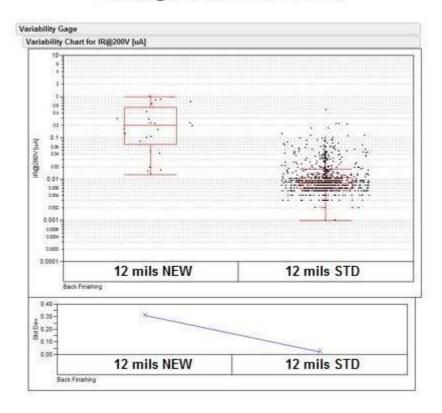

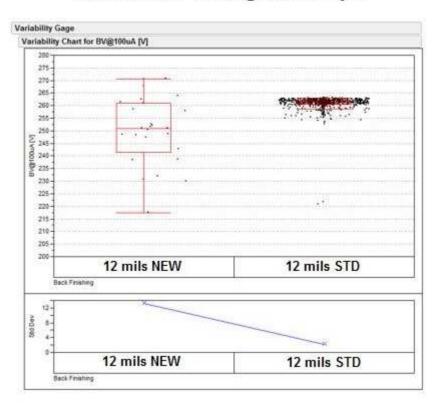

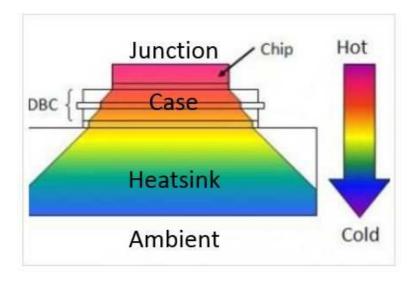

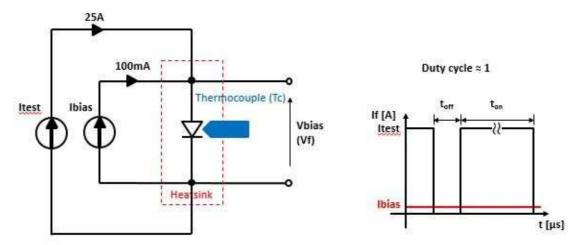

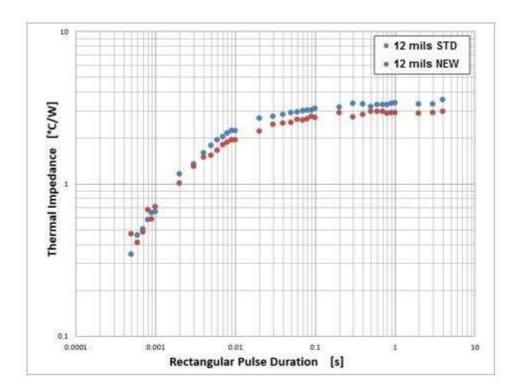

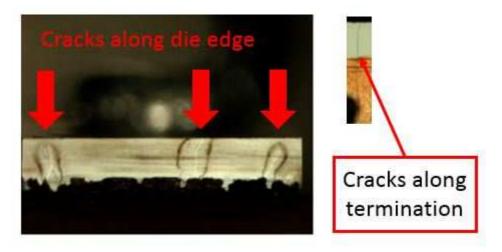

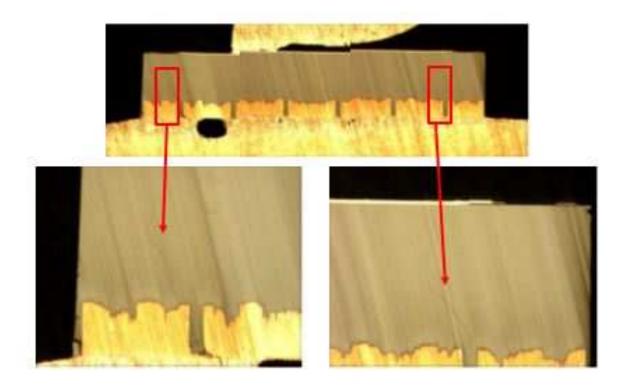

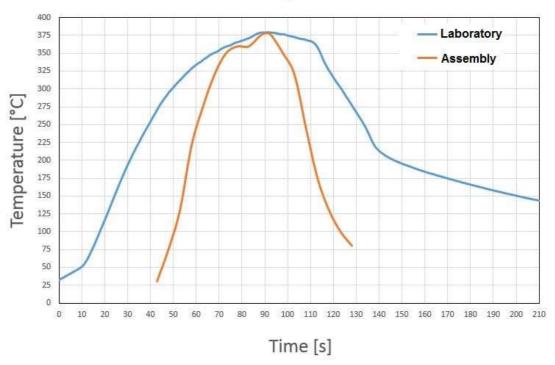

using developers specifically formulated for this dispense method. Using a process identical to spin development, the developer is sprayed, rather than poured, on the wafer by using a nozzle that produces a fine mist of developer over the wafer (Figure 1-8). This technique reduces developer usage and gives more uniform developer coverage. Another in-line development strategy is called puddle development. Again using developers specifically formulated for this process, the developer is poured onto a stationary wafer that is then allowed to sit motionless for the duration of the development time. The wafer is then spin rinsed and dried. Note that all three in-line processes can be performed in the same piece of equipment with only minor modifications, and combinations of these techniques are frequently used.