Doctoral Dissertation Doctoral Program in Electronic Engineering (29<sup>th</sup> Cycle)

# Advanced High Efficiency and Broadband Power Amplifiers Based on GaN HEMT for Wireless Applications

By

Mustazar Iqbal

\*\*\*\*\*

**Supervisor(s):**

Prof. Marco Pirola, Supervisor

#### **Doctoral Examination Committee:**

Prof. Alessandro Cidronali, University of Firenze Prof. Antonio Raffo, University of Ferrara

> Politecnico di Torino 2016

## **Declaration**

Mustazar Iqbal

2016

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

## Acknowledgment

Foremost, I would like to express my sincere gratitude to my adviser Professor Marco Pirola, for the continuous support of my PhD study and research, for his patience, enthusiasm, motivation and extensive knowledge. He has been my research adviser since I started my PhD degree and I have always been honored of working under his supervision.

I would also like to thank Professor Wing-Sing Chan from City University of Hong Kong, for giving me the opportunity to continue my research work at State Key laboratory and for his support during my visiting research periods in City University of Hong Kong.

Especially, I would like to express my appreciation to Professor Vittorio Camarchia at Microwave Electronics group of Politecnico di Torino for his immense help on laboratory projects, worthwhile discussions and beneficial guidance throughout my PhD degree.

I would also like to thank Dr. Roberto Quaglia at Cardiff University, U.K. He has been a continued source of support and enthusiasm right from the outset of beginning my PhD. I would also like to thank Assistant Professor Zheng Shaoyong at Sun Yen-Sen University, China for his guidance and material support during this thesis project. I would like to thank the thesis committee for their time and consideration.

Finally, I would like to extend a special gratitude to my family, and all of my friends, in and outside, of university; for all their support and encouragement. My mother and father especially, who have been very willing to help where they could and have always been there for me when I needed them the most. Most importantly, I wish to thank my wife, who has supported me throughout this entire process. Her encouragement and understanding has helped bringing this thesis project to fruition.

#### **Abstract**

In advanced wireless communication systems, a rapid increase in the mobile data traffic and broad information bandwidth requirement can lead to the use of complex spectrally efficient modulation schemes such as orthogonal frequency-division multiplexing (OFDM). Generally, complex non-constant envelope modulated signals have very high peak-to-average ratios (PAPR). Doherty Power Amplifier (DPA) is the most commonly used power amplifier (PA) architecture for meeting high efficiency requirement in advanced communication systems, in the presence of high PAPR signals. However, limited bandwidth of the conventional DPA is often identified as a bottleneck for widespread deployment in base-station application for multi-standard communication signals. The research in this thesis focuses on the development of new designs to overcome the bandwidth limitations of a conventional PA. In particular, the bandwidth limitation factors of a conventional DPA architecture are studied. Moreover, a novel design technique is proposed for DPA's bandwidth extension.

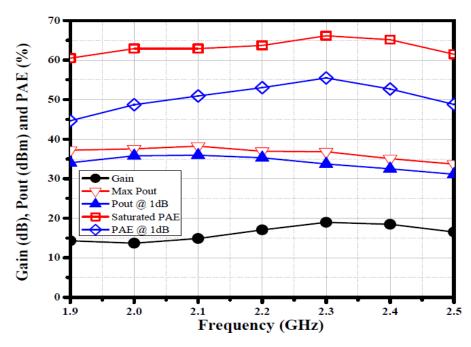

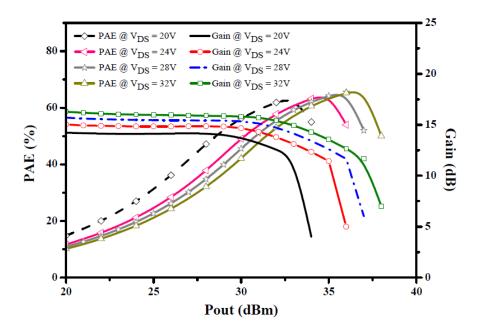

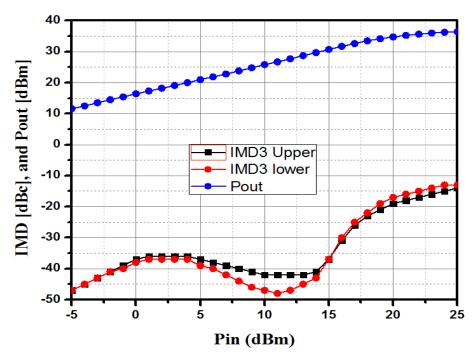

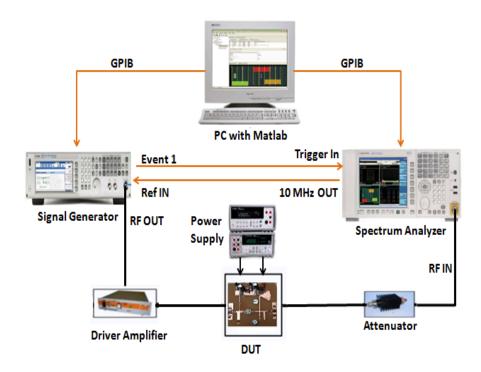

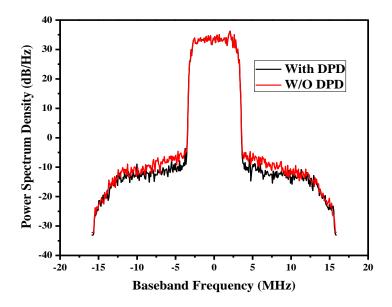

In the first PA design, limited bandwidth and linearity problems are addressed simultaneously. For this purpose, a new Class-AB PA with extended bandwidth and improved linearity is presented for LTE 5 W pico-cell base-station over a frequency range of 1.9–2.5 GHz. A two-tone load/source-pull and bias point optimization techniques are used to extract the sweet spots for optimum efficiency and linearity from the 6 W Cree GaN HEMT device for the whole frequency band. The realized prototype presented saturated PAE higher than 60%, a power gain of 13 dB and an average output power of 36.5 dBm over the desired bandwidth. The proposed PA is also characterized by QAM-256 and LTE input communication signals for linearity characterization. Measured ACPRs are lower than -40 dBc for an input power of 17 dBm. The documented results indicate that the proposed Class-AB architecture is suitable for pico-cell base-station application.

In the second PA design, an inherent bandwidth limitation of Class-F power amplifier forced by the improper load harmonics terminations at multiple harmonics is investigated and analyzed. It is demonstrated that the impedance

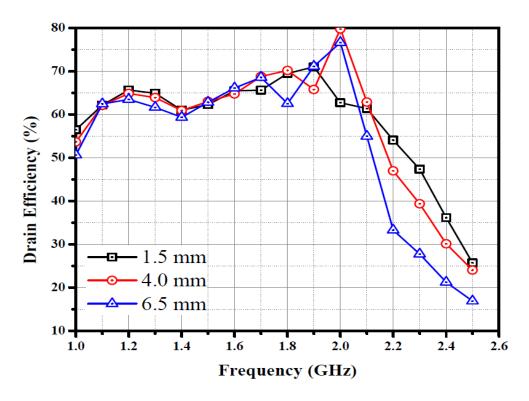

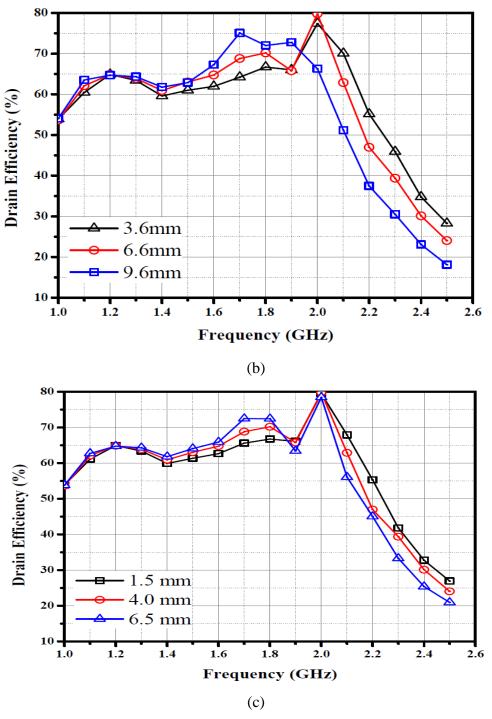

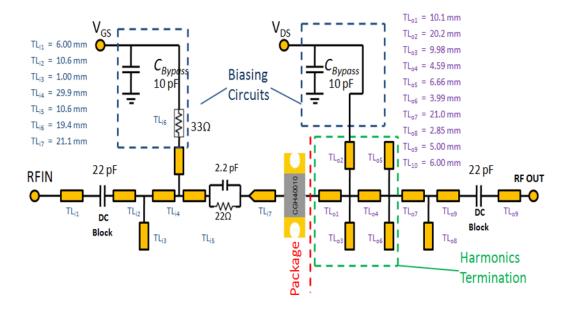

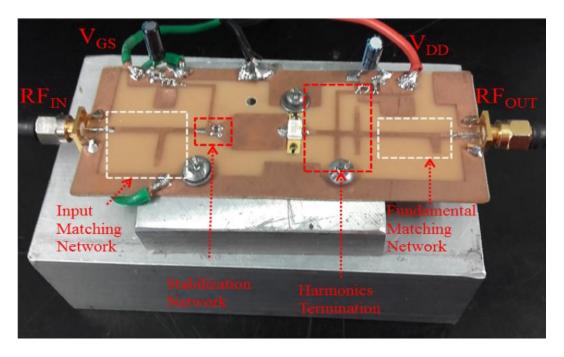

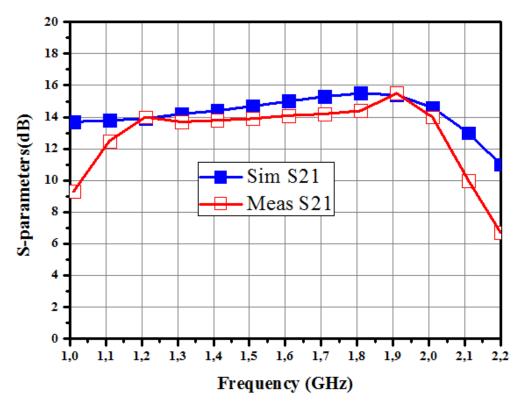

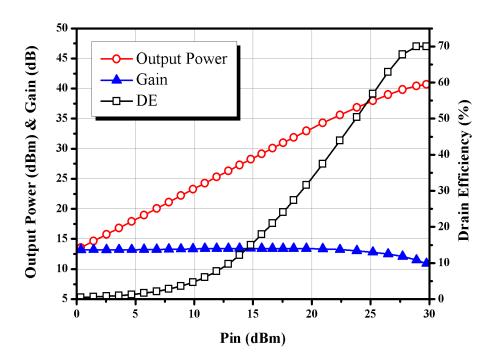

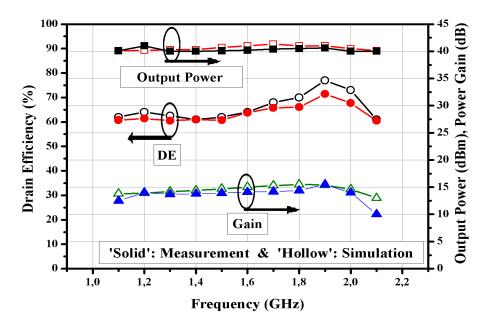

tuning of the second and third harmonics at the drain terminal of a transistor is crucial to achieve a broadband performance. The effect of harmonics terminations on power amplifier's bandwidth up to fourth harmonics is investigated. The implemented broadband Class-F PA achieved maximum saturated drain efficiency 60-77%, and 10 W output power throughout (1.1-2.1 GHz) band. The simulated and measured results verify that the presented Class-F PA is suitable for a high-efficiency system application in wireless communications over a wide range of frequencies.

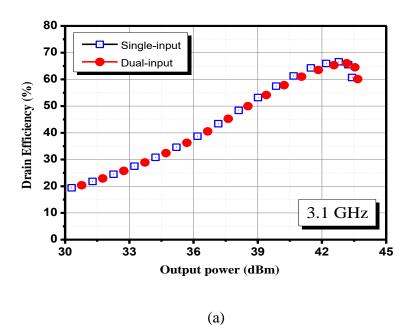

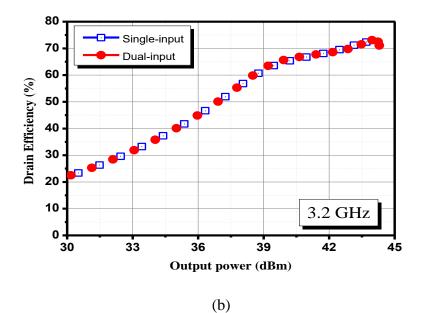

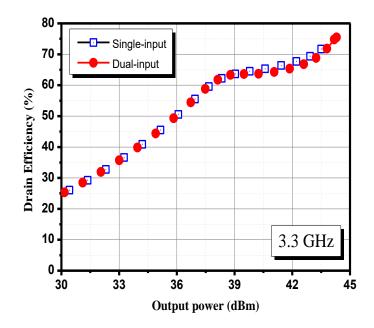

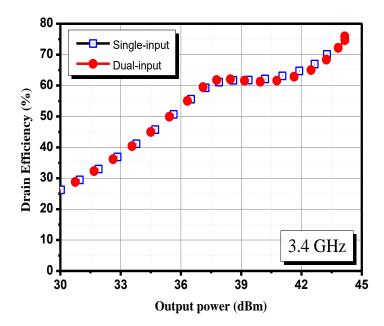

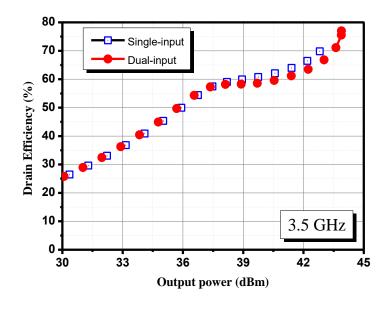

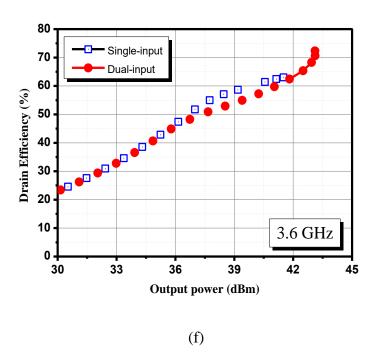

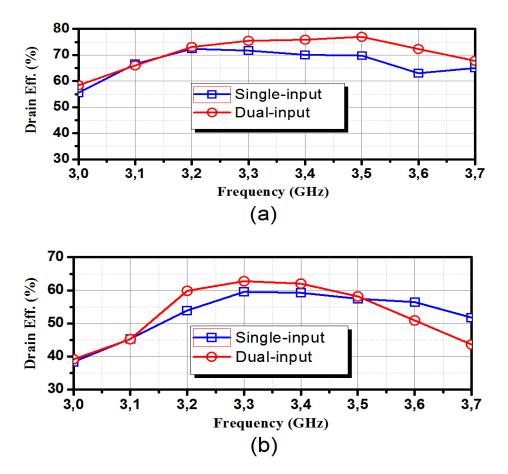

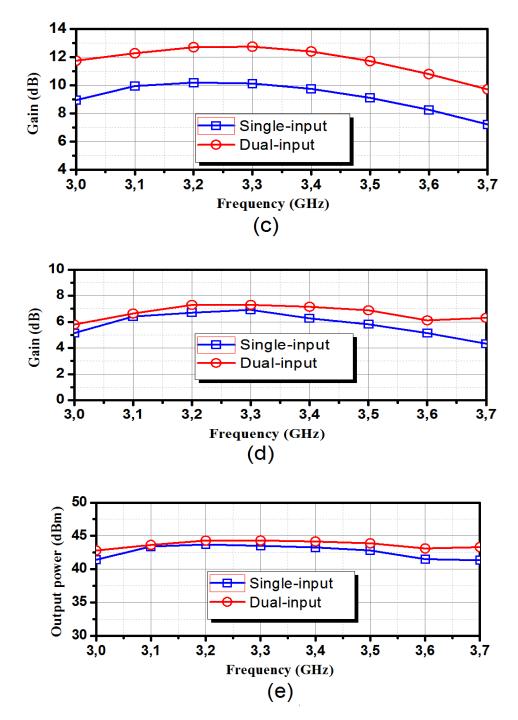

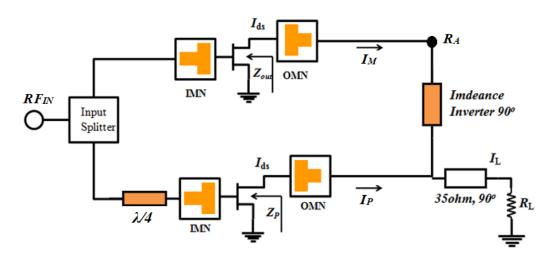

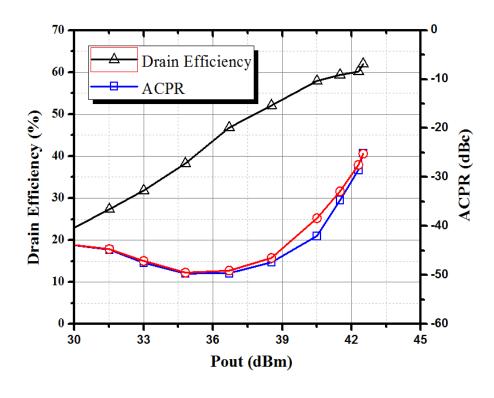

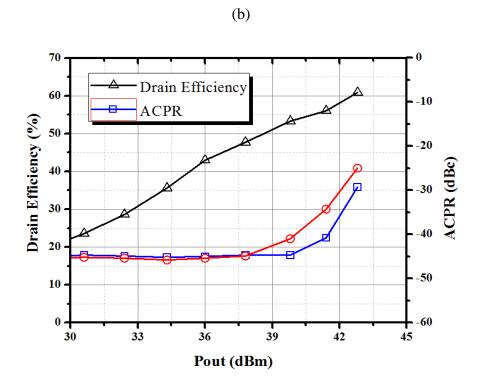

In the third PA design, a single- and dual-input DPA for LTE application in the 3.5 GHz frequency band are presented and compared. The main goal of this study is to improve the performance of gallium–nitride (GaN) Doherty transmitters over a wide bandwidth in the 3.5 GHz frequency band. For this purpose, the linearity-efficiency trade-off for the two proposed architectures is discussed in detail. Simulated results demonstrate that the single- and dual-input DPA exhibited a peak drain efficiency (DE) of 72.4% and 77%, respectively. Both the circuits showed saturated output power more than 42.9 dBm throughout the designed band. Saturated efficiency, gain and bandwidth of dual-input DPA is higher than that of the single-input DPA. On the other side, dual-input DPA linearity is worse as compared to the single-input DPA.

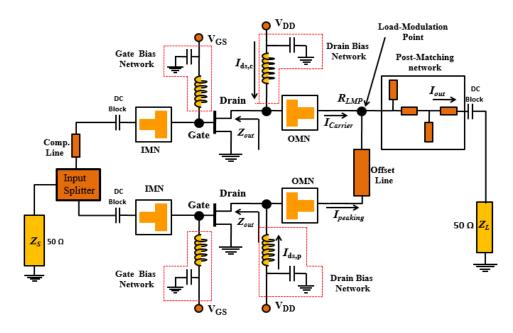

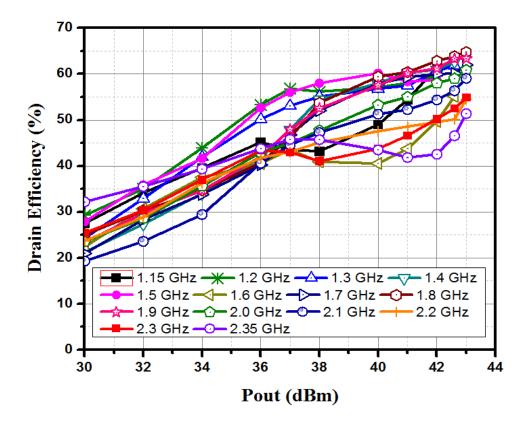

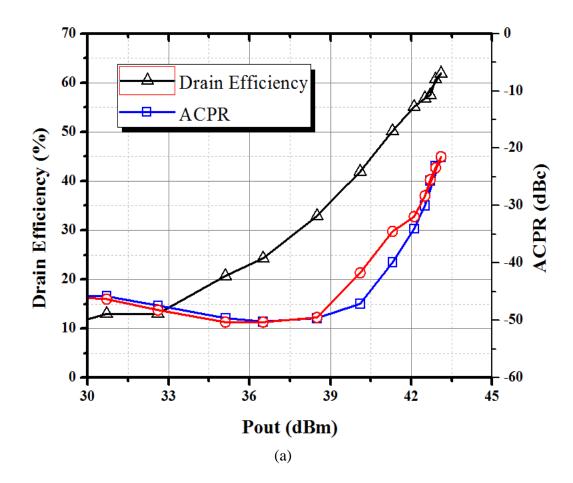

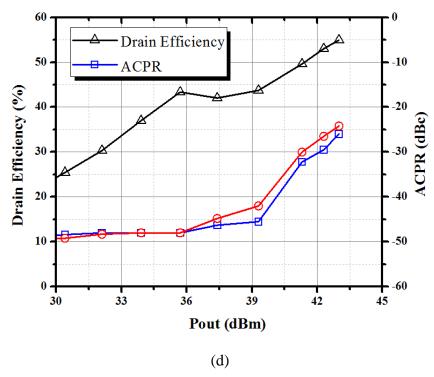

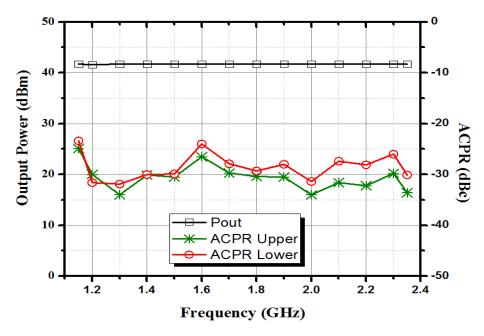

In the last PA design, a novel design methodology for ultra-wide band DPA is presented. The bandwidth limitation factors of the conventional Doherty amplifier are discussed on the ground of broadband matching with impedance variation. To extend the DPA bandwidth, three different methods are used such as post-matching, low impedance transformation ratio and the optimization of offset line for wide bandwidth in the proposed design. The proposed Doherty power amplifier was designed and realized based on two 10 W GaN HEMT devices from Cree Inc. The measured results exhibited 42-57% of efficiency at the 6-dB back-off and saturated output power ranges from 41.5 to 43.1 dBm in the frequency range of 1.15 to 2.35 GHz (68.5% fractional bandwidth). Moreover, less than -25 dBc ACPRs are measured at 42 dBm peak output power throughout the designed band.

In a nutshell, all power amplifiers presented in this thesis are suitable for wideband operation and their performances are satisfying the required operational standard. Therefore, this thesis has a significant contribution in the domain of high efficiency and broadband power amplifiers.

# **Contents**

| 1. | Introduction                                                  |

|----|---------------------------------------------------------------|

|    | 1.1 Motivation1                                               |

|    | 1.2 Problem statement6                                        |

|    | 1.3 Thesis organization                                       |

| 2. | Power Amplifiers Overview9                                    |

|    | 2.1 Introduction9                                             |

|    | 2.2 Power amplifier and FOM9                                  |

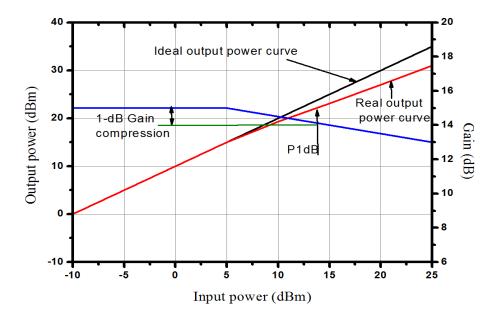

|    | 2.2.1 Gain and gain compression point (P1dB)10                |

|    | 2.2.2 Power efficiency12                                      |

|    | 2.2.3 Intermodulation distortion                              |

|    | 2.3 Power amplifier classes                                   |

|    | 2.3.1 Class-A amplifier                                       |

|    | 2.3.2 Reduced conduction angle modes: Class -AB, -B, -C       |

|    | 2.3.3 Switch-mode Class-F and F <sup>-1</sup> power amplifier |

|    | 2.4 Power amplifier design flow                               |

|    | 2.5 Power amplifier design                                    |

|    | 2.5.1 Device package & de-embedding prasitics25               |

|    | 2.5.2 Bias network and stability27                            |

|    | 2.5.3 Load-pull and source-pull29                             |

|    | 2.5.4 Input matching requirements                             |

|    | 2.5.5 Multi-harmonics output matching network design31        |

|    | 2.6 Summary33                                                 |

| 3. | 5 W Class-AB Power Amplifier                      | 34 |

|----|---------------------------------------------------|----|

|    | 3.1 Introduction                                  | 34 |

|    | 3.2 Class-AB theory                               | 35 |

|    | 3.3 Design specification                          | 36 |

|    | 3.4 Device stability analysis                     | 37 |

|    | 3.5 Matching network design                       | 38 |

|    | 3.5.1 Output matching network                     | 39 |

|    | 3.5.2 Input matching network                      | 43 |

|    | 3.5.3 Bias point optimization                     | 44 |

|    | 3.6 Bias network design                           | 45 |

|    | 3.7 Final design                                  | 47 |

|    | 3.8 Performance evaluation                        | 49 |

|    | 3.8.1 Small-signal testing                        | 49 |

|    | 3.8.2 Single-tone power sweep                     | 50 |

|    | 3.8.3 Two-tone test                               | 52 |

|    | 3.8.4 Modulated signal characterization           | 54 |

|    | 3.9 Summary                                       | 57 |

| 4. | Ultra-wideband Class-F Power Amplifier            | 58 |

|    | 4.1 Introduction                                  | 58 |

|    | 4.2 Class-F theory                                | 59 |

|    | 4.3 Design specification                          | 64 |

|    | 4.4 Device characteristics and model              | 65 |

|    | 4.5 Device stability analysis                     | 66 |

|    | 4.6 Source-pull /load-pull analysis for harmonics | 69 |

|    | 4.7 Output multi-harmonic matching network        | 70 |

|    | 4.8 Input matching network                        | 75 |

|    | 4.9 Effect of harmonic termination on bandwidth   | 75 |

|    | 4.10 PA implementation                            | 79 |

|    | 4.11 Experimental results                            | 80  |

|----|------------------------------------------------------|-----|

|    | 4.12 Summary                                         | 83  |

| 5. | Single- and Dual-Input Doherty PA                    | 84  |

|    | 5.1 Introduction                                     | 84  |

|    | 5.2 Doherty power amplifier theory                   | 85  |

|    | 5.3 Circuit design methodology                       | 89  |

|    | 5.4 Doherty PA designs example from 3.1 to 3.7 GHz   | 89  |

|    | 5.4.1 Wideband carrier matching network              | 90  |

|    | 5.4.2 Wideband peaking matching network              | 93  |

|    | 5.4.3 Input matching network                         | 94  |

|    | 5.3.5 Power dividing network                         | 96  |

|    | 5.5 Final design                                     | 98  |

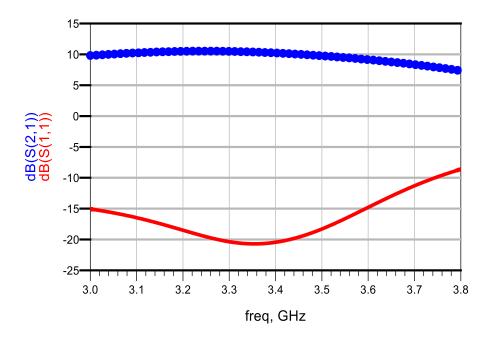

|    | 5.6 Small-signal gain                                | 100 |

|    | 5.7 Single-tone power sweep                          | 100 |

|    | 5.8 Comparison with other publication                | 106 |

|    | 5.9 Summary                                          | 106 |

| 6. | Ultra-Wideband Doherty Power Amplifier               | 107 |

|    | 6.1 Introduction                                     | 107 |

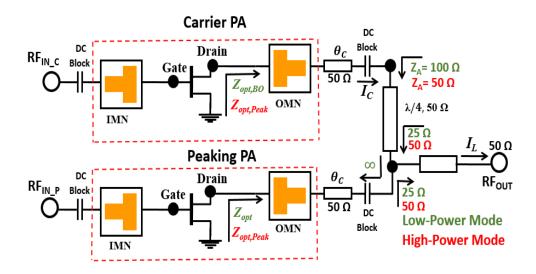

|    | 6.2 Bandwidth limitation factors of conventional DPA | 107 |

|    | 6.2.1 Influence of the impedance inverter            | 108 |

|    | 6.2.2 High impedance transformation ratio            | 108 |

|    | 6.2.3 Quasi-open-circuit requirements                | 108 |

|    | 6.3 A novel Doherty power amplifier                  | 109 |

|    | 6.3.1 Advantages of the proposed design methodology  | 112 |

|    | 6.4 Circuit design methodology                       | 113 |

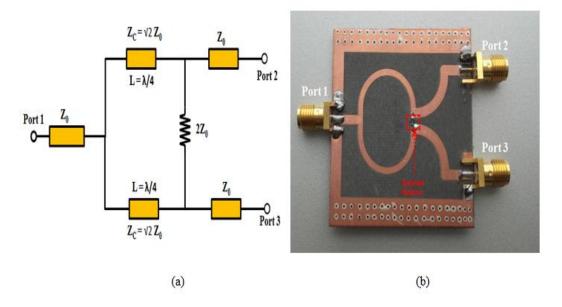

|    | 6.5.1 Power dividing network                         | 115 |

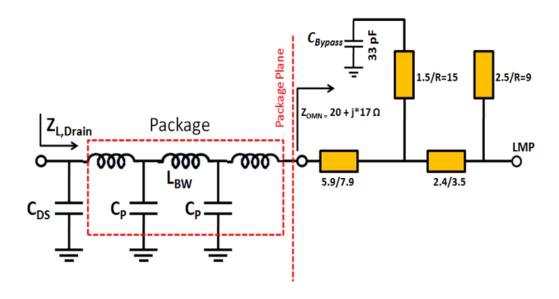

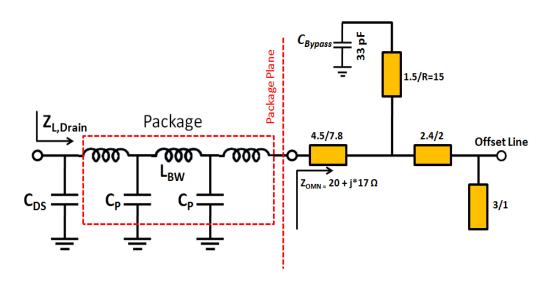

|    | 6.5.2 Carrier and peaking impedance inverters        | 118 |

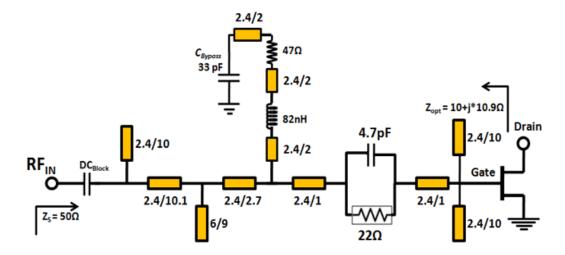

|    | 6.5.4 Input matching network                         | 121 |

|     | 6.5.5 Post-matching network                 |

|-----|---------------------------------------------|

|     | 5.5.6 Offset-line and compensating-line     |

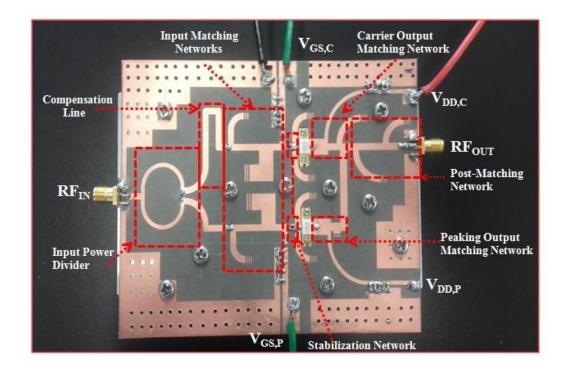

|     | 6.6 Final design                            |

|     | 6.7 Performance evaluation                  |

|     | 6.7.1 Small-signal testing                  |

|     | 6.7.3 Single-tone power sweep               |

|     | 6.7.3 Modulated signal characterization     |

|     | 6.8 Comparison with other published results |

|     | 6.9 Summary141                              |

| 7.  | Conclusion and Future Work                  |

|     | 7.1 Conclusion                              |

|     | 7.2 Future work                             |

| 8.  | Appendix A                                  |

| 9.  | Appendix B147                               |

| 10. | Appendix C                                  |

| 11. | Appendix D                                  |

| 12. | References 152                              |

# **List of Figure**

| Figure 1.1: Evolution of wireless communications                                   | 2           |

|------------------------------------------------------------------------------------|-------------|

| Figure 1.2: Use of OFDM modulation scheme in wireless communication                | ations3     |

| Figure 1.3: An OFDM modulation with four subcarriers.                              | 4           |

| Figure 1.4: An OFDM waveform illustrating with high PAPR                           | 4           |

| Figure 1.5: PAPR effect on power amplifier average efficiency                      | 5           |

| Figure 2.1: A simplified block diagram of a front-end transmitter                  | 10          |

| Figure 2.2: (a) PA gain measurement schematic and (b) gain vs. inpplot.            | _           |

| Figure 2.3: Plot for 1dB compression point of a Class-A power ampli                |             |

| Figure 2.4: Power amplifier concept.                                               | 12          |

| Figure 2.5: Intermodulation lower and upper tones due to non-line [14]             |             |

| Figure 2.6: Simplified diagram of Class-A, -AB, -B and -C amplifier                | 15          |

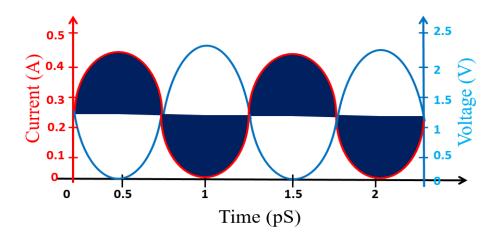

| Figure 2.7: Current and voltage waveforms of a Class-A power ampli                 | ifier16     |

| Figure 2.8: Current and voltage waveforms of a Class-AB power amp                  | olifier. 17 |

| Figure 2.9: Current and voltage waveforms a of Class-B power ampli                 | fier 18     |

| Figure 2.10: Current and voltage waveforms a of Class-C power amp                  | lifier18    |

| Figure 2.11: Class-F power amplifier topology with ideal infinite termination.     |             |

| Figure 2.12: Ideal drain voltage and current waveforms for a Class amplifier [22]. |             |

| Figure 2.13: Flow chart of a typical power amplifier.                              | 24          |

| Figure 2.14: Generic block scheme of a single-stage Microwave amp                  | lifier25    |

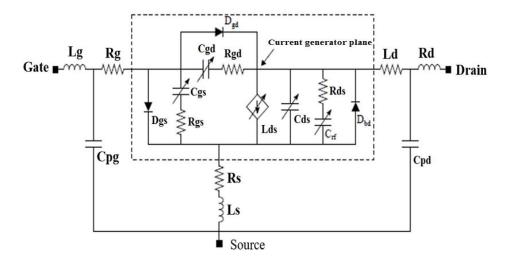

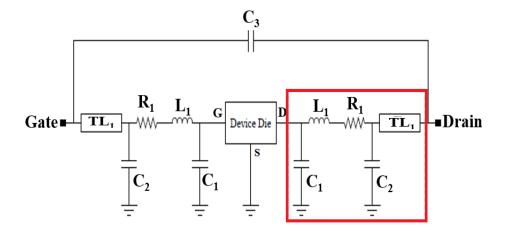

| Figure 2.15: A generic signal model [23].                                          | 26          |

| Figure 2.16: A typical device package model.                                       | 26          |

| Figure 2.17: A simplified lead and source pull setup                               | 20          |

| Figure 2.18: Input matching network between RF source and input side active device [4]                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

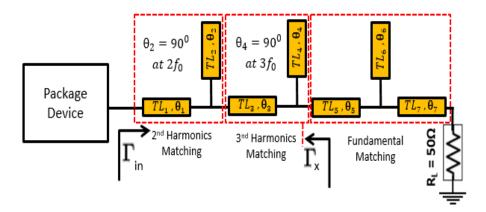

| Figure 2.19: A multi-harmonic output-matching network with harmonics control                                                                                                                                         |

| Figure 3.1: Block diagram of a single-stage Class-AB power amplifier circuit.                                                                                                                                        |

| Figure 3.2: Voltage and current waveforms of an Ideal Class-AB PA36                                                                                                                                                  |

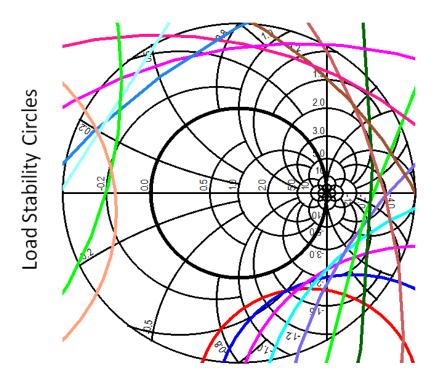

| Figure 3.3: Load stability circle of the designed PA after adding stability circuit and optimization with industrial standard component                                                                              |

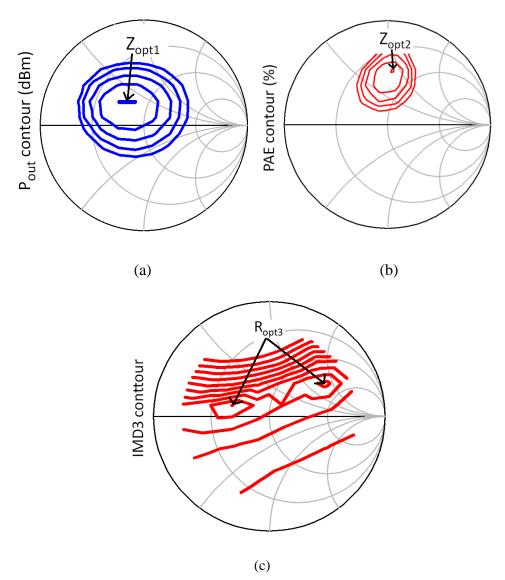

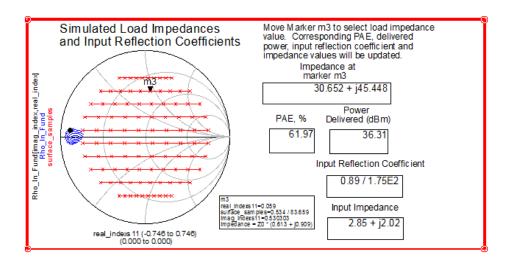

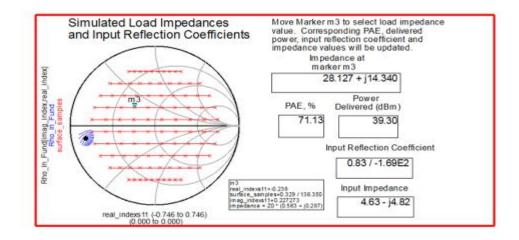

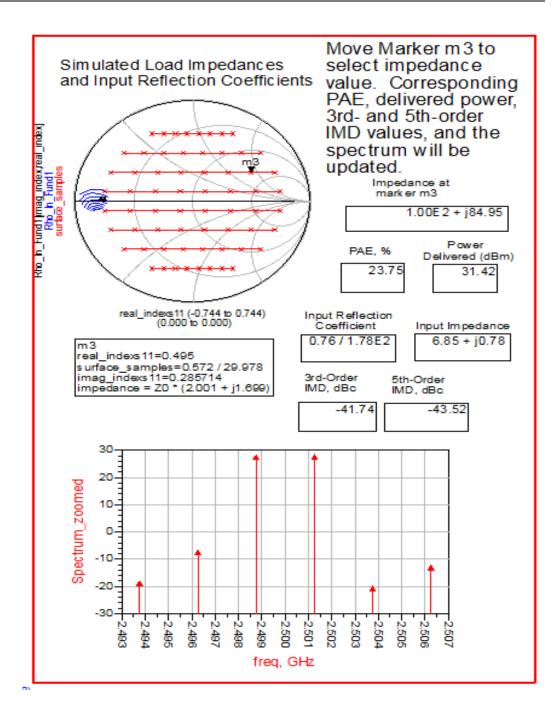

| Figure 3.4: Simulated load-pull contours of the investigated 6 W GaN device (at $V_{DS}=28~V,~V_{GS}=-3.1~V,~I_{DS}=35~mA-10\%$ and Pin = 25 dBm): (a) output power (b) PAE and (c) IMD <sub>3</sub> 40              |

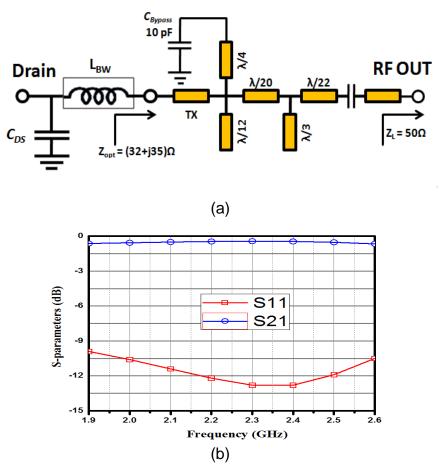

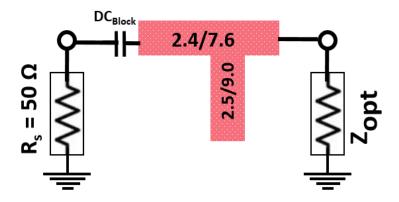

| Figure 3.5: Output matching network: (a) schematic and (b) simulated transmission coefficient $S_{21}$ and input reflection coefficient $S_{11}$ 42                                                                  |

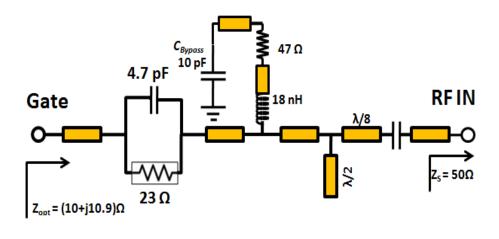

| Figure 3.6: Input matching network: (a) topology and (b) simulated transmission coefficient $S_{21}$ and input reflection coefficient $S_{11}$ 44                                                                    |

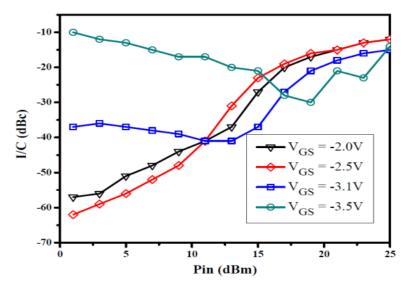

| Figure 3.7: Simulated carrier to intermodulation ratio versus input power level for $V_{GS}=$ -3.5 V, $V_{GS}=$ -3.1 V, $V_{GS}=$ -2.5 V and $V_{GS}=$ -2 V. The results are obtained with a drain voltage of 28 V45 |

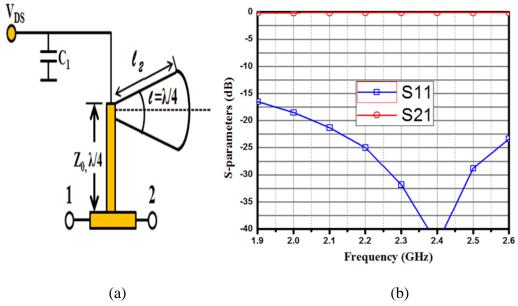

| Figure 3.8: Radial-stub drain bias network: (a) topology (b) simulated transmission coefficient $(S_{21})$ and input reflection coefficient $(S_{11})$ 46                                                            |

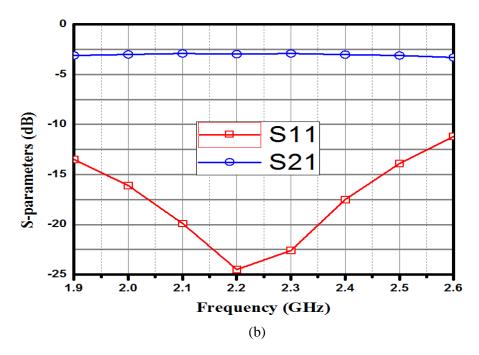

| Figure 3.9: Gate bias network: (a) topology ( $R=47~\Omega,L=18~nH$ and $l=5~mm$ ) (b) simulated transmission coefficient ( $S_{21}$ ) and input reflection coefficient ( $S_{11}$ )                                 |

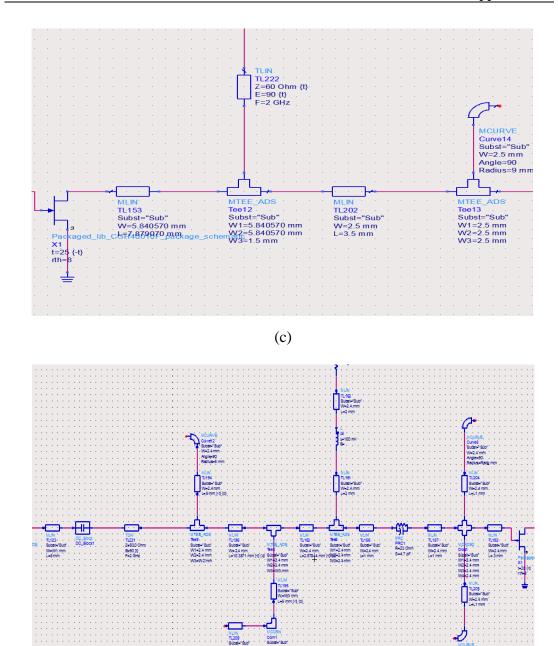

| Figure 3.10: EM simulation of proposed PA in ADS simulator47                                                                                                                                                         |

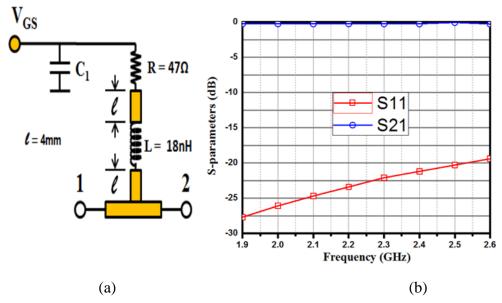

| Figure 3.11: Schematic circuit of 2.3 GHz Class-AB Power Amplifier48                                                                                                                                                 |

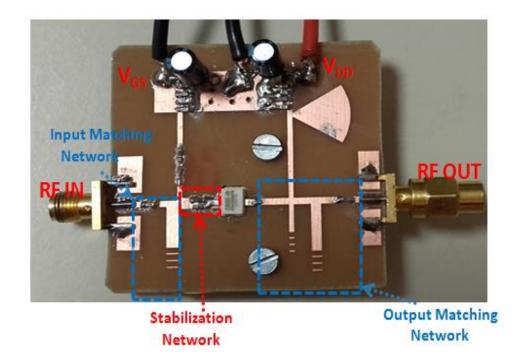

| Figure 3.12: Photo of realized 5 W Class-AB Power Amplifier48                                                                                                                                                        |

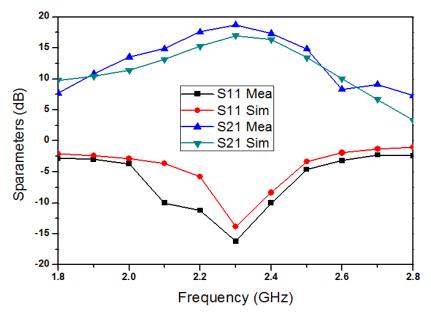

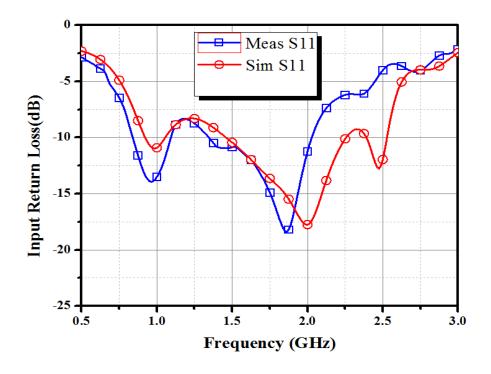

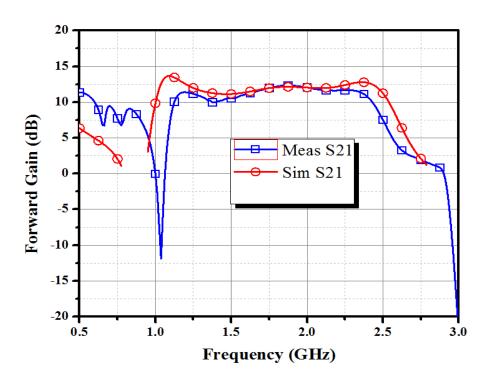

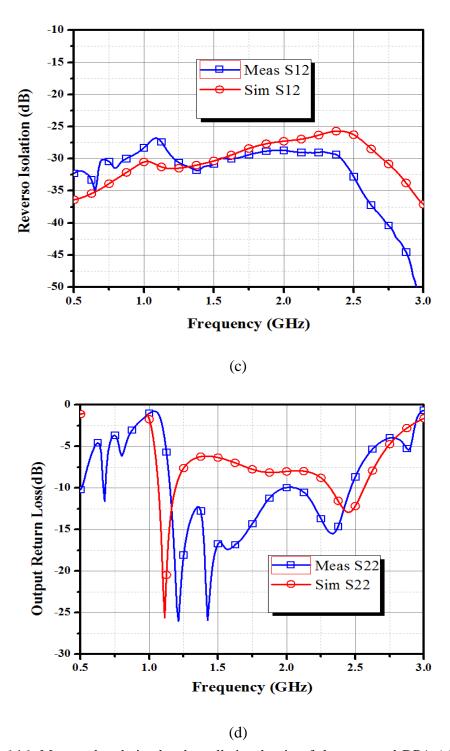

| Figure 3.13: Measured and simulated S-parameters of 5 W Class-AB Power Amplifier ( $S_{11}$ and $S_{21}$ , at a bias point of $V_{GS}$ = -3.1 V, $V_{DS}$ = 28 V and $I_{DS}$ = 35 mA)                               |

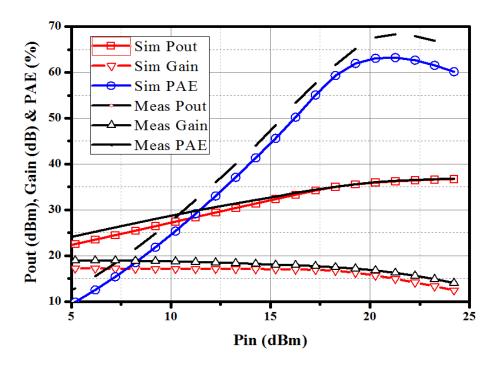

| Figure 3.14: Measured and simulated gain, PAE and Pout at the $V_{DS}=28\ V$ and $I_{DS}=35\ mA$ for 2.3 GHz50                                                                                                       |

| Figure 3.15: Measured gain, PAE, and Pout versus frequency at the $V_{DS} = 28$ V and $I_{DS} = 35$ mA.                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.16: The PAE and gain of the proposed PA at different drain bias voltages ( $V_{DS}=20\ V,V_{DS}=24\ V,V_{DS}=28\ V,$ and $V_{DS}=32\ V)52$                                                                                                                       |

| Figure 3.17: Simulated output spectrum, when the PA is excited with a two-tone input signal (16 dBm each of them) at a center frequency of 2.3 GHz and spacing of 10 MHz                                                                                                  |

| Figure 3.18: Linearity characterization setup55                                                                                                                                                                                                                           |

| Figure 3.19: Output spectrum of the power amplifier when excited with a QAM-256 at 2.3 GHz56                                                                                                                                                                              |

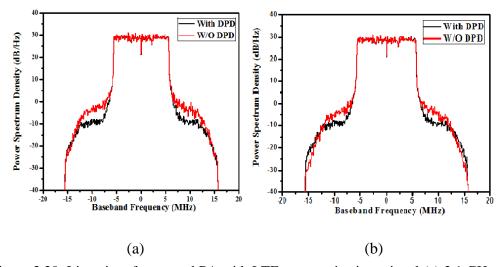

| Figure 3.20: Linearity of proposed PA with LTE communications signal (a) 2.1 GHz and (b) 2.4 GHz56                                                                                                                                                                        |

| Figure 4.1: Class-F power amplifier topology with ideal infinite harmonic termination                                                                                                                                                                                     |

| Figure 4.2: Ideal drain voltage and current waveforms for a Class-F power amplifier                                                                                                                                                                                       |

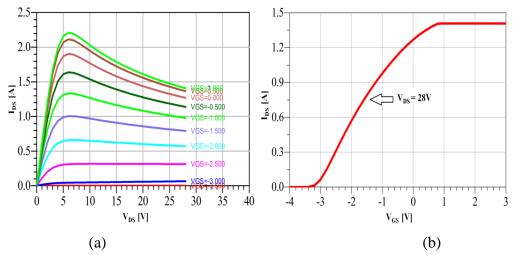

| Figure 4.3: Cree 10W GaN HEMT active device (a) simulated current and voltage curve, and (b) simulated transfer characteristics at $V_{DS}=28\ V$ and $V_{GS}=-2\ V$                                                                                                      |

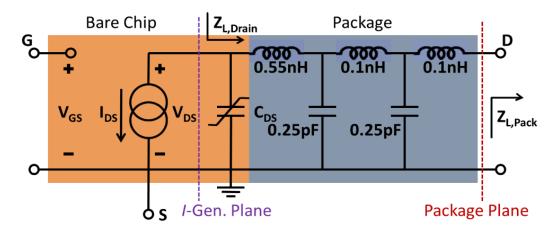

| Figure 4.4: Approximated equivalent network of device output parasitics for DUT CGH40010F [55]66                                                                                                                                                                          |

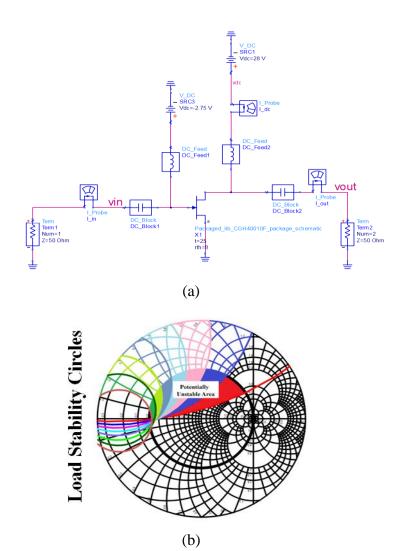

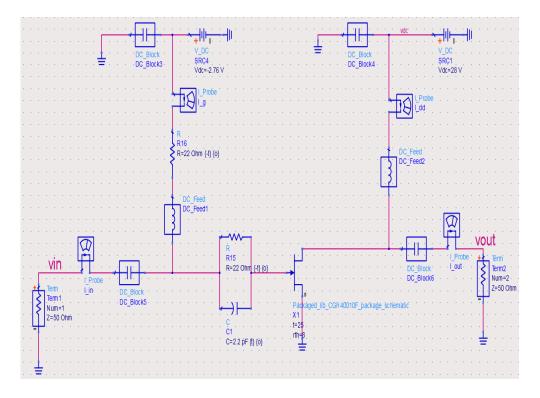

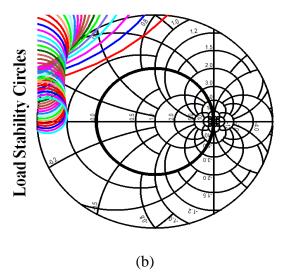

| Figure 4.5: (a) Simulation setup in ADS for stability measurement and (b) simulated wideband active device load stability circles without stabilization network, highlighting the potentially unstable area in unity circle from 500 MHz to 4 GHz.                        |

| Figure 4.6: (a) Simulation setup after adding the stability circuit and (b) simulated wideband active device load stability circles with the stabilization network, highlighting the removal of potentially unstable region from the frequency range of 500 MHz to 4 GHz. |

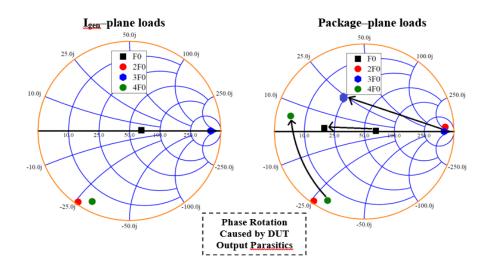

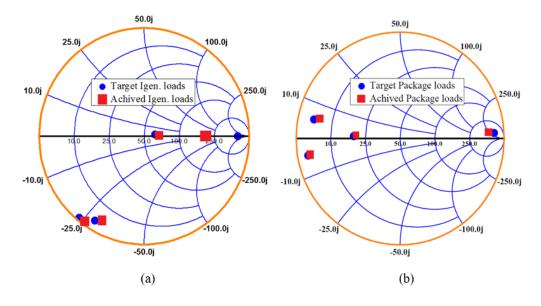

| Figure 4.7: Smith charts showing effect of the output parasitics on the desired optimum lgenplane Class-F loading translation to the device package-plane71                                                                                                               |

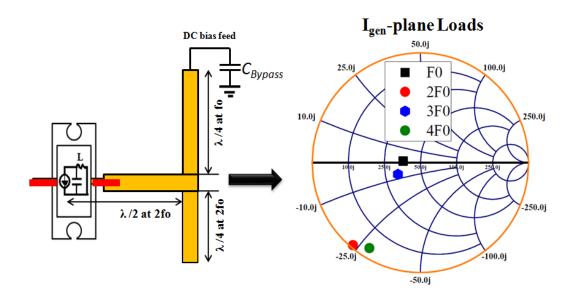

| Figure 4.8: Matching the second harmonic load (short) with a $\lambda/2$ at $2f_0$ shorted stub and $\lambda/4$ at $2f_0$ open stub, with the effect of this on the third and fundamental loads shown |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

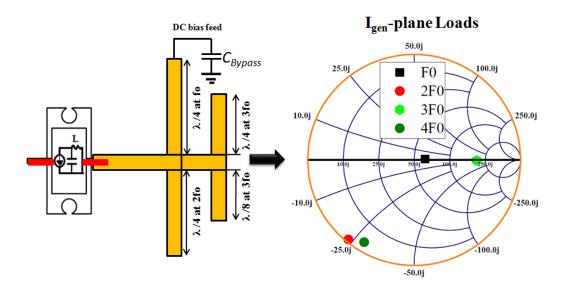

| Figure 4.9: Third (open) and second harmonic loads now matched with the addition of a $\lambda/4$ at $3f_0$ open stubs. The effect of this on the fundamental load is also shown                      |

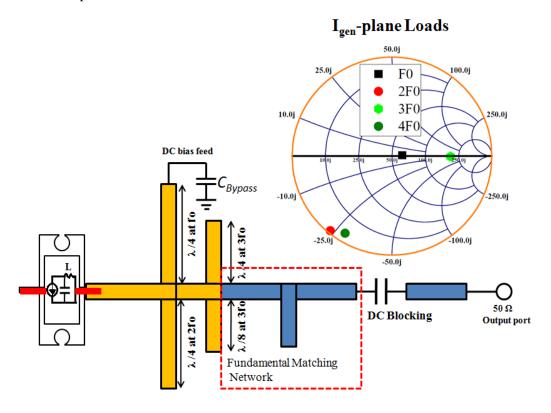

| Figure 4.10: Fundamental loading now completes the three harmonic matching networks to approximately the impedances required                                                                          |

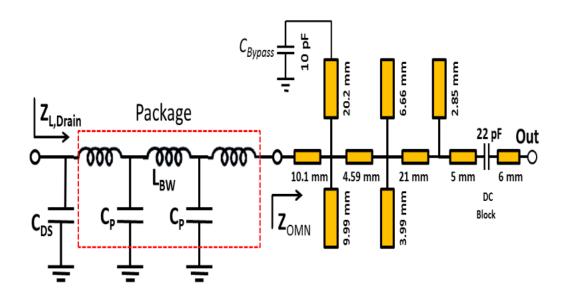

| Figure 4.11: Optimized output matching network design at 2 GHz for Class-FPA                                                                                                                          |

| Figure 4.12: S-parameter simulation results displaying the impedances presented by the output network to the device package-plane and Igen. plane, as specified                                       |

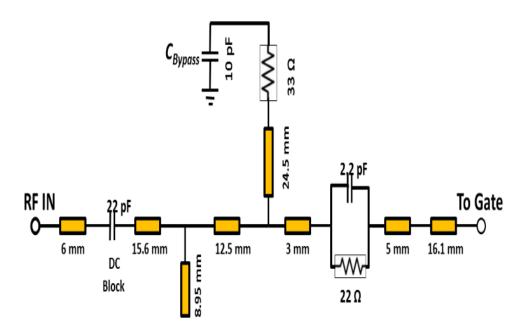

| Figure 4.13: Final input matching based on microstrip at 2 GHz for Class-FPA                                                                                                                          |

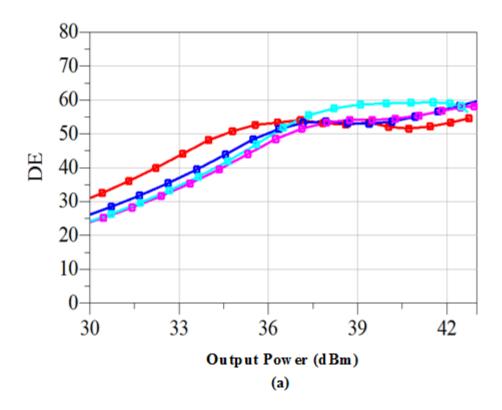

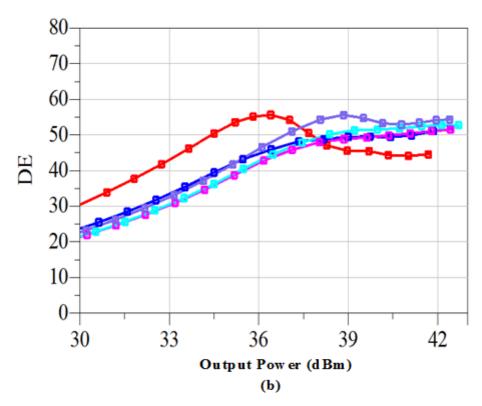

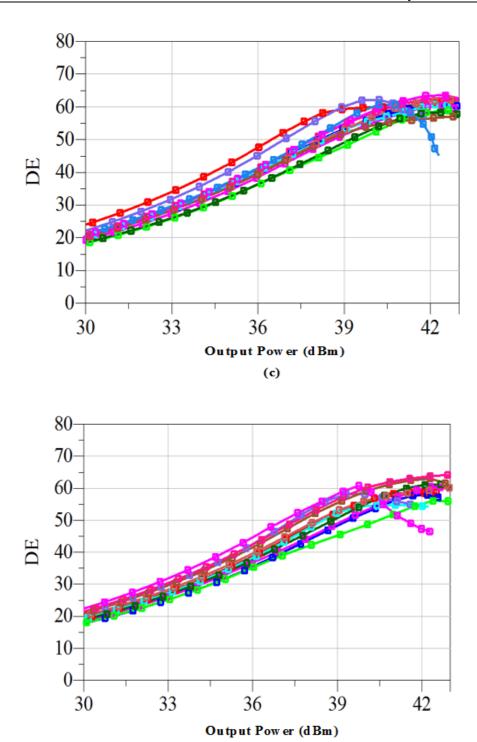

| Figure 4.14: Simulated DE for different circuit configurations for desired bandwidth, (a) 2nd harmonics impedance variation, (b) 3rd harmonics impedance variation, and (c) 4rth impedance variation  |

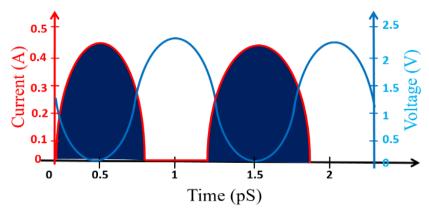

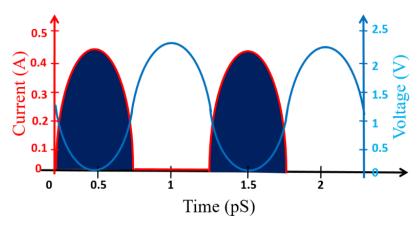

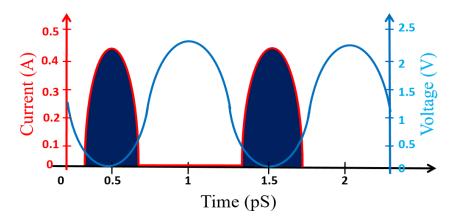

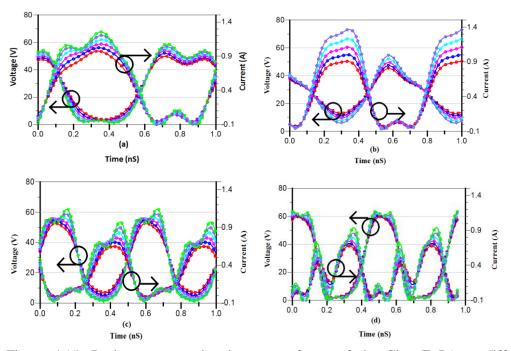

| Figure 4.15: Drain current and voltage waveforms of the Class-F PA at different frequencies with the increasing input power (a) 1.1 GHz, (b) 1.5 GHz, (c) 1.95 GHz design frequency and (d) 2.1 GHz   |

| Figure 4.16: Final circuit schematic of the ultra-wide band Class-F PA79                                                                                                                              |

| Figure 4.17: The photograph of realized prototype of broadband Class-F PA.                                                                                                                            |

| Figure 4.18: Simulated and measured small-signal gain versus frequency for the realized PA                                                                                                            |

| Figure 4.19: Measured drain efficiency, output power and gain vs. input of the proposed Class-F at 1.95GHz                                                                                            |

| Figure 4.20: Simulated output power, power added efficiency and drain efficiency vs. frequency                                                                                                        |

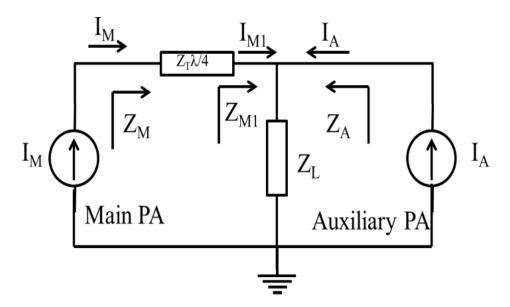

| Figure 5.1: A simplified schematic of the conventional Doherty power amplifier                                                                                                                        |

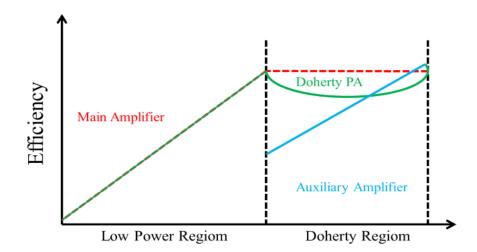

| Figure 5.2: Efficiency behavior of main, auxiliary and Doherty amplifiers86                                                                                                                           |

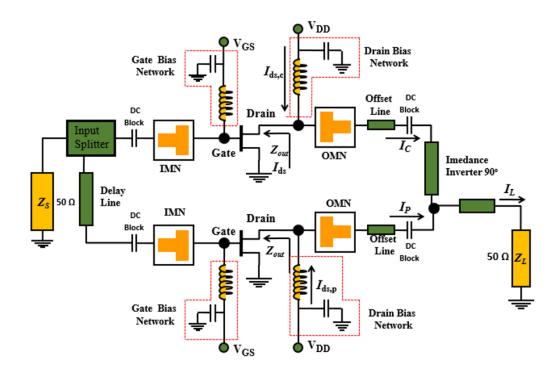

| Figure 5.3: Circuit topology of single-input Doherty power amplifier88                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

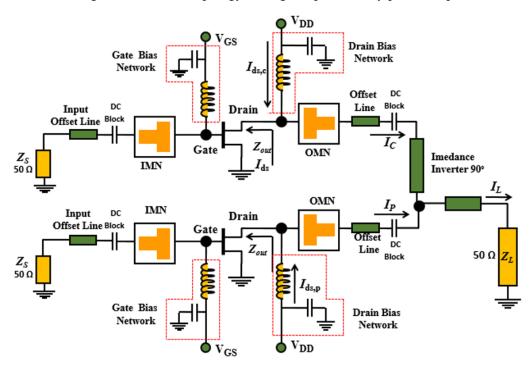

| Figure 5.4: Circuit topology of dual-input Doherty power amplifier88                                                                                                                   |

| Figure 5.5: Block diagram of the proposed dual-input Doherty power amplifier                                                                                                           |

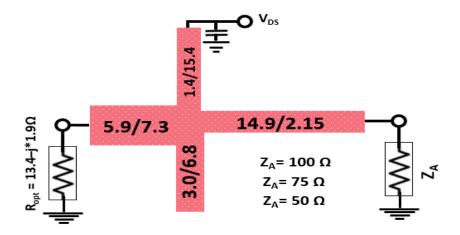

| Figure 5.6: Synthesized output matching networks of peaking amplifier simulated on an $Er=2.33$ microstrip substrate with a thickness of 0.79 mm. All dimensions are in millimeters    |

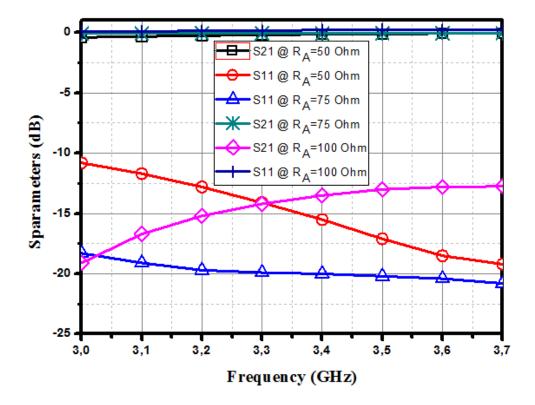

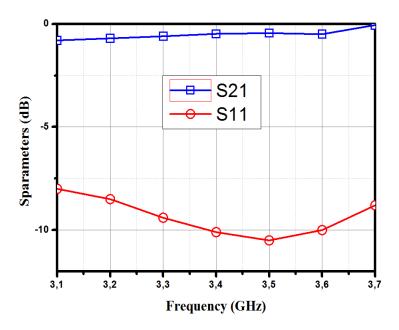

| Figure 5.7: Return and insertion losses of the proposed OMN of carrier PA. 92                                                                                                          |

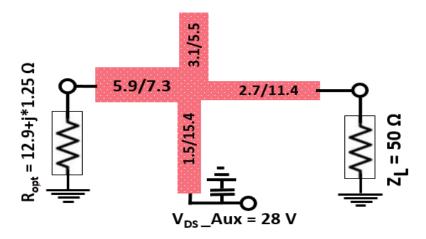

| Figure 5.8: Synthesized output matching networks of peaking amplifier simulated on an $Er = 2.33$ microstrip substrate with a thickness of 0.79 mm. All dimensions are in millimeters. |

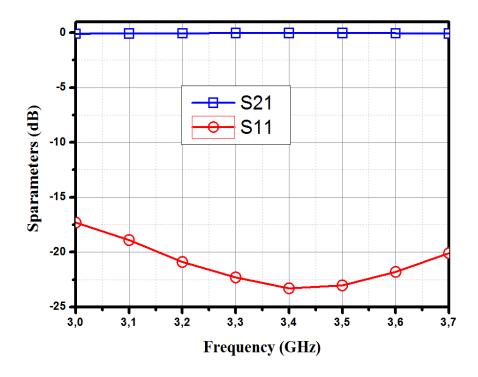

| Figure 5.9: Return and insertion losses of the proposed OMN of peaking PA.                                                                                                             |

| Figure 5.10: Layout of the input matching network of both PAs95                                                                                                                        |

| Figure 5.11: Return and insertion losses of the proposed IMN of both PAs95                                                                                                             |

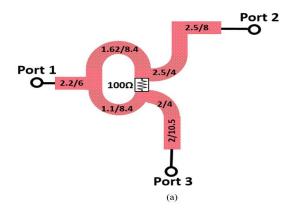

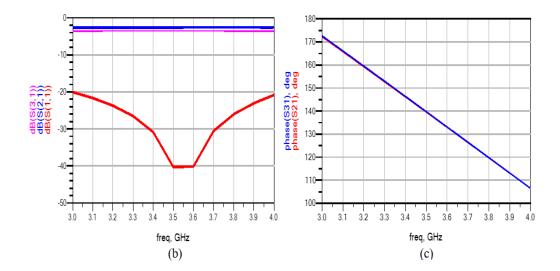

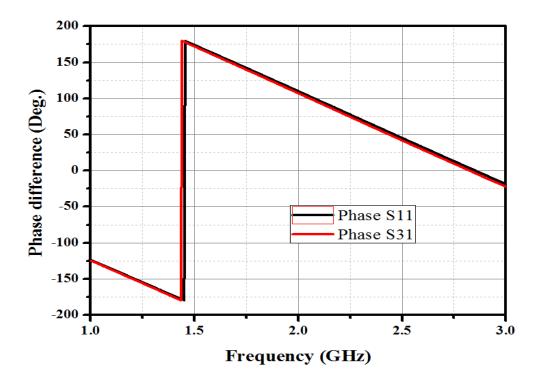

| Figure 5.12: (a) Wilkinson power divider, (b) simulated insertion loss $(S_{21})$ and reflection loss $(S_{11})$ , (b) phase difference between port 2 and 397                         |

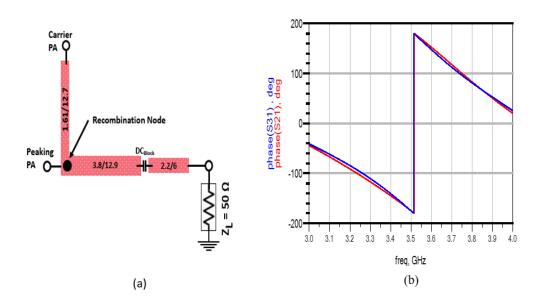

| Figure 5.13: (a) Output combining network, and (b) simulated phase at the recombination node                                                                                           |

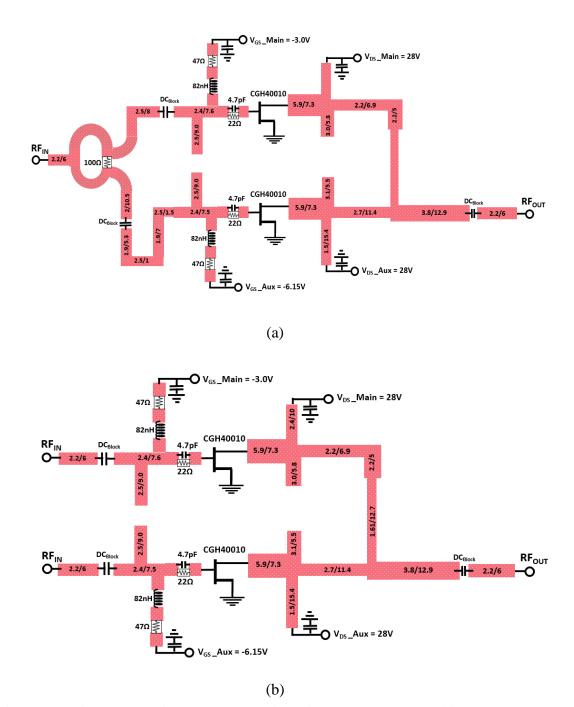

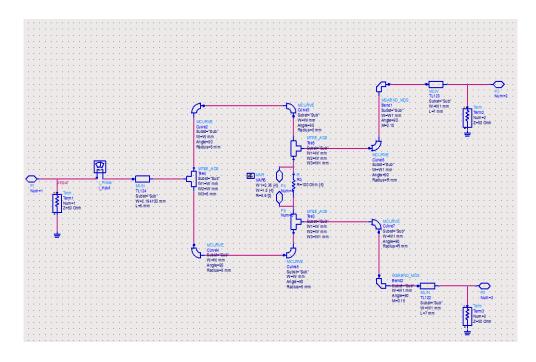

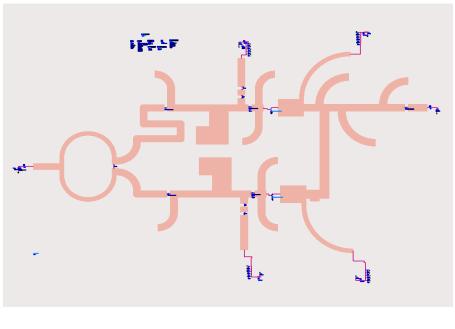

| Figure 5.14: Final layouts of the proposed (a) single-input DPA and (b) dual-input DPA99                                                                                               |

| Figure 5.15: Simulated $S_{21}$ (blue line with square mark) small-signal gain of the proposed DPA and input return loss $S_{11}$                                                      |

| Figure 5.16: Simulated drain efficiency vs. output power for designed bandwidth at the $V_{DS} = 28\ V$ and $I_{DS} = 68\ mA$                                                          |

| Figure 5.17: Simulated output power, drain efficiency, and gain versus frequency for the both PAs under optimum input power conditions105                                              |

| Figure 6.1: Basic building blocks of conventional Doherty power amplifier.                                                                                                             |

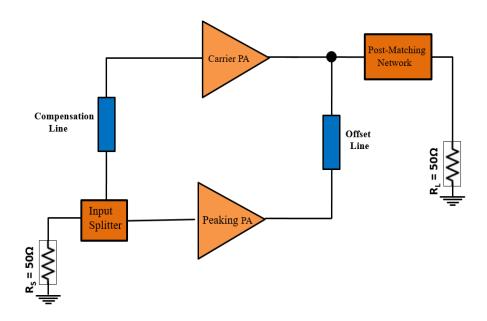

| Figure 6.2: Circuit topology of proposed Doherty power amplifier111                                                                                                                    |

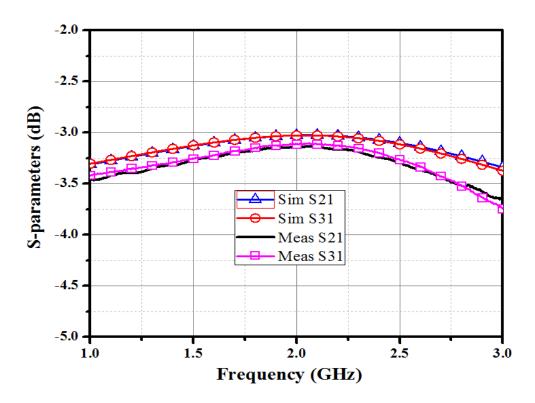

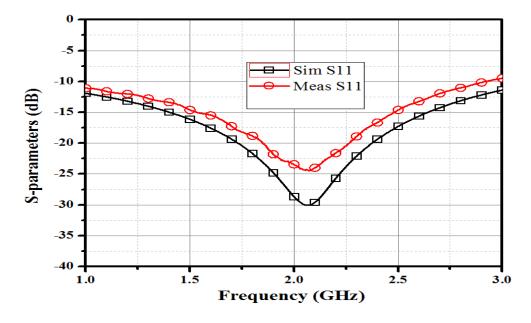

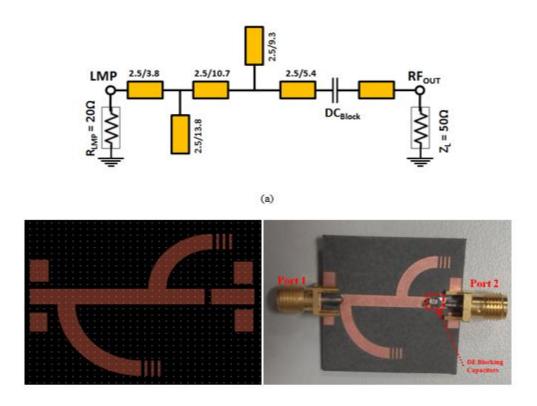

| Figure 6.3: Wilkinson power divider (a) transmission line circuit and (b) photograph of the realized circuit                                                                           |

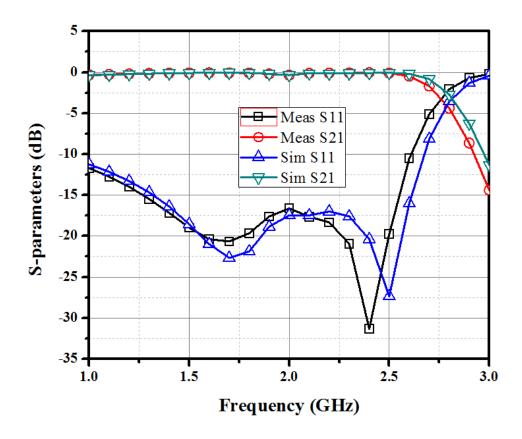

| Figure 6.4: Measured and simulated insertion loss $(S_{21})$ of the ring structured Wilkinson power divider                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.5: Measured and simulated reflection loss (S <sub>11</sub> ) of the ring structured Wilkinson power divider                                                 |

| Figure 6.6: Measured phase difference in port 2 and 3 of the ring structured Wilkinson power divider.                                                                |

| Figure 6.7: Carrier impedance inverter and drain biasing network120                                                                                                  |

| Figure 6.8: Peaking impedance inverter and drain biasing network121                                                                                                  |

| Figure 6.9: Input matching network topology                                                                                                                          |

| Figure 6.10: (a) Circuit topology, (a) EM simulation and (b) photo of realized post-matching network                                                                 |

| Figure 6.11: Measured and simulated transmission coefficient $S_{21}$ and input reflection coefficient $S_{11}$ .                                                    |

| Figure 6.12: Basic building blocks of proposed Doherty power amplifier125                                                                                            |

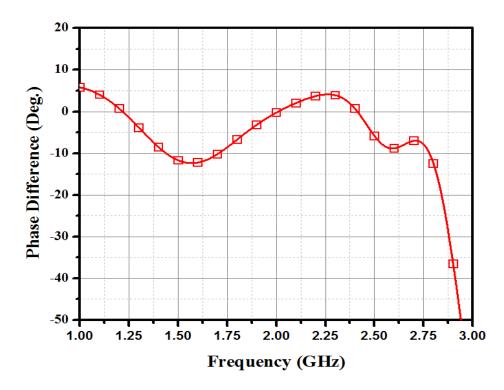

| Figure 6.13: Phase difference in degree at load modulation point after the final optimization of offset-line and compensation-line                                   |

| Figure 6.14: Drain efficiency at different offset line combination                                                                                                   |

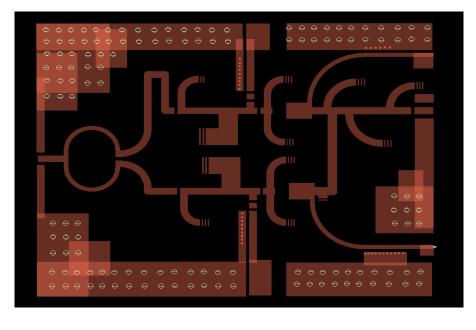

| Figure 6.15: Photo of realized Doherty power amplifier                                                                                                               |

| Figure 6.16: Measured and simulated small-signal gain of the proposed DPA (a) input return loss, (b) forward gain, (c) reverse isolation, and (d) output return loss |

| Figure 6.17: The measured drain efficiency vs. output power for designed bandwidth at the $V_{DS} = 28\ V$ and $I_{DS} = 50\ mA$ .                                   |

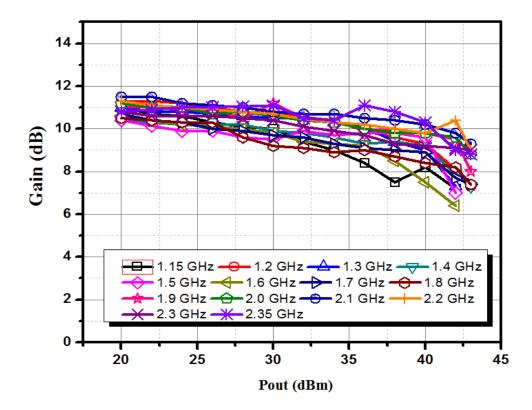

| Figure 6.18: The measured gain vs. output power for designed bandwidth at the $V_{DS}=28\ V$ and $I_{DS}=50\ mA$                                                     |

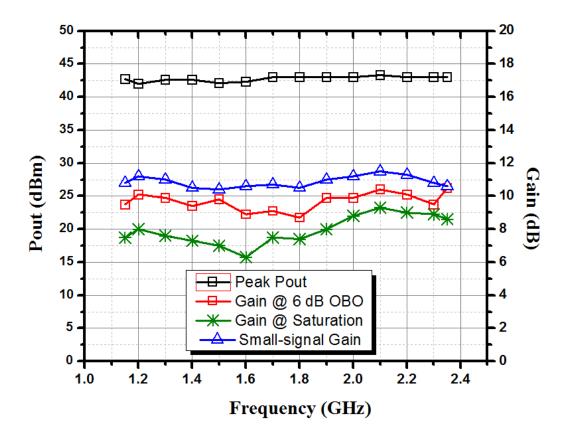

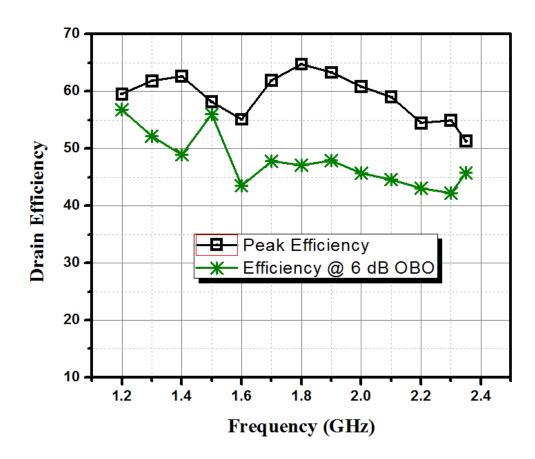

| Figure 6.19: The measured gain at three different levels and output power versus frequency at the $V_{DS}=28\ V$ and $I_{DS}=50\ mA$                                 |

| Figure 6.20: The measured peak drain efficiency and efficiency at 6 dB back-off vs. frequency at the $V_{DS}=28\ V$ and $I_{DS}=50\ mA$                              |

| Figure 6.21: Measured drain efficiency, upper ACPR and lower ACPR, when DPA is excited with a 5 MHz WCDMA input signal, which has PAPR 6.5 dB at                     |

| Figure 6.22: The measured ACPRs Vs. frequency at 1.6 dBm output, when DPA is based at the $V_{DS}=28\ V$ and $I_{DS}=50\ mA$                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure A.1: (a) Simulated output power, (b) efficiency, and (c) intermodulation distortion of 6 W GaN HEMT device in ADS simulator at different load impedances.                   |

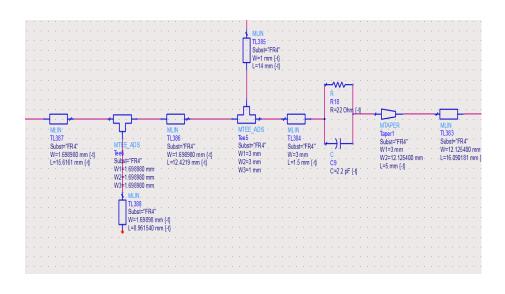

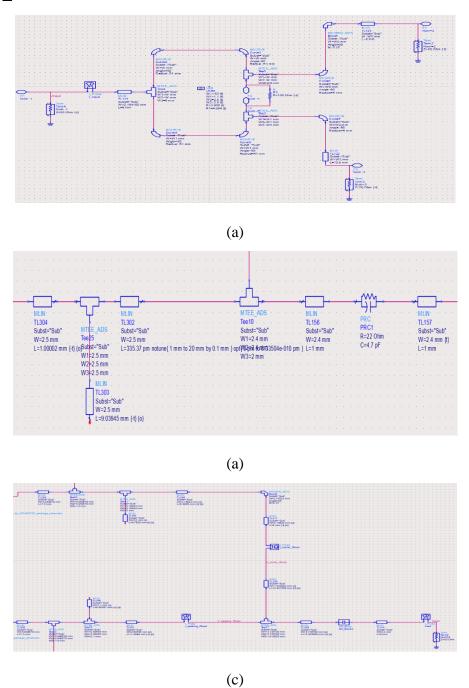

| Figure B.1: (a) Input matching network and (b) output matching network ADS circuit schematic layouts                                                                               |

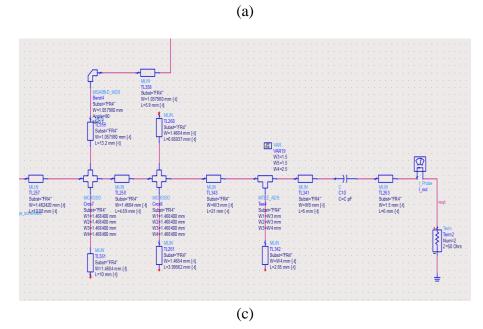

| Figure C.1: (a) power divider network, (b) input matching network, (c) and combining network in ADS circuit schematic                                                              |

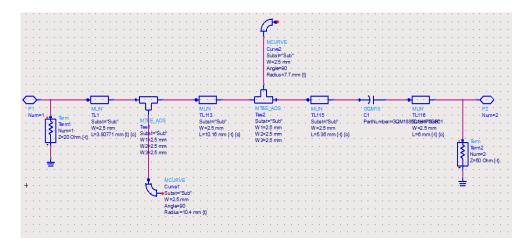

| Figure D.1: (a) power divider network, (b) post-matching network, (c), output matching network and (d) input matching network of the proposed DPA in ADS circuit schematic layouts |

| Figure D.2: (a) Co-simulation setup and (b) ADS layout of the proposed DPA.                                                                                                        |

| List of Tables                                                                                                                                                                     |

|                                                                                                                                                                                    |

| Table 2.1: Theoretically efficiency of different classes of amplifier operation.                                                                                                   |

| 19                                                                                                                                                                                 |

| Table 2.2: Summary of amplifier classes of operation                                                                                                                               |

| Table 2.2: Summary of amplifier classes of operation                                                                                                                               |

| Table 2.2: Summary of amplifier classes of operation                                                                                                                               |

| Table 2.2: Summary of amplifier classes of operation                                                                                                                               |

| Table 2.2: Summary of amplifier classes of operation                                                                                                                               |

| Table 4.3: Class-F PA harmonic load reflection coefficients at current generator and package-plane at 2 GHz                       |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Table 4.4: Optimum harmonics load impedances of Class-F PA at current generator and embedded package-plane at 2 GHz71             |

| Table 4.5: Performance compression with state-of-the power amplifier83                                                            |

| Table 5.1: Extracted optimum impedances for efficiency and output power from load-pull simulations in Class-AB bias conditions91  |

| Table 5.2: Extracted optimum impedances for efficiency and output power from load-pull simulation in Class-C bias conditions      |

| Table 5.3: Performance compression of the proposed DPAs with state-of-the Doherty power amplifier in the 3.5 GHz frequency band   |

| Table 6.1: Compression of conventional and proposed design methodology.                                                           |

| Table 6.2: Load-pull simulation for optimum efficiency and power at the 3 dB back-off, when biased with $V_{GS} = -3.0 \text{ V}$ |

| Table 6.3: Load-pull simulation for optimum efficiency and power at saturation, when biased with $V_{GS} = -6.15 \ V$             |

| Table 6.4: DPA bandwidth with the variation of offset/compensation-lines length and width                                         |

| Table 6.5: Performance compression of the proposed DPA with state-of-the Doherty power amplifier                                  |

# Chapter 1

## Introduction

#### 1.1 Motivation

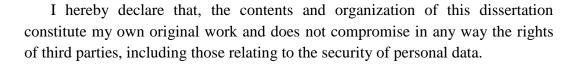

Communication among the people has been dramatically changed by the mobile communication systems in the last two decades. Mobile communication systems have achieved an outstanding popularity in history of wireless communication. Figure 1.1 presents the evolution of wireless access technologies from the first mobile generation (1G) to the upcoming fifth generation (5G) with their capabilities and capacities. In advanced mobile communication systems, currently, 4G Long Term Evolution (LTE) networks are very well developed in terms of both mobile handset and the network infrastructure. Now, the eyes of the mobile telecommunications industry are turning towards the next generation of technology i.e. 5G [1-3]. Although, the first deployment is a few years away, however much work needs to be done to lay the ground for 5G. In order to satisfy the growing demand of capacity and capability of wireless communications, the new generation of mobile communications will clearly add more spectrum to the capacity. However, some of the capabilities are very important, for example high-speed video, low latency, ultra-reliability, and low power consumption.

A rapid increase in the mobile data traffic can be attributed to mobile internet devices such as tablet computers, wearable watches and smart phones. There are several internet devices, which are not operating to their full capacity due to the slow internet connection and mobile data limitation imposed by the telecom operators. Based on this argument, it is logical to say that the mobile data

requirement is much larger than what the mobile infrastructure is capable to provide. Moreover, it is more practical to calculate the amount of data consumption from the capacity and speed of the mobile infrastructure instead of estimating it from the capacity of mobile internet devices.

Figure 1.1: Evolution of wireless communications.

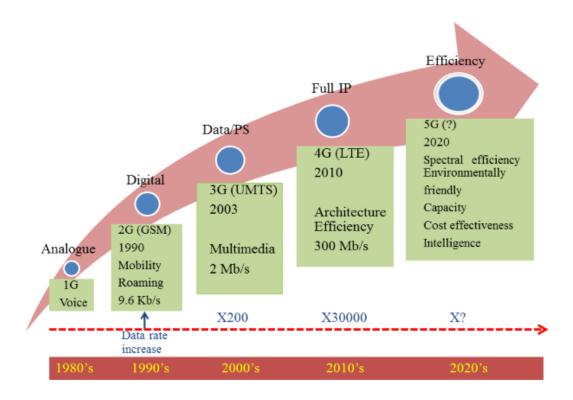

In the 4G mobile infrastructure, wireless standards such as Long Term Evolution (LTE) and Worldwide Interoperability for Microwave Access (WiMAX) were approved and the infrastructure based on these standards were implemented extensively throughout the world to satisfy the data requirements of mobile users. Both of these well known wireless standards make use of spectrally efficient modulation schemes such as orthogonal frequency-division multiplexing (OFDM). The system that utilizes OFDM modulation scheme is able to maximize the data throughput and network capacity. Figure 1.2 shows the extensive use of OFDM modulation scheme for different wireless communication standards for enhancing the data rate.

Figure 1.2: Use of OFDM modulation scheme in wireless communications.

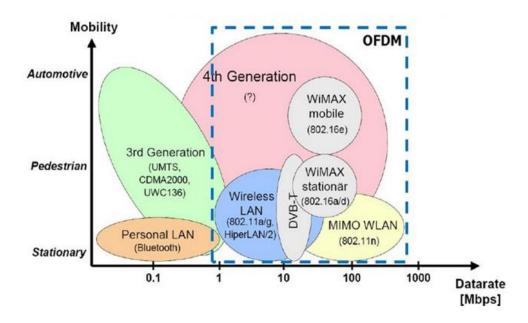

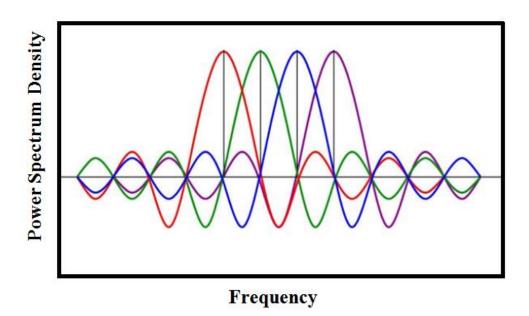

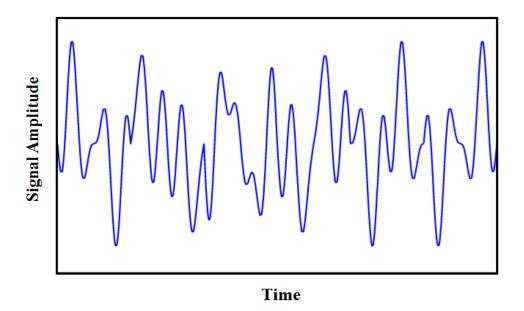

If we look from the power amplifier (PA) perspective, a widespread use of higher order spectral modulation schemes to satisfy the growing demand of high data rate can also have significant effect on the power amplifier performance [2]. The most commonly used spectral modulation is OFDM and generally, it is based on four subcarriers, as depicted in Figure 1.3. An orthogonal frequency division multiplexing based system produces signals with a very high crest in the time domain subcarrier components, which are added through an inverse fast Fourier transformation (IFFT) operation. Consequently, when OFDM systems are compared with single carrier GSM systems, it has a very high peak-to-average power ratio (PAPR), as can be seen from Figure 1.4. Indeed, in an advanced wireless base-station, a signal with high peak-to-average power ratio is a major challenge for radio frequency PA designers; the reason of this is that power amplifier significantly reduces the average efficiency at the back-off power level.

High crest signal has fewer effects on the PA average efficiency during downlink frequency operation in a base-station. On the contrary, it has significant effects on the average efficiency of a PA during uplink frequency operation. This is due to the fact that the efficiency of the power amplifier is a major concern in mobile terminal devices and in base-stations due to the limited battery power and required expensive cooling setup, respectively. Moreover, a communication signal with high crest can also shrink the signal-to-quantization noise ratio (SQNR) of

the Analog to Digital Convertor (ADC) and Digital to Analog Convertor (DAC), while degrading the efficiency of the power amplifier in the transmitter [4].

Figure 1.3: An OFDM modulation with four subcarriers.

Figure 1.4: An OFDM waveform illustrating with high PAPR.

In emerging wireless standards, for maintaining high signal to noise ratio (SNR) and bit error rate (BER) at the receiver side of a base-station, a power amplifier with high linearity and high output power is required [5]. Furthermore, in the near future, the base-station PA design will be more complicated by the arrival of next generation standard in wireless communications. It is also required that the emerging and legacy standards must coexist for satisfying the data hanger of mobile devices. Generally, multiple narrowband radios are installed to support different standards such as WiFi, WiMAX, GSM and LTE. This approach is redundant in hardware and power inefficient as well.

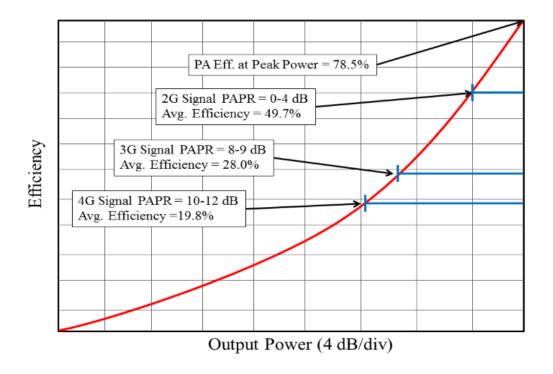

Figure 1.5: PAPR effect on power amplifier average efficiency.

Figure 1.5 shows the typical power amplifier efficiency versus output power; with the passage of time, the progress from the 1G to the 4G modulated signal's PAPR raised from 0 dB to 12 dB and the drain efficiency reduced from 78.5% from 19.8%, respectively. Finally, there are also environmental and ecological challenges and the power utilization should be as low as possible. It is presented in [6] that mobile networks alone contribute to 0.2% of the global CO<sub>2</sub> emissions and it is predicted that this Figure will rise to 0.4% in 2020.

#### 1.2 Problem statement

As discussed in the previous section, the advanced base-station power amplifier needs to meet multiple criteria including efficiency, linearity, output power, and bandwidth. In particular, the amplifier must be highly efficient in terms of drain efficiency when operated with a high PAPR signal. To obtain high efficiency in power amplifier at back-off level, many advanced techniques have been proposed in the literature such as H. Chireix [7], Doherty power amplifier (DPA) [8] and the envelope-tracking amplifier (ET) [9]. The Doherty amplifier has been widely adopted in the industry thanks to its ease implementation and better average efficiency.

Unfortunately, the conventional Doherty power amplifier has a limited bandwidth. Therefore, even if it is capable of fulfilling the linearity and power output requirement of the modern base-station, the conventional DPA is not capable to satisfy the bandwidth requirement of modern base-station. The limited bandwidth means that more Doherty amplifiers are distributed in a single base-station, one for each standard that a mobile service provider uses. This could leads to inefficient power usage and surplus hardware.

In contrast to the outphasing power amplifier, the conventional DPA is based on a static phase between the sub-amplifier output signals. As an alternative, the load modulation is achieved by changing the amplitude of their relationship. The advantage of the DPA over the other advanced efficiency enhancement techniques is that mainly accurate amplitude ratios can be achieved using a single RF-driver combination with an analog power splitter and sub-gate-bias amplifier. This advantage ascertains the DPA as the best candidate for efficiency enhancement purpose without using any additional control circuitry.

Because of high efficiency and high linearity, DPA has become the prime choice of today's commercial RF transmitters for mobile communications. However, it has limited bandwidth. For example, Cripps in [10] reported that DPA has only 10% fractional bandwidth. Therefore, a number of solutions have been proposed to overcome the bandwidth limitation. The DPA has a hard time in meeting the wideband requirement. In the near future, with the arrival of new technology (5G), bandwidth requirements of a PA will be more demanding. In order to reduce the time to market for new technology and PA operation for multistandards communication signals such as WiFi, WiMAX and LTE, a wideband PA is highly demanded.

In this thesis, we propose a new Class-AB PA with the extended bandwidth and linearity for the LTE communication band. In the second proposed design, an ultra-wide band Class-F PA is designed and implemented. In the third PA design, a single- and dual-input DPA for LTE application in the 3.5 GHz frequency band are presented and compared. Moreover, a novel design technique is proposed to extend the bandwidth of the conventional Doherty power amplifier. In order to validate the proposed technique, it is also applied on two 10W GaN HEMT devices and the designed PA presented satisfactory results. The proposed DPA is implemented and it meets all the requirements of a modern base-station. The advanced design technique is a fundamental reference point towards the construction of a single power amplifier capable of simultaneously support multiple wireless communication standards, reducing the complexity and the cost of the transmitter.

#### 1.3 Thesis organization

The thesis is organized as follows. Chapter 2 provides the background and theory of conventional RF power amplifiers. All the fundamental figure-of-merits of the power amplifier are discussed in detail. Furthermore, operating classes of traditional and high efficiency power amplifiers are introduced based on the study of voltage and current waveforms. The input and output requirements of the matching network practices are outlined with the design of the widely adopted load-pull technique.

Chapter 3 outlines the design of a highly linear and broadband single-ended power amplifier using two-tone load-pull simulation and bias optimization technique to synthesize the matching networks. The design of a 5 W Class-AB PA for 1.9 to 2.5 GHz LTE communication band based on GaN HEMT active device is discussed in detail.

Chapter 4 proposes a novel design with ultra-wide bandwidth of the Class-F power amplifier based on 10 W GaN HEMT from Cree Inc. The conventional Class-F PA has high drain efficiency. However, it is a narrow bandwidth PA. Multiple harmonics termination is exploited for high drain efficiency and maintaining ultra-wide bandwidth as well.

Chapter 5 introduces the single- and dual-input Doherty amplifier, which uses two devices in parallel to obtain the improvement of the efficiency in power level of back-off. Derivations based on the concept of load modulation and the

conventional Doherty amplifier shows that it has a narrow bandwidth. The widely adopted traditional technique is outlined and a review of the literature shows the limited bandwidth of conventional Doherty amplifier. A conventional GaN HEMT based Doherty amplifier, with 600 MHz bandwidth is designed and implemented at 3.5 GHz for the LTE communication signal.

In chapter 6, a novel design technique is proposed to overcome the conventional Doherty power amplifier bandwidth limitation. The reasons of limited bandwidth of the widely adopted traditional technique are outlined. Moreover, it is explained that by regulating the offset-line of the auxiliary PA, it is possible to control the bandwidth of the proposed DPA. In order to validate the proposed technique, it is applied on two 10 W GaN HEMTs devices. The realized DPA exhibited satisfactory results as expected. The measured results show a good agreement with the simulated results.

Finally, in the last chapter of this thesis, a summary of the entire research work is presented. In addition to this, a future work to extend the practicability of the anticipated theory to higher frequencies is described.

2.1 Introduction 9

# Chapter 2

# **Power Amplifiers Overview**

#### 2.1 Introduction

In this chapter, we describe the underlying theory and design of a RF power amplifier for front-end transmitters. Key figure-of-merits (FOM) of a typical power amplifier (PA) and various classes of operations are briefly discussed as well. In addition to this, the practical design considerations of a single-ended PA such as the parasitic effects of a device, the package effect on load impedances, stability, input and output matching network designs are presented. The study in the subsequent chapters provided the basis for understanding the advanced circuit design techniques for high efficiency PA such as Class-F and Doherty power amplifiers.

### 2.2 Power amplifier and FOM

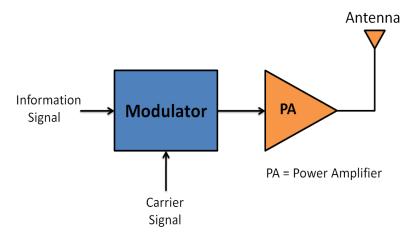

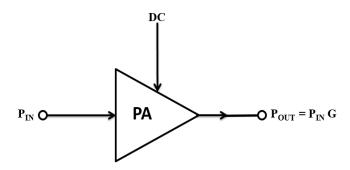

A PA is a non-linear system that has an output power level equal to the input power multiplied by gain at a specified frequency [11]. A transmitter is a backbone of modern wireless communication system. In front-end transmitter, an information input signal is modulated at a specific high frequency. After that, the modulated input signal is amplified by using a PA and then the amplified signal is radiated from the antenna [12]. A simplified block diagram of the front-end transmitter is shown in Figure 2.1.

Figure 2.1: A simplified block diagram of a front-end transmitter.

A PA is a critical module in frond-end transmitter architecture. The working class of a PA can be described such as Class-A, Class-AB, Class-B, Class-C, and Class-F. In addition to the working class, there are some important FOM for PA characterization, for instance gain, output power, linearity and efficiency. Whereas, PA efficiency is straightway linked to the DC power consumption. If a PA operational efficiency is not adequate, a large amount of power is consumed instead of passing to the antenna. As a result, PA increases the cost of transmission in wireless communication. Moreover, other depraved effects in the form of shorter device life, required addition cooling setup and week compactness. Three important FOM of a PA gain, efficiency and intermodulation are described in following sub-sections.

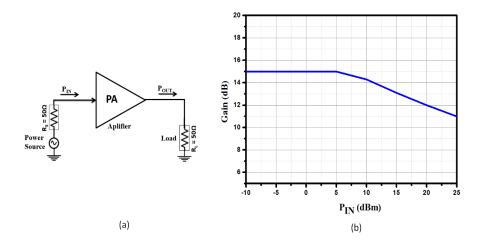

#### 2.2.1 Gain and gain compression point (P1dB)

The gain of an amplifier is defined as the ratio of its output power to the input power

$$G = 10log_{10} \left(\frac{P_{OUT}}{P_{IN}}\right) \tag{2.1}$$

Where in equation 2.1, G is the gain of an amplifier in dB, P<sub>OUT</sub> and P<sub>IN</sub> are output power and input power in watt, respectively. When a PA is supplied with comparatively small input power signal, the gain of the PA is flat and independent of input signal power level up to certain point. On the other hand, the PA gain "drop" depends on the selected class of operation, when it is driven with comparatively a large input power signal due to transistor nonlinearities, a curve

of typical PA gain response is shown in Figure 2.2 (b). As a matter of fact, the proposed analysis is strictly correct only under Class-A operation.

Figure 2.2: (a) PA gain measurement schematic and (b) gain vs. input power plot.

Figure 2.3: Plot for 1dB compression point of a Class-A power amplifier.

As described above, when the supplied input power of a PA reaches to certain power level, the gain of a PA start to drops due to the presence of nonlinearities in transistor. In order to describe the linearity of an amplifier, 1 dB compression point  $(P_{1dB})$  is considered, that is the point where gain of a PA declined 1 dB lower than its small signal gain, as it is presented in Figure 2.3. In real system

application, in order to get higher gain sometime two or more PAs are cascaded. For two cascaded PAs, the gain of the PA is depend on second PA and the effect of P1dB on system can be formed

$$G = G_0 - e^{\frac{P_{IN} - P_{IN1dB}}{5}} (2.2)$$

Where in equations 2.2, G is the gain of the single-stage amplifier.  $G_0$  and  $P_{IN}$  are small-signal gain (dB) and input power (W) of the amplifier, respectively. Therefore,  $P_{1dB}$  of the cascaded amplifier is  $(P_{IN1dB} + G_0 - 1)$ .

#### 2.2.2 Power efficiency

An amplifier efficiency can be defined as the ratio of radio frequency (RF) output power to the injected DC power. In wireless applications, we mostly concerned with output power at the fundamental frequency. Efficiency of an amplifier can also be completely determined by the time domain voltage and current waveforms at the device intrinsic drain terminal. PA should provide high efficiency, when its drain and current voltage waveforms have minimum overlap as in Class-F power amplifier. Conversely, PA has low efficiency in case of Class-A amplifier due to large overlap exists in current and voltage waveforms.

Figure 2.4: Power amplifier concept.

At any given frequency gain of an amplifier can be calculated by given equation (2.3) below

$$G(f_0) = \frac{P_{OUT}(f_0)}{P_{IN}(f_0)}$$

(2.3)

In equation 2.3,  $P_{IN}$  and  $P_{OUT}$  are the input and output power of the PA at a specific frequency, respectively. As explained above, power amplifiers increase the power of the input signal and transforms the DC power into RF power at a fundamental frequency ( $f_0$ ). Unfortunately, some quantity of the injected DC power to the PA is dissipated in the form of heat from the active device and some quantity of the injected power is sent to the harmonics at drain terminal. Total DC power consummation can be described by equation 2.4 given below

$$P_{DC}(f_0) = P_{OUT}(f_0) + P_{DIS} + \sum_{n=2}^{\infty} P_{OUT}(nf_0)$$

(2.4)

where,  $P_{OUT}(f_0)$  is the output of the amplifier at a specified frequency.  $P_{DIS}$  is the dissipated power from the active device and last term in the equation is the harmonics power. PA efficiency can be defined as Drain efficiency (DE) and Power Added Efficiency (PAE). Drain efficiency is the ratio between output powers to the supplied DC power [10]

$$\eta = \frac{P_{OUT}}{P_{DC}} \tag{2.5}$$

where  $P_{OUT}$  is the output power and  $P_{DC}$  is the DC power consumption of the amplifier. Power Added Efficiency (PAE) is the ratio of difference between output and input power to the DC power consumption [10]

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}} = \frac{P_{OUT}}{P_{DC}} \left( 1 - \frac{1}{G} \right)$$

(2.6)

In equation 2.6,  $P_{OUT}$  is the output power,  $P_{IN}$  is the input power,  $P_{DC}$  is the DC power consumption and G is the gain of an amplifier.

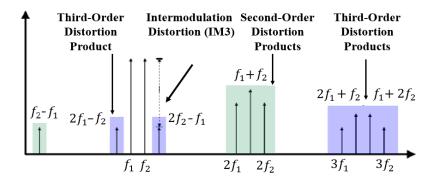

#### 2.2.3 Intermodulation distortion

The intermodulation distortion (IMD<sub>3</sub>) is another figure-of-merit used to describe the linearity of a power amplifier. IMD<sub>3</sub> involves the use of a two-tones stimulus. If the power of two-tones is equal, then it is the difference between the power of the fundamental signal and the third-order products. IMD<sub>3</sub> can be calculated from the subsequent equation [13]

$$IMD_3 = P_0 - P_{30} (2.7)$$

where  $P_{\rm O}$  is the output power of the fundamental signal of the DUT, and  $P_{\rm 3O}$  is the output power level of third-order products. IMD<sub>3</sub> should be as low as possible for a linear power amplifier or it should be within the limit of communication standard. Intermodulation distortion products are spaced too close to the fundamental frequency stimulus, as can be seen from Figure 2.5. These upper and lower intermodulation distortion products should be perfectly filtered for noise free communication. In order to measure the IP3 performance of a system, the two fundamental tones powers are set at the same power level. A 1 dB change in the fundamental tones results in a 3 dB change in the third-order distortion products.

In addition to IMD<sub>3</sub> and IP3, linearity of a power amplifier can also be determined by ACPRs, also known as Adjacent Channel Leakage Ratio (ACLR). ACPR linearity metric is used in many wireless standards such as UMTS or 3GPP LTE to define the power amplifier and system linearity. ACPR can be defined by the ratio of power in a modulated signal versus power emitted into an adjacent channel [14]. In order to measure ACPR, one must provide the device under test (DUT) with a modulated stimulus.

Figure 2.5: Intermodulation lower and upper tones due to non-linear device [14].

## 2.3 Power amplifier classes

Transconductance power amplifiers are non-linear systems that have an output power level equal to the input power multiplied by gain at a specified frequency [11]. A transconductance power amplifier is used as a controlled current sources and can be described by their working class such as Class-A, Class-AB, Class-B, and Class-C amplifiers. These amplifiers are extensively deployed in wireless transmitters and have been discussed in detail in number of

books/articles [10], [15-17]. Figure 2.6 shows a simplest circuit diagram of Class-A, Class-AB, Class-B, Class-C amplifiers. The PA circuit is single-ended. It is assumed that the RF choke, DC-coupling capacitor and the filter are all ideal component or circuit.

The easiest way to describe the transconductance amplifiers classes is the conduction angle. Class-A amplifier has a conduction angle of  $\theta_C = 2\pi$ , Class-AB amplifier has a conduction angle of  $\pi < \theta_C < 2\pi$ , Class-B amplifier has a conduction angle of  $\pi$ , and Class-C amplifier has a conduction angle of  $0 < \theta_C < \pi$ . In Figure 2.6, current-voltage waveforms at the drain and gate terminal of the amplifier are drown for a Class-A amplifier. The Class-A amplifier is a highly linear and also the most "well-behaved" amplifier.

Figure 2.6: Simplified diagram of Class-A, -AB, -B and -C amplifier.

#### 2.3.1 Class-A amplifier

Regardless of the Class-A amplifier's simplest architecture, it also offers efficiency and linearity benchmark for other advanced classes of operation. Moreover, the concept of load line analysis that is easily illustrated using a Class-A amplifier; is applicable to other classes of operation as well. Class-A PA has a conduction angle of  $\theta_C = 2\pi$ , and its voltage-current waveforms are presented in Figure 2.7. The maximum output power of a Class-A PA can be calculated by given equations [10]

$$P_{Max} = \frac{(V_{max} - V_{knee}) I_{max}}{8}$$

(2.8)

Where in equation (2.8),  $V_{max}$  and  $V_{knee}$  are the breakdown voltage and the knee voltage of Class-A PA, respectively.  $I_{max}$  is the maximum bearable current of the elected transistor. Although, Class-A amplifier has high linearity and output power compare to other classes. However, it has a major disadvantage. Theoretically, the maximum possible efficiency is only 50%. In practice, Class-A efficiency is significantly reduced to about 30-35% for L-band applications. If we assume practical possible efficiency's value is 33% from a PA. In this case, the amount of heat produced by a transistor can be higher than the heat-handling capability of a common-source transistor package. Because of this reason, Class-A amplifier is not an appropriate choice for L-band high power application.

Nowadays, Class-A amplifiers are only used at upper microwave frequency from 5 GHz to millimeter-wave region. The reasons of using Class-A PA at high frequency is that it requires comparatively less input power to drive the PA and it has higher small-signal gain compare to other classes as well. Since at microwave and millimetre frequencies, the power gain is typically the restrictive feature in PA design, Class-A is consider an appropriate choice.

Figure 2.7: Current and voltage waveforms of a Class-A power amplifier.

## 2.3.2 Reduced conduction angle modes: Class -AB, -B, -C

In order to increase the drain efficiency of an amplifier, the ratio of the fundamental signal output power to the DC power consumed must increase, as defined in equation (2.5). One way to enhance the drain efficiency is to regulate the gate bias ( $V_{GG}$ ) of the transistor; as a result, conduction ( $\theta_C$ ) of the active device is reduced accordingly. For reduced conduction angle modes amplifiers, a

part of the gate voltage waveform dips underneath the zero level into the non-conducting area. Based on conduction angle, amplifier can be classified into different classes, which are described in the following paragraphs.

The current and voltage waveforms of a Class-AB amplifier are shown in Figure 2.8. Since, the gate bias voltage (V<sub>GG</sub>) of a Class-AB amplifier is reduced from Class-A amplifier, the current clipping occurs. Even though the current clipping produces harmonics and nonlinear effects, Class-AB amplifier is still a running horse for L-band wireless application due to fair compensation between linearity and drain efficiency. Class-AB has higher efficiency and lower linearity compare to Class-A amplifiers. Many PA designers use Class-AB amplifiers as a starting point, and apply harmonic control techniques to improve efficiency. We designed a 5 W Class-AB amplifier by terminating second and third harmonics at the drain terminal of the active device. The detail of the proposed Class-AB amplifier is given in the subsequent chapter.

Figure 2.8: Current and voltage waveforms of a Class-AB power amplifier.

The current and voltage waveforms of a Class-B amplifier are shown in Figure 2.9. Class-B amplifier is a transition in the middle of the Class-AB and the Class-C amplifiers. The theoretical possible maximum drain efficiency of a Class-B amplifier is 78.5%, which is significantly higher than the Class-A amplifier. In practice, Class-B amplifier can achieve a drain efficiency of 60% in L-band. Since, the gate bias voltage (V<sub>GG</sub>) of a Class-B amplifier is reduced from Class-AB amplifier; the more current clipping happens compared to Class-AB amplifier. The Class-B amplifier efficiency is much higher than the Class-A amplifier. Therefore, there is no more need of a sophisticated and expansive cooling setup. Consequently, it is a low cost amplifier. However, its linearity is worse compared to Class-AB modules.

Figure 2.9: Current and voltage waveforms a of Class-B power amplifier.

The current and voltage waveforms of a Class-C amplifier is shown in Figure 2.10. Class-C amplifier is an efficient amplifier compared to other reduced angle amplifiers. Theoretically, it has drain efficiency from 78.5 to 100%. However, there are several drawbacks to implement Class-C amplifier in the L-band application. The first disadvantage is the high drain efficiency originates at the cost of the power gain. The other disadvantages is that the amplifier is highly nonlinear. Consequently, it can be exploited only for highly nonlinear systems, or will require additional complex linearization techniques to improve linearity. Theoretically, maximum possible efficiency of different classes of amplifier operation are presented in Table 2.1.

Figure 2.10: Current and voltage waveforms a of Class-C power amplifier.

| Class of operation | Peak drain efficiency (η) |  |

|--------------------|---------------------------|--|

| Class-A            | $\eta = 50\%$             |  |

| Class-AB           | 50% < η < 78.5%           |  |

| Class-B            | η = 78.5%                 |  |

| Class-C            | 78.5% < η < 100%          |  |

Table 2.1: Theoretically efficiency of different classes of amplifier operation.

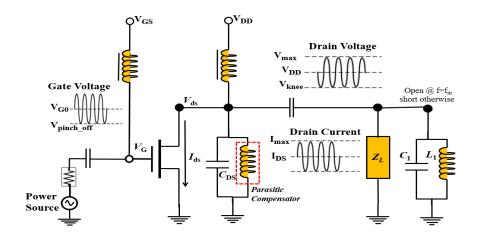

# 2.3.3 Switch-mode Class-F and F<sup>-1</sup> power amplifier

Switching-mode power amplifiers use active transistor as a switch. Active device is ideally fully on (short-circuit) or fully off (open-circuit). Switching-mode PA are very common in switch-mode power supply (SMPS). However, recently these circuits have been exploited for RF power amplifiers as well, because of the availability of commercial active devices with sufficient gain and power at microwave frequencies. The theoretical maximum drain efficiency for Class-E and Class-E/F amplifiers is 100%; in practice many published articles reported maximum drain efficiencies from 70-85% [18-20]. Class-F and Class-F<sup>-1</sup> amplifiers are built on waveform shaping technique by properly terminating the harmonics in output-matching network.

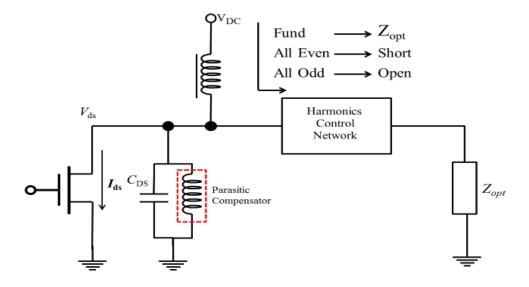

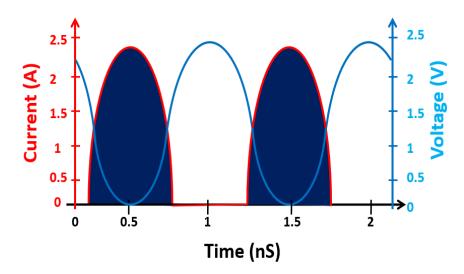

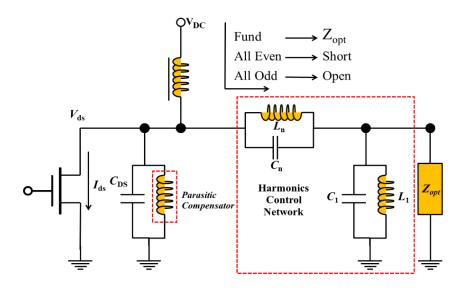

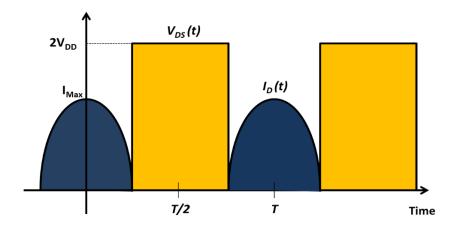

Typically, Class-F power amplifier is biased in Class-B mode and active device is precisely loaded with harmonics terminations at fundamental and harmonic frequencies. For an ideal Class-F operation open-circuit terminations at all the odd harmonics and short-circuit terminations at all the even harmonics are required, and vice versa for Class-F<sup>-1</sup> amplifier, as shown in Figure 2.11. Due to the switching nature of the active device, harmonics will be generated within the transistor and harmonics control network is presenting the ideal short-circuits at the even harmonics and open-circuits at the odd ones. Ideal Class-F PA drain waveforms consist of squared drain voltage and truncated sinusoidal drain current. The Class-F power amplifier drain voltage waveform comprises fundamental signal and odd harmonics, which is approximately exhibit a square wave and drain current waveform consist of even harmonics, respectively. Figure 2.12 shows the ideal drain and voltage current waveforms of the Class-F PA at the intrinsic drain terminal of the active device. Moreover, in an ideal Class-F PA

load impedance at all odd harmonics should be tuned to open circuit  $(Z=\infty)$  and the load impedance at all even harmonic should be tuned to short circuit (Z=0). The third harmonic of the drain voltage has to be out-of-phase with the fundamental to generate the Class-F-like drain voltage waveform.

Figure 2.11: Class-F power amplifier topology with ideal infinite harmonic termination.

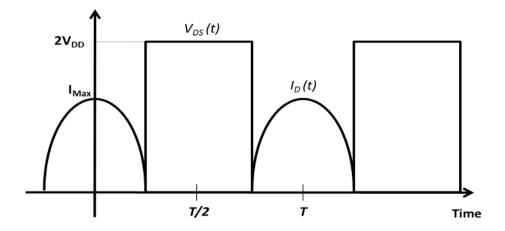

Figure 2.12: Ideal drain voltage and current waveforms for a Class-F power amplifier [22].

The general equations of Class-F PA for current and voltage waveforms are reported in [21]. These equations are (2.9) and (2.10), where Ø is the phase difference between the fundamental signal and harmonics

$$V(t) = V_{ds} + V_1 \cos(w_0 t + \phi_1) + V_2 \cos(2w_0 t + \phi_2) + V_3 \cos(3w_0 t + \phi_3) + \dots (2.9)$$

$$I(t) = I_{dd} + I_1 \cos(w_o t + \emptyset_1) + I_2 \cos(2w_o t + \emptyset_2) + I_3 \cos(3w_o t + \emptyset_3) + \dots (2.10)$$

Class-F PA can only maximize efficiency and output power, if no overlap exists between current and voltage waveforms at intrinsic drain terminal of the active device. No overlap between current and voltage waveforms means less power dissipation in active device. Furthermore, no power is sent to harmonics.

$$i_D(\theta) = \begin{cases} I_{Max} . \cos(\theta) & If & -\frac{\pi}{2} \le \theta \le \frac{\pi}{2} \\ 0 & otherwise \end{cases}$$

(2.11)

$$v_{DS}(\theta) = \begin{cases} 0 & If -\frac{\pi}{2} \le \theta \le \frac{\pi}{2} \\ 2.VDD & otherwise \end{cases}$$

(2.12)

As it can be seen from expression (2.11) and (2.12), current  $(i_D(\theta))$  and voltage  $(v_{DS}(\theta))$  components with the same order does not exist [22]. Moreover, it also clear from Figure 2.12 that ideally drain current and voltage waveforms do not overlap at any point. As a result null power dissipation in the active device and the first condition for maximizing the efficiency is achieved [22].

$$P_{diss} = \frac{1}{T} \int_0^T V_{DS}(t) \cdot i_D(t) dt = 0$$

(2.13)

From the Fourier analysis of drain current and voltage waveforms, their harmonic components are expressed as:

$$i_D(\theta) = \sum_{n=0}^{\infty} I_n. \cos(n\theta)$$

(2.14)

Where

$$I_{n} = \begin{cases} \frac{I_{Max}}{\pi} & n = 0\\ \frac{I_{Max}}{2} & n = 1\\ \frac{2 \cdot I_{Max}}{2} & (-1)^{\frac{n}{2} + 1} \\ 0 & n \text{ odd} \end{cases}$$

And

$$v_{DS}(\theta) = \sum_{n=0}^{\infty} V_n \cdot \cos(n\theta)$$

(2.15)

Where

$$V_n = egin{cases} V_{DD} & n = 0 \ -\frac{4 \cdot V_{DD}}{2} & n = 1 \ 0 & n \ even \ \hline \frac{4 \cdot V_{DD}}{\pi} & n \ odd \end{cases}$$

As it can be noted from the expressions above, current and voltage, Fourier components with the same order n are alternately not present. As a result, the power delivered at harmonic frequencies (Pout, nf = 0, n > 1) is zeroed, thus also fulfilling the remaining condition to achieve maximum efficiency. In summary, both conditions maximizing the efficiency are simultaneously fulfilled and a theoretical 100% drain efficiency is achieved.

On the other hand, however, previously described ideal waveforms must be generated via a proper output network, able to synthesize all the requested loading conditions for the output current harmonic content. The values of terminations are easily inferred as the ratio between the respective Fourier components Vn and In, i.e.

$$Z_{n} = \frac{V_{n}}{I_{n}} = \begin{cases} \frac{8}{\pi} \cdot \frac{V_{DD}}{I_{Max}} & n = 1\\ 0 & n \text{ even}\\ \infty & n \text{ odd} \end{cases}$$

In particular, the terminating impedance at fundamental frequency must be purely resistive (R<sub>F</sub>), since it results from perfectly phased behaver of the other harmonics.

$$R_F = \frac{4}{\pi} \cdot \frac{2 \cdot V_{DD}}{I_{Max}} \tag{2.16}$$

The requested set of terminations, including harmonics, has to be synthesized by a purely passive output-matching network. As anticipated, it results in a short-circuit condition for even harmonics and an open-circuit for odd ones. Finally, a comprehensive comparison is presented in Table 2.2 based on theoretically performance in terms of efficiency, output power and linearity of all the amplifiers classes.

| Class | Efficiency | Power  | Linearity       | Conduction |

|-------|------------|--------|-----------------|------------|

|       |            |        |                 | angle      |

| A     | 50% Max.   | High   | Best            | 100%       |

| AB    | < 68%      | High   | Some Distortion | < 100%     |

| В     | < 78.5%    | High   | More Distortion | 50%        |

| С     | 78.5%      | Low    | Poor            | < 50%      |

| D     | < 100%     | Medium | Moderate        | 50%        |

| E/F   | 100%       | Low    | Poor            | 0%         |

Table 2.2: Summary of amplifier classes of operation.

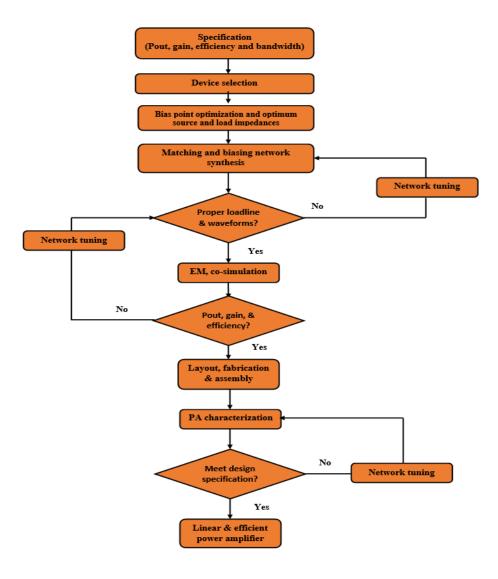

# 2.4 Power amplifier design flow

PA design specifications and selection of an appropriate device is the first step toward power amplifier design, as shown in Figure 2.13. The key parameters to consider for selecting a transistor are gain, power capability and input/output impedances. After the selection of the appropriate transistor, stability at in-band and out-of-band frequencies should be determined. If the selected transistor is not unconditionally stable, lumped component based stability networks are inserted at the input of the transistor in order to achieve stability. After making transistor

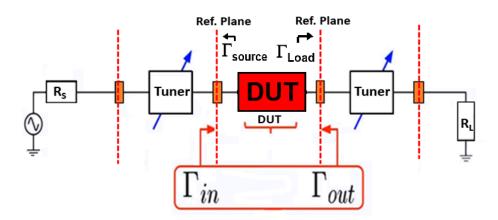

stability at operating frequencies, optimum load and source impedances are extracted for achieving best power and gain performance. In this research work, optimum load and source impedances are decided through the load- and source-pull simulations in ADS. From the power and efficiency contours on a Smith chart of the selected device, the optimum impedances can be selected for required performance. In final step, biasing networks are designed for required band and impedance transformation. The designed procedure and practical design constrains of a PA from the first to final step of realization are discussed in detail in next section.

Figure 2.13: Flow chart of a typical power amplifier.

# 2.5 Power amplifier design

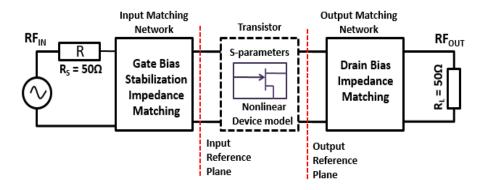

The power amplifier theory, classes and design flow described in above section primarily focused on the ideal working environments that predict a highly efficient amplifier operation and relaxed strategy to develop a faultless amplifier. However, in practice there are many challenges of applying these concepts in practical power amplifiers. In the following sections, we will present these issues and the solutions for applying theoretical concepts. Figure 2.14 shows the main modules of a real-world RF power amplifier.

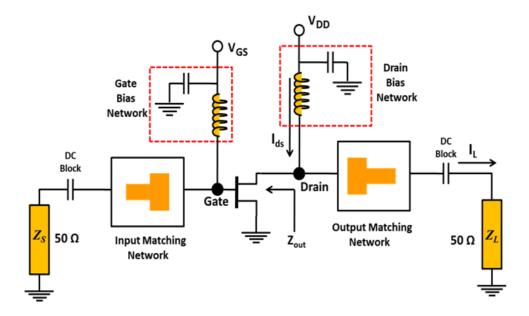

Figure 2.14: Generic block scheme of a single-stage Microwave amplifier.

## 2.5.1 Device package & de-embedding prasitics

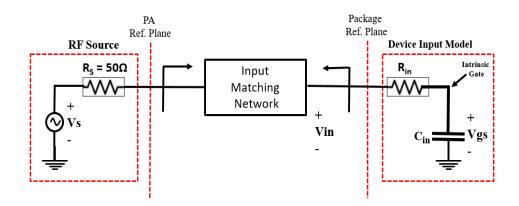

Usually, hybrid RF PAs use packaged devices, in order to protect the bare device from external environment and to help the thermal dissipation as well. Limited number of designs are available in the literatures that uses pre-matched transistors. For enhancing the design flexibility, many PA designer use classically unmatched transistor. Figure 2.14 is presenting a conventional packaged, unmatched active device after removing the top cover. The transistor die is fixed on thermal conductivity flange, which also works as source terminal for an electrical ground. The bond-wires are exploited for drain and gate terminal connection to the external world. The model of a typical active device based on lumped and distributive components depicted in Figure 2.16. Figure 2.15 shows the bare die generic signal model reported in [13]. Where major parasitics are on the drain side of the device and represented L1 and TL1 respectively. When accounting the package effect, the packaged device has a narrower matching bandwidth and more frequency dispersive effects compare to a bare die device. Due to the impedance alteration produced by the device and package parasitics is

required to address the impedance shift compensation in the matching network design, the reference plane of interest may shift from the current generator plane to the package reference plane. Multi-harmonics termination in the output matching networks at the intrinsic drain is problematic due to inaccuracy in the active device parasitics model. At microwave frequencies, the harmonics termination is even worse, particularly at the intrinsic drain terminal.

Figure 2.15: A generic signal model [23].

Figure 2.16: A typical device package model.

## 2.5.2 Bias network and stability

Biasing networks are used to supply the gate and drain voltages to the active device for maintaining the drain current at predefined bias voltages. Generally, PA is required two biasing circuits to supply the drain and gate voltages to the active device. Gate and drain biasing circuits should be capable to block the RF signal for entering into the power supplies throughout the desired band of interest and should presents low impedance at lower frequency. To stop the RF signal from entering into the DC supply, an RF choke is connected between the DC supply and the transistor. The RF choke can be a large inductor or a short-circuited  $\lambda/4$  transmission line at the designed frequency. Both, RF choke and quarter-wave transmission line should present a very high resistance to the RF input signal at the fundamental frequency. A  $\lambda/4$  transmission line can also work as second harmonics short stub as well.

Moreover, both the drain and gate basing networks should provide high impedance to the RF input signal for a required bandwidth to stop the bias modulation. The RF input and output should be DC-decoupled to stop interference. Therefore, DC blocking capacitors are placed in series with the matching networks. The value of the blocking capacitors is chosen so that the capacitors behave as a short circuit at the fundamental frequency. The most commonly used biasing network in the literature is based on a  $\lambda/4$  transmission line at the designed frequency with 50  $\Omega$  impedance characterization for the both drain and gate biasing circuits in the RF power amplifier. A short circuit  $\lambda/4$  transmission line transforms the short into open at RF frequency. The input impedance of a short circuit transformer can be calculated from transmission line theory by using equation (2.17) given below [24]

$$Z_{in} = jZ_0 \tan\beta l \approx j2\pi Z_0 \sqrt{\frac{\varepsilon_{eff}(f_0) f_0 l}{C_0}}$$

(2.17)