# POLITECNICO DI TORINO

## SCUOLA DI DOTTORATO

Dottorato in Ingegneria Elettronica e delle Comunicazioni – XXVIII ciclo

# Tesi di Dottorato

# Multilevel Modeling and Architectural Solutions for Emerging Technology Circuits

## Juanchi Wang

Tutore

prof. Mariagrazia Graziano

prof. Maurizio Zamboni

Coordinatore del corso di dottorato

prof. Ivo Montrosset

March 2016

# Summary

In the last decades, the main driving force behind the astonishing development of CMOS technology, was the transistor scaling process. The reduction of transistor sizes has granted a continuous boost in circuits performance. But now that the scaling process is reaching its physical limits, researchers are forcusing on new emerging technologies.

Research on these new technologies is usually carried on using a traditional approach. Some studies concentrate on new devices without analyzing circuits based on them. Other studies analyze circuit architectures without considering devices characteristics and limitations. However, given that the nature of emerging technologies can be very different from CMOS, new research methodologies should be adopted. A clear link between device and architectural analysis is necessary to understand the true potential of the technology under study.

The objective of this PhD thesis is the analysis of emerging technologies using an innovative methodology. Using complex and realistic circuits as benchmark, high level models are built incorporating low level device characteristics. This methodology strongly links device and architectural levels.

The methodology was applied to two emerging technologies: NanoMagnet Logic (NML) and Nanoscale Application Specific Integrated Circuits (NASIC). A brief introduction of fundamental information on the two technologies is given in Chapter 1.

The application of the methodology on NML technology is divided in two parts (Chapter 2): i) architecture-level timing and performance analysis and circuits optimization; (ii) area and power estimations using VHDL modeling. Starting from an exhaustive analysis of the effects and the consequences derived by the presence of loops in a complex NML sequential architecture, solutions have been proposed to address the problem of signal synchronization, and optimization techniques have been explored for performance maximization. Area and power estimations have been performed on multiple NML architectures in order to obtain a complete evaluation on the implementation of NanoMagnet Logic in comparison with the CMOS technology.

Chapter 4 is dedicated to NASIC technology with basic principles described in Chapter 3. Basic computational blocks are implemented using a multilevel modeling approach. A detailed analysis of circuits' area and power estimations is obtained. Techniques to optimize the area of circuits at the cost of reduced throughput were also investigated.

The research activity presented in this thesis highlights the development of an innovative methodology based on high-level models that embed information obtained from physical level simulations. By exploiting this methodology to different emerging technologies, such as NML and NASIC, it allows to efficiently analyze circuits and therefore to bring architectural improvements.

# Contents

| Sι | ımm  | ary    |                                                      | II |

|----|------|--------|------------------------------------------------------|----|

| 1  | Intr | roduct | ion to NanoMagnet Logic                              | 1  |

|    | 1.1  | Techn  | ology Background                                     |    |

|    |      |        | tum-dot Cellular Automata                            | 1  |

|    |      | 1.1.1  | QCA Logic                                            | 1  |

|    |      | 1.1.2  | QCA Clock Mechanism                                  | 3  |

|    |      | 1.1.3  | QCA Implementation                                   | 3  |

|    | 1.2  | Nanol  | Magnet Logic (NML)                                   | 5  |

|    |      | 1.2.1  | NML Basic Cell                                       | 6  |

|    |      | 1.2.2  | NML Logic Gates                                      | 7  |

|    |      | 1.2.3  | Clock Mechanism                                      | 8  |

|    |      | 1.2.4  | Multiphase Clock System                              | 8  |

|    |      | 1.2.5  | Clock Zone Layout                                    | 10 |

|    |      | 1.2.6  | VHDL Modeling                                        | 12 |

| 2  | Nar  | noMag  | net Logic Architecture Analysis                      | 16 |

|    | 2.1  | Smith  | -Waterman Systolic Array Architecture Implementation | 16 |

|    |      | 2.1.1  | Biosequences Alignment Analysis                      | 16 |

|    |      | 2.1.2  | Smith-Waterman Systolic Array Architecture           | 17 |

|    |      | 2.1.3  | SW NML Implementation                                | 21 |

|    | 2.2  | Perfor | rmance Optimization                                  | 24 |

|    |      | 2.2.1  | Data Interleaving                                    | 24 |

|    |      | 2.2.2  | Architecture Redesign for Loops Lengths Reduction    | 27 |

|    | 2.3  | Signal | Synchronization                                      | 29 |

|    |      | 2.3.1  | Nested Loops                                         |    |

|    |      | 2.3.2  | Additional Delay Loops                               |    |

|    | 2.4  | NML    | Architecture Area and Power Evaluation               | 32 |

| <b>3</b>     | $\operatorname{Intr}$ | roduction to Nanoscale Application Specific Integrated Circuits | <b>3</b> 4 |

|--------------|-----------------------|-----------------------------------------------------------------|------------|

|              | 3.1                   | Nanowire Field Effect Transistors (NW FETs)                     | 34         |

|              | 3.2                   | Nanoscale Application Specific Integrated Circuits (NASICs)     | 38         |

|              |                       | 3.2.1 Nanotile                                                  | 36         |

|              |                       | 3.2.2 NASIC Clock Mechanism                                     | 41         |

|              |                       | 3.2.3 2-bit Full Adder                                          | 43         |

|              |                       | 3.2.4 N3ASIC                                                    | 44         |

|              |                       | 3.2.5 NASIC VHDL Modeling                                       | 46         |

| 4            | NA                    | SIC Circuit Modeling and Implementation                         | 49         |

|              | 4.1                   | Area and Power Evaluation                                       | 49         |

|              |                       | 4.1.1 Area Evaluation                                           | 49         |

|              |                       | 4.1.2 Power Estimation                                          | 51         |

|              |                       | 4.1.3 Nanowire Capacitance $(C_{nanowire})$ Estimation          | 51         |

|              |                       | 4.1.4 Nanowire Switching Activity Computation                   | 52         |

|              |                       | 4.1.5 Simplified Dynamic Power Estimation                       | 55         |

|              | 4.2                   | NASIC Circuits Implementation                                   | 56         |

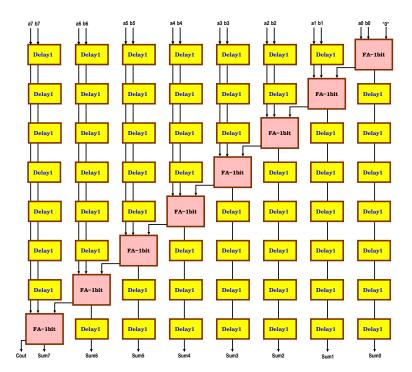

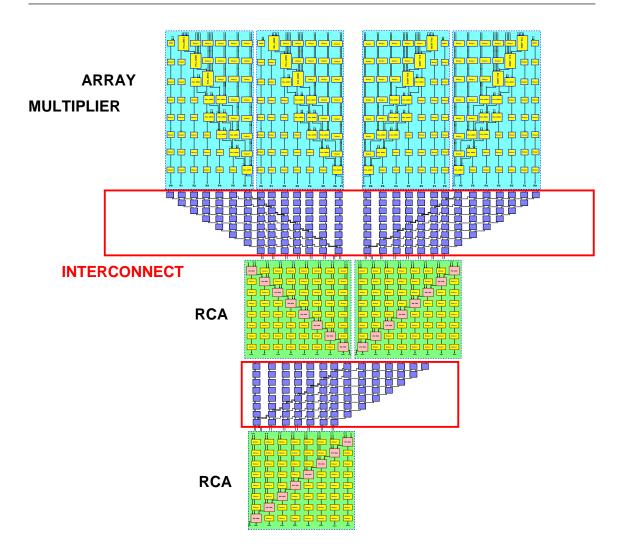

|              |                       | 4.2.1 Ripple Carry Adder                                        | 56         |

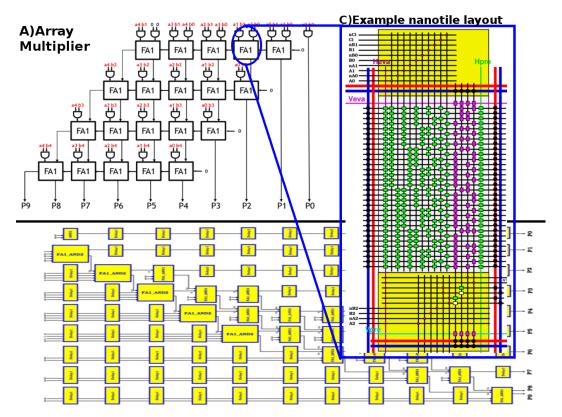

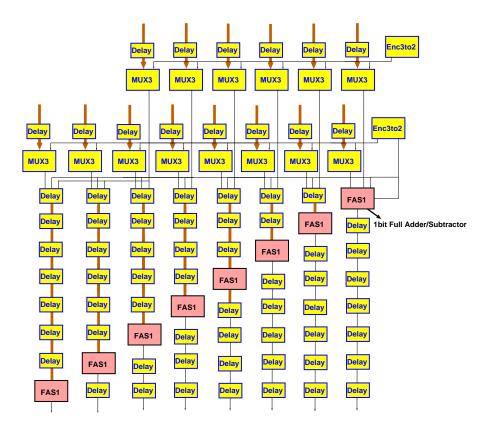

|              |                       | 4.2.2 Array Multiplier                                          | 57         |

|              |                       | 1                                                               | 59         |

|              |                       |                                                                 | 61         |

|              | 4.3                   | Structural Optimization                                         | 63         |

| т            | •                     | 1*                                                              | 00         |

| Ι            | Ap                    | ppendix                                                         | 69         |

| $\mathbf{A}$ | Mer                   | mristive Devices                                                | 70         |

|              | A.1                   | Introduction to Memristive Devices                              | 70         |

|              | A.2                   | Memristive Devices and Switching Mechanisms                     |            |

|              | A.3                   | Memristive Devices Architecture                                 | 77         |

| В            | SW                    | NML Implementation VHDL Modeling                                | <b>7</b> 8 |

|              | B.1                   | NML Power Estimation VHDL Model                                 | 78         |

|              | B.2                   | NML 1-bit Full Adder VHDL code with power estimator             | 80         |

|              | B.3                   | NML Generic Ripple Carray Adder VHDL code with power estimator  | 83         |

| $\mathbf{C}$ |                       |                                                                 | 87         |

|              | C.1                   | Nanotile Power Estimation VHDL Model                            | 87         |

| D            |                       | •                                                               | 90         |

|              | D.1                   | Testbench for optimized 6-bit Accumulator structure             | 90         |

Bibliography 94

# List of Tables

| 2.1 | Power consumption and area estimation for a single processing el-  |    |

|-----|--------------------------------------------------------------------|----|

|     | ement of the systolic array with main NML implementations and      |    |

|     | CMOS LOP 21nm technology. J. Wang et al. "Biosequences anal-       |    |

|     | ysis on NanoMagnet Logic", International Conference on IC Design   |    |

|     | and Technology (ICICDT), May 2013                                  | 33 |

| 4.1 | Ripple Carry Adder area and power estimation with NASIC circuit    |    |

|     | modeling.                                                          | 57 |

| 4.2 | Array Multiplier area and power estimation with NASIC circuit mod- |    |

|     | eling                                                              | 58 |

| 4.3 |                                                                    |    |

| 4.4 | Booth Multiplier area and power estimation with NASIC circuit mod- |    |

|     | eling                                                              | 61 |

| 4.5 | FIR area and power estimation with NASIC circuit modeling          | 62 |

| 4.6 | RCA area estimation comparison with and without pre-skew and de-   |    |

|     | skew networks.                                                     | 64 |

| 4.7 | Area estimation comparison between two structures of 2-level Accu- |    |

|     | mulator (data = 8/16 bits_feedback_latency = 6 clock_cycles)       | 68 |

# List of Figures

| 1.1        | Basic 4-dot QCA cells and logic states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

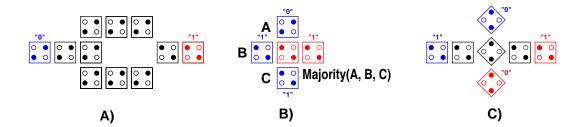

| 1.2        | Basic QCA logic gates. A)Inverter B)Majority Voter C)Crosswire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2      |

| 1.3        | Basic 6-dot QCA cells with 3 states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3      |

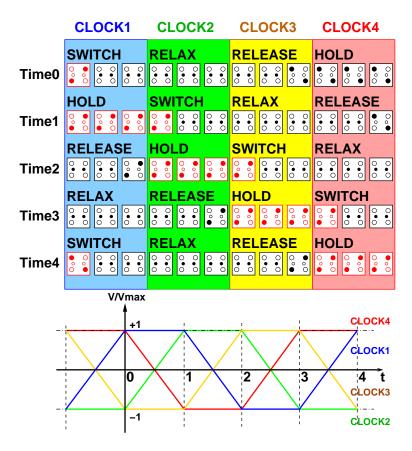

| 1.4        | QCA clock mechanism with 4-phase clock signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4      |

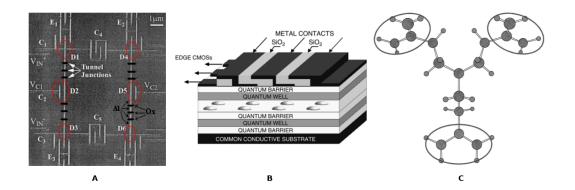

| 1.5        | A) Metal QCA structure B) Semiconductor QCA structure C) Molecular QCA structure. A) R. K. Kummamuru et al. "Operation of a Quantum-Dot Cellular Automata (QCA) Shift Register and Analysis of Errors", IEEE Transactions on Eletron Devices, vol. 50, n. 9, Sept. 2003. B) A. Khitun et al. "Multi-functional edge driven nano-scale cellular automata based on semiconductor tunneling nano-structure with a self assembled quantum dot layer", Superlattices and Microstructures, vol. 37, pp. 55-76, 2005. C)C.S. Lent et al. "Clocked Molecular Quantum-Dot Cellular Automata", IEEE | 5      |

| 16         | Transactions on Electron Device, vol. 50, no. 9, september 2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5<br>6 |

| 1.6<br>1.7 | NML wire configurations. A) Harizantal wire. B) Vertical wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6      |

|            | NML wire configurations. A) Horizontal wire. B) Vertical wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | O      |

| 1.8        | NML basic logic gates. A) Inverter. B) Crosswire. C) Majority Voter. D) OR gate. E) AND gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7      |

| 1.9        | NML clock mechanism with magnetic field forcing nanomagnets into an intermediate unstable state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8      |

| 1.10       | NML clock implementation. A) Magnetic field. B) STT-current. C) Magnetoelastic. J. Wang et al. "Biosequences analysis on NanoMagnet Logic", International Conference on IC Design and Technology (ICICDT), May 2013                                                                                                                                                                                                                                                                                                                                                                       | 9      |

| 1 11       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10     |

|            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

|            | 3-phase clock zone layout. A) Traditional layout. B) Snake-like layout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11     |

| 1.13       | Snake-like layout physical view. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                                                                                                                                                                                                                                                                                | 11     |

| 1.14 | NML circuit VHDL modeling. J. Wang et al. "Biosequences analysis on NanoMagnet Logic", International Conference on IC Design and Technology (ICICDT), May 2013                                                                                                                                                                               | 12 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.15 | Parameters and constants used in the NML power model. M. Vacca et al. "NanoMagnet Logic Microprocessor: Hierarchical Power Analysis", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, pp. 1410-1420, 2012                                                                                                         | 15 |

| 2.1  | Amino Acide alphabetical character representation. L. R. Murphy et al. "Simplified Amino Acid Alphabets for Protein Fold Recognition and Implication for Folding", Protein Engineering, vol. 13, pp. 149-152, 2000                                                                                                                           | 17 |

| 2.2  | Biosequence alignment analysis principle                                                                                                                                                                                                                                                                                                     | 17 |

| 2.3  | Systolic Array Structures. A) Matrix Systolic Array. B) Linear Systolic Array. C) Special Systolic Array. G. Causapruno et al. "Protein Alignment Systolic Array Throughput Optimization", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 1, pp. 68-77, 2014                                                 | 18 |

| 2.4  | Smith-Waterman systolic array architecture with processing elements .G. Urgese, "Analysis and Design of an Optimized HW Accellerator for Protein Alignment", Master thesis, Politecnico di Torino, Dept. Eletr., Torino, Italy, Sept. 2012.                                                                                                  | 19 |

| 2.5  | Smith-Waterman systolic array architecture with processing elements.                                                                                                                                                                                                                                                                         | 20 |

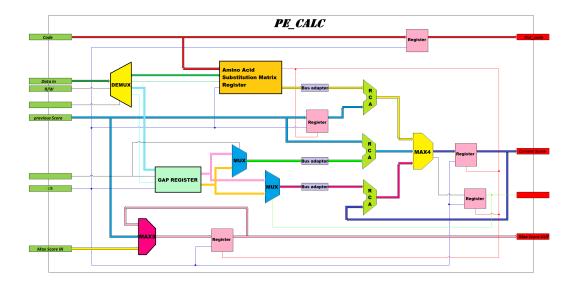

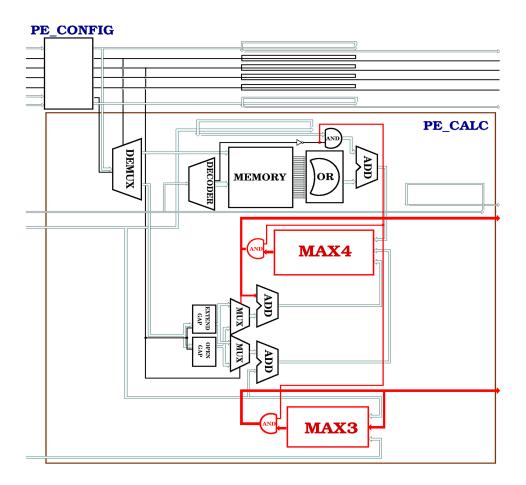

| 2.6  | Structure of PE_Calc block. G. Urgese, "Analysis and Design of an Optimized HW Accellerator for Protein Alignment", Politecnico di Torino, Dept. Eletr., Torino, Italy, Sept. 2012                                                                                                                                                           | 20 |

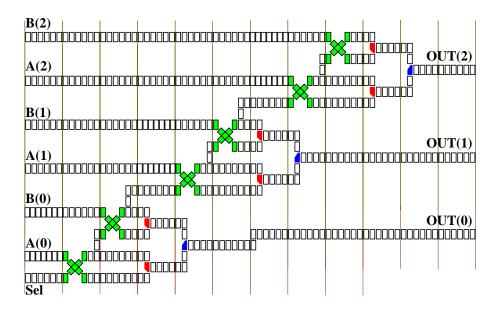

| 2.7  | NML Multiplexer implementation                                                                                                                                                                                                                                                                                                               | 21 |

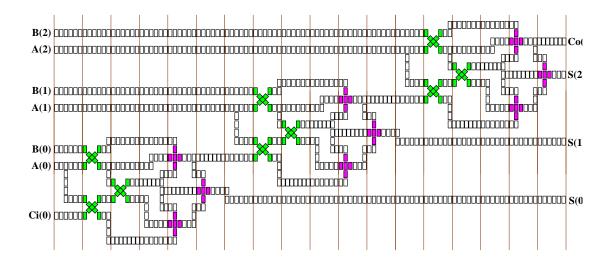

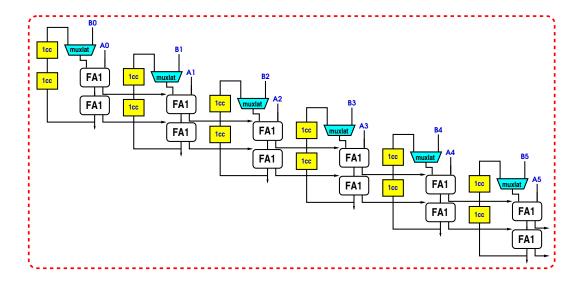

| 2.8  | NML Ripple Carry Adder implementation                                                                                                                                                                                                                                                                                                        | 22 |

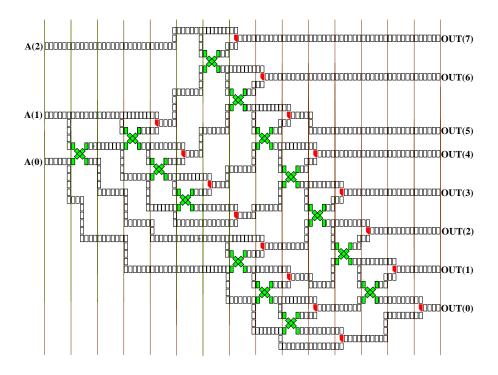

| 2.9  | NML 3-to-8 Decoder implementation                                                                                                                                                                                                                                                                                                            | 22 |

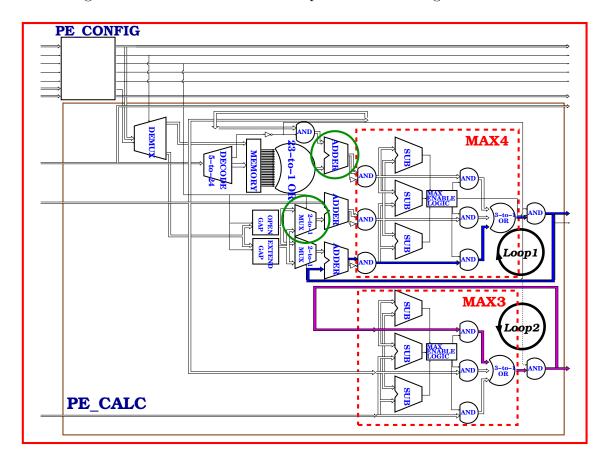

| 2.10 | NML processing element implementation. There are two loops present in the architecture, Loop1 and Loop2. The longer loop (Loop1) occupies 208x3 clock zones. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                       | 23 |

| 2.11 | Smith-Waterman algorithm architecture simulation results. Subject_ID represents the number of the AA sequences analyzed, and OUT_MAX is the corresponding maximum alignment score. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015 | 24 |

| 2.12 | Example of NML architecture performance reduction due to the presence of loops inside intrinsically pipelined circuits. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                         | 25 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.13 | Data Interleaving application example. Four operations are executed in parallel to maximize the circuit throughput. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                             | 26 |

| 2.14 | Simulation result of SW NML architecture with interleaving 3. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                                                                                   | 27 |

| 2.15 | PE Architecture redesign to reduce loops lengths. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                                                                                               | 28 |

| 2.16 | Simulation results comparison between redesigned PE architecture with folded loop and the original. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                                             | 29 |

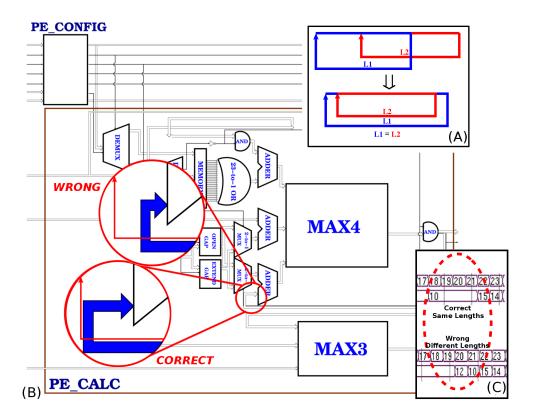

| 2.17 | PE signal synchronization with nested loops. A) Simplified schematic presentation of nested loops. B) Highlight of nested loops in Smith-Waterman processing element NML architecture. C) Simulation comparison with correct and wrong signal synchronizations. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015 | 30 |

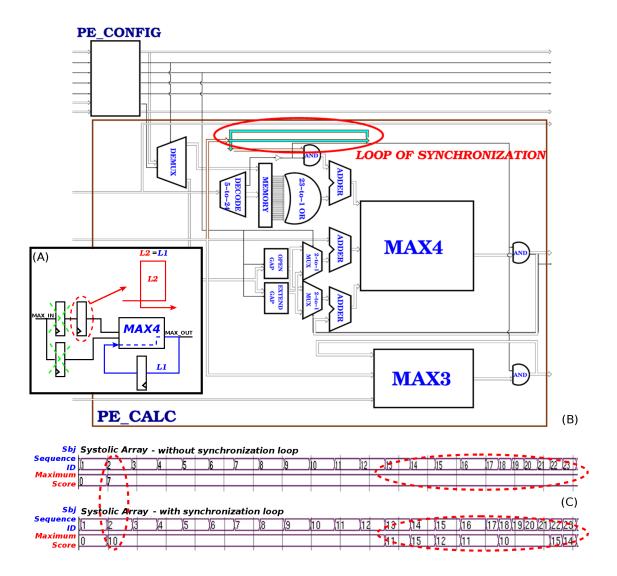

| 2.18 | PE signal synchronization with additional delay loops. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015                                                                                                                                                                                                          | 31 |

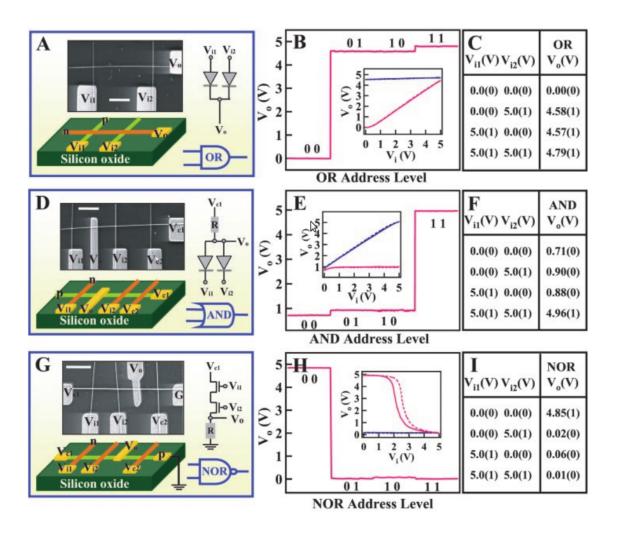

| 3.1 | Nanowire nano-logic gates. A) Schematics of logic OR gate constructed from a 2 by 1 crossed NW p-n junction. B) OR gate input and output voltage levels. C) The experimental truth table for the OR gate. D) Schematic of logic AND gate constructed from a 1 by 3 crossed NW junction array. E) AND gate input and output voltage levels. F) The experimental truth table for the AND gate. G) Schematic of logic NOR gate constructed from a 1 by 3 crossed NW junction array. H) NOR gate input and output voltage levels. I) The experimental truth table for the NOR gate. Y. Huang et al. "Logic Gates and Computation from Assembled Nanowire Building Blocks", Science, vol. 294, Nov. 2001. | 35 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

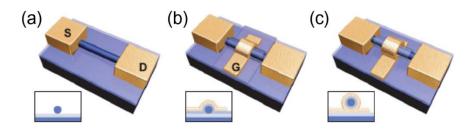

| 3.2 | Schematic of nwFETs with A) back gate, B) semicylindrical top gate, and C) cylindrical gate-all-around configurations. W. Lu et al. "Nanowire Transistor Performance Limits and Applications", IEEE Transactions on Electron Devices, vol. 55, Nov. 2008                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36 |

| 3.3 | Crossed Nanowire Field Effect Transistors. A) Basic device structure with self-aligned n+ drain, gate, source and underlap. B) NiSi gate xnwFET. C) Omega-gated xnwFET. P. Narayanan et al. "Nanoscale Application Specific Integrated Circuits", IEEE/ACM International Symposium on Nanoscale Architectures, June 2011                                                                                                                                                                                                                                                                                                                                                                             | 36 |

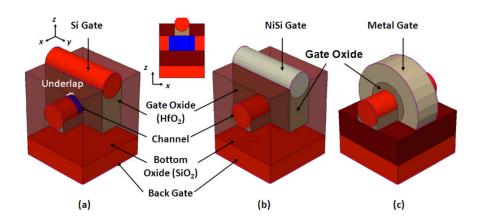

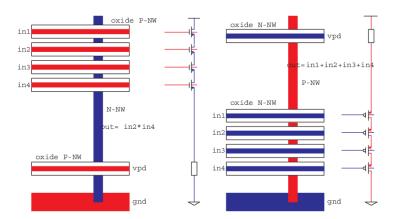

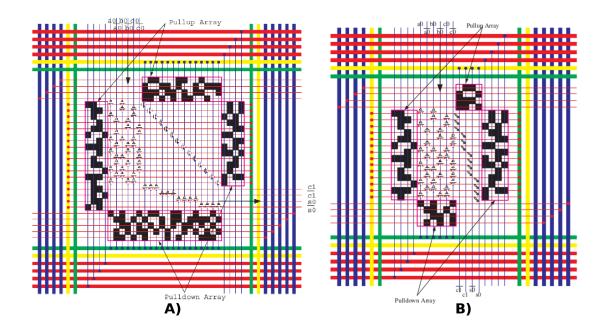

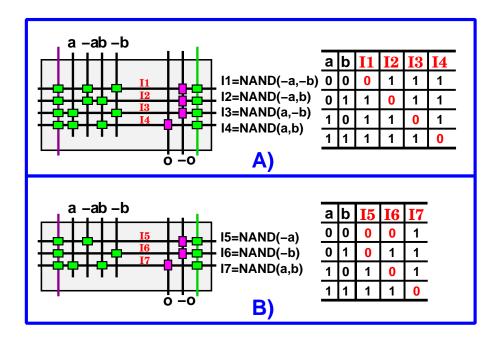

| 3.4 | 4-input OR and AND logic implemented with xnwFETs. T. Wang et al. "NASICs: A Nanoscale Fabric for Nanoscale Microprocessors", Electrical and Computer Engineering Department, University of Massachusetts Amherst, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37 |

| 3.5 | 1-bit Full-Adder with 2-D nanoarray structure. T. Wang et al. "Opportunities and challenges in application-tuned circuits and architectures based on nanodevices", First ACM International Conference On Computing Frontiers, pp. 503-511, april 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38 |

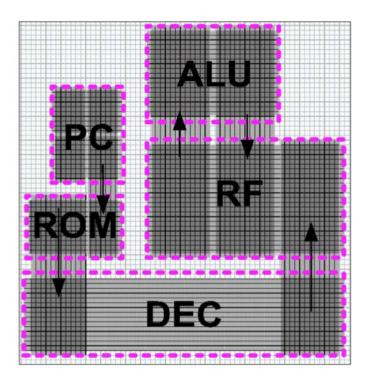

| 3.6 | Floorplan of the WISP-0 processor. WISP-0 is a five-stage pipelined streaming architecture in five nanotiles: PC, ROM, DEC, RF and ALU. T. Wang et al. "Heterogeneous Two-Level Logic and Its Density and Fault Tolerance Implications in Nanoscale Fabrics", IEEE Transactions on Nanotechnology, vol. 8, n. 1, Jan. 2009                                                                                                                                                                                                                                                                                                                                                                           | 39 |

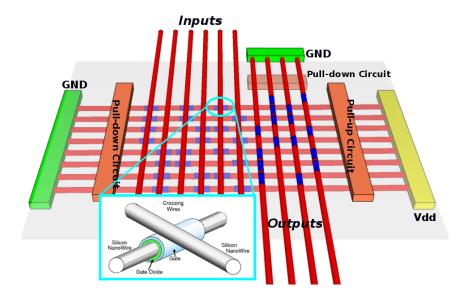

| 3.7 | Nanotile structure built with silicon nanowires and nanoFETs. P. Narayanan et al. "Nanoscale Application Specific Integrated Circuits", IEEE/ACM International Symposium on Nanoscale Architectures, June 2011. (Inserted) M. Graziano et al. "A Hardware Viewpoint on Biosequence Analysis: What's Next?", ACM Journal on Emerging Technologies in Computing Systems, Nov. 2013                                                                                                                                                                                                                                                                                                                     | 40 |

| 3.8  | Schematic representations of 1-bit Full Adder with A) mixed types of |    |

|------|----------------------------------------------------------------------|----|

|      | nanoFETs, and B) single n-type nanoFETs. T. Wang et al. "NA-         |    |

|      | SICs: A Nanoscale Fabric for Nanoscale Microprocessors", Electrical  |    |

|      | and Computer Engineering Department, University of Massachusetts     |    |

|      | Amherst, USA                                                         | 40 |

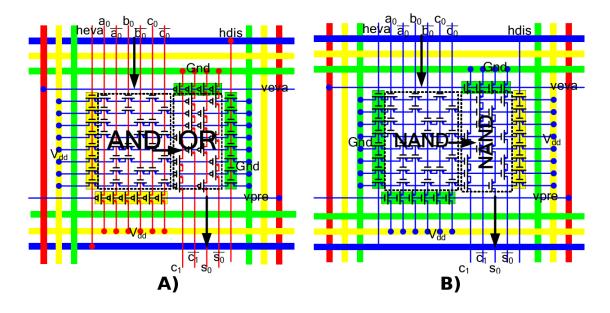

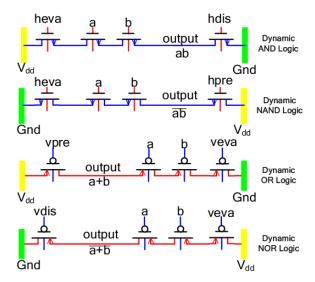

| 3.9  | Dynamic circuits implementing AND, NAND, OR, and NOR logic           |    |

|      | functions on NWs. T. Wang et al. "Heterogeneous Two-Level Logic      |    |

|      | and Its Density and Fault Tolerance Implications in Nanoscale Fab-   |    |

|      | rics", IEEE Transactions on Nanotechnology, vol. 8, n. 1, Jan. 2009. | 41 |

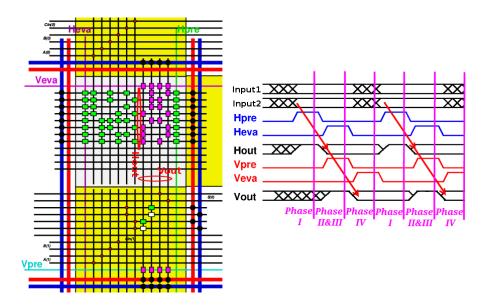

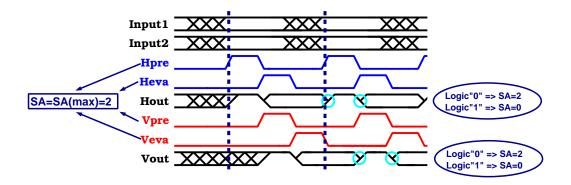

| 3.10 | Nanotile clock mechanism with dynamic logic. The rectangular green   |    |

|      | boxes on nanowire cross sections are n-type nanoFETs while the white |    |

|      | ones are p-type nanoFETs                                             | 42 |

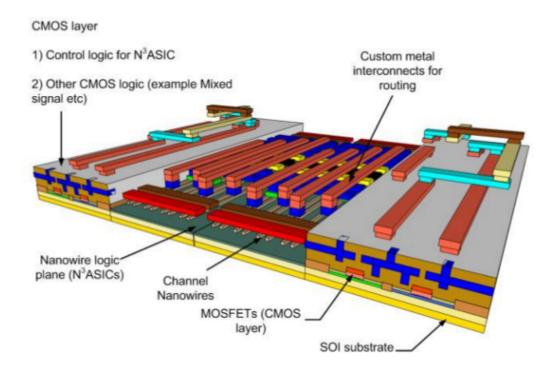

| 3.11 | Nanotile behavior modeling in VHDL                                   | 43 |

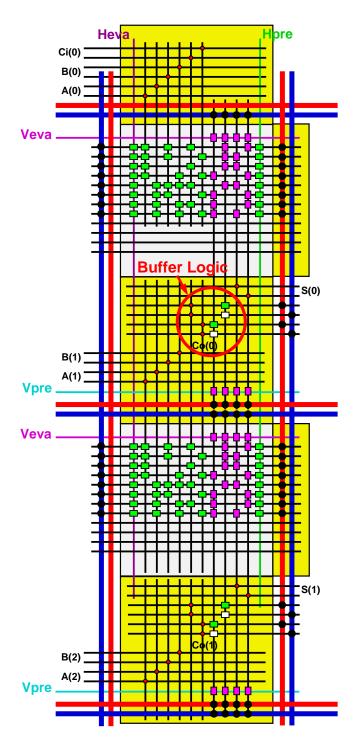

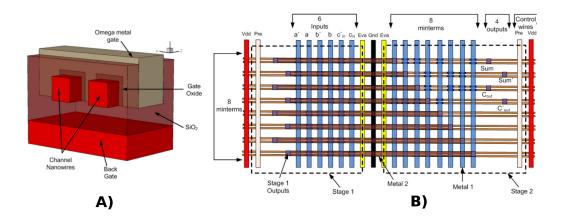

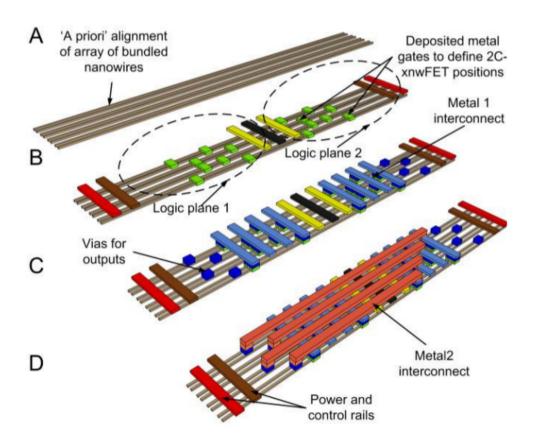

| 3.12 | N3ASIC Nanotile structure. A) 3D structure of Omega metal gate       |    |

|      | NanoFET in N3ASIC. B) 1-bit Full Adder N3ASIC. P. Panchapake-        |    |

|      | shan et al. "3-D Integration Requirements for Hybrid Nanoscale-      |    |

|      | CMOS Fabrics", IEEE International Conference on Nanotechnology,      |    |

|      | Aug. 2011                                                            | 44 |

| 3.13 | N3ASIC Nanotile structure. P. Panchapakeshan et al. "3-D Inte-       |    |

|      | gration Requirements for Hybrid Nanoscale-CMOS Fabrics", IEEE        |    |

|      | International Conference on Nanotechnology, Aug. 2011                | 45 |

| 3.14 | Hybric Nano-CMOS 3D integrated fabric structure. P. Panchapake-      |    |

|      | shan et al. "N3ASICs: Designing Nanofabrics with Fine-Grained        |    |

|      | CMOS Integration", IEEE/ACM International Symposium on Nanoscale     |    |

|      | Architectures, 2011                                                  | 46 |

|      | Nanotile behavior modeling in VHDL                                   | 47 |

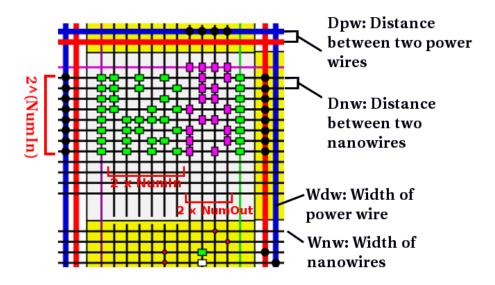

| 4.1  | Nanotile area evaluation parameters                                  | 50 |

| 4.2  | Nanotile switching activity                                          | 53 |

| 4.3  | 2-input AND gate nanotile switching activity analysis. A) Without    |    |

|      | Karnaugh map simplification. B) With Karnaugh map simplification.    | 54 |

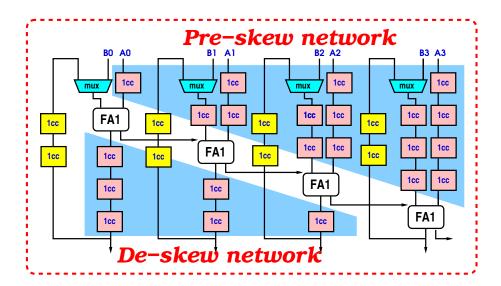

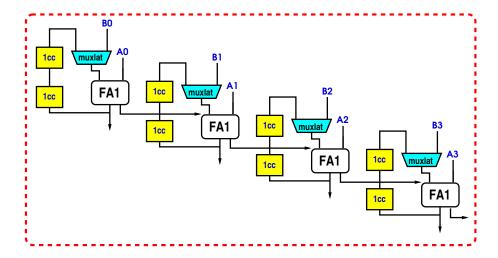

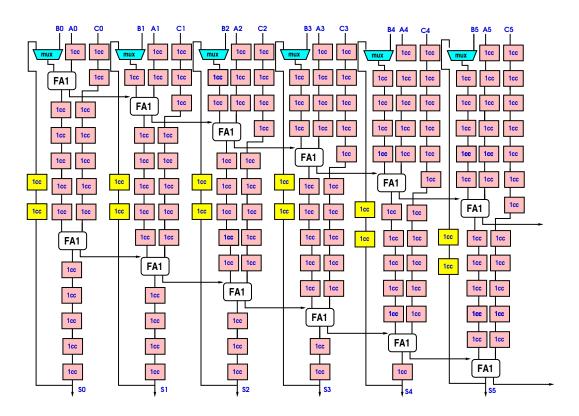

| 4.4  | 8-bit Ripple Carry Adder NASIC block diagram with pre-skew and       |    |

|      | de-skew networks                                                     | 56 |

| 4.5  | NASIC Array Multiplier. A) Circuit schematic of 5-bit Array Multi-   |    |

|      | plier. B) Block diagram of 5-bit Array Multiplier. C)Example nan-    |    |

|      | otile of 1-bit Full Adder with two AND gates at input                | 58 |

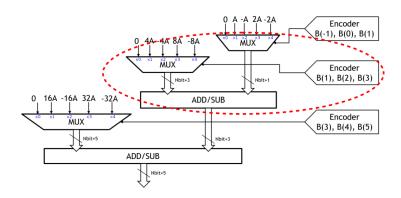

| 4.6  | Booth Multiplier block diagram                                       | 60 |

| 4.7  | Block diagram of NASIC implementation on partial Booth Multiplier.   | 60 |

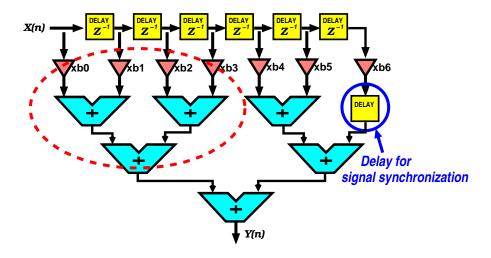

| 4.8  | FIR Block diagram                                                    | 62 |

| 4.9  | Detailed NASIC implementation of partial FIR architecture in 4 bits. | 63 |

| 4.10 | 3-bit Ripple Carry Adder structure in NASIC circuit layout           | 64 |

| 4.11 | NASIC block diagram of 4-bit accumulator structure with pre-skew                                   |   |

|------|----------------------------------------------------------------------------------------------------|---|

|      | and de-skew networks. Feedback latency equals 2 clock cycles and                                   |   |

|      | total loop length is 5 clock cycles                                                                | ) |

| 4.12 | Block diagram of the optimized structure of 4-bit accumulator. The                                 |   |

|      | pre-skew and de-skew networks are eliminated                                                       | ; |

| 4.13 | Detailed block diagram of traditional 6-bit accumulator with 2 RCAs                                |   |

|      | in cascade                                                                                         | • |

| 4.14 | Detailed block diagram of optimized 6-bit accumulator with 2 RCAs                                  |   |

|      | in cascade                                                                                         | , |

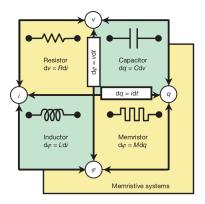

| A.1  |                                                                                                    |   |

|      | tor, inductor and memristor. D.B. Strukov et al. "The missing mem-                                 |   |

|      | ristor found", Nature, vol. 453, n. 1, 2008                                                        | ) |

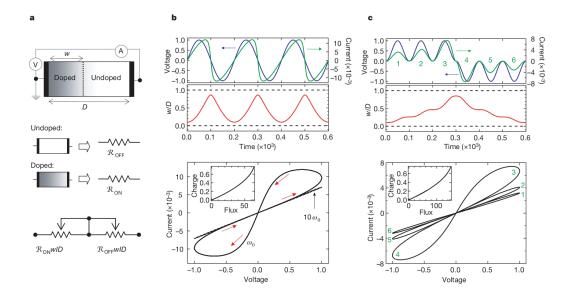

| A.2  |                                                                                                    |   |

|      | with a simplified equivalent circuit. b) c) The applied voltage (blue)                             |   |

|      | and resulting current (green) as a function of time $t$ for a typical                              |   |

|      | memristor. The resistance ratio are in $ROFF/RON = 380$ b), and                                    |   |

|      | ROFF/RON = 160 in c). The insets in the i-v plots in b) and c)                                     |   |

|      | show that for these examples the charge is a single-valued function                                |   |

|      | of the flux, as it must be in a memristor. D.B. Strukov et al. "The                                |   |

|      | missing memristor found", Nature, vol. 453, n. 1, 2008 71                                          |   |

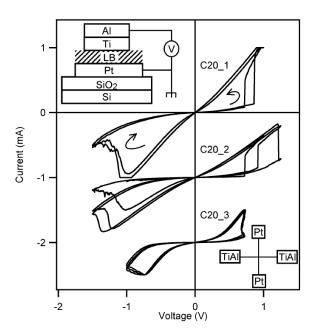

| A.3  |                                                                                                    |   |

|      | different $C_{20}$ molecular monolayer devices. D. R. Stewart et al. "Molecule-                    |   |

|      | Independent Electrical Switching in Pt/Organic Monolayer/Ti De-                                    |   |

|      | vices", Nano Letters, vol. 4, n. 1, 2004                                                           | ) |

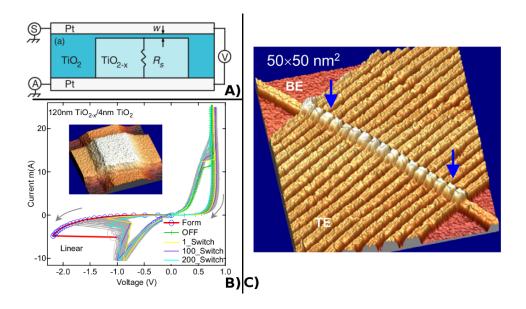

| A.4  |                                                                                                    |   |

|      | with example switching i-v curve. B)The data from a Pt/120nm                                       | , |

|      | $TiO_{2-x}/4$ nm $TiO_2/Pt$ device, showing 200 consecutive switching loops                        |   |

|      | after the forming step. C) AFM image of 1x17 nanojunctions. The                                    |   |

|      | cross-section profile shows $50 \text{ nm}$ half pitch and $13 \text{ nm}$ height nanowires. $A$ ) |   |

|      | M. D. Pickett et al. "Switching dynamics in titanium dioxide mem-                                  |   |

|      | ristive devices", Journal of Applied Physics, 2009. B) C) J. J. Yang                               |   |

|      | et al. "The mechanism of electroforming of metal oxide memristive                                  |   |

|      | switches", Nanotechnology, May 2009                                                                | ; |

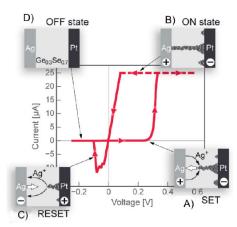

| A.5  | Typical i-v characteristic of a Ag/Ag-Ge-Se/Pt electrochemical met-                                |   |

|      | alization cell. Starting from OFF state D), under the external electri-                            |   |

|      | cal field rising, metallic filaments are grown gradually as A) to reach                            |   |

|      | ON state B) creating galvanic metallic contacts. With voltage drop-                                |   |

|      | ping C), the metal filaments dissolute, and resets the cell. R. Waser et                           |   |

|      | al. "Redox-Based Resistive Switching Memories - Nanoionic Mech-                                    |   |

|      | anisms, Prospects, and Challenges", Advanced Materials, vol. 21,                                   |   |

|      | issue 25-26. July. 2009                                                                            | = |

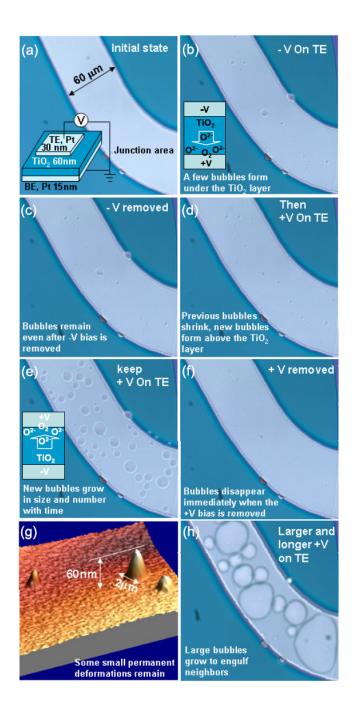

| A.6 | Gas bubble behavior under electric field in a large 60um device for     |    |

|-----|-------------------------------------------------------------------------|----|

|     | observation purpose. a) Junction initial state. b) c) Junction negative |    |

|     | biased. d)-h) Junction positive biased. g) Atomic force micrograph      |    |

|     | of eruption features remaining after the bias voltage was removed.      |    |

|     | J. J. Yang et al. "The mechanism of electroforming of metal oxide       |    |

|     | memristive switches", Nanotechnology, May 2009                          | 75 |

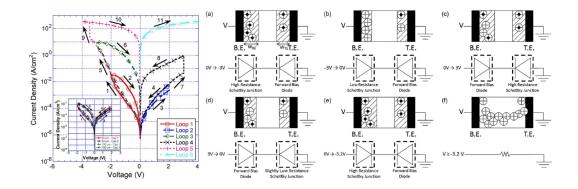

| A.7 | Electron trapping-detrapping in $V_o$ -induced modification of Schot-   |    |

|     | tky contact resistance model. B. Long et al. "Understanding the         |    |

|     | Charge Transport Mechanism in VRS and BRS States of Transition          |    |

|     | Metal Oxide Nanoelectronic Memristor Devices", IEEE Transactions        |    |

|     | on Electron Devices, vol. 58, n. 11, Nov. 2011                          | 76 |

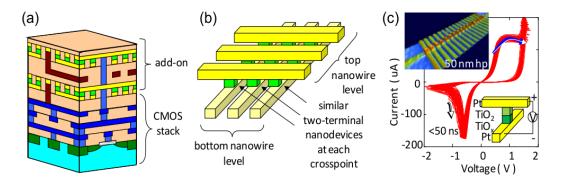

| A.8 | Basic idea of 3D Hybrid CMOS/Memristor circuits. A) Stackup of          |    |

|     | CMOS subsystem with layers of memristor crossbar circuits. B) Mem-      |    |

|     | ristor crossbar topology. C) micrograph of array of metal oxide mem-    |    |

|     | ristive devices, and typical switching I-V curves. D. B. Strukov, "3D   |    |

|     | Hybrid CMOS/Memristor Circuits: Basic Principle and Prospective         |    |

|     | Applications", COMMAD, Dec. 2012.                                       | 77 |

# Chapter 1

# Introduction to NanoMagnet Logic

NanoMagnet Logic (NML) is a new technology based on the field coupled principle. Devices are built using identical cells. Information propagates through magnetic field coupling among neighbor nanomagnets. NML main interest lies in its magnetic nature, that leads to circuits with low dynamic power consumption and now leakage, circuits that can act both as logic and memory devices.

# 1.1 Technology Background Quantum-dot Cellular Automata

NML Technology is one of the implementation of Quantum dot Cellular Automata (QCA). QCA technology has received in recent years a lot of attention thanks to its nanoscale dimensions and a new way of computation and information elaboration.

## 1.1.1 QCA Logic

Basic QCA cells are quantum wells which confine free electrons in a square shaped nanostructure containing four quantum dots that can hold a single electron each and sit at four corners [1]. Electrons are able to tunnel between the dots but are not able to escape the cell. Only two stable electric charge states, representing logic "0" and "1", are possible by Coulombic repulsion as shown in Figure 1.1 A).

Due to the electrostatic interaction among neighbor cells, QCA cells will reach a stable polarization state depending on the state of neighbor cells. This phenomenon can be seen as a signal propagation (Figure 1.1 B)), which can be employed to construct digital systems. To build logic circuits, a set of logic gates (Figure 1.2), such as Inverters, Majority Voters, and Crosswire blocks must be developed. As

Figure 1.1. Basic 4-dot QCA cells and logic states.

shown in Figure 1.2B), a majority voter computes the output according to the states of three input cells. It can implement AND/OR gates by forcing one input to be "0" or "1" [2]. In a crosswire block, QCA cells rotated by 45 degrees Figure 1.2 C), allows to cross propagate two signals on the same flat plain without influencing each other [3].

Figure 1.2. Basic QCA logic gates. A)Inverter B)Majority Voter C)Crosswire

#### 1.1.2 QCA Clock Mechanism

By introducing the concept of "Clock" mechanism and modifying the 4-dot QCA structure into 6-dot (Figure 1.3), it is possible to set the cells in a metatstable state ("NULL") by applying an external electric field. When the electric field is removed, the cell reach one of the two stable states according to its neighbors, propagating therefore the information through the circuit.

Figure 1.3. Basic 6-dot QCA cells with 3 states.

As depicted in Figure 1.4, a long QCA wire can be divided into "clock zones", each of which is driven by separated clock signals. These clock signals are derived from the same signal with 4 different phases shifting. QCA cells can be therefore in one of four possible states (HOLD, RELEASE, RELAX, SWITCH).

When a clock zone is in HOLD phase, the potential barrier of the QCA cells are increased by the external clock field (V=Vmax), making them insensible to neighbor cells and impossible to switch to the other state. Then the clock zone enters into RELEASE phase, with the clock signal decreasing to -Vmax gradually. Cells reach "NULL" intermediate state. In the next RELAX phase, by stablizing the field V=-Vmax, the previous logic states of all the cells are erased. With the clock signal rising again up to +Vmax, there is the transition to the new logic states according to the new input, which is the so-called SWITCH phase.

An example of information propagation is depicted in Figure 1.4. It can be noticed that in time step1, with clock zone 1 in HOLD, clock zone 2 switches according to the cells in clock zone 1. At the same time, clock zone 3 is totally relaxed and can not influence the switching in clock zone 2. Therefore, after a complete clock cycle of 4 phases, the input signal "0" is propagated to the end of the wire.

## 1.1.3 QCA Implementation

The theoretical principle of the QCA can be implemented in different ways. There are four physical implementation of QCA, which are briefly discussed below.

• Metal QCA. As shown in Figure 1.5(A), the metal QCA are made with isles of aluminum, used to represent the dots, on a substrate of silicon dioxide (SiO2). The dots are connected to each other by tunnel-junctions which allow

Figure 1.4. QCA clock mechanism with 4-phase clock signal.

the electrons to be exchanged among neighbor dots. This technology has been the first implementation, while its main disadvantage is that it works only at a temperature near the absolute zero [7].

- Semiconductor QCA. Complex heterostructures of Si-Ge or GaAs are used to create quantum dots that are able to trap electrons [7] as shown in Figure 1.5(B). The main limitations of this QCA type are the necessity to work at near absolute zero temperature and the huge impact of fabrication defects.

- Molecular QCA. It employs single molecules with complex structures as basic cell. Each molecule contains multiple oxide-reduction centers as shown in Figure 1.5(C). Electrons can react with every center inside the molecule, changing the spatial distribution of the electric charge, and thus the logic value associated to it [7]. This is one of the most promising implementation technologies, since the molecules are very small (a few nanometers), allowing

Figure 1.5. A) Metal QCA structure B) Semiconductor QCA structure C) Molecular QCA structure. A) R. K. Kummamuru et al. "Operation of a Quantum-Dot Cellular Automata (QCA) Shift Register and Analysis of Errors", IEEE Transactions on Eletron Devices, vol. 50, n. 9, Sept. 2003. B) A. Khitun et al. "Multi-functional edge driven nano-scale cellular automata based on semiconductor tunneling nano-structure with a self assembled quantum dot layer", Superlattices and Microstructures, vol. 37, pp. 55-76, 2005. C)C.S. Lent et al. "Clocked Molecular Quantum-Dot Cellular Automata", IEEE Transactions on Electron Device, vol. 50, no. 9, september 2003.

to reach a very high device density, and it permits an operating frequency of some THz. Moreover, with respect to Metal QCA, it can work under room temperature. The problem is that until now, with the up-to-date technology, Molecular QCA fabricated is challenging because it requires the ability of manipulating single molecule [3].

• NanoMagnet Logic. The basic cell of NML is a single domain nanomagnet, and is one of the most promising implementation of QCA. With respect to Molecular QCA, it has a bigger dimension, and can only reach a basic frequency of some hundred of MHz theoretically. However, it is possible to implement it with current technology, allowing to experiment and study the QCA principle so that most of the achievements can be adapted in a near future to molecular QCA, as soon as this solution becomes feasible [7].

# 1.2 NanoMagnet Logic (NML)

NanoMagnet Logic, also known as Magnetic QCA, is one of the promissing technology based on Quantum Cellular Automata (QCA) principle. The advantage of this technology resides in its magnetic nature which leads to expected low power consumption.

#### 1.2.1 NML Basic Cell

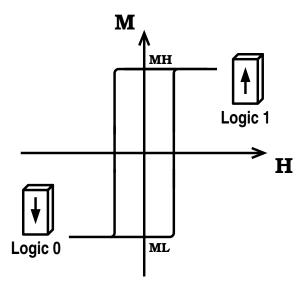

The basic cell of NML is a retangular shaped single domain nanomagnet. Due to its shape, only two stable magnetization states are possible, which can be used to rappresent logic states "0" and "1" (Figure 1.6).

Figure 1.6. NML basic cells with stable magnetizations rappresenting logic states

By placing the nanomagnets in cascade horizontally or vertically, signals can be propagated due to magnetic coupling among neighbor magnets as shown in Figure 1.7.

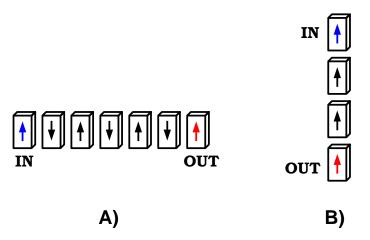

Figure 1.7. NML wire configurations. A) Horizontal wire. B) Vertical wire.

## 1.2.2 NML Logic Gates

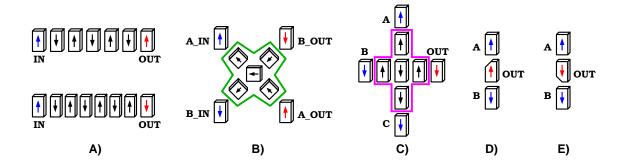

Several basic logic gates can be built with NML cells, such as inverter, crosswire, and majority voter.

#### • Inverter

As can be noticed, a horizontal wire is constructed by placing an odd number of nanomagnets between input and output. Therefore, by placing an even number of nanomagnets within the same total length, the signal at the output is inverted as shown in Figure 1.8 A).

#### • Crosswire

A crosswire block is a functional block which allows to the cross two signals on the same plane without interferences. This characteristic can be achieved by organizing the square shaped nanomagnets according to Figure 1.8 B).

#### • Majority Voter

The output value of a majority voter (Figure 1.8 C)) is equal to the majority of the inputs.

#### • AND/OR Gate

By fixing an input signal to "0" or "1", a majority voter can be converted to an AND/OR gate. Another possibility is to exploit the shape dependent switching behavior. Cutting a nanomagnet leads to an asymmetric shape, in order to obtain a preferential magnetization direction for the output signal (Figure 1.8 D)).

Figure 1.8. NML basic logic gates. A) Inverter. B) Crosswire. C) Majority Voter. D) OR gate. E) AND gate.

#### 1.2.3 Clock Mechanism

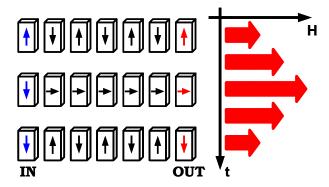

In order to lower the energy barrier during the switching between two stable states, a magnetic field [8] can be exploited to force the nanomagnets into a transient metastable state as shown in Figure 1.9. When the field is removed, the nanomagnets re-enter into one of the stable states depending on the value of neighbor magnets. This mechanism is called clock.

The magnetic field can be generated by a current flowing through a wire placed under the magnets plane (Figure 1.10 A)).

Figure 1.9. NML clock mechanism with magnetic field forcing nanomagnets into an intermediate unstable state.

As shown in [9] a current of 545 mA on a 1 um width wire is required to successfully switch magnets in the RESET state. This is a very high value of current that leads to a very high power consumption, wasting the advantage related to the tiny power dissipation due to magnet switching. To reduce power consumption other mechanisms were proposed. For example in the STT-current approach [21] magneto-tunnel junctions (MTJ) are used as basic element. MTJ can be reset by a current flowing through them leading to a power consumption of just 1.6fJ for each magnet (Figure 1.10 B)). Alternatively, in [10] an innovative clock system is proposed based on the use of an electric field instead of a magnetic field. With this clock solution magnets are deposited on a piezoelectric layer (Figure 1.10 C)). When an electric field is applied, the strain of the piezoelectric layer induces a mechanical stress on the magnets forcing them in the RESET state. With this clock solutions an energy of just 2 pJ is required to switch magnets [10] allowing to build true low power circuits.

## 1.2.4 Multiphase Clock System

To reduce the influence of thermal noise during magnet switch, a NML circuit must be divided into "clock zones". A clock zone is a small circuit area composed by a

Figure 1.10. NML clock implementation. A) Magnetic field. B) STT-current. C) Magnetoelastic. J. Wang et al. "Biosequences analysis on NanoMagnet Logic", International Conference on IC Design and Technology (ICICDT), May 2013.

limited number of magnets. A 3-phase overlapped clock signal is applied in order to propagate information [11].

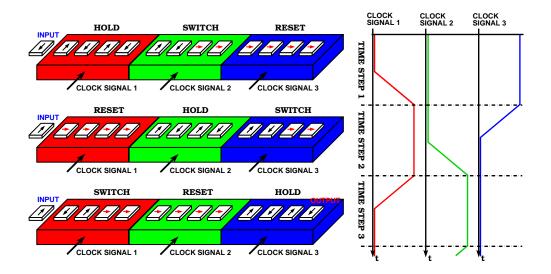

Taking as an example a NML wire composed by 3 clock zones (Figure 1.11), magnets can be in three different states ("HOLD", "RESET" and "SWITCH").

- Time Step 1: the clock zone 1 is in "HOLD" state, all the magnets in the zone are in a stable state. The nanomagnets in clock zone 2 switch ("SWITCH" state) in anti-ferromagnetic order one by one, as a domino effect, propagating the signal from left to right. In the meantime, clock zone 3 is in the "RESET" state, so it has no influence on the switching magnets.

- Time Step 2: nanomagnets in clock zone 1 are in the "RESET" state, clock zone 2 has finished the switching process and has entered into "HOLD" state. By removing the clock signal in clock zone 3, the magnets start to switch.

- Time Step 3: clock zone 1 starts switching according to the new input, and clock zone 2 is now reset. At this point, with clock zone 3 being in "HOLD" state, the signal propagation reaches the end of the wire.

A NML wire is equivalent to a CMOS shift register, and the multiphase clock system leads to an intrinsic pipelined behavior [12]. Each group of 3 consecutive clock zones has exactly a delay of one clock cycle.

In order to reduce the energy necessary for the magnet to switch, the clock signal should have a rise time of at least 8 to 10 ns for the concept of adiabatic switching. When the number of magnets is higher than five, a long fall time is necessary to assure that magnets switching occurs with a reduced probability of error [13]. The maximum allowed clock frequency is around 1 GHz, while the more realistic value turns to be between 10 and 100 MHz considering all constraints due to thermal noise and clock zone layout [14].

Figure 1.11. NML 3-phase clock system.

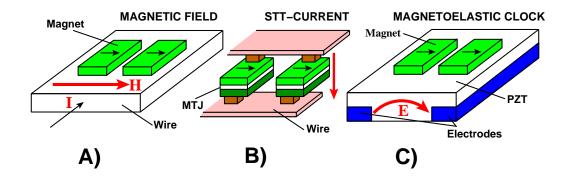

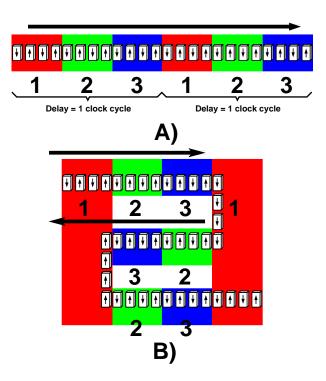

## 1.2.5 Clock Zone Layout

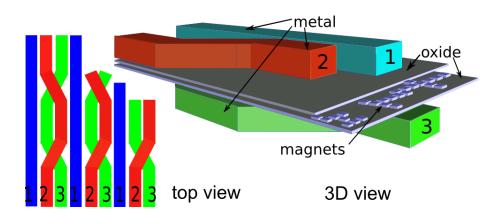

With the 3-phase clock system described previously, NanoMagnet Logic can only propagate in one direction. The delay of a signal which passes through 3 clock zones is equal to one clock cycle. The circuits latency is equivalent to one third of the total number of clock zones. This is the so-called "Layout = Timing" problem (Figure 1.12 A)). Circuits delay depend on the layout of circuits. Careful layout design is required to have a perfect signal synchronization. This traditional layout is not feasible in design of complex NML circuit. As a consequence, a "Snake-like" clock zone layout is proposed to allow feedback signal propagation (Figure 1.12 B)). It helps reducing the "Layout=Timing" problem. Figure 1.13 represents a 3D view of the snake clock wires used to generate the clock signals.

Figure 1.12. 3-phase clock zone layout. A) Traditional layout. B) Snake-like layout.

Figure 1.13. Snake-like layout physical view. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015.

## 1.2.6 VHDL Modeling

#### VHDL behavioral model

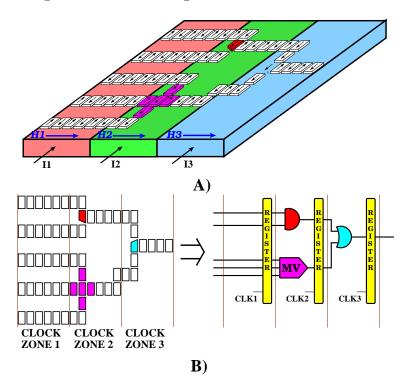

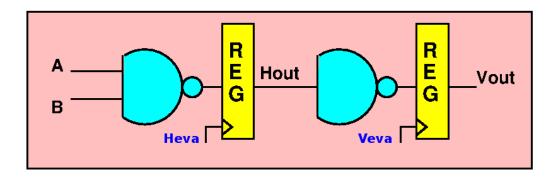

Independent of the clock mechanism chosen, as described before, the intrinsic pipelined behavior of circuits can be modeled by combinational logic gates with registers controlled by clock signals as shown in Figure 1.14.

Figure 1.14. NML circuit VHDL modeling. J. Wang et al. "Biosequences analysis on NanoMagnet Logic", International Conference on IC Design and Technology (ICICDT), May 2013.

Registers simulate signals propagation delay, while ideal logic gates model the circuits behavior. An RTL model of NML circuits can therefore be easily described using VHDL language. In the following, the VHDL code describing the circuit of Figure 1.14 is reported.

```

-- Example NML circuit with VHDL modeling

-- It occupies 3 clock zones (1 clock cycle)

library ieee;

use ieee.std_logic_1164.all;

entity ExampleNML is

```

```

port (

clk

in std_logic_vector (3 downto 1);

ANDIn1 : ANDIn2 :

in std_logic;

in std_logic;

MVIn1

:

in std_logic;

MVIn2

in std_logic;

MVIn3 : Output :

in std_logic;

out std_logic);

end ExampleNML;

architecture STRUCTURAL of ExampleNML is

: std_logic_vector(4 downto 0);

signal S1

signal S1_reg0 : std_logic_vector(4 downto 0);

: std_logic_vector(1 downto 0);

signal S2

signal S2_reg0

: std_logic_vector(1 downto 0);

signal S3

: std_logic_vector(0 downto 0);

signal S3_reg0 : std_logic_vector(0 downto 0);

component MV is

port(

A_in: in std_logic;

B_in: in std_logic;

C_in: in std_logic;

out_MV: out std_logic);

end component;

component gate_AND is

port(

A_in: in std_logic;

B_in: in std_logic;

out_AND: out std_logic);

end component;

component gate_OR is

port(

A_in: in std_logic;

B_in: in std_logic;

out_OR: out std_logic);

end component;

component register_generic is

generic ( NBIT : integer );

port(

CLK:

in std_logic;

D:

in std_logic_vector (NBIT-1 downto 0);

out std_logic_vector (NBIT-1 downto 0));

Q:

end component;

begin

-- enter into Stage1

S1(0) <= ANDIn1;

S1(1) <= ANDIn2;

S1(2) <= MVIn1;

S1(3) <= MVIn2;

S1(4) <= MVIn3;

-- passing the signals through REG1

REG1:

register_generic

generic map (5)

```

```

port map (clk(1), S1, S1_reg0);

--endREG

-- enter into Stage2

and_stage2_0: gate_AND port map (S1_reg0(0), S1_reg0(1), S2(0));

mv_stage2_0: MV port map (S1_reg0(2), S1_reg0(3), S1_reg0(4), S2(1));

-- passing the signals through REG2

REG2: register_generic

generic map (2)

port map (clk(2), S2, S2_reg0);

--endREG

-- enter into Stage3

or_stage3_0: gate_OR port map (S2_reg0(0), S2_reg0(1), S3(0));

-- passing the signals through REG3

REG3: register_generic

generic map (1)

port map (clk(3), S3, S3_reg0);

--endREG

-- assign the output

S <= S3_reg0(0);

end STRUCTURAL;

```

#### Area and Power model

The VHDL code embeds an area estimator. For each logic block, the total number of magnets is calculated summing the number of magnets of each logic gate. A multiplicative factor takes into account the interconnections overhead. Area is therefore calculated from the total number of magnets. Details are reported in [15].

Regarding Power consumption, as stated in [11], there are two main power losses in NML circuits: the power loss to force magnets in the RESET state and the loss in the clock generation. The first component is calculated by multiplying the switching energy of each magnet for the total number of magnets and for the frequency. The second component is calculated estimating the clock wires length from the total circuits area. Knowing the wire length and by defining some parameters as shown in Figure 1.15, a series of equations are employed to calculate wires section and resistance.

$$\begin{cases} Swire = (Width\_zone - Width\_sep) * Wire\_thick \\ Rwire\_i = Resistivity * \frac{Lwire\_eff\_i}{Swire} \end{cases}$$

$$(1.1)$$

Knowing the wires resistance, it is possible to estimate clock power consumption by estimating joule losses through the wires.

| Parameter name         | Default value | Explanation                                                                      |

|------------------------|---------------|----------------------------------------------------------------------------------|

| h_zone                 | 6.0e-7        | Height of clock zone (meters)                                                    |

| h_zone_sep             | 2.0           | Vertical separation between zones, where no magnets are allowed.                 |

| Width_zone             | 7.0e-7        | Width of a clock zone (meters)                                                   |

| Width_zone_mag         | 10.0          | Width of a clock zone in terms of magnets                                        |

| Wire_thick             | 6.0e-7        | Clock wire thickness (meters)                                                    |

| Wire_sep               | 2.0e-8        | Space between clock wires (meters)                                               |

| Wasted_Space           | 2.0           | Relative area used by components (magnets + separation spaces)                   |

| h                      | 1.0e-7        | Height of a nanomagnet (meters)                                                  |

| W                      | 5.0e-8        | Width of a nanomagnet (meters)                                                   |

| vert_space             | 2.0e-8        | Vertical separation space between magnets (meters)                               |

| oriz_space             | 2.0e-8        | Horizontal separation space between magnets (meters)                             |

| Wire_curves            | 1.1           | Overhead due to path wires for connecting different wires pieces                 |

| OV1_logic_gate_level   | 1.1           | Interconnect overhead inside a logic gate                                        |

| OV2_intermediate_level | 2.0           | Interc. overhead in small clusters of logic gates (full_adder, mux, registers)   |

| OV3_logic_block_level  | 1.5           | Interconn. overhead inside functional element (alu, counter,)                    |

| OV4_top_level          | 1.2           | Interconnect overhead due to logic blocks interconnection                        |

| I_max                  | 1.0e-3        | Maximum current flowing in clock wires (Ampere)                                  |

| clock_overlap          | 11.0          | Clock overlap percentage                                                         |

| Resistivity            | 1.78e-8       | Clock wire resistivity                                                           |

| T_clock                | 9.0e-9        | Clock period (seconds)                                                           |

| Energy_mag             | 30.0*KT       | Energy associated to a single magnet switch (with T=300 and K=boltzman constant) |

| N_mag_mv               | 5.0           | Number of magnets in a Majority Voter                                            |

| N_mag_inv              | 7.0           | Number of magnets in an Inverter                                                 |

Figure 1.15. Parameters and constants used in the NML power model. M. Vacca et al. "NanoMagnet Logic Microprocessor: Hierarchical Power Analysis", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, pp. 1410-1420, 2012.

$$Mag\_Power = \sum_{i=1,2,3} N_i * \frac{Energy\_mag}{T\_clock}$$

(1.2)

$$P\_joule\_total = \sum_{i=1,2,3} Rwire\_i * I\_max^2$$

(1.3)

Model details can be found in [15]. It is important to underline that the effectiveness of this model relies on the chosen values of overheads such as interconnections overhead and wire curves. Therefore, the constants were extrapolated starting from NML theory and low level simulations, taking into account all the physical and layout constraints actually known. This model is later on employed on the chosen complex NML circuit, the Smith-Waterman Systolic Array architecture in Section 2.4, allowing technological comparison with CMOS technology.

# Chapter 2

# NanoMagnet Logic Architecture Analysis

In order to link device and architectural analysis, a complex architecture is chosen as benchmark using multilevel models that consider the information gained from physical level finite element simulator. Basic structures and gates are validated through physical level simulator taking into account the limitations in magnets placement. This methodology that includes both fast behavioral simulation and area and power evaluation, allows us to gain significant information on NML performance.

# 2.1 Smith-Waterman Systolic Array Architecture Implementation

## 2.1.1 Biosequences Alignment Analysis

The chosen architecture as NML benchmark is the Smith-Waterman (SW) Systolic Array Architecture that is employed in biosequences alignment analysis. Biosequences alignment analysis is an important application iin the bioinformatics field. Being the essential constituents of animal and plant cells, proteins are manufactured by the instructions encoded in Deoxyribonucleic Acid (DNA). It contains the genetic information (genes) to guide the development of organs, to distinguish one species from other living beings and to pass to its descendants from generation to generation. By identifying the similarities between two biosequences, it is possible to reconstruct the evolutionary pathway that led to differentiation of species or to understand the genetic cause of a disease [16].

Each protein is a long chain of Amino Acids (AAs), which are normally represented by alphabetical characters as in Figure 2.1. Therefore, the biosequence

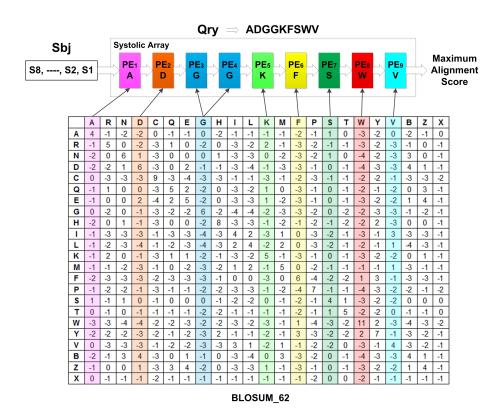

analysis is commonly done by comparing one sequence of AAs (**Query**) to other sequences taken from databases (**Subject**) that have been already developed. There are various sequence alignment methods found in literature. Among them there is **Smith-Waterman** algorithm which is mostly used for finding small regions of local similarity between distantly related biosequences [17].

| Letter | Amino acids   | Letter | Amino acids   | Letter | Amino acids   | Letter | Amino acids |

|--------|---------------|--------|---------------|--------|---------------|--------|-------------|

| A      | Alanine       | Q      | Glutamine     | L      | Leucine       | S      | Serine      |

| R      | Arginine      | Е      | Glutamic acid | K      | Lycine        | T      | Threonine   |

| N      | Asparagine    | G      | Glycine       | M      | Methionine    | W      | Tryptophan  |

| D      | Aspartic acid | Н      | Histidine     | F      | Phenylalanine | Y      | Tyrosine    |

| C      | Cysteine      | I      | Isoleucine    | P      | Proline       | V      | Valine      |

Figure 2.1. Amino Acide alphabetical character representation. L. R. Murphy et al. "Simplified Amino Acid Alphabets for Protein Fold Recognition and Implication for Folding", Protein Engineering, vol. 13, pp. 149-152, 2000.

#### 2.1.2 Smith-Waterman Systolic Array Architecture

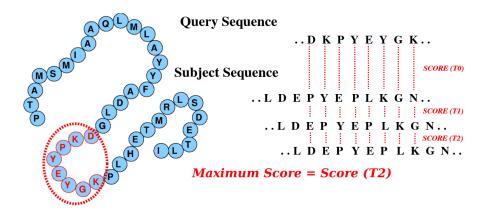

The Smith-Waterman algorithm evaluates the alignment between two AA sequences using a score mechanism that identify the percentage of similarity between them. As results, it outputs the best alignment identified by the maximum score as shown in Figure 2.2 [3].

Figure 2.2. Biosequence alignment analysis principle.

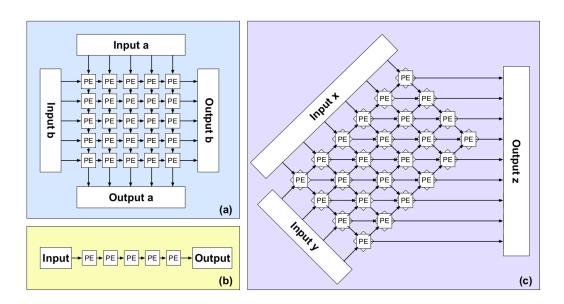

The algorithm can be parallelized and implemented using a Systolic Array (SA) to increase the performance and to accelerate the computation. As shown in Figure

2.4, Systolic Arrays are composed of Processing Elements (PEs) which can be organized in a matrix structure, or a linear structure or other parallel structures. The Processing Elements are identical processors that receive data from neighbor PEs and compute results that are passed to the next PEs.

Figure 2.3. Systolic Array Structures. A) Matrix Systolic Array. B) Linear Systolic Array. C) Special Systolic Array. G. Causapruno et al. "Protein Alignment Systolic Array Throughput Optimization", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 1, pp. 68-77, 2014.

As depicted in Figure 2.4, a linear systolic array is employed for the Smith-Waterman algorithm is employed. Each amino acid of the *Query sequence* is stored in one PE. Therefore, the more PEs there are in the systolic array, the longer Query sequences can be analyzed. The systolic array receives the *Subject sequence* AAs one by one at the input, passes them through the entire structure and generates the alignment score at the end. By sending multiple sequences in series, the circuit is able to compute the maximum alignment score at the systolic array output.

The detailed CMOS implementation ([18]) of a S-W Processing Element can be divided into two major blocks: Configuration block ( $PE\_Config$ ) and Computation block ( $PE\_Calc$ ) (Figure 2.5). The configuration block is responsible of generating control signals such as register read/write signals, while the computation block (Figure 2.6) contains the memory to store the alignment scores between the representing Query amino acid with all 23 amino acids. Using these values, the computational block is able to calculate the local alignment score. The datapath of the computational block is composed mostly by adders, used to design comparator blocks,

Figure 2.4. Smith-Waterman systolic array architecture with processing elements .G. Urgese, "Analysis and Design of an Optimized HW Accellerator for Protein Alignment", Master thesis, Politecnico di Torino, Dept. Eletr., Torino, Italy, Sept. 2012.

multiplexers and registers. A detailed description of the Smith-Waterman architecture and its hardware implementation can be found in [18].

Figure 2.5. Smith-Waterman systolic array architecture with processing elements.

Figure 2.6. Structure of PE\_Calc block. G. Urgese, "Analysis and Design of an Optimized HW Accellerator for Protein Alignment", Politecnico di Torino, Dept. Eletr., Torino, Italy, Sept. 2012.

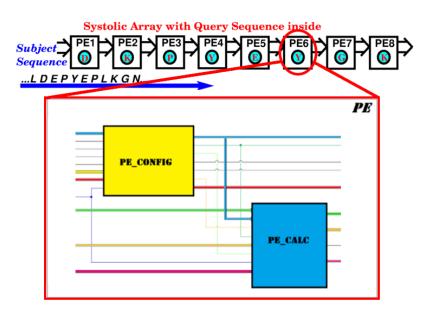

## 2.1.3 SW NML Implementation

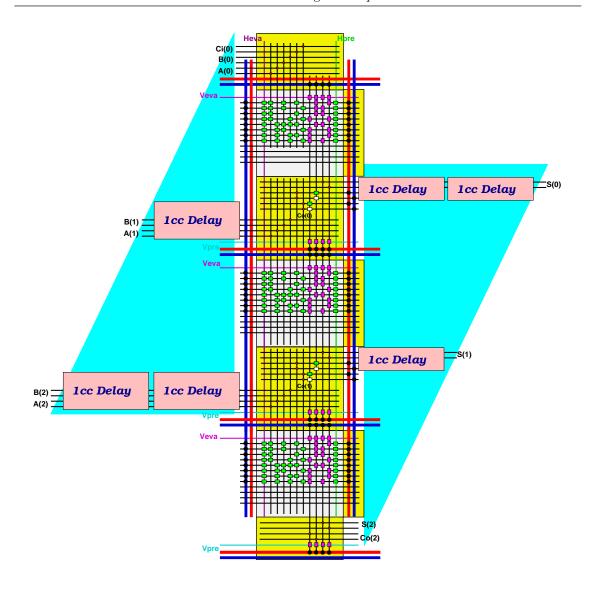

To design the Smith-Waterman in NML technology, the layout of each main component was created by hand. Figures 2.7, 2.8, and 2.9 reports for example the NML layout of a multiplexer, a ripple carry adder and a 3-to-8 decoder. Layouts are created considering constraints on magnets placement derived by physical fabrication of clock wires. The circuits are modeled with VHDL and assembled creating the whole processing element. Its schematic is depicted in Figure 2.10.

Figure 2.7. NML Multiplexer implementation.

Figure 2.8. NML Ripple Carry Adder implementation.

Figure 2.9. NML 3-to-8 Decoder implementation.

Looking at Figure 2.10, it can be noticed that there are two loops (Loop1 and

Loop2) in the structure. Given the intrinsic pipelined nature of NML technology, the presence of loop has a relevant impact on circuits performance. The length of Loop1 is longer than Loop2, and Loop1 includes two groups of signals, one is a 1-bit control signal and the other one is a multiple-bit feedback signal.

Figure 2.10. NML processing element implementation. There are two loops present in the architecture, Loop1 and Loop2. The longer loop (Loop1) occupies 208x3 clock zones. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015.

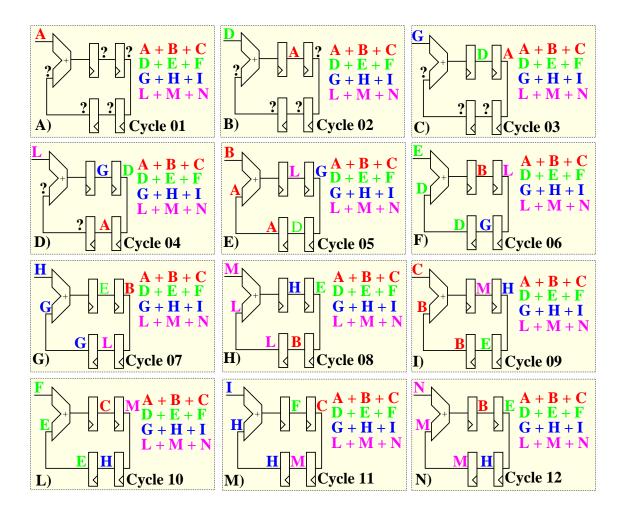

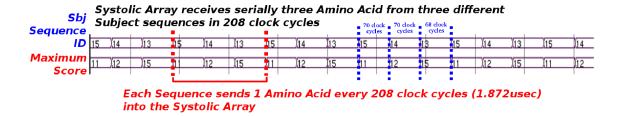

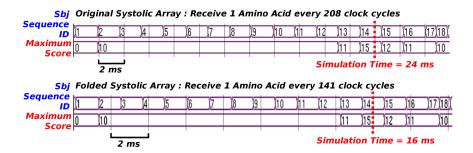

To simulate and evaluate the circuit, the Smith-Waterman algorithm was implemented with 8 processing elements, using a parallelism of 9 bit. Given the presence of a loop with a delay of 208 clock cycles, a new AA is fed to the circuit every 208 clock cycles, making the circuit latency equal to 208 clock cycles (Figure 2.11). Since every Subject sequence contains N AAs, to find the maximum alignment score for a particular sequence, 208\*N clock cycles is the required time. This means about 1.8 ms with an average clock frequency of 100 MHz and a value of N equal to 969

[9]. In this test case, the Subject sequences used for the test were made by the same number of AAs, but in general, every sequence can have a different length. The longer the sequence is, the longer is the time required for the analysis to be completed. Figure 2.11 depicts the simulation waveforms. The *Subject\_ID* identifies the biosequence number, while *OUT\_MAX* is the calculated alignment score. As can be seen sequence 14 has the highest alignment score among the first 16 sequences.

| NML        | Arc | hite | ctui | re : La | tency | / 208 cl | lock | c cycle | es, fr | eque | ency 1 | 100 | MHZ |     |    |    |   |

|------------|-----|------|------|---------|-------|----------|------|---------|--------|------|--------|-----|-----|-----|----|----|---|

| Subject_ID | 1   | 2    |      | 4       | ),5   | (6       | 7    | .8      | (9     | (10  | 11     | 12  | 13  | 14  | 15 | 16 | N |

| OUT_MAX    | û   | (10  |      |         |       |          |      |         |        |      |        |     | 11  | (15 | 12 | 11 | 7 |

|            |     |      |      |         |       |          |      |         |        |      |        |     |     |     |    |    |   |

Figure 2.11. Smith-Waterman algorithm architecture simulation results.  $Subject\_ID$  represents the number of the AA sequences analyzed, and  $OUT\_MAX$  is the corresponding maximum alignment score. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 23, Vol. 23, Vol. 2015.

### 2.2 Performance Optimization

Having implemented a complex and realistic architecture, some architectural-level problems about circuit performance and synchronization were put in evidence. For each problem, a solution is proposed here. Performance optimization techniques are also evaluated.

### 2.2.1 Data Interleaving

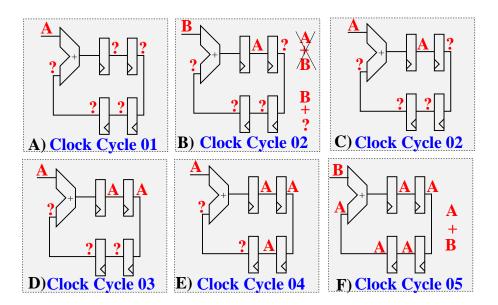

As described previously, the long delay between two subsequent inputs is due to the NML intrinsic pipelined nature which leads to long propagation delay on the feedback path. As demonstrated in Figure 2.12, the new input needs to wait for the previous result to propagate back, if a loop is present. As a consequence, the total latency in terms of clock cycles is determined by the number of registers in the loop.

Throughput of SW NML circuit =

$$\frac{1}{\text{loop length}} = \frac{1}{208 \text{ clock cycles}}$$

(2.1)

Figure 2.12. Example of NML architecture performance reduction due to the presence of loops inside intrinsically pipelined circuits. M. Vacca et al. "Feedbacks in QCA: A Quantitative Approach", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 10, Oct. 2015.