# POLITECNICO DI TORINO

SCUOLA DI DOTTORATO

Ph.D. in Electronics and Communications Engineering – XXVIII cycle

## Ph.D. Dissertation

# VLSI architectures design for encoders of High Efficiency Video Coding (HEVC) standard

Guoping Xiao

Coordinator of the Ph.D. course

Supervisor Prof. Guido Masera Prof. Maurizio Martina

Prof. Ivo Montrosset

To my parents, Zhao Heyun and Xiao Caiheng, and my beloved fiancee, Liu Yu

# Summary

The growing popularity of high resolution video and the continuously increasing demands for high quality video on mobile devices are producing stronger needs for more efficient video encoder. Concerning these desires, HEVC, a newest video coding standard, has been developed by a joint team formed by ISO/IEO MPEG and ITU/T VCEG. Its design goal is to achieve a 50% compression gain over its predecessor H.264 with an equal or even higher perceptual video quality. Motion Estimation (ME) being as one of the most critical module in video coding contributes almost 50%-70% of computational complexity in the video encoder. This high consumption of the computational resources puts a limit on the performance of encoders, especially for full HD or ultra HD videos, in terms of coding speed, bit-rate and video quality. Thus the major part of this work concentrates on the computational complexity reduction and improvement of timing performance of motion estimation algorithms for HEVC standard.

First, a new strategy to calculate the SAD (Sum of Absolute Difference) for motion estimation is designed based on the statistics on property of pixel data of video sequences. This statistics demonstrates the size relationship between the sum of two sets of pixels has a determined connection with the distribution of the size relationship between individual pixels from the two sets. Taking the advantage of this observation, only a small proportion of pixels is necessary to be involved in the SAD calculation. Simulations show that the amount of computations required in the full search algorithm is reduced by about 58% on average and up to 70% in the best case.

Secondly, from the scope of parallelization an enhanced TZ search for HEVC is proposed using novel schemes of multiple MVPs (motion vector predictor) and shared MVP. Specifically, resorting to multiple MVPs the initial search process is performed in parallel at multiple search centers, and the ME processing engine for PUs within one CU are parallelized based on the MVP sharing scheme on CU (coding unit) level. Moreover, the SAD module for ME engine is also parallelly implemented for PU size of  $32 \times 32$ . Experiments indicate it achieves an appreciable improvement on the throughput and coding efficiency

of the HEVC video encoder.

In addition, the other part of this thesis is contributed to the VLSI architecture design for finding the first W maximum/minimum values targeting towards high speed and low hardware cost. The architecture based on the novel bit-wise AND scheme has only half of the area of the best reference solution and its critical path delay is comparable with other implementations. While the FPCG (full parallel comparison grid) architecture, which utilizes the optimized comparator-based structure, achieves 3.6 times faster on average on the speed and even 5.2 times faster at best comparing with the reference architectures. Finally the architecture using the partial sorting strategy reaches a good balance on the timing performance and area, which has a slightly lower or comparable speed with FPCG architecture and a acceptable hardware cost.

# Acknowledgements

I would like to express my sincere gratitude to my supervisors, Prof. Guido Masera and Prof. Maurizio Martina. Attributed to their professional guidance, kindly encouragement and great patience I can finally accomplish the thesis work.

I am deeply grateful to my fiancee for her careful attendance and strong support all the way.

I also appreciate the help and encouragement from many of my friends, especially Zhang Qiutao, Bai Ou and Du Boyang.

I am sincerely grateful to my parents and elder sisters for their selfless love and support.

Finally I sincerely thank all those who have ever helped me these years, without your support, I would never reach where I am now.

# Contents

| Sι       |              |        |                                                                     | Ι   |

|----------|--------------|--------|---------------------------------------------------------------------|-----|

| A        |              |        |                                                                     | III |

| 1        | Introduction |        |                                                                     |     |

|          | 1.1          | Gener  | al Video Coding System                                              | 1   |

|          |              | 1.1.1  | Basics of Digital Video Coding                                      | 2   |

|          |              | 1.1.2  | Hybrid Video Coding                                                 | 4   |

|          | 1.2          | Overv  | iew of Current Video Coding Standard: HEVC                          | 6   |

|          |              | 1.2.1  | Partitioning                                                        | 7   |

|          |              | 1.2.2  | Intra-frame Prediction                                              | 8   |

|          |              | 1.2.3  | Inter-frame Prediction                                              | 8   |

|          |              | 1.2.4  | Transform and Quantization                                          | 10  |

|          |              | 1.2.5  | Entropy Coding                                                      | 10  |

|          | 1.3          | Motio  | n Estimation Algorithms                                             | 10  |

|          |              | 1.3.1  | Three Step Search                                                   | 11  |

|          |              | 1.3.2  | Diamond Search                                                      | 11  |

|          | 1.4          | Major  | Contributions                                                       | 12  |

|          | 1.5          | Organ  | ization of the Dissertation                                         | 13  |

| <b>2</b> | AN           | New SA | AD Computing Algorithm for Full Search Motion Estimation            | 14  |

|          | 2.1          | ME D   | istortion Measure Criterion                                         | 14  |

|          | 2.2          | The N  | ew SAD Computing Algorithm                                          | 16  |

|          |              | 2.2.1  | A New Strategy to Calculate the SAD                                 | 16  |

|          |              | 2.2.2  | The New SAD architecture to accelerate the FS ME algorithm          | 18  |

|          |              | 2.2.3  | Rate-Distortion Performance Evaluation with HM Test Model $\ . \ .$ | 25  |

|          | 2.3          | Hardw  | vare Implementation                                                 | 28  |

|          | 2.4          | Summ   | ary                                                                 | 31  |

| 3                                                     | An              | Enhan  | ced TZ (Test Zone) Search Algorithm for Fast Motion Esti-          |    |  |  |

|-------------------------------------------------------|-----------------|--------|--------------------------------------------------------------------|----|--|--|

|                                                       | mation of HEVC  |        |                                                                    |    |  |  |

|                                                       | 3.1             | Introd | uction of TZ Search Algorithm                                      | 32 |  |  |

| 3.2 An Enhanced TZ Search using Parallelized Strategy |                 |        | hanced TZ Search using Parallelized Strategy                       | 39 |  |  |

|                                                       |                 | 3.2.1  | Multiple Initial Search Centers                                    | 39 |  |  |

|                                                       |                 | 3.2.2  | Parallel ME Engines using Shared AMVP                              | 44 |  |  |

|                                                       |                 | 3.2.3  | Hardware Implementation                                            | 44 |  |  |

|                                                       |                 | 3.2.4  | Experimental Results                                               | 48 |  |  |

|                                                       | 3.3             | Summ   | ary                                                                | 48 |  |  |

| 4                                                     | Hig             | h Spee | d VLSI architecture for finding the first $W$ maximum/minimum      | n  |  |  |

|                                                       | valu            | les    |                                                                    | 50 |  |  |

|                                                       | 4.1             | Introd | uction                                                             | 50 |  |  |

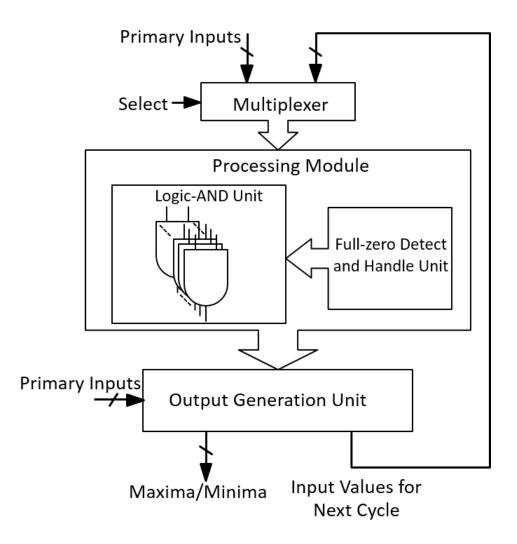

|                                                       | 4.2             | A Rad  | ix-sort-based VLSI Architecture with Low Cost                      | 52 |  |  |

|                                                       |                 | 4.2.1  | Problem formulation and the BWA Algorithm                          | 52 |  |  |

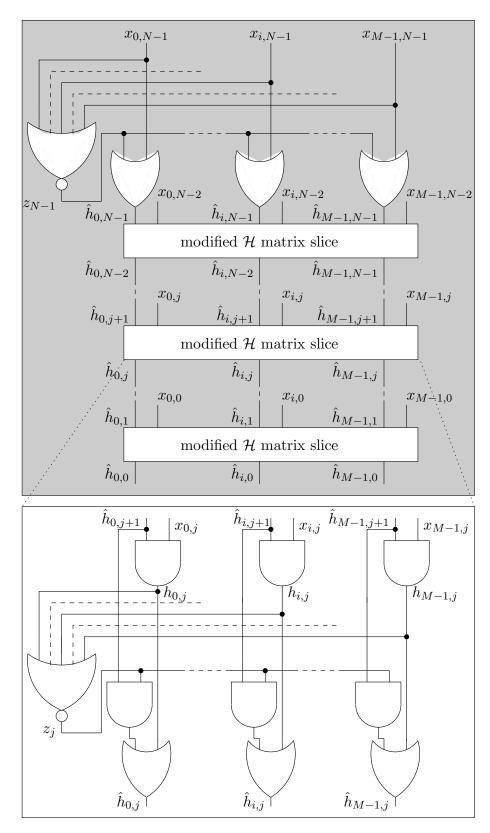

|                                                       |                 | 4.2.2  | Completed BWA Architecture                                         | 54 |  |  |

|                                                       | 4.3             | Compa  | arator-based VLSI Architectures with High Speed                    | 63 |  |  |

|                                                       |                 | 4.3.1  | The Architecture of Partial Sorting (PS)                           | 64 |  |  |

|                                                       |                 | 4.3.2  | The Architecture using Fully Parallellized Comparision Grid (FPCG) | 67 |  |  |

|                                                       | 4.4             | Experi | mental Results and Comparisons                                     | 76 |  |  |

| <b>5</b>                                              | Conclusion      |        |                                                                    |    |  |  |

|                                                       | 5.1             | Contri | butions                                                            | 80 |  |  |

|                                                       | 5.2             | Future | Work                                                               | 81 |  |  |

| Bi                                                    | Bibliography 82 |        |                                                                    |    |  |  |

# List of Figures

| 1.1  | Block diagram of a general video coding system                            | 2  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | Three typical YCrCb sampling patterns.                                    | 3  |

| 1.3  | Block diagram of general hybrid video coding system                       | 5  |

| 1.4  | Block diagram of HEVC coding system [1]                                   | 6  |

| 1.5  | HEVC quad-tree partitioning structure including CU, PU and TU (solid      |    |

|      | line for CU, dashed line for TU).                                         | 7  |

| 1.6  | Intra prediction modes for $4 \times 4$ block size in H.264 [2]           | 8  |

| 1.7  | Intra prediction modes in HEVC standard [1]                               | 9  |

| 1.8  | An example for block merging in HEVC [3]                                  | 9  |

| 1.9  | An example of Three Step Search                                           | 11 |

| 1.10 | An example of Diamond Search                                              | 12 |

| 2.1  | An example for block matching ME.                                         | 15 |

| 2.2  | 6 video sequences for test on statistics of "minority"                    | 18 |

| 2.3  | The percentage of pixel per MB that can be accounted as "minority" to     |    |

|      | the SAD calculation in six video sequences frame by frame [4]. $\ldots$ . | 19 |

| 2.4  | Block diagram of the new SAD algorithm.                                   | 19 |

| 2.5  | Successive SAD calculation.                                               | 20 |

| 2.6  | An example for the sub-blocks.                                            | 22 |

| 2.7  | Block diagram of coarse search                                            | 24 |

| 2.8  | HD video sequences for test used in the simulation                        | 25 |

| 2.9  | Rate-Distortion curves for all test sequences                             | 29 |

| 2.10 | Hardware architecture of proposed SAD algorithm.                          | 30 |

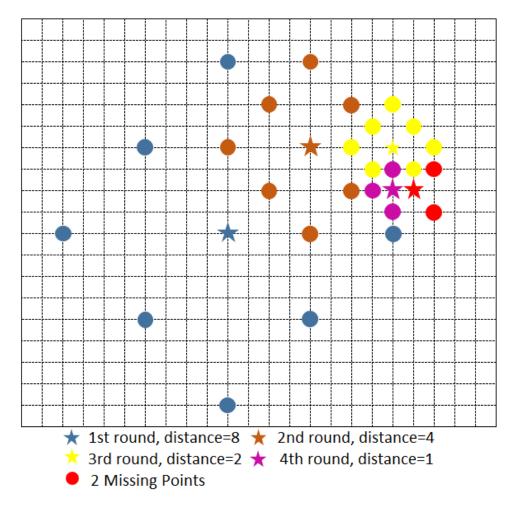

| 3.1  | The flowchart diagram of TZ Search.                                       | 33 |

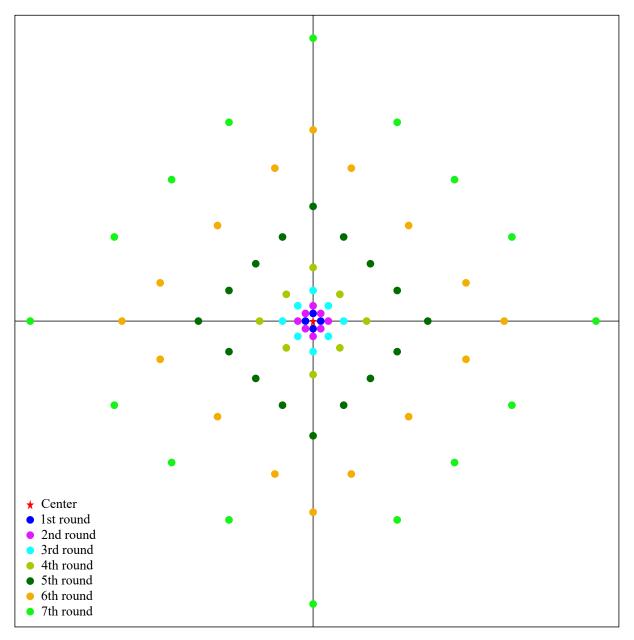

| 3.2  | The 7-round Diamond Search in the TZ Search algorithm.                    | 34 |

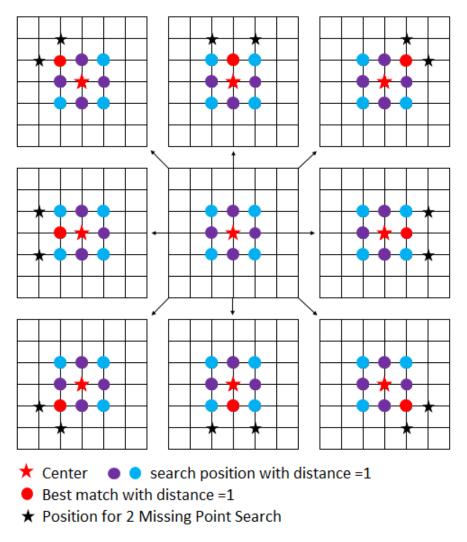

| 3.3  | 2 Missing Points Search                                                   | 36 |

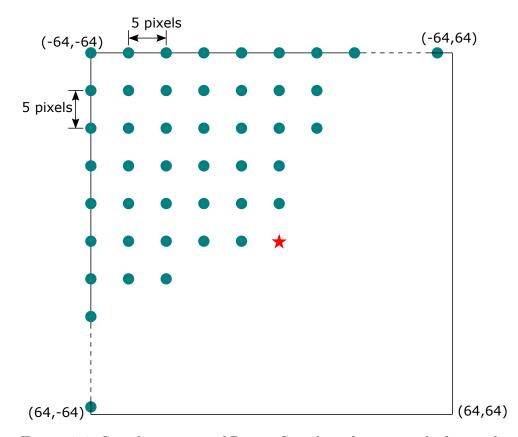

| 3.4  | Search patterns of Raster Search with a interval of 5 pixels              | 37 |

| 3.5  | An example for Raster Refinement Search.                                  | 38 |

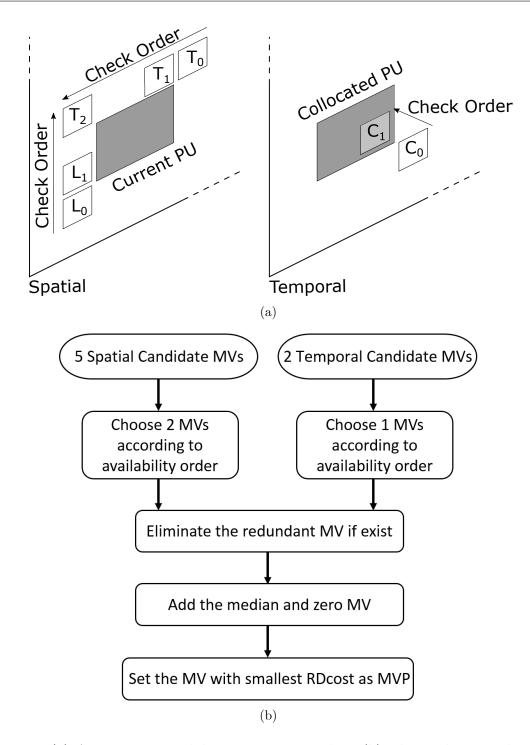

| 3.6  | (a) AMVP MV candidates construction list. (b) The working mechanism                                         |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | of AMVP.                                                                                                    | 40 |

| 3.7  | The derivation of MVP List                                                                                  | 41 |

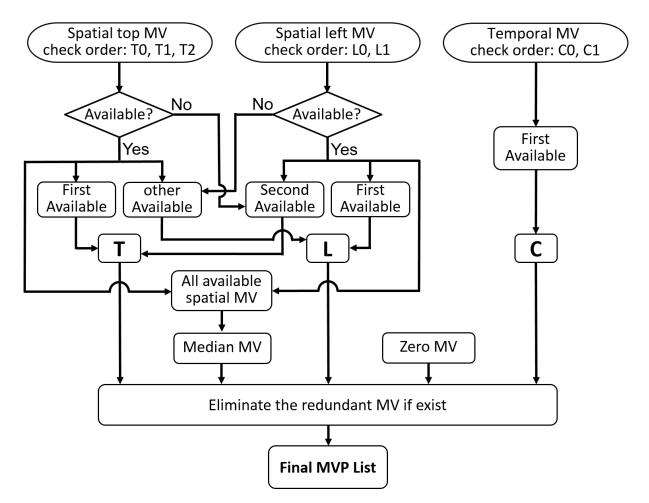

| 3.8  | The flowchart of the enhanced TZ Search.                                                                    | 42 |

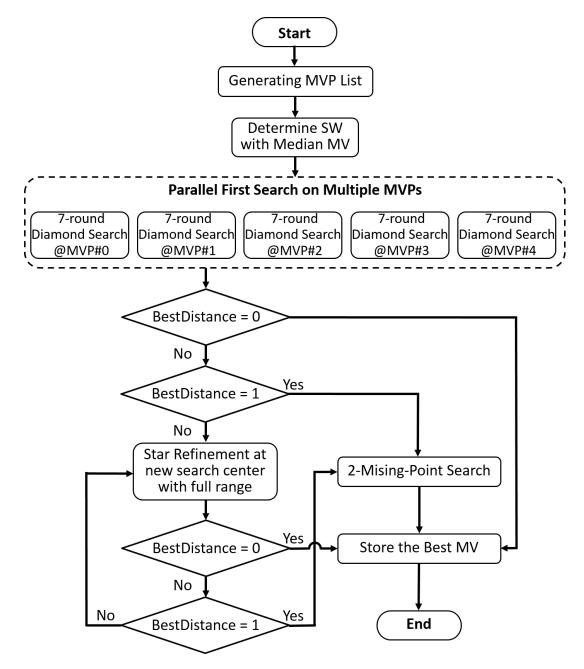

| 3.9  | (a) The default sequential processing order of PUs inside one CU. (b) Mech-                                 |    |

|      | anism of sharing MVP between PUs of one CU                                                                  | 43 |

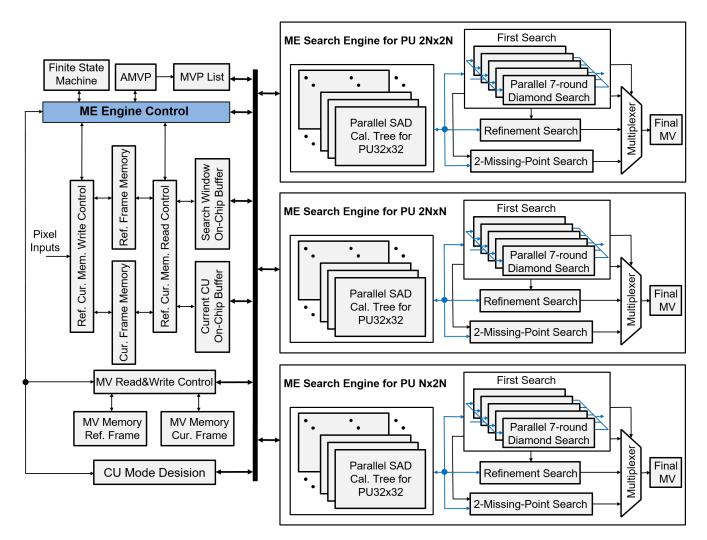

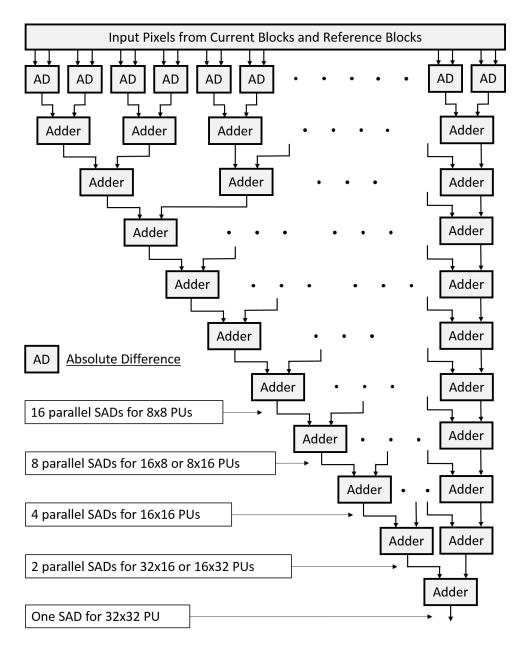

| 3.10 | The architecture of the enhanced TZ Search                                                                  | 46 |

| 3.11 | The architecture of parallel SAD calculation tree for PU32 $\times$ 32                                      | 47 |

| 4.1  | Block diagram of BWA architecture.                                                                          | 51 |

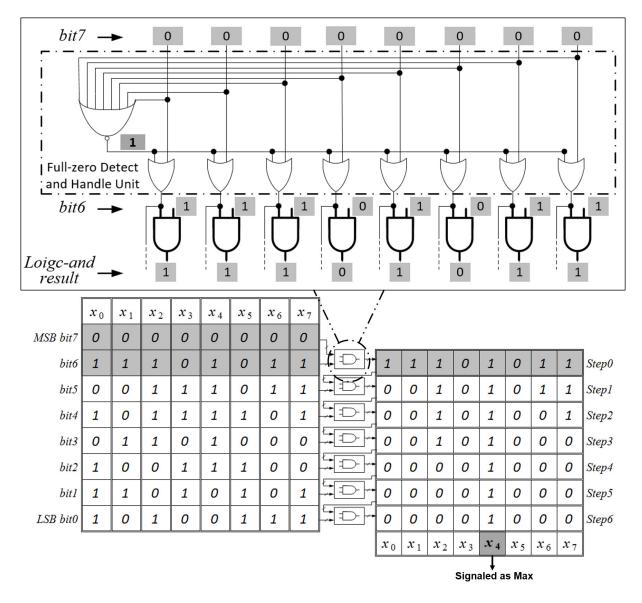

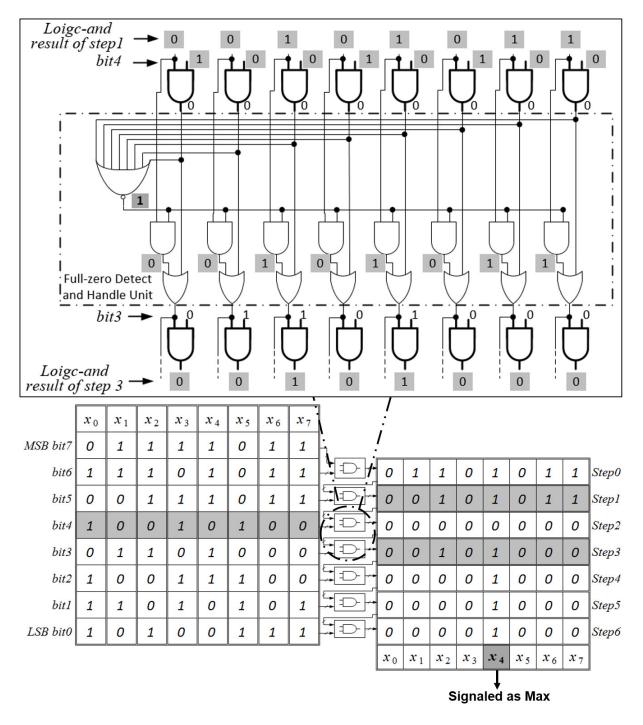

| 4.2  | An example to exhibit working principle of BWA algorithm                                                    | 53 |

| 4.3  | A special case $\#1$ for showing the failure of the initial BWA principle                                   | 54 |

| 4.4  | A special case $\#2$ for showing the failure of the initial BWA principle                                   | 55 |

| 4.5  | A special case #3 for showing the failure of the initial BWA principle                                      | 55 |

| 4.6  | A special case #4 for showing the failure of the initial BWA principle                                      | 56 |

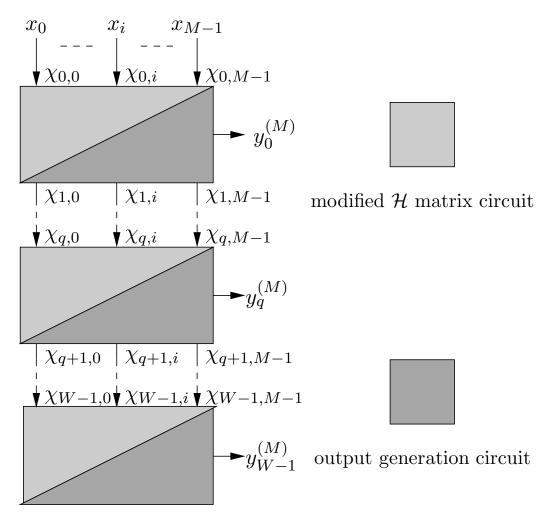

| 4.7  | BWA architecture: modified $\mathcal{H}$ matrix                                                             | 57 |

| 4.8  | The working principle of Full-zero Detect and Handle Unit for special case                                  |    |

|      | #1 in Figure 4.3. $\ldots$ | 59 |

| 4.9  | The working principle of Full-zero Detect and Handle Unit for special case                                  |    |

|      | #4 in Figure 4.6. $\ldots$ | 60 |

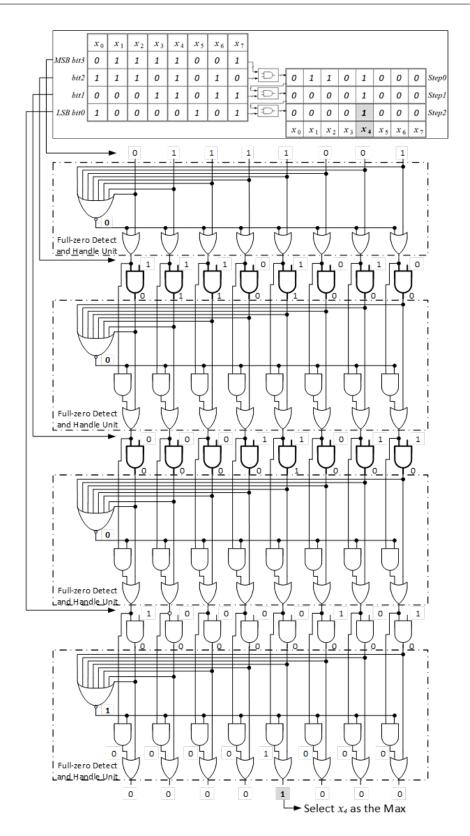

| 4.10 | An example for the full BWA architecture                                                                    | 61 |

| 4.11 | BWA architecture: output generation circuit in the case $q = 0. \ldots \ldots$                              | 62 |

| 4.12 | BWA architecture: cascade of $W$ stages                                                                     | 63 |

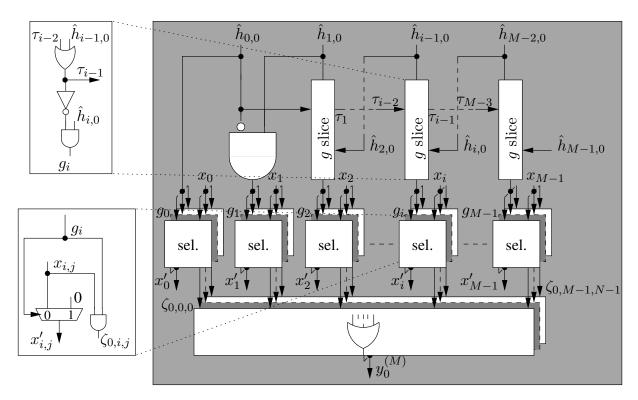

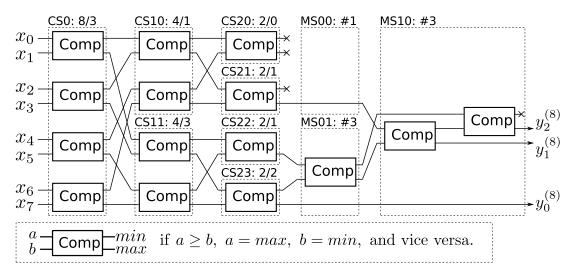

| 4.13 | An example: Structure for finding the first 3 maximum values from 8 inputs                                  | 64 |

| 4.14 | Structure of Partial-sorting for finding $W$ maximum values from $M$ inputs                                 | 65 |

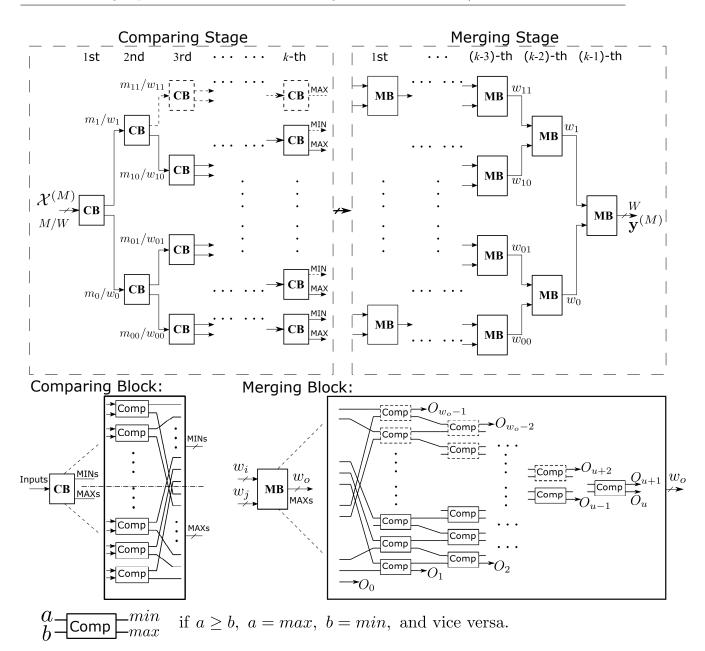

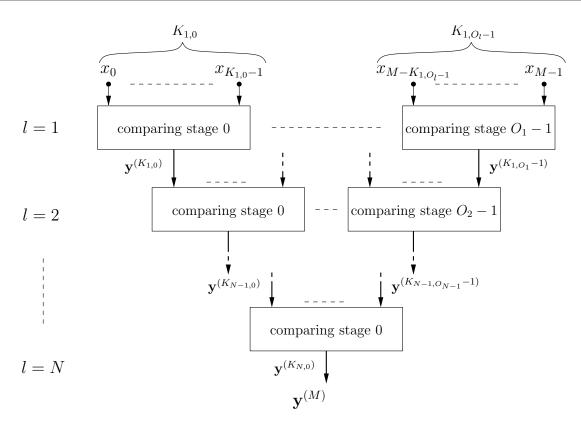

| 4.15 | Tree structure for finding the first $W$ maximum values                                                     | 68 |

| 4.16 | Graphical representation of the number of comparators required to find the                                  |    |

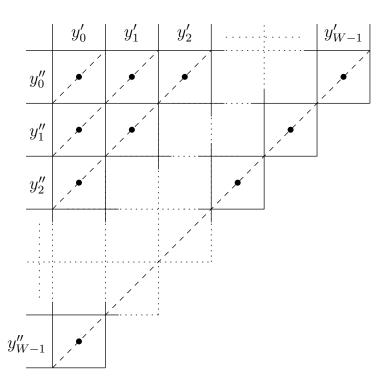

|      | first W maximum values in $\mathbf{y}'$ and $\mathbf{y}''$                                                  | 69 |

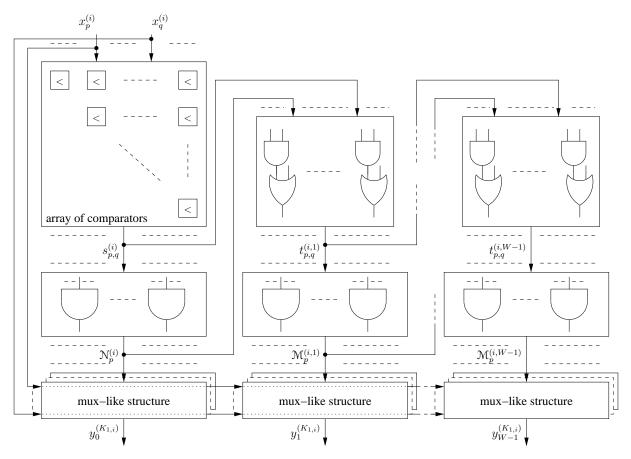

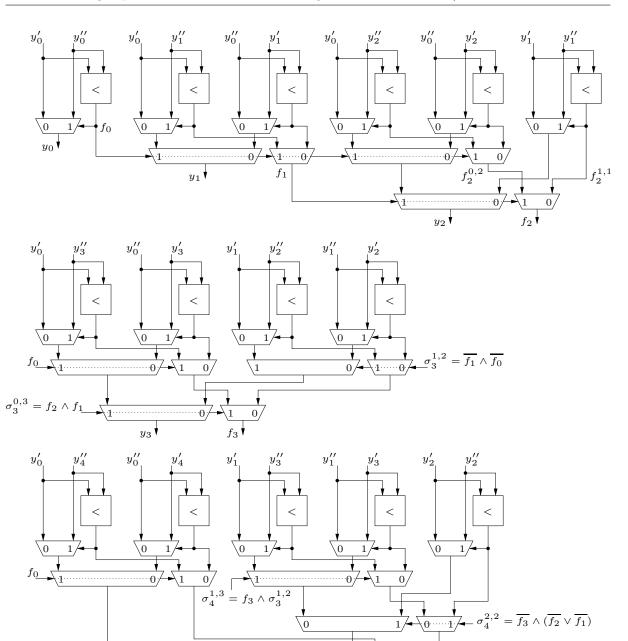

| 4.17 | Architecture of a comparing stage at $l = 1$                                                                | 71 |

| 4.18 | Details of the architecture of a comparing stage at $l = 1$ : one-hot signals                               |    |

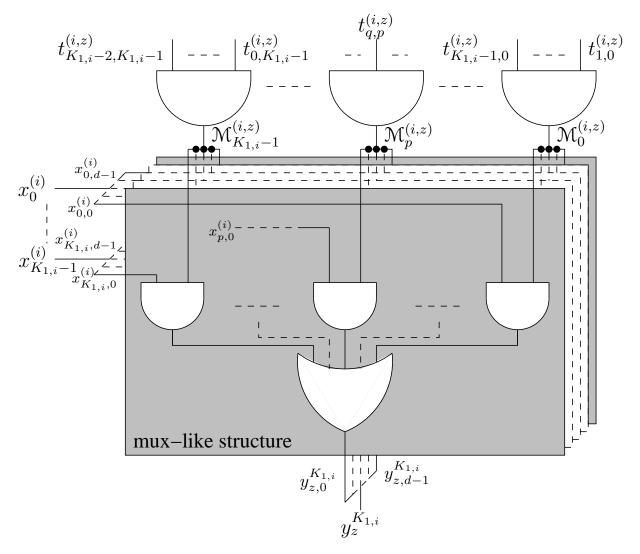

|      | and mux-like structure                                                                                      | 74 |

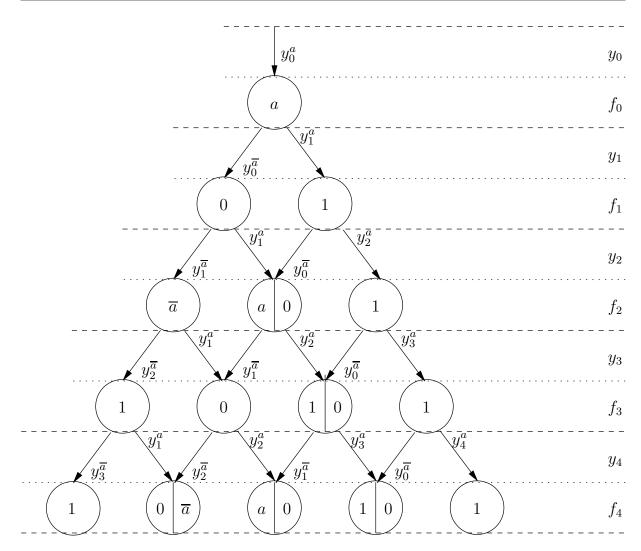

| 4.19 | Tree representation of the possible $\mathbf{y}$ sequences and $f_n$ values for $W = 5$ .                   | 75 |

| 4.20 | Circuit derived from the tree representation in Figure 4.19                                                 | 76 |

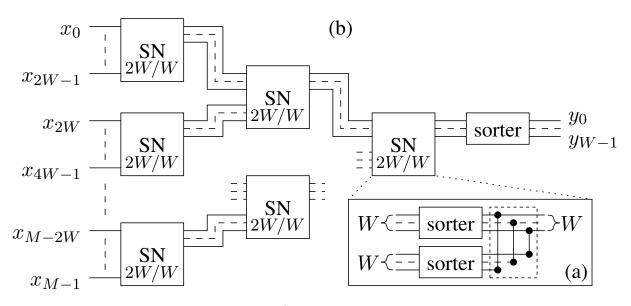

| 4.21 | M/W SN general structure                                                                                    | 77 |

# List of Tables

| 2.1 | Simulation results using different QP parameters for test sequence of Four                      |    |

|-----|-------------------------------------------------------------------------------------------------|----|

|     | People                                                                                          | 26 |

| 2.2 | Simulation results using different QP parameters for test sequence of Bas-                      |    |

|     | ketball Drive                                                                                   | 26 |

| 2.3 | Simulation results using different QP parameters for test sequence of Park                      |    |

|     | Scene                                                                                           | 27 |

| 2.4 | Simulation results using different QP parameters for test sequence of Traffic.                  | 27 |

| 2.5 | Simulation results using different QP parameters for test sequence of Ready                     |    |

|     | Steady Go                                                                                       | 28 |

| 3.1 | Design Specifications of an HEVC encoder considered in this work                                | 44 |

| 3.2 | Design Specifications of an HEVC encoder considered in this work. $\ldots$                      | 45 |

| 3.3 | Simulation result using difference test sequences with QP=32. $\ldots$ .                        | 48 |

| 4.1 | Post place and route results comparing area (A) $[\mu m^2]$ , critical path delay               |    |

|     | (C) [ns] and a<br>rea-delay-product (P=A·C ) $[\rm mm^2 \cdot ns]$ for different architectures. | 79 |

# Chapter 1 Introduction

As smart phone, tablet and HDTV has been an inseparable part of our life, digital video plays a more and more important role in the modern society. With the growing popularity of high resolution and high quality videos, digital video compression techniques has a increasing significance in the telecommunication and multimedia system in which bandwidth is still a valuable resource.

Digital video signal is represented as a sequence of real-world or virtual visual scenes [5,6]. Each frame is composed of a two-dimensional grid of pixels. The product of the number of columns and rows of pixels in the grid is known as resolution of the frame or video. For instance, a frame with the resolution of standard definition (SD) has  $720 \times 480$  pixels. Whereas its resolution can be various as small as  $176 \times 144$  (QCIF), or as large as  $1920 \times 1080$  (FHD) [7] or even 4K and 8K UHD. A pixel generally consists of three fundamental components represented in RGB or YUV. Each component normally takes 8 or 12 digital bits. It can be observed that the size and data rate of a raw video signal is tremendous. Taking a FHD video (typically with a frame rate of 30 fps) as an example, its data rate is  $30 \times 1920 \times 1080 \times 3 \times 8 = 1.49$  Gbit per second. Apparently it has already far surpassed the capacity of today's telecommunication infrastructure. Moreover, situation will be even more critical if targeting for the higher resolution videos like UHD.

## 1.1 General Video Coding System

Since video sequences are sampled spatially and temporally with a high frame rate (e.g. 30 fps). There exists an immense amount of temporal and spatial redundant information since both the consecutive frames and the blocks inside one frame are highly correlated. Digital video coding, as the process of compression and decompression of video signal, generally is to exploit and eliminate these redundancies from the video sequences in order to alleviate the requirement on bandwidth for transmission and space for storage [8].

#### 1.1.1 Basics of Digital Video Coding

#### Overview

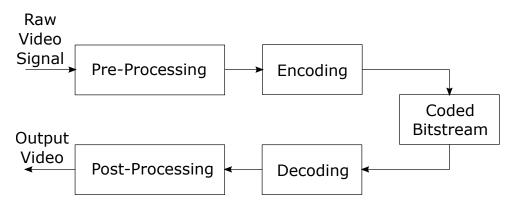

Generally, a raw video is firstly captured by a camera or video recording device in digital or analogue format [9]. Figure.1.1 illustrates the block diagram of a typical digital video coding system. The pre-processing unit is to pre-process the raw video signal, in which if the format of raw videos from CCD camera is analogue, it will be firstly digitized into RGB images and then the digital signal in RGB presentation is converted into YUV representation [10]. In the next the signals will be compressed and encoded by the encoding unit. This encoding process is able to compress the raw video in a high compression ratio and maintains an good video quality through powerful smart strategies and high efficient algorithms. On the contrary, the output video for displaying can be acquired through decoding and post-processing modules as shown in Figure.1.1.

Figure 1.1: Block diagram of a general video coding system.

#### **Concepts and Definitions**

As aforementioned video compression seeks to eliminate redundancies from video sequences, there are two types of compression : lossless compression and lossy compression, which are categorized depending on whether the encoding process brings about loss in the information after compression. Although the lossy compression can't fully reconstruct the video sequences thus suffers from a degradation of video quality, it achieves a compression ratio almost 95% higher than lossless compression. Therefore lossy compression is utilized by most practical video encoding systems. Before diving into the details of compression techniques, some basic concepts and definitions of video coding are introduced firstly in the following.

**Color Space-** Generally speaking, each sample point of the colorful video signal displayed by most of the digital video applications requires three numbers to accurately represent a color. One popular color space system is the RGB color space, of which the

three numbers indicate the relative proportions of Red, Green and Blue. Each number is represented with 'N' digital bits, for instance, a number of 8-bit can hold 256 color levels for each color element. A Combination of these three color elements in varying proportions can produce any color. Whereas for the sake of decreasing the bandwidth requirement for transmitting video signals, the YCrCb color space is widely utilized because normally it can represents every pixel with less bits. YCrCb employs a luminance/chrominance coordinate which extracts the luminance from the color information and represent luma (Y) part using a higher resolution than chroma color parts (Cr and Cb) [11]. Since according to human visual system (HVS) it is more sensitive to luminance than chromince [12]. In this way YCrCb can represents a color image more efficiently. The converting relationship between the two color spaces, RGB and YCrCb, is expressed by

$$Y = k_r R + k_g G + k_b B$$

$$Cr = R - Y$$

$$Cg = G - Y$$

$$Cb = B - Y$$

(1.1)

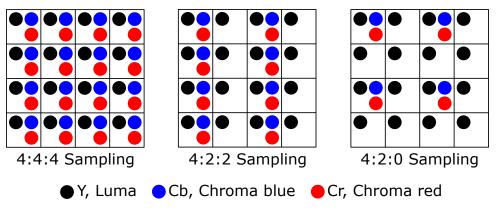

where  $k_r, k_g, k_b$  are weighting factors. It is easy to observe that Cr+Cg+Cb is a constant, thus using only two of them is sufficient for storage or transmission and the last component can be obtained from the other two. Furthermore, the YCrCb color space and its variants are referred as YUV. Based on several typical weighting factors there are three common YCrCb sampling patterns widely supported by video coding standards which are shown in Figure 1.2. The 4:4:4 sampling indicates Y, Cr and Cb components all have full resolution

Figure 1.2: Three typical YCrCb sampling patterns.

so that it retains full fidelity of the chrominance component. In the 4:2:2 sampling, chrominance components are sub-sampled into half resolution in horizontal direction. While 4:2:0 sampling half the samples of chrominance components in both horizontal and vertical resolution. Since in 4:2:0 sampling each of Cr and Cb components only holds 1/4

of the number of samples of Y component, video in 4:2:0 YCrCb format needs half of the storage space or transmission bandwidth relative to that of 4:4:4 YCrCb video. As a result, 4:2:0 sampling is the most widely utilized one.

**Frame Rate-** As mentioned before, a video is captured by camera temporally at a specific frequency. The frame rate represented in Hz or frames per second (fps) is referred as the rate for capturing or playing back. Typically the Standard Definition television supports a frame rate of 25 or 30 fps. Whereas in order to generate a video with very smooth apparent motion, it requires 50 or 60 frames per second or even higher like 120 fps. However, high frame rate means a very high data rate. Thus choosing a reasonable frame rate is very important when encoding a video signal for specific applications.

Video Resolutions- Typically the video resolution is expressed as the size of frame, namely length  $\times$  width, in pixels. There are some common resolutions including:

8K UHD (Ultra High Definition): it refers to a resolution of  $7680 \times 4320$ .

4K UHD: it refers to a resolution of  $3840 \times 2160$ .

FHD (Full High Definition): it refers to a resolution of  $1920 \times 1080$ .

HD: it normally refers to a resolution of  $1280 \times 720$ .

SD (Standard Definition): it refers to a resolution of  $640 \times 480$ .

CIF (Common International Format): it refers to a resolution of  $352 \times 288$ .

QCIF (Quarter CIF): it refers to a resolution of  $176 \times 144$ .

**Color Depth-** It is also called as bit depth, which is usually referred to the number of bits used for one pixel or one color component [1]. Color depth defines how many color levels can be expressed. Typically a 8-bit color depth enables 256 kinds of colors which is widely utilized by monitor of consumer devices. Moreover, for some special applications there are 24-bit color depth for true color and 30/36/48-bit color depth for deep color [13].

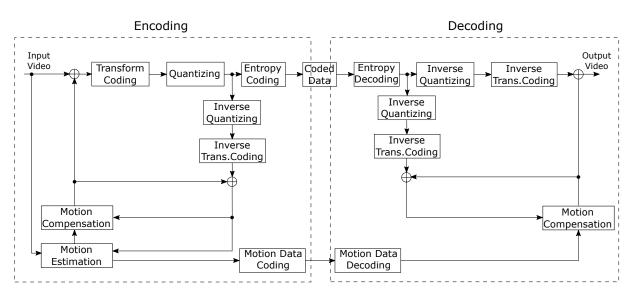

#### 1.1.2 Hybrid Video Coding

Resorting to bunch of compression tools, hybrid coding system regularly consists of several standard video compression techniques [14–19]. Figure 1.3 depicts a typical hybrid video coding system, which is composed of the encoding part and decoding part. As aforementioned, the main purpose of video coding is to compress the video by reducing the redundancy of the video sequences. In general, there are two kinds of redundancy existing in video signal: the spatial and the temporal. The spatial redundancy is exploited through intra-frame prediction, of which the mechanism is to find a best matching block

Figure 1.3: Block diagram of general hybrid video coding system.

for current one from its left and upper neighboring blocks assuming a coding mode of raster-scan order is applied. It is because there is a high correlation between neighboring pixels inside a frame. As a result in intra-frame prediction a block is reconstructed by the blocks that has already been encoded and stored in the bit-stream for output. While on the contrary inter-frame prediction is designed to deal with the temporal redundancy existed between consecutive frames such as the frame in the past or in the future. The temporal redundancy is normally referred to the correlation of two adjacent frames, since they usually have similar backgrounds or a same object with a relative motion. Thus the purpose of inter-frame prediction is to search for a best matching block for the current one in the reference frame from the past or the future or both of them.

After the best matching candidate for the current block is found by either intra-frame or inter-frame prediction, only the difference between the original block and the predicted one needs to be encoded. As seen from Figure 1.3, these differences (also called residuals) will be further processed and converted into the coefficients of transform domain by the Transform Coding Unit. Transforming is an operation to reconstruct the residuals into signals of frequency domain using transform algorithms such as Discrete Cosine Transform (DCT), which will make the signals more compact. Therefore more redundant information can be eliminated through transforming.

In the next the transforming coefficients will be further quantized by quantization operation which is trying to reduce the range of the signal for saving the number of bits for transmission or storage. And there is an important criterion measured by Quantization Parameter (QP) for the step size between consecutive re-scaled values [2]. Since a large QP can reach a high compression ratio but result in a relative low video quality because of a rough approximation of original signal. On the contrary a small QP will realize a more closely approximation of original signal, so it will achieve high video quality but degrade the compression efficiency. Finally the quantized transform coefficients together with the motion data are converted into compressed output bit-stream for transmission by the Entropy Encoding Unit shown in Figure 1.3. On the other hand the decoding part performs the inverse operations on the bit-stream to reconstruct the video for playing.

Figure 1.4: Block diagram of HEVC coding system [1].

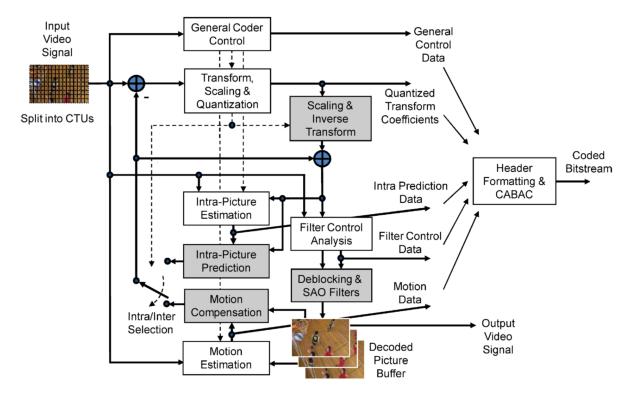

## 1.2 Overview of Current Video Coding Standard: HEVC

The High Efficiency Video Coding standard is formally issued by the Joint Collaborative Team on Video Coding (JCT-VC) founded by the international standardization organizations of ITU-T Video Coding Experts Group (VCEG) and ISO/IEC Moving Picture Experts Group (MPEG) [20]. Besides addressing all the available application of the preceding video coding standard, H.264/AVC, two critical aspects: higher and higher video resolution and more parallelized architectures for coding are the main concerning in the design of HEVC [1]. With respect to H.264, HEVC aims to gain an 50% more compression with no loss on the video quality. Being the same with its predecessors such as H.264, H.263, MPEG-2 and so on, HEVC standard defines the syntax and structure for compressing videos and generating decoded sequences, and specifies a bunch of necessary techniques or tools for video coding. A typical block diagram of HEVC coding system

is depicted in Figure 1.4. In the following sections new features of HEVC standard are introduced in details.

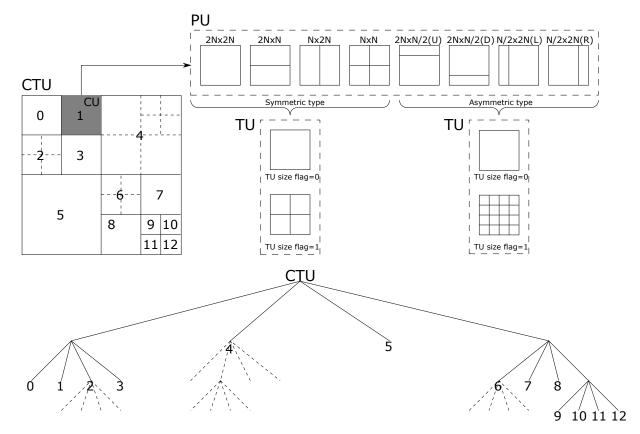

Figure 1.5: HEVC quad-tree partitioning structure including CU, PU and TU (solid line for CU, dashed line for TU).

#### 1.2.1 Partitioning

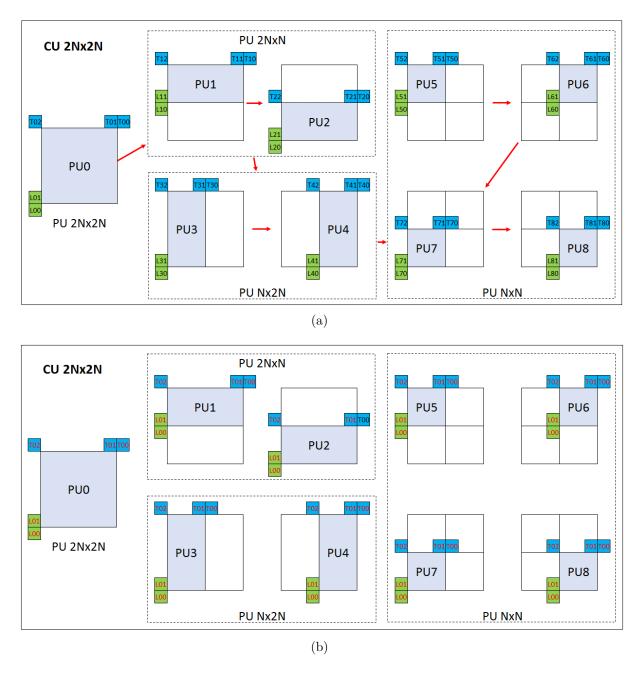

In the former video coding standard H.264 variable sizes of Macro-Block (MB) from  $4\times4$  to as large as  $16\times16$  are supported [21]. Whereas larger MB size is utilized in HEVC standard, which extends the maximum traditional MB size of  $16\times16$  in H.264 to  $64\times64$  for facilitating the compression of high definition videos. Additionally more flexible partitioning of video frames is supported for improving the coding efficiency, where available block size varies from  $4\times4$  up to  $64\times64$  including symmetric partitioning such as  $2N \times 2N$ ,  $2N \times N$ ,  $N \times 2N$  and  $N \times N$ , and also asymmetric motion partitioning (AMP) for instance  $2N \times N/4(U)$ ,  $2N \times N/4(D)$ ,  $N/4 \times 2N(L)$  and  $N/4 \times 2N(R)$ . In particular  $N \times N$  is only allowed for minimum coding unit (CU) and the AMP is not applied to CU whose size is smaller than  $16 \times 16$ . Figure 1.5 illustrates the partitionings and quadtree structure utilized in the HEVC standard, in which the analogous structure, called coding tree unit (CTU), is spitted into CUs using a quad-tree partitioning structure, and

a CU can be further sub-divided into prediction units (PU) for inter-frame or intra-frame prediction and its transformation is performed using one or more transform units (TU).

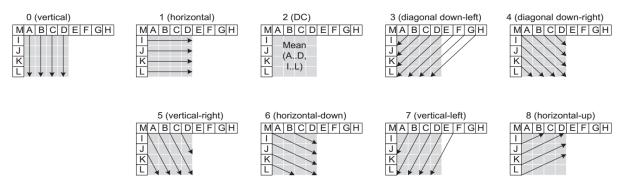

Figure 1.6: Intra prediction modes for  $4 \times 4$  block size in H.264 [2].

#### 1.2.2 Intra-frame Prediction

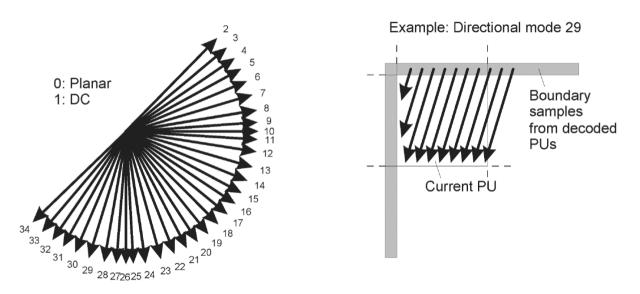

According to the syntax of HEVC standard, the choice of intra-frame or inter-frame prediction of a PU is made at the CU level. When the intra mode is determined for the CU, as discussed in Section 1.1.2, intra-frame prediction is to code PUs of the CU using its upper and left neighboring PUs which have already been encoded. In H.264 standard, 9 prediction modes are available for performing the prediction of  $8 \times 8$  and  $4 \times 4$  block size, that is shown in Figure 1.6 for  $4 \times 4$  block size. And for block size  $16 \times 16$  there are only 4 prediction modes available: vertical, horizontal, DC and plane. Whereas in HEVC standard for the sake of improving prediction accuracy, the total number of available prediction modes is increased to 35, 33 angular modes as well as the DC and planar modes, which is depicted in Figure 1.7. Specifically the number of most probable intra prediction modes for every PU is set to 3 which is determined by the modes of two neighboring PUs: the one on the left and the one on the upper.

#### **1.2.3** Inter-frame Prediction

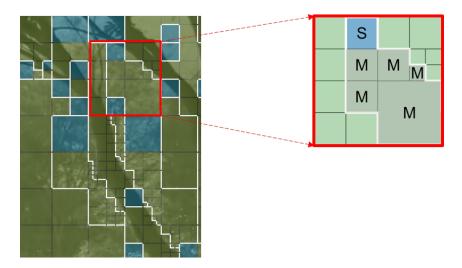

Since only the correlation between neighboring blocks inside a single frame is exploited by intra-frame prediction, it can not reach a high compression ratio. Most of pictures in the video sequence is encoded using inter-frame prediction because it reduces much more redundancy by employing the temporal correlation between blocks from different frames. With respect to H.264 standard, in HEVC the advanced motion vector prediction (AMVP) technique utilizing both spatial and temporal motion vectors has improved the accuracy of motion vector prediction. Moreover, with the replacement of spatial direct mode in H.264, a new technique of block merging mode is applied in the inter-frame

Figure 1.7: Intra prediction modes in HEVC standard [1].

prediction of HEVC, which further enhance the bit-rate reduction by joining the blocks with equal motion parameters and sharing the motion data. An example for block merging is presented in Figure 1.8, in which the shared motion information is held by the seed block (S) and the other merged blocks (M) copy it from S when required. As for the fractional inter-frame prediction, in order to realize high precision interpolation a 8-tap and 7-tap interpolation filter are utilized for the half-pixel positions and quarter-pixel positions respectively [22].

Figure 1.8: An example for block merging in HEVC [3].

#### **1.2.4** Transform and Quantization

After the motion estimation, all the prediction error residuals are transformed into a set of coefficients for efficient transmission and storage. In HEVC standard, as indicated in Figure 1.5, TU size of  $4 \times 4$ ,  $8 \times 8$ ,  $16 \times 16$  and  $32 \times 32$  are supported. The 2-D transforms based on discrete cosine transform (DCT) are designed for them and special efforts are particularly spent on selecting the value of the transfrom matrix for retaining the property of easy-to-implementation [1]. Furthermore when conducting the transform for block size of  $4 \times 4$  in intra-frame prediction mode, an alternative integer transform grounded on discrete sine transform (DST) is available for use. As for the quantization, a same quantizing mechanism with H.264 is applied with a QP value varying from 0 to 51.

#### 1.2.5 Entropy Coding

In HEVC standard a bit-stream is produced using motion parameters, prediction modes, quadtree partitioning information, quantized transform coefficients and some other control data through entropy coding. And only one entropy coding method, Context-Adaptive Binary Arithmetic Coding (CABAC), is specified in the standard. Although there is no change made on the core algorithm of CABAC, it is optimized on the aspects of context modeling, adaptive coefficient scanning, coefficient coding, sign data hiding and so on to improve its throughput.

### **1.3** Motion Estimation Algorithms

Motion Estimation (ME) as one of the most significant part of video coding contributes a great proportion of the compression and also occupies a large part of the computational complexity of the encoder [23–26]. There are a lot of algorithms proposed to conduct the ME operation [24,27–46]. Full Search is a ME strategy with a highest estimation accuracy which exhaustively compares all available candidate blocks in the search area with the current one to find the best matching block, thus it is at a high computational cost. With respect to Full Search, many fast search algorithms for ME are developed by reducing the number of search points to achieve an improvement on complexity degradation and throughput but at a cost of video quality loss. In the following, details of some well known fast search algorithms such as Three Step Search (TSS) [44] and Diamond Search (DS) [45, 46] are introduced.

#### 1.3.1 Three Step Search

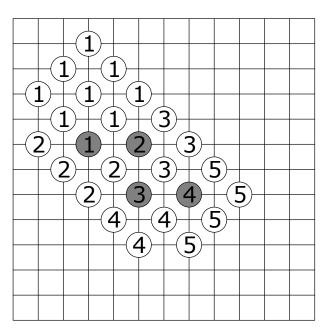

The TSS starts the search at the motion vector predictor (MVP), namely search center, assuming its coordinate is  $(MVP_x, MVP_y)$ . Thus with a step size of d, the coordinates of the 9 search positions for each step of TSS are  $(MVP_x, MVP_y)$ ,  $(MVP_x - d, MVP_y - d)$ ,  $(MVP_x, MVP_y - d)$ ,  $(MVP_x + d, MVP_y - d)$ ,  $(MVP_x + d, MVP_y)$ ,  $(MVP_x + d, MVP_y + d)$ ,  $(MVP_x, MVP_y + d)$ ,  $(MVP_x - d, MVP_y + d)$  and  $(MVP_x - d, MVP_y)$ . The best matching position of current step will be the search center of next step and the step size d is updated with a decrement. This algorithm is terminated after exactly 3 steps with the position of minimum distortion in the third step as the final best match. An example with a initial step size of 3 and a decrement of 1 in each step is shown in Figure 1.9, where gray circles represent best match position in each step and the one in third step marks the final best match.

Figure 1.9: An example of Three Step Search.

#### 1.3.2 Diamond Search

Although there are also 9 search positions initially in DS algorithm, these positions are placed according the shape of a diamond at the center of MVP. It is not as same as a square pattern in TSS algorithm. Figure 1.10 exhibits an instance of DS algorithm. In every round of search, if the point with minimum distortion is on the vertex or face of the diamond pattern, DS will continue to do the next search round at the new center. From Figure 1.10 we can see except for the first round, 3 to 5 new positions will be evaluated in each following round. The termination criterion of DS algorithm is that it will not stop

searching until the best matching position is at the center of diamond pattern.

Figure 1.10: An example of Diamond Search.

TSS and DS algorithms or their enhanced variants have been widely used. In the HEVC reference software, the Test Zone (TZ) search is adopted as the default fast search algorithm, which is also based on the DS search mechanism.

## **1.4 Major Contributions**

In this work, research efforts are dedicated to the computational complexity reduction and improvement of timing performance of motion estimation algorithms for HEVC and the implementation and optimization of their VLSI architectures.

Firstly, relative to the conventional computing method of SAD (Sum of Absolute Difference) a new strategy to calculate the SAD is designed grounded on the statistics on property of pixel data of video sequences. With this strategy the amount of computations required in the full search algorithm is greatly reduced, thus the total encoding time is saved by a large scale. Moreover, in order to strengthen the performance of TZ search for HEVC, a novel scheme of parallel initial search is applied utilizing multiple motion vector predictors. Besides, with the mechanism of sharing MVP on the CU level the ME engines for PUs inside one CU are parallelized. Applying with these enhancement, the proposed TZ search algorithm achieves an appreciable improvement on the throughput and coding efficiency of the HEVC video encoder. Finally VLSI architectures based on the schemes of BWA (Bit-Wise AND) and parallel comparison for finding the first W

maximum/minimum values are developed to degrade the hardware cost and improve the timing performance.

## **1.5** Organization of the Dissertation

**Chapter 2** gives an overview of distortion measure criterion in ME and introduces the new SAD computing strategy for full search algorithm.

**Chapter 3** firstly places an introduction on the original TZ search algorithm from HEVC reference software, and in the next presents several proposed schemes for enhancing the TZ search and its detailed hardware implementation.

Chapter 4 presents two kinds of VLSI architectures for finding the first W maximum/minimum values based on BWA (Bit-Wise AND) and parallel comparison strategies respectively. The performance of these architectures and comparisons with reference architectures are also introduced.

**Chapter 5** addresses a summary for this research work. The ideas and directions for future work are also discussed.

# Chapter 2

# A New SAD Computing Algorithm for Full Search Motion Estimation

Motion Estimation (ME) is one of the most critical module in video encoder. It occupies almost 50%-70% of computational complexity of codecs [23–26], which will be a bottleneck for further improving the performance of encoders in terms of coding speed, bit-rate and video quality when targeting for full HD or ultra HD videos. Therefore improving the efficiency and reducing the computational load of ME component without degrading video quality is of great significance. In this chapter, based on the statistics on property of pixel data of video sequences, a new strategy to calculate the SAD (Sum of Absolute Difference) for ME is explored. Before introducing the details of this strategy, an discussion on the ME distortion measure criterion is given at first.

## 2.1 ME Distortion Measure Criterion

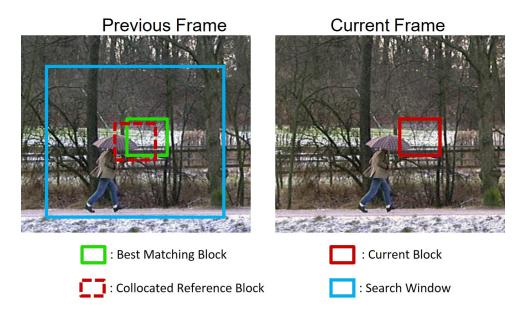

As mentioned in section 1.3, the main task of ME is to find the best matching block within the search window in the reference frame for the current block and generate the best motion vector. Figure.2.1 shows an example for block matching ME. In order to find the best matching block (highlighted by green box), it is necessary to search within the whole search window (highlighted by blue box) for the most similar one. Thus a matching criterion or distortion computing method is required to measure the similarity between a possible candidate block and the current block. However, the perceptual similarity or distortion in visual content is very difficult to quantify, since human visual system is complex and hard to understood [47]. In practice, for the digital video signal there are many distortion measure models [48, 49]. Amongst, Mean Squared Error (MSE) and Sum of Absolute Difference (SAD) are in the most common use. We assume f(i, j, t)represents the intensity of a pixel at the coordinate (i, j) in the frame t and accordingly

Figure 2.1: An example for block matching ME.

$f(i + MV_x, j + MV_y, t - 1)$  is the intensity of a pixel of a candidate block in the t - 1 frame as a reference with a motion vector  $(MV_x, MV_y)$ , furthermore, the size of a target MB is  $N \times N$  pixels, and search range is of  $\pm W$  in each direction, so the search window is of size  $(2W + N) \times (2W + N)$ . Supposing current block is at the location of (u, v), then MSE distortion measure model [50] is defined as

$$MSE(MV_x, MV_y) = \frac{1}{N \times N} \sum_{i=u}^{u+N-1} \sum_{j=v}^{v+N-1} [f(i, j, t) - f(i + MV_x, j + MV_y, t - 1)]^2.$$

(2.1)

From Equation 2.1 it is clear that MSE calculates the square of the difference between every two corresponding pixels of current and candidate block, then sums them up and computes its average as the final value. As a result, this value is used to assess the similarity, or the matching degree, of a candidate block. Thus in order to obtain the best matching block, the MSE model is applied for every candidate block with a different motion vector  $(MV_x, MV_y)$  within the search window defined by the search range in the reference frame. Finally a candidate block with the minimum MSE will be denoted as the best matching block which is given by

$$MSE_{min} = min\{MSE(MV_x, MV_y)\}, (-W, -W) \le (MV_x, MV_y) \le (+W, +W).$$

(2.2)

The MSE can be interpreted as the Euclidian distance [51] between the candidate block and target block which is considered as a good block similarity measure model, because it is very close to the perceived similarity by the human visual system. Although MSE can achieve a precise distortion assessment, it is at the expense of high computational complexity. From Equation 2.1 for one  $N \times N$  candidate block, it spends  $N^2$  subtractions,  $N^2$  squaring operations (or multiplication), and  $N^2$ -1 additions on calculating the MSE result. Whereas considering the HEVC standard is targeting for FHD or UHD videos and its search range is enlarged to  $\pm 64$ , the MSE will result in tremendous computations which is extremely not practical.

On the meantime, there is a similar block distortion measure model, Sum of Absolute Difference (SAD) [52], which calculates the absolute difference between every two pixels of current block and candidate block instead of the square difference in MSE. The SAD at location (u, v) with a motion vector  $f(i + MV_x, j + MV_y, t - 1)$  is denoted as

$$SAD(MV_x, MV_y) = \sum_{i=u}^{u+N-1} \sum_{j=v}^{v+N-1} |f(i, j, t) - f(i + MV_x, j + MV_y, t - 1)|, \qquad (2.3)$$

and similarly the best matching block is with the minimum SAD given by

$$SAD_{min} = min\{SAD(MV_x, MV_y)\}, \ (-W, -W) \le (MV_x, MV_y) \le (+W, +W).$$

(2.4)

From aforementioned equations the SAD distortion measure model needs  $N^2$  subtractions with absolute operation and  $N^2$ -1 additions for every candidate block. Compared to MSE, with the absence of multiplication operations to get the distortion results, it is more feasible for the hardware implementation despite of less accuracy.

## 2.2 The New SAD Computing Algorithm

#### 2.2.1 A New Strategy to Calculate the SAD

As discussed in the beginning of this chapter, in the video coding system the ME module is one of the most critical part which contributes almost 50%-70% the computational complexity of the video encoder. Therefore it is highly meaningful to design more efficient algorithm and architecture to reduce the amount of computations of ME. Although the SAD criterion is better than the MSE on the complexity, it still requires a huge amount of computations since it involves every pixel of the target block and perform the subtracting, absoluting and adding operations. Especially in the full search algorithm for the high definition videos, the situation will be even worse. Based on the algorithm presented in [4], a new SAD computing algorithm is proposed to improve the efficiency of the SAD architecture based on the statistics on property of pixel data of video sequences. Let  $\Psi$  and  $\Phi$  be the two sets of N natural numbers denoted as:

$$\Psi = \{\psi_0, \psi_1, \psi_2, ..., \psi_i, ..., \psi_{N-2}, \psi_{N-1}\}$$

(2.5)

and

$$\Phi = \{\varphi_0, \varphi_1, \varphi_2, ..., \varphi_i, ..., \varphi_{N-2}, \varphi_{N-1}\}.$$

(2.6)

If we sum up all the elements of  $\Psi$  and  $\Phi$  respectively using

$$\Psi_{sum} = \sum_{i=0}^{N-1} \psi_i \tag{2.7}$$

and

$$\Phi_{sum} = \sum_{i=0}^{N-1} \varphi_i. \tag{2.8}$$

Since targeting for the data processing for video signals, we assume that  $0 \leq \psi_i$ ,  $\varphi_i \leq 255$ ,  $\forall \psi_i \in \Psi$  and  $\forall \varphi_i \in \Phi$ . Based on the mathematical statistics, it is true that

$$\mathbb{N} > \mathbb{M} \quad if \ \Psi_{sum} > \Phi_{sum} \tag{2.9}$$

and vice versa, where  $\mathbb{N}$  denotes the number of elements that  $\psi_i > \varphi_i(i \in (0, N-1))$  and similarly  $\mathbb{M}$  denotes the number of elements that  $\varphi_i > \psi_i(i \in (0, N-1))$ . Thereby according to Equation 2.9, if the sum of set  $\Psi$  is larger than that of  $\Phi$ , based on the one-to-one correspondence the number of elements that  $\psi_i$  is smaller than  $\varphi_i$  is much less than the opposite case. In that case in order to calculate the SAD between  $\Psi$  and  $\Phi$ , the sum difference is firstly obtained by

$$\operatorname{Diff}_{sum} = \begin{cases} \Psi_{sum} - \Phi_{sum} & if \ \Psi_{sum} > \Phi_{sum} \\ \Phi_{sum} - \Psi_{sum} & otherwise. \end{cases}$$

(2.10)

Then the SAD is acquired through

$$SAD = \begin{cases} \text{Diff}_{sum} + \sum_{\varphi_i < \psi_i} 2(\psi_i - \varphi_i) & \text{if } \Psi_{sum} > \Phi_{sum} \\ \text{Diff}_{sum} + \sum_{\varphi_i > \psi_i} 2(\psi_i - \varphi_i) & \text{if } \Psi_{sum} < \Phi_{sum} \\ \sum_{i=0}^{N-1} |\psi_i - \varphi_i| & \text{if } \Psi_{sum} = \Phi_{sum} \end{cases}$$

(2.11)

From Equation 2.11, it is clear that based on the size relationship of the difference of sum, only the elements that have a opposite size relationship between two sets are involved to calculate the SAD. Moreover, this part of elements is the minority of the whole two sets.

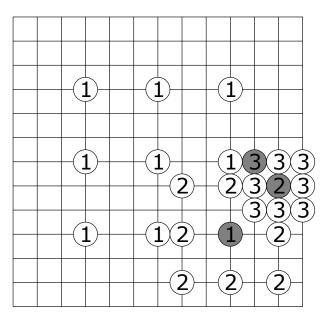

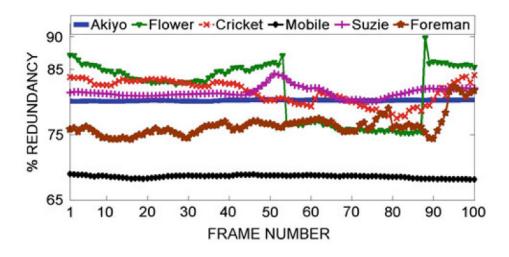

For the sake of having a more quantized understanding of the "minority", statistics on percentage of pixels per block in video signals accounted as minority has been collected [4]. The test is performed on six video sequences (Figure 2.2) frame by frame to observe the percentage of pixels per MB ( $16 \times 16$  applied) that can be accounted as "minority" to the SAD calculation. The experimental results shown in Figure 2.3 indicate that the "minority" is referred to  $10\% \sim 32\%$  pixels in these video sequences. It means when calculating the SAD only  $10\% \sim 32\%$  pixels are involved in Equation 2.11, hence the amount of computation of SADs can be reduced by a large scale.

Figure 2.2: 6 video sequences for test on statistics of "minority".

## 2.2.2 The New SAD architecture to accelerate the FS ME algorithm

Section 1.3 has given an introduction of Full Search algorithm for details. It is a ME search algorithm which can guarantee the best video quality and lowest bitrate but suffer from high complexity and poor encoding speed. Many fast ME search algorithms has been proposed in the literature [24, 27–43], for instance three-step search, diamond search, hexagonal patterns Search and so on (introduced in Section 1.3). They speed up the ME search process through reducing the number of search points and win a reduction on the encoder complexity and an improvement on the throughput at a cost of video quality

Figure 2.3: The percentage of pixel per MB that can be accounted as "minority" to the SAD calculation in six video sequences frame by frame [4].

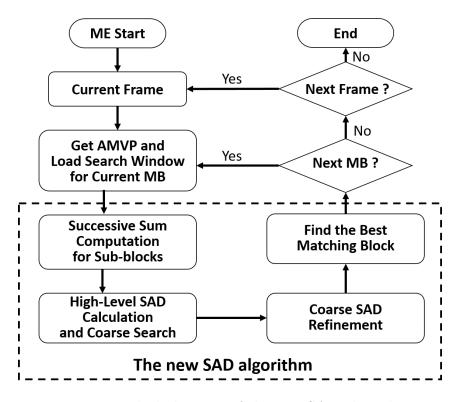

loss and bitrate increase. In this section a new SAD architecture to accelerate the FS algorithm is proposed based on the strategy described in Section 2.2.1 by removing the computing redundancies in the conventional SAD architecture. The block diagram of the new SAD algorithm for ME is illustrated in Figure 2.4.

Figure 2.4: Block diagram of the new SAD algorithm.

#### Fast Successive Sum Computation

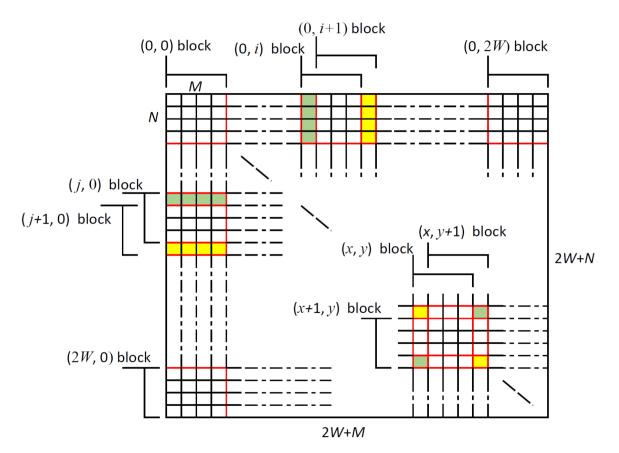

As for the FS algorithm, it is necessary to search every candidate block within the search window one by one. In the new SAD algorithm the sum of the block needs to be known first. Since between two consecutive candidate block most of the pixels are overlapped, performing sum operation separately for each blocks must bring about high redundancy of additions. Thus a fast successive sum computational strategy is explored to alleviate computational load, which is exhibited in Figure 2.5. One thing has to be pointed out

Figure 2.5: Successive SAD calculation.

that, according to Section 1.2 HEVC standard support flexible partitions from  $4 \times 4$  up to  $64 \times 64$  and also including the symmetrical block size such as  $8 \times 4$ ,  $16 \times 8$ ,  $32 \times 16$  and  $64 \times 32$  and their transformed block sizes. Therefore for a MB size  $N \times M$  with a search range of  $\pm W$ , the search window's dimension is  $(2W + N) \times (2W + M)$ . In order to find the best matching block, the total number of candidate block is  $(2W + 1)^2$ . As shown in Figure 2.5, when fast successive sum computation starts the first (at (0, 0) position) candidate block's sum is calculated first with a cost of  $(N \times M-1)$  additions. In the following for the candidate blocks in the first row, the sum of the latter block can be obtained by using the sum of the former block plus the pixels of the last column of current block (highlighted by

the yellow strip) and minus the pixels of the first column of the former block(highlighted by the green strip) as shown in Figure 2.5. For instance let  $Sum_{(0,i)}$  and  $Sum_{(0,i+1)}$  denote the sum of the (0, i) and (0, i + 1) block respectively,  $Sum_{(0,i+1)}$  is calculated using

$$Sum_{(0,i+1)} = Sum_{(0,i)} + \sum_{s=0}^{N-1} SW(s, i+M) - \sum_{s=0}^{N-1} SW(s, i),$$

(2.12)

where SW(s, i) is the pixel intensity at point (s, i). Correspondingly for the candidate blocks in the first column, its sum is acquired by

$$Sum_{(j+1,0)} = Sum_{(j,0)} + \sum_{s=0}^{M-1} SW(j+N,s) - \sum_{s=0}^{M-1} SW(j,s).$$

(2.13)

As a result, the number of operations to compute the sum of candidate blocks in the first row and column except the (0, 0) block is 2(N+1) and 2(M+1) additions (or subtractions) respectively. Then as well for the rest candidate blocks, the sum is obtained based on the sum of top, left and top-left neighboring blocks. As shown in Figure 2.5, the sum of block (x + 1, y + 1) is given by

$$Sum_{(x+1,y+1)} = Sum_{(x,y+1)} + Sum_{(x+1,y)} - Sum_{(x,y)} + SW(x,y) - SW(x+M,y) - SW(x,y+N) + SW(x+M,y+N).$$

(2.14)

Apparently Equation 2.14 only spend 6 additions (or subtractions) on computing sum of each candidate block not belonging to first row or column. Therefore the total number of operations to calculate the sum of all candidate blocks within the search window using fast successive sum strategy, denoted as  $\Gamma_{\text{fast}}$ , is

$$\Gamma_{\text{fast}} = (N \times M - 1) + 2W \times [2(N+1) + 2(M+1)] + (2W)^2 \times 6.$$

(2.15)

Meanwhile the total number of operations to calculate the sum of every candidate block separately in the original FS algorithm turns out to be

$$\Gamma_{\rm org} = (2W+1)^2 \times (N \times M - 1).$$

(2.16)

Taking a real case as an example, in HEVC standard the CTU's size is  $64 \times 64$  and search range is typical of  $\pm 64$ , hence

$$\Gamma_{\text{fast}} = (64 \times 64 - 1) + 2 \times 64 \times [2 \times (64 + 1) + 2 \times (64 + 1)] + (2 \times 64)^2 \times 6$$

= 135679 (2.17)

and

$$\Gamma_{\rm org} = (2 \times 64 + 1)^2 \times (64 \times 64 - 1) = 68144895.$$

(2.18)

Furthermore it is easy to find that the computational savings is  $\frac{68144895 - 135679}{68144895} \times 100\% = 99.8\%$ .

#### High Level SAD Calculation and Coarse Search

In the new SAD algorithm, for the purpose of further improving the search efficiency a coarse search will be applied initially. Since most of the ME modules in the video encoding system support symmetric block size, Equation 2.3 for a MB of size  $N \times M$  has to be rewrote as

$$SAD(MV_x, MV_y) = \sum_{i=u}^{u+N-1} \sum_{i=v}^{v+M-1} [f(i, j, t) - f(i + MV_x, j + MV_y, t - 1)].$$

(2.19)

Figure 2.6: An example for the sub-blocks.

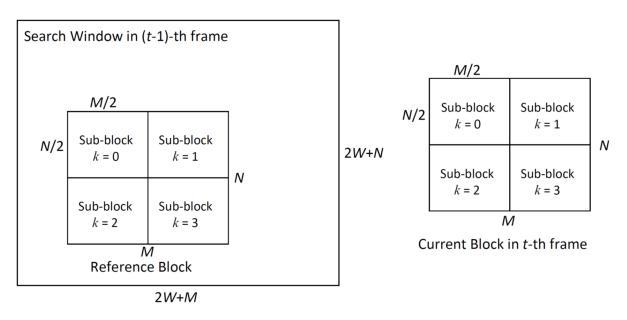

In order to perform the coarse search, both of the current MB and reference MB are firstly divided into 4 sub-blocks respectively thus each of  $(N/2) \times (M/2)$ , denoted as  $f_k(i, j, t)$  and  $f_k(i + MV_x, j + MV_y, t - 1)$  ( $k \in [0,3]$ ), which is illustrated in Figure 2.6. Then as indicated in Figure 2.4 the sum of each sub-block of the current MB and all the reference MB inside the search window is obtained through

$$Sum(i,j,t)_k = \sum_{i=0}^{N/2-1} \sum_{j=0}^{M/2-1} f(i,j,t)_k$$

(2.20)

and

$$Sum(i + MV_x, j + MV_y, t - 1)_k = \sum_{i=0}^{N/2-1} \sum_{j=0}^{M/2-1} f(i + MV_x, j + MV_y, t - 1)_k$$

(2.21)

respectively, where  $Sum(i + MV_x, j + MV_y, t - 1)_k$ 's computation resorts to the fast successive sum module. In the next the high level absolute difference between the two k-th current and reference sub-blocks, denoted as  $CSAD(i + MV_x, j + MV_y)_k$  (Coarse Sum of Absolute Difference), can be calculated by

$$CSAD(i + MV_x, j + MV_y)_k = |Sum(i, j, t)_k - Sum(i + MV_x, j + MV_y, t - 1)_k|.$$

(2.22)

Consequently, the coarse sum of absolute difference between the current block and reference block is obtained using

$$CSAD(i + MV_x, j + MV_y) = \sum_{k=0}^{3} CSAD(i + MV_x, j + MV_y)_k.$$

(2.23)

where  $(MV_x, MV_y)$  is a displacement within the search window, thus  $(-W, -W) \leq (MV_x, MV_y) \leq (+W, +W)$ .

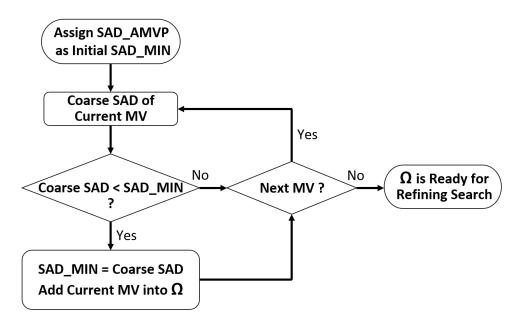

Let's assign the SAD result at the start point, namely AMVP, to  $SAD_{min}$  as its initial value, the coarse search is conducted in the way that if  $CSAD(i + MV_x, j + MV_y) < SAD_{min}$  the current motion vector  $(MV_x, MV_y)$  is added to the MV set,  $\Omega$ , and the  $SAD_{min}$  is updated to the newest minimum value, or current displacement is discarded. After coarse search is finished, the MVs stored in the  $\Omega$  will be used in the final best matching block search. The block diagram of coarse search is shown in Figure 2.7. This process helps to exclude a number of impossible candidates which can alleviate the workload of refining search in the next stage and save the computational cost.

#### **Coarse SAD Refinement**

When finishing coarse search, it is ready to carry out the refinement of the coarse SAD using the positions with  $MV \in \Omega$ . Grounded on the introduction in Section 2.2.1, the refinement can be fulfilled basing on the size relationship between  $Sum(i, j, t)_k$  and  $Sum(i + MV_x, j + MV_y, t - 1)_k$  and the "minority" pixels which have a opposite size relationship to their block size relationship. So the SAD between the two k-th corresponding current and reference sub-blocks, being  $SAD_k(i + MV_x, j + MV_y)$  can be expressed as:

Figure 2.7: Block diagram of coarse search.

If

$$Sum(i, j, t)_k > Sum(i + MV_x, j + MV_y, t - 1)_k$$

:

$SAD(i + MV_x, j + MV_y)_k = CSAD(i + MV_x, j + MV_y)_k$

$+ \sum_{\Lambda} 2 \times [f(i + MV_x, j + MV_y, t - 1) - f(i, j, t)]$

(2.24)

where  $\Lambda$  refers to a set containing all pixels that  $f(i, j, t) < f(i + MV_x, j + MV_y, t - 1)$ within the two k-th sub-blocks.

If

$$Sum(i, j, t)_k < Sum(i + MV_x, j + MV_y, t - 1)_k$$

:

$SAD(i + MV_x, j + MV_y)_k = CSAD(i + MV_x, j + MV_y)_k$

$+ \sum_{\Lambda'} 2 \times [f(i, j, t) - f(i + MV_x, j + MV_y, t - 1)]$

(2.25)

where  $\Lambda'$  refers to a set containing all pixels that  $f(i, j, t) > f(i + MV_x, j + MV_y, t - 1)$ within the two k-th sub-blocks.

If

$$Sum(i, j, t)_k = Sum(i + MV_x, j + MV_y, t - 1)_k$$

:

$$SAD(i+MV_x, j+MV_y)_k = \sum_{i=u}^{u+N/2-1} \sum_{i=v}^{v+M/2-1} |f(i, j, t) - f(i+MV_x, j+MV_y, t-1)|.$$

(2.26)

And finally the distortion between the current and reference block, denoted as SAD(i +

$MV_x, j + MV_y$ , is obtained by

$$SAD(i + MV_x, j + MV_y) = \sum_{k=0}^{3} SAD(i + MV_x, j + MV_y)_k.$$

(2.27)

From Equation 2.24 and 2.25, it can observed that the SAD refinement only involves the minority pixels (discussed in Section 2.2.1) which is just a small proportion of the total amount of pixels in a MB. Therefore, it can be expected that a large scale of the computing load in ME process will be alleviated.

(a) Four People, 1280x720, 60fps, (b) Basketball Drive, 1920x1080, (c) Park Scene, 1920x1080, 24fps, Class E 50fps, Class B Class B

(d) Traffic, 2560x1600, 30fps, Class A

(e) Ready steady go, 3840x2160, 120fps, 4K Test Sequence

Figure 2.8: HD video sequences for test used in the simulation.

## 2.2.3 Rate-Distortion Performance Evaluation with HM Test Model

The proposed new SAD computing algorithm for Full Search ME algorithm are implemented, verified and tested in HEVC Test Model (HM16.2). The simulations are performed under JCT-VC common conditions (Low Delay using P pictures with uniprediction) on the platform of Ubuntu OS with Intel Core i5 2.67GHz CPU and 8 Gigabyte main memory. In order to evaluate its performance, several high definition standard video sequences for test from different classes are encoded using a prediction structure of Low Delay P picture (LDP) defined by Common Test Conditions (CTC). The LDP specifies

|         |             | Four Peo  | ple 1280     | $\times 720 @60$ | Hz           |         |              |

|---------|-------------|-----------|--------------|------------------|--------------|---------|--------------|

| QP      | Algorithm   | BitRa     | ite          | YUV-             | PSNR         | Encodi  | ng Time      |

| QI      | Algorithm   | kbps      | $\Delta(\%)$ | dB               | $\Delta(\%)$ | seconds | $\Delta(\%)$ |

| 37      | Full search | 862.7040  | _            | 36.4348          | _            | 4454.33 | _            |

| 57      | Proposed    | 864.5760  | 0.22%        | 36.4293          | -0.02%       | 1509.19 | -66.12%      |

| 32      | Full search | 1454.9280 | _            | 39.1425          | _            | 4422.22 | _            |

| 52      | Proposed    | 1458.6720 | 0.26%        | 39.1439          | 0.00%        | 1342.92 | -69.63%      |

| 27      | Full search | 2463.4080 | —            | 41.5813          | —            | 4471.51 | _            |

| 21      | Proposed    | 2468.9760 | 0.23%        | 41.5761          | -0.01%       | 1221.93 | -72.67%      |

| 22      | Full search | 4793.1360 | —            | 43.5971          | —            | 4478.89 | —            |

|         | Proposed    | 4795.6800 | 0.05%        | 43.5941          | -0.01%       | 1172.37 | -73.82%      |

| Average | Proposed    | _         | 0.19%        | _                | -0.01%       | _       | -70.56%      |

2 – A New SAD Computing Algorithm for Full Search Motion Estimation

Table 2.1: Simulation results using different QP parameters for test sequence of Four People.

|         | Basketball Drive 1920×1080@50Hz |            |                        |         |              |          |              |  |  |  |  |  |  |

|---------|---------------------------------|------------|------------------------|---------|--------------|----------|--------------|--|--|--|--|--|--|

| QP      | Algorithm                       | BitRat     | te                     | YUV-J   | PSNR         | Encodin  | g Time       |  |  |  |  |  |  |

| QI      | Algorithm                       | kbps       | $\Delta(\%)$           | dB      | $\Delta(\%)$ | seconds  | $\Delta(\%)$ |  |  |  |  |  |  |

| 37      | Full search                     | 1759.0400  | - 36.1091 $-$ 10061.71 |         | 10061.71     | —        |              |  |  |  |  |  |  |

| 57      | Proposed                        | 1789.5200  | 1.73%                  | 36.0666 | -0.12%       | 5623.51  | -44.11%      |  |  |  |  |  |  |

| 32      | Full search                     | 3248.8400  | —                      | 37.9569 | —            | 10015.84 | —            |  |  |  |  |  |  |

| 32      | Proposed                        | 3297.2000  | 1.49%                  | 37.9238 | -0.09%       | 5106.57  | -49.02%      |  |  |  |  |  |  |

| 27      | Full search                     | 6524.1200  | —                      | 39.5933 | —            | 10145.28 | —            |  |  |  |  |  |  |

| 21      | Proposed                        | 6606.0800  | 1.26%                  | 39.5816 | -0.03%       | 4627.32  | -54.39%      |  |  |  |  |  |  |

| 22      | Full search                     | 17836.1200 | —                      | 41.0429 | —            | 10249.15 | —            |  |  |  |  |  |  |

|         | Proposed                        | 17953.4400 | 0.66%                  | 41.0363 | -0.02%       | 4401.93  | -57.05%      |  |  |  |  |  |  |

| Average | Proposed                        | _          | 1.28%                  | _       | -0.06%       | _        | -51.14%      |  |  |  |  |  |  |

Table 2.2: Simulation results using different QP parameters for test sequence of Basketball Drive.

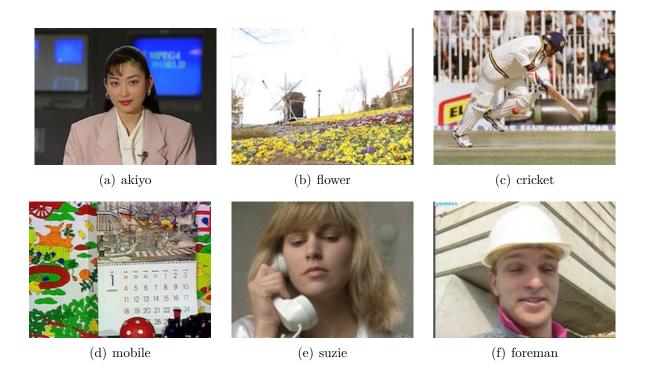

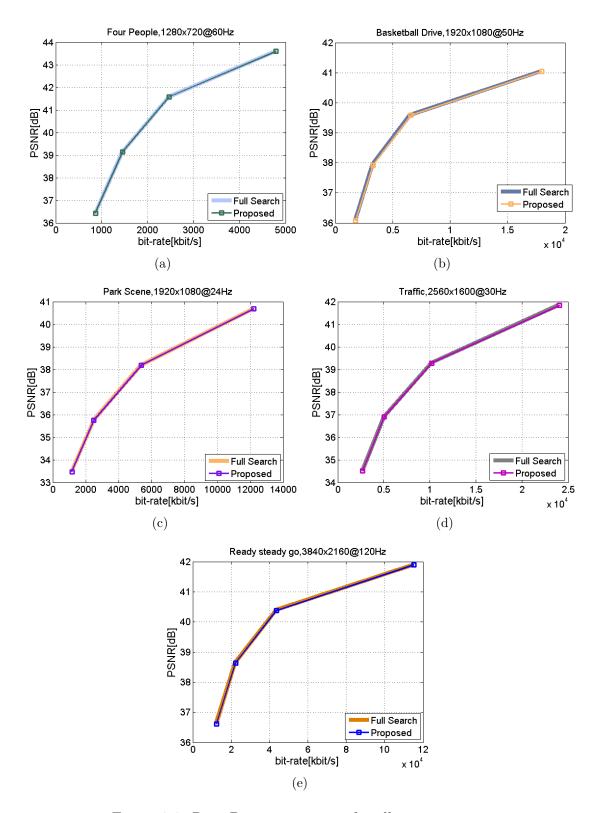

that video frames are configured to one I picture followed by 8 P pictures and reordering of pictures is not allowed and only past pictures are used for prediction [22,53–55]. Figure 2.8 lists all video sequences used in the test: (1) Four People(1280x720@60Hz, Class E), (2) Basketball Drive (1920x1080@50Hz, Class B), (3) Park Scene (1920x1080@24Hz, Class B), (4) Traffic (2560x1600@30Hz, Class A) and (5) Ready steady go (3840x2160@120Hz, 4K Test Sequence). The simulation run with 10 frames of each of the test sequences using 4 different Quantized Parameters (QP, 22, 27, 32 and 37)and a search range of  $\pm 64$ . In the test, data of BitRate, YUV-PSNR [52] and total encoding time are collected for performance comparison. The results , presented in Table 2.1-2.5, 2.2 clearly show

|    |             | Park Sce | ne 1920>     | ×1080@24 | Hz           |         |              |

|----|-------------|----------|--------------|----------|--------------|---------|--------------|

| OP | Algorithm   | BitRat   | te           | YUV-     | PSNR         | Encodin | g Time       |

| જા | Aigorithiin | kbps     | $\Delta(\%)$ | dB       | $\Delta(\%)$ | seconds | $\Delta(\%)$ |

0.28%

0.25%

0.48%

\_\_\_\_

0.48%

0.37%

1160.9664

1164.2112

2500.8768

2507.0208

5358.2592

5383.8528

12178.6368

12237.6768

\_

33.4954

33.4719

35.7674

35.7466

38.1899

38.1773

40.6841

40.6765

\_

-0.07%

-0.06%

-0.03%

-0.02%

-0.04%

10053.54

6185.51

10001.12

5674.58

10138.20

5244.51

10268.81

5062.84

\_

-38.47%

-43.26%

-48.27%

-50.70%

-45.18%

Full search

Full search

Full search

Full search

Proposed

Proposed

Proposed

Proposed

Proposed

37

32

27

22

Average

2 – A New SAD Computing Algorithm for Full Search Motion Estimation

Table 2.3: Simulation results using different QP parameters for test sequence of Park Scene.

|         |             | Traffic    | $2560 \times 16$ | 500 @30Hz | Z            |          |              |

|---------|-------------|------------|------------------|-----------|--------------|----------|--------------|

| QP      | Algorithm   | BitRat     | te               | YUV-]     | PSNR         | Encodin  | g Time       |

|         | Algorithm   | kbps       | $\Delta(\%)$     | dB        | $\Delta(\%)$ | seconds  | $\Delta(\%)$ |

| 37      | Full search | 2679.7680  | —                | 34.5202   | —            | 20124.47 | —            |

| 51      | Proposed    | 2695.4880  | 0.59%            | 34.5096   | -0.03%       | 7866.48  | -60.91%      |

| 32      | Full search | 5021.1360  | —                | 36.9135   | _            | 20009.43 | —            |

| 02      | Proposed    | 5054.4960  | 0.66%            | 36.8998   | -0.04%       | 6907.14  | -65.48%      |

| 27      | Full search | 10146.9600 | —                | 39.2883   | —            | 20249.14 | —            |

| 21      | Proposed    | 10203.9600 | 0.56%            | 39.2756   | -0.03%       | 6273.78  | -69.02%      |

| 22      | Full search | 23945.0400 | —                | 41.8368   | _            | 20433.65 | _            |

|         | Proposed    | 24091.3440 | 0.61%            | 41.8290   | -0.02%       | 5964.33  | -70.81%      |

| Average | Proposed    | _          | 0.61%            | —         | -0.03%       | _        | -66.55%      |

Table 2.4: Simulation results using different QP parameters for test sequence of Traffic.

that compared to the ME with original FS algorithm, the proposed one can accomplish a reduction on the total encoding time on average by at least 45.18% or 70.56% in the best case, with only a minor increase on bit-rate and a negligible PSNR loss. Furthermore there is a more clear illustration on the Rate-Distortion performance comparison exhibited in Figure 2.9, where the curves of PSNR v.s. bit-rate for all test sequences are almost totally coincided. It means the proposed new SAD algorithm achieves a significant reduction on computational load but with a negligible performance loss.

|         |             | Ready Steady | 7 Go 384     | 0×2160 @ | 120Hz        |          |              |

|---------|-------------|--------------|--------------|----------|--------------|----------|--------------|

| QP      | Algorithm   | BitRat       | e            | YUV-I    | PSNR         | Encodin  | g Time       |

| Q1      | Algorithm   | kbps         | $\Delta(\%)$ | dB       | $\Delta(\%)$ | seconds  | $\Delta(\%)$ |

| 37      | Full search | 12231.7440   | —            | 36.6316  | —            | 41151.41 | —            |

| 51      | Proposed    | 12291.0720   | 0.49%        | 36.6056  | -0.07%       | 19285.25 | -53.14%      |

| 32      | Full search | 22159.2960   | —            | 38.6549  | —            | 40398.51 | —            |

| 02      | Proposed    | 22270.5600   | 0.50%        | 38.6410  | -0.04%       | 17737.61 | -56.09%      |

| 27      | Full search | 43401.3120   | _            | 40.3937  | _            | 40853.98 | —            |

| 21      | Proposed    | 43619.5200   | 0.50%        | 40.3836  | -0.03%       | 16576.12 | -59.43%      |

| 22      | Full search | 114894.3360  | —            | 41.9054  | —            | 41265.31 | —            |

|         | Proposed    | 115226.7840  | 0.29%        | 41.8967  | -0.02%       | 16357.89 | -60.36%      |

| Average | Proposed    | _            | 0.44%        | —        | -0.04%       | —        | -57.25%      |

Table 2.5: Simulation results using different QP parameters for test sequence of Ready Steady Go.

### 2.3 Hardware Implementation

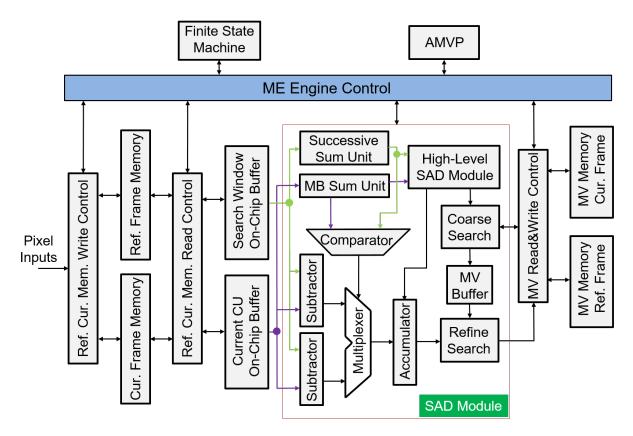

As discussed in the last section, the new SAD algorithm consists of two parts: high-level SAD coarse search and coarse SAD refinement and final search. The high-level SAD computation utilizes the fast successive sum strategy. And the sum results of the sub-blocks obtained in the high-level SAD stage can be reused for the size relationship between sub-blocks in the SAD refinement. The hardware implementation of whole ME module is depicted in Figure 2.10.

#### ME Engine Control Unit

The ME Engine control is mainly responsible for the control signals generation for all the other function units. Initially after the power-on reset signal switches on the encoding system, it firstly transmits a enable signal and a corresponding address to Memory Read&Write Unit to load the first frame of pixels for reference and the first LCU ( $64 \times 64$ ) for encoding. In the next it needs to arrange the coding loop order for all the CUs of current CTU which is normally from CU64×64, CU64×32, CU32×64... till to CU16×8, CU8×8. Then after the AMVP unit determines the search start point, the important task of ME Engine control is to configure the search window and guarantee its border lies inside the reference frame according to the AMVP's coordinate and search range, and then load the pixels of search window for current CU from memory bank to the on-chip buffer. In the end, when the motion estimation of current CTU is finished it will guide the MV Read&Write Control Unit to store the final optimal MVs.

Figure 2.9: Rate-Distortion curves for all test sequences.

Figure 2.10: Hardware architecture of proposed SAD algorithm.

#### Finite State Machine

For the sake of managing all the functional units to work in orderly and efficiently, the Finite State Machine is to control the state switching of the whole system between memory reading and writing, matching block searching, CU encoding looping and CU mode decision. The ME Engine Control Unit arranges different enable signals for different function unit according to the current state.

#### AMVP

When the encoding process for a new CU starts, the AMVP unit will check and read the available spatial and temporal motion vector predictors from MV memory and determine the best MV as the start search point. While the search window is decided using the AMVP by the ME Engine Control unit.

#### Memory Read Write Control

Here in the proposed architecture, either the current and reference frame memory or MV memory for current and reference frame are implemented in a ping-pong mode to save

the off-chip memory size and improve the memory reading and writing efficiency. Hence there are two separate memory banks, denoting as Bank#0 and Bank#1. When encoding the current frame if Bank#0 stores pixels for the past reference frame and Bank#1 holds the data from current frame, then when encoding the next frame the pixels stored in the Bank#1 will be used as the reference and meantime pixels of the new frame to be encoded will be loaded into Bank#0, and so on and so forth. Meanwhile as for the MV memory for current and reference frame the same mode is also applied. The functionality of the this working mechanism is fulfilled by the Memory Read Write Control unit.

#### SAD Module

As discussed in this chapter, the SAD module is the key unit in the top level architecture of ME structure. After the search window for current PU is finished loading, the MB Sum unit and Successive Sum unit will perform summing operation for the sub-blocks of current MB and all the candidate blocks respectively, meantime the coarse SAD between sub-blocks of current MB and reference MB is also generated. Based on these coarse SADs, impossible candidates are excluded by the coarse search process and motion vectors of valid candidates are pushed into in the MV buffers for the refining search. With the sum results of sub-blocks, a comparator generates a select signal for the multiplexer which together with two subtractors are responsible for the coarse SAD refinement by adding up the high level SAD and difference between corresponding pixels produced from Multiplexer. At last the Refine Search module will generate the best MV for the current PU from candidates stored in MV buffer based on the refined SADs.

### 2.4 Summary

A new SAD computing architecture is developed to alleviate the computational load of full search ME algorithm. Simulating in the HM test model using several standard FHD or UHD test sequences, the proposed architecture can reduce up to 70% of the computations with respect to the original FS algorithm with an imperceptible bit-rate increase and PSNR loss. This architecture is applicable to the video encoding system which pursuits highest video quality.

# Chapter 3

# An Enhanced TZ (Test Zone) Search Algorithm for Fast Motion Estimation of HEVC

Generally speaking, in the block based video coding system there are two categories of ME algorithms: Full Search and Fast Search [56–58]. The former one searches all the possible candidates within the pre-determined search window, which can guarantee a highest output video quality and a smallest amount of bit-rate. But its complexity usually is very high and the scale of computations is huge. On the other hand, the fast search algorithms, such as Three-Step Search, Diamond Search and so on (discussed in Section 1.3), reduce the complexity and computations by partially searching of candidates in the search window. Consequently, its throughput is incremented but with a cost of video quality loss and bit-rate increase. Along with the prevalence of high definition videos, full search algorithm is rarely utilized in encoding applications because of extremely high complexity. Whereas fast search algorithms are widely used. Since currently some of the best fast search algorithms can reach a comparable good video quality as full search algorithm is one of them.

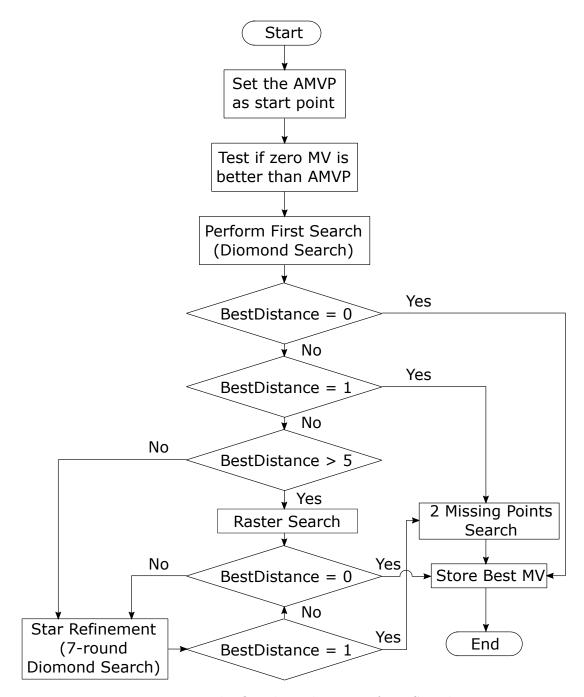

## 3.1 Introduction of TZ Search Algorithm