## POLITECNICO DI TORINO SCUOLA DI DOTTORATO Dottorato in INGEGNERIA INFORMATICA E DEI SISTEMI – XXVIII ciclo

Tesi di Dottorato

# Fault Tolerant Electronic System Design

Boyang Du

**Tutore** Prof. Luca Sterpone **Coordinatore del corso di dottorato** Prof. Matteo Sonza Reorda

${\rm Maggio}\ 2016$

# Summary

Due to technology scaling, which means reduced transistor size, higher density, lower voltage and more aggressive clock frequency, VLSI devices may become more sensitive against soft errors. Especially for those devices used in safety- and mission-critical applications, dependability and reliability are becoming increasingly important constraints during the development of system on/around them. Other phenomena (e.g., aging and wear-out effects) also have negative impacts on reliability of modern circuits. Recent researches show that even at sea level, radiation particles can still induce soft errors in electronic systems.

## Online error detection and Board-level functional test in processor-based system

On one hand, processor-based system are commonly used in a wide variety of applications, including safety-critical and high availability missions, e.g., in the automotive, biomedical and aerospace domains. In these fields, an error may produce catastrophic consequences. Thus, dependability is a primary target that must be achieved taking into account tight constraints in terms of cost, performance, power and time to market. Several solutions exist, acting either on hardware or software: however, they all have to face the high efforts required for designing, manufacturing, testing and qualifying processor-based systems. While standards and regulations (e.g., ISO-26262, DO-254, IEC-61508) clearly specify the targets to be achieved and the methods to prove their achievement. In this scenario, techniques working at system level (i.e., without changing the technology and the processor) are particularly attracting, especially if they can effectively meet dependability needs more efficiently without changes in the existing hardware and software.

Approaches to detect soft errors in processor-based systems are traditionally divided in techniques that deal with faults affecting the data and faults affecting the execution flow of the software application. For the faults affecting the data, to detect and eventually correct such errors in the data, i.e. *Data Error*, either detection and correction strategies can be applied to the data memory itself, such as the *Error Correction Coding* (ECC), or the software or hardware (or both) needs to be modified so that certain redundancy could be applied, for example, variable duplication plus the instructions for checking data in the software. While for the faults affecting the execution flow, although part of them are overlapped with the faults affecting the data, for example, the faults corrupting variable used in branch instruction, the rest them are difficult to handle, such as the faults affecting the registers used in the pipeline of the processor. For mitigating soft errors affecting the execution flow, i.e. Control Flow Error (CFE), traditional Triple Modular Redundancy (TMR) could be an effective solution when it is applied at gate level of the processor, in case the netlist of the target processor is available, which is usually not the case when *Commercial Off The Shelf* (COTS) component is used, let alone the cost it introduces for verification of compliance to the standards and regulations as mentioned above, since the processor's hardware is modified. Avoiding the huge hardware overhead caused by TMR if applied at system level (>200%), solutions have been proposed to firstly detect the CFE either with extra instructions inserted into software or an extra component monitoring the processor (e.g. a watchdog processor); and then correction of CFE could be done either simply reset the processor or replying on further software techniques such as checkpoint rollback depending on the nature and requirement of workload for the processor. This work mainly focuses on online test for detecting CFEs in the first part, a hybrid solution is discussed afterwards. Since there already exists debug interface in many processors (standalone or cores), assisting designer for debugging hardware/software at different stages, which can provide information of the software running on the processor in a non-intrusive way (e.g., the debug interface in LEON3 processor), an external hardware module, namely CFC module, was proposed to be attached to the processor through debug/trace interface, to extract the information and monitor the execution of the software on the processor.

With the debug interface in the processor as LEON3, the CFC module is able to extract executed instructions and the corresponding Program Counter (PC) value. Meanwhile the software running on the processor can be divided into *Basic Blocks* (BBs), in which all the instruction will be executed sequentially without branch or jump instructions. The main idea behind the CFC module is to calculate the signature of each BB executed by the processor and compare it with the signature previously stored in the table, namely CFC Signature Table in side the CFC module.

The CFC module is greatly smaller than the processor itself in terms of area consumption. With data from simulation-based fault injection campaign on both LEON3 and miniMIPS processor with several benchmark applications, the proposed CFC module proved to be a non-intrusive, effective way for detecting CFEs without modifying the software and processor implementation.

As the CFC module focuses only on the CFEs, a hybrid technique was proposed with dual control flow monitoring to detect soft errors, together with a software-based technique targeting on Data Errors.

The hybrid technique consists of an external *Hardware Monitor* (HM) that also attaches to the debug/trace interface of the processor for extracting the same information as in CFC module. However, the HM also monitors the communication between the processor and the memory on the system bus. By extracting the processor's reading address sent to memory component, and the data it retrieves, the HM is able to get the input stream of the instructions fetched by the processor; and the information from the debug/trace interface provides the output stream of the instructions executed by the processor. Inside the HM, the input and output instruction streams are carefully synchronized and compared to detect occurrence of CFE, and a part of Data Error is also covered in this way, and in order to achieve full coverage including the Data Errors, a software-based technique, combining "Dataflow duplication" and "inverted branches" is applied.

The fault injection campaign, emulating effects of *Single Event Upset* and *Single Event Transient*, was carried out, and the results verified the high fault coverage the hybrid technique can achieve, with a small hardware overhead.

To further exploit the existing debug interface in the processor for testing purpose, *Printed Circuit Board Assembly* (PCBA) *Power-On Self-Test* (POST) was investigated for finding feasible solution to increase processor's observability. POST plays an important role in many systems, since it may detect faults arising during the life time of the product, thus increasing its dependability. POST may use different solutions, which should match the constraints of the environment the system is deployed in.

Functional test represents a commonly adopted solution for POST. More in general, functional test is adopted in many scenarios, at the device, board and system levels. In some of them it complements other test steps, performed resorting to *Design For Testability* (DFT). The importance of this kind of defects is significantly increasing in the last years, especially since they are considered one of the major contributors for *Non Failure Found* (NFF), thus raising the interest for any solution able to improve the achievable defect coverage.

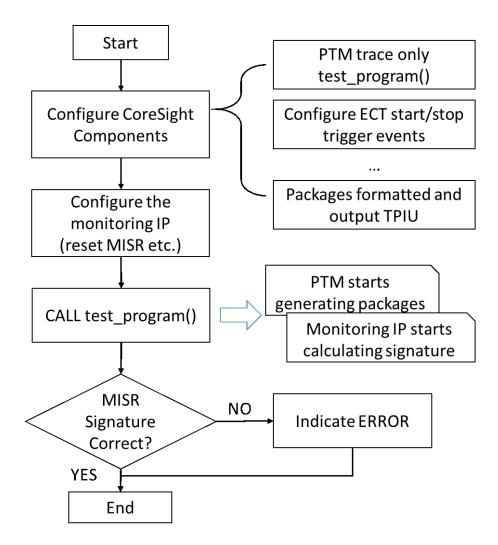

A Monitoring IP was proposed which can be mapped to a FPGA device on board, which is able to be configured to connect to the debug interface of the target processor on board (test for other devices on board is out scope of this work, and can resort other specific methods). For concept evaluation, the CoreSight Trace Infrastructure available in processors from ARM was used, which is able to provide various information related to execution of the software, such as target address of a branch instruction and information of an exception. A Monitoring IP was developed on Zynq device from Xilinx, which equips a single chip integrated an ARM Coretex-A9 dual core processor and FPGA device. By a demo project implement on Zynq device with the Monitoring IP validated that it is feasible for such an external module resides in the FPGA, monitoring the processor while a test program is being executed, to increase the observability of the processor for POST.

Since lacking of detailed information about the structure of the ARM processor clearly prevents us from computing the increase in defect coverage that can be achieved using our solution, fault simulation experiments were executed on a MIPS-like processor for which the model is available. The same information produced by the ARM debug interface is extracted from this processor during the execution of the test, and the achieved fault coverage is computed. Results show the effectiveness of the proposed solution. Interestingly, they demonstrate that the stuck-at fault coverage that can be achieved is comparable with the one reachable using a corresponding test program in a scenario where all the processor outputs can be continuously monitored.

## Single Event Effects analysis and mitigation on Field Programmable Gate Array

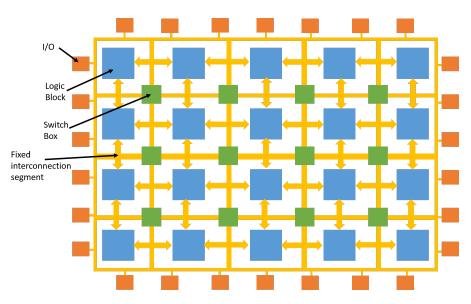

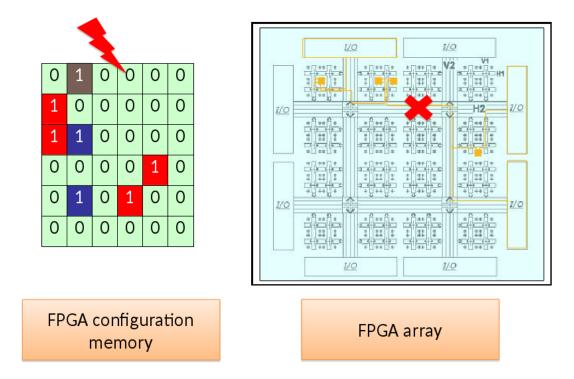

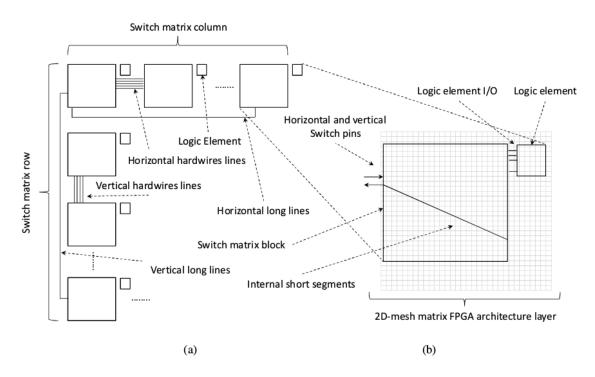

On the other hand, *Field Programmable Gate Array* (FPGA) devices are becoming more and more attractive, also in safety- and mission-critical applications due to the high performance, low power consumption and the flexibility for reconfiguration they provide. Two types of FPGAs are commonly used, based on their configuration memory cell technology, i.e., SRAM-based and Flash-based FPGA. Besides the hardware resources for I/O, clock managing and on-chip memory etc., FPGA device can be modeled as an matrix of Logic Block and Switch Box connected by interconnection segments of various lengths. The Logic Block contains configuration logic resources such as Look Up Table (LUT), Multiplexes and Flip-Flops for implementing different user logic functions. While the Switch Box (or Switch Matrix) contains programmable interconnection segments user can configure as active or inactive to form different interconnection networks among Logic Blocks and other hardware resources for routing of the implemented design. And the configuration memory of FPGA device holds the configuration data of all the resources to be used in the design, including the Logic Blocks and Switch Boxes. When the FPGA device is used in harsh environment, such as in space and avionic applications, fault tolerant strategies must be applied as highly charged particles could induce Single Event Effects (SEEs) in configuration memory and/or user logic leading to system misbehavior.

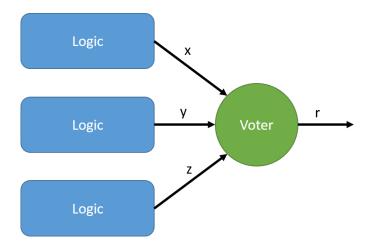

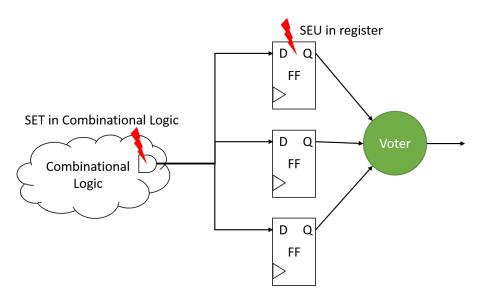

For SRAM-based FPGA, since SRAM cells are highly susceptible to radiation induced effects and one bit corruption inside the configuration memory may leads to drastic change in the logic mapped on the FPGA, certain fault tolerant strategy needs to be applied when SRAM-based FPGA is used especially in safety- and mission-critical applications. Traditional techniques include Triple Modular Redundancy (TMR) and configuration memory scrubbing.

The TMR technique can be carried out at different levels, for example, at gate level, logic path level, entity level and even system level. However as the name suggested, TMR introduces large resource overhead, including area and power consumption. So to trade off the reliability and overhead, different variations were proposed, for example, TMR on selective gates, TMR with approximate logic etc.

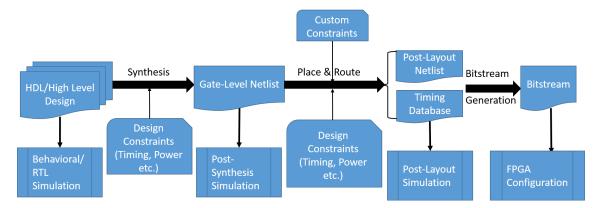

In this part of the work, the Verification and Error Rate Integrated (VERI-Place) tool was used for error rate prediction and mitigation on SRAM-based FPGA. The VERI-Place tool takes files from standard commercial flow (from Xilinx) as inputs, and generates report including information regarding the sensitive part of the target design and error rate when Single Event Upset (SEU) accumulated in the configuration memory. Furthermore, the tool acts on the Place & Route step of the design, without introduce extra hardware overhead into the design, to improve the reliability of the circuit to be mapped on the FPGA.

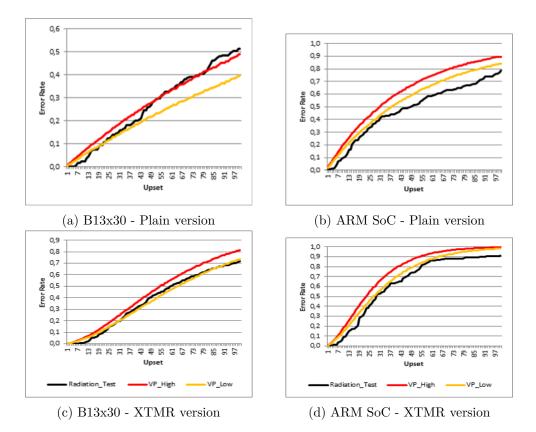

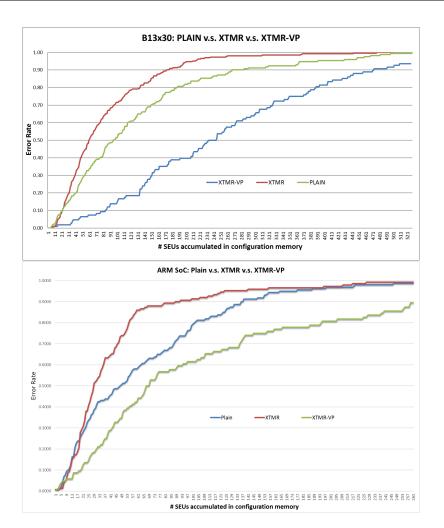

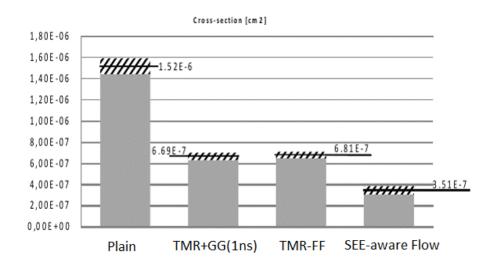

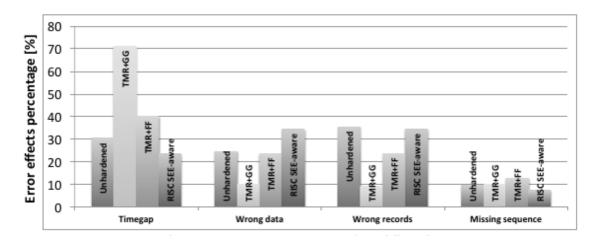

The accuracy of the error rate prediction and effectiveness of the SEU mitigation made by the VERI-Place has been verified in simulation analysis and two radiation experiments with two benchmark circuits, including an ARM-based SoC, in two different facilities with different radiation profiles. The design version generated by the VERI-Place tool based on the version with *Xilinx TMR* (XTMR) applied is able to achieve an improvement of reliability by two orders in terms of *Silent Data Corrupt* (SDC) cross-section.

For Flash-based FPGA, even though their configuration memory made of non-volatile flash cells that are almost immune to SEU, the floating-gate-based switches and the Flipflops in the configurable logic can still suffer from SEEs induced by radiation particles.

Regarding Flash-based FPGAs, two distinct effects may be identified. The former occurs inside of the floating gate switch: the pass transistor and floating gate transistors usually constitute the floating gate switch. The second occurs when a high charged particle hits a sensitive node of a logic cell belonging to the FPGA's configuration tile. The generated pulse may propagate through the logic depending on the FPGA tile configuration. If the tile is configured to implement a latch, the pulse may turn directly into a SEU because of the feedback paths implemented by the tile logic configuration. Meanwhile if the tile is configured to implement a logic gate, the transient pulse is assumed to be propagated only if the voltage glitch generated by the particle hit on the struck node changes by more than  $V_{DD}/2$ . Once a SET is generated into the sensitive area of a logic gate it starts its propagation through the logic paths until a sequential element is reached. During its propagation through logic gates undergo to different electrical phenomena that affect the shape of the pulse modifying its voltage amplitude, the width and the speed along the traversed logic path.

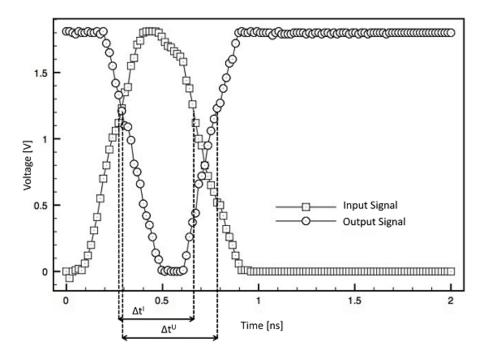

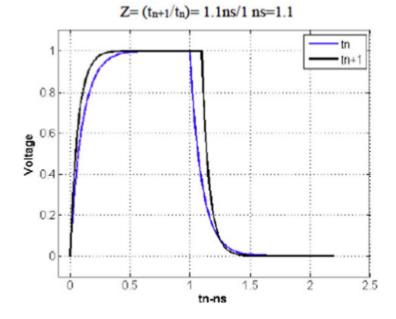

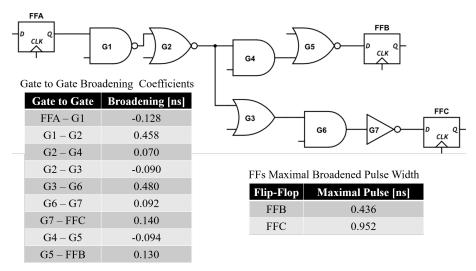

An analytical SET model was developed for accurately investigate the SET behavior when it propagates through the logic paths in the design. Depending on the type of gate and its input and output load, a SET pulse could be filtered or broadened when it traverses through the gate. The model has been verified with the data collected in the SET analysis experiment via electrical pulse injection carried out before.

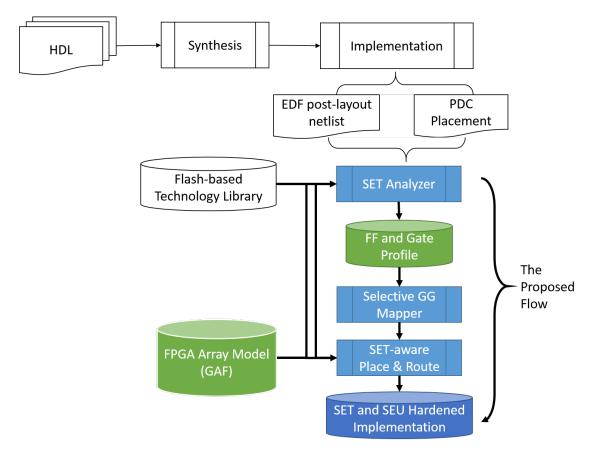

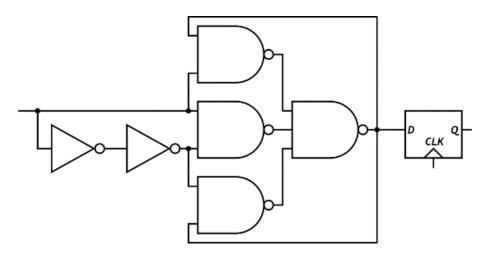

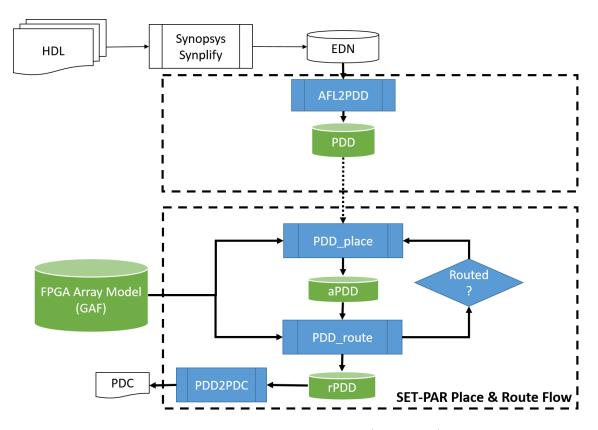

Furthermore, a SET-Analyzer (SETA) tool was used for analyzing the SEE sensitivity of several benchmark circuits including a RISC microprocessor from OpenCores. The SETA tool takes netlist and placement files generated from the commercial tool (Libero SoC in case of Microsemi FPGA), generates a set of transient pulses, and with the analytical SET model, it propagates the pulses along the logic paths in the design. SEE sensitivity information regarding the probability of SET pulses reaching a Flip-flop and eventually sampled is reported by the SETA tool. With this information, designer can determine which FFs are critical and sensitive, and need to be protected using techniques such as *Guard Gate* (GG) insertion as proposed. The GG is a configurable circuit macro that can be inserted at the input of a FF for filtering a user-defined length SET pulse. Depending on the output of SETA tool, designer can selectively choose to insert GG structures to the design.

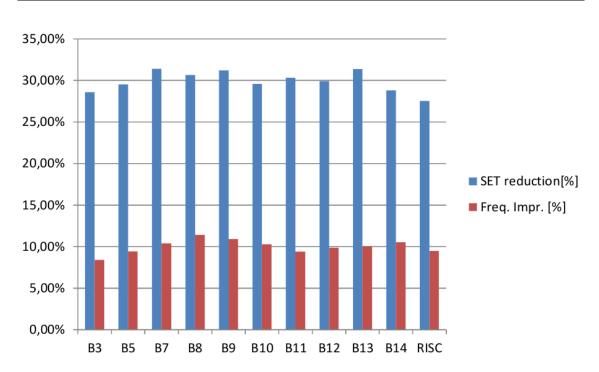

Finally, a SET-aware place and route tool (SET-PAR) was used to generate an improved version of the target design regarding SET sensitivity, by acting on the placement and routing resources optimization for SET filtering. The SET-PAR tries to place the gates with SET filtering effect close to each other and the gates with broadening effects far from each other to reduce the probability of a SET reaching and sampled by the FF, i.e. reducing the SET sensitivity of the target design, while respecting the timing constraints.

With all the models and tools mentioned above, a complete SEE analysis and mitigation flow for Flash-based FPGA was proposed. Since the flow takes the files from commercial tool as input and generates improved design as constraint files, it can be easily integrated into standard commercial toolchain, and with analysis of simulation experiments over several ITC99 benchmark circuits and a heavy-ion radiation experiment carried out on Microsemi ProASIC3 Flash-based FPGA with a RISC microprocessor, the propose flow has been proven to be accurate in the SEE sensitivity analysis and effective in SEE mitigation without introducing extra hardware overhead and performance degradation.

# Acknowledgements

I would like to thank Prof. Luca Sterpone and Prof. Matteo Sonza Reorda for providing me the opportunity to pursue my research activity in the CAD group, and for their great support and generous help over the three pleasant years of PhD.

I also would like to thank all the people I had the chance to have collaboration with for the thing I have learned from them and the results we achieved together along the way, and also all my colleagues in the CAD group and all the people in the Lab3 for the pleasant time we spend together.

Finally, I would like to thank all my friends for the companion they provide me over the years starting from the very beginning when I came here in Italy, and all my families for the support and love they provide me generously and constantly.

# Contents

| Summary         | II   |

|-----------------|------|

| List of Figures | XI   |

| List of Tables  | XIII |

| Tes  | sting for SoC/SoPC by Exploiting Debugging Infrastructures                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inti | roduction                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.1  | Online test of Control Flow Error                                                                                                                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 1.1.1 Previously proposed techniques                                                                                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 1.1.2 Control Flow Checking module                                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.2  | A hybrid nonintrusive error detection technique                                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.3  | Print Circuit Board Assemblies Power-On Self-Test                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 1.3.1 Functional test for POST                                                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 1.3.2 Monitoring IP                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Onl  | ine Test of Control Flow Error                                                                                                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1  | Background                                                                                                                                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.2  | Control Flow Checking module                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 2.2.1 Architecture of the CFC module                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.3  | Experiment results with fault injection                                                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.3.1 Experiment setup                                                                                                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.3.2 Fault injection results                                                                                                                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Hyl  | orid Nonintrusive Error Detection Technique                                                                                                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1  | Background                                                                                                                                                 | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2  | Dual Control-Flow monitoring                                                                                                                               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.2.1 External hardware module                                                                                                                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 3.2.2 Data hardening technique                                                                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3  | Fault injection campaign                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | <ul> <li>Intr</li> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>Onl</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>Hyl</li> <li>3.1</li> <li>3.2</li> </ul> | 1.1.1       Previously proposed techniques         1.1.2       Control Flow Checking module         1.2       A hybrid nonintrusive error detection technique         1.3       Print Circuit Board Assemblies Power-On Self-Test         1.3.1       Functional test for POST         1.3.2       Monitoring IP         1.3.2       Monitoring IP         1.3.2       Control Flow Error         2.1       Background         2.2       Control Flow Checking module         2.2.1       Architecture of the CFC module         2.3       Experiment results with fault injection         2.3.1       Experiment setup         2.3.2       Fault injection results         3.1       Background         3.2       Dual Control-Flow monitoring         3.2.1       External hardware module         3.2.2       Data hardening technique |

| 4 | Pri  | ted Circuit Board Assembly Power-On Self-Test                             | 33 |

|---|------|---------------------------------------------------------------------------|----|

|   | 4.1  | Background                                                                | 34 |

|   |      | 4.1.1 CoreSight Architecture from ARM                                     | 35 |

|   | 4.2  | Monitoring IP                                                             | 36 |

|   | 4.3  | Fault coverage analysis                                                   | 41 |

|   |      |                                                                           |    |

| Π | A    | alysis and Mitigation of Single Event Effects on FPGAs                    | 43 |

| 5 | Inti |                                                                           | 45 |

|   | 5.1  | Single Event Effects on FPGAs                                             | 46 |

|   |      | 5.1.1 SEEs on SRAM-based FPGA                                             | 47 |

|   |      | 5.1.2 SEEs on Flash-based FPGA                                            | 48 |

| 6 | Sin  | le Event Effects in SRAM-based FPGA                                       | 51 |

|   | 6.1  | Background                                                                | 51 |

|   |      | 6.1.1 Techniques based on redundancy                                      | 52 |

|   |      | 6.1.2 Configuration memory scrubbing via Partial Reconfiguration          | 54 |

|   | 6.2  | 0                                                                         | 55 |

|   |      |                                                                           | 56 |

|   |      | 0 1                                                                       | 56 |

|   | 6.3  | 1 0                                                                       | 57 |

|   |      | 6.3.1 Radiation experiments with ARM-based SoC on SRAM-based FPGA         |    |

|   |      | 6.3.2 Radiation experiment with custom benchmark on SRAM-based FPGA       |    |

|   |      | 6.3.3 Experimental results and analysis                                   | 62 |

| 7 | Sin  | le Event Effects on Flash-based FPGA                                      | 67 |

|   | 7.1  | 0                                                                         | 67 |

|   |      |                                                                           | 68 |

|   |      | 7.1.2 Previous analysis and mitigation techniques for SEEs on Flash-based |    |

|   |      |                                                                           | 69 |

|   | 7.2  | 1 0                                                                       | 71 |

|   |      | J. J                                  | 72 |

|   |      |                                                                           | 74 |

|   |      |                                                                           | 75 |

|   |      |                                                                           | 77 |

|   |      | •                                                                         | 78 |

|   | 7.3  |                                                                           | 80 |

|   |      | 7.3.1 Radiation experiment on Microsemi Flash-based FPGA                  | 82 |

# List of Figures

| 2.1  | Architecture of a system adopting the proposed approach                | 10 |

|------|------------------------------------------------------------------------|----|

| 2.2  | CFC module architecture diagram                                        | 12 |

| 2.3  | Dynamic CFC module architecture diagram                                | 13 |

| 2.4  | CFC-ST update mechanism                                                | 13 |

| 3.1  | Hardware monitor observation points                                    | 23 |

| 3.2  | Internal architecture of the hardware monitor                          | 24 |

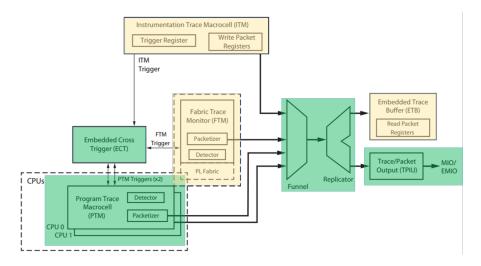

| 4.1  | CoreSight System Diagram in Zynq-7000[5]                               | 36 |

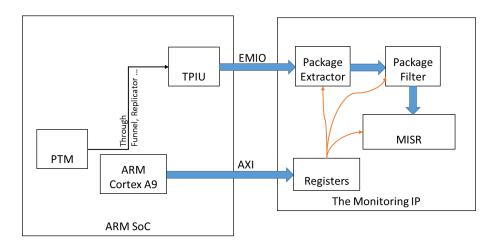

| 4.2  | Architecture of the Monitoring IP                                      | 38 |

| 4.3  | Format of the branch with exception package [5]                        | 39 |

| 4.4  | Workflow of the proposed technique                                     | 40 |

| 5.1  | FPGA general architecture                                              | 46 |

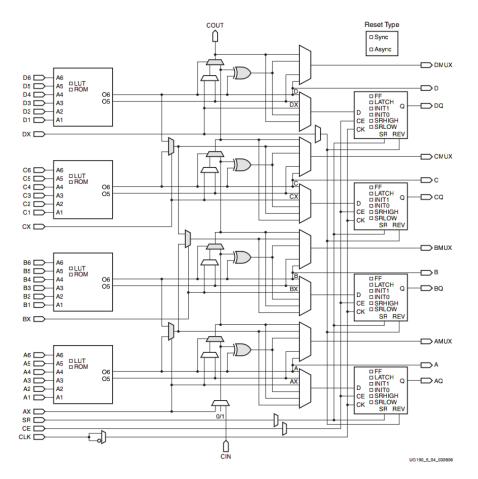

| 5.2  | Logic Block (SLICEL) diagram from Virtex-5 device of Xilinx [74]       | 47 |

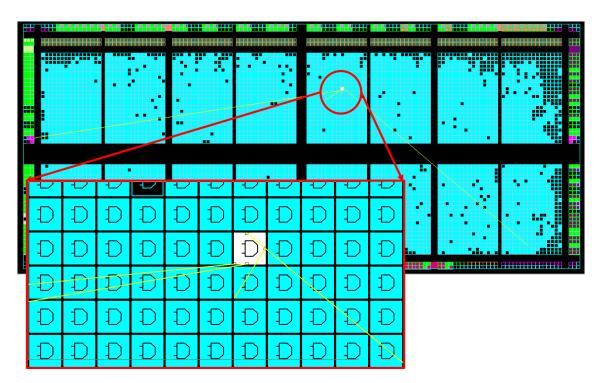

| 5.3  | A routed design mapped on ProASIC3 from Microsemi                      | 48 |

| 5.4  | Typical FPGA design flow                                               | 48 |

| 5.5  | A SEU in configuration memory corrupting interconnection               | 49 |

| 6.1  | General TMR architecture                                               | 52 |

| 6.2  | TMR applied at gate-level with registers triplicated                   | 53 |

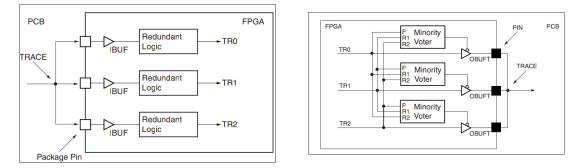

| 6.3  | Input and output triplication in XTMR [80]                             | 53 |

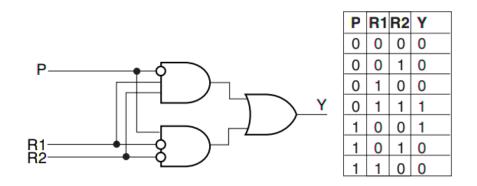

| 6.4  | XTMR minority voter implementation [80]                                | 53 |

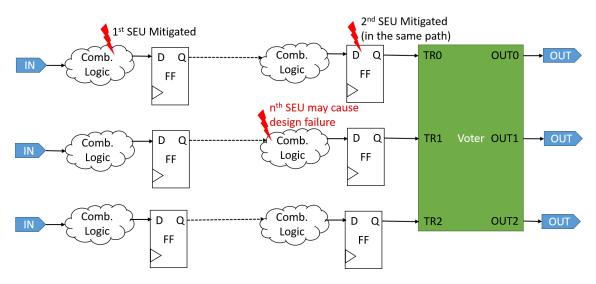

| 6.5  | Accumulated SEU in configuration memory corrupts design with XTMR      | 54 |

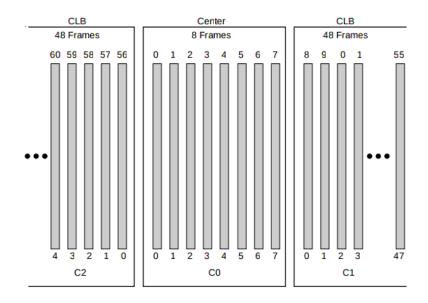

| 6.6  | Frames in Virtex-5 SRAM-based FPGA's configuration memory [81]         | 55 |

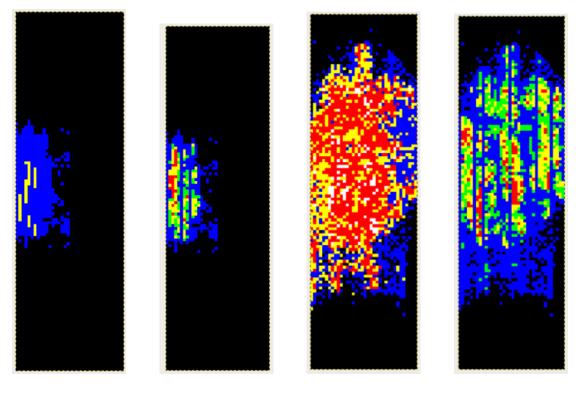

| 6.7  | Heatmaps generated by VERI-Place tool on B14 from ITC99 benchmarks     |    |

|      | [18]                                                                   | 57 |

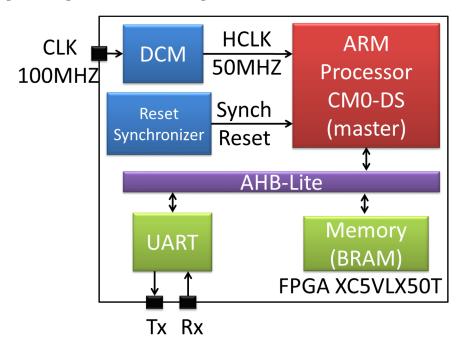

| 6.8  | Architecture of ARM SoC on Virtex-5 FPGA                               | 58 |

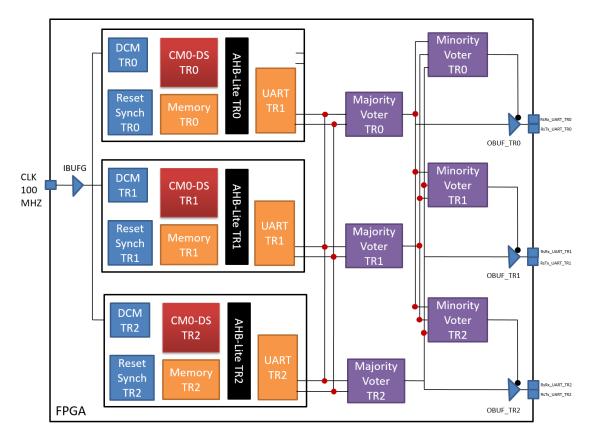

| 6.9  | Architecture of ARM SoC with XTMR applied on Virtex-5 FPGA             | 59 |

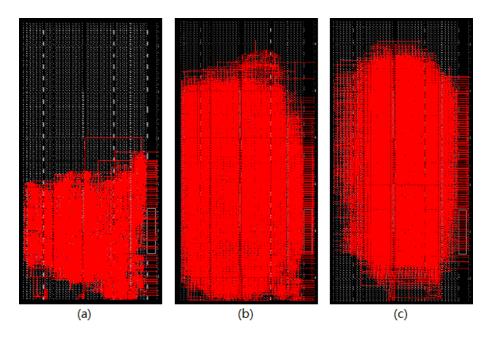

| 6.10 | Physical layouts showing interconnection networks of a)Plain b)XTMR c) |    |

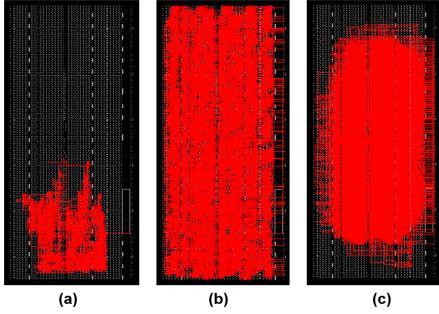

|      | XTMR-VP version of the ARM-SoC from FPGA Editor tool                   | 60 |

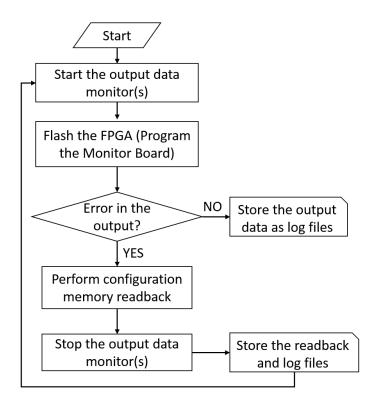

| 6.11 | Workflow of the host PC application                                    | 61 |

| 6.12 | Physical layouts showing interconnection network of a)Plain b)XTMR c)  |    |

|      | XTMR-VP version of the B13x30 from FPGA Editor tool                    | 62 |

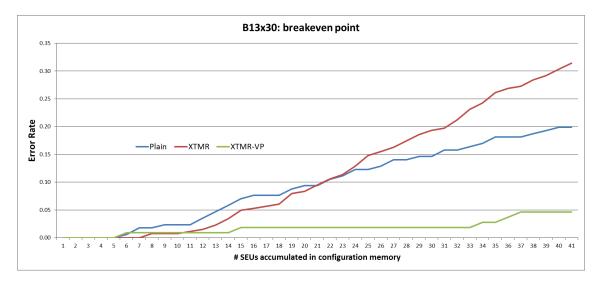

| 6.14 | The error rate from radiation experiments and VERI-Place tool The SDC error rate comparison over three design versions Breakeven point in case of B13x30 benchmark | 64<br>65<br>66 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7.1  | The SET propagation through an inverting gate with an input transition 0-1-0                                                                                       | 69             |

| 7.2  | The proposed flow for analysis and mitigation of SEEs in Flash-based FPGA                                                                                          | 71             |

| 7.3  | SET pulse shape modeling the original pulse (i.e., positive transition) generated from the GDS-I model $(t_n)$ and after the propagation through a logic           |                |

|      | gate $(t_{n+1})$                                                                                                                                                   | 73             |

| 7.4  | Parametric architectural FPGA model for mesh-matrix oriented place and route algorithms (a) and the mesh matrix format in two-dimension (b)                        | 75             |

| 7.5  | The main SETA algorithm steps                                                                                                                                      | 76             |

| 7.6  | Example circuit and results from SETA tool                                                                                                                         | 77             |

| 7.7  | Example of inserted GG logic with filtering capability of 900 ps                                                                                                   | 78             |

| 7.8  | SET-aware Place & Route (SET-PAR) flow                                                                                                                             | 79             |

| 7.9  | The PDD placement algorithm                                                                                                                                        | 80             |

| 7.10 | SET reduction and Frequency improvements of the SET-PAR implemented<br>circuits w.r.t. the previously developed solution based on Microsemi com-                   |                |

|      | mercial tools                                                                                                                                                      | 82             |

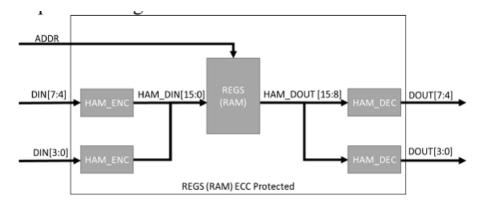

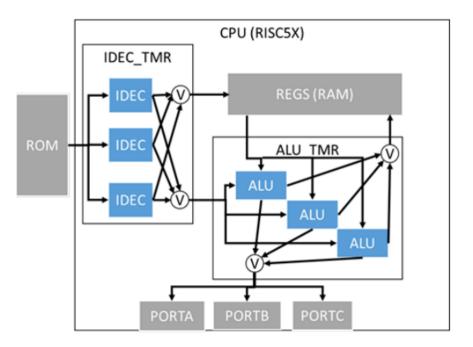

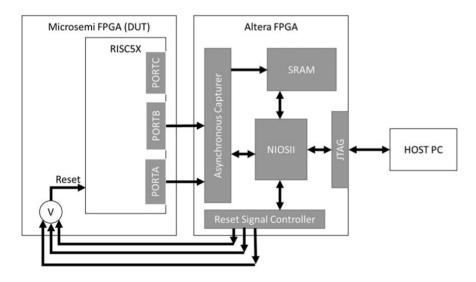

| 7.11 | RISC5x architecture                                                                                                                                                | 83             |

| 7.12 | ECC scheme adopted in order to protect RISC register file, implemented                                                                                             |                |

|      | using Flash-based FPGA embedded RAM modules against SEU accumulation                                                                                               | 83             |

| 7.13 | TMR at entity level (IDEC & ALU)                                                                                                                                   | 84             |

| 7.14 | Radiation experiment setup                                                                                                                                         | 85             |

| 7.15 | SEE cross-section comparison between different RISC5x versions                                                                                                     | 86             |

| 7.16 | Error events classification                                                                                                                                        | 87             |

# List of Tables

| 2.1 | Benchmark applications                                | 16 |

|-----|-------------------------------------------------------|----|

| 2.2 | Fault injection results                               |    |

| 2.3 | Detection capabilities (Unlimited CFC-ST size)        | 17 |

| 2.4 | Fault coverage with a smaller static CFC-ST           |    |

| 2.5 | Detection capabilities with Dyn-CFC module            | 19 |

| 3.1 | Synthesis results                                     | 26 |

| 3.2 | Fault injection results with BBS                      | 28 |

| 3.3 | Fault injection results with Mmult                    | 28 |

| 3.4 | Fault injection results with AES                      | 29 |

| 3.5 | Fault injection results with Register File            | 31 |

| 4.1 | Resource consumption for the Monitoring IP            | 38 |

| 4.2 | Experimental results on the MIPS-like processor       | 41 |

| 6.1 | Design characteristics for three versions of ARM SoC  | 59 |

| 6.2 | Design characteristics for three versions of B13x30   | 62 |

| 6.3 | Fluence and SDC cross-section                         | 63 |

| 7.1 | Characteristics of the implemented benchmark circuits | 81 |

| 7.2 | Characteristics of four RISC5x versions               | 85 |

## Part I

# Testing for SoC/SoPC by Exploiting Debugging Infrastructures

# Chapter 1 Introduction

Facing the effects of faults in electronic systems is an increasingly important issue, especially when they are used in safety- or mission-critical applications. Reduced transistor size, higher density, lower voltage and more aggressive clock frequency may increase the susceptibility to soft errors to unacceptable levels. Other phenomena (e.g., aging and wearout effects) also impact negatively the reliability of modern circuits. As a consequence, the need for effective techniques providing the ability to detect the possible occurrence of faults during the operational phase is becoming a major issue from a practical point of view.

Processor-based systems are commonly used in a wide variety of applications, including safety-critical and high availability missions, e.g., in the automotive, biomedical, telecommunication and aerospace domains. In these fields, an error may produce catastrophic consequences. Thus, dependability is a primary target that must be achieved taking into account tight constraints in terms of cost, performance, power and time to market. Several solutions exist, acting either on hardware or software: however, they all have to face the high efforts required for designing, manufacturing, testing and qualifying processor-based systems. Standards and regulations (e.g., ISO 26262 [34], DO-254 [10], IEC 61508 [33]) clearly specify the targets to be achieved and the methods to prove their achievement. In this scenario, techniques working at system level (i.e., without changing the technology and the processor) are particularly attracting, especially if they can effectively meet dependability needs more efficiently without changes in the existing hardware and software. Solutions based on additional modules that monitor the processor behavior and check its evolution looking for possible fault effects belong to this category.

## 1.1 Online test of Control Flow Error

Among the techniques that can be applied at system level, *Control Flow Checking* (CFC) is particularly effective. Control Flow Checking consists in verifying the sequence of instructions executed by a processor. It must be noted that CFC alone cannot detect data errors, i.e., errors in data registers or data memory, and must be generally complemented by some technique focused to data error detection. However, a significant percentage of

errors in a processor usually manifest themselves as *Control Flow Errors* (CFE), and most data errors can be effectively addressed by adding proper fault management mechanisms to memory and relevant registers (e.g., parity check or hamming codes).

#### 1.1.1 Previously proposed techniques

Several CFC approaches are based on signature monitoring [60]: the program is divided into a set of blocks (named basic blocks), having only one entry-point and only one exitpoint: hence, whenever the entry-point instruction is executed, the following instructions in the block are executed. Each basic block has an associated signature that is calculated at compile time and stored in the system. During the operational phase, a run-time signature is calculated and (at the end of the block execution) compared with the reference signature, thus allowing to detect any error affecting the block execution flow.

Signature monitoring techniques usually require software and/or hardware modifications to calculate the run-time signatures and perform comparisons. Since the calculation of signatures is computationally expensive, dedicated hardware (e.g., a *watchdog processor*) is sometimes used for this purpose. In some cases the approach is combined with software modifications, which support the watchdog processor operation. The *Disjoint Signature Monitoring* (DSM) approach [35, 15] solves these problems by storing reference signatures in an auxiliary memory and using a watchdog processor to compare the reference signatures with the run time signatures. This approach does not require support from the software program. However, a drawback of the DSM approach is that the watchdog processor does not have access to the internal operation of the processor, which leads to a lower error coverage, particularly with complex processors [15].

#### 1.1.2 Control Flow Checking module

A new method was proposed for the control flow checking approach resorting to available debug infrastructures as a means to monitor the processor behavior. Debug infrastructures are intended to support software debugging in embedded system development, and are very common in modern processors. Since they are useless when the operational phase is entered, they can be easily reused for on-line monitoring in an inexpensive way [8, 29, 54, 56]. On the other hand, they can provide internal access to the processor without disturbing it and do not require any modification either to the processor or to the software running on it. It must be noted that in some processors the debug information is processed and compacted by a specialized module, such as LEON3's Debug Support Unit (DSU) or ARM's Embedded Trace Module (ETM). Such modules are not used in our approach, which is based on direct access to the trace interface.

In the proposed approach, control flow checking is performed by an external hardware module that monitors the sequence of instructions executed by the processor through the debug interface and performs some checks to detect possible deviations. The developed hardware module, named *Control Flow Checking Module*, consists of a core able to perform some checks at the end of each basic block, using the information provided by the debug interface. Along the work, different versions of CFC Module were proposed providing possibility for designer to choose the trade-off between the detection capability and the cost in terms of area consumption. The detection capability of the developed module has been experimentally evaluated by means of fault injection on two different pipelined processors.

### 1.2 A hybrid nonintrusive error detection technique

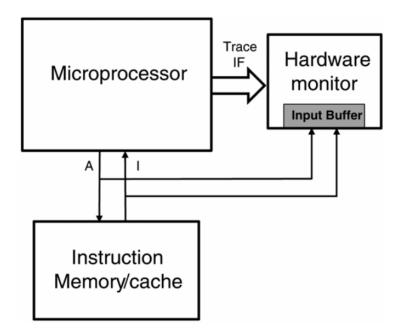

The CFC module proposed can effectively detect Control Flow Errors, however to detect Data Errors, such solution must be accompanied by other techniques. So a new method was proposed to use dual control-flow monitoring for nonintrusive error detection, combing software techniques with an external hardware module that monitors the execution of a microprocessor.

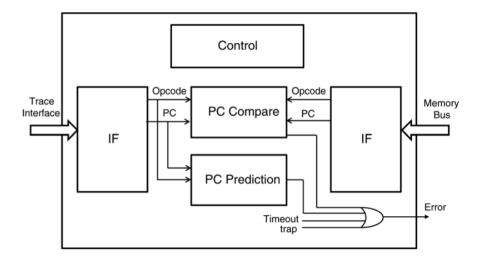

The external hardware module used in this method is similar to the CFC module in the way that it also monitors the downstream information extracted from the trace interface of the processor (e.g., LEON3 [27]), however, it also captures the upstream communication at the bus between the memory and the microprocessor. If an error corrupts the instruction flow at any stage, it is detected by comparing the downstream instruction flow with upstream instruction flow. On the other hand, errors in the generation of fetch addresses are detected using a PC prediction technique. In this way, all errors in the program counter and the instruction register at any of the pipeline stages can be detected. These include all control-flow errors, as described in [76]. It can also detect some data errors produced by corrupted instructions that generate wrong data or data addresses without affecting the control flow.

To achieve full error coverage, it is necessary to protect data as well as control flow. A combination of two software-based techniques

- total data-flow duplication, based on techniques presented in [17] and [59]

- inverted branches, based on the approach presented in [8]

were chosen for data hardening to lessen the impact of data-flow hardening in the hardware module since hardware-based data-flow hardening requires additional connections to the microprocessor architecture that are not easily available, and the hardware implementation leads to area increase.

## 1.3 Print Circuit Board Assemblies Power-On Self-Test

Besides being used for online test of CFE, the debug infrastructure can also be exploited during the Power-On Self-Test (POST). POST plays an important role in many systems, since it may detect faults arising during the life time of the product, thus increasing its dependability. POST may use different solutions, which should match the constraints of the environment the system is deployed in.

#### **1.3.1** Functional test for POST

Functional test [67, 65] represents a commonly adopted solution for POST. More in general, functional test is adopted in many scenarios, at the device, board and system levels [39]. In some of them it complements other test steps, performed resorting to Design For Testability (DFT). For example, when considering Printed Circuit Board Assemblies (PCBAs) test, it is common to see functional test as the last step, mainly targeting dynamic defects. The importance of this kind of defects is significantly increasing in the last years, especially since they are considered one of the major contributors for NFF [37, 41], thus raising the interest for any solution able to improve the achievable defect coverage.

Hence, functional test plays a key role for in-field test of PCBAs [26]. In this context, functional test is particularly attractive due to its relatively low implementation cost (no equipment required), low intrusiveness (no or limited changes in the PCBA design and low impact on the application) and flexibility (since functional test is typically based on forcing the processor to execute a suitable test program, possibly mimicking some specific application code). A commonly adopted solution consists in launching at the power-on the execution of a functional test targeting all the critical modules in the system, or, alternatively, some specifically crafted test able to make observable the highest percentage of defects [55]. Functional test is normally based on a sequence of instructions to be executed by the in-system processor(s), aimed at exciting possible defects in the processor itself or in any other device on the board, as well as in the interconnect. Therefore, this kind of test is sometimes referred to as *Software-Based Self-Test* (SBST) including [57].

Major limitations to the effectiveness of functional test include

- The difficulty in assessing the achieved defect coverage: although many efforts have been done to introduce high-level metrics, their correlation with real defect coverage is still a matter of discussion and a hot research topic [36];

- The cost for creating suitable functional stimuli; a lot of work has been done to automate this part, or at least to provide guidelines for the test engineer in charge of developing suitable functional tests;

- The limited observability that can be obtained on the behavior of the system under test, both as a whole and in terms of its components.

#### 1.3.2 Monitoring IP

As in the CFC Module, a Monitoring IP mapped into FPGA device on the same board of the target processor can be used to extract information via Debug Interface of the processor for assisting functional test. The onboard FPGA (if exists) can be configured as the Monitoring IP during the POST, and reconfigured to carry out normal operations afterwards. The implemented Monitoring IP is targeted on ARM processor (to be precise, Cortex A9 on Zynq-7000 device), whose CoreSight components can generate various information packets related to the execution of the software on the processor, which then can be extracted from the Trace Port Interface Unit (TPIU).

However, internal characteristics of the ARM processor is not directly available that makes impossible to execute fault injection to verify the effectiveness of proposed approach. Instead, a pseudo debug interface was added in a pipelined processor mimicking the behaviors of the one in ARM processor.

## Chapter 2

# **Online Test of Control Flow Error**

This chapter discusses about the technique proposed for online test of *Control Flow Error* (CFE), i.e. the CFC module<sup>1</sup>. The CFC module is used to exploit the debug/trace interface, that already exists in many processors, to monitor the software running on the processor for detecting CFEs.

The chapter is organized as follows: firstly, a background section is presented providing information regarding soft errors in processor-based systems, the existing debug interface and related approaches proposed to detect the CFEs; then the proposed technique involving the CFC module is presented explaining different solutions enabling designer to achieve trade-off between hardware overhead and test capability; finally, the data analysis from fault injection campaigns on two target processors is presented, showing that even with very low hardware overhead and no performance penalty, the proposed CFC module is able to achieve very high test coverage with respect to CFEs.

#### 2.1 Background

Approaches to detect soft errors are traditionally divided in techniques that deal with faults affecting the data and faults affecting the control flow. In order to mitigate errors affecting data, the common approach is duplication. Duplication can be accomplished at different levels: computation duplication, procedure duplication and program duplication. Many of the methods to detect soft errors affecting data require some software modification. Because of the required duplication and additional data checks, a considerable performance decrease is produced, as illustrated in [17] and [23].

Several approaches have been proposed to detect and mitigate soft errors affecting the control flow. The most common approach is known as Embedded Signature Monitoring (ESM) [60]. Variations can be applied to this technique but the basic idea consists in pre-computing a signature for certain parts of the code and then re-computing the same

<sup>&</sup>lt;sup>1</sup>This work was done with collaboration with our colleagues in University Carlos III of Madrid, Leganes, Madrid and supported in part by EU FP7 STREP project BASTION; related publications can be found as [20, 21, 22]

signature at run time, checking whether the two match. In these techniques, code is divided into sections called *Basic Blocks* (BBs). A BB is a fragment of code that does not contain any incoming or outgoing branch, i.e., all the instructions belonging to the BB are always executed sequentially, once the first is reached.

In Enhanced Control flow Checking using Assertions (ECCA) [3] ESM is implemented through assertions. In each block, two assertions are included: one at the beginning of the block which assigns an identifier to the block and checks the correctness of the branch previously taken and the other at the end of the block, which updates the identifier and checks it. In this technique, short blocks increase the error detection capability as well as decrease the latency. The main drawback of this technique is the high memory and performance overhead it introduces.

In Control Flow checking by Software Signature (CFSS) [51], a signature is assigned to each block. At runtime, a signature is continuously computed out of the opcodes of the executed instructions: each time a branch takes place the signature is compared with the expected one. Signatures are computed in different ways depending on the number of predecessors the block has. The main limitation of this method lies in its limited detection capability, since some errors (e.g., when the processor wrongly executes another instruction of the same block, or when a legal but incorrect branch is taken) are not detected.

In Control flow Error Detection through Assertions (CEDA) [75], the signatures are computed in different ways depending on the block type. For each block two signatures are assigned (the signature at the beginning and the signature at the end of the block). Check instructions are inserted in certain points of the code to verify the correctness of the signature.

In Automatic Correction of Control-flow Errors (ACCE) [76], a software method allows not only to detect, but also to correct control flow errors.

Summarizing, all the described techniques compute one or several signatures and compare them with the ones previously assigned and stored. Mismatches between signatures trigger an error signal, and the possible correction. Detection problems can arise when incorrect branches are taken inside a block or when legal but incorrect branches are taken. As a major limitation, most of the methods involve a significant overhead in terms of memory and performance.

Other methods, essentially based on an additional monitor processor, like the approaches presented in [35, 15, 13] require a large overhead of hardware resources to detect the soft errors; moreover, the detection capability is not independent from the application. Thus, not surprisingly, in these methods the error detection capability increases with the complexity of the additional hardware.

Another drawback of these methods is the difficulty in observing the processor behavior from the outside. In [15] a watchdog processor connected to the cache memory is used to detect soft errors. This watchdog processor uses a combination of techniques that are applied when a block ends or when frequent instructions are executed. For intra-block instructions a special signature is computed and address checking is performed. For nonconditional branch instructions the destination address is compared with the information about the code stored previously, while for conditional branch instructions, the watchdog processor verifies the correctness of the taken branch. Exceptions are also taken into account by accessing the interrupt vector. Data errors are handled by duplicating only critical variables. Although the error coverage is incremented, the proposed watchdog processor is quite complex and requires a large amount of resources for its implementation.

Some major limitations of these methods are the following:

- 1. The presence of caches prevents the watchdog to know what the processor is exactly doing, and may significantly decrease the detection capabilities of the approach.

- 2. If the processor is based on a pipeline architecture, observing the bus during the fetch operation does not allow to understand which instructions are really executed, due to the effects of branches.

In [8] the authors proposed a method to implement some checks (partly in hardware, partly in software) able to detect both data and control flow errors; according to the authors the method is able to detect all possible faults, but it requires some relevant modifications on the application software, and it assumes that the processor bus is accessible, which is not the case when caches exist.

The usage of debug infrastructures has been proposed as a way to increase the observability of soft errors with very limited latency, as presented in [29, 54, 56]. The technique proposed in this work follows the same approach, taking advantage of the already available features existing in many processors (standalone or cores) and using them to detect soft errors. In particular, the method exploits the feature offered by some debug architectures, which allows tracing the values of both the Program Counter and the Instruction Register during the execution of an application. In order to exploit on-the-fly these information, an external hardware module is added, which monitors the values provided by the debug port and processes them for detection purposes. In this way the processor is not modified and the connection to it can be made in an easy and efficient way, while caches do not represent any more an obstacle.

In [29] the debug infrastructure is exploited to get the value of the Program Counter of two processors running the same application, checking for possible divergences caused by faults. The technique explored in [56] further extends this idea, and assumes that either time, or hardware redundancy is used, and the debug interface allows checking for discrepancies between the two execution replicas. An extension of this idea is presented in [54] where the authors evaluate the effectiveness and cost of different checks that can be performed on the values stemming from the debug port.

### 2.2 Control Flow Checking module

The CFC module was proposed as a technique for online test of CFE in which:

- the address and machine code of each executed instruction are available through the debug port

- these two information items processed on-the-fly by a suitable hardware module (i.e., *CFC module*) aiming at detecting possible CFEs affecting the processor.

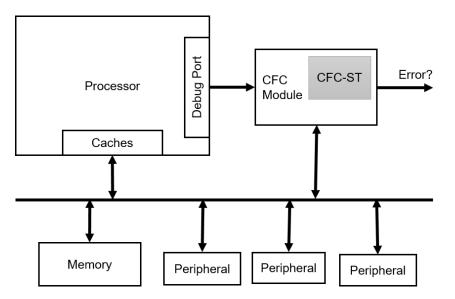

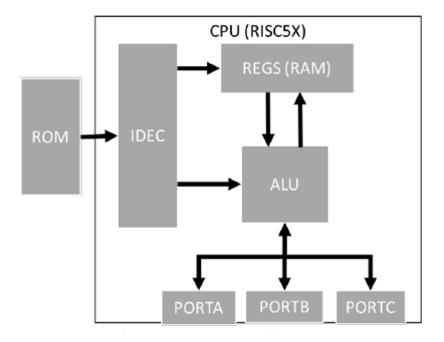

The CFC module can be implemented either as an Infrastructure IP, if *System-on-Chip* (SoC) is considered, or as an additional device (if board systems are considered): in the latter case it could also be implemented on an FPGA located close to the processor. The CFC module implements some checks aimed at detecting control-flow errors and triggers an Error signal when it detects any error. The architecture of the resulting system is shown in Fig. 2.1.

Figure 2.1: Architecture of a system adopting the proposed approach

The proposed method for CFE detection requires that the target processor be equipped with a debug port interface available for the external CFC module to link with; moreover, the method assumes the debug port provides a continuous flow of information about instructions executed (i.e., completed) by the processor, skipping instructions which are fetched, and then aborted (due for example to branch effects). This assumption is justified by the fact that many of current existing processors have a trace bus (such as the ones compliant with IEEE ISTO 5001-1999 Class 2+).

#### 2.2.1 Architecture of the CFC module

In summary, there are two checks performed by the CFC module:

1. Check #1: at each clock cycle, the CFC module receives the address and machine code of the currently completed instruction (if any): it checks whether the address is correct with respect to the previous instruction. In particular, if the previous instruction was a branch, the CFC module decoded it and computed the target address T: hence, the address  $X_i$  of the current instruction i should be equal either to T (branch taken) or to  $X_{i-1} + IS$  (branch not taken), being  $X_{i-1}$  the address of the previous instruction, and IS the instruction size in bytes.

2. Check #2: the CFC module continuously compacts the machine codes of the executed instructions: each time a branch instruction is executed, a BB ends, and the module compares the computed signature for the block with the expected one. The signature is computed by compressing into a single value the machine codes of the instructions belonging to the BB.

The CFC module supports the executions of both Check #1 and Check #2. The implementation of a hardware module supporting Check #1 requires some proper logic, able to remember some proper information about the previous instruction, as well as to perform the proper comparison between the new and expected values of the PC.

However, to support the Check #2, a table inside the CFC module is implemented to store the pre-computed signatures of BBs, i.e. the *CFC Signature Table* or *CFC-ST*. In the operational time, each time a BB starts, the CFC module records internally the address of its first instruction (*Starting Address* or *SA*); when the BB ends, the module retrieves the expecting signature of the BB from CFC-ST using the least significant bits of SA as an index, and compares it to the signature computed on-the-fly by the Signature Monitor component. If a mismatch is found between the two signatures, an Error signal is triggered.

Along the work, different versions of CFC module were proposed focusing on how the signatures of the BBs in the software running on the processor should be stored and managed to enable the trade-off between the detection capability of the CFC module and resource consumption overhead.

#### The CFC module with static CFC-ST

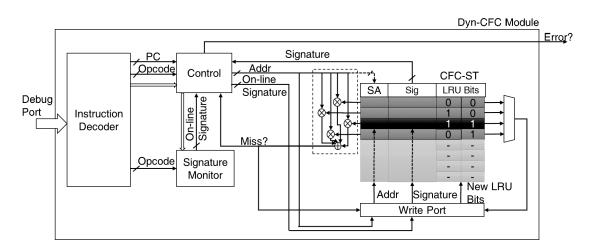

On the assumption that the software running on the processor or at least the critical part of the software is small, in terms of number of BBs, so that all the signatures can be stored directly in the CFC-ST, the architecture of the CFC module is quite simple as illustrated in Fig. 2.2.

The CFC module consists of the following blocks:

- *Instruction Decoder* (ID) block detects when a new instruction is being executed and checks whether that instruction is a branch instruction or not, in order to identify the beginning and end of a BB execution,

- Signature Monitor computes the signature of the executed machine code values by means a MISR (Multiple Input Shift Register),

- CFC-ST stores the off-line signatures corresponding to each BB and its SA,

- Control Block is in charge of managing the CFC module behavior, enabling and clearing the signature monitor for each BB, reading the off-line signature and triggering the Error signal when the on-line signature differs from the expecting one in CFC-ST. It is also in charge of implementing the Check #1.

On the other hand, in case of the CFC-ST is not large enough to hold all the signatures of BBs in the software, then certain mechanism needs to be applied to choose which

Figure 2.2: CFC module architecture diagram

signatures should be stored in the CFC-ST. Three techniques were proposed for ranking the BBs: