# POLITECNICO DI TORINO

DOCTORAL THESIS in Electronic Devices - XXVIII cycle -DISAT Department

# Electronic systems for intelligent particle tracking in the High Energy Physics field

# DAVIDE CERESA

Supervisors: Prof. Fabrizio Pirri Prof. Felice Iazzi

**Ph.D coordinator:** Prof. Giovanni Ghione

#### POLITECNICO DI TORINO

# Abstract

#### **DISAT** department

#### Ph.D in Electronic Device

## Electronic systems for intelligent particle tracking in the High Energy Physics field

by Davide CERESA

#### English version

This Ph.D thesis describes the development of a novel readout ASIC for hybrid pixel detector with intelligent particle tracking capabilities in High Energy Physics (HEP) application, called Macro Pixel ASIC (MPA). The concept of intelligent tracking is introduced for the upgrade of the particle tracking system of the Compact Muon Solenoid (CMS) experiment of the Large Hadron Collider (LHC) at CERN: this detector must be capable of selecting at front-end level the interesting particle and of providing them continuously to the back-end. This new functionality is required to cope with the improved performances of the LHC when, in about ten years' time, a major upgrade will lead to the High Luminosity scenario (HL-LHC).

The high complexity of the digital logic for particle selection and the very low power requirement of  $< 100 \,\mathrm{mW/cm^2}$  drive the choice of a 65 nm CMOS technology. The harsh environment, characterized by a high ionizing radiation dose of 100 Mrad and low temperature around  $-30^{\circ}$ C, requires additional studies and technology characterization. Several architecture for intelligent particle tracking has been studied and evaluated with physics events from Monte-Carlo simulation. The chosen one reaches an efficiency > 95% in particle selection and a data reduction from  $\sim 200 \,\mathrm{Tb/s/cm^2}$  to  $\sim 1 \,\mathrm{Tb/s/cm^2}$ .

A prototype, called MPA-Light, has been designed, produced and tested. According to the measurements, the prototype respects all the specifications. The same device has been used for multi-chip assembly with a pixelated sensor. The assembly characterization with radioactive sources confirms the result obtained on the bare chip.

#### Versione italiana

La tesi di seguito riportata descrive lo sviluppo di un nuovo ASIC studiato per la lettura di rivelatori ibridi constituiti da pixel con un sistema di tracciamento intelligente di particelle per applicazioni nel campo della fisica delle particelle, chiamato Macro Pixel ASIC (MPA). Il concetto di tracciamento intelligente è stato introdotto per l'aggiornamento dell'esperiemento Compact Muon Solenoid (CMS), uno dei due grandi rivelatori per la fisica delle particelle generale, costruito sull'acceleratore Large Hadron Collider (LHC) al CERN. Il sistema di tracciamento deve essere in grado di selezionare a livello frontend le particelle interessanti, e di fornirle ininterrottamente al back-end. Questa nuova funzionalità è stata richiesta per far fronte al miglioramento delle prestazioni del acceleratore quando, in circa dieci anni, un vasto aggiornamento condurrà allo scenario chiamato High Luminosity (HL-LHC).

La complessità della logica digitale necessaria per la selezione di particelle e la richiesta di una densità di potenza totale  $< 100 \text{ mW/cm}^2$  conducono alla scelta della tecnologia CMOS a 65 nm. L'ambiente ostile, caratterizzato da un'alta dose di radiazioni ionizzanti fino a 100 Mrad e le basse temperature intorno ai  $-30^{\circ}$ C, richiedono studi aggiuntivi e la caratterizzazioni della tecnologia. Differenti architetture per il tracciamento intelligente di particelle sono state studiate e valutate con eventi fisici ottenuti grazie a simulazioni Monte-Carlo. L'architettura scelta permette di raggiungere un'efficienza >95% nella selezione di particelle e una riduzione di dati da  $\sim 200 \text{ Tb/s/cm}^2$  a  $\sim 1 \text{ Tb/s/cm}^2$ .

Un prototipo, chiamato MPA-Light, è stato disegnato, prodotto e testato. Sulla base delle misure effettuate, il prototipo rispetta tutte le specifiche. Lo stesso dispositivo è stato usato per l'assemblaggio di moduli multichip con un sensore pixellato. L'illuminazione del modulo con fonti radioattive ha inoltre confermato i risultati ottenuti sul chip senza il sensore connesso.

Dedicated to Stefania,

and to Our Dreams.

# Contents

| Abstract |       |         |                                              | i    |

|----------|-------|---------|----------------------------------------------|------|

| С        | onter | nts     |                                              | v    |

| Li       | st of | Figur   | es                                           | ix   |

| A        | bbre  | viatior | 15 2                                         | xiii |

| 1        | Intr  | oduct   | ion                                          | 1    |

|          | 1.1   | Main    | challenge                                    | 4    |

|          | 1.2   | Thesis  | s organization                               | 5    |

| 2        | Silie | con De  | etectors for High Energy Physics             | 7    |

|          | 2.1   | Silicor | n for particle detection                     | 8    |

|          | 2.2   | Detect  | tor structure                                | 8    |

|          |       | 2.2.1   | Microstrip detector                          | 9    |

|          |       | 2.2.2   | Hybrid pixel detector                        | 10   |

|          | 2.3   | Reado   | out ASIC                                     | 11   |

|          |       | 2.3.1   | Front-End Electronics                        | 11   |

|          |       | 2.3.2   | Readout architecture                         | 13   |

|          |       | 2.3.3   | Power estimation technique                   | 14   |

|          | 2.4   | Partil  | ce tracking system in HEP experiments        | 16   |

|          | 2.5   | Radia   | tion induced effect on CMOS technologies     | 18   |

|          |       | 2.5.1   | Total Ionizing Dose effects                  | 18   |

|          |       | 2.5.2   | Single event effects                         | 20   |

|          |       | 2.5.3   | Radiation-hardening techniques               | 21   |

| 3        | Ар    | article | e tracking system for future HEP experiments | 23   |

|          | 3.1   | The C   | CMS experiment                               | 24   |

|          |       | 3.1.1   | The current CMS Silicon Strip Tracker        | 25   |

|          | 3.2   | The H   | Iigh Luminosity LHC                          | 26   |

|          | 3.3   | The C   | CMS Phase-2 upgrade                          | 27   |

|          |       | 3.3.1   | The $p_T$ modules concept                    | 29   |

|          | 34    | A par   | ticle tracking system for the HL-LHC         | 30   |

|   |      | 3.4.1   | CMS Tracker structure                                                           | 1 |

|---|------|---------|---------------------------------------------------------------------------------|---|

|   |      | 3.4.2   | Outer Tracker module design                                                     | 2 |

|   |      | 3.4.3   | Silicon sensors choice                                                          | 4 |

|   | 3.5  | Outer   | Tracker electronics                                                             | 5 |

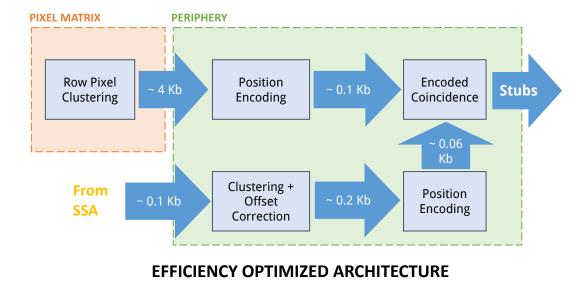

|   |      | 3.5.1   | Data flow reduction                                                             | 7 |

|   |      | 3.5.2   | Pixel-Strip module                                                              | 8 |

|   | 3.6  | DC/D    | C converter for the Outer Tracker                                               | 0 |

|   |      | 3.6.1   | On-module power distribution                                                    | 1 |

|   | 3.7  | Chapte  | er Summary                                                                      | 2 |

| 4 | A r  | eadout  | chip with momentum discrimination capabilities for pixel                        |   |

|   | dete | ector   | 43                                                                              | 3 |

|   | 4.1  | Reado   | ut electronics requirements                                                     | 4 |

|   |      | 4.1.1   | Pixel Sensor specifications                                                     | 5 |

|   |      | 4.1.2   | Power requirements                                                              | 5 |

|   | 4.2  | The 65  | 5 nm CMOS technology                                                            | 6 |

|   | 4.3  | Macro   | Pixel ASIC Architecture                                                         | 7 |

|   |      | 4.3.1   | Dimensions and connectivity                                                     | 9 |

|   |      | 4.3.2   | Preliminary power estimation                                                    | 0 |

|   |      | 4.3.3   | Floorplan                                                                       | 1 |

|   | 4.4  | Clock   | $Distribution  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 3 |

|   | 4.5  | Front-  | end electronics                                                                 | 5 |

|   |      | 4.5.1   | Analog front-end                                                                | 5 |

|   |      | 4.5.2   | Digital front-end                                                               | 6 |

|   | 4.6  | Trigge  | r Path                                                                          | 7 |

|   |      | 4.6.1   | Stub Finding algorithm                                                          | 7 |

|   |      | 4.6.2   | Clustering and centroid extraction implementation 6                             | 0 |

|   |      | 4.6.3   | Offset correction and correlation implementation                                | 3 |

|   | 4.7  | Positio | on encoding technique                                                           | 5 |

|   | 4.8  | L1 Da   | ta path                                                                         | 7 |

|   |      | 4.8.1   | A radiation tolerant low power SRAM compiler                                    | 7 |

|   |      | 4.8.2   | Memory gating technique                                                         | 8 |

|   | 4.9  | Supply  | Voltage scaling                                                                 | 0 |

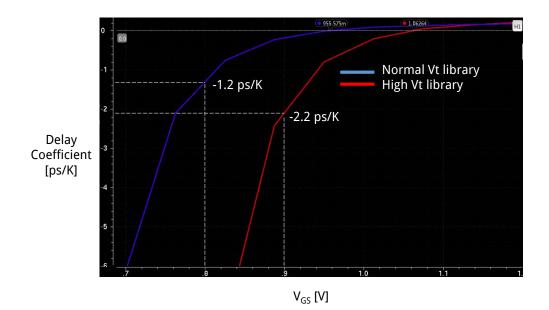

|   |      | 4.9.1   | Temperature inversion effect                                                    | 1 |

|   | 4.10 | I/O in  | terfaces                                                                        | 3 |

|   |      | 4.10.1  | High speed communication                                                        | 3 |

|   | 4.11 | Simula  | tion Studies                                                                    | 5 |

|   |      | 4.11.1  | Simulation with Monte-Carlo events                                              | 5 |

|   |      | 4.11.2  | Efficiency analysis                                                             | 5 |

|   | 4.12 | Data I  | $\operatorname{Format}$                                                         | 9 |

|   |      | 4.12.1  | Trigger path transmission                                                       | 9 |

|   |      |         | L1 data path transmission                                                       | 1 |

|   | 4.13 | Chapte  | er Summary                                                                      | 3 |

| 5 | A p  | rototy  | pe in 65 nm technology 8                                                        | 5 |

|   | 5.1  | Descri  | ption of the MPA-Light                                                          | 6 |

|   |      | 5.1.1   | ASIC architecture                                                               | 6 |

| 6 | Con | clusio  | ns                               | ]   | L07 |

|---|-----|---------|----------------------------------|-----|-----|

|   | 5.5 | Chapt   | ter summary                      | ••• | 105 |

|   |     |         | Digital logic results            |     |     |

|   |     | 5.4.1   | Analog blocks results            |     | 101 |

|   | 5.4 | Total 1 | Ionization Dose characterization | • • | 100 |

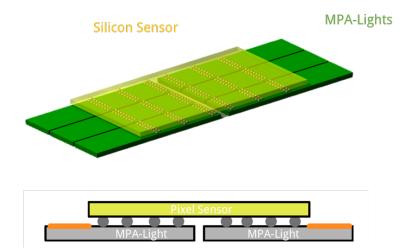

|   |     | 5.3.3   | MaPSA-Light results              |     | 96  |

|   |     | 5.3.2   | MaPSA-Ligth assembly process     |     | 96  |

|   |     | 5.3.1   | Assembly architecture            |     | 94  |

|   | 5.3 | Multi-  | -chip module prototype           |     | 93  |

|   |     | 5.2.1   | Front-end characterization       |     | 90  |

|   | 5.2 | Electri | rical characterization           |     | 89  |

|   |     | 5.1.3   | Periphery back-end               |     | 88  |

|   |     | 5.1.2   | Pixel front-end                  |     | 87  |

# List of Figures

| 1.1 | depth 3 cm. The movable piston is suddenly lowered by opening the valve c and so connecting the vacuum chamber d with the part of the apparatus                                                                                                                                        |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | beneath the piston                                                                                                                                                                                                                                                                     | 1  |

| 1.2 | Bubble chamber and an image obtained                                                                                                                                                                                                                                                   | 2  |

| 1.3 | Current CMS Silicon Strip Tracker with an event from Run 1                                                                                                                                                                                                                             | 3  |

| 2.1 | p <sup>+</sup> -on-n silicon detector structure.                                                                                                                                                                                                                                       | 9  |

| 2.2 | $\rm p^+-on\text{-}n$ silicon sensor bump-bonded with the pixel readout ASIC                                                                                                                                                                                                           | 10 |

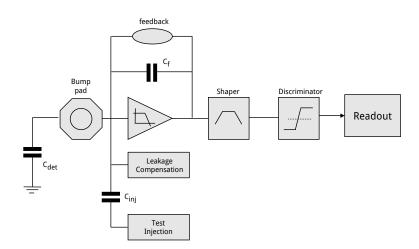

| 2.3 | Component of a generic front-end circuit.[5]                                                                                                                                                                                                                                           | 11 |

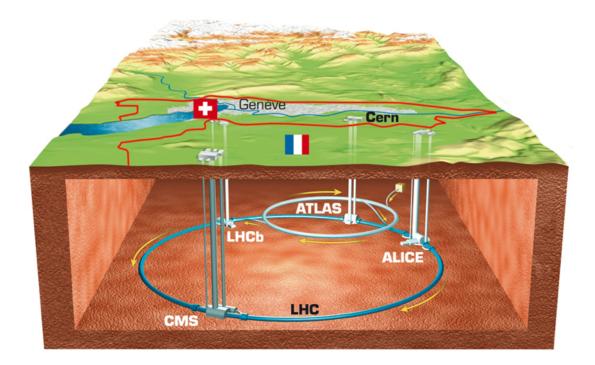

| 2.4 | Section of the LHC accelerator with the four experiment.                                                                                                                                                                                                                               | 16 |

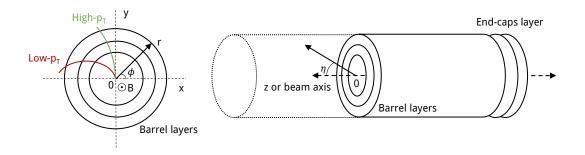

| 2.5 | Structure and coordinate system of a generic tracking system. On the left it is shown the r- $\phi$ plane with an example of low and high p <sub>T</sub> tracks. On                                                                                                                    |    |

|     | the right it is shown the r-Z plane with the end caps layer at the end                                                                                                                                                                                                                 | 17 |

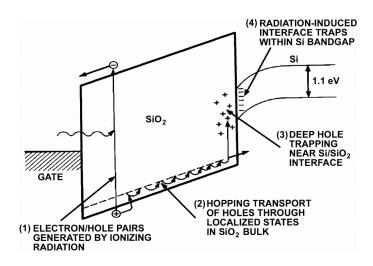

| 2.6 | Schematic energy band diagram for MOS structure, indicating major                                                                                                                                                                                                                      |    |

|     | physical processes underlying radiation response[12]                                                                                                                                                                                                                                   | 19 |

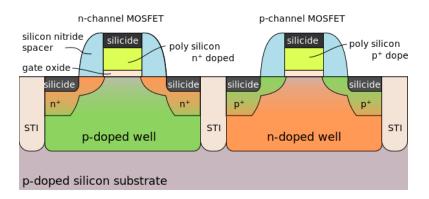

| 2.7 | n-channel and p-channel MOSFET's. Individual transistors are electricaly                                                                                                                                                                                                               |    |

|     | separated by STI trenches                                                                                                                                                                                                                                                              | 20 |

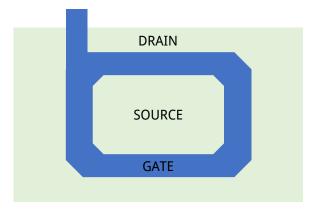

| 2.8 | Layout of an Enclosed Layout Transistor.                                                                                                                                                                                                                                               | 22 |

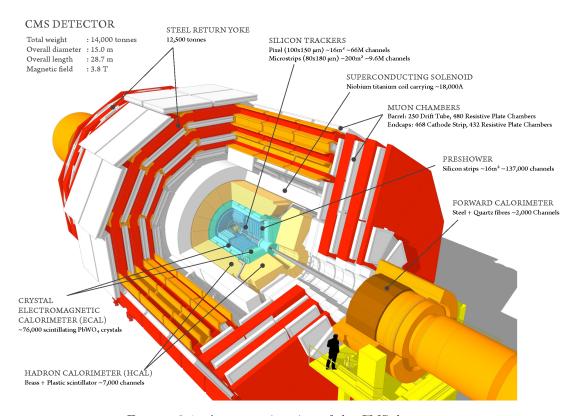

| 3.1 | A perspective view of the CMS detector                                                                                                                                                                                                                                                 | 24 |

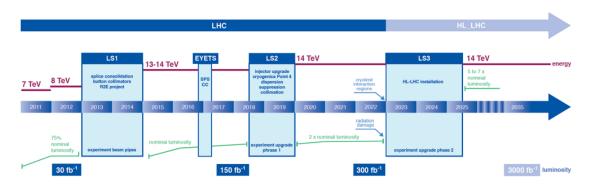

| 3.2 | High Luminosity LHC plan [17].                                                                                                                                                                                                                                                         | 26 |

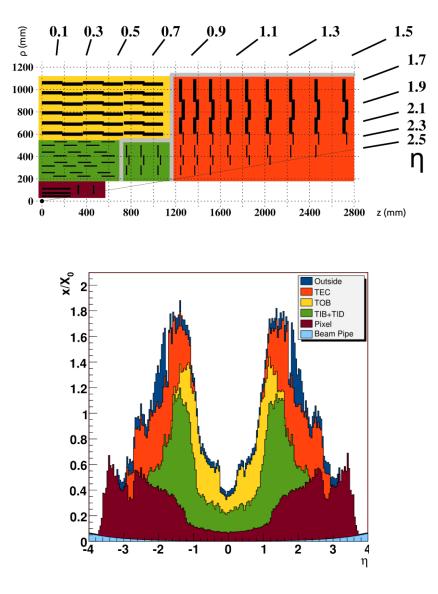

| 3.3 | Sketch of the Silicon Strip Tracker layout (top), and distribution of ma-<br>terial in radiation lengths as a function of pseudorapidity (bottom). The<br>peak in the region $1 < \eta < 2$ contains an important contribution from the<br>services routed between barrel and end-cap. | 27 |

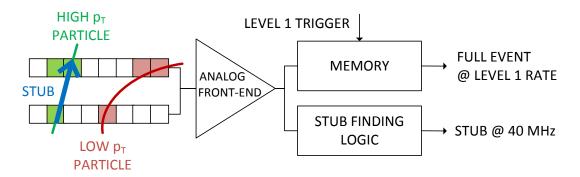

| 3.4 | A simplified view of the readout electronics including $p_T$ discrimination.                                                                                                                                                                                                           | 30 |

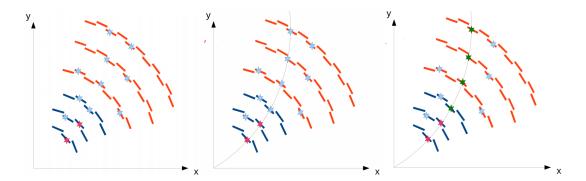

| 3.5 | A three steps track reconstruction algorithm is illustrated. Step 1: pairs                                                                                                                                                                                                             | 00 |

| 0.0 | of stubs in neighboring layers are combined to form the seeds. Step 2:                                                                                                                                                                                                                 |    |

|     | the seeds are projected to the other layers and matching stubs are found.                                                                                                                                                                                                              |    |

|     | Step 3: the matched hits are included in the final track fit.                                                                                                                                                                                                                          | 31 |

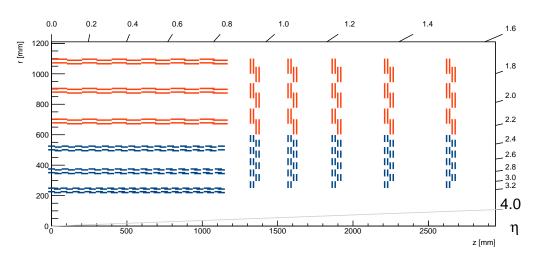

| 3.6 | Sketch of one quarter of the Tracker Layout. Outer Tracker: blue lines                                                                                                                                                                                                                 |    |

|     | correspond to PS modules, red lines to 2S modules. The Pixel detector,                                                                                                                                                                                                                 |    |

|     | with forward extension, is shown in green.                                                                                                                                                                                                                                             | 33 |

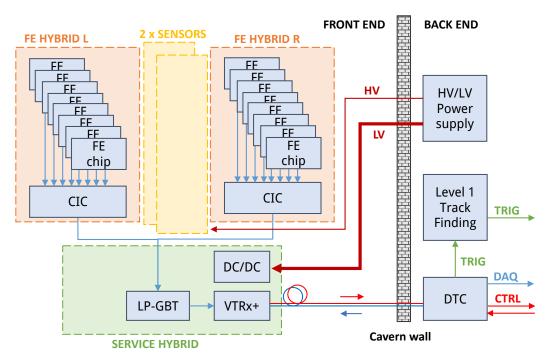

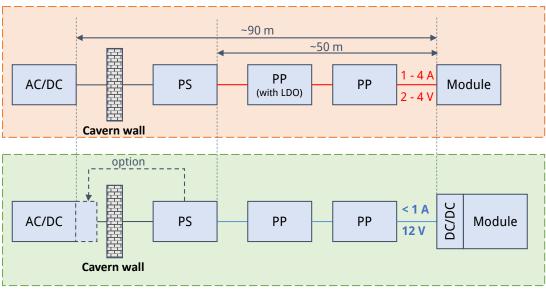

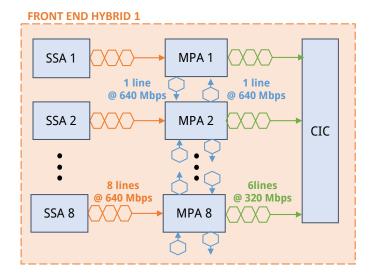

| 3.7 | Electronic system block diagram.                                                                                                                                                                                                                                                       | 36 |

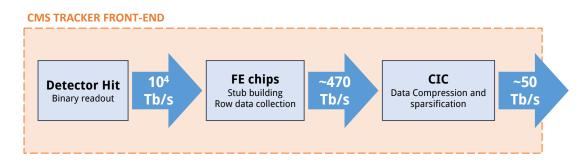

| 3.8  | CMS Tracker front-end data reduction scheme.                                                                                                                                                                                                                                                         | 37   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

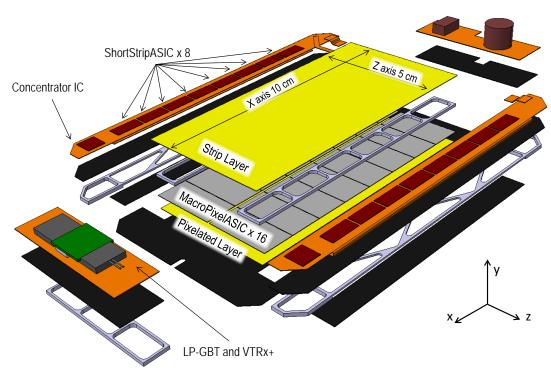

| 3.9  | PS module 3D model.                                                                                                                                                                                                                                                                                  | 38   |

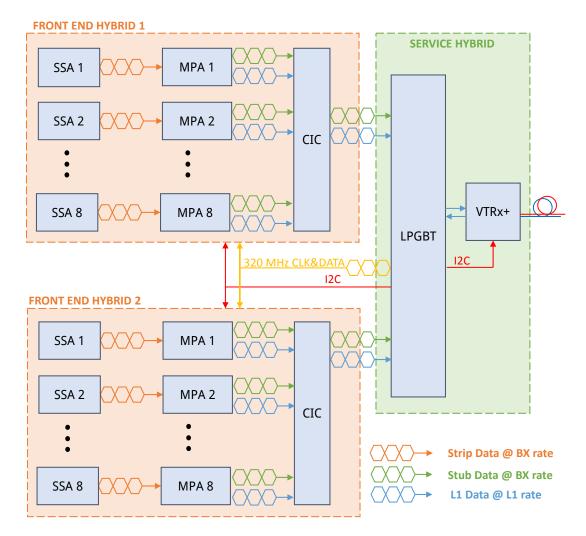

| 3.10 | PS module block diagram.                                                                                                                                                                                                                                                                             | 39   |

| 3.11 | Current and proposed configuration for tracker power scheme                                                                                                                                                                                                                                          | 41   |

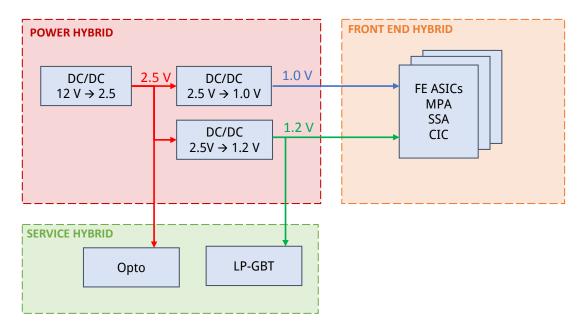

| 3.12 | PS-module power distribution scheme.                                                                                                                                                                                                                                                                 | 42   |

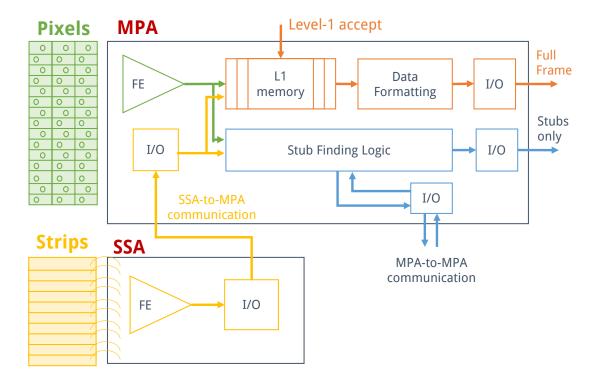

| 4.1  | Pixel and Strip Data Block diagram.                                                                                                                                                                                                                                                                  | 48   |

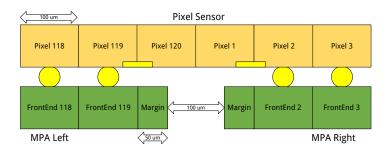

| 4.2  | Connectivity and spacing at ASIC edge                                                                                                                                                                                                                                                                | 50   |

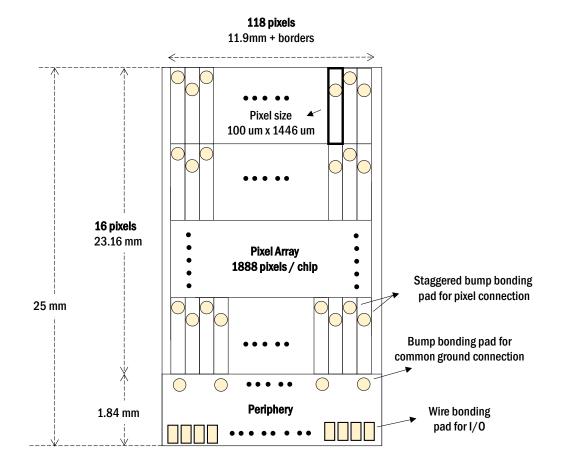

| 4.3  | Structure and the dimensions of the MPA.                                                                                                                                                                                                                                                             | 52   |

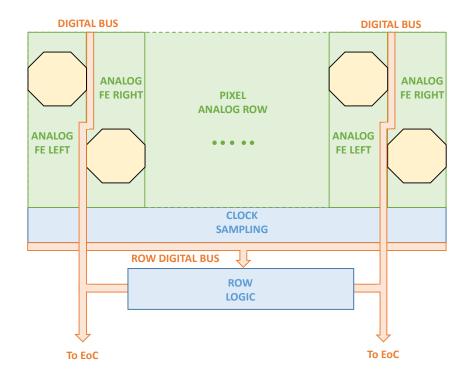

| 4.4  | Schematic representation of the Pixel Row architecture.                                                                                                                                                                                                                                              | 53   |

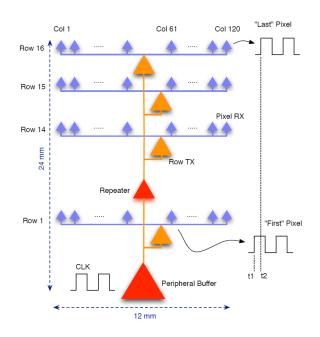

| 4.5  | Row-based clock distribution architecture                                                                                                                                                                                                                                                            | 54   |

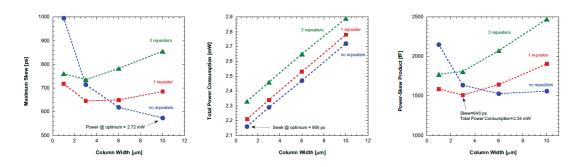

| 4.6  | Maximum skew (left), total power consumption (centre) and power-skew                                                                                                                                                                                                                                 | ~ .  |

|      | product (right) as a function of the column width.                                                                                                                                                                                                                                                   |      |

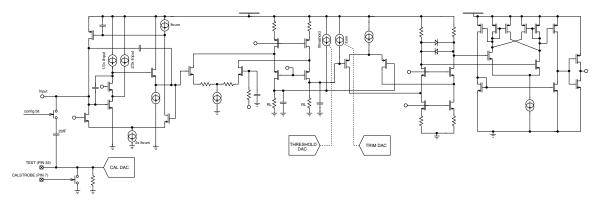

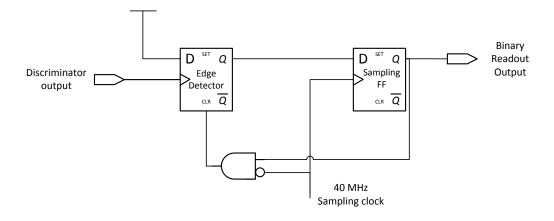

| 4.7  | MPA Analog schematic.                                                                                                                                                                                                                                                                                |      |

| 4.8  | Binary readout schematic.                                                                                                                                                                                                                                                                            |      |

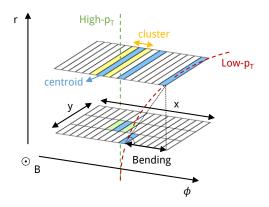

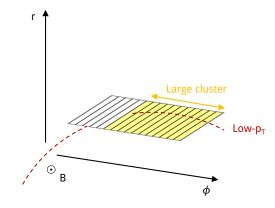

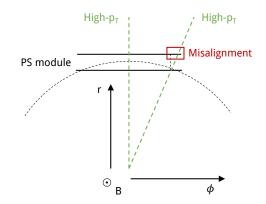

| 4.9  | Bending calculation in a Pixel-Strip module                                                                                                                                                                                                                                                          |      |

|      | Large cluster caused by very low- $p_T$ particle.                                                                                                                                                                                                                                                    | . 59 |

| 4.11 | Sketch of the misaligment caused by approximating the cylindrical geom-<br>etry of the tracker with planar sensor.                                                                                                                                                                                   | 59   |

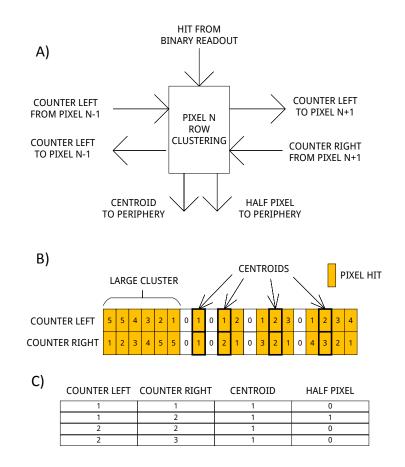

| 4 19 | Pixel Clustering connectivity and examples                                                                                                                                                                                                                                                           |      |

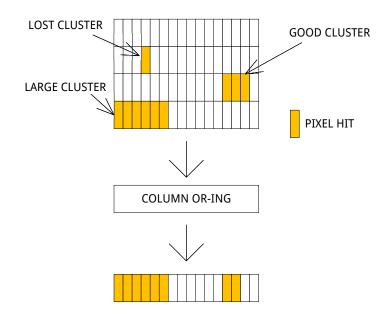

|      | Column OR-ing example. The figure shows the hiding problem caused by                                                                                                                                                                                                                                 | 01   |

| 4.10 | large cluster during the Column OR-ing. A large cluster on the first row                                                                                                                                                                                                                             |      |

|      | of the pixel frame hides the good cluster above it                                                                                                                                                                                                                                                   | 62   |

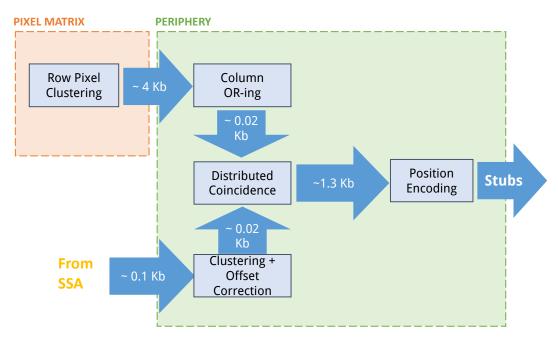

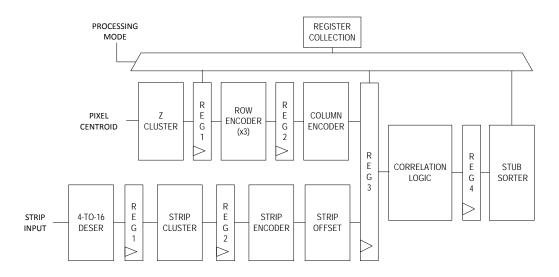

| 4.14 | Trigger path architecture                                                                                                                                                                                                                                                                            |      |

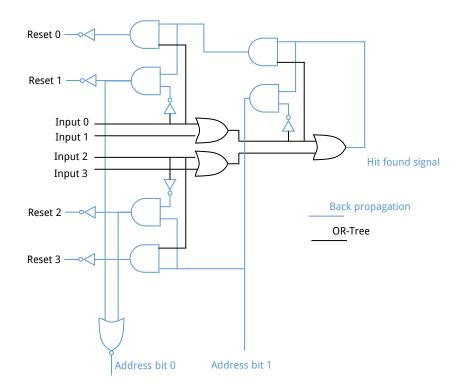

|      | Logic diagram for a 4 bit MEPHISTO priority encoder.                                                                                                                                                                                                                                                 |      |

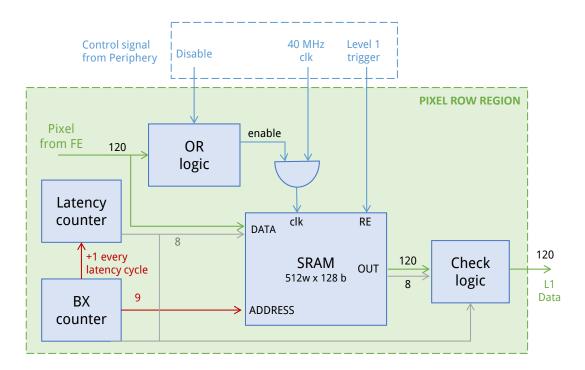

|      | Memory gating schematic                                                                                                                                                                                                                                                                              |      |

|      | Delay temperature coefficient variation respect $V_{GS}$                                                                                                                                                                                                                                             |      |

|      | FE ASICs connectivity scheme                                                                                                                                                                                                                                                                         |      |

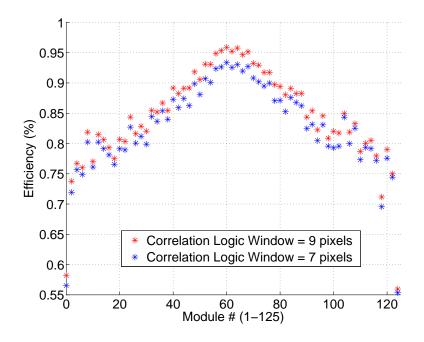

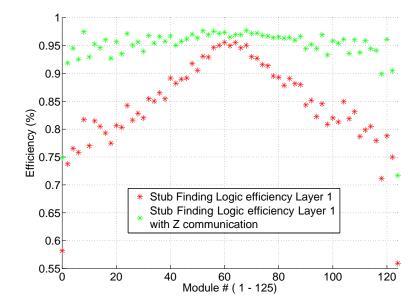

| 4.19 | Stub finding logic efficiency for different module number in Layer 1. Red points represents the stub finding Logic efficiency with a correlation logic window of 9 pixels, while blue points represents the same efficiency with                                                                     |      |

|      | a correlation logic window of 7 pixels.                                                                                                                                                                                                                                                              | 76   |

| 4.20 | Stub finding logic efficiency respect to the module number in Layer 1.<br>Module 63 is located at $z = 0$ . Higher and lower module numbers cor-<br>respond to positions with larger absolute z values, with a maximum z of<br>+/- 1100 mm. The lower efficiencies of module 1 and 125 are artifacts |      |

|      | due to the absence of the end-caps in the simulation                                                                                                                                                                                                                                                 |      |

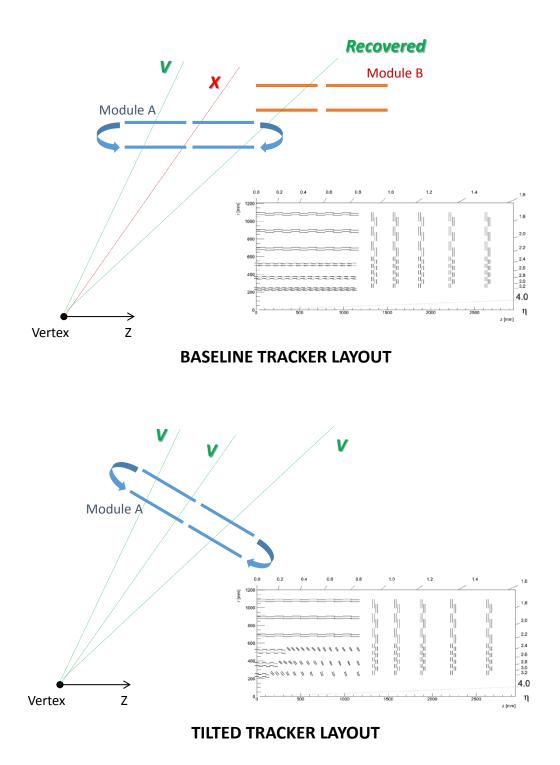

|      | Baseline and Tilted tracker layout                                                                                                                                                                                                                                                                   |      |

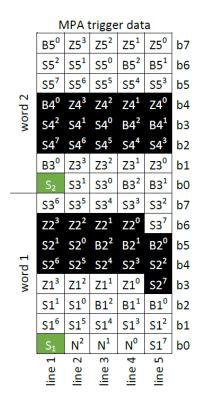

|      | Trigger path data format                                                                                                                                                                                                                                                                             |      |

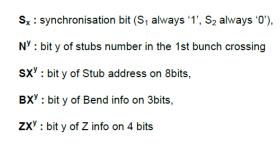

|      | Stub efficiency for different SW                                                                                                                                                                                                                                                                     |      |

|      | MPA L1 data format                                                                                                                                                                                                                                                                                   |      |

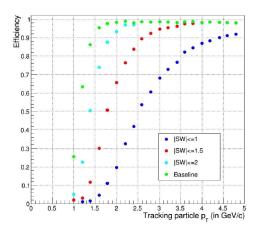

|      | MPA L1 data cluster multiplicities                                                                                                                                                                                                                                                                   |      |

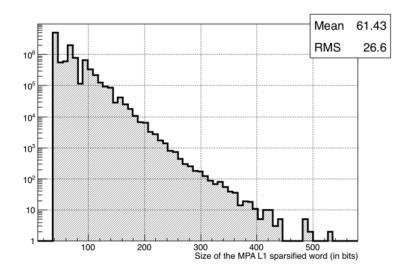

| 4.20 | Size of the MPA L1 sparsined words                                                                                                                                                                                                                                                                   | 83   |

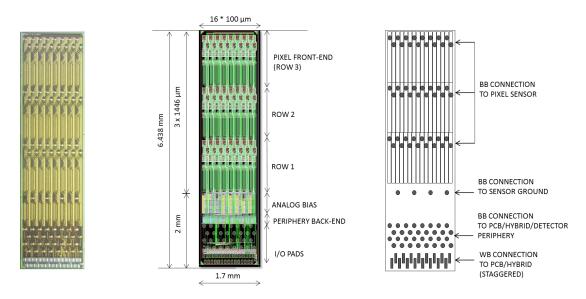

| 5.1  | Left: picture of the MPA-Light. Centre: layout view of the MPA-Light with dimensions and components. Right: connectivity view of the MPA-Light (WB = wire-bond, BB = bump-bond).                                                                                                                     | 87   |

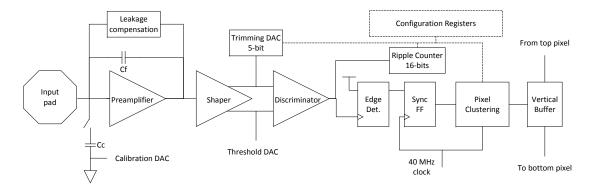

| 5.2  | Pixel front-end. Dashed lines represent configuration signals.                                                                                                                                                                                                                                       |      |

| 0.4  | i nor none one. Dublice must represent configuration signation                                                                                                                                                                                                                                       | . 00 |

| 5.3  | Periphery schematic.                                                                                                                           | 89  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

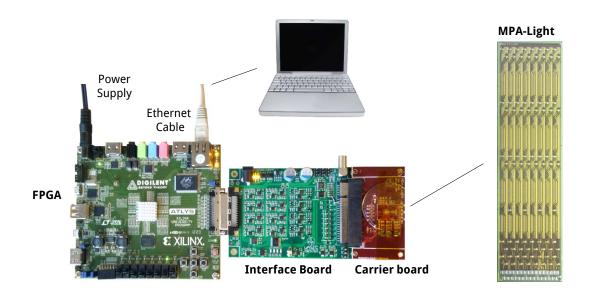

| 5.4  | MPA-Light test system.                                                                                                                         | 90  |

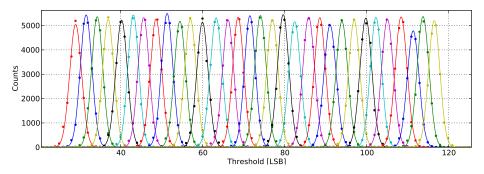

| 5.5  | Baseline scan of a pixel for the 32 different DAC codes of the trimming DAC.                                                                   | 91  |

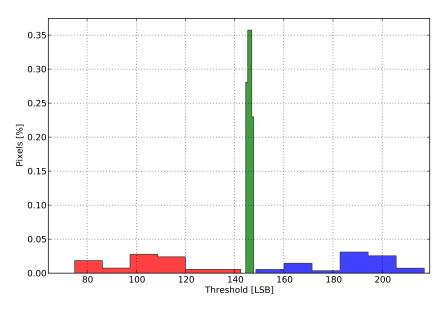

| 5.6  | Red and blue histograms show the threshold distribution of all pixels with<br>the minimum and maximum DAC codes; the green histogram shows the | -   |

|      | same distribution for calibrated matrix.                                                                                                       | 91  |

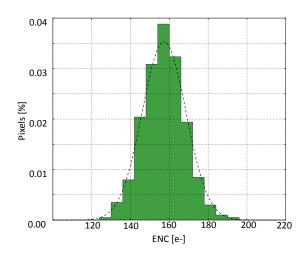

| 5.7  | Noise distribution                                                                                                                             | 92  |

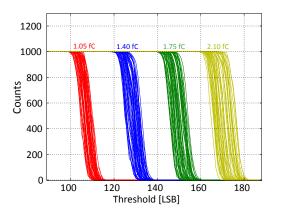

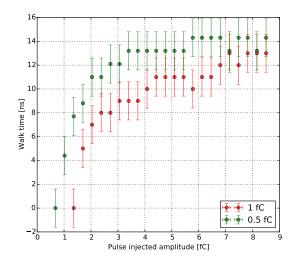

| 5.8  | S-curves for different pulse amplitudes                                                                                                        | 92  |

| 5.9  | Shaper output for different input charges                                                                                                      | 93  |

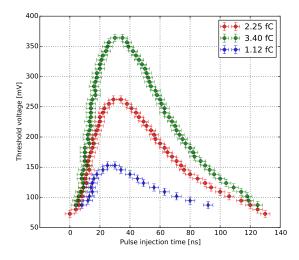

| 5.10 | Time walk for different thresholds                                                                                                             | 93  |

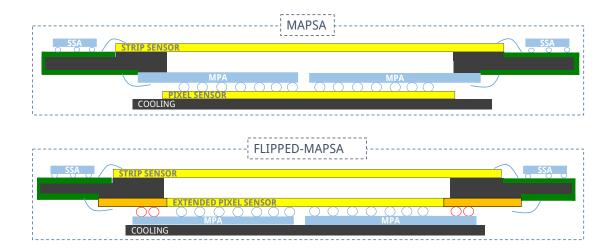

| 5.11 | Top: MaPSA-Light 3-D view. Bottom: MaPSA-Light side view.                                                                                      | 94  |

| 5.12 | Top: Schematic of the PS-module with MaPSA. Bottom: Schematic of                                                                               |     |

|      | the PS-module with Flipped-MaPSA.                                                                                                              | 95  |

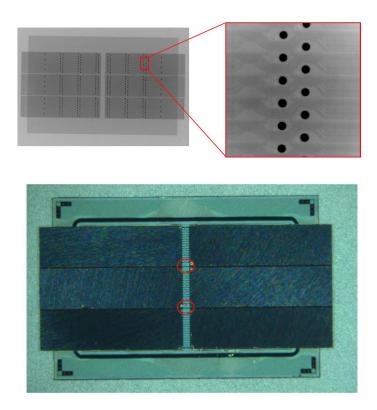

| 5.13 | Top: X-ray image of MaPSA-Light. Zoomed image allows to see the                                                                                |     |

|      | alignment of the bumps. Bottom: Image of the MaPSA-Light after under-                                                                          |     |

|      | filling. Red circles shows the application points                                                                                              | 97  |

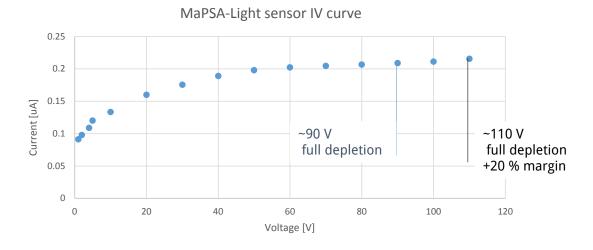

| 5.14 | MaPSA-Light sensor IV characteristic.                                                                                                          | 98  |

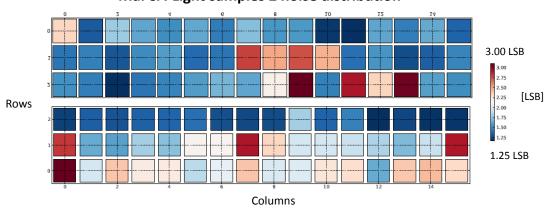

| 5.15 | MaPSA-Light sample 2 noise distribution                                                                                                        | 99  |

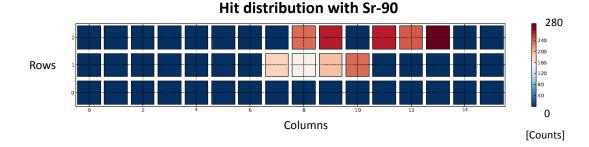

| 5.16 | MaPSA-Light sample 2 hit distribution with a Sr90 source for the MPA-                                                                          |     |

|      | Light on the top of the assembly                                                                                                               | 99  |

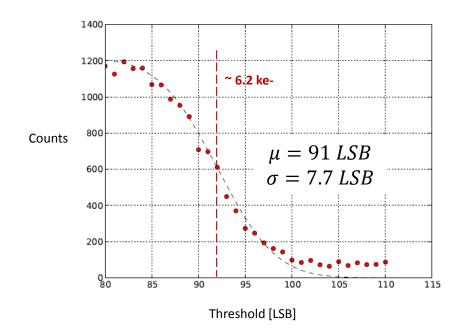

| 5.17 | Threshold scan of a Cd-109 source                                                                                                              | 100 |

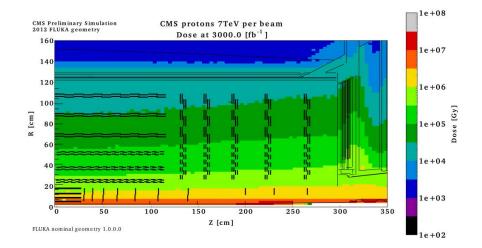

|      | Total Ionizing Dose in Grey for the full tracker.                                                                                              |     |

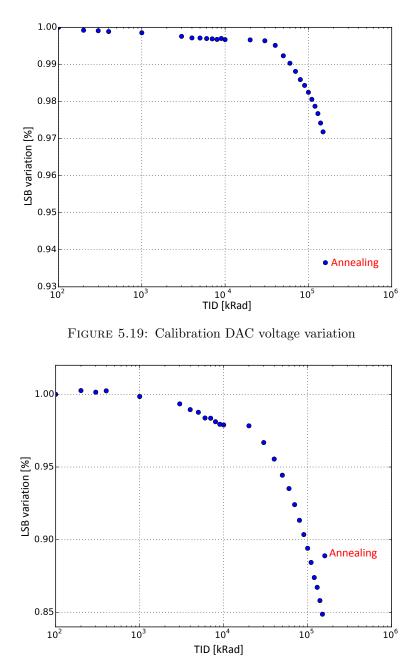

| 5.19 | Calibration DAC voltage variation                                                                                                              | 102 |

| 5.20 | Threshold value variation extracted from s-curve                                                                                               | 102 |

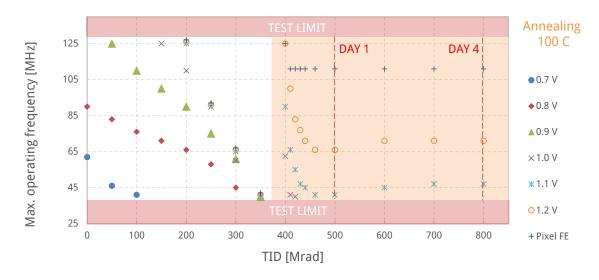

| 5.21 | Degradation of the maximum operative frequency with TID. The orange                                                                            |     |

|      | coulored part shows the annealing at 100 °C. $\ldots \ldots \ldots \ldots \ldots \ldots$                                                       | 103 |

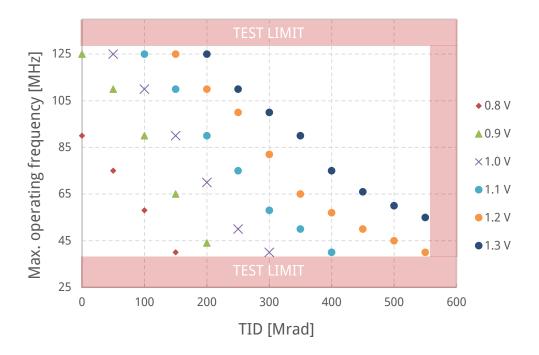

| 5.22 | Degradation of the maximum operative frequency with TID at 100 $^{\circ}\mathrm{C.}$ .                                                         | 104 |

# Abbreviations

| MOS            | $\mathbf{M}$ etal $\mathbf{O}$ xide $\mathbf{S}$ emiconductor                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOS           | $\mathbf{C} \mathbf{o} \mathbf{m} \mathbf{p} \mathbf{e} \mathbf{m} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} n$ |

| PMOS           | $\mathbf{P}\text{-type}\ \mathbf{M}\text{etal}\ \mathbf{O}\text{xide}\ \mathbf{S}\text{emiconductor}$                                              |

| NMOS           | $\mathbf{N}\text{-type}\ \mathbf{M}\text{etal}\ \mathbf{O}\text{xide}\ \mathbf{S}\text{emiconductor}$                                              |

| LHC            | Large Hadron Collider                                                                                                                              |

| $\mathbf{CMS}$ | Compact Muon Solenoid                                                                                                                              |

| MPA            | $\mathbf{M}$ acro $\mathbf{P}$ ixel $\mathbf{A}$ SIC                                                                                               |

| MIP            | $\mathbf{M}_{\text{inimum Ionizing Particle}}$                                                                                                     |

| HPD            | $\mathbf{H}$ ybrid $\mathbf{P}$ ixel $\mathbf{D}$ etector                                                                                          |

| $\mathbf{FE}$  | Front End                                                                                                                                          |

| $\mathbf{CSA}$ | Charge Sensitive Amplifier $\mathbf{A}$                                                                                                            |

| TOT            | $\mathbf{T}ime \ \mathbf{O}ver \ \mathbf{T}hreshold$                                                                                               |

| DAQ            | $\mathbf{D}$ ata $\mathbf{A}$ c $\mathbf{Q}$ uisition                                                                                              |

| RTL            | $ {\bf R} {\bf e} {\bf g} {\bf i} {\bf s} {\bf t} {\bf r} {\bf n} {\bf s} {\bf f} {\bf r} {\bf L} {\bf e} {\bf v} {\bf e} {\bf l} $                |

| VCD            | Value Change Dump                                                                                                                                  |

| TID            | Total Ionizing Dose                                                                                                                                |

| SEE            | Single Event Effect                                                                                                                                |

| MOS            | $\mathbf{M}$ etal $\mathbf{O}$ xide $\mathbf{S}$ emiconductor                                                                                      |

| STI            | Shallow Trench Isolation                                                                                                                           |

| LDD            | $\mathbf{Light} \ \mathbf{D} \mathbf{oped} \ \mathbf{D} \mathbf{rain}$                                                                             |

| SEU            | Single Event Upset                                                                |

|----------------|-----------------------------------------------------------------------------------|

| $\mathbf{LET}$ | Linear Energy Transfer                                                            |

| ELT            | Enclosed Layout Transistor                                                        |

| TMR            | $\mathbf{T} \text{riple } \mathbf{M} \text{odular } \mathbf{R} \text{edundancy}$  |

| ECC            | Error Correction Code                                                             |

| $\mathbf{SST}$ | Silicon Strip Tracker                                                             |

| L1             | Level 1                                                                           |

| IP             | Interaction Point                                                                 |

| LHC            | Large Hadron Collider                                                             |

| HLT            | $\mathbf{H} \mathrm{igh} \ \mathbf{L} \mathrm{evel} \ \mathbf{T} \mathrm{rigger}$ |

| BX             | Bunch Xcrossing                                                                   |

| MaPSA          | Macro Pixel Sub Assembly                                                          |

| CIC            | Concentrator IC                                                                   |

| LV             | Low Voltage powering                                                              |

| $\mathbf{HV}$  | $\mathbf{H}$ igh $\mathbf{V}$ oltage biasing                                      |

| DTC            | Data Trigger Control                                                              |

| SSA            | Short Strip ASIC                                                                  |

| $\mathbf{PS}$  | $\mathbf{P}_{ower} \ \mathbf{S}_{upply}$                                          |

| FEA            | $\mathbf{F}$ inite $\mathbf{E}$ lement $\mathbf{A}$ nalysis                       |

| STI            | ${\bf S} {\rm hallow} \ {\bf T} {\rm rench} \ {\bf I} {\rm solation}$             |

| DACs           | Digital to Analog Converters                                                      |

| DLL            | Delay Locked Loops                                                                |

| PSP            | $\mathbf{P} ower \ \mathbf{S} kew \ \mathbf{P} roduct$                            |

| ТоА            | $\mathbf{T}ime \ \mathbf{o}f \ \mathbf{A}rrival$                                  |

| BX-ID          | Bunch X<br>crossing Identification $\mathbf{D}\mathrm{ata}$                       |

| SNM            | $\mathbf{S}$ ignal to $\mathbf{N}$ oise $\mathbf{M}$ argin                        |

| SET            | Singe Event Transient                                                             |

| ESD            | $\mathbf{E}$ lectro $\mathbf{S}$ tatic $\mathbf{D}$ ischarge                      |

| SLVS           | $\mathbf{S}_{\text{calable Low Voltage Signaling}}$                               |

| FIFO           | First In First Out                                                                |

| RTL            | $\mathbf{R}$ egister $\mathbf{T}$ ransfer $\mathbf{L}$ evel                       |

| $\mathbf{MC}$  | Monte Carlo                                                                       |

| FPGA           | ${\bf F} ield \ {\bf P} rogrammable \ {\bf G} ate \ {\bf A} rray$                 |

|                |                                                                                   |

| $\mathbf{CML}$ | $\mathbf{C} \mathrm{urrent} \ \mathbf{M} \mathrm{ode} \ \mathbf{L} \mathrm{ogic}$ |

|----------------|-----------------------------------------------------------------------------------|

| $\mathbf{LSB}$ | ${\bf L} {\rm east} \ {\bf S} {\rm ignificant} \ {\bf B} {\rm it}$                |

| ENC            | $\mathbf{E}$ quivalent $\mathbf{N}$ oise $\mathbf{C}$ harge                       |

| UBM            | Under Bump Metalization                                                           |

| $\mathbf{MPW}$ | $\mathbf{M}$ ulti $\mathbf{P}$ roject $\mathbf{W}$ afer                           |

|                |                                                                                   |

# Chapter No. 1

# Introduction

In 1910 Wilson built his masterpiece and realised his dream: a cloud chamber that could visualise particle tracks – resembling something like the vapour trails left in the wake of an airplane. The next year he took his first photographs of tracks, exclaiming excitedly:

"they are as fine as little hairs"

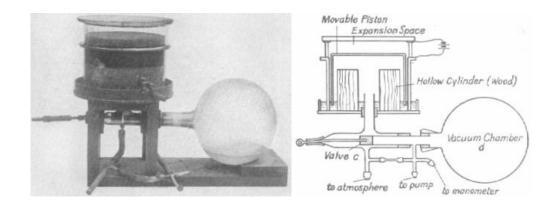

FIGURE 1.1: Wilson's 1910 Cloud Chamber. The diameter of the chamber is 16.5 cm, depth 3 cm. The movable piston is suddenly lowered by opening the value c and so connecting the vacuum chamber d with the part of the apparatus beneath the piston

For the first time, physicists could see the activity of the subatomic world. Wilson's cloud chamber (in figure 1.1) allowed visualization of the particle tracks coming from the natural radioactivity and from the cosmic rays. The particle could be easily identified by a visual analysis of the tracks left in real time. During this exciting time of exploring the unknown domain of the reality, many new particles like for example muon, pion and positron have been discovered by analyzing the "pictures" recorded from the cloud chambers. Wilson received the Nobel Prize in Physics in 1927 for his invention.

In 1973, a modified version of the cloud chamber, a bubble chamber called "Gargamelle" (see Figure 1.2(a)) allowed one of the greatest discoveries at European Organization for Nuclear Research (CERN): the neutral current. The bubble chamber is filled with a superheated liquid and contains a piston which allows to make a fast change of the pressure inside the chamber, thus bringing the liquid into a superheated state. As the particles traverse the superheated medium, they vaporize the liquid along their paths. These trails of bubbles were photographed and the films were analyzed manually (see Figure 1.2(b))

(A) The Gargamelle bubble chamber.

(B) Track reconstruction and analysis.

Towards the end of the 1970s, also semiconductor detectors began to be explored for their tracking capabilities. The spatial resolution in the 5-10  $\mu$ m range, the introduction of planar technology and the possibility to develop a dedicated readout for integration of detector and electronics provided the definitive boost to the use of this technology. Nowadays, all particle physics spectrometers have inbuilt vertex detectors, which deliver excellent results. The application of silicon tracking detectors has expanded to nuclear physics, solid-state physics, astrophysics, biology and medicine.

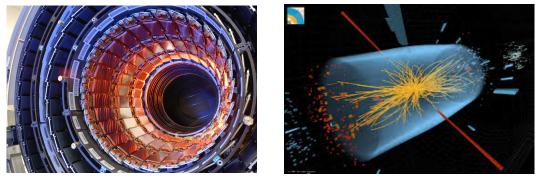

(A) The CMS Silicon Strip Tracker.

(B) CMS event from Run 1.

The four experiments on the Large Hadron Collider (LHC) at CERN use silicon detectors in their central vertexing/tracking systems. The largest silicon detector is the Silicon Strip Tracker (see Figure 1.3(a)) of the Compact Muon Solenoid (CMS) experiment: about  $210 \text{ m}^2$  of active silicon subdivided into many thousands of detector modules. The readout system is based on radiation hard electronics, fabricated in submicron commercial processes. It samples, amplifies, buffers and processes signals from the silicon detector. Samples are stored for a latency of a few  $\mu$ s, and are transmitted if a trigger is received.

As explained in the paper from the CMS collaboration [1], the CMS silicon strip tracker worked throughout LHC Run 1 from 2009 to 2013 (an event is shown in figure 1.3(b)), providing fundamental data to the discovery of a particle at about 125 GeV "consistent with the Higgs boson". Currently, the tracker is acquiring data during LHC Run 2 with a center of mass energy of 13 TeV.

The path of evolution of the LHC is now oriented towards the High Luminosity (HL-LHC) scenario, described in the preliminary design report [2], where event reconstruction will become impossible with the current detectors due to the increased luminosity and pile-up. A major upgrade is foreseen after 2020 which comprises the complete substitution of the CMS tracking system. This upgrade will introduce the concept of "intelligent" particle tracking which requires a front-end electronics capable of selecting the interesting physics events. Thanks to this capability the detector will provide selected information to the experiment back-end for every collision event, making possible the event reconstruction in the High Luminosity environment.

This work is dedicated to the development of the electronic system for intelligent particle tracking. In particular, it is focused on the desing of a dedicated readout electronics for hybrid pixel detector with particle discrimination capabilities, called Macro Pixel ASIC (MPA). This represents one of the key components and one of the main engineering challenges in the construction of the new CMS tracking system.

### 1.1 Main challenge

The capability of reconstructing physics event in the High Luminosity scenario together with the requirement of reducing the material makes the design of this new particle tracking system an hard engineering challenge. On the one hand, introducing the "intelligence" to select interesting information at front-end level requires very complex and power angry readout electronics. On the other hand, minimizing the amount of interaction with the incoming particle makes necessary the reduction of cooling material and consequently of power consumption.

Moreover, in order to keep the occupancy at a few percent and allow the track reconstruction at higher luminosity, the objective is to design a particle tracking system with an higher granularity (x5 respect current one) introducing pixelated sensors. Since the amount of material in the tracker must be sensitively lower than the current system, the use of pixel detector in some region requires an important effort in power and data readout optimization.

In particular, bandwidth and power limitations require a front-end module able to reduce "on-line" the amount of data to be transmitted to the back-end. The data selection is made by a novel concept of silicon detector modules, the so-called  $p_T$ -modules. The main novelty is the capability of tracking charged particles with a transverse momentum ( $p_T$ ) higher than a certain threshold (nominally 2 GeV/c) at every Bunch Crossing (BX) i.e every 25 ns. This value is provided by the intrinsic collision frequency of the collider. Thanks to the technology improvements, the front-end electronics can include complex digital circuits providing the "intelligence" to select and transmit the interesting events.

Furthermore, the requirement for radiation hardness increases of  $\sim$  one order of magnitude, and requires a full characterization of the technologies used as well as radiation hardening technique to limit the performance degradation. All these features cost in term of power, and require the introduction of power reduction technique as clock and memory gating, low power supply, and dedicated design for many components in the system.

In conclusion, this Ph.D thesis describes the development of an electronic device with particle discrimination capabilities for the readout of hybrid pixel detector. The main challenge is represented by the very low power density of  $< 100 \text{ mW/cm}^2$  available for the complex data processing required. Further studies address the problem related with high radiation level up to 100 Mrad and low temperature operation around  $-30^{\circ}$ C.

### 1.2 Thesis organization

This document is organized as follow:

- The second chapter (the first is this introduction) provides a theoretical background on the silicon detectors for High Energy Physics application with emphasis on the pixel electronics and readout system;

- The third chapter reports about the various aspects of the particle tracking system of the CMS experiment for the High Luminosity LHC. It provides an overview of the module architecture, power distribution, electronics components and readout system;

- The fourth chapter describes the author's work on the development of an electronic device with particle discrimination capabilities for the readout of hybrid pixel detector;

- The fifth chapter provides the description of the first prototype produced with a 65 nm CMOS technology. Electrical characterization as well as radiation test and module assembly results are reported.

# Chapter No. 2

# Silicon Detectors for High Energy Physics

This chapter describes the hybrid pixel detectors, which is the technology used for the electronic device developed in this thesis. The principles about silicon detector, readout electronics and their application in the silicon tracking systems for High Energy Physics experiments are introduced. The effect of radiation on the electronics and the technique for radiation hardness conclude the chapter.

### 2.1 Silicon for particle detection

Silicon presents several features which make its use favourable for particle detection [3]. The small energy band gap (1.12 eV at room temperature) produces a large number of charge carriers per unit of energy loss by the ionizing particles to be detected. Besides, the high material density  $(2.33 \text{ g/cm}^3)$  leads to a large energy loss per traversed length of the ionizing particle (3.8 MeV/cm for a minimum ionizing particle). It is then possible to build thin detectors that still produce large enough signals to be measured. The mobility of electrons and holes is high at room temperature, and only moderately influenced by doping. The charge can thus be rapidly collected, with collection times in the order of ns, and detectors can be used in high-rate environments. On the other hand, the silicon band gap is large enough to have a sufficiently low leakage current due to electron-hole pair generation.

As far as detector fabrication is concerned, the major advantage of silicon resides in the availability of a developed technology, which also allows the integration of detector and electronics on the same substrate. Moreover, its excellent mechanical rigidity allows the construction of self-supporting structures. An overview of silicon detector and of other particle detectors types can be found in Grupen and Swartz [4].

### 2.2 Detector structure

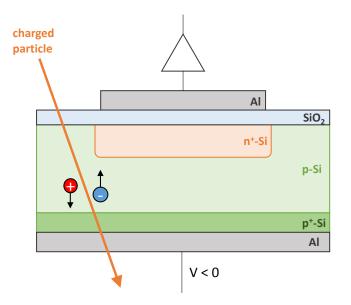

The basic element of silicon detectors, shown in figure 2.1, is a highly doped area of silicon on a resistive substrate of the opposite polarity acting as diode, which is then reverse-biased. Usually, the applied voltage is above the full depletion in order to use the whole volume for charge collection. Aluminium contacts connects the doped area to the readout electronics, while the back-side metallization provides the bias voltage.

If an ionizing particle is traversing the detector sensitive volume, electron-hole pairs are created along its path. The electric field in the depleted volume separates electrons and holes, which drift to the positive, respectively negative electrode inducing a current in the readout circuit. This current can be amplified and integrated by a charge sensitive amplifier resulting in an output voltage which is proportional to the collected charge.

FIGURE 2.1: p<sup>+</sup>-on-n silicon detector structure.

If the particle is stopped inside the detector, the measured charge is proportional to the energy of the particle, otherwise the particle will traverse the detector and the measured signal will be proportional to the energy loss of the particle. The energy loss is due to Coulomb interaction, Bremsstrahlung and scattering with the electrons and the core of the silicon atoms. The mean energy needed for the creation of an electron-hole pair in silicon is of 3.6 eV. In a silicon detector with a thickness of 200  $\mu$ m the most probable value of electron-hole pairs generated by a Minimum Ionizing Particle (MIP) is of 16000.

#### 2.2.1 Microstrip detector

Microstrip detectors are obtained by segmenting the doped side into strips over the full length of the detector. The strips are usually from few tens to few hundreds of  $\mu$ m apart, with the detector position resolution increasing with the decreasing strip pitch. The segmented side is usually covered by a few  $\mu$ m layers of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>, which protect the wafer during fabrication but also the detector itself. The Aluminium contacts can be placed directly on the doped strips (DC coupled detectors) or on a thin oxide or nitride layer, in which case the doped strips are capacitively connected to the readout electronics (AC coupled detectors). The latter solution is more expensive, due to the additional steps needed in the production, however capacitive coupling prevents leakage currents to flow through the electronics. The electrical connection between the strips and the readout electronics is usually realized via thin wires (wire-bonding).

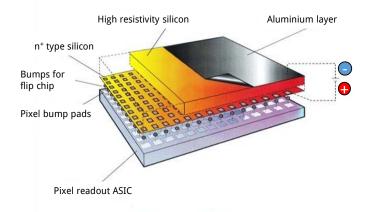

FIGURE 2.2: p<sup>+</sup>-on-n silicon sensor bump-bonded with the pixel readout ASIC.

### 2.2.2 Hybrid pixel detector

The planar process allows also the segmentation of one of the detector sides into a two-dimensional array of pixels. In this case an unambiguous 2-dimensional information about the position of the hit is achieved. The lateral size of pixels usually ranges between a few tens of  $\mu$ m and a few mm. The number of pixels and by that the number of readout channels increases linearly with the active area of the detector, while for silicon strip detectors the number of readout channels increases with the square root of the active detector area. A higher cost of pixel detectors results from the complexity of the readout electronics and of the mounting techniques, especially when the pixel dimensions are small. The use of pixel detectors is nevertheless inevitable in environments in which the detector occupancy is high, i.e. the sensor is traversed by many close-by particles. The use of strip detectors is in this case impossible due to ambiguities in the determination of the hit positions.

Several categories of pixel detector are available and they can be divided according to the technology used for charge collection. As mentioned in Rossi et Al. [5], Hybrid Pixel Detector (HPD) is the most used technology for HEP application. It uses highresistivity silicon substrates like in the case of microstrip detectors. The sensor is divided in pixels with the same pitch as the readout chip and the two are connected using flipchip technology. This technique, also known as controlled collapse chip connection or its acronym, C4, is a method for interconnecting chips to external circuitry with solder bumps that have been deposited onto the chip pads.

## 2.3 Readout ASIC

In HPD, since the two parts are produced separately, they can be optimized and designed independently from each other. Also, any standard CMOS technology can be used to design the readout electronics, so the advances in the lithographic process can be exploited to build more advanced systems, with smaller features and/or more features. The main disadvantage of this architecture is the cost of the flip chip process, especially for detectors with very small pixels.

#### 2.3.1 Front-End Electronics

Silicon sensors provide a typical signal in the range of tens of thousands of electrons within the collection time of a few nanoseconds. Front-end (FE) electronics process the signal from the sensor. Signal processing starts with the conversion of the signal charge into voltage which is performed by a Charge Sensitive Amplifier (CSA). This voltage is then discriminated and digitized. The resulting data are then coded into a comprehensive data format so that information about pixel address, time and amplitude can be disentangled from the data pattern. The common circuit blocks, shown in figure 2.3, are:

**The Charge Sensitive Amplifier** is an electronic circuit converting the electric charge Q to the voltage  $V_{out}$ . The core of the CSA is a voltage amplifier (core amplifier) providing high open loop gain A. The voltage amplifier has a capacitive feedback  $C_f$ .

FIGURE 2.3: Component of a generic front-end circuit.[5]

In the ideal case, the CSA behaves as an integrator with a closed loop gain inversely proportional to the feedback capacitance. In the real life, the finite open loop gain A of the core amplifier and the capacitance of the sensor  $C_d$  affects the gain:

$$V_{out} = \frac{Q}{C_f} \qquad g_{ideal} = \frac{1}{C_f} \qquad g = g_{ideal} \cdot \frac{1}{1 + \frac{1}{A} + \frac{C_d}{C_f A}}$$

(2.1)

The Feedback Circuit is required to define the DC-operation point of the charge sensitive preamplifier and to remove signal charges from the input node (or from  $C_f$ after the dynamic response of the amplifier) so that the preamplifier output voltage returns to its initial value.

The Leakage Compensation Circuit is implemented to sink all or a significant fraction of the leakage current. The sensor pixels are usually DC-coupled to the preamplifier inputs (this eliminates the need for biasing structures and AC-coupling capacitors on every sensor pixel), thus a leakage current  $I_{leak}$  of up to a few hundreds of nA after irradiation must be sunk/sourced by the pixel circuit.

**The Shaper** is an electronic filter, usually a band-pass, defining the bandwidth of the signal output of the CSA. The shaper helps to suppress the low and high frequency noise component and therefore improves the signal to noise ratio of the pixel detector.

The Discriminator compares the voltage at the output of the shaper (or CSA) with a reference value and sets its output either to HIGH level or LOW level depending on whether the input voltage is above or below the detection threshold, thus providing digitization with a single bit resolution. If the discriminator processes a signal from the CSA with a constant current source feedback, the length of the pulse at the output of the discriminator is directly proportional to the signal charge. The length of the pulse can be used for amplitude measurement called Time Over Threshold (TOT).

**Test Charge Injection** allows to verify the correct operation of the Front-End electronics. The controlled injection of known charges into the preamplifier is accomplished by applying a known voltage step to a well-defined calibration capacitor  $C_{inj}$ .

#### 2.3.2 Readout architecture

The digital hit signals of the discriminator must be further processed by circuitry in the pixel and at the chip periphery. The architecture of this readout depends strongly on the target application. In some application like medical device, the number of hits during a given time interval in every pixel can be sufficient. This requires simple counters in the pixels and a mechanism to transfer the counter values to I/Os. More detailed information is required in HEP applications. The positions, often also the times and possibly the corresponding pulse amplitudes, of all hits belonging to an interaction must be provided. This requires a timing precision of 25 ns (the bunch crossing interval) for the detectors at LHC. Concerning the readout of events, it can be started immediately after the interaction. Very often, however, a trigger system selects only a fraction of the events for readout in order to reduce the data volume sent to the Data Acquisition (DAQ). Since the trigger signal arrives with a significant delay, all hits must be identified and buffered for some time. At the LHC experiments, the current trigger latency is in the order of 2–3  $\mu$ s which corresponds to ~100 interactions. Almost all architectures perform an immediate zero suppression (i.e. process only pixels with amplitudes above a threshold) to reduce the size of the required buffers. Anyway, the limited buffer space available can lead to a loss of hits in high-rate events.

The choice of a suited architecture mainly depends on the available chip technology, on the required information and on the acceptable hit losses which can have very different characteristics for different readout concepts. Detailed simulations of the hit losses are therefore required before a choice can be made. Important parameters for analyzing the performance of a readout ASIC are the occupancy, the hit rate and the efficiency.

**Occupancy** is an indication of the utilization of the front-ends or of the data traffic inside a chip within a certain period. It indicates which fraction of its resources a readout chip is using at a given moment and is defined as:

$$O = \frac{N_{pixel_{hit}}}{TN_{pixel_{schip}}} \cdot 100\%$$

(2.2)

where O is the occupancy,  $N_{pixel_{hit}}$  the number of pixels containing hit information,  $N_{pixel_{schip}}$  the number of pixels in a full chip and T is a period. In many applications, occupancy is a time-averaged quantity and the period is not explicitly mentioned. In the case of HEP experiments on LHC, the occupancy is expressed as occupancy per Bunch Crossing.

**Hit rate** indicates the flux of particle on a certain area, which in the case of a readout ASIC is the active area of the sensor:

$$R = \frac{N_{pixel_{hit}}}{TA_{chip}} \tag{2.3}$$

where  $R_{hit}$  is the hit rate, T the acquisition time and  $A_{chip}$  area of a chip. Typically, hit rate is expressed as  $\frac{hits}{s \cdot cm^2}$ .

**Efficiency**. Occupancy and hit rate provide the quantity of data to be processed by a digital readout architecture. Instead, the efficiency of the digital readout architecture gives the ratio of the correct work performed by the architecture and is defined as:

$$E = \frac{N_{output}}{N_{input}} \tag{2.4}$$

where E is the readout efficiency,  $N_{output}$  the number of correct hits received at output of the chip and  $N_{input}$  the number of hits received from the output of the front-end stage.

#### 2.3.3 Power estimation technique

Another important parameter to estimate the performance of a readout electronics is its power consumption. Consequently, the contributions from logic circuits, interconnections, clock distribution, on chip memories and I/Os must be estimated during the design. Yet, power consumption of a system cannot be solely determined from high-level models, but the models can be used as tools to estimate the power consumption of the full architecture. Once an architecture with sufficient performance in terms of efficiency and latency has been found, a pixel region or even a pixel block can be designed at Register Transfer Level (RTL). This block can then be synthesized and a prototype of the physical design completed. A back-annotated netlist of this prototype can be used in simulation to obtain toggling rates for all nets in the design in the form of Value Change Dump (VCD) information. Again back-annotating this information into a physical design tool, an accurate estimate for power consumption of this block is obtained.

In a large design, the modelling of the interconnections becomes an important contribution to the total power consumption. Three wire categories are defined: local wires connect gates, intermediate wires connect subsystem and global wires, which includes data, control and address buses, connect different regions of the design. The wire width is assumed to be minimum, excluding the clock distribution, as the wire RC constant does not change with wire width. Knowing the data activity and the bus dimensions, the power contribution is calculated as:

$$P_{dynamic} = \alpha C_{total} V_{DD}{}^2 f \tag{2.5}$$

where  $\alpha$  is the switching factor,  $C_{total}$  the total capacitance,  $V_{DD}$  the power supply and f the operating frequency. The total capacitance includes also the repeaters input capacitances and the wire parasitics.

The I/O power is consumed in two parts. One is the power used to drive off-chip capacitance, bonding wires and the pad capacitance. The other is the power consumed by the driver itself. The value strongly depends on the architecture chosen for the driver: CMOS driver power depends on the activity and on the load capacitance, while differential driver uses a contant current. In the latter case, the power it does not change significantly with activity and load capacitance.

The estimation of on-chip memory power requires the characterization of the cell. The latter provides models which give the consumption for write and read operations, and consequently, the power consumption can be estimated knowing operating frequency and switching factors.

## 2.4 Partilce tracking system in HEP experiments

Silicon detectors are largely used in HEP experiments. This is also the case of the LHC which is the world's largest and most powerful particle collider, the largest, most complex experimental facility ever built, and the largest single machine in the world. It was built by CERN between 1998 and 2008 in collaboration with over 10,000 scientists and engineers from over 100 countries, as well as hundreds of universities and laboratories. As shown in figure 2.4, it lies in a tunnel 27 kilometres in circumference, as deep as 175 metres beneath the France–Switzerland border near Geneva, Switzerland.

The LHC accelerator is designed to collide protons at a centre of mass energy of 14 TeV and luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. Bunches of  $10^{11}$  protons collides every 25 ns (Bunch Crossing period). A detailed description of LHC can be found in its design report [6]. At the collision point, where about one billion proton-proton collisions are produced every seconds, are installed four large experiment. ATLAS [7] and CMS [8] are general purpose experiments, while ALICE [9] is dedicated to the study of heavy ion collision

FIGURE 2.4: Section of the LHC accelerator with the four experiment.

and LHCb [10] to the study of the b-physics. These experiments measure parameters of secondary particles produced in the collisions of the high energetic primary particles. In order to precisely measure trajectories and origins (vertices) of these secondary particles, the tracking detectors are situated very close to the collision point. Tracking and vertexing detectors are finely segmented silicon pixel or strip detector systems with short recovery time and high data throughput.

The tracking system, called tracker, is an essential component of a large HEP experiment. It performs a precise measurement of particle trajectories. Electrically charged particles are detected in sensitive layers of the detector.

The coordinates system used throughout this thesis is based on r, z,  $\phi$ ,  $\eta$  where:

- r is the radial distance from the nominal beam line;

- z axis coincides with the nominal beam line;

- $\phi$  is azimuthal angle and is measured in the plane perpendicular to the beam line;

- $\eta$ , called pseudorapidity, is the angle of a particle relative to the beam axis.

The sensitive layers of a tracker are usually arranged in barrel layers, coaxial with respect to z axis, and several end-cap disks to provide a broad angular coverage. Trackers operate in a strong magnetic oriented along z axis. The magnetic field curves the particle trajectories proportionally to their transverse momentum  $(p_T)$  as shown in figure 2.5. By measuring the curvature of the trajectory, the momentum of the particle is determined.

FIGURE 2.5: Structure and coordinate system of a generic tracking system. On the left it is shown the r- $\phi$  plane with an example of low and high  $p_T$  tracks. On the right it is shown the r-Z plane with the end caps layer at the end.

An additional challenge for the silicon detectors in HEP application is the resistance to radiation. Moreover in the case of the tracker, the detectors work in close proximity of the collision point and undergo extremely high radiation levels. For the application described in this thesis, the expected radiation level are more than three order of magnitude higher than the one reached in space application. This is the reason why, it is very important to study the radiation effects and to use radiation hardening technique which can prevent failures.

## 2.5 Radiation induced effect on CMOS technologies

Ionizing radiation can cause parametric degradation and ultimately functional failures in electronic devices. High energy electromagnetic radiation or particle radiation are a common hazard in environments such as outer space, high-altitude flight or near particle accelerators. These effects are particularly important for High Energy Physics detectors, as their role is to perform measurements in close proximity of particle collisions where they are exposed to higher radiation fluxes than in all the other applications. Thus, it is important to understand the different types of radiation effects and how to properly design electronics to minimize their impact on the performances of the systems.

Cumulative effects are gradual effects taking place during the whole lifetime of the electronics exposed in a radiation environment. A device sensitive to Total Ionizing Dose (TID) or displacement damage will exhibit failure in a radiation environment when the accumulated TID (or particle fluence) has reached its tolerance limits. It is therefore in principle possible to foresee when the failure will happen for a given, well known and characterized component. On the contrary, Single Event Effects (SEE) are due to the energy deposited by one single particle in the electronic device. Therefore, they can happen in any moment since the beginning of its operation in a radiation environment, and their probability is expressed in terms of cross-section.

### 2.5.1 Total Ionizing Dose effects

TID is the measurement of the dose, that is the energy, deposited in the material of interest by radiation in the form of ionization energy. The unit to measure it in the

FIGURE 2.6: Schematic energy band diagram for MOS structure, indicating major physical processes underlying radiation response[12].

International System (SI) is the Gray, but the radiation effects community still uses most often the old unit, the rad. The equivalence between the two is:

$$1 \operatorname{Gray}\left(\operatorname{Gy}\right) = 100 \operatorname{rad}.\tag{2.6}$$

TID effects are a typical case of cumulative effects. The ionization dose is deposited by particles passing through the materials constituting the electronic devices as described in Oldham and McLean [11] and shown in figure 2.6. These physical processes lead from the initial deposition of energy by ionizing radiation to the creation of ionization defects in the dielectric of a Metal-Oxide-Semiconductor (MOS) structure and can be summarized in: 1) the generation of electron hole pairs, 2) the prompt recombination of a fraction of the generated electron hole pairs, 3) the transport of free carriers remaining in the oxide, and either 4a) the formation of trapped charge via hole trapping in defect precursor sites or 4b) the formation of interface traps via reactions mostly involving hydrogen.

Using as reference the MOS structure shown in figure 2.7, the charges at the gate oxide of the transistor will screen or enhance (depending on the polarity of the transistor) the gate electric field. This will led to a threshold voltage shift. In lateral oxide as the Shallow Trench Isolation (STI) oxide used to isolate transistors from each other, they might attract an image charge in the semiconductor which can invert the interface and open leakage path [12]. This effect is typical of nMOS transistor. The defects formed at

FIGURE 2.7: n-channel and p-channel MOSFET's. Individual transistors are electricaly separated by STI trenches.

the interface between silicon and silicon dioxide (this is the region where the conductive channel forms in a MOS transistor) are called interface states. They trap charge from the channel, which leads to both a threshold voltage shift and also affects the mobility of carriers in the channel. The two types of effects, the trapping of holes and the creation of interface states, have a very different dynamic. Holes are trapped very quickly, and can be detrapped by thermal energy (this is called annealing). Therefore, increasing the temperature is a good method to anneal the trapped charge. Interface states instead exhibit a slow formation, and they do not anneal at temperature below about 400°C.